# A Platform-Based Approach to Verification and Synthesis of Linear Temporal Logic Specifications

Antonio Iannopollo

# Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2018-173 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2018/EECS-2018-173.html

December 14, 2018

Copyright © 2018, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Acknowledgement

The work in this dissertation and related publications has been supported by the National Science Foundation (NSF), via the project "ExCAPE: Expeditions in Computer Augmented Program Engineering" (CCF-1139138), by the Camozzi group, IBM, and United Technologies Corporation (UTC) via the iCyPhy consortium, and by TerraSwarm, one of six centers of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA.

### A Platform-Based Approach to Verification and Synthesis of Linear Temporal Logic Specifications

by

Antonio Iannopollo

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Alberto L. Sangiovanni-Vincentelli, Chair Professor Sanjit A. Seshia Professor Francesco Borrelli

Fall 2018

## A Platform-Based Approach to Verification and Synthesis of Linear Temporal Logic Specifications

Copyright 2018 by Antonio Iannopollo

### Abstract

### A Platform-Based Approach to Verification and Synthesis of Linear Temporal Logic Specifications

by

Antonio Iannopollo

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

### University of California, Berkeley

Professor Alberto L. Sangiovanni-Vincentelli, Chair

The design of Cyber-Physical Systems (CPS) is challenging as it requires coordination across several domains (e.g., functional, temporal, mechanical). To cope with complexity, rarely a CPS is built from scratch. Instead, it is assembled by reusing available components and subsystems. If a component is not available, then it is made to order according to a specification which ensures its compatibility with the rest of the system.

To achieve design goals faster while guaranteeing system safety, the correct instantiation of modules and subsystems is essential. Formal specifications, such as those expressed in Linear Temporal Logic (LTL), have the potential to drastically reduce design and implementation efforts by enabling rigorous requirement analysis and ensuring the correct composition of reusable designs. Composing formal specifications, however, is a tedious and error-prone activity, and the scalability of existing formal analysis techniques is still an issue.

In this dissertation, we present a set of techniques and algorithms that leverage compositional design principles to enable faster verification and correct-by-construction, platformbased synthesis of LTL specifications. In our framework, a design is a composition of several components (which could describe both hardware and software elements) represented through their specifications, expressed as LTL assume/guarantee interfaces, or contracts. The collection of all the available contracts, i.e., a library, describes the design platform. The contracts in the library are the building blocks of different possible designs, and they are simple enough that their correctness can be easily verified, yet complete enough to guarantee the correct and safe use of the components they represent.

Our contribution is two-fold. On the one hand, we address the verification task: given an existing composition of contracts from the library, we want to check whether it satisfies a set of desired requirements. We improve the scalability of existing verification techniques by leveraging pre-verified relations between contracts in the library. On the other hand, we enable specification synthesis: given a (possibly incomplete) set of desired system properties, we are able to automatically generate a composition of contracts, chosen from a library, that satisfies them. We do so by devising a set of algorithms based on formal inductive

synthesis, where a candidate is either accepted as correct or is used to infer new constraints and guide the synthesis process towards a solution. Additionally, we show how to increase the scalability of our approach by leveraging principles from the contract framework to decompose a synthesis problem into several independent tasks, which are simpler than the original problem. We validate our work by applying it to several industrial-relevant case studies, including the problem of verification and synthesis of a controller for the electrical power system of an aircraft. To Alessandro Ingegnoli, mentor and friend.

# Contents

| Co             | Contents                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                            |

|----------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lis            | st of                                   | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | v                                                                                                                                                          |

| List of Tables |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | viii                                                                                                                                                       |

| 1              | Intr<br>1.1<br>1.2<br>1.3<br>1.4        | oduction         Dissertation Overview         Main Contributions         Dissertation Outline         Related Publications                                                                                                                                                                                                                                                                                                                                                                                                            | <b>1</b><br>2<br>4<br>5<br>5                                                                                                                               |

| <b>2</b>       | Rela                                    | ated Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7                                                                                                                                                          |

| 3              | Prel<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | liminariesLinear Temporal Logic3.1.1 Reactions, Behaviors, and Synchronous Assertions3.1.2 Syntax of LTL formulas3.1.3 Semantics of LTL formulas3.1.4 LTL Applications, Satisfiability, and Realizability3.1.4 LTL Applications, Satisfiability, and Realizability3.2.1 Assume/Guarantee ContractsContract LibrariesLTL A/G Contracts3.4.1 Compatibility and Consistency for LTL A/G ContractsLTL Satisfiability and Validity as a Model Checking Problem3.5.1 LTL Validity as an SMV Program3.5.2 Structure of a NUXMV Counterexample | <ul> <li>11</li> <li>11</li> <li>12</li> <li>12</li> <li>13</li> <li>14</li> <li>15</li> <li>22</li> <li>23</li> <li>24</li> <li>24</li> <li>26</li> </ul> |

| 4              | <b>The</b><br>4.1<br>4.2<br>4.3         | Aircraft Electrical Power System Case StudyEPS DetailsEPS SpecificationEPS Library                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>28</b><br>29<br>30<br>32                                                                                                                                |

| <b>5</b> | Mo  | re Scalable Refinement Checking with Contract Libraries               | 35 |

|----------|-----|-----------------------------------------------------------------------|----|

|          | 5.1 | Introduction                                                          | 35 |

|          | 5.2 | Problem formulation                                                   | 36 |

|          |     | 5.2.1 Library of Contracts and Library Validation Problem             | 36 |

|          | 5.3 | Scalable Contract Refinement Checking                                 | 38 |

|          |     | 5.3.1 Library Validation                                              | 38 |

|          |     | 5.3.2 Checking Refinement with Contract Libraries                     | 38 |

|          | 5.4 | Application Example: the EPS Case Study                               | 43 |

|          | 5.5 | Conclusion                                                            | 46 |

|          | 0.0 |                                                                       | 10 |

| 6        |     | nstrained Synthesis from Libraries of Generic Components              | 47 |

|          | 6.1 | Introduction                                                          | 47 |

|          | 6.2 | Constrained Synthesis from Component Libraries (CSCL)                 | 49 |

|          |     | 6.2.1 A combinatorial analysis of CSCL                                | 52 |

|          |     | 6.2.2 Synthesis Constraints                                           | 53 |

|          | 6.3 | Solving a concrete instance of the CSCL problem                       | 56 |

|          |     | 6.3.1 The CSCL algorithm                                              | 58 |

|          |     | 6.3.2 An efficient representation for the synthesis constraints       | 60 |

|          | 6.4 | Implementing the CSCL algorithm                                       | 62 |

|          | 6.5 | Case studies                                                          | 64 |

|          |     | 6.5.1 The Brushless DC electric Motor Design (BLDC)                   | 64 |

|          |     | 6.5.2 The Aircraft Electrical Power System (EPS)                      | 68 |

|          | 6.6 | Conclusion                                                            | 71 |

| _        | ~   |                                                                       |    |

| 7        | ÷   | thesis from Libraries of LTL A/G Contracts                            | 73 |

|          | 7.1 | Introduction                                                          | 73 |

|          | 7.2 | Constrained Synthesis from LTL A/G Contracts Libraries (LTL-CSCL)     | 74 |

|          | 7.3 | Solving a Simplified Version of the LTL-CSCL Problem                  | 75 |

|          |     | 7.3.1 LTL-CSCL as a CEGIS instance                                    | 75 |

|          |     | 7.3.2 Implementation of the CEGIS Paradigm for the LTL-CSCL problem . | 77 |

|          |     | 7.3.3 Handling Infinite Input Sequences                               | 78 |

|          | 7.4 | Performance Considerations                                            | 81 |

|          |     | 7.4.1 Nondeterminism, Cycles, and Depth                               | 82 |

|          | 7.5 | Addressing the Full LTL-CSCL Problem                                  | 83 |

|          | 7.6 | Putting It All Together: Revisited LTL-CSCL                           | 85 |

|          | 7.7 | Evaluation                                                            | 86 |

|          |     | 7.7.1 The BLDC problem                                                | 87 |

|          |     | 7.7.2 The EPS problem                                                 | 88 |

|          |     | 7.7.3 The SPI Analog-to-Digital Converter problem                     | 89 |

|          | 7.8 | Conclusion                                                            | 92 |

| 8  | Spee         | cification Decomposition for Synthesis from Libraries of LTL A/G |     |  |

|----|--------------|------------------------------------------------------------------|-----|--|

|    | Con          | itracts                                                          | 94  |  |

|    | 8.1          | Introduction                                                     | 94  |  |

|    | 8.2          | Preliminaries                                                    | 95  |  |

|    | 8.3          | Decomposing Contracts                                            | 95  |  |

|    |              | 8.3.1 Projection for LTL A/G Contracts                           | 96  |  |

|    | 8.4          | Solving the Contract Decomposition Problem                       | 98  |  |

|    |              | 8.4.1 Using Projections for Synthesis                            | 99  |  |

|    | 8.5          | An Efficient Decomposition Algorithm                             | 101 |  |

|    |              | 8.5.1 Algorithm DecomposeContract is sound                       | 103 |  |

|    | 8.6          | Evaluation                                                       | 103 |  |

|    |              | 8.6.1 The EPS problem                                            | 103 |  |

|    |              | 8.6.2 The SPI-ADC problem                                        | 104 |  |

|    | 8.7          | Conclusion                                                       | 105 |  |

| 9  | Con          | nclusions                                                        | 107 |  |

| Bi | Bibliography |                                                                  |     |  |

iv

# List of Figures

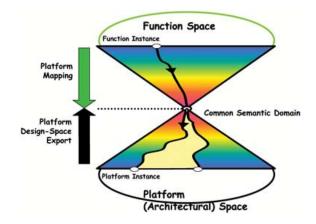

| 2.1                               | A graphical representation of the mapping process typical of Platform-Based Design. A specification, i.e., function, is implemented as a composition of elements in a more concrete abstraction levels through a mapping process. Image from [72].                                                                                                        | 7              |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.1<br>3.2<br>3.3                 | An SMV program implementing a 3-bit counter <sup>1</sup>                                                                                                                                                                                                                                                                                                  | 25<br>26<br>27 |

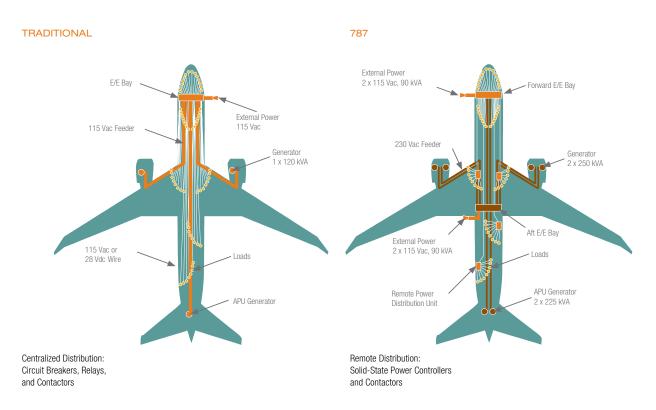

| <ul><li>4.1</li><li>4.2</li></ul> | A comparison between the EPS system in traditional aircrafts and the one typical of modern aircrafts, such as the Boeing 787. The main difference is the distributed architecture of the modern design, introduced to increase reliability and reduce cost. The details about the components in the picture are discussed in Section 4.1. Image from [79] | 29             |

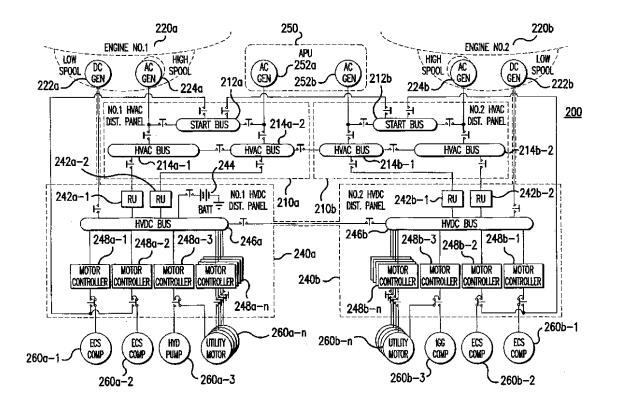

|                                   | the power flow.                                                                                                                                                                                                                                                                                                                                           | 30             |

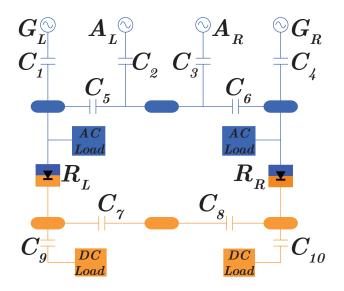

| 4.3                               | Simplified single line diagram of the EPS [58]                                                                                                                                                                                                                                                                                                            | 31             |

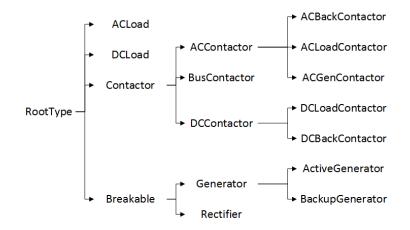

| 4.4                               | Tree representing the typeset used in the EPS case study                                                                                                                                                                                                                                                                                                  | 31             |

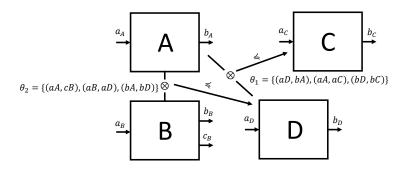

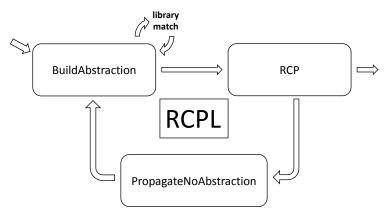

| $5.1 \\ 5.2 \\ 5.3$               | Example contract library with refinement assertions                                                                                                                                                                                                                                                                                                       | 37<br>39       |

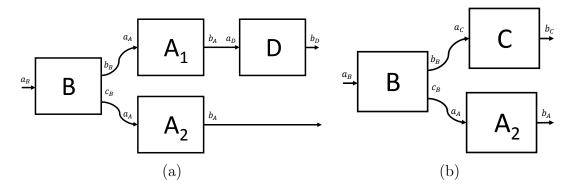

| 0.0                               | (a) and its abstraction (b)                                                                                                                                                                                                                                                                                                                               | 43             |

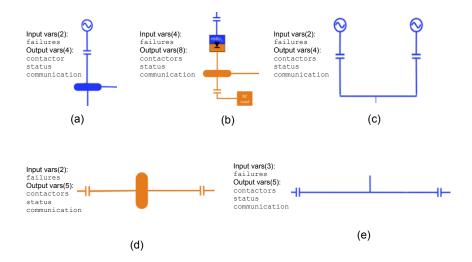

| 5.4                               | Subsets of components of the EPS plant and number of variables associated with<br>the related contracts, including communications variables and variables related to                                                                                                                                                                                      | 10             |

| 5.5                               | the health status of plant components (e.g. buses, contactors)                                                                                                                                                                                                                                                                                            | 43             |

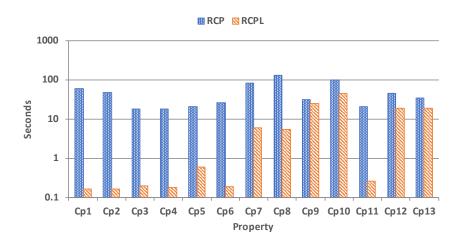

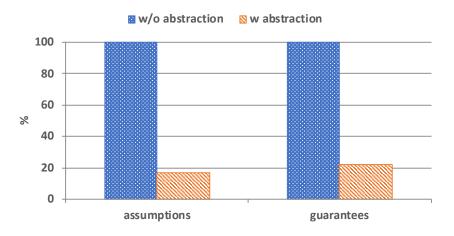

|                                   | verification of the set of 13 property contracts                                                                                                                                                                                                                                                                                                          | 45             |

| 5.6                               | LTL formula size ratio of the abstract EPS contract w.r.t. the non-abstract version                                                                                                                                                                                                                                                                       | 45             |

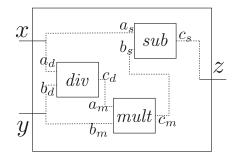

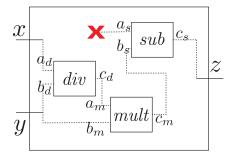

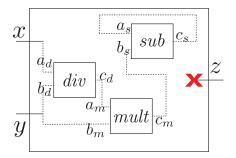

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Modulo operation composition from elements in $L_{op}$                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $52 \\ 54$ |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| $\begin{array}{c} 6.3 \\ 6.4 \end{array}$ | Illegal composition of elements in $L_{op}$ (z disconnected)                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55         |

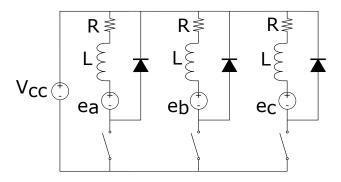

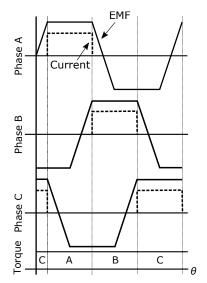

| 6.5                                       | represent the Electromotive Force (EMF) for the three phases of the motor [36].<br>Waveforms for the half bridge driver. Input current from the driver induces torque<br>through one of the three phases of the motor at a time [36]. To ensure the proper<br>forward rotation of the rotor, inputs from the driver need to be sent in a specific<br>order.                                                                                                                                                       | 65<br>66   |

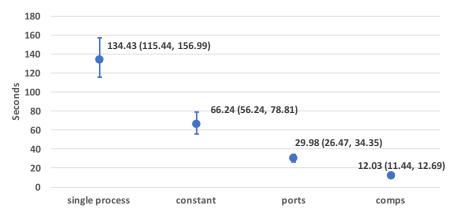

| 6.6                                       | Summary of the results for the BLDC experiments. We synthesized a controller<br>using the single process CSCL algorithm first, with a constant cost function.<br>Then, we used the Parallel CSCL algorithm with a constant cost function,<br>minimizing the number of components, and minimizing the number of ports. For<br>each category, we ran 100 experiments. Each point represents the mean synthesis<br>time, while the bars represent its 95% confidence interval, also indicated within<br>parentheses. | 68         |

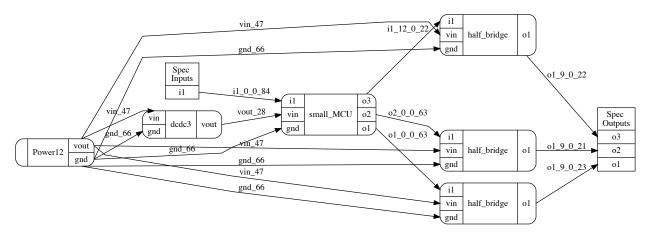

| 6.7                                       | Graphical representation of a synthesized design. Names on arrows represent port renamings induced by the function $\theta$ , returned by the synthesis process                                                                                                                                                                                                                                                                                                                                                   | 68         |

| 6.8                                       | BPCU synthesis times in the various experiments. In each graph, each point has<br>been computed running 100 experiments. The central point represents the mean,                                                                                                                                                                                                                                                                                                                                                   | 08         |

| 6.9                                       | while bars represent the 95% confidence interval for the mean. The horizontal axis refers to the subset of specifications considered in each experiment Graphical representation of a synthesized design satisfying all 9 specifications with                                                                                                                                                                                                                                                                     | 70         |

| 6.10                                      | minimal number of connected ports. Names on arrows represent port renamings<br>induced by the function $\theta$ , returned by the synthesis process                                                                                                                                                                                                                                                                                                                                                               | 71<br>72   |

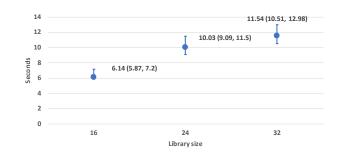

| 7.1                                       | Summary of the results for the BLDC experiments. We synthesized a controller                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12         |

| 1.1                                       | using three libraries including 16, 24, and 32 contracts respectively, for the same specification. For each category, we ran 80 experiments, and then bootstrapped the samples. Each point represents the bootstrap mean for the synthesis time, while the bars represent its 95% confidence interval, also indicated within parentheses.                                                                                                                                                                         | 88         |

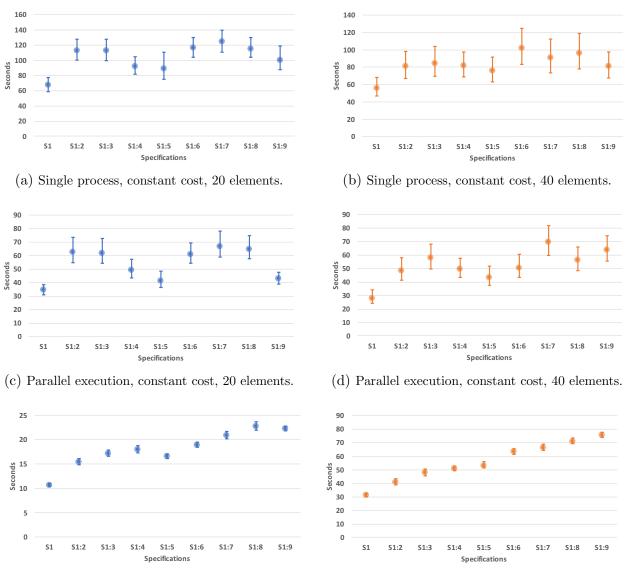

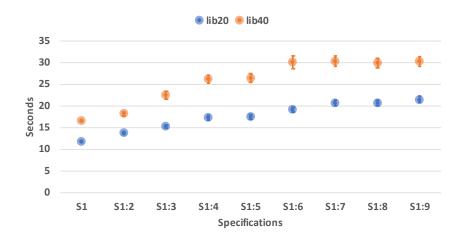

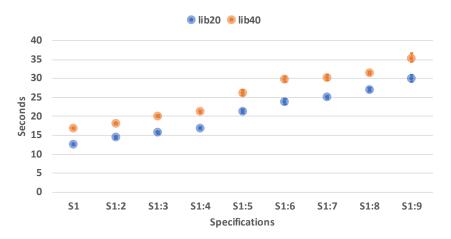

| 7.2                                       | Summary of the EPS experiments. We synthesized a controller using two different libraries, one with 20 and the other with 40 contracts, defined in Table 4.2. For each category, we ran 80 experiments and then bootstrapped the sample. Each point represents the bootstrap mean synthesis time, while the bars represent its                                                                                                                                                                                    |            |

|                                           | 95% bootstrap confidence interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 88         |

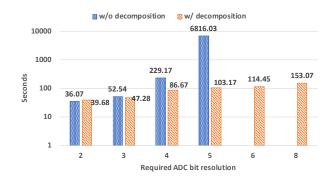

| 7.3 | Synthesis times with and without specification decomposition. The horizontal axis indicates a subset of the guarantees in Table 4.1, while the vertical one, in                                                                                                                                                                | 0.0 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.4 | logarithmic scale, the synthesis time                                                                                                                                                                                                                                                                                          | 90  |

|     | The graph is in logarithmic scale.                                                                                                                                                                                                                                                                                             | 92  |

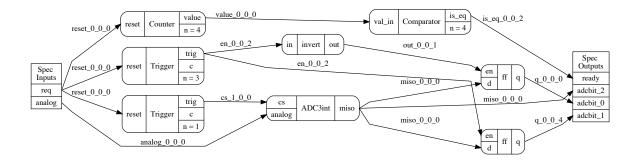

| 7.5 | Typical synthesized composition for the ADC-SPI problem, in case of the specification and ADC with 3 bit resolution $(n = 3)$ .                                                                                                                                                                                                | 92  |

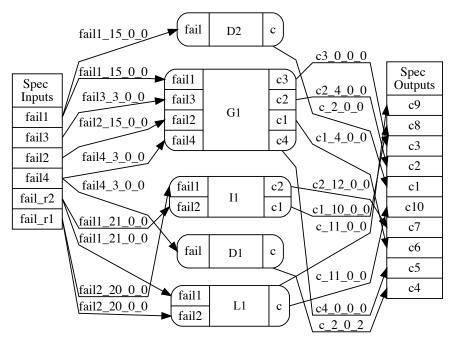

| 8.1 | Summary of the EPS experiments. We synthesized a controller using two different libraries, one with 20 and the other with 40 contracts, defined in Table 4.2. For each category, we ran 30 experiments and then bootstrapped the sample. Each point represents the bootstrap mean synthesis time, while the bars represent its |     |

|     | 95% bootstrap confidence interval.                                                                                                                                                                                                                                                                                             | 104 |

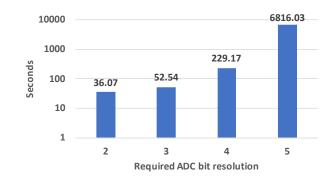

| 8.2 | Summary of the results for the ADC-SPI experiments, for specifications with parameter $n \in \{2, 3, 4, 5, 6, 8\}$ and library size of 11 contracts, respectively. Each library had the appropriate ADC according to $n$ . The other contracts, including                                                                      |     |

|     | the parametric ones, were replicated as needed. The graph is in logarithmic scale.                                                                                                                                                                                                                                             | 105 |

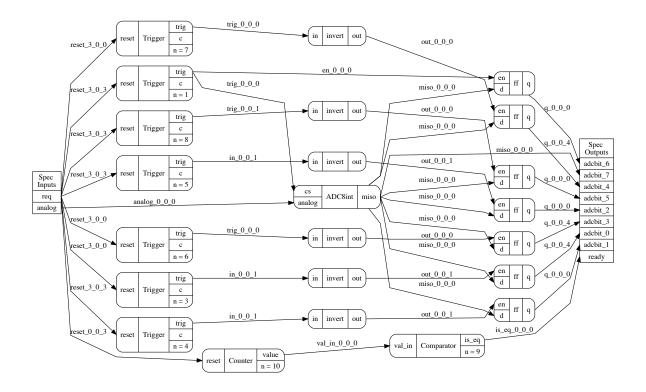

| 8.3 | Typical synthesized composition for the ADC-SPI problem, in case of the specification and ADC with 8-bit resolution $(n = 8)$ .                                                                                                                                                                                                | 106 |

# List of Tables

| <ul><li>4.1</li><li>4.2</li></ul> | Set of system specifications $S_1  dots S_9$ to satisfy. Input ports reflect the status<br>of EPS elements (such as generators), while output ports represent contactors.<br>Assumptions are common to all the specifications and capture the expectation<br>that when a component fails, it will not be operational again. Guarantees include<br>the promise that faulty generators will be isolated, no short-circuit will happen,<br>and loads will always be powered. $\dots$ Structure of the EPS library. In our experiments, the library contained first 2 and                   | 32       |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                   | then 4 instances of these components, for a total of 20 and 40 elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34       |

| 6.1                               | Specification for the BLDC synthesis problem. The interface has one input, which<br>is a 3V pin from the Hall effect sensor (its type is <i>IOPin3</i> ), and three outputs<br>as 12V pins to drive the electromagnets of the motor. The specification assumes<br>that the input is initially negative and, once started, it will keep commuting. The<br>guarantee is that only one output line will be active at each commutation point in<br>a round-robin fashion. The specification also requires distinct outputs, meaning<br>that the sentent he centrelied has the sentent work. | 66       |

| 6.2                               | that they cannot be controlled by the same port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>67 |

| 6.3                               | Summary of the EPS experiments. For each specification subset (one for each row), we report the mean value and its 95% confidence interval. All values are expressed in seconds. Experiments named "Constant Cost" and "Minimize Ports" are run using parallel processes.                                                                                                                                                                                                                                                                                                               | 69       |

| 7.1                               | Structure of the BLDC library, which contains three separate instances of each component. This library is a revisited version of the one in Table 6.2, which now                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 7.2                               | includes only deterministic contracts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 87       |

|                                   | its 95% confidence interval (in parentheses). All values are expressed in seconds.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 89       |

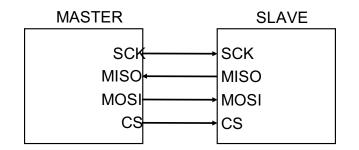

- 7.3 Specification for the SPI-ADC synthesis problem parameterized for n (in the experiments, n ∈ {2,3,4,5}). The contract reads an analog input, represented as an integer variable, and a request line. After n + 2 clock cycles, it needs to assert a ready signal. Moreover, it needs to compute the *i*-th bit of the analog input for each output bit b<sub>i</sub>, representing the state of the analog signal two cycles after the request line was asserted. The fractions represent integer division, where the expression a/2<sup>i</sup> 2 · a/2<sup>i+1</sup> computes the *i*-th bit of *a*. Port types indicate the type label, used to describe each port, and their domain (integer or Boolean). . . . 90

7.4 Structure of the ADC-SPI library. The ADC component is used, in the experiments, with n ∈ {2,3,4,5}. Some components are parameterized, if in their output ports

### Acknowledgments

Being a Ph.D. student is like being in the middle of a journey. It can be difficult at times, but every step forward brings you new adventures, excitement, and awe. As with every journey, the people you walk with can make an immense difference in the way you remember the experience, even when you share with them only a small part of the path. I have been extremely lucky in meeting so many wonderful individuals along the way and, in these few lines, I want to thank them for their support and friendship.

First, I would like to thank my adviser, Prof. Alberto Sangiovanni-Vincentelli, who has been an extraordinary guide and inspiration in these past few years. He has always been there for me and, without his help, I would not be here today. He never ceases to amaze me with the breadth and depth of his knowledge and inquisitive mind.

Many thanks to Prof. Stavros Tripakis, who has been my unofficial co-adviser in my first years in Berkeley. I really enjoyed working with him, and I learned a lot during our discussions about computer science topics such as formal languages and interfaces, but also about politics and movies.

I am extremely grateful to Prof. Sanjit Seshia and Prof. Edward Lee, who have been a constant positive presence during these years. Sanjit, one of my first teachers here in Berkeley, introduced me to the beauty of formal methods. His brilliant work has greatly influenced my research. Edward has been a wonderful mentor. Among his many qualities, I admire his scientific acumen and the passion he puts in his work. His course on models of computation has been one of the most enjoyable I have ever taken. I would also like to thank Prof. Francesco Borrelli, who has served as a member of my qualifying exam and dissertation committees. His comments on my research were precious.

I have had the fortune to meet, here in Berkeley, some of the most brilliant students, researchers, and engineers in the world. I am thankful to call many of them great friends of mine. Thanks to Nikunj Bajaj, Alberto Puggelli, Marten Lohstroh, Shromona Ghosh, Tommaso Dreossi, Ben Zhang, Alberto Tempia Bonda, Inigo Incer, Fabio Cremona, Ankush Desai, John Finn, Baruch Sterin, Baihong Jin, Eddie Kim, Ankush Desai, Xiangyu Yue, Hokeun Kim, and Daniela De Venuto. We spent a lot of time together, both inside and outside of UC Berkeley, and I enjoyed every minute. My gratitude also goes to Chung-Wei Lin, Liangpeng Guo, Mehdi Maasoumy, Chris Shaver, Christos Stergiou, Matt Weber, Gil Lederman, Ilge Akkaya, Rohit Ramesh, Tianshi Wang, Richard Lin, Tomi Raty, Garvit Juniwal, Anil Aswani, Maryam Bagheri, Elisabetta Alfonsetti, Yen-Sheng Ho, Pangun Park, Raaz Dwivedi, Wei Yang Tan, Rohit Sinha, Ben Caulfield, Daniel Fremont, Yi-Chin Wu, Nishant Totla, and all the other DOP center residents. You guys rock! I am also extremely grateful to Jessica Gamble and Shirley Salanio for helping me navigate the bureaucracy of the EECS department and being super supportive.

I would like to thank United Technologies Corporation (UTC) and the Camozzi Group for the collaboration opportunities, and for the chance to learn a lot and meet so many brilliant collaborators. Thanks especially to Luiz Bacellar, Clas Jacobson, Michael Regelski, Dario Ferrarini, Andrea Camisani, and all the Camozzi research team. I also would like to thank the National Science Foundation (NSF), the ICyPhy Consortium, the Terraswarm Research Center, and the John R. Mott Scholarship Foundation for their support.

My gratitude goes also to the many great teachers and mentors that I had in my life. I will always be immensely grateful to Alessandro Ingegnoli, to whom I dedicate this dissertation, for believing in me and being the one who started the sequence of events that brought me here today. Among many others, I would also like to give a special thank to Marco Sgroi, Prof. Daniel Bovet, and Lucio Ficara.

Finally, I want to thank my family for being so incredibly loving and supporting. To my wife, Lauren, goes the deepest gratitude for her love, enthusiasm, and patience during these years of unpredictable work hours and last minute schedules. I could not have asked for a better partner. You are my oasis in the desert, and make every day so much better! Thanks to Santiago, Enza, Christopher, Giovanni, Karin, Alan, Charlotte, Matthew, zia Maria, and zio Guglielmo. You are the best family one could ask for. And, above everything else, thanks to my parents, Caterina and Girolamo, for being so wonderful and for giving me the best chances in life. I wish to be to my children what you have been for me.

# Chapter 1 Introduction

System design is a process that starts with a high-level idea of what the system should be and ends with a blueprint for its construction. During design, the initial idea is refined iteratively until no ambiguity is left, proceeding in a top-down fashion. Requirements about the system as a whole are used to define specifications for its subsystems, which, in turn, are broken-down into specifications for lower-level components, following a fractal-like process [72, 83]. At each step, more and more details about the final design are added, until there is enough information to build the system.

To reduce costs, and shorten time-to-market, modern design methodologies emphasize design reuse by leveraging platforms, which are libraries of parametric components which include functional and non-functional details and define rules for their composition. A design iteration, then, becomes a mapping process in which a specification is realized in terms of platform components. Consider, for instance, the automotive design process. Original Equipment Manufacturers (OEMs), e.g., BMW or Ford, design several vehicles adapting the same floorplan, axles, etc., and by incorporating subsystems, such as suspension control, provided by tier 1 suppliers. In turn, tier 1 suppliers are able to build subsystems to order by adapting their own platform, and using components provided by tier 2 suppliers. This approach to design is formalized in a methodology called Platform-Based Design (PBD), which has been successfully applied in areas including electronic, automotive, and network design [74, 72, 77].

When system complexity increases, especially for safety-critical systems, maintaining consistency between design iterations and level of abstractions is an onerous task. When done manually, in fact, the refinement of a specification in terms of a composition of platform elements can introduce errors, and the inevitable design reviews sessions are costly and ineffective [23]. Formal languages, such as temporal logic [68, 52], can help to formalize specifications and maximize the benefits of methodologies, such as PBD, by enabling automated reasoning. Specifications can be effectively described, at different levels of abstractions, by mathematical constraints which define what behaviors are to be expected by a correct implementation provided some assumptions on the environment in which the implementation will need to operate. At the same time, components in the platform expose formal descriptions of their capabilities, which are formally consistent with the specification, meaning that the verification of compliance reduces to solving a mathematical problem. The difference between specification and components is, then, quantitative. The specification will likely describe a smaller set of desirable, higher level properties of the system. It will not include, however, all the details of the necessary subsystems, which will be added to the design only when a suitable platform component is selected and instantiated. For instance, a specification might define what is the desired voltage from a battery module to power a device. A component in the library could satisfy the voltage requirement, and it might add additional constraints such as safety measures to manage overheating, or details about its interconnections. Once verified, then, the mapping process of PBD produces an instance of the platform, where each component represents a new specification for the successive iteration.

Having a formal description of design elements brings at least two substantial benefits to the design process. First, it allows for the automatic verification that a composition of platform elements implements, or refines, the specification. Second, it enables synthesis, i.e., the automatic generation of a composition of components which refines the specification. Yet, especially when described by temporal constraints, scalability remains an issue even for simple designs. In this dissertation, we describe methods to handle complexity when design elements are described by temporal constraints, and improve scalability.

## 1.1 Dissertation Overview

In this dissertation, we focus on specifications and platform components characterized by formal interfaces. Each design element specifies its static interface as a set of inputs and output ports, and defines its set of behaviors by means of Linear Temporal Logic (LTL) formulas [68, 80]. LTL is especially useful in expressing specifications for discrete systems, where the ordering of events matters more than their precise timing. A number of domains are characterized well, functionally, by LTL. Examples include software, communication protocols, motion planning, reactive systems, and digital components in general [12, 25, 7, 52, 65, 63, 86].

To successfully apply techniques and methodologies that support automated reasoning, these design elements need to interact with each other in a well-defined manner. Indeed, components first need a mechanism to be interconnected together to represent a single, coherent subsystem which then needs to be compared to the specification, to verify correctness. Thus, design elements need to support composition (horizontal relation), and refinement verification (vertical relation). We leverage Assume/Guarantee (A/G) contracts [75, 11, 10, 2, 62, 30] to rigorously characterize components interfaces. Component ports, then, represent contract variables, and LTL formulas describe explicitly assumptions, i.e., what the component expects from its environment, and guarantees, i.e., its promise. The resulting LTL A/G contracts, analyzed in Chapter 3, formalize notions such as compatibility (are there legal environment for a component?) and consistency (are there legal implementations?), and support composition and refinement. Contracts, in this case, can be seen as the language unifying PBD, where all the considerations made about the libraries of components (platforms) apply to libraries of contracts, too. Hence, both the system specification and the platform components are described by LTL A/G contracts, and contract libraries represent domain knowledge that will be added to the design upon instantiation of their elements. Our goal is to verify, for such contracts, the mapping process of PBD first, and then to automate it. The result will be a formally correct instantiation of the platform, which in this case will be a composition of LTL A/G contracts. Therefore, in this dissertation, we talk about verification and synthesis of LTL specifications.

At the core of the techniques and algorithms that we develop there is the capability of manipulating LTL A/G contracts and verifying refinement among them, which can be reduced to a model checking problem [33, 19]. Our first goal is to improve the performance of current approaches to the refinement checking problem when verifying the compliance to a specification of a composition of contracts, i.e., the system, provided by the user. In Chapter 5, we show how pre-verified refinement relations stored in the contract library allow for faster verification of specification compliance by the system, by building decremental abstractions. In this case, the library contains both basic components and several subsystems realized with those components. Building abstractions, then, reduces to a mapping problem. We show that this approach can improve dramatically the verification performance by applying it to a case study of industrial relevance, i.e., the realization of a controller for the Electrical Power System (EPS) of an aircraft. We describe the EPS problem in Chapter 4, and we will use it as a common example throughout the dissertation.

We, then, direct our attention to the synthesis of correct composition of contracts, proceeding stepwise. First, in Chapter 6, we concentrate on the problem of synthesis assuming that the only output of the refinement verification procedure is a simple yes/no answer. We call this problem "Constrained Synthesis from Component Libraries" (CSCL), and we devise a synthesis procedure based on the Oracle-Guided Inductive Synthesis (OGIS) paradigm [49, 48], where erroneous candidate solutions are used to infer new constraints to guide the synthesis process. In this case, the only information available to the solver are the erroneous candidates themselves, which are used to identify equivalent compositions in the library so that they won't appear as candidate solutions in the future. The main advantage of this approach is that the verification tasks are independent one another, allowing for the parallel execution of the resulting algorithm. Additionally, as we point out in the chapter, this technique is loosely related to the use of LTL A/G contracts, and we argue that it could be applicable to other formalisms, too.

Then, in Chapter 7, we change our perspective and focus exclusively on LTL A/G contracts. Here we tighten the assumptions on the refinement verification process, that now is required to return, when the refinement does not hold, counterexample traces over the contract variables in addition to the usual yes/no answer. The result is a procedure based on a specialization of OGIS called CounterExample-Guided Inductive Synthesis (CEGIS) [81, 49, 50] where we deal with infinite-length counterexamples by encoding them as state machines. Each state machine, then, is integrated into the refinement verification process

of the subsequent CEGIS iteration. For this problem, we show that our approach indeed terminates in spite of an infinite input space, and discuss several performance improvement techniques.

Finally, in Chapter 8, we address the problem of increasing the scalability of the synthesis techniques we developed in the previous chapters. We do so by leveraging contract properties to decompose, under certain conditions, a specification in several independent synthesis problems. Each synthesis task is simpler than the original one, as the resulting decomposed specification will have fewer ports to be mapped into a candidate composition of components. Thus, this allows us to handle synthesis problems that are unfeasible with the other techniques. We apply all the synthesis techniques that we introduced to several case studies, including the EPS synthesis problem.

Part of the software and experiments discussed in this dissertation have been implemented in a tool called  $PYCO^1$ .

## **1.2** Main Contributions

The focus of this dissertation is the following:

System design automation can be fully achieved only through the definition and application of rigorous analysis and synthesis techniques. In this dissertation we study, propose, and validate such techniques and algorithms enabling platform-based verification and synthesis of refinements of linear temporal logic specifications.

The main theoretical results in this dissertation are related to the problem of synthesis of contract compositions. We provide, in Chapter 3, a definition of LTL A/G contracts that supports disjoint sets of variables and describe the mechanisms necessary to interconnect them. This adds flexibility when indicating compositions and mappings between specification and library components. In Chapter 6, we provide a general formulation of the CSCL problem, and analyze its complexity. We provide two synthesis approaches based the OGIS paradigm justified by different capabilities of the verification engine(Chapters 6 and 7). We also introduce a novel concept of contract decomposition, in Chapter 8, based on projections, and show how it can be used in the context of the CSCL problem, where synthesis can be broken down into several simpler tasks, guaranteeing the same solution space of the original problem.

We propose, and describe algorithmically, a number of techniques related to verification and synthesis of compositions of contracts. We show how to leverage relations in a library to speed-up refinement verification, and apply it to the EPS case study (Chapter 5). We develop and implement algorithms for all the synthesis techniques we discuss, and evaluate them in several case studies.

<sup>&</sup>lt;sup>1</sup>https://github.com/ianno/pyco

## **1.3** Dissertation Outline

The rest of the dissertation is organized as follows.

In Chapter 2, we survey the related literature and discuss its relation with our work. In Chapter 3, then, we formalize the core concepts that will support the rest of the work. We introduce A/G contracts and describe a variant of the theoretical framework in which contracts can be defined over disjoint sets of variables and connections are explicitly referenced. Additionally, we show how to express assumptions and guarantees of contracts as LTL formulas, and discuss details on techniques and tools to perform basic operations, such as refinement check, which becomes a model checking problem.

In Chapter 4, we introduce the main case study, i.e., the design of a controller for an aircraft electrical power distribution system. We describe the system and then formalize the controller specification as an LTL A/G contract. We also illustrate the contract library that will be used as a reference for both the verification and the synthesis tasks.

In Chapter 5, we present the results about the scalable refinement check technique that leverage library information to build abstractions of compositions. This work is based on a collaboration with Pierluigi Nuzzo, Stavros Tripakis, and Alberto Sangiovanni-Vincentelli [41].

In Chapter 6, we introduce the problem of constrained synthesis from component libraries. After analyzing it, we provide a solution based on the OGIS approach which relies on minimal information from the verification engine, i.e., only a yes/no answer. This work has been developed jointly with Stavros Tripakis and Alberto Sangiovanni-Vincentelli [43, 44], while one of the examples has been developed with Richard Lin and Rohit Ramesh.

In Chapter 7, we specialize the CSCL problem and its solution to handle exclusively LTL A/G contracts, requiring the verification engine to returns counterexamples over the contract variables. The solution is a CEGIS algorithm which encodes the counterexamples as state machines. This work is novel. One of the examples has been developed with Íñigo Íncer Romeo.

In Chapter 8, we discuss how to improve the scalability of the synthesis algorithms described in the previous chapters by decomposing specifications, introducing the notion of projection for LTL A/G contracts. This is a joint work with Stavros Tripakis and Alberto Sangiovanni-Vincentelli [42].

Finally, in Chapter 9, we draw conclusions on the work presented in the dissertation and discuss future research directions.

## **1.4 Related Publications**

The material discussed in this dissertation extends the results reported in the following publications.

• [41] A. Iannopollo et al. "Library-based scalable refinement checking for contractbased design". In: Design, Automation and Test in Europe Conference and Exhibition (DATE), 2014. Mar. 2014, pp. 1–6. DOI: 10.7873/DATE.2014.167.

- [43] Antonio Iannopollo, Stavros Tripakis, and Alberto Sangiovanni-Vincentelli. "Constrained Synthesis from Component Libraries". In: Formal Aspects of Component Software: 13th International Conference, FACS 2016, Besanccon, France, October 19-21, 2016, Revised Selected Papers. Ed. by Olga Kouchnarenko and Ramtin Khosravi. Springer International Publishing, 2017, pp. 92–110. ISBN: 978-3-319-57666-4. DOI: 10.1007/978-3-319-57666-4\_7.

- [44] Antonio Iannopollo, Stavros Tripakis, and Alberto Sangiovanni-Vincentelli. "Constrained synthesis from component libraries". In: *Science of Computer Programming* 171 (2019), pp. 21–41. ISSN: 0167-6423. DOI: https://doi.org/10.1016/j. scico.2018.10.003.

- [42] A. Iannopollo, S. Tripakis, and A. Sangiovanni-Vincentelli. "Specification decomposition for synthesis from libraries of LTL Assume/Guarantee contracts". In: 2018 Design, Automation Test in Europe Conference Exhibition (DATE). Mar. 2018, pp. 1574–1579. DOI: 10.23919/DATE.2018.8342266.

The work in this dissertation and related publications has been supported by the National Science Foundation (NSF), via the project "ExCAPE: Expeditions in Computer Augmented Program Engineering" (CCF-1139138), by the Camozzi group, IBM, and United Technologies Corporation (UTC) via the iCyPhy consortium, and by TerraSwarm, one of six centers of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA.

# Chapter 2 Related Works

**Platform-Based Design** Platform-Based Design (PBD) [72, 73, 77, 74, 64] is an iterative design methodology which has been successfully applied in a number of domains, including electronic, automotive, and building automation design. It has been introduced in the late 1980s as a design methodology able to support the design process of complex systems.

Figure 2.1: A graphical representation of the mapping process typical of Platform-Based Design. A specification, i.e., function, is implemented as a composition of elements in a more concrete abstraction levels through a mapping process. Image from [72].

In PBD, design is carried out as the mapping of a user defined function to a platform instance, as illustrated in Figure 2.1. This platform instance represents a network of interconnected components, chosen from a library. Together with their functionality, in PBD components expose also other characteristics such as composition rules, performance indices, and cost. This additional information is used to optimize the mapping process, according to both functional and non-functional specifications. Two main principles are defined within PBD, abstraction/refinement and composition/decomposition. The former enables a vertical process which allows the design to proceed within different levels of abstraction, while the latter is an horizontal process with describe how design components can be combined or decomposed at the same abstraction level.

**Contract Refinement Verification** The problem of building and verifying compositions of formally define components has been studied extensively. Pinto *et al.* [64] propose the Contract-Based Specification Language for Platforms (CSL4P). CSL4P provides mechanisms to define component platforms, and to build designs by instantiating, interconnecting, and composing components. Designs can then be formally verified for compliance with platform composition rules.

Grumberg and Long [33] describe the inspirational idea of decomposing a verification task into smaller sub-tasks, where an aggregation of components is replaced by a more abstract representation, according to an assume-guarantee framework. However, in most cases, finding the appropriate abstraction is an issue, since no general guidelines are available to the verification engineer. A few approaches have been proposed, which use learning algorithms to automatically build such abstractions, e.g., see [21, 35]. In Chapter 5, the abstraction process is instead guided by the contract library, which systematically encodes the available information on both the structural decomposition of the system architecture and the relevant system domain knowledge. Based on the library, we provide a mechanism to automatically build abstractions on the fly, as we solve the problem by successive refinements. In this respect, our solution is inspired by the platform-based design paradigm [72], where a design at each abstraction layer is also regarded as a platform instance, i.e. a legal interconnection of component out of a pre-characterized library, which also includes composition rules. As we describe in Section 3.3, the concept of library is further extended to also include relations between contracts and their ports. In the context of this chapter, such relations include refinement rules between contracts in the library. Cimatti and Tonetta [17] exploit the relation between decomposition of component contracts and system architecture and provide a concrete framework to verify a system architecture relying on temporal logic formulas.

**Synthesis** Our work on synthesis from component libraries is inspired by two major contributions in this field:

- Pnueli and Rosner [66] show that the problem of synthesizing a set of distributed finite-state controllers such that their network, which is given and fixed, satisfies a given specification is undecidable. In that work, each component in the network is controlled by a finite-state machine (or *program*), and the goal is to synthesize programs that cooperate to satisfy a certain linear temporal logic formula  $\phi$ ;

- Lustig and Vardi [54] show that the problem of synthesis from component libraries for *data-flow* compositions is also undecidable. Here components are *transducers*, i.e., finite-state machines able to map a set of input strings to a set of output strings. The specification, also in this case, is a linear temporal logic formula  $\phi$ . In data-flow compositions, the output of a component is fed to another one, while all the components

work synchronously to satisfy the specification. The paper also analyzes another type of composition, *control-flow*, where each component takes full control of the system for a certain period of time, before releasing the system resources to the other components.

Thus, [66] shows that fixing the topology of the network while letting the synthesis process find the components is undecidable, while [54] shows that fixing the components while letting the synthesis process find the topology (possibly by replicating components) is also undecidable. In our work, in Chapters 6 and 7, we too focus on data-flow compositions, and the undecidability results in [66] and [54] are relevant. In our synthesis approach, however, we achieve decidability by imposing a bound on the total number of component instances, which are chosen from a library, positioning our efforts in between the two approaches presented above.

The general idea of synthesis from component libraries adopted here is reminiscent of the work in [48, 34]. There, Jha et al. considered the problem of synthesis of finite loop-free programs from libraries of atomic program statements, using a SMT solver to carry on synthesis. Our work is different, however, as our components are defined as LTL A/G contracts, thus, their have temporal constraints.

A different perspective in synthesis from component libraries has also been described by Alur *et al.* [4]. There, a controller is built out of library components in a control-flow fashion (using the terminology introduced in [54] and discussed above). That approach, while being relevant in the broader topic of synthesis from component libraries, is orthogonal to ours since we focus on data-flow compositions.

Relevant is also the extensive work done in the area of Supervisory Control Synthesis (SCS) [69]. SCS is the problem of synthesizing a controller for a discrete event system, i.e., an automaton, which exposes some controllable and uncontrollable behaviors. The specification defines which behaviors are admissible, and the goal of the controller is to restrict the controllable behaviors of the discrete event system in a way that satisfies the specification. Existing SCS algorithms, however, do not deal with libraries of components but, instead, their goal is to synthesize a controller *ex novo*. Here, we provide a more generic notion of components and focus our effort in synthesizing a controller through the composition of existing components.

Ramesh *et al.* [70] focus on the problem of synthesis of embedded designs from component libraries. In that work, components are represented exclusively by their interface and connections are made on the basis of static relations between component ports. Given a specification, a particularly rich type system takes care of efficiently pruning the search space by solving a constraint satisfaction problem. Although our type system is not as expressive, our approach is more general as we consider components described by more complex specifications (not necessarily static) in addition to their interface.

Manolios *et al.* [55] present a constraint solving framework based on Integer Linear Programming (ILP) where some variables need to be interpreted according to some first-order theories. They develop a constraint solver, Inez, and use it to synthesize architectural models related to the aerospace industry. **Oracle-Guided and Counterexample-Guided Inductive Synthesis, and the combination of Induction, Deduction, and Structure** OGIS [49, 48] is a general paradigm to address formal inductive synthesis. It is characterized by the interaction between an inductive learning engine, also called "learner", and a verification engine, i.e., the "teacher". The learner submits queries to the teacher, which replies with some information (for instance, a yes/no answer or an execution trace) that is used by the learner to improve its guesses.

CEGIS [81, 49, 50], a specialization of OGIS, is a well-known synthesis paradigm which originates from techniques of debugging using counterexamples [78] and *CounterExample-Guided Abstraction Refinement* (CEGAR) [20]. CEGIS is an inductive synthesis approach where synthesis is the result of inferring details of the solution from I/O examples, which usually are counterexamples for previous incorrect guesses, provided by a constraint solver. In CEGIS an iterative algorithm, according to a certain concept class, generates candidate solutions which are processed by an oracle and either declared valid, in which case the algorithm terminates, or used to derive counterexamples to restrict the search space. CEGIS has been successfully used in a number of research areas, including program synthesis and sketching [34, 81], and synthesis and completion of distributed protocols [6, 5, 3]. Recently, Seshia [76] proposed a methodology that formalizes the combination of *Structure, Inductive and Deductive* reasoning (SID), representing a generalization of both CEGAR and OGIS.

**Specification Decomposition** Filippidis [30] studies the problem of specification decomposition into A/G contracts, when they are described in a fragment of Temporal Logic of Actions (TLA<sup>+</sup>) [51], by proving that unnecessary variables can be efficiently hidden and eliminated from the resulting specifications.

Henzinger *et al.* [37] propose a method to decompose the refinement verification process for reactive systems in a series of sub-tasks that are simpler than the original problem, leveraging the structure of the design and using the Assume/Guarantee paradigm to manage circular dependencies.

Dallal and Tabuada [22], given a set of components and a safety specification, propose a decomposition technique where the goal is to generate a set of minimally restrictive assumptions (one per component). Such assumptions, found through a fixed point computation, are then used to synthesize controllers for the components. Our goal is similar: breaking down the synthesis process in simpler sub-tasks.

Incer Romeo *et al.* [46] introduce means to compute the operation of quotient for A/G contracts. Given a specification C to be implemented, and the specification C' of a component to be used in the design, the quotient describes the properties that need to be satisfied, in addition to those required by C', in order to meet C.

# Chapter 3

# Preliminaries

In this chapter, we provide some basic notions that will be the foundation of the work developed in the other chapters. Here, our goal is two-fold. On the one hand, we describe the details of the formalisms we use and how they relate to each other. For instance, we introduce Linear Temporal Logic (LTL), and discuss how it can be used to specify Assume/Guarantee (A/G) contracts. On the other hand, we provide insights on the techniques we use to manipulate such formalisms, which then we assume in the next chapters. This is the case for LTL manipulation using a model-checker. Here we describe how we can use an off-the-shelf tool to perform the basic operations of validity and satisfiability checks, which will be useful later.

The chapter is organized as follows. Section 3.1 introduces LTL. In Section 3.2, we describe the general A/G contract framework we use in this dissertation, and introduce the concept of contract library in Section 3.3. Then, in Section 3.4, we discuss how to use LTL as a concrete formalism for A/G contracts and show how to practically verify refinement as a model checking problem in 3.5.

## 3.1 Linear Temporal Logic

Temporal Logic is an extension of propositional logic, introduced by Amir Pnueli [68], that allows for the specification of properties that can be verified over an infinite sequence of symbols. Here we focus on Linear Temporal Logic (LTL), which is particularly useful in expressing properties of systems having a state that evolves in a discrete manner, where time is seen as a linear sequence in which system variables are evaluated. Programs, electric and electronic devices, and motion planning are just a few example of areas that can benefit from having specifications expressed using LTL. LTL is expressive enough to describe complex specifications, including properties such as safety (something bad will never happen), liveness (something will keep happening), stability (a certain state will be eventually reached), etc. [52]

### 3.1.1 Reactions, Behaviors, and Synchronous Assertions

Given a set of variables  $\Sigma$  with domain D, we call *reaction*, or *state*,  $r \in D^{\Sigma}$  an evaluation of the variables in  $\Sigma$  within their domain. A synchronous run  $\sigma$ , or *behavior*, is a infinite sequence of reactions:

$$\sigma \in (D^{\Sigma})^{\omega} = r_0, r_1, r_2, \cdots$$

(3.1)

A set of behaviors is called a synchronous assertion. A synchronous assertion P is defined as:

$$P \subseteq \mathcal{T} \tag{3.2}$$

where  $\mathcal{T} = (D^{\Sigma})^{\omega}$  is the set of all the behaviors.

We call *atomic proposition* any statement over evaluations of variables in  $\Sigma$  which has a unique truth value. This means that for an atomic proposition p is always possible to determine if it is true or false. Given a reaction  $r \in D^{\Sigma}$ , we say that  $r \vdash p$  if p is true over the evaluation in r. If p is false, then  $r \nvDash p$ .

### 3.1.2 Syntax of LTL formulas

Given a set of atomic propositions AP over evaluations of an alphabet  $\Sigma$ , the syntax of an LTL formula  $\varphi$  can be defined inductively as follows:

$$\varphi := True \mid p \mid \neg \varphi \mid \varphi \land \psi \mid \bigcirc \varphi \mid \varphi \mathcal{U} \psi \tag{3.3}$$

where  $p \in AP$  and  $\psi$  is another LTL formula,  $\bigcirc$  is the *next* operator—also indicated as X—and  $\mathcal{U}$  is the *until* operator.

Additional logic and linear temporal operators, such as disjunction  $(\lor)$ , material implication  $(\rightarrow)$ , eventually  $(\diamondsuit$ , or F), and globally  $(\Box$ , or G) can be derived as follows:

$$\varphi \lor \psi := \neg (\neg \varphi \land \neg \psi)$$

$$\varphi \to \psi := \neg \varphi \lor \psi$$

$$\diamond \varphi := True \ \mathcal{U} \ \varphi$$

$$\Box \varphi := \neg \diamond \neg \varphi$$

### 3.1.3 Semantics of LTL formulas

LTL formulas are evaluated over infinite sequences of states, i.e., behaviors. Let  $\sigma = r_0, r_1, \cdots$  be a behavior. Then, the satisfaction of a formula  $\varphi$  by  $\sigma$  at time *i* is recursively defined as follow:

- $\sigma_i \models p$  if and only if  $r_i \vdash p$ , where  $p \in AP$ ;

- $\sigma_i \models \neg \varphi$  if and only if  $\sigma_i \not\models \varphi$ ;

- $\sigma_i \models \varphi \land \psi$  if and only if  $\sigma_i \models \varphi$  and  $\sigma_i \models \psi$ ;

- $\sigma_i \models \bigcirc \varphi$  if and only if  $\sigma_{i+1} \models \varphi$ ;

- $\sigma_i \models \varphi \mathcal{U} \psi$  if and only if there exist  $j \ge i$  such that  $\sigma_j \models \psi$  and  $\sigma_k \models \varphi$  for all  $k \in [i, j)$ ;

where  $\psi$  is another LTL formula. If a formula is true at time 0, i.e.,  $\sigma_0 \models \varphi$ , we will drop the subscript and just say that the behavior  $\sigma$  satisfies the formula  $\varphi$ , written  $\sigma \models \varphi$ .

For an LTL formula  $\varphi$ , we indicate with  $\mathcal{L}(\varphi)$  its language, i.e., its associated synchronous assertion, which is the set of infinite behaviors satisfying it.

### 3.1.4 LTL Applications, Satisfiability, and Realizability

LTL is widely used in model checking and synthesis. [33, 67, 71, 16, 65] In the first case, it is possible to automatically verify if a model exhibits certain properties. Several model checking algorithms and tools have been developed over the years. These algorithms can be grouped into two categories: symbolic and explicit-state; symbolic algorithms use Binary Decision Diagrams (BDD) [15] to encode the whole state space and perform model checking. Explicit state algorithms [40], instead, declare all the state variables for each time step and then rely on a SAT solver to find an answer to the model checking problem. These algorithms cannot represent a system evolution of infinite length, thus are used to compute bounded model checking (BMC) [13], where a property is verified up to a finite number of temporal steps. While symbolic methods are complete, they tend to use a significant amount of memory to represent the whole system. BMC algorithms, instead, represent a faster solution for a large number of applications, where the verification of properties within a finite horizon is acceptable.

In the case of synthesis, given a set of desirable LTL properties, the goal is to automatically generate a state machine implementing them. This is achieved by solving a two players game, where a system implementation is required to be able to react to any possible move from an adversarial environment [67, 71, 27]. If a winning strategy does not exist, then synthesis fails. Otherwise, an implementation of such strategy is returned.

In this work, however, we verify and synthesize compositions of components described using LTL, and all the algorithms and techniques we study are based on the capability of asserting the validity of an LTL formula. In the previous sections, we have discussed how LTL formulas can express sets of infinite-length behaviors. Indeed, Wolper *et al.* [85] show that the models satisfying an LTL formula can be described as a  $\omega$ -regular language over a certain alphabet. Thus, checking the validity of an LTL formula can be reduced to checking emptiness of the associated language, which is a PSPACE-complete problem [80].