## **Towards Wideband Signal Acquisition Systems**

Nima Baniasadi Ali Niknejad, Ed.

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2020-171 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2020/EECS-2020-171.html

August 14, 2020

Copyright © 2020, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Towards Wideband Signal Acquisition Systems

by

Nima Baniasadi

A thesis submitted in partial satisfaction of the requirements for the degree of  $$\operatorname{Master}$  of Science, Plan II

in

Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Kristofer S. J. Pister

Summer 2020

The thesis of Nima Baniasadi, titled Towards Wideband Signal Acquisition Systems, is approved:

Chair

$\mathcal{D}_{\text{ate}} \ll 1/(3/$

Date

University of California, Berkeley

# IEEE Copyright Notice

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of University of California, Berkeley products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to https://www.ieee.org/publications/rights/reqperm.html to learn how to obtain a License from RightsLink.

#### Abstract

Towards Wideband Signal Acquisition Systems

by

#### Nima Baniasadi

Master of Science, Plan II in Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali M. Niknejad, Chair

Deep scaling of CMOS technology has provided an exceptional opportunity for wideband high data-rate digital communication. However, since the medium between transceivers accept only analog signals, use of analog to digital converters is inevitable. Currently, ADCs are the bottleneck of communication links, where speed trades off with resolution. Moreover, all digital equalization is desirable but necessitates higher resolution and higher bandwidth ADCs. Several methods for increasing the speed of ADCs are considered in this thesis. An extensive analysis, confirmed by simulations, on the jitter-induced error shows that proper system architecture can improve the total SNDR of ADCs.

# Contents

| Contents |                                   |                                                                                                                                                              | i                          |  |  |

|----------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

| Li       | List of Figures                   |                                                                                                                                                              |                            |  |  |

| Li       | List of Tables                    |                                                                                                                                                              |                            |  |  |

| 1        | Intro<br>1.1<br>1.2<br>1.3<br>1.4 | Motivation                                                                                                                                                   | 1<br>1<br>4<br>4<br>5      |  |  |

| 2        | 2.1<br>2.2<br>2.3                 | C Basics and Considerations Quantization Error Jitter-Induced Error Misinterpretation: Correlated vs Uncorrelated Oversampling Testing Methods and Drawbacks | 6<br>8<br>9<br>12          |  |  |

| 3        | 3.1<br>3.2                        | easing Information Rate  Modulation techniques                                                                                                               | 15<br>16<br>23<br>24<br>24 |  |  |

| 4        | 4.1<br>4.2<br>4.3                 | er Error Sampling Error Phase Noise and Jitter Phase Noise Sources Principles of Improving Jitter-limited SNR                                                | 30<br>30<br>32<br>37<br>39 |  |  |

| 5        | _                                 | quency-Interleaved ADC Architecture                                                                                                                          | <b>47</b><br>47            |  |  |

| •   | • |

|-----|---|

| 1   | 1 |

| - 1 | 1 |

|    | 5.2<br>5.3   | Quantization Noise            |           |  |

|----|--------------|-------------------------------|-----------|--|

| 6  | Con          | clusion                       | <b>58</b> |  |

|    | 6.1          | TI-ADC vs FI-ADC              | 58        |  |

|    | 6.2          | Implementation Considerations | 59        |  |

|    | 6.3          | Future Directions             | 59        |  |

| Bi | Bibliography |                               |           |  |

# List of Figures

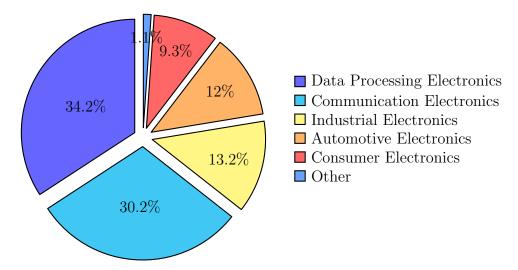

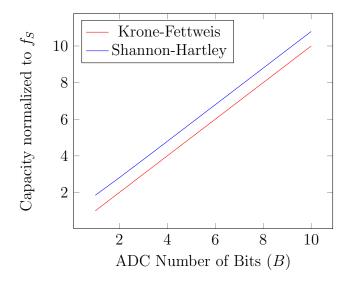

| 1.1<br>1.2 | Expected global semiconductor sales revenue per category in 2022 [1]                                 | 1  |

|------------|------------------------------------------------------------------------------------------------------|----|

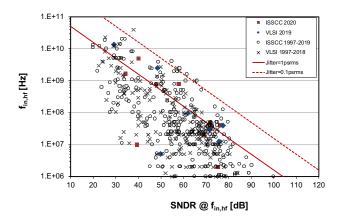

| 1.3        | 2020 ADC survey showing the speed-resolution trade off [2]                                           | 4  |

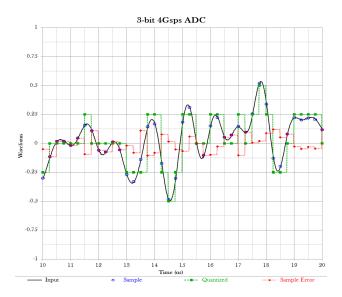

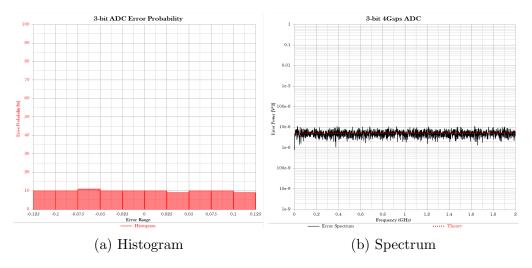

| 2.1        | Waveforms for a 3-bit 4Gsps ADC                                                                      | 7  |

| 2.2        | Quantization noise for a 3-bit 4Gsps ADC                                                             | 1  |

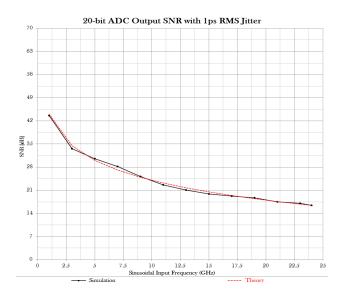

| 2.3        | Output SNR of a 20-bit ADC with $1ps$ RMS Jitter as a function of input frequency                    |    |

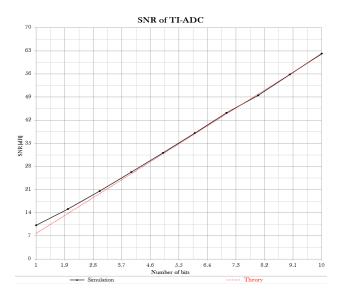

| 2.4        | SNR vs ADC resolution in TI-ADC                                                                      | 11 |

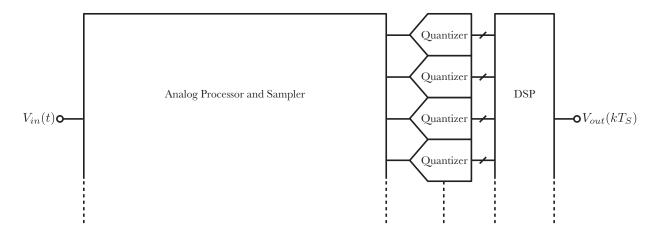

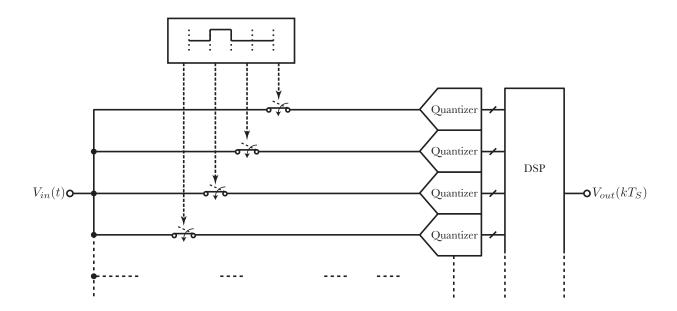

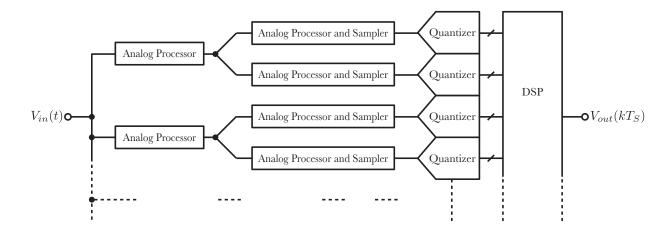

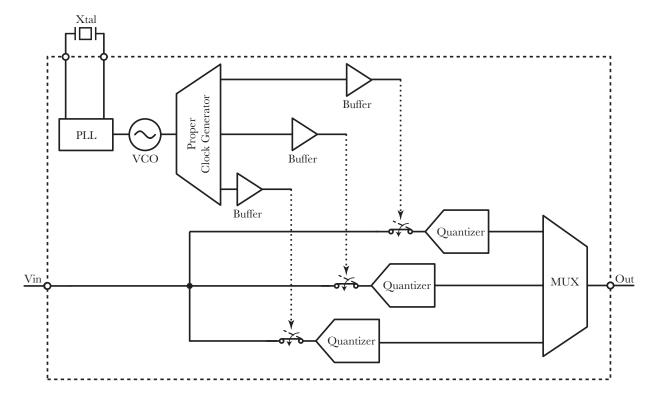

| 3.1        | Running multiple quantizers in parallel                                                              | 15 |

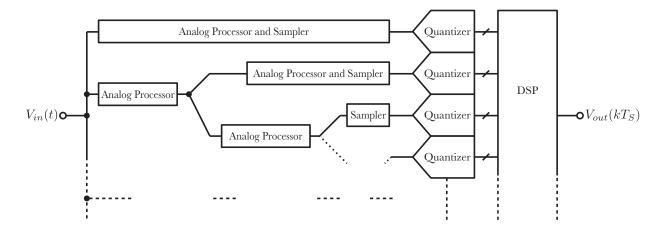

| 3.2        | Time-interleaved structure.                                                                          | 16 |

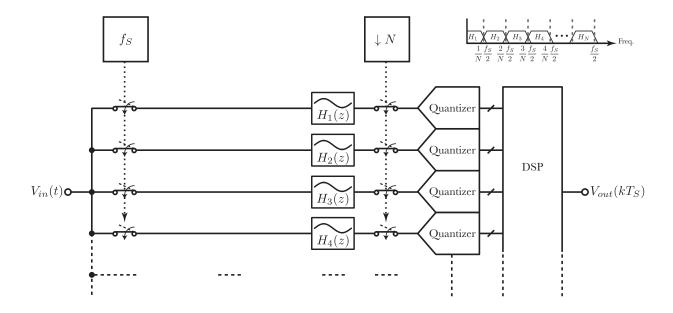

| 3.3        | High-speed ADC incorporating a QMF Bank                                                              | 17 |

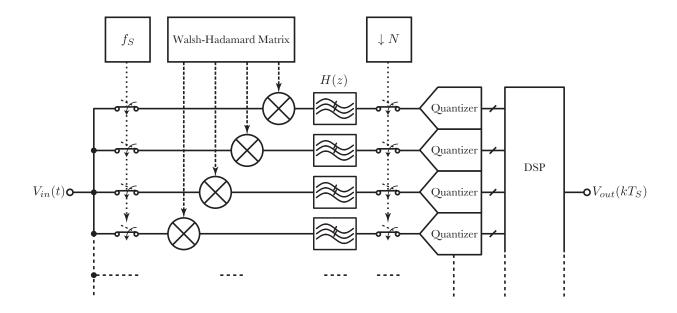

| 3.4        | Parallel quantization using Hadamard modulation                                                      | 18 |

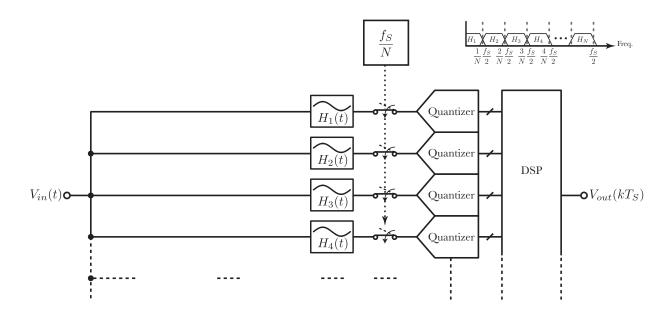

| 3.5        | High-speed ADC incorporating hybrid filter banks                                                     | 21 |

| 3.6        | Frequency-translating hybrid architecture                                                            | 22 |

| 3.7        | Architecture of a frequency-folded ADC                                                               | 22 |

| 3.8        | Pre-processing at the absence of a priori knowledge                                                  | 23 |

| 3.9        | Processing all channels in parallel                                                                  | 24 |

| 3.10       | Sequentially processing all channels in a balanced tree                                              | 25 |

|            | Processing channels in an unbalanced tree                                                            | 25 |

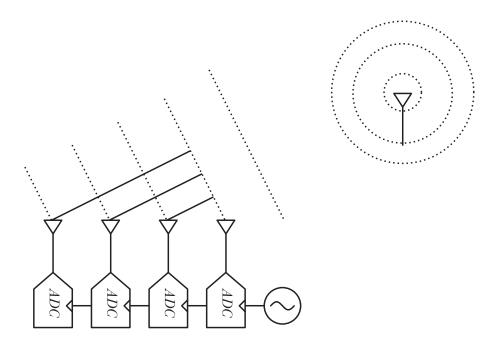

|            | Spatial stretching using extended transmission line                                                  | 26 |

|            | Spatial stretching using antenna array                                                               | 26 |

|            | Time-varying all-pass filter                                                                         | 28 |

| 3.15       | Simulation results for time-stretching using time-varying all-pass filter                            | 29 |

| 3.16       | Time-stretching with envelope modulation                                                             | 29 |

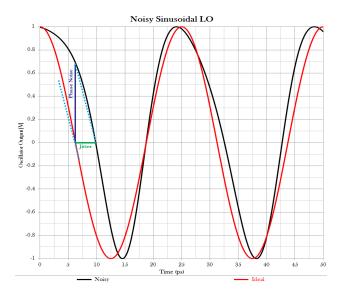

| 4.1        | Errors due to the clock edge jitter                                                                  | 31 |

| 4.2        | Subtleties in the definition of the jitter and phase noise                                           | 33 |

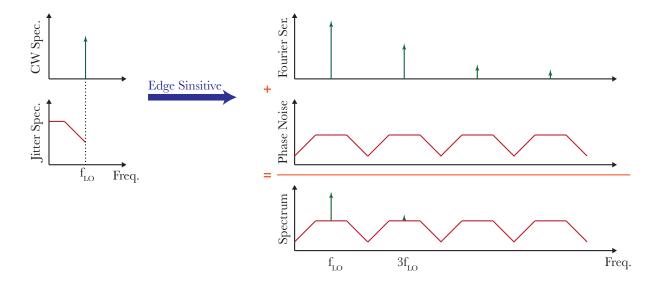

| 4.3        | Effective spectrum of a noisy LO (with jitter) after passing through an edge-<br>sensitive circuitry | 35 |

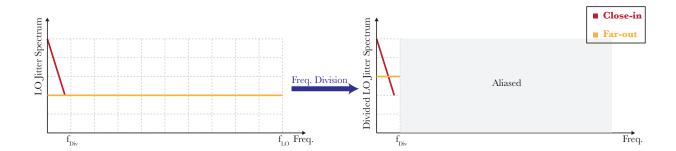

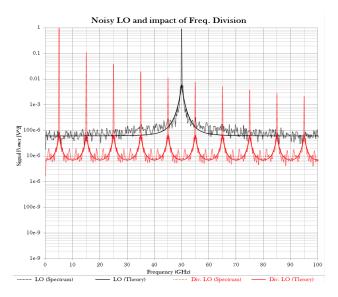

| 4.4        | Jitter spectrum before and after frequency division                                                  | 36 |

| 4.5        | Effective LO spectrum for an edge-sensitive circuitry before and after frequency                     |    |

|            | division.                                                                                            | 37 |

| 4.6  | Simulation of the effective LO spectrum for an edge-sensitive circuitry before and |    |

|------|------------------------------------------------------------------------------------|----|

|      | after frequency division                                                           | 38 |

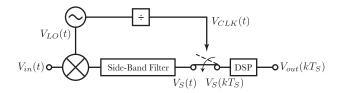

| 4.7  | Simplified model of LO generation and distribution to the sampling stage           | 38 |

| 4.8  | Mixer-assisted sampler with only one time reference                                | 40 |

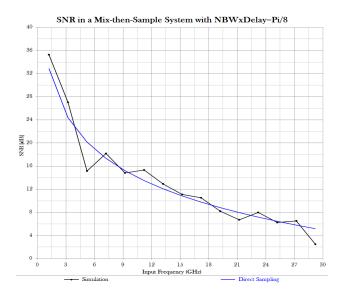

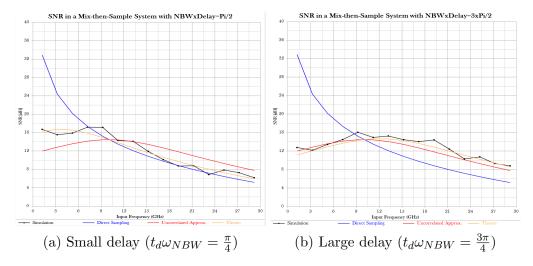

| 4.9  | SNR of a Mix-then-Sample system with phase noise dominated by close-in part        | 42 |

| 4.10 | SNR of a Mix-then-Sample system with white phase noise                             | 43 |

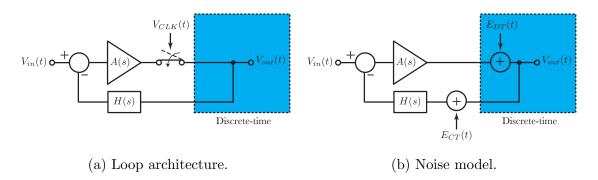

| 4.11 | Hybrid feedback loop                                                               | 43 |

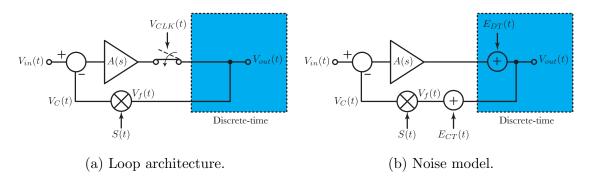

| 4.12 | Hybrid feedback loop with noise shaping                                            | 44 |

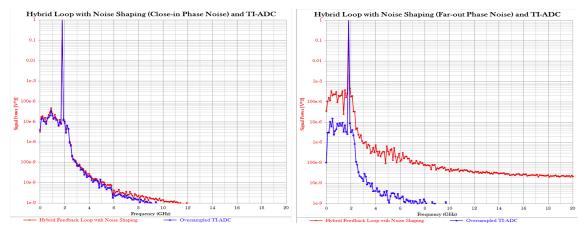

|      | Noise Shaping in a hybrid feedback loop                                            | 45 |

| 4.14 | Simulation results for comparison of direct sampling versus employing hybrid       |    |

|      | feedback loop                                                                      | 46 |

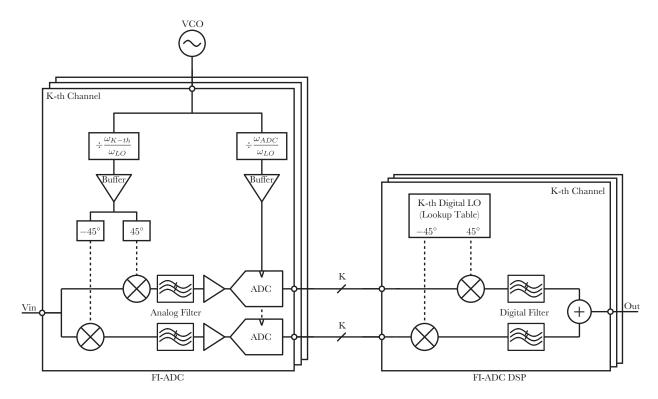

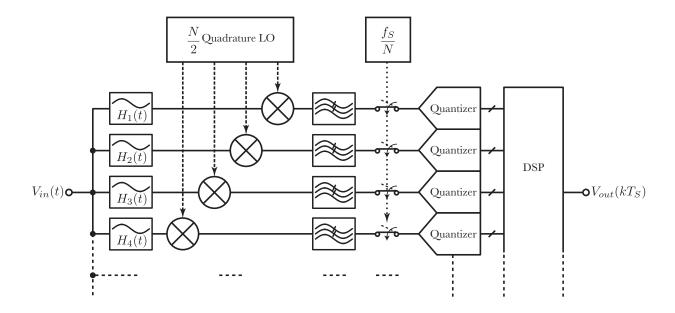

| 5.1  | Block diagram of a frequency-interleaved ADC and digital signal processing         | 47 |

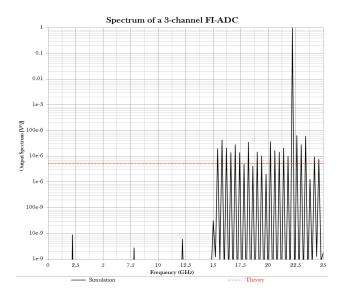

| 5.2  | Output spectrum of a 3-channel FI-ADC with no nonidealities                        | 49 |

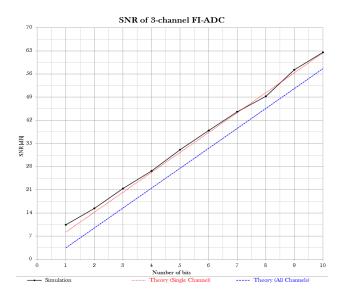

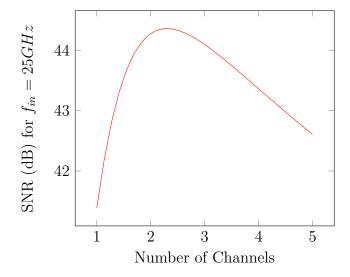

| 5.3  | SNR vs ADC resolution in an ideal FI-ADC                                           | 51 |

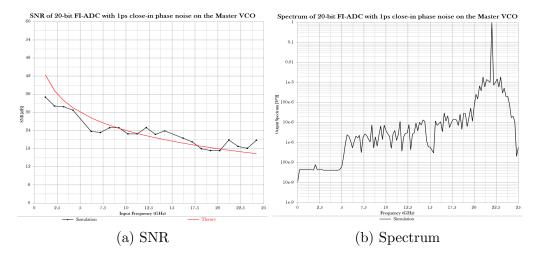

| 5.4  | Simulation of 20-bit 3-channel FI-ADC with $1ps$ of RMS Jitter ( $1GHz$ band-      |    |

|      | width) on the Master VCO                                                           | 54 |

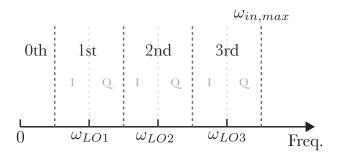

| 5.5  | Example of 4-channel FI-ADC                                                        | 54 |

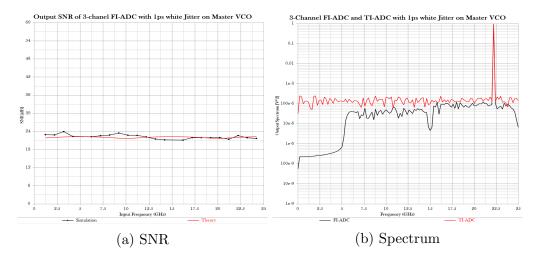

| 5.6  | 3-channel FI-ADC with 1ps or RMS white jitter on the master VCO                    | 56 |

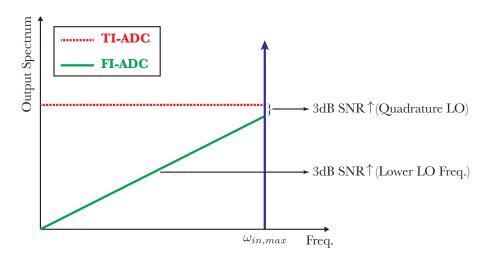

| 5.7  | Intuitive explanation of FI-ADC SNR improvement over TI-ADC                        | 57 |

| 6.1  | FIADC with 8-bit sub-ADCs, $100fs$ far-out jitter on the master VCO, and $300fs$   |    |

|      | ADC jitter                                                                         | 59 |

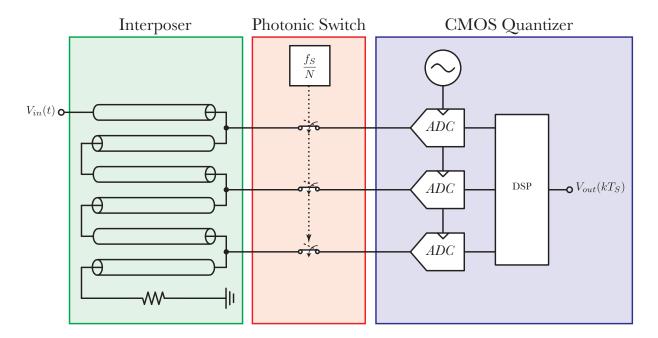

| 6.2  | Frequency interleaved architecture with initial coarse channel filtering           | 60 |

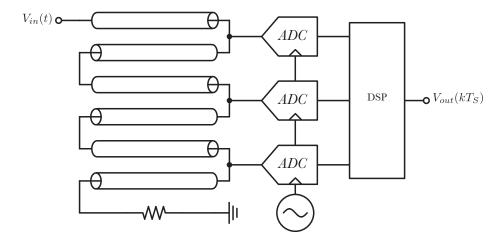

| 6.3  | High speed sampling using mixed technologies                                       | 61 |

# List of Tables

# Chapter 1

## Introduction

#### 1.1 Motivation

The semiconductor industry has been one of the rapidly-growing industries in the past several decades with an expected annual revenue of more than \$500 billion in 2020[1]. As shown in Fig. 1.1, more than one-third of this revenue comes from communication electronics (including wired and wireless electronics) where many different applications such as hand-held mobile electronics and backbone infrastructure demand for higher communication capacity. This industry trend has resulted in 10-fold increase in data rates every five years <sup>1</sup> [3].

Figure 1.1: Expected global semiconductor sales revenue per category in 2022 [1].

Thanks to the several decades of technology advances based on Moore's law and Dennard's law, digital circuits using CMOS technology and digital signal processing are well-

<sup>&</sup>lt;sup>1</sup>Compare this with the capacity of batteries used in mobile devices which has improved by only 5-10 percent every year.

suited for such high data-rate applications and incomparable with other technologies when considering performance with other factors such as implementation density, power consumption, integration level, and cost. However, in most of the communication applications, two or more transceivers are talking with each other through a channel medium which naturally carries analog signals (electrical or other). Analog and mixed signal circuits scale poorly with process technology in terms of size and speed compared to digital circuits, so it has encouraged designers to simplify analog and RF circuits for high data rates and large bandwidths to save power and compensate for the impairments by adding complexity on the digital baseband side [3]. This means that before and after each channel medium, analog/digital conversion is required.

The analog-to-digital converter (ADC) is also currently the bottleneck for high data-rate communication systems [4]. This has led researchers to explore the possible fundamental computational limits [5] and also limits coming from the implementation [6]. It can be shown [7] that the maximum capacity C for a receiver with an ADC at the front-end (assuming everything else is ideal) is:

$$C = f_S \times B \tag{1.1}$$

where B is the number of bits of the ADC and  $f_S$  is the sampling rate. Intuitively, it should have been expected since unpredictability defines information and with an ADC with B bits, we cannot have more than  $f_S \times B$  elements of surprise every second. Although Eq. 1.1 sets a principal upper limit to the capacity based on the number of bits, it is not clear how other ADC nonidealities affect the data rate. Shannon-Hartley theorem can be employed which takes other noise sources into account:

$$C = BW \log_2 \left( 1 + \frac{P_{Sig}}{P_{Noise}} \right) \tag{1.2}$$

where  $BW \leq \frac{f_S}{2}$  is the bandwidth of the input signal,  $P_{Sig}$  is its power, and  $P_{Noise}$  is the sum of the power of all white noise sources<sup>2</sup>. By statistical modeling in Chapter 2, we will show that the limited number of bits (B) from the ADC results in an effective pseudo-white quantization noise with  $P_{QN} = \frac{\Delta^2}{12}$  where  $\Delta$  is the difference between quantization levels. Therefore, the maximum capacity expected (neglecting all other noise sources) based on Shannon-Hartley theorem is

$$C_{max} = \frac{f_S}{2} \log_2 \left( 1 + \frac{\left(\frac{2^B \Delta}{2}\right)^2}{\frac{\Delta^2}{12}} \right)$$

$$\approx f_S \times \left( B + \frac{\log_2(3)}{2} \right) \tag{1.3}$$

The extra factor in Eq. 1.3 compared to Eq. 1.1 comes from the error of separate statistical modeling of quantization noise and channel capacity. The result of both theorems are shown

<sup>&</sup>lt;sup>2</sup>If noise is colored or partially correlated with the input signal, the Eq. 1.2 is not correct.

in Fig. 1.2 where for the benefit of clarity, a continuous range of values of B has been considered.

Figure 1.2: Maximum capacity of a channel with an ADC at the receiver.

Both theorems clearly show that the path for increasing the data rate is increasing the speed-resolution product. However, looking into the published results from different surveys [2], one can observe that speed and resolution come with a trade-off. This is shown in Fig. 1.3 where the maximum input frequency  $f_{in,hf}$  is used as a proxy for the speed<sup>3</sup>, and SNDR<sup>4</sup> or ENOB<sup>5</sup> as a proxy for the resolution.

Speed-resolution trade-off has been linked to the Heisenberg uncertainty principle (at least at higher sample rates). Although the original link in [8] is disputed [5], quantum theory still sets an upper limit to the maximum achievable data rate [7]. However, this fundamental limit is many orders of magnitude higher than the performance of the current state-of-the-art systems. As it will be shown in the next chapters of this thesis, speed-resolution product tends to be limited by our ability to make a low-jitter clock [9].

It should be mentioned that the proxies we used here cannot be directly substituted in Eq. 1.1. It is due to the fact that SNDR and ENOB are most of the times characterized based on a pure sinusoidal input signal. Depending on the different schemes and applications, the system-in-use can beat the expected performance based on those proxies.

<sup>&</sup>lt;sup>3</sup>Based on the Nyquist sampling theory,  $f_{in,hf} \leq \frac{f_S}{2}$ , however, ADCs are typically running at higher-than-Nyquist sampling rates.

<sup>&</sup>lt;sup>4</sup>Signal-to-Noise-and-Distortion-Ratio

<sup>&</sup>lt;sup>5</sup>Effective Number Of Bits

Figure 1.3: 2020 ADC survey showing the speed-resolution trade off [2].

## 1.2 Increasing the information rate

As mentioned earlier, the channel capacity is ultimately limited by the speed-resolution product. However, SNR<sup>6</sup> of high-speed ADCs in Fig. 1.3 is limited by the clock jitter. Therefore, in this article, we will investigate on methods to increase the effective sampling rate of the ADC, and also methods to mitigate jitter-induced SNR degradation.

It should be mentioned that the data rate and information rate are net necessarily the same. For example, consider a situation in which the channel is shared among multiple users. In this case, the digitized output of ADC has the data for all different users, however, only a portion of that is relevant information for a specific user. Obviously, information rate  $(R_{info})$  is smaller than data rate  $(R_{data})$ . If resources were equally shared among M users, information rate for a specific user will be M times lower than the data rate expected by Eq. 1.1. Therefore, with prior processing<sup>7</sup> in the analog domain, the ADC can be substituted by an analog-to-information converter (AIC) which relaxes the speed-resolution. Although AICs are typically more suitable for IoT applications [10] where a priori knowledge such as sparsity in any domain can be exploited, the concept can be expanded to cover to all sorts of applications. Without going too much into details, we will explain AICs in next chapters and how they link to several different parallel architectures.

# 1.3 Utilizing other technologies, domains, and modalities

As mentioned in the first section, CMOS is the designers' choice for digital processing. However, other technologies may be used next to the CMOS chip in order to relax the

<sup>&</sup>lt;sup>6</sup>As a proxy for resolution.

<sup>&</sup>lt;sup>7</sup>Prior processing can be as simple as a mixer or filter or delayed sampler.

CMOS design. For example, in a jitter-limited system, sampling can be done in another semiconductor technology [11] and then rely on the CMOS for quantization.

Furthermore, if sampling is preferred to be done in CMOS, the incoming signal can be continuously stretched in different domains such as time [12] or space [13]. Given that the input signal has a wave nature, spatio-temporal characteristics of the wave can be used [14, 15] to increase the effective sampling rate without an explicit stretching.

Finally, the input signal can be continuously converted from one modality to another one, and samples are taken afterwards. For example, a voltage-to-time converter (VTC) can be used before time-to-digital conversion [16]. Although power consumption can be potentially higher in this architecture [17], it matches well with the scaling trends of the semiconductor industry [18] for area reduction [19].

We will discuss about a few of these strategies in next chapters, however, detailed modeling and analysis are beyond the scope of this thesis.

## 1.4 Thesis Organization

In this thesis, the focus will be on issues and system design aspects of a wideband signal acquisition while CMOS implementation is explained in details in [20]. In the next chapter, we will cover different strategies designers have proposed to increase the output rate of an analog to digital converter. In Chapter 3, we will briefly review basic concepts and definitions in analog to digital converters since some of them need to be adapted later. As mentioned earlier, jitter is the main limitation of the high-speed ADCs which will be explained in details in chapter 4. Chapter 5 is dedicated to the frequency-interleaved architecture and different noise sources are modeled and simulated. Finally, the last chapter concludes the thesis.

# Chapter 2

## **ADC** Basics and Considerations

In this chapter, we will review some of the basic concepts in analog to digital converters. Although this topic is very well covered by the literature, we will review the root cause of some of the problems and debunk common mistakes among published papers.

### 2.1 Quantization Error

Here we briefly review the model for the quantization error. Let us assume that the input range of [-1,1) is divided into  $2^B$  bins. If each of these bins is represented by the mid-value, the output error QN(t) will be bounded to  $\left[-\frac{\Delta}{2},\frac{\Delta}{2}\right] = \left[-\frac{1}{2^B},\frac{1}{2^B}\right)^1$ , as illustrated in Fig. 2.1. Therefore, the output can be written as<sup>2</sup>

$$V_{out}(t) = V_{in}(t) + QN(t)$$

(2.1)

Assuming that the quantization error is uniformly distributed in the aforementioned range with the error probability of  $P(e) = \frac{1}{\Delta}$ , the root mean square (RMS) of the quantization error can be calculated as

$$QN_{RMS}^{2} = \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} |e|^{2} \times P(e) de$$

$$= 2 \times \int_{0}^{\frac{\Delta}{2}} e^{2} \times \frac{1}{\Delta} de$$

$$= \frac{\Delta^{2}}{4 \times 3}$$

(2.2)

Assuming that the quantization error of consecutive samples are uncorrelated<sup>3</sup>, QN(t) can be modeled as a white noise with a uniformly distributed power spectral density over

$<sup>^{1}\</sup>Lambda = \frac{2}{3}$

<sup>&</sup>lt;sup>2</sup>Since the input signal is sampled before quantization, t will have discrete values in Eq. 2.1.

<sup>&</sup>lt;sup>3</sup>In other words,  $R_{QN}(\tau) = 0$  if  $\tau \neq 0$  where  $R_{QN}(\tau)$  is the auto-correlation function.

Figure 2.1: Waveforms for a 3-bit 4Gsps ADC

Figure 2.2: Quantization noise for a 3-bit 4Gsps ADC

the whole ADC frequency range. Strictly speaking, none of the previous assumptions is necessarily valid, but they are very good approximations as Fig. 4.10 suggests <sup>4</sup>.

It is very helpful if the quantization noise can be reported as SNR or ENOB. With a

$<sup>\</sup>overline{\phantom{a}}^{4}$ Note that y-axis of Fig. 2.2b has dimension of  $V^{2}$ . In other words, power spectral density is multiplied by the frequency width of each frequency bin.

sinusoidal wave covering the full scale input range of the ADC [-1,1), we get:

$$SNR_{ADC} = \frac{Signal}{QN}$$

$$= \frac{\frac{1^2}{2}}{\frac{\Delta^2}{12}}$$

$$= \frac{3}{2} (2^B)^2$$

$$= 6.02 \times B + 1.76 [dB]$$

(2.3)

#### 2.2 Jitter-Induced Error

Since jitter analysis is an integral part of this thesis, we will briefly introduce its impact here and postpone details to the next chapters. First let us find what happens when a sampling stage has  $\sigma(t) = \frac{Phase\ Noise}{\omega_{Sampling}}^5$  uncertainty on the sampling edge. For a sinusoidal input with frequency of  $\omega_{in}$  and amplitude of A, the sampled output is:

$$V_{in}(t) = A\sin(\omega_{in}t) \xrightarrow{AfterSampling} V_{Out}(kT_S) = A\sin(\omega_{in}(kT_S - \sigma(kT_S)))$$

(2.5)

where  $T_s$  is the ideal sampling period. Note that sampling happens when

$$t + \sigma(t) = kT_S$$

Assuming small  $\sigma(t)$ , we can divide the signal and noise in the previous equation:

$$V_{Out}(kT_s) \approx A\sin(\omega_{in}kT_S) - \omega_{in}\sigma(kT_S)A\cos(\omega_{in}kT_S)$$

(2.6)

Therefore, the noise components in Laplace domain is nothing but the convolution of jitter and the derivative of the input signal:

$$V_{Noise}(s) \approx -\sigma(s) * (s V_{in}(s))$$

(2.7)

and therefore, at the presence of sampling time uncertainty, the SNR will be limited to

$$SNR = \frac{\frac{1}{2}A^2}{\frac{1}{2}(\omega_{in}\sigma_{RMS}A)^2} = \frac{1}{(\omega_{in}\sigma_{RMS})^2}$$

(2.8)

where  $\sigma_{RMS}$  is the RMS power of jitter. Statistical analysis also confirms that the SNR is independent from the the jitter profile<sup>6</sup>, as long as jitter power stays constant [21]. Results of simulation (Fig. 2.3) shows agreement with the theory. Although it may seem boundless, increasing  $\sigma(t)$  at some point breaks the assumption made earlier. A large signal analysis shows that for almost any input signals, SNR due to the jitter approaches -3dB at the limit when DC component is removed [22].

<sup>&</sup>lt;sup>5</sup>Note that in this section,  $\sigma(t)$  is defined as phase error normalized by the oscillation frequency.

<sup>&</sup>lt;sup>6</sup>Assuming that  $\sigma(t)$  has no DC component.

Figure 2.3: Output SNR of a 20-bit ADC with 1ps RMS Jitter as a function of input frequency

## 2.3 Misinterpretation: Correlated vs Uncorrelated

One common place to make a mistake is whether two nodes in a system are correlated or not, considering both desired signals and undesired noise sources<sup>7</sup>. For example, let us consider a situation for an M-channel time-interleaved ADC. Neglecting quantization error, the output of each ADC,  $y_m(t)$ , can be written as:

$$y_m(t) = x(t) \sum_{k} \delta\left(t - kT_{CK} - \frac{(m-1)T_{CK}}{M}\right)$$

(2.9)

where  $m \in [1, M]$  is the channel index and  $T_{CK}$  is the sampling period of each channel while  $\frac{(m-1)T_{CK}}{M}$  takes care of proper time-interleaving. Author of [23] states that "the signal power in  $Y_1(f) + Y_2(f)$  is equal to  $4P_X$  because the desired components  $Y_1(f)$  in  $Y_2(f)$  and add in-phase" where  $P_X$  is the power of x(t) and  $Y_m(f)$  is the frequency domain representation of  $y_m(t)$ . This interpretation may lead to the question of whether M interleaved stages can help to improve the output SNR. The rational here is that signals will be correlated and add in-phase while quantization noise will be uncorrelated. In order to answer this question, Let us calculate the correlation between  $y_1(t)$  and  $y_2(t)$  once the continuous-time analog signal

<sup>&</sup>lt;sup>7</sup>We will deal with correlated jitter-induced errors in the next chapter.

<sup>&</sup>lt;sup>8</sup>Similar to phased array systems.

is reconstructed:

$$R_{y_1,y_2} = \lim_{T \to \infty} \frac{1}{T} \int_{-\frac{T}{2}}^{\frac{T}{2}} \left[ \operatorname{sinc} \left( \frac{t}{T_{CK}} \right) * y_1(t) \right] \left[ \operatorname{sinc} \left( \frac{t}{T_{CK}} \right) * y_2(t) \right] dt$$

$$= \lim_{T \to \infty} \frac{1}{T} \int_{-\frac{T}{2}}^{\frac{T}{2}} \left[ \operatorname{sinc} \left( \frac{t}{T_{CK}} \right) * \sum_{k} x(t) \delta \left( t - kT_{CK} \right) \right] \times$$

$$\left[ \operatorname{sinc} \left( \frac{t}{T_{CK}} \right) * \sum_{k} x(t) \delta \left( t - k'T_{CK} - \frac{T_{CK}}{M} \right) \right] dt$$

$$= \lim_{T \to \infty} \frac{1}{T} \int_{-\frac{T}{2}}^{\frac{T}{2}} \int \int \sum_{k} \sum_{k}' x(t - u) x(t - u') dt du du' \times$$

$$\delta \left( t - u - kT_{CK} \right) \operatorname{sinc} \left( \frac{u}{T_{CK}} \right) \delta \left( t - u' - k'T_{CK} - \frac{T_{CK}}{M} \right) \operatorname{sinc} \left( \frac{u'}{T_{CK}} \right)$$

$$= \lim_{T \to \infty} \frac{1}{T} \int_{-\frac{T}{2}}^{\frac{T}{2}} \sum_{k} \sum_{k}' x(kT_{CK}) x(k'T_{CK} + \frac{T_{CK}}{M}) dt \times$$

$$\operatorname{sinc} \left( \frac{t - kT_{CK}}{T_{CK}} \right) \operatorname{sinc} \left( \frac{t - k'T_{CK} - \frac{T_{CK}}{M}}{T_{CK}} \right)$$

$$= \sum_{k} \sum_{k}' x(kT_{CK}) x(k'T_{CK} + \frac{T_{CK}}{M}) \times$$

$$\left[ \lim_{T \to \infty} \frac{1}{T} \int_{-\frac{T}{2}}^{\frac{T}{2}} \operatorname{sinc} \left( \frac{t - kT_{CK}}{T_{CK}} \right) \operatorname{sinc} \left( \frac{t - k'T_{CK} - \frac{T_{CK}}{M}}{T_{CK}} \right) \operatorname{d}t \right]$$

$$(2.10)$$

The term in the bracket is the auto-correlation of the sinc(t) function, which is another sinc(t) function:

$$R_{\rm sinc}(t) = {\rm sinc}(t) \tag{2.11}$$

Therefore, for integer values of k and k', we get

$$R_{\rm sinc}(M(k-k')-1) = \operatorname{sinc}(M(k-k')-1)$$

= 0 (2.12)

which means that  $y_1(t)$  and  $y_2(t)$  are uncorrelated.

$$R_{y_1,y_2} = 0 (2.13)$$

This means that ADCs' outputs are uncorrelated and the quoted statement of [23] is not accurate. Moreover, time-interleaving neither helps nor degrades output SNR since

$$SNR_{TI-ADC} = \frac{M \times Signal}{M \times QN} = SNR_{ADC}$$

(2.14)

Figure 2.4: SNR vs ADC resolution in TI-ADC

Fig. 2.4 shows the SNR in TI-ADC simulation vs ADC resolution in comparison with the theory developed in Eq. 2.3.

Similar misinterpretation may occur in the context of frequency-folded ADCs (Fig.  $3.7^9$ ). Authors of [24] state that "since each baseband path and sub-ADC is independent, noise injected into each path will be uncorrelated. However, signal content in each path is correlated, with only a relative phase shift between paths. Thus the signals add in voltage while the baseband noise adds in power." First, it should be noted that relative shift is enough to make signals uncorrelated (e.g.  $\sin(t)$  and  $\cos(t)$ ). Second, any signal processing should be considered before one can conclude on the correlation of two different paths. From our discussion on the Hadamard modulation in section 3.1, we will show that perfect signal recovery requires multiplication of the each channel's output by interleaved pulse sequences. Let us find the correlation of the signal content in the first two paths:

$$R_{y_{1},y_{2}} = \lim_{T \to \infty} \frac{1}{T} \int_{\frac{-T}{2}}^{\frac{T}{2}} y_{1}(t)y_{2}(t)dt$$

$$= \lim_{T \to \infty} \frac{1}{T} \int_{\frac{-T}{2}}^{\frac{T}{2}} \left( \left[ x(t) \sum_{k} \Pi_{\frac{T_{CK}}{M}} (t - kT_{CK}) \right] * h(t) \right) \sum_{k} \Pi_{\frac{T_{CK}}{M}} (t - kT_{CK}) dt \times$$

$$\left( \left[ x(t) \sum_{k} \Pi_{\frac{T_{CK}}{M}} \left( t - kT_{CK} - \frac{T_{CK}}{M} \right) \right] * h(t) \right) \sum_{k} \Pi_{\frac{T_{CK}}{M}} \left( t - kT_{CK} - \frac{T_{CK}}{M} \right)$$

$$= 0$$

(2.15)

<sup>&</sup>lt;sup>9</sup>This architecture will be introduced in the next chapter.

where h(t) is the impulse response of low-pass filters and  $\Pi_{\frac{T_{CK}}{M}}(t)$  is the rectangular pulse train with pulse width of  $\frac{T_{CK}}{M}$ . Note that since the pulse train functions in the digital domain are non-overlapping, the final output of different channels are uncorrelated. N times SNR boosting due to oversampling is expected if only one the sub-bands are considered, which is explained next.

## 2.4 Oversampling

Consider a situation in which the sample rate  $(f_S)$  of the ADC is OSR times higher than the Nyquist rate of a bandwidth-limited (BW) input signal<sup>10</sup>.

$$f_S = 2 \times BW \times OSR \tag{2.16}$$

In this situation, any source of noise with flat spectral density (including thermal noise, quantization noise, and jitter induced errors as long as jitter itself has a white spectral content) at the output of ADC can be filtered out since only a fraction  $(\frac{1}{OSR})$  of the output spectrum contains data. Therefore, from Shannon's point of view (Eq. 1.2), data-rate can be maintained if for each 1-bit reduction in the number of bits of ADC, sampling rate grows by a factor of 4.

$$B - \alpha \Leftrightarrow f_S \times 4^{\alpha} \tag{2.17}$$

Now, let us examine the total capacity (Eq. 1.1) under this frequency scaling condition:

$$C = (B - \alpha) \times f_S \times 4^{\alpha} \tag{2.18}$$

This shows that for a bandwidth-limited input signal, choosing quantization resolution B between 1 bit and 2 bits ( $B = \ln(4) = 1.38$ ) minimizes the capacity limitations due to the ADC. It is worth mentioning that from Heisenberg's uncertainty principle, existence of an optimum for quantization resolution B between 1 bit and 2 bits ( $B = \frac{1}{\ln(2)} = 1.44$  in this case) for maximum data rate is expected [7].

## 2.5 Testing Methods and Drawbacks

The concept of converting analog signals to digital words is very simple. Yet quantifying the performance and how it limits the system as a whole is challenging given that in most systems, the output of ADC is not the ultimate goal of the system. The IEEE standard [25] provides different test methods for this purpose by considering an ADC as a standalone block.

The most commonly used test setup uses a sine wave as the input of the ADC. The advantage of using a sine wave is that:

<sup>&</sup>lt;sup>10</sup>It should be mentioned that the input signal does not need to be in the first Nyquist zone.

- Appropriate signals are readily available using a sine wave generator.

- It is easy to establish the quality of the sine wave using spectrum analyzer.

- Filters can easily remove harmonics (or sub-harmonics) of the sine wave for a clean input waveform.

- Locked frequency synthesizers can be used to generate the sine wave and the ADC clock for precise timing.

Therefore, many performance metrics such as SNR or ENOB are measured using a sine wave input. However, this convention might not be appropriate for some cases, such as in a hybrid filter bank or a frequency-interleaved architecture where input signal gets completely filtered out before sub-ADCs in undesired channels. Therefore, we have to either re-consider testing methods, or try to rationally correct for any errors.

Moreover, a sine wave test performance does not necessarily represent the performance of the system. For example, while a test sine wave can use the whole ADC's input full scale range, in practice, enough margin should exist such that ADC's input does not saturate. In fact, saturation of input or output of ADC changes the statistical models used in different parts which results in deviation of measurement results from simulations.

Although in this thesis, we will mostly consider standalone ADCs and methods to improve their functionality and performance, since ADCs are usually used as a part of a system with predefined parameters, optimum ADC specifications and architecture changes based on the application.

For example, consider an ADC with clock jitter in a data link where the incoming signal with limited bandwidth of  $\omega_{max}$  is random in time (uniform power spectral density of  $P(\omega) = \frac{P_{sig}}{\omega_{max}}$ ). Using Eq. 2.6 and breaking the input spectrum into small sub-bands, we can write

$$P_{noise} = \int_0^{\omega_{max}} (\omega \sigma_{RMS})^2 P(\omega) d\omega$$

$$= \frac{(\omega_{max} \sigma_{RMS})^2}{3} P_{sig}$$

(2.19)

The factor of 3 (nearly 10dB improvement compared to Eq. 2.8) is due to the fact that in the conventional test method, a distributed quantity (spectral content) is approximated by a lumped quantity (sinusoidal wave at  $\omega_{max}$ ) [23]. Similar results can be derived by performing a statistical analysis [21]. Therefore, in a wideband system, jitter specifications can be almost 10dB relaxed.

Better performance does not necessarily come from wide bandwidth. Consider a softwaredefined radio receiver for example, in which only a narrow portion of the converted signal is relevant. Per wireless standards, these systems should tolerate out-of-band interfering signals with known maximum power based on the wireless standard. Since jitter-induced noise is the convolution of (the derivative of) the input signal and the jitter, low-frequency content<sup>11</sup> of the jitter will not show up in the band-of-interest which means the system can tolerate much higher RMS jitter. In fact, based on the wireless standard, the optimum jitter spectrum can be calculated [26]. Therefore, we will try to distinguish between low-frequency content and wideband content of the jitter when it comes to SNR calculation since low-frequency content can be tolerated in many applications and even compensated (e.g. by using a CDR loop).

<sup>&</sup>lt;sup>11</sup>Close-in phase noise.

# Chapter 3

# **Increasing Information Rate**

In this chapter, we try to go over different structures proposed to increase the effective speed of the analog-to-digital converter. Remember that based on the sampling theorem, in order to perform a perfect digital reconstruction of an analog input signal with a bandwidth of  $f_{max}$ , samples at a rate of  $f_S = 2 \times f_{max}$  are required.

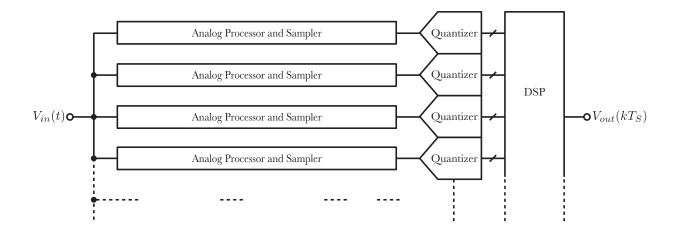

Figure 3.1: Running multiple quantizers in parallel.

Methods of increasing the speed of an ADC can be divided into two general categories:

- 1. Increasing the speed of the quantizer unit: In this category, designer aims to increase the speed of the quantizer. Popular topologies are flash, pipelined, successive-approximation register (SAR), and their combinations.

- 2. Utilizing quantizers in parallel: In this category, with the assumption of a *fixed quantization time*, multiple low-speed quantizers are working in parallel. Before and after quantizer banks, proper analog (analysis) and digital (synthesis) processing are re-

quired for a perfect signal reconstruction. It should be mentioned that processing units still have to satisfy the Nyquist criteria.

Since the assumption of fixed quantization time is not realistic, in order to increase the effective speed of an ADC, there always exists a trade-off between the two aforementioned categories; whether the designer should increase the speed of the each quantizer unit or increase the number of units working in parallel. We will mostly focus on the second category in this chapter as depicted in Fig. 3.1, while providing insight into the trade-offs.

### 3.1 Modulation techniques

In this section, we will introduce some of the proposed methods to use multiple quantizers by modulating the signal before digitizing. While pros and cons are briefly mentioned, details can be found in other references such as [27, 28].

#### Time Interleaving

Figure 3.2: Time-interleaved structure.

Time interleaving (shown in Fig. 3.2) is currently the most popular method of increasing the speed. In this method, each quantizer is connected to a separate sampler (sampling at  $\frac{f_S}{N}$ ) which are driven from N different clock edges. Therefore, quantizer conversion time is N-times relaxed.

Moreover, this method may reduce the power consumption of the whole ADC. Since most of the state-of-the-art quantizers are already working at the limits of the technology, power-speed trade-off is nonlinear, and relaxing conversion time by N results in more than N times reduction in the power consumption of the quantizer [23]. Therefore, considering the total power consumption, we expect that:

$$P_{Quantizer_{f_S}} \ge N \times P_{Quantizer_{f_S}}$$

(3.1)

It should be mentioned that using 50% duty cycle for the sampler relaxes the stepresponse time of the sampler, however, the small-signal bandwidth of the sampler still has to exceed the bandwidth of the input signal which will become the bottleneck. In fact, [23] shows that a medium-resolution ADC negligibly benefits from interleaving for N > 4.

Finally, it should be mentioned that while gain and offset mismatch of the quantizers can be calibrated since the corresponding error is either a DC error or fully correlated with the input signal, sampling time mismatches, which manifest themselves in both the generation and the distribution of the clock phases, cannot be easily calibrated since the corresponding error has no resemblance to the input signal [23].

#### Quadrature Mirror Filter Banks (QMF)

Figure 3.3: High-speed ADC incorporating a QMF Bank.

Using quadrature mirror filter banks (shown in Fig. 3.3) can relax the timing mismatch problem. In a simplified model, after sampling at a rate of  $f_S$ , discreet-time samples are

passed though discrete-time filters, usually designed by switched capacitors. Each filter is designed to pass a specific Nyquist Zone and filter out any spectral content outside of the selected Nyquist zone. The output of the filter is then down-sampled by N and passed to quantizers. Since the input signal passes through a proper bandpass filter, despite subsampling, harmonic folding does not introduce any problems [29].

Since all samplers are driven from the same clock source (as opposed to the time-skewed clocks in in a time interleaved ADC), this architecture is less prone to the time-mismatch issue. Furthermore, assuming that filters are ideal, each channel is only responsible for a specific frequency band. Therefore, in applications where phase distortion can be tolerated, this approach offers an interesting alternative [30].

Finally, it should be mentioned that this technique does not overcome the need for high-speed sampling circuits.

#### **Hadamard Modulation**

Figure 3.4: Parallel quantization using Hadamard modulation.

In QMF architecture, N different analog filters should be designed separately. If sampled data is modulated before the filters, all the filters can be identical.

One such modulation is Hadamard modulation which was originally proposed to be used in the context of  $\Pi\Delta\Sigma$  modulators [31]. A Hadamard matrix  $(M_{N\times N})$  consists exclusively of plus and minus ones and has the property that  $M^TM=NI^{-1}$ . Samples on each channel are

$<sup>^{1}</sup>I$  is the identity matrix.

multiplied by a periodically-extended sequence from one row of Hadamard matrix, filtered, quantized, and multiplied by the same sequence<sup>2</sup>. A sufficient condition for existence of an  $N \times N$  Hadamard matrix is that N be a positive power of two in which the Walsh matrix can be used.

Eq. 3.2 shows an 8 × 8 Walsh matrix. By analyzing this matrix, it can be observed that multiplying each row by the input signal is effectively mixing different frequency components. The advantage of multiplying by a Walsh matrix instead of mixing by sine and cosine functions is that the circuit implementation of multiplying by plus and minus ones<sup>3</sup> is much easier than mixing by corresponding functions. Furthermore, Walsh matrix takes care of harmonic folding which is not an easy task in conventional mixing by sinusoidal functions. In fact, N-path filters can be implemented using Walsh matrices [32]. Due to the required harmonic correction, rows of Walsh matrices of higher order cannot be associated with one single frequency.

Discrete-time analysis is provided in [31]. However, here we provide a generalized and simplified continuous-time mathematical framework. Let us assume that modulation in row k is performed by multiplying the input signal with modulation function  $M_k(t)$ . Then, the modulated signal is passed through a filter and demodulated by multiplication by  $M'_k(t-t_d)$  where  $t_d$  is the relative delay of the modulation and demodulation functions.

$$V_{out}(t) = \sum_{k=1}^{N} M'_{k}(t - t_{d}) \left[ (V_{in}(t)M_{k}(t)) * H(t) \right]$$

(3.3)

where (\*) is the convolution operation and H(t) is the impulse response of the filter. By

<sup>&</sup>lt;sup>2</sup>Or a delayed version of the sequence.

<sup>&</sup>lt;sup>3</sup>Either pass the signal or invert its polarity.

representing the convolution operation in the integral form, we get

$$V_{out}(t) = \sum_{k=1}^{N} M'_{k}(t - t_{d}) \int_{-\infty}^{\infty} V_{in}(t - \tau) M_{k}(t - \tau) H(\tau) d\tau$$

(3.4)

By changing the order of summations and multiplications, we arrive to a simplified equation

$$V_{out}(t) = \int_{-\infty}^{\infty} V_{in}(t-\tau) \left[ \sum_{k=1}^{N} M_k'(t-t_d) M_k(t-\tau) H(\tau) \right] d\tau$$

(3.5)

If  $\sum_{k=1}^{N} M'_k(t-t_d)M_k(t-\tau)$  is chosen to be independent of t, the above equation can be further simplified as

$$V_{out}(t) = \int_{-\infty}^{\infty} V_{in}(t-\tau) \left[ R_{t_d}(\tau) H(\tau) \right] d\tau$$

(3.6)

where  $R_{t_d}(\tau) = \sum_{k=1}^{N} M'_k(t-t_d) M_k(t-\tau)$ . In the frequency domain, we have

$$V_{out}(f) = [R_{t_d}(f) * H(f)] V_{in}(f)$$

(3.7)

A useful scenario is when  $R_{t_d}(f)$  is an impulse train and H(f) is a brick-wall filter. By choosing the right bandwidth for the filter, its impact can be completely compensated after demodulation. Implementation of a brick-wall filter might not be feasible depending on the application. As a popular alternative, integrate-and-dump  $(H_{I-D})$  filters can replace the brick-wall filter<sup>4</sup> as long as

$$R_{t_d}(t)H_{I-D}(t) = \delta(t) \tag{3.8}$$

where  $\delta(t)$  is the Dirac delta function. Therefore, for  $H_{I-D}(t)$ ,  $R_{t_d}(t)$  needs to have a single impulse inside the integration window and any arbitrary value out of that. This criterion can be easily satisfied by making sure that the integration window is equal to the periodicity of the modulator.

#### Hybrid Filter Banks (HFB)

Switched capacitors incorporated in the QMF method limits the speed of the system. Therefore, it makes sense to replace discrete-time QMF filters with continuous-time filters (e.g. LC filters). The new architecture, shown in Fig. 3.5, is called a hybrid filter bank ADC since analysis filters are in the analog domain while synthesis filters <sup>5</sup> are in the digital domain.

Frequency-band separation before sampling allows the sampler to work at N-times lower rate. However, samplers used in higher frequency bands still have to support the high input bandwidth of the corresponding frequency range [33].

$<sup>^4</sup>$ Although there is no obvious penalty in the continuous-time analysis, down-sampling by N after the filter may introduce errors since integrate-and-dump filters do not provide enough bandwidth reduction.

<sup>&</sup>lt;sup>5</sup>Reconstruction of the signal in the digital domain is called synthesis "filter" in the literature since it is usually composed of an up-sampler followed by band-selection filters.

Figure 3.5: High-speed ADC incorporating hybrid filter banks.

The practical challenge in constructing an HFB is to compensate for the effects of hardware components whose characteristics are imprecise and drift with time and temperature [34]. The filter response can be included in the design of the corresponding quantizer using continuous-time bandpass  $\Delta\Sigma$  modulators (CTBPDSM) [35].

#### Frequency-Translating Hybrid Architecture

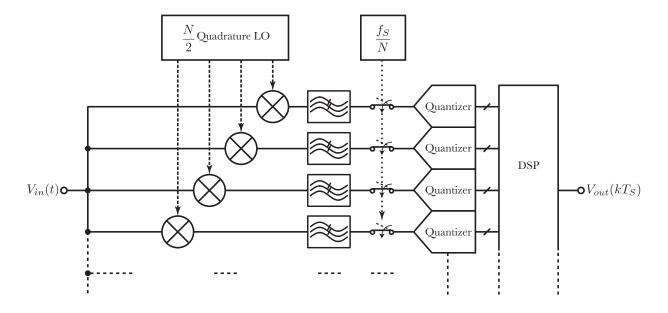

Instead of designing separate filters for each channel in HFB, input signal can be first down-converted with a proper LO frequency and then passed to identical low-pass filters (which can be implemented with no inductors). This frequency-translating hybrid architecture [36], also known as frequency channelized [37] or frequency-interleaved ADC [38] is shown in Fig. 3.6.

In this architecture, sub-ADCs are working in the first Nyquist zone. The reduced input bandwidth of the sampler relaxes the required small-signal bandwidth by N and provides higher tolerance to sampling jitter. Discussion on the filter design can be found in [39]. We will discuss in details about this architecture in next chapters.

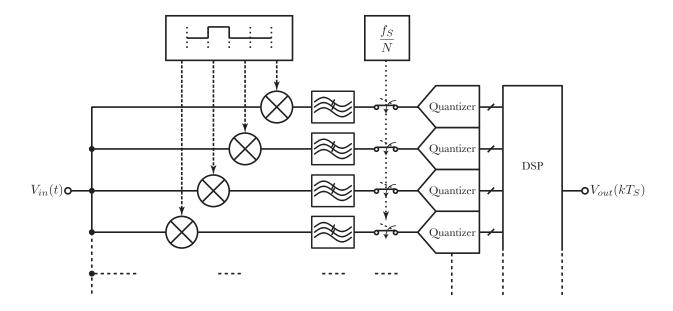

#### Frequency-Folded ADC

As is was previously mentioned, proper modulation before filtering can remove the impact of bandwidth reduction. Modulation can be applied to continuous-time signals. Given that identity matrix (continuously extended in the time domain) can satisfy Eq. 3.8, a

Figure 3.6: Frequency-translating hybrid architecture.

Figure 3.7: Architecture of a frequency-folded ADC.

frequency-folded architecture based on the architecture in Fig. 3.7 can be realized. An interesting advantage of this architecture is that since the full-scale range of the signal before quantization is reduced by N, a gain stage can be used after the filter to increase the total signal power by N. It means that, despite the similarity of this architecture to

time-interleaved ADCs, higher number of channels also result in lower quantization noise. Filter design considerations for this architecture can be found in [40].

### 3.2 Analog-to-Information Conversion

Nyquist rate sampling guarantees full reconstruction of the original signal without taking into account any heuristic or a priori side information about the signal or its information content other than the physical bandwidth [10]. However, a priori information such as sparsity in any domain can be used to reduce the sampling rate well below the physical bandwidth. Therefore, analog-to-information converters (AIC) are proposed in which the input signal is first pre-processed in the analog domain (which is still running at Nyquist rate or higher). For example, an audio signal (20KHz) modulated on an RF carrier (2GHz) is sparse in its bandwidth (2.000002GHz). Analog pre-processing (down-conversion of the RF signal) can relax the Nyquist rate by 5 orders of magnitude while the audio signal is perfectly reconstructed. Sparsity of the incoming signal<sup>6</sup> is the key and as it gets less sparse, the required sample rate gets closer to the Nyquist rate [41].

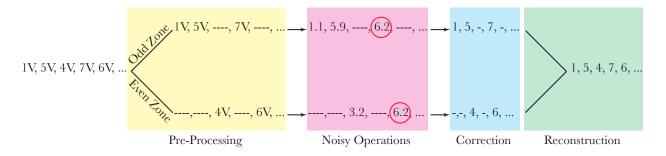

Figure 3.8: Pre-processing at the absence of a priori knowledge.

What happens at the absence of a priori knowledge? Does analog pre-processing still help? Consider the scheme in Fig. 3.8 in which the random analog input voltage generated by a DAC is divided into two zones of odd and even. After pre-processing, each sequence has a higher error margin for any additive noise. Note that at the absence of the pre-processing, 6.2 could be either 6 or 7, however, there is no ambiguity in this scheme. Therefore, the answer is affirmative, and analog pre-processing can still benefit the system if stages later on add considerable noise.

In fact, all of the modulation techniques mentioned in section 3.1 can be considered as special cases of analog to information converters where there is no enhancement due to the input signal sparsity, but design relaxation and noise reduction is achieved through the means of analog pre-processing. When sparsity is provided, same techniques can be combined with compressive sensing algorithms [42].

<sup>&</sup>lt;sup>6</sup>Here in the frequency domain.

Although it has been shown that jitter and other clock nonidealities impact AIC performance [43], as it will be shown in the following chapters, the system as a whole can potentially outperform conventional ADCs.

### 3.3 Performing Modulations

Figure 3.9: Processing all channels in parallel.

Modulation techniques can be immediately applied to the input signal, or the scheme is first dissected into several parts and then sequentially performed on the input signal. Up to here, we assumed that the input signal is directly fed into all of modulators simultaneously as shown in Fig. 3.9. However, it is also possible to dissect the modulation scheme into several parts and perform them sequentially. For example, a balanced<sup>7</sup> tree, as in Fig. 3.10, can be utilized to avoid generating multiple LOs on chip [44]. Also, QMF architecture was originally implemented with a balanced tree structure [45]. From the circuit point of view, having a balanced tree makes the whole system less prone to systematic mismatch between channels. However, the circuit mismatch reduction may introduce other issues. For example, [46] proposes to use an unbalanced tree structure, as depicted in Fig. 3.11, to reduce the error due to the finite harmonic rejection and I/Q imbalance of quadrature mixers.

#### 3.4 Spatio-Temporal Stretching

Another way of dealing with fast signals is to stretch them. Stretching can be done in one domain (e.g. time, space, ...) or a combination of them. Here we will discuss about a few techniques from the literature.

<sup>&</sup>lt;sup>7</sup>Balanced in terms of the circuitry that the signal has to go thorough before it gets sampled.

Figure 3.10: Sequentially processing all channels in a balanced tree.

Figure 3.11: Processing channels in an unbalanced tree.

#### Spatial-Stretching

The key observation here is that a set of parallel quantizers are located separately in space. Therefore, the delay between the travel time of the clock signal and the input signal through the chip and to the input of samplers has be carefully considered and any mismatches should be compensated [47]. However, the mismatch between the travel time can be exploited as a new degree of freedom to relax the system requirements.

For example, consider the architecture in Fig. 3.12 where travel time of the input signal is explicitly increased by extended length of transmission lines. It works like a time-interleaved ADC, but with single clock shared among all ADCs. Similar idea was proposed by [13], however, the spacial stretching does not need to be always implemented artificially. For example, the traveling nature of electromagnetic waves in air can be used, as shown in

Figure 3.12: Spatial stretching using extended transmission line.

Fig. 3.13 [14]. It should be noted that despite relaxed quantization time, the sampler at each ADC still has to cover the whole bandwidth of the input signal, unless modulation techniques are used before samplers.

Figure 3.13: Spatial stretching using antenna array.

#### Time-stretching

Without lose of generality, if we could stretch the signal in time *before* the sampler, not only is the quantization time relaxed, but also the sampling stage would have relaxed timing-related specifications such as small signal bandwidth or rms jitter.

Stretching before the sampling stage is the key here, otherwise the sampler still has to support the whole input bandwidth and the sampling circuity will become the bottleneck [23] eventually. For example, time-interleaving stretches the already-taken samples for the following quantizer. Similarly, in a time-to-digital converter, the processor has more time to quantize the time-domain representative of the input signal after it is generated.

Despite the promising benefits of the time-stretching approach, a direct time-manipulation seems impossible<sup>8</sup>. However, the delay it takes for the input signal to pass through a "time-stretching block" can be modulated over time. It has to be noted that although dispersion can smooth a sharp transition, it is not considered as time-stretching since the mechanism of smoothing the signal is just distorting the frequency components. Now, Let us assume that we have designed a block such that

$$V_{out}(t) = V_{in}(t - \tau(t)) \tag{3.9}$$

where  $\tau$  is the delay between input and output and is a function of time. If we take the time derivative of both sides, we get

$$\frac{\mathrm{d}V_{out}(t)}{\mathrm{d}t} = \left. \frac{\mathrm{d}V_{in}(t')}{\mathrm{d}t'} \right|_{t'=t-\tau(t)} \left( 1 - \frac{\mathrm{d}\tau(t)}{\mathrm{d}t} \right) \tag{3.10}$$

This shows that rate of changes at the output will be smaller than the rate of changes at the input by the stretch factor S of:

$$S = \frac{1}{1 - \frac{\mathrm{d}\tau(t)}{\mathrm{d}t}} \tag{3.11}$$

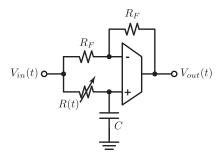

Now, let us consider the all-pass filter in Fig. 3.14. Assuming a limited rate of changes for R(t) such that  $\frac{\mathrm{d}R(t)C}{\mathrm{d}t} \ll 1$ , the output phase as a function of frequency can be written as

$$\Phi_{out}(\omega, t) = -2 \arctan(\omega R(t)C)$$

(3.12)

Calculating the group-delay as  $\tau_g(\omega, t) = -\frac{\mathrm{d}\Phi_{out}(\omega, t)}{\mathrm{d}\omega}$ , we get

$$\tau_g(\omega, t) = \frac{2R(t)C}{1 + (\omega R(t)C)^2}$$

(3.13)

<sup>&</sup>lt;sup>8</sup>Assuming no relativistic velocities or Doppler shift!

Figure 3.14: Time-varying all-pass filter.

and therefore, the rate of changes in the group delay is

$$\frac{\mathrm{d}\tau_g(\omega, t)}{\mathrm{d}t} = 2 \left[ \frac{1 - (\omega R(t)C)^2}{(1 + (\omega R(t)C)^2)^2} \right] \frac{\mathrm{d}R(t)C}{\mathrm{d}t}$$

(3.14)

The term in the bracket is negligible if  $\omega \ll \frac{1}{R(t)C}$ . Therefore, the stretching factor is

$$S \approx \frac{1}{1 - 2\frac{\mathrm{d}R(t)C}{\mathrm{d}t}} \tag{3.15}$$

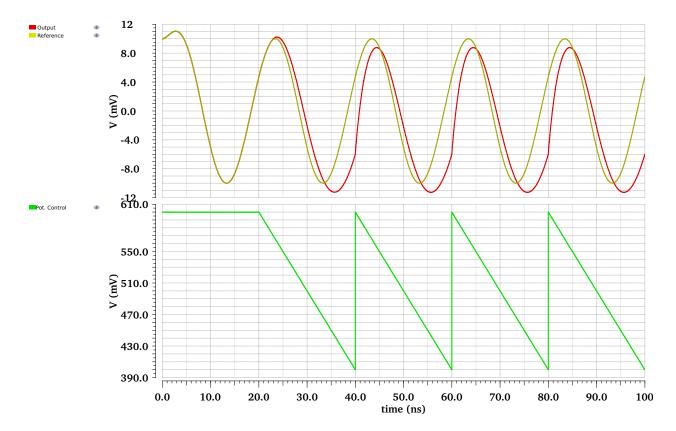

Time-stretching is confirmed by simulation and Fig. 3.15 shows the results where the time-varying resistor is implemented using an NMOS transistor.

It can be seen that since R(t) has a limited variation range, at some point, it has to be reset. Therefore, some sort of segmentation is required (not shown). Hence, time-stretched ADCs are also referred to as segment-interleaved ADCs[48].

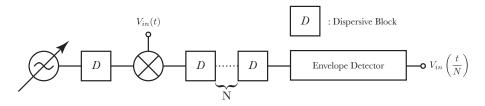

The feedback loop here sets the upper limit of the input bandwidth due to the technology limits. In order to avoid the feedback loop, another approach can be taken [49] as shown in Fig. 3.16:

- 1. Generate a chirped local oscillator<sup>9</sup>.

- 2. Pass the LO signal through a dispersive block.

- 3. Use the input signal to modulate the envelope of the LO signal.

- 4. Pass the modulated wave through a multiple a cascade of N dispersive blocks identical to the one used in the second step<sup>10</sup>.

- 5. Use an envelope detector to recover the stretched input signal.

<sup>&</sup>lt;sup>9</sup>It can be in electrical or optical domain.

<sup>&</sup>lt;sup>10</sup>Amplification might be used between stages. It is due to the temporal spreading of the energy and also dissipation.

Figure 3.15: Simulation results for time-stretching using time-varying all-pass filter.

Figure 3.16: Time-stretching with envelope modulation.

It can be shown the stretch factor here is S = N. Time-stretching based on the aforementioned procedure has been reported in optical domain [50, 51] where low-jitter optical clocks formed by mode-locked lasers are available[12]. Segmentation can be done using filters that pass only a portion of the oscillator's frequency range, and hence called wavelength-interleaved [52]. Electrical domain implementation of a similar idea is also reported [53, 54].

## Chapter 4

## Jitter Error

In this chapter, we investigate the impact of non-ideal LO and clock signals. First, we briefly review the basics of jitter and phase noise and their relationship. Then, we explain about what happens when our time reference is not ideal.

## 4.1 Sampling Error

There are many mechanisms that introduce error to samples of an analog signal from timing perspective which stem from [9]:

- 1. The clock signal driving the sampling stage (assuming ideal sampling circuit) or

- 2. Non-ideal response of the sampling circuitry to the clock signal

or a mixture of both. Let us bring examples for each of them considering an NMOS transistor (as a sampling switch) where its gate is being driven by a clock signal.

- **Jitter Error**: This type of error is coming from the uncertainty on the instance of the analog input which the sampler holds until the next period. The input clock always has phase uncertainty due to different noises added during the generation and distribution. However, even if the clock signal has no phase noise, the sampling circuit itself may cause additional error. For example, the channel response of the transistor switch strongly depends on  $V_{gs}$  where the source port has thermal noise. It also depends weakly on  $V_{sb}$  where the bulk port may have strong supply-induced noise. The slope of the otherwise-ideal clock signal determines how much those noise sources affect the sampling time.

- Aperture error: Since the clock signal has a finite slope, the NMOS transistor does not switch abruptly and the gradual switching adds error to the sample which is not frequency-flat (if modeled as a windowed integration [43]). Moreover, the sampling

switch has dependency on other ports which may make the aperture window tighter or wider.

Figure 4.1: Errors due to the clock edge jitter.

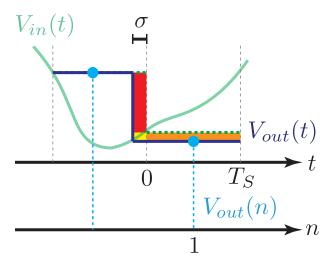

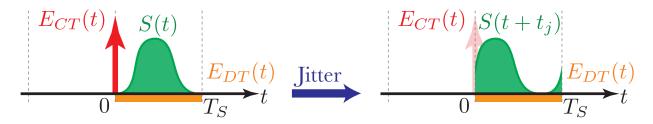

In this thesis, we will focus on the jitter error from the clock signal assuming that the clock has a sharp edge to minimize other impacts. Consider Fig. 4.1 where clock edge at t=0 arrives  $\sigma$  earlier. The continuous-time error has three components (colored as yellow, orange, and red) while the discrete-time error is only sensitive to the final value (colored as orange). The discrete-time error  $(E_{DT}(n))$ : colored as orange can be approximated as:

$$E_{DT}(n) = -\sigma(n) \frac{\mathrm{d}V_{in}(t)}{\mathrm{d}t} \bigg|_{t=nT_{-}}$$

(4.1)

Discrete-time error persists for  $T_S$  in the continuous-time domain. As long as  $\sigma \ll T_S$ , we can ignore the error area colored as yellow. Moreover, with the same assumption, we can model the red error area as an impulse with the same area. Therefore, continuous-time-specific error<sup>1</sup> ( $E_{CT}(t)$ : colored as red) can be written as:

$$E_{CT}(t) = [V_{in}(t) - V_{in}(t - T_S)] \sum_{n} \sigma(t)\delta(nTs)$$

(4.2)

It should be noted that the total error in the continuous-time domain is  $E_{CT}(t) + E_{DT}(t)$  where  $E_{DT}(t)$  is simply the convolution of  $E_{DT}(n)$  and the zero-order hold function.

<sup>&</sup>lt;sup>1</sup>Meaning that it only shows up in the continuous-time domain.

#### 4.2 Phase Noise and Jitter

#### Phase Noise vs Jitter

"Phase noise" and "jitter" are terms that are referring to the same issue: the LO generation circuitry and the LO distribution network have noise and other nonidealities which effectively manipulate the output phase  $(\phi)$  of the sinusoidal LO output. "Phase noise" is the (normalized) power of the noise manipulating the output phase and is usually reported in dBc/Hz which refers to the spectral content of the phase noise in the frequency domain  $(\mathcal{L}(f))$ . If the circuit driven by the LO is only sensitive to zero-crossings (or the clock "edge"), timing uncertainty can be reported with jitter ( $\sigma$  usually reported in ps or fs) which refers to the deviation of the output zero-crossing time from the ideal zero-crossing time. Keep in mind that both  $\phi$  and  $\sigma$  are functions of time implicitly. A popular conversion of phase noise to jitter relies on

$$V_{LO}(t) = \cos(\omega_{LO}t + \phi)$$

= \cos(\omega\_{LO}(t + \sigma))

and  $thus^2$

$$\sigma = \frac{\phi}{\omega_{LO}}$$

however, subtleties are ignored in this equation. First, phase noise  $\phi(t)$  is defined with the spontaneous variations of LO output  $(V_{LO}(t))$ . However, jitter  $\sigma(t)$  deals with the occurrence of zero-crossings at incorrect time  $(V_{LO}(t') = 0)$ :

$$\phi(t): V_{LO}(t) = \cos(\omega_{LO}t + \phi(t))$$

$$\sigma(t): V_{LO}(t - \sigma(t)) = \cos(\omega_{LO}t)$$

In other words, as depicted in Fig. 4.2, phase noise at each time adds a (phase) error parameter to match the y-axis (voltage) of the ideal LO with the noisy LO while jitter has to look ahead and behind in x-axis (time) to find the (time) error parameter which matches with the zero-crossing. For example, in a sampling system, if the phase error at the nominal sampling time is  $\sigma(kT_S)$ , at  $t = kT_S - \sigma(kT_S)$  we have

$$t + \sigma(t)|_{t=kT_S - \sigma(kT_S)} = kT_S - \sigma(kT_S) + \sigma(kT_S - \sigma(kT_S)) \neq 0$$

since  $\sigma(kT_S) \neq \sigma(kT_S - \sigma(kT_S))$  (specially at the presence of noise with high-frequency content). However, if  $\sigma(kT_S) \approx \sigma(kT_S - \sigma(kT_S))$ , the earlier approximation is very close to the simulation results. While the conversion of phase noise to jitter at the absence of high frequency noise is just a matter of finding the right slope<sup>3</sup>, it is not easy to do the conversion

<sup>&</sup>lt;sup>2</sup>Later we show that this equation is not precise.

<sup>&</sup>lt;sup>3</sup>Even with this simplified case, the actual slope may not match with the slope of ideal LO.

Figure 4.2: Subtleties in the definition of the jitter and phase noise.

at the presence of high-frequency noise. Unfortunately there is no easy way of calculating jitter from phase noise other than the equations provided earlier. Therefore, while we keep in mind that modeling error may exist, we will use aforementioned equations.

There is one more issue with the previous sets of equations which cannot be ignored. Remember that jitter only cares about the "clock edges", and therefore it only considers LO output at specific times. In other words, jitter takes samples of time-error only when zero-crossing occurs. This is not a typical sampling scenario, yet as long time-error is small enough compared to the period of the output signal, it can be approximated as a sampling system. Therefore:

- 1. Jitter in the frequency domain has be to described inside the bandwidth of  $[0, \omega_{LO})^4$  while phase noise is described for the whole frequency range  $[0, \infty)$ . Phase noise spectral content above  $\omega_{LO}$  will be folded back into the jitter bandwidth of  $[0, \omega_{LO})$ .

- 2. The phase noise to jitter conversion equation is valid only if we consider the rms power<sup>5</sup>

$$\overline{\sigma} = \frac{\overline{\phi}}{\omega_{LO}} \tag{4.3}$$

3. While derivation of jitter from phase noise is possible, it is not possible to do the opposite.

<sup>&</sup>lt;sup>4</sup>Assuming both rising and falling edges.

<sup>&</sup>lt;sup>5</sup>Strictly speaking, since jitter only cares about zero-crossings, if for any reason the LO output is more or less noisy around zero-crossings, Eq. 4.3 is not valid. However, we will ignore this case.

#### Edge-sensitive Circuitry Driven by Noisy LO

In this part, we assume that LO signal is driving edge-sensitive circuitry. Although the LO is sinusoidal, as long as the circuitry driven by the LO is edge sensitive, there will be an inherent LO sharpening which makes the LO signal look like a square wave. As a reminder, the Fourier series of a square wave  $\Pi(\omega_{LO}t)$  is:

$$\Pi(\omega_{LO}t) = \frac{4}{\pi} \sum_{n:odd}^{\infty} \frac{1}{n} \sin(n\omega_{LO}t)$$

(4.4)

Therefore, if the LO signal has  $\sigma$  jitter, it can be written as:

$$\Pi\left(\omega_{LO}\left(t+\sigma\right)\right) = \frac{4}{\pi} \sum_{n:odd}^{\infty} \frac{1}{n} \sin\left(n\omega_{LO}\left(t+\sigma\right)\right)$$

$$\approx \frac{4}{\pi} \sum_{n:odd}^{\infty} \frac{1}{n} \left(\sin(n\omega_{LO}t) + n\omega_{LO}\sigma\cos(n\omega_{LO}t)\right)$$

$$\approx \frac{4}{\pi} \sum_{n:odd}^{\infty} \frac{1}{n} \sin(n\omega_{LO}t) + \omega_{LO}\sigma\cos(n\omega_{LO}t)$$

(4.5)

Note that although the power of the first term in the series decreases as the n increases, the power of the second term (which indicates the phase noise) remains constant<sup>6</sup>. As Fig. 4.3 depicts, jitter will be up-converted and repeated over the whole frequency band. Before ending this section, let us consider the situation in which jitter  $\sigma$  is white noise and try to simplify Eq. 4.5. Given that white noise has a uniform spectral density, the double side-band power spectral density is  $|\sigma_{DSB}(\omega)|^2 = \frac{\sigma_{RMS}^2}{2\omega_{LO}}$ . This jitter is multiplied in the time domain by  $\omega_{LO} \sum_{n:odd}^{\infty} \cos(n\omega_{LO}t)$  which means a convolution of  $\sigma_{DSB}(\omega)$  with  $\omega_{LO} \sum_{-\infty}^{\infty} \frac{1}{2}\delta((2n+1)\omega_{LO})$  in the frequency domain. The result of this convolution is

$$|\sigma'_{DSB}(\omega)|^{2} = \left| \mathcal{L} \left\{ \sigma(t) \times \omega_{LO} \sum_{n:odd}^{\infty} \cos(n\omega_{LO}t) \right\} \right|^{2}$$

$$= \left| \sigma_{DSB}(\omega) * \omega_{LO} \sum_{-\infty}^{\infty} \frac{1}{2} \delta((2n+1)\omega_{LO}) \right|^{2}$$

$$= \frac{\sigma_{RMS}^{2}}{2\omega_{LO}} \times \frac{\omega_{LO}^{2}}{2^{2}}$$

$$= \frac{\omega_{LO}\sigma_{RMS}^{2}}{8}$$

$$(4.6)$$

<sup>&</sup>lt;sup>6</sup>It may seem like that the noise power approaches infinity if the noise remains constant over the whole bandwidth. However, remember that  $\sigma$  is a discrete function of time and this "mathematical" modeling error occurs since we are mixing discrete-time and continuous-time functions together.

Figure 4.3: Effective spectrum of a noisy LO (with jitter) after passing through an edge-sensitive circuitry.

Therefore, in the case of white jitter, Eq. 4.5 can be written as

$$\Pi\left(\omega_{LO}\left(t+\sigma\right)\right) \approx \frac{4}{\pi} \left( \left[ \sum_{n:odd}^{\infty} \frac{1}{n} \sin(n\omega_{LO}t) \right] + \sigma'(t) \right)$$

$$\approx \Pi\left(\omega_{LO}t\right) + \frac{4}{\pi} \sigma'(t)$$

(4.7)

where  $\sigma'(t)$  has a single side-band power spectral density of

$$\left|\sigma_{SSB}'(\omega)\right|^2 = \frac{\omega_{LO}\sigma_{RMS}^2}{4} \tag{4.8}$$

#### Frequency Division

In this part, we will review the impact of frequency division on the jitter and its spectral content. Such a circuitry effectively divides the phase accumulation of sinusoidal signal:

$$\sin(\phi) \xrightarrow{Freq.\,Div.} \sin\left(\frac{\phi}{DR}\right)$$

where  $DR = \frac{\omega_{LO}}{\omega_{Div}}$  stands for "Division Ratio". If we substitute  $\phi = \omega_{LO}(t+\sigma)$ , we have:

$$\sin(\omega_{LO}(t+\sigma)) \xrightarrow{Freq. Div.} \sin\left(\frac{\omega_{LO}}{DR}(t+\sigma)\right) = \sin(\omega_{Div}(t+\sigma))$$

Therefore, after frequency division, **rms of jitter** remains almost the same<sup>7</sup>. Could we say that the jitter of the LO signal is the same as the frequency-divided signal<sup>8</sup>? It depends on the application and modeling precision needed. Remember that the jitter of an oscillator with angular frequency of  $\omega_{osc}$  is a discrete function of time with a bandwidth of  $[0, \omega_{osc})$ . After division, the new jitter is a sampled version of the undivided-LO jitter in the time domain and thus, in the frequency domain, aliasing happens and the divided-LO's jitter spectrum looks completely different. In order to simplify the aliasing analysis, we assume that the LO jitter has two separate contributors:

- 1. "Close-in" phase noise concentrated at frequency below the divided frequency  $[0, \omega_{Div})$ .

- 2. "Far-out" phase noise uniformly distributed in the bandwidth of  $[0, \omega_{LO})$  like a white noise.

With these assumptions, the jitter spectral content of the divided LO  $(S_{LO,Div})$  will be as following:

- The close-in portion of the jitter is the same as the close-in portion of the LO jitter  $(S_{LO})$  with no aliasing.

- The far-out portion is uniformly distributed in the bandwidth of  $[0, \omega_{Div})$  while in the frequency domain, the spectral content is DR times higher due to aliasing. Keep in mind that the total far-out noise power is almost the same since  $\omega_{LO} \times S_{LO} = \frac{\omega_{LO}}{DR} \times [DR \times S_{LO}] = \omega_{Div} \times S_{LO,Div}$ .

Figure 4.4: Jitter spectrum before and after frequency division.

Fig. 4.4 shows the impact of division on the jitter profile. Now let us mathematically investigate what the phase noise looks like for an edge-sensitive circuitry. Using Eq. 4.5, we

<sup>&</sup>lt;sup>7</sup>Phase noise power at the harmonics of divided output will vanish.

<sup>&</sup>lt;sup>8</sup>Assuming ideal noise-less division.

observe that

$$\Pi\left(\omega_{Div}\left(t + \sigma_{Div}\right)\right) \approx \frac{4}{\pi} \sum_{n:odd}^{\infty} \frac{1}{n} \sin(n\omega_{Div}t) + \omega_{Div}\sigma_{Div}\cos(n\omega_{Div}t)$$

(4.9)

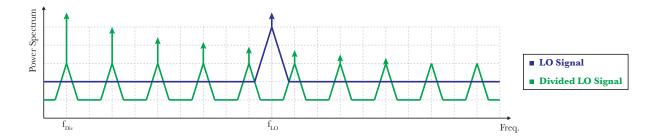

the effective power of each noise term is  $DR^2$  times lower. Therefore,

- The close-in content of the LO jitter will repeatedly appear at the phase noise spectrum every  $2\omega_{Div}$  with a  $DR^2$  lower spectral power level.

- The far-out content of the LO jitter will uniformly appear all over the frequency range  $[0, \infty)$  with a DR lower spectral power level.

Figure 4.5: Effective LO spectrum for an edge-sensitive circuitry before and after frequency division.

Fig. 4.5 summarizes what the LO signal looks like for an edge-sensitive block after frequency division. Also, simulation results (Fig. 4.6) confirms the theory provided here.

### 4.3 Phase Noise Sources

In this section, we will briefly discuss about the origin of the jitter error. Fig. 4.7 shows a simplified architecture with focus on the LO generation and distribution. Different contributors are:

- Off-chip time reference is usually modeled to have a white phase noise.

- The PLL usually has a bandwidth much smaller than the reference frequency and therefore, the close-in phase noise of the VCO is controlled by the PLL. State-of-the-art locked oscillators have around  $50fs \sim 100fs$  of RMS jitter [55] from close-in phase noise.

- Out of the PLL bandwidth, the VCO is the dominant noise source. While a ring oscillator has white far-out phase noise, an LC oscillator's phase noise scales with  $\frac{1}{f^2}$ .

Figure 4.6: Simulation of the effective LO spectrum for an edge-sensitive circuitry before and after frequency division.

Figure 4.7: Simplified model of LO generation and distribution to the sampling stage.

• Noise added by any blocks after VCO is not controlled by the PLL. Therefore, buffers

and all other circuitry to generate sampling clocks (from the master VCO) has to burn enough power to lower the phase noise. State-of-the-art generation and distribution networks also have around  $50fs \sim 100fs$  of RMS jitter [2] from far-out phase noise.

It should be noted that since sharp clock edges are favorable, using LC tuned networks, specially at low sampling rates<sup>9</sup>, is not desirable. Therefore, buffers usually contribute to a flat phase noise.

## 4.4 Principles of Improving Jitter-limited SNR

In this section, we will discuss about the principles of how the SNR can be improved in a system which the noise level is dominated by the sampling jitter. We will show that the system architecture by itself cannot improve jitter-limited SNR unless more "timing units" are used. Keep in mind that a "timing unit" is not always an off-chip crystal oscillator. We can use anything else which has memory effect:

- A notch filter with a specific center frequency. 10.

- Time domain response of a filter.

- Delay of a transmission line<sup>11</sup>.

- Multiple oscillators (as long as they are independent with uncorrelated noise).

## Mix then Sample

Let us investigate what happens if the input signal is first down-converted and then passed to the ADC.

$$V_{in}(t) = A\cos(\omega_{in}t)$$

$$V_{LO}(t) = \cos(\omega_{LO}(t+\sigma))$$

$$V_{CLK}(t) = \cos(\omega_{CLK}(t+\sigma))$$

where  $V_{in}(t)$  is the ADC input,  $V_{LO}(t)$  is the mixer LO, and  $V_{CLK}(t)$  is the clock to the sampler, as illustrated in Fig. 4.8. Assuming that the lower side-band is the desired one after the mixer, at the input of the sampler  $(V_S(t))$  we have:

$$V_S(t) = A\cos(\omega_{in}t - \omega_{LO}(t+\sigma))$$

=  $A\cos((\omega_{in} - \omega_{LO})t - \omega_{LO}\sigma)$

<sup>&</sup>lt;sup>9</sup>Remember that even high sampling rate ADCs usually have time-interleaved channels were sampling of each channel does not exceed a few gigahertz.

<sup>&</sup>lt;sup>10</sup>The most famous on-chip time reference, the LC circuit, is a notch filter.

<sup>&</sup>lt;sup>11</sup>In general, any physical routing.

Figure 4.8: Mixer-assisted sampler with only one time reference

Now  $V_S(t)$  should be sampled by the zero-crossing of  $V_{CLK}(t)$ . Keep in mind that if  $V_{CLK}$  is  $\sigma$  seconds ahead of time, sampling happens  $\sigma$  seconds earlier which means that the sample belongs to  $kT_S - \sigma$ .

$$V_S(kT_S) = A\cos((\omega_{in} - \omega_{LO})(kT_S - \sigma) - \omega_{LO}\sigma)$$

=  $A\cos((\omega_{in} - \omega_{LO})kT_S - (\omega_{in} - \omega_{LO})\sigma - \omega_{LO}\sigma)$

=  $A\cos((\omega_{in} - \omega_{LO})kT_S - \omega_{in}\sigma)$

When the output is digitally up-converted, we end up with

$$V_{out}(kT_S) = A\cos(\omega_{in}kT_S - \omega_{in}\sigma)$$

$$= A\cos(\omega_{in}(kT_S - \sigma))$$

which is the same as Eq. 2.5 and the same SNR is be expected. It should have been obvious from the beginning that if you have one and only one (time) reference which is used to conduct any type of measurement, the accuracy of the result will not be better than the accuracy of the reference in a memory-less system.

Now, let us quickly do the same math again, but this time, we will take the delay of the frequency divider  $t_d$  into account and define  $\sigma_d(t) = \sigma(t - t_d)$ . Therefore, we have

$$V_{in}(t) = A\cos(\omega_{in}t)$$

$$V_{LO}(t) = \cos(\omega_{LO}(t+\sigma))$$

$$V_{CLK}(t) = \cos(\omega_{CLK}(t+\sigma_d))$$

$$V_S(t) = A\cos(\omega_{in}t - \omega_{LO}(t+\sigma))$$

$$= A\cos((\omega_{in} - \omega_{LO})t - \omega_{LO}\sigma)$$

$$V_S(kT_S) = A\cos((\omega_{in} - \omega_{LO})(kT_S - \sigma_d) - \omega_{LO}\sigma)$$

$$= A\cos((\omega_{in} - \omega_{LO})kT_S - (\omega_{in} - \omega_{LO})\sigma_d - \omega_{LO}\sigma)$$

$$V_{out}(kT_S) = A\cos(\omega_{in}kT_S - (\omega_{in} - \omega_{LO})\sigma_d - \omega_{LO}\sigma)$$