# Broadband mm-Wave Transceivers for Sensing and Communication

Andrew Townley

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2020-25 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2020/EECS-2020-25.html

May 1, 2020

Copyright © 2020, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Broadband mm-Wave Transceivers for Sensing and Communication

by

Andrew Townley

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Elad Alon Professor Martin White

Spring 2018

|       | tion of Andrew Tommunication, | Broadband m | m-Wave Transc | eeivers for |

|-------|-------------------------------|-------------|---------------|-------------|

|       |                               |             |               |             |

|       |                               |             |               |             |

|       |                               |             |               |             |

|       |                               |             |               |             |

|       |                               |             |               |             |

| Chair |                               |             | Date          |             |

|       |                               |             | Date          |             |

|       |                               |             | Date          |             |

|       |                               |             |               |             |

University of California, Berkeley

# Broadband mm-Wave Transceivers for Sensing and Communication

Copyright 2018 by Andrew Townley

#### Abstract

Broadband mm-Wave Transceivers for Sensing and Communication

by

Andrew Townley

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali M. Niknejad, Chair

Scaling in silicon semiconductor process technology, although driven by digital applications, has also enabled the operation of analog integrated circuits (ICs) at higher and higher frequencies. Over the past 15-20 years, ICs operating at millimeter-wave (mm-Wave), the frequency range between 30 GHz and 300 GHz, have been demonstrated with increasing performance and complexity.

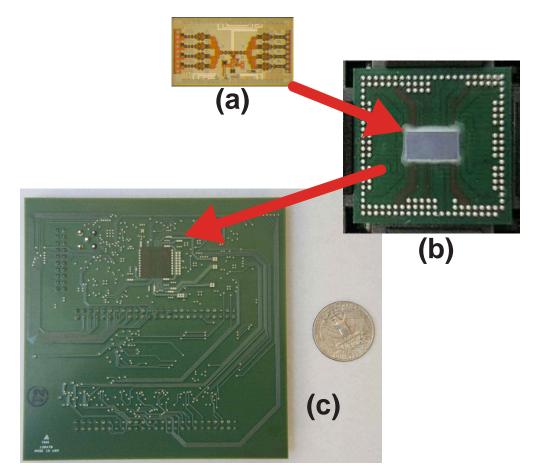

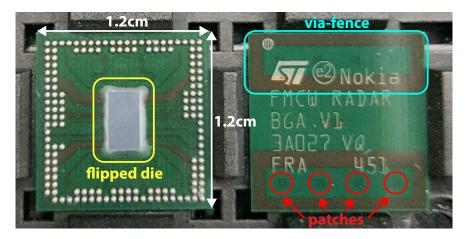

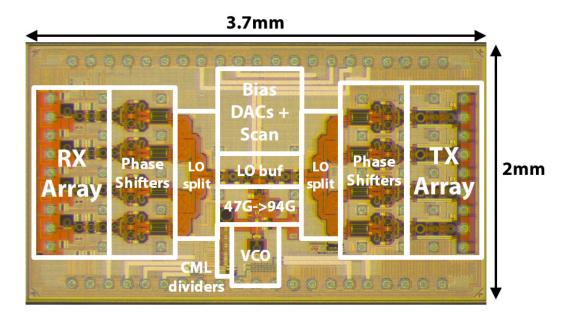

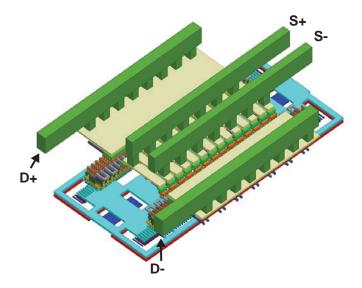

One important application for mm-Wave ICs has been in automotive radar, where they have been used to make accurate measurements of distance and velocity with minimal processing required. There also has been significant interest in adapting this technology for non-vehicular applications, such as gesture recognition, room occupancy detection, or heart-rate monitoring, where performance and energy efficiency are both important. The first part of this thesis describes a custom IC for gesture recognition radar demonstrating state-of-the-art energy efficiency. The IC consists of four transmitters and four receivers with shared frequency generation circuitry, and is packaged onto a 1.2x1.2cm antenna module containing eight antennas.

The other key application for mm-Wave technology has been for wireless communication. Products are finally coming to the market now that offer nearly 5 Gigabits per second of wireless data throughput for indoor wireless LAN applications, and mm-Wave technology will likely play a role in the next generation of wireless cellular standards as well. To demonstrate the possibility for yet-higher data rates to be achieved, a broad-bandwidth custom integrated circuit transceiver has been designed targeting a factor of 10 improvement in wireless data throughput beyond commercially available technology. The second half of this thesis will discuss the details of a transceiver and antenna design for broad-bandwidth and high data rate operation.

## To my parents,

without whose love and encouragement I never could have made it this far.

# Contents

| C  | onten                  | ats                                                   | ii |  |  |  |  |  |  |  |  |  |

|----|------------------------|-------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|

| Li | st of                  | Figures                                               | iv |  |  |  |  |  |  |  |  |  |

| Li | st of                  | Tables                                                | ix |  |  |  |  |  |  |  |  |  |

| 1  | <b>Intr</b><br>1.1     | Poduction  Motivation                                 |    |  |  |  |  |  |  |  |  |  |

| 2  | Mill                   | limeter-Wave Background                               | 4  |  |  |  |  |  |  |  |  |  |

|    | 2.1                    | Technology: Bipolar vs MOSFET                         | 4  |  |  |  |  |  |  |  |  |  |

|    | 2.2                    | LO Generation and Distribution                        | 5  |  |  |  |  |  |  |  |  |  |

|    | 2.3                    | Modulation Techniques                                 | 5  |  |  |  |  |  |  |  |  |  |

|    |                        | 2.3.1 Modulation Techniques for Radar                 | 5  |  |  |  |  |  |  |  |  |  |

|    |                        | 2.3.2 Modulation Techniques for Digital Communication | 7  |  |  |  |  |  |  |  |  |  |

|    | 2.4                    | Phased Array Techniques                               | 10 |  |  |  |  |  |  |  |  |  |

| 3  | $\mathbf{F}\mathbf{M}$ | FMCW Radar Phased-Array Transceiver Design            |    |  |  |  |  |  |  |  |  |  |

|    | 3.1                    | Proposed System Architecture                          | 11 |  |  |  |  |  |  |  |  |  |

|    | 3.2                    | Transmitter                                           | 13 |  |  |  |  |  |  |  |  |  |

|    | 3.3                    | Phase Shifter                                         | 16 |  |  |  |  |  |  |  |  |  |

|    | 3.4                    | LO Distribution                                       | 18 |  |  |  |  |  |  |  |  |  |

|    | 3.5                    | Receiver                                              | 22 |  |  |  |  |  |  |  |  |  |

|    | 3.6                    | Packaging                                             | 25 |  |  |  |  |  |  |  |  |  |

| 4  | Rad                    | lar IC Measurements                                   | 28 |  |  |  |  |  |  |  |  |  |

|    | 4.1                    | Probe Station Measurements                            | 29 |  |  |  |  |  |  |  |  |  |

|    |                        | 4.1.1 LO                                              | 29 |  |  |  |  |  |  |  |  |  |

|    |                        | 4.1.2 Transmitter                                     | 29 |  |  |  |  |  |  |  |  |  |

|    |                        | 4.1.3 Receiver                                        | 30 |  |  |  |  |  |  |  |  |  |

|    | 4.2                    | Packaged Measurements                                 | 31 |  |  |  |  |  |  |  |  |  |

|    |                        | 4.2.1 Array Characterization                          | 31 |  |  |  |  |  |  |  |  |  |

|    |                        | 4.2.2 Radar Measurements and Characterization         | 35 |  |  |  |  |  |  |  |  |  |

|    | 4.3    | Conclusion                                               | 37  |

|----|--------|----------------------------------------------------------|-----|

| 5  | Wic    | leband mm-Wave Transceiver Design                        | 40  |

|    | 5.1    | Motivation and System Architecture                       | 40  |

|    |        | 5.1.1 System Architecture                                | 41  |

|    |        | 5.1.2 Packaging Approach                                 | 42  |

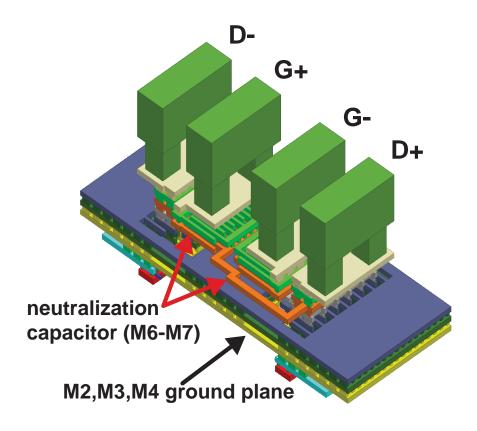

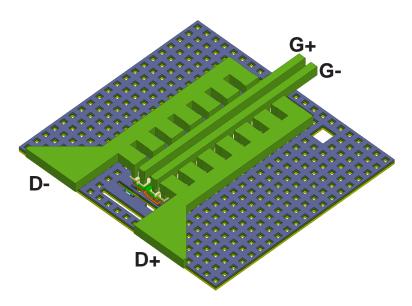

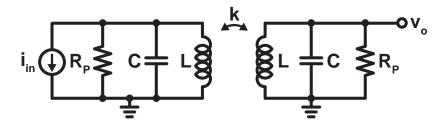

|    | 5.2    | Building Blocks                                          | 44  |

|    |        | 5.2.1 Modular Common-Source Neutralized Amplifier Layout | 44  |

|    |        | 5.2.2 Coupled Resonators using Low-K Transformers        | 45  |

|    |        |                                                          | 49  |

|    | 5.3    | · ·                                                      | 51  |

|    |        | 5.3.1 Modulator Design                                   | 51  |

|    |        | ~                                                        | 68  |

|    |        |                                                          | 71  |

|    | 5.4    |                                                          | 74  |

|    |        | 5.4.1 Baseband Amplification                             | 74  |

|    |        | 5.4.2 Active Mixer with TIA load                         | 75  |

|    |        | 5.4.3 LNA                                                | 81  |

|    |        |                                                          | 83  |

|    | 5.5    |                                                          | 84  |

|    |        |                                                          | 85  |

|    |        |                                                          | 88  |

|    |        |                                                          | 89  |

|    |        | <u> </u>                                                 | 94  |

|    | 5.6    |                                                          | 98  |

|    | 5.7    |                                                          | 01  |

| 6  | Con    | aclusion 1                                               | 02  |

|    | 6.1    | Summary of Thesis                                        | 02  |

|    | 6.2    | ·                                                        | 03  |

|    |        |                                                          | 03  |

|    |        | · ·                                                      | 04  |

| Bi | ibliog | graphy 1                                                 | .05 |

# List of Figures

| 1.1  | United States Frequency Allocations Chart, 30–300GHz band                                                                                                                                                                                            | 2   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

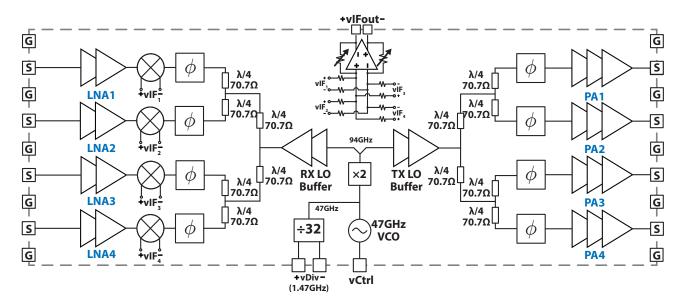

| 3.1  | Complete phased-array transceiver block diagram. mm-wave IOs use a single-ended, ground-signal-ground (GSG) pad configuration. Ground pads are shared                                                                                                |     |

|      | between adjacent phased-array elements to reduce die area                                                                                                                                                                                            | 12  |

| 3.2  | Three-stage power amplifier schematic. $R_5$ is chosen to result in an emitter voltage of about 100mV under small-signal bias conditions. The annotated DC currents correspond to the operating points in small-signal (left of arrow) and saturated |     |

|      | large-signal (right of arrow) conditions                                                                                                                                                                                                             | 13  |

| 3.3  | Full 3D EM model of PA interstage and output transformers                                                                                                                                                                                            | 14  |

| 3.4  | Simulated PA power gain and power-added efficiency at 94GHz, plotted versus                                                                                                                                                                          |     |

|      | output power                                                                                                                                                                                                                                         | 15  |

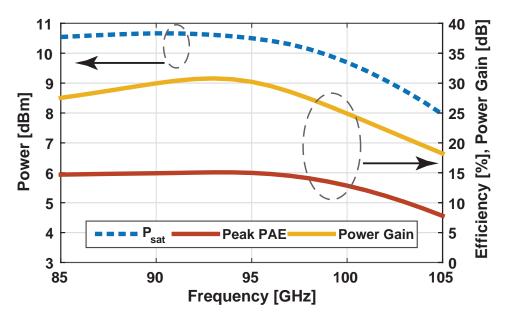

| 3.5  | Simulated PA saturated output power, power gain, and peak power-added effi-                                                                                                                                                                          |     |

|      | ciency vs. frequency.                                                                                                                                                                                                                                | 16  |

| 3.6  | Phase shifter schematic                                                                                                                                                                                                                              | 17  |

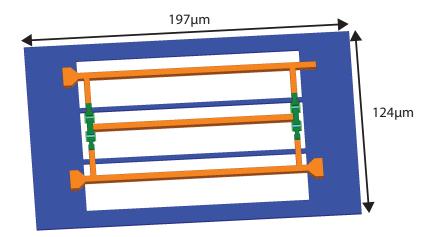

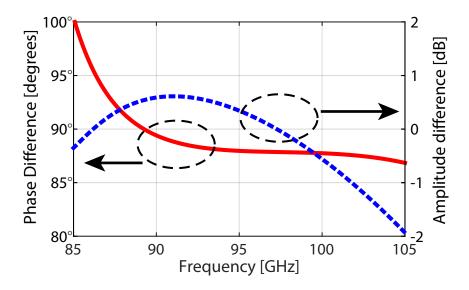

| 3.7  | Quadrature hybrid HFSS model. The dimensions of the simulated region are                                                                                                                                                                             |     |

|      | $197 \mu \text{m} \text{ by } 124 \mu \text{m}. \dots \dots$                                                                                   | 18  |

| 3.8  | Quadrature hybrid simulated IQ mismatch                                                                                                                                                                                                              | 18  |

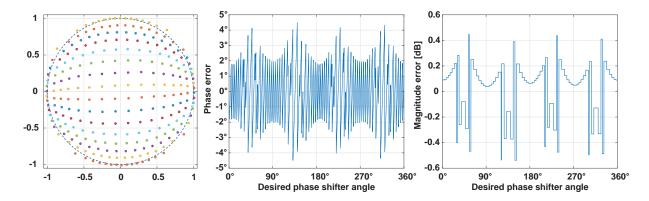

| 3.9  | Phase shifter constellation points, showing combinations of phase and amplitude                                                                                                                                                                      |     |

|      | settings, and the phase and amplitude error for a desired phase angle                                                                                                                                                                                | 19  |

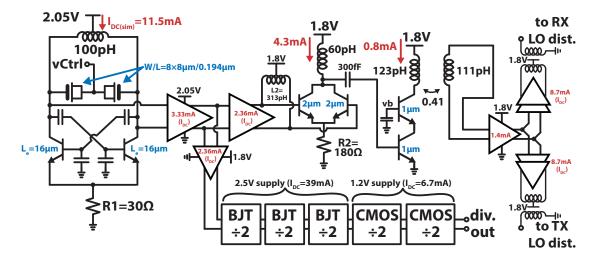

|      | Schematic of LO generation and distribution circuitry                                                                                                                                                                                                | 20  |

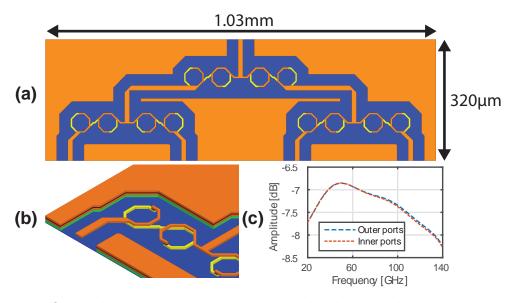

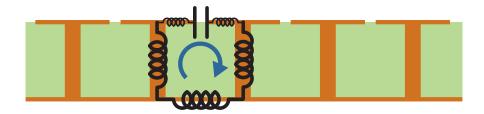

| 3.11 | LO distribution network and power divider, based on lumped-element artificial                                                                                                                                                                        |     |

|      | transmission line. Each artificial quarter-wavelength line consists of a 1.5 turn                                                                                                                                                                    |     |

|      | inductor in series with a 1.25 turn inductor, which interfaces with a 50ohm trans-                                                                                                                                                                   | 0.0 |

| 0.40 | mission line.                                                                                                                                                                                                                                        | 20  |

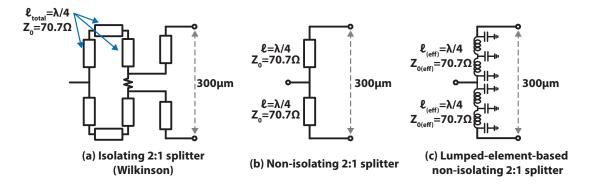

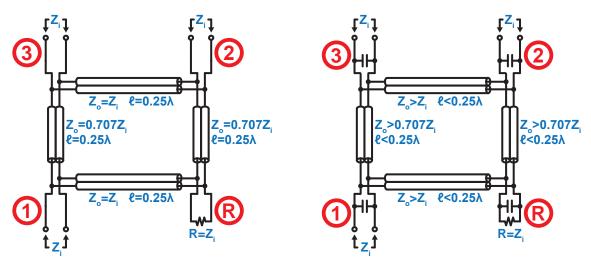

|      | Power splitter topologies considered for LO distribution                                                                                                                                                                                             | 22  |

|      | Receiver schematic                                                                                                                                                                                                                                   | 22  |

|      | Input impedance locus of the LNA, at various stages of the matching network                                                                                                                                                                          | 23  |

|      | Receiver HFSS model                                                                                                                                                                                                                                  | 24  |

| 3.16 | Simulated receiver conversion gain and noise figure vs mixer LO frequency, for                                                                                                                                                                       | 0.4 |

|      | all 5 gain control settings                                                                                                                                                                                                                          | 24  |

|                                 | (a) Percentage contributions of different blocks to total output noise. The contributions are separated by sideband. (b) Noise circles                                                                                                  | 25                              |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                 | HFSS simulations of antenna module                                                                                                                                                                                                      | 25                              |

| 3.20                            | to a much smaller size                                                                                                                                                                                                                  | <ul><li>26</li><li>27</li></ul> |

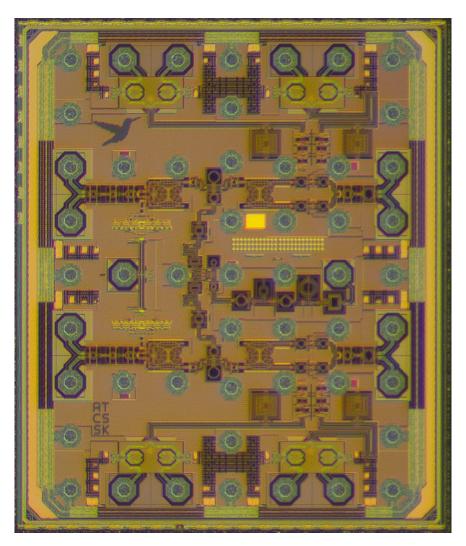

| 4.1<br>4.2<br>4.3               | Die photograph of fabricated chip                                                                                                                                                                                                       | 28<br>29<br>30                  |

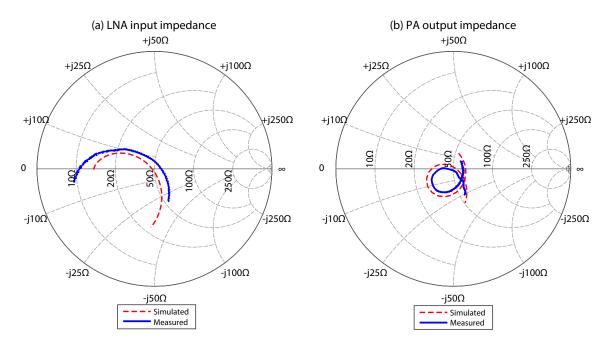

| 4.4                             | The measured LNA input impedance (a) and PA output impedance (b) showed good agreement with simulation                                                                                                                                  | 30                              |

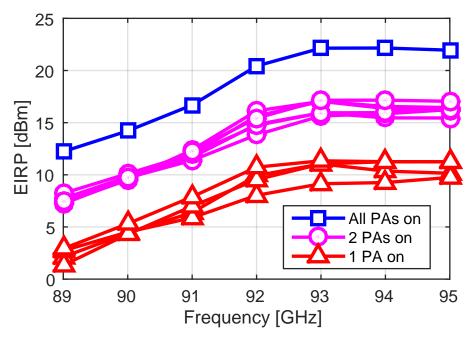

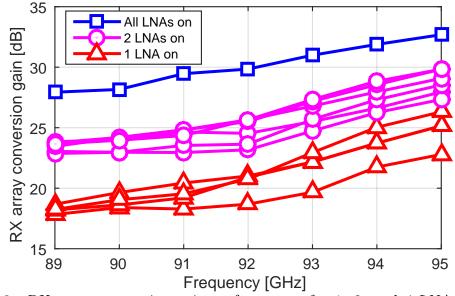

| 4.5<br>4.6                      | Measured receiver single-sideband noise figure (probe station) vs frequency EIRP at broadside vs frequency, for 1, 2, and 4 PAs enabled. All possible combinations of the 1 and 2 PA cases are plotted                                  | 31<br>32                        |

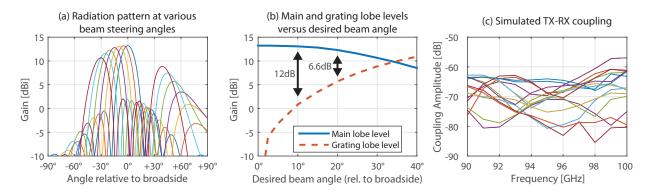

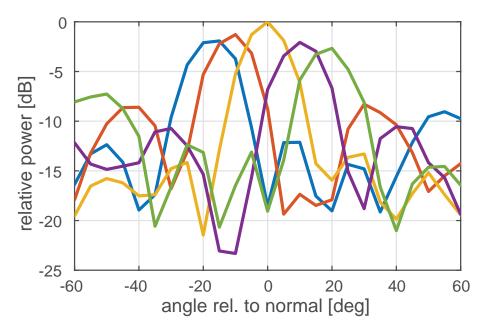

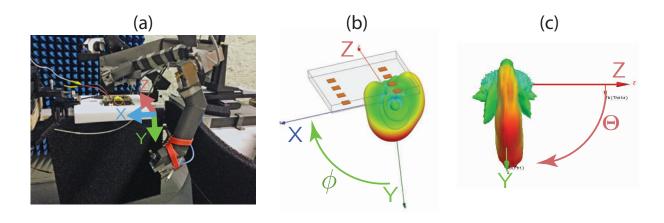

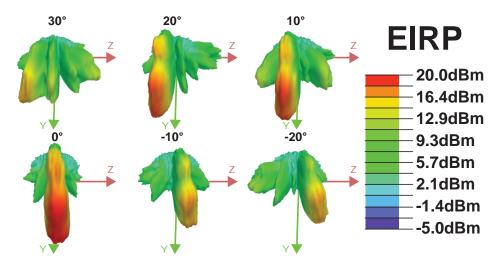

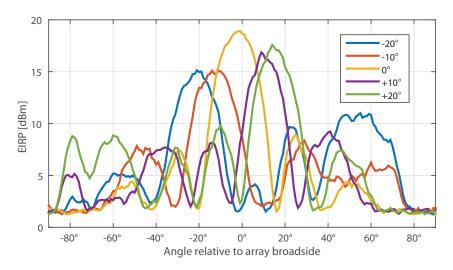

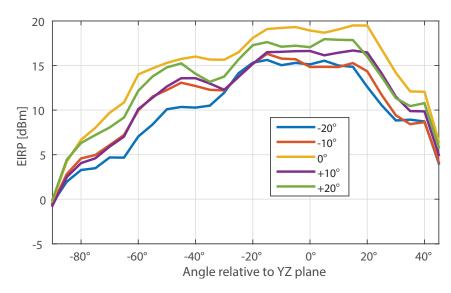

| 4.7                             | Beam steering of transmitter at 94GHz, characterized manually at BWRC                                                                                                                                                                   | 33                              |

| 4.8                             | RX array conversion gain vs frequency, for 1, 2, and 4 LNAs enabled. All possible combinations of the 1 and 2 LNA cases are plotted                                                                                                     | 33                              |

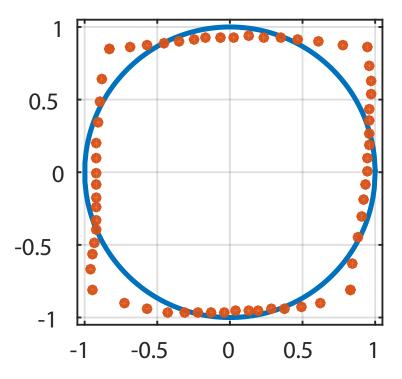

| 4.9<br>4.10                     | Measured phase shifter constellation points, with circle showing amplitude level with least average amplitude error                                                                                                                     | 34                              |

|                                 | placed with the radiating side downward, and the arm with the receive antenna is swept across phi and theta angles. The measured radiation pattern data is imported into HFSS and plotted. The axes shown in (a) correspond to the axes | 34                              |

| 4.11                            | in the HFSS plots (subfigures b and c)                                                                                                                                                                                                  |                                 |

| 4.13                            | at UNS)                                                                                                                                                                                                                                 | 35<br>36<br>36                  |

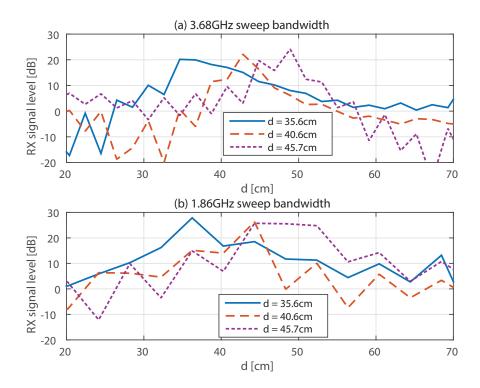

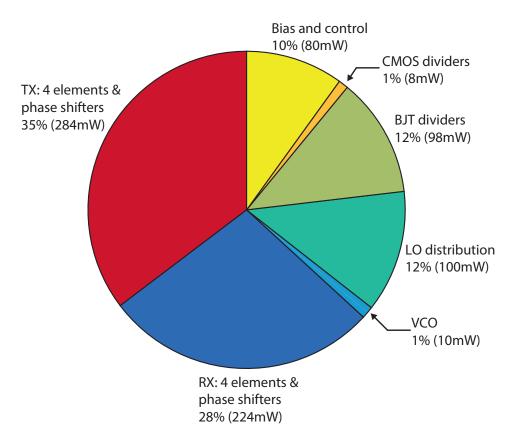

|                                 | sweep bandwidth (b) with narrower RF sweep bandwidth                                                                                                                                                                                    | 37<br>39                        |

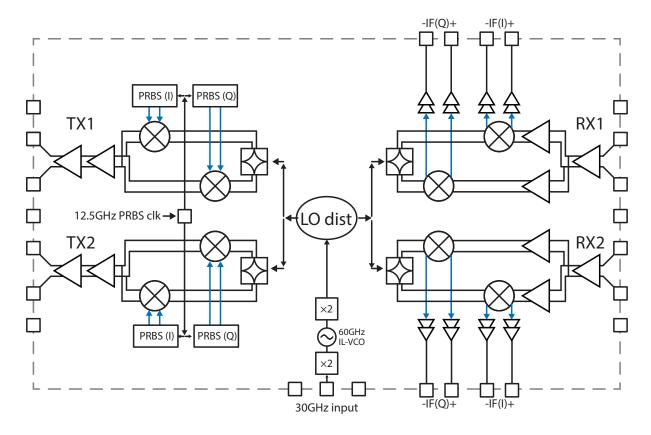

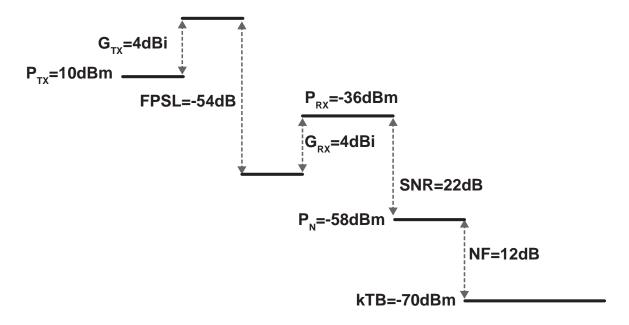

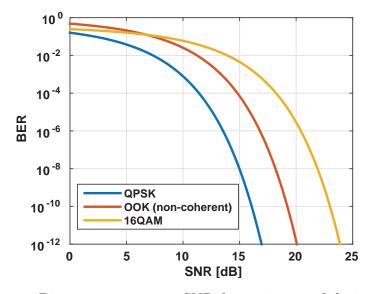

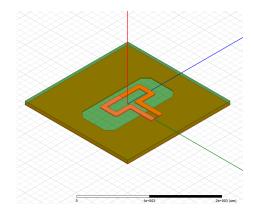

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Block diagram of 120GHz dual-channel communication transceiver.  Link budget, assuming a 10cm transmit distance.  Bit error rate versus SNR for various modulation techniques.  Angle view of neutralized unit cell layout              | 42<br>43<br>43<br>44<br>45      |

|                                 |                                                                                                                                                                                                                                         |                                 |

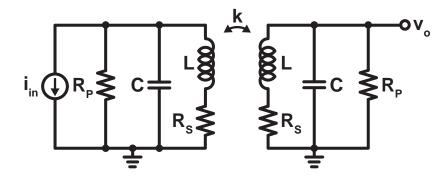

| 5.6  | Magnetically coupled LC resonators                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------------|

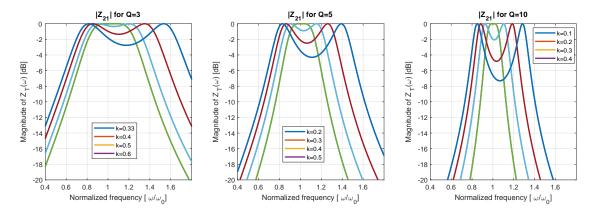

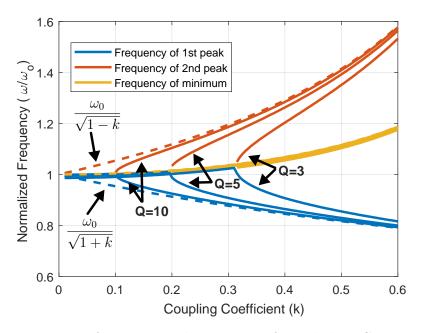

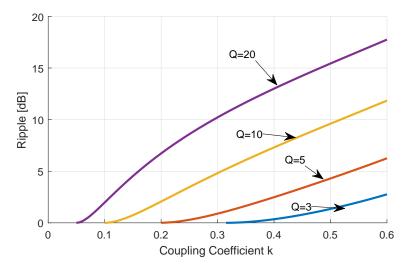

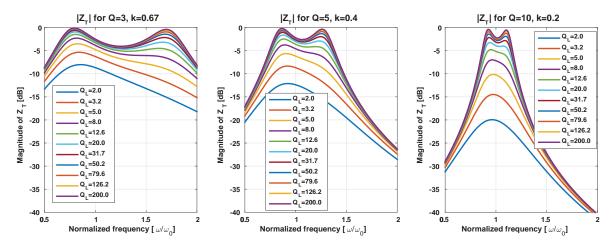

| 5.7  | $ Z_{21} $ transfer functions for various values of the uncoupled resonator Q                                                |

| 5.8  | Frequencies of maxima and minimum of coupled RLC circuit transimpedance for                                                  |

|      | various values of Q                                                                                                          |

| 5.9  | Ripple of the magnitude of the transimpedance vs coupling coefficient                                                        |

| 5.10 | Magnetically coupled LC resonators with finite Q inductors                                                                   |

| 5.11 | $ Z_{21} $ transfer functions with finite-Q inductors                                                                        |

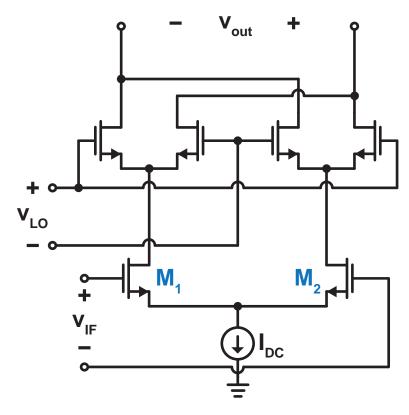

| 5.12 | Conventional upconversion mixer topology typically used at low frequencies 5                                                 |

|      | Unit element of common-gate RF DAC                                                                                           |

| 5.14 | DAC operation for 8-level amplitude modulation. The DAC is depicted at code                                                  |

|      | 101, so the total current at the output is $+\frac{4}{7} - \frac{2}{7} + \frac{1}{7} = \frac{3}{7}$ of the full scale value. |

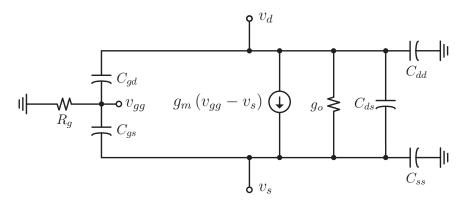

| 5.15 | Small signal model of common-gate amplifier                                                                                  |

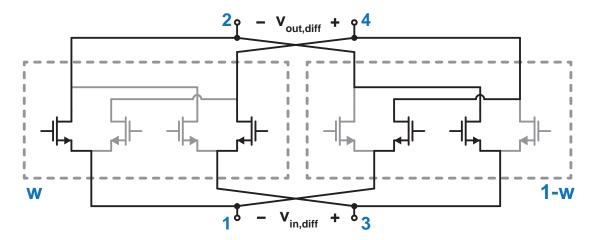

|      | DAC model with continuous current steering. $w$ represents the proportion of DAC                                             |

|      | unit elements steered in the "+1" state, so then $1-w$ represents the proportion                                             |

|      | of DACs in the "-1" state                                                                                                    |

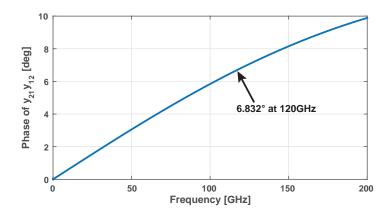

| 5.17 | Phase of $\tilde{y}_{21}\tilde{y}_{12}$                                                                                      |

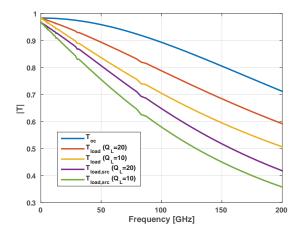

| 5.18 | Magnitude of DAC loop gain under various loading conditions                                                                  |

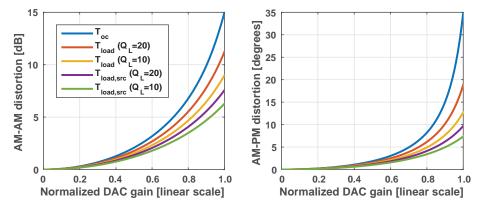

| 5.19 | AM-AM and AM-PM nonlinearity of DAC                                                                                          |

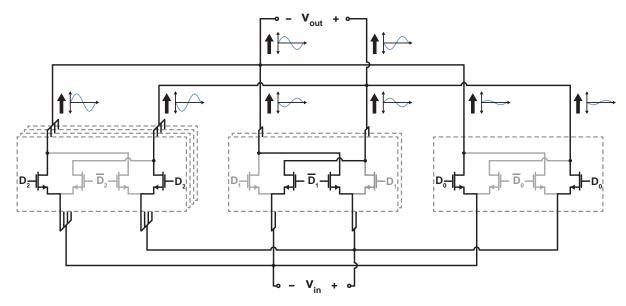

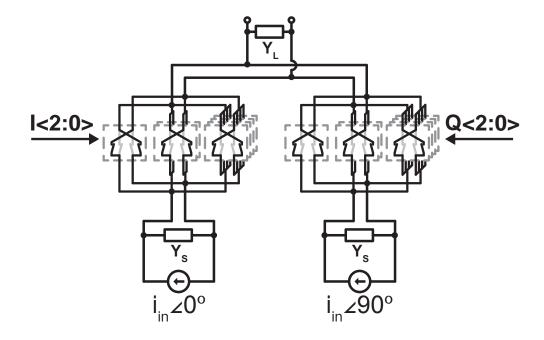

| 5.20 | I and Q DACs with current-combining at output                                                                                |

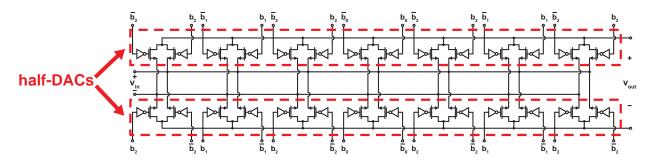

| 5.21 | DAC schematic highlighting "half-DAC" cells                                                                                  |

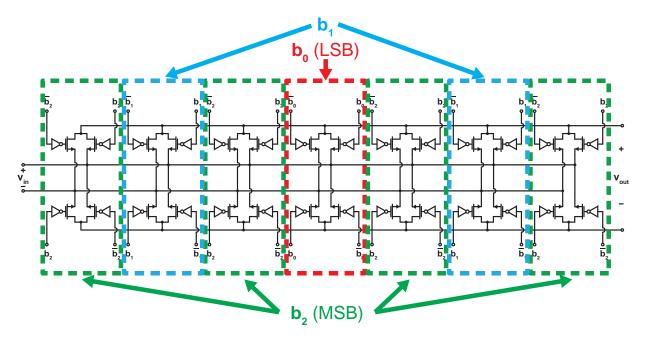

| 5.22 | DAC schematic highlighting segmentation of bits within DAC                                                                   |

| 5.23 | Layout of DAC cell including top level metal routing                                                                         |

| 5.24 |                                                                                                                              |

| 5.25 |                                                                                                                              |

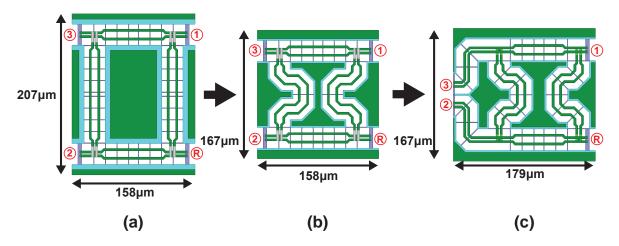

| 5.26 | Design iterations for quadrature hybrid                                                                                      |

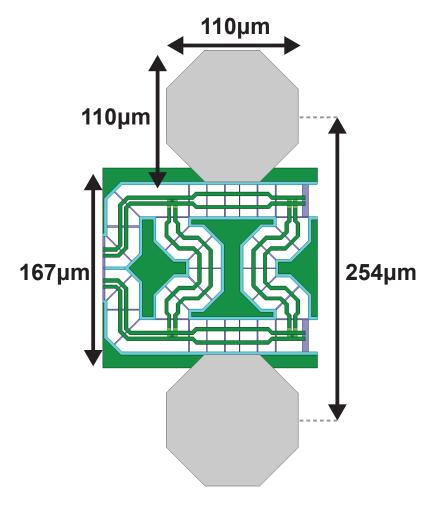

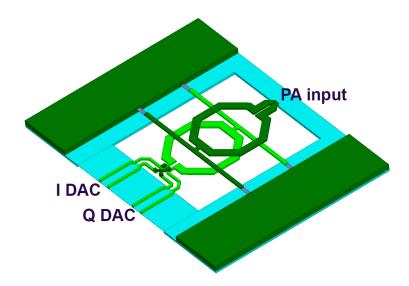

| 5.27 | Quadrature hybrid layout in between flip-chip pads                                                                           |

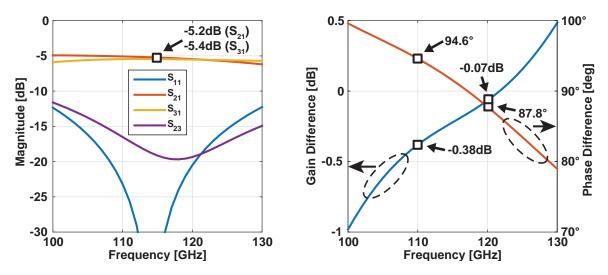

|      | Simulated S-parameters of final quadrature hybrid design                                                                     |

| 5.29 | DAC output transformer / PA input transformer                                                                                |

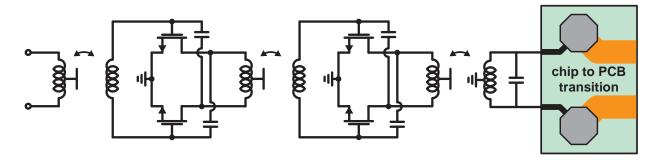

| 5.30 | Power Amplifier Schematic                                                                                                    |

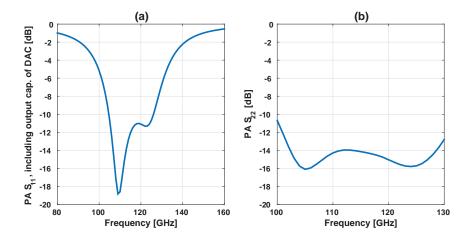

| 5.31 | Simulated PA input and output return losses                                                                                  |

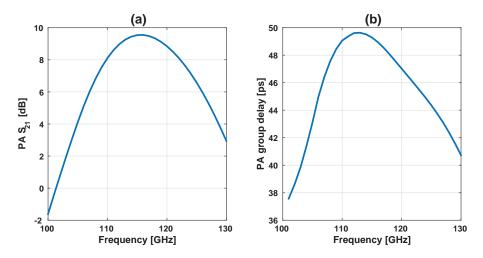

|      | Simulated PA gain and group delay                                                                                            |

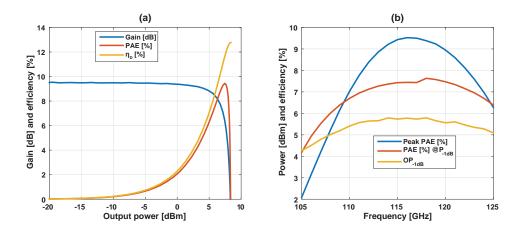

| 5.33 | Simulated PA efficiency and gain compression curves                                                                          |

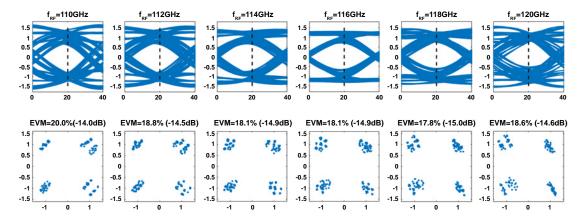

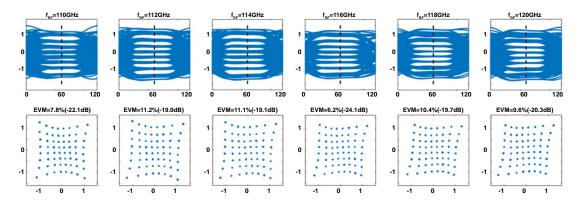

| 5.34 | Static TX constellations from 110GHz to 120GHz                                                                               |

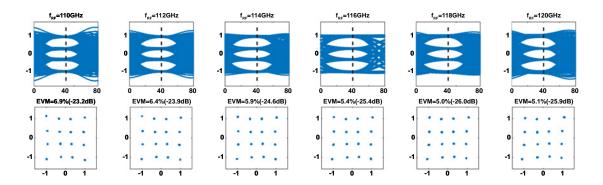

| 5.35 | Simulated QPSK eye diagram and constellations for 40ps symbol period, corre-                                                 |

|      | sponding to 50Gb/s data rate                                                                                                 |

| 5.36 | Simulated 16QAM eye diagram and constellations for 80ps symbol period, corre-                                                |

|      | sponding to 50Gb/s data rate                                                                                                 |

| 5.37 | Simulated 64QAM eye diagram and constellations for 120ps symbol period, cor-                                                 |

|      | responding to 50Gb/s data rate                                                                                               |

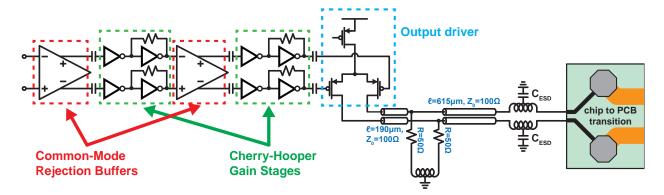

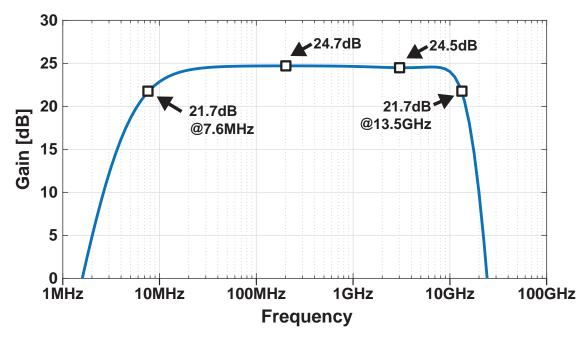

| 5.38 | Baseband amplifiers and output driver                                                                                        |

|      | Voltage gain of baseband amplifier and output driver (including transmission line                                            |

|      | routing)                                                                                                                     |

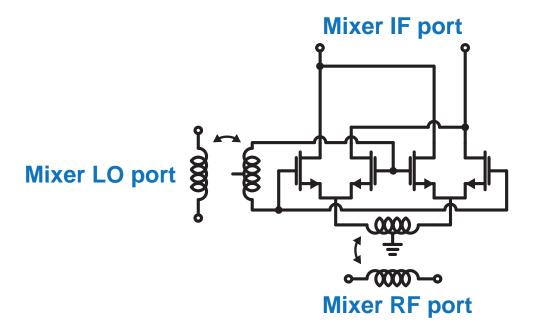

|      | Double balanced active mixer core schematic                                                                                                                          | 76             |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

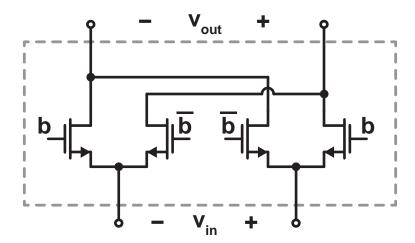

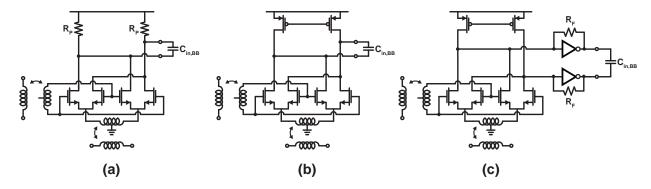

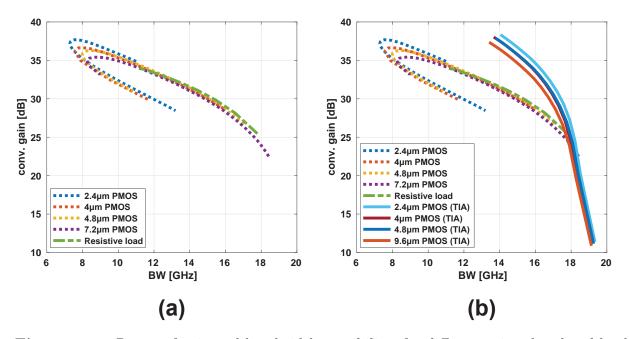

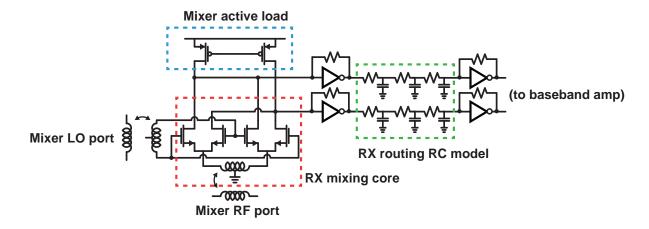

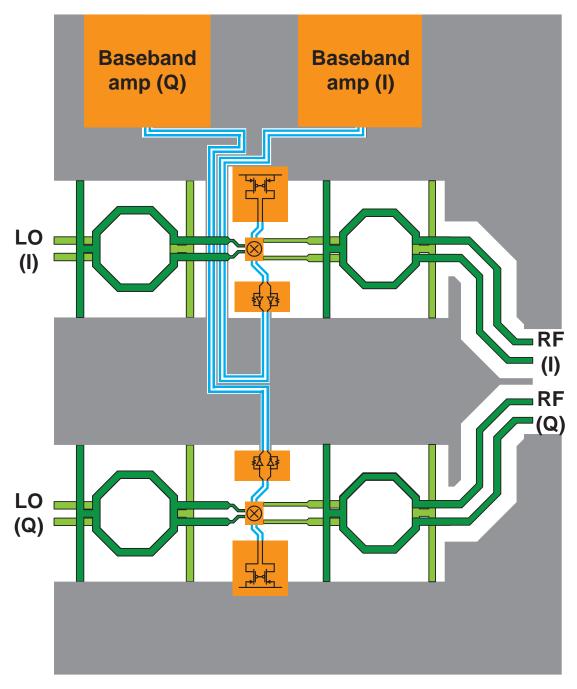

|      | (b), PMOS load with TIA (c)                                                                                                                                          | 77<br>78<br>79 |

|      | Finalized mixer schematic                                                                                                                                            | 80             |

| 5.45 | LNA schematic                                                                                                                                                        | 81             |

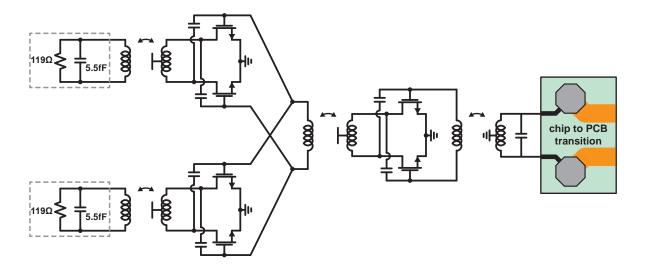

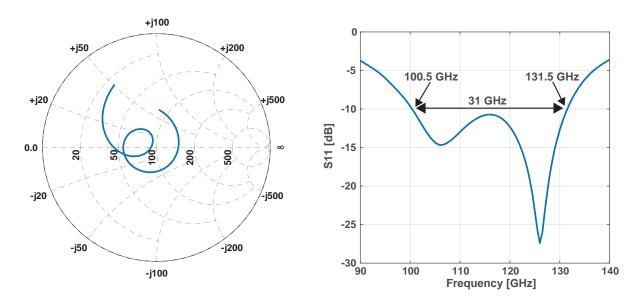

| 5.46 | Simulated LNA input impedance seen from PCB (including chip-to-PCB transition model)                                                                                 | 82             |

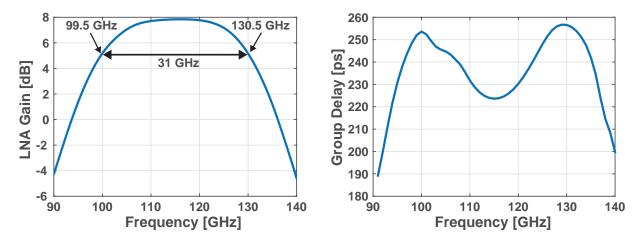

| 5.47 | Simulated LNA Gain and Group Delay (including 3dB loss from I-Q split)                                                                                               | 82             |

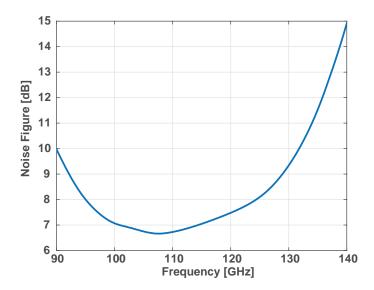

| 5.48 |                                                                                                                                                                      | 83             |

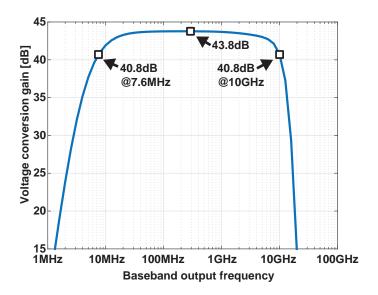

|      | Simulated conversion gain of the full receiver chain, including LNA, mixer, and baseband amplification. The x-axis represents the frequency offset from the          |                |

|      | 115GHz LO signal and the baseband tone frequency that it downconverts to                                                                                             | 84             |

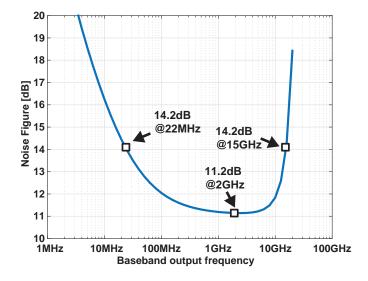

| 5.50 | Simulated double sideband noise figure for the full RX chain with 115GHz LO                                                                                          | 01             |

|      | frequency                                                                                                                                                            | 84             |

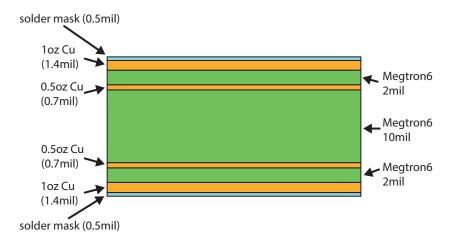

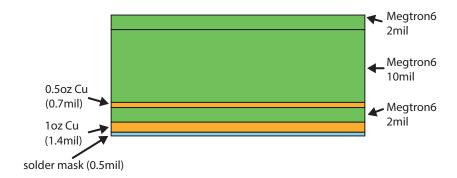

| 5.51 | Selected PCB stackup                                                                                                                                                 | 85             |

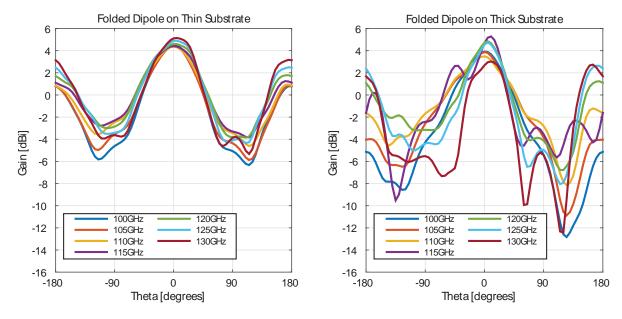

| 5.53 | ·                                                                                                                                                                    | 87             |

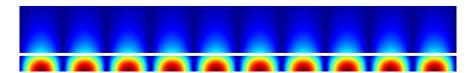

| 5 54 | Dielectric slab which supports $TM_0$ surface waves                                                                                                                  | 88             |

|      | Calculated H field of grounded slab $TM_0$ surface wave mode according to theory.                                                                                    | 00             |

| 3.33 | The horizontal axis is the direction of propagation, and the vertical distance from the bottom of the image. The white horizontal line represents the air-dielectric |                |

|      | interface                                                                                                                                                            | 88             |

| 5.56 | Sievenpiper "mushroom" EBG structure, side view                                                                                                                      | 89             |

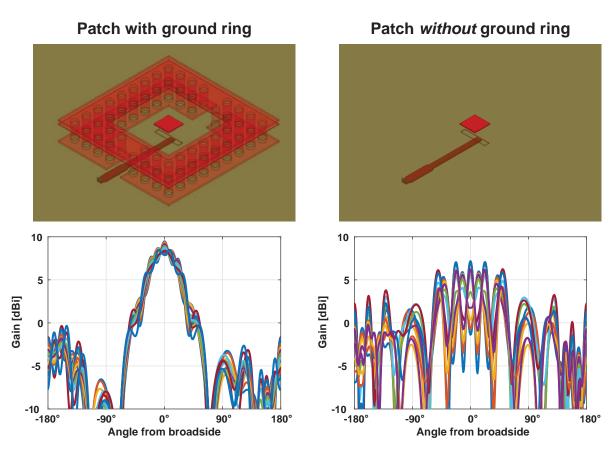

| 5.57 | Patch antenna gain (at 115GHz) with and without guard ring, as the PCB substrate size is varied                                                                      | 90             |

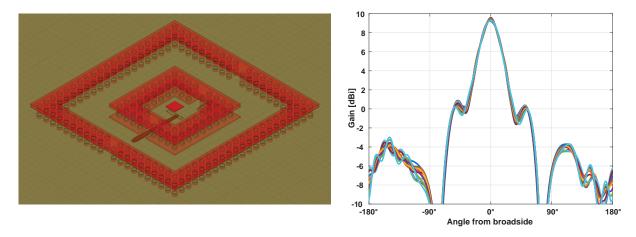

| 5.58 | Antenna gain (at 115GHz) with two guard rings, as PCB substrate size is varied.                                                                                      | 91             |

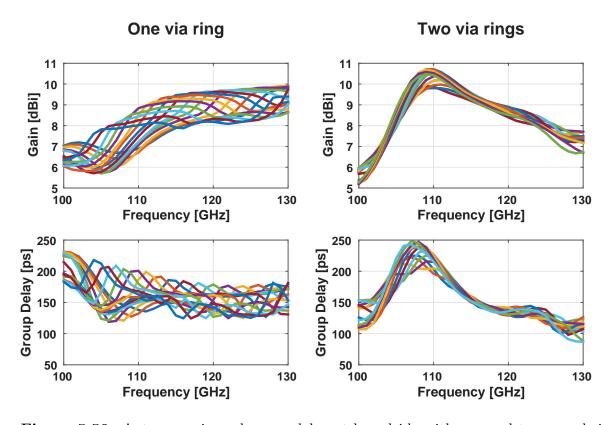

|      | Antenna gain and group delay at broadside with one and two guard rings                                                                                               | 91             |

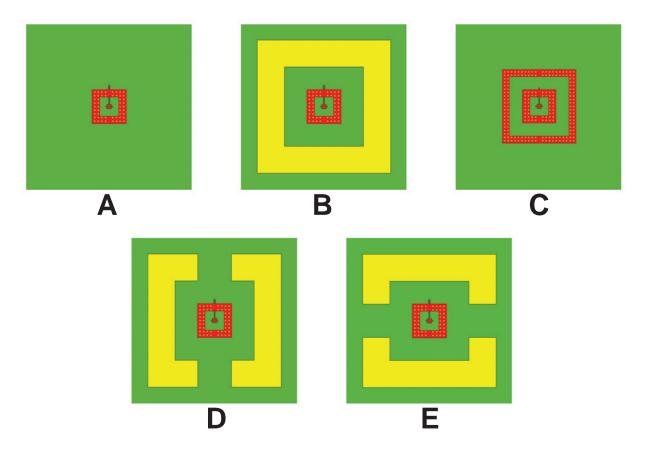

|      | Patch with grounded via ring and partial substrate removal                                                                                                           | 92             |

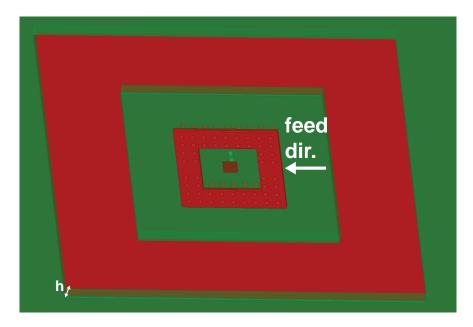

|      | Different surface wave suppression technques. Trench/substrate removal areas are shown in yellow.                                                                    | 93             |

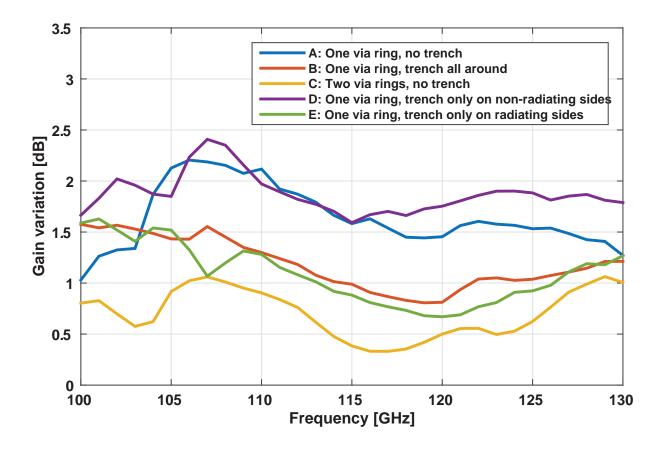

| 5.62 | Worst-case gain variation (minimum to maximum) of various surface wave mitigation techniques, as the (square) substrate size is varied from 12 to 15mm               | 94             |

| F 62 |                                                                                                                                                                      |                |

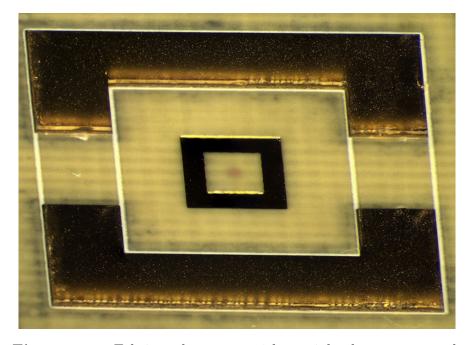

|      | Fabricated antenna with partial substrate removal                                                                                                                    | 95<br>95       |

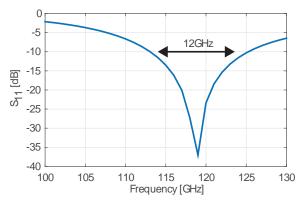

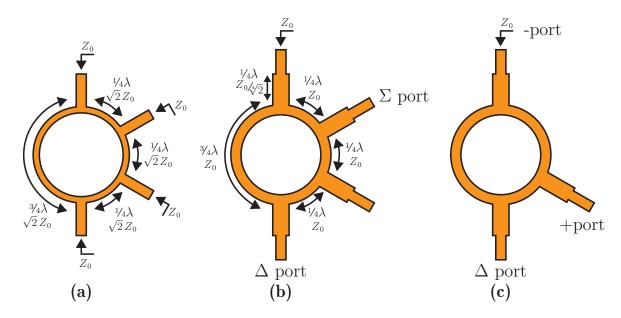

|      | Design process for optimized rat-race hybrid without sum port termination                                                                                            | 95<br>96       |

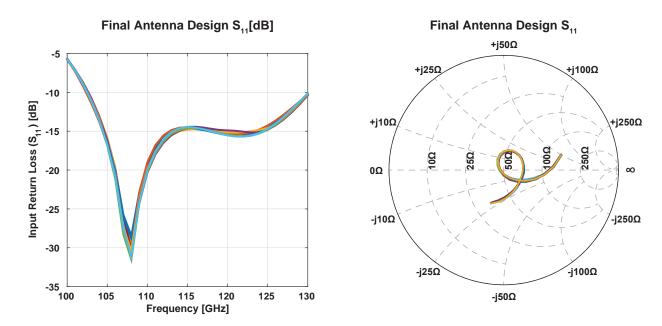

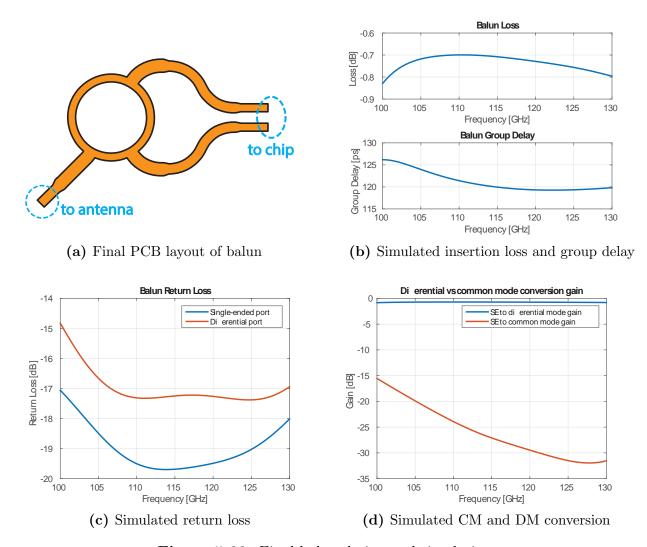

|      | Final balun design and simulations                                                                                                                                   | 90<br>97       |

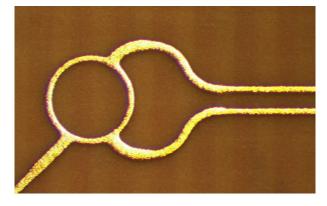

|      | Fabricated rat-race hybrid on PCB                                                                                                                                    | 97             |

|      | Die photo                                                                                                                                                            | 98             |

| 5.00 | _= p                                                                                                                                                                 |                |

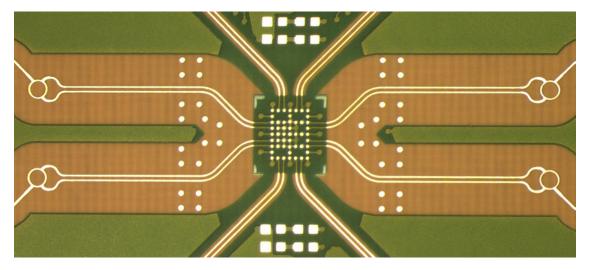

| 5.69 | Flip-chip | footprint, | differe | ential | rout | ting, | and | l mr | n-W | /ave | balı | ıns | as | fal | ori | ca | tec | d | n |     |

|------|-----------|------------|---------|--------|------|-------|-----|------|-----|------|------|-----|----|-----|-----|----|-----|---|---|-----|

|      | PCB       |            |         |        |      |       |     |      |     |      |      |     |    |     |     |    |     |   |   | 99  |

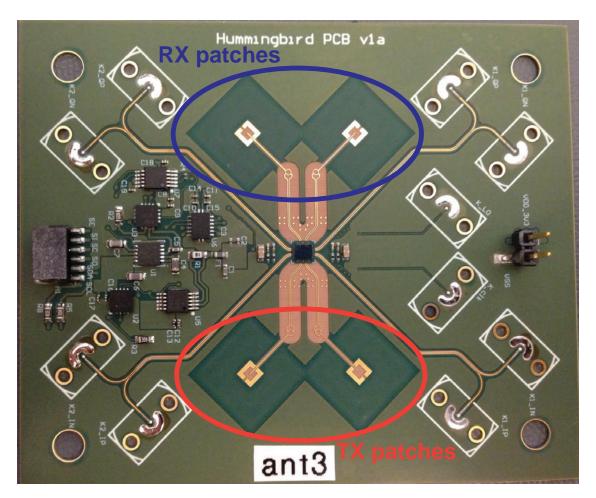

| 5.70 | Antenna l | PCB with   | chip a  | ttach  | ed   |       |     |      |     |      |      |     |    |     |     |    |     |   |   | 100 |

# List of Tables

| 4.1 | Performance Comparison of Published W-Band Phased Array Transceivers | 38  |

|-----|----------------------------------------------------------------------|-----|

| 5.1 | Mapping from DAC bits to amplitude values                            | 53  |

| 5.2 | Characteristics of Various PCB Materials                             | 86  |

| 5.3 | Performance and Energy Efficiency of mm-Wave Wideband Transmitters   | 101 |

| 5.4 | Performance and Energy Efficiency of mm-Wave Wideband Receivers      | 101 |

### Acknowledgments

First and foremost, I cannot thank my advisor Ali Niknejad enough for his technical advice and project guidance. I've had the luxury and flexibility of choosing my projects throughout most of my PhD, and I think few advisors would be willing to do that. It's been fantastic to work for someone who has such a depth of technical expertise. Ali has also been a great advocate for my ambitious system-scale projects, and hopefully they will continue on in the center after I leave. I also want to thank Elad Alon who basically acted as an informal coadvisor during the design of the "Hummingbird" 120GHz chip, and provided many valuable insights.

I had the benefit of having great lecturers for all of the courses I've taken at Berkeley, and thank Ali, Elad, Bernhard Boser, Simone Gambini, Bora Nikolić, Chris Hull, Joseph Orenstein, and Martin White. Extra thanks to Elad, Bora, and Martin for serving on my quals committee and to Elad and Martin as readers for this thesis. Also an extra thanks to Simone, for helping me figure out what I wanted out of grad school over probably the most important beer of my career.

I would like to thank Nokia Research / Nokia Labs for research funding and support on the radar project, specifically Vason Srini and Klaus Doppler. I also appreciated the various technical discussions I had during my internship with Michael Reiha and my fellow co-intern Paul Swirhun. I owe many thanks to Paul for his design efforts on the phased-array radar IC. I also would like to thank the NSF-EARS program for its financial support for me and my research. Thank you to the BWRC member companies and sponsors as well.

I also enjoyed my summer internships at Analog Devices and Google, and learned a lot from them. Thanks to John Cowles, Todd Weigandt, Prabir Saha, Daryl Carbonari, Joel Dobler, Monica Cordrey, and Barrie Gilbert for a really enjoyable summer up in the northwest. And thank you to Ben Mossawir and Will Wesson for mentoring me during my summer at Google.

In my (admittedly biased) opinion, BWRC is probably the best possible place in the universe to do a PhD in integrated circuits. A big part of that is the people. Firstly, I would like to thank all of the BWRC "senior students" who I have bugged over the years with various questions: Amin Arbabian, Jungdong Park, Jiashu Chen, Lingkai Kong, Matt Spencer, Sahar Tabesh, Siva Thyagarajan, Shinwon Kang, Steven Callender, and Jun-Chau Chien. I also really enjoyed all of the technical feedback, discussions, and collaborations with my peers in the Niknejad and Alon groups. In particular, I would like to thank Nathan Narevsky, Greg LaCaille, Luke Calderin, Constantine Sideris, Pramod Murali, Nai-Chung Kuo, and Sashank Krishnamurthy. Costis and Sashank also contributed quite a bit to making the 120GHz transceiver a reality and it would not have been possible without them.

Over the years at BWRC, we have also had great support from the staff, and I would be remiss if I did not thank them profusely for all that they do for the center and its students. At the EE department level, I also really would like to thank Shirley Salanio for her tireless efforts on keeping the entire department of grad students on track, myself included.

I owe a big thanks to my research collaborators at the University of Nice Sophia Antipolis and STMicroelectronics: Cyril Luxey, Aimeric Bisognin, Diane Titz, Fred Gianesello, and Romain Pilard. I also really appreciate Cyril and Diane's hospitality during my visit to Nice for the radar active measurements, during a very difficult week for the city of Nice.

On a personal level, I want to thank my fellow Shattuck house roommates, for a really enjoyable five and a half years. Special thanks to Daniel Gerber, for reminding me how much I love the outdoors and many camping and climbing trips. And thanks to Joe Corea for showing me the importance of having a good hobby or two (or three).

To Allison, thank you so much for your love, support, and understanding throughout the final years of my PhD, even when they took twice as long as I thought they would.

Finally, thank you to my parents for their support and encouragement, and for everything you have done for me that got me to this point. Thank you for cheering me on to the finish line from the other side of the country.

# Chapter 1

# Introduction

Since the introduction of digital wireless communication into the industrial and consumer space, the evolution of wireless technology has been a self-reinforcing cycle, with each new generation of technology generating the demand for the next. Wireless LAN on laptops first paved the way for internet access without being tied to a desktop PC. This was followed by the popularization of smartphones, which provided users wireless connectivity anywhere a cellular connection could be found. In turn, the maturation of smartphone technology has taken place alongside dramatic increases in cellular data capacity. Basic internet connectivity and picture sharing has been joined by video messaging and live streaming, and perhaps in the near future will be joined by augmented or virtual reality.

To enable these developments to take place, wireless technology has had to advance continuously. But satisfying the demand for higher and higher wireless data rates, at some point, will inevitably be constrained by physical limitations. Once that happens, there are really only two ways to improve the situation, according to Shannon's capacity theorem [1]:

$$C = BW \cdot \log_2 \left[ 1 + \frac{S}{N} \right] \tag{1.1}$$

When up against fundamental limits, either the signal-to-noise ratio or the signal bandwidth should be increased. Increasing signal-to-noise ratio allows for the use of more complex modulation schemes, but requires a higher transmit power and/or a lower receiver noise level to achieve. Because of the logarithm in the capacity equation, there are also diminishing returns in increasing the SNR. For high SNR, a further doubling of SNR only leads to a linear increase in channel capacity. At some point, increasing the SNR becomes prohibitive from a DC power consumption point of view, or even simply impossible due to regulatory constraints on transmitted power level or interference from other users.

If that is the case, the only available route forward is to scale bandwidth. This, too, has costs when it comes to the physical implementation of the communication link. Transmitters, receivers, and antennas cannot be made arbitrarily broadband without taking some performance hits (or causing significant headaches for the circuit, antenna, and system design engineer). The performance hit (or the size of the engineer's headache) is not related

Figure 1.1: United States Frequency Allocations Chart, 30–300GHz band.

to the absolute bandwidth required, but in fact the *fractional* bandwidth — the ratio of the bandwidth to the center frequency. It is quite difficult to design a 5 GHz carrier frequency wireless link with 5 GHz of bandwidth, while a link bandwidth of 5 GHz is readily achievable at 60GHz carrier frequency.

Shannon's law does not say anything about the center frequency of the available channel, so any 5 GHz chunk of spectrum is equally usable. But in order to more practically and efficiently take advantage of broad bandwidth channels, we need to operate at higher frequency. This is the motivation behind operating circuits and systems in the so-called "millimeter-Wave" band.

Millimeter-Wave (mm-Wave) refers to radio frequencies with a wavelength of between 1 and 10mm, or equivalently frequencies between 30 and 300GHz (Figure 1.1). Until fairly recently, this spectrum was limited to military and radioastronomy applications. However, in the last 15-20 years, there has been significant development of circuits and systems operating in the mm-Wave band. Initially, 60GHz-band wireless communications were the driving force, culminating in the development of fully integrated transceivers supporting large antenna arrays, supporting up to 7Gb/s of peak data rate [2][3].

More recently, the major application driving mm-Wave development has been automotive radar [4][5][6]. Mm-Wave radar was initially proposed for driver-assist technologies such as adaptive cruise control and lane change warning systems, which both require the high bandwidth available at mm-Wave frequencies for accurate distance resolution. Getting automotive radar systems into the average car required driving the cost down, necessitating a change from the very first modules using gallium-arsenide (GaAs) integrated circuits, to lower-cost silicon solutions. Fully integrated CMOS systems will soon be reaching the market [6], and as interest in fully autonomous vehicles continues to grow, development of this technology will accelerate further.

## 1.1 Motivation

The goal of this thesis is to explore the design tradeoffs and challenges in the design of broadbandwidth millimeter-wave integrated transceivers, with an emphasis on the demonstration of practical, complete systems. In this thesis, two transceiver designs are described, one intended for mm-Wave short-range radar, and another for short-range communication. Due to the complexity of routing signals on and off chip at millimeter-wave, it is also necessary to consider the packaging and antenna design as part of the system design itself. Both transceivers are integrated using flip-chip die attach technology directly onto the printed circuit boards (PCBs) with included antennas.

# Chapter 2

# Millimeter-Wave Background

# 2.1 Technology: Bipolar vs MOSFET

A substantial amount of design work at millimeter-wave has been done using silicon germanium (SiGe) bipolar transistor technologies. These tend to be fairly inexpensive technologies to use, since the critical dimension for high performance is the defined not by lithography but by layer thickness (width of the base region of the bipolar transistor, in a conventional vertical bipolar device). In addition to reduced fabrication mask cost, bipolar transistors also have a better  $\frac{g_m}{I_C}$  than CMOS devices, and the  $g_m$  efficiency is constant versus bias, rather than trading off with  $f_T$  as in CMOS.

Modern bipolar process offerings do almost always include some CMOS transistors as well—this type of process is referred to as SiGe BiCMOS—though the feature size is usually several process nodes behind the cutting edge [7][8]. Because of this, BiCMOS is best suited for analog-heavy applications such as power amplifiers [9], where low-speed digital circuitry may sometimes be included but it is not critical to the performance of the system.

For digitally intensive circuits, CMOS clearly has the advantage. High data-rate digital transmitters have been demonstrated with intensive digital filtering while still maintaining high efficiency [10][11]. This certainly would not be possible using bipolar transistor logic, although it could perhaps be matched in performance with some efficiency cost using a sufficiently finely scaled BiCMOS technology. Since SiGe BiCMOS scaling has not caught up with pure CMOS scaling, it is not able to efficiently provide the high performance digital functionality necessary to the operation of a complex mm-Wave system. CMOS is the de facto technology of choice for any millimeter-wave SoC intended for mass-market production [6].

As CMOS technology scales further into the FinFET regime, more challenges are introduced: thinner and more resistive routing layers, higher parasitic capacitances due to non-planar device geometry, and stringent metal fill requirements. Initial investigations published in the literature suggest that these challenges can be overcome, and millimeter wave CMOS can still achieve high performance even scaled below 28nm [12]. Once FinFET

processes become more widely available and the design challenges better understood, it is possible that performance can be improved even further — the  $f_T$  of FinFET devices in subthreshold operation may be sufficient to achieve high gain at millimeter wave, which translates to an efficiency boost due to improved  $\frac{g_m}{I_D}$ .

### 2.2 LO Generation and Distribution

One of the most challenging aspects of generating an LO signal at millimeter-wave is designing a high-performance oscillator with wide tuning range. The poor analog varactor Q at high frequency degrades oscillator phase noise [13][14]. Therefore, it is advantageous to generate the LO frequency at a lower frequency, and use a nonlinear frequency multiplier to scale it up by the desired amount.

In a multi-channel transceiver, where the LO signal is shared across multiple channels, a transmission-line-based routing network is usually required to keep impedances well-matched over long distances. This can also be a source of high power consumption, since large LO buffers are required to drive the fairly low transmission line impedances that can be realized on chip (which typically do not exceed  $100\Omega$ ) without incurring high losses.

## 2.3 Modulation Techniques

## 2.3.1 Modulation Techniques for Radar

Of the various modulation schemes used for radar, all have the same main idea in common. A signal is transmitted with a known time-varying modulation, which reflects off of various scatterers in the environment, and some small amount of energy is reflected back to the receiver. Because the received signal is simply a time-delayed and attenuated version of the transmitted signal, it can be compared with the known transmitted waveform to determine the time delay. From the time delay, the round-trip distance is trivial to compute:  $d = \frac{c}{t_d}$ .

Also, because the transmitted signal and the received signal are both derived from the same clock, their phase noise will largely cancel out. When the offset frequency of the phase noise is equal to  $\frac{1}{T_{roundtrip}}$ , the phase noise will add coherently, and increase the noise floor of the receiver. This is not as much of an issue for targets that are far away — the signal will be heavily attenuated. The greatest concern is with high amplitude signals from nearby targets. As these signals (often referred to as "clutter") also tend to degrade the linearity of the receiver, it is obviously desirable to avoid them.

In practice, the transmitted signal tends to be periodic, which potentially introduces some ambiguity. If the period of the transmitted signal is T, then a given receive waveform could correspond to a round-trip time delay of  $\tau, \tau + T, \tau + 2T, \ldots$  For millimeter-Wave radar, this tends to not be an issue because the high signal attenuation tends to push the reflected signals from longer distances below the noise floor of the receiver.

A critical parameter for the performance of a radar system is the bandwidth of the modulated signal. In most types of radar system, the distance resolution is inversely proportional to the bandwidth of the radar signal: a signal with larger bandwidth can better resolve two close-together targets [15]. This tradeoff is broadly applicable, since time (and therefore also distance, because of the constancy of the speed of light) and frequency are related by the Fourier transform — a signal that is confined to a small region in time is necessarily broad in frequency space.

#### 2.3.1.1 Pulse-Based Radar

Pulse-based radar is straightforward to understand: a short pulse is transmitted, the pulse reflects off of various objects in the environment, and a series of pulses is received corresponding to reflections from objects at different distances. The narrower the pulse, the more accurately closely spaced objects can be resolved. One nice feature is that the pulse need not be detected coherently, since the information is contained only in the amplitude of the signal. This approach is commonly used at optical frequencies in LiDAR (typically referred to as "time of flight" imaging) [16]. It has also been demonstrated in mm-Wave integrated circuit form, with significant design effort required to ensure sufficiently narrow pulses [17].

#### 2.3.1.2 Continuous Wave Radar

In contrast with pulse-based radar, continuous wave radar is always transmitting a signal. This presents significant challenges for the receiver, as it must either be carefully isolated from the transmitter to avoid saturation at its output, or it must somehow tolerate the large transmitter signal without compromising linearity and noise figure.

Continuous wave radar has no amplitude modulation, so in order to be able to measure range, phase or frequency modulation must be added. Phase modulated continuous wave radar (PMCW radar) is attractive in that it can be implemented in an extremely simple and efficient manner, and orthogonal pseudo-random sequences can be used at different times to reduce the probability of inter-user interfence from multiple radar systems operating in close proximity [18]. The bandwidth in a PMCW system is set by the sample rate at which the phase is modulated. Unfortunately, this also requires the same high bandwidth in the receiver baseband amplification chain [18], which can become very challenging in high bandwidth / high resolution applications.

Frequency modulation, on the other hand, requires low baseband bandwidth [19][6], and low instantaneous transceiver bandwidth. In a frequency modulated continuous wave radar (FMCW radar) system, high resolution still requires high bandwidth, but the bandwidth does not come from fast frequency steps. Instead, high bandwidth is achieved using a slow, smooth frequency ramp over multiple GHz. By removing the need for an instaneously wideband signal, FMCW radar relaxes the specifications on the circuit design. This leads to a more efficient overall implementation.

#### 2.3.1.3 Advantages of Linear FMCW Radar for Millimeter-Wave

One specific type of FMCW waveform has some very desirable properties: linear FMCW. If the transmitted signal increases linearly in frequency, it can simply be mixed with the received reflected signal to yield an IF tone whose frequency is proportional to round-trip time delay [19]. Linear frequency modulated continuous wave (FMCW) radar is an attractive radar modulation scheme for energy-efficient mm-wave applications for a few main reasons: constant-envelope and simplicity.

Firstly, because FMCW is a constant-envelope modulation scheme, transmitter linearity is not a concern. This allows for use of linear power amplifiers close to saturation, or even nonlinear switching power amplifiers, either of which will improve the overall transmitter efficiency. Also, because the modulated LO signal is constant-envelope, it can be generated at a low frequency and scaled up to a higher frequency using a nonlinear frequency multipler, without negative impacts from the nonlinearity of the multiplier.

In a phased-array system, the modulated LO signal can be generated centrally, scaled in frequency, and routed out to all elements. As the LO routing network likely needed to be there anyway, there is no penalty for doing this.

Secondly, because the modulation is simple and shared across all elements, the frequency modulation can be incorporated into the PLL that is likely present in the system anyway. For a pulsed radar system, a high-bandwidth modulation requires fast on/off times to achieve a short pulse width [17], which means the circuit creating the modulation needs to be carefully designed to support that bandwidth. In a FMCW radar system, although large overall bandwidth is needed in the RF transmit and receive chains (as in the pulsed radar case), a large *instantaneous* bandwidth is not necessarily needed, since it is the overall bandwidth of the sweep itself that determines the resolution. So, a slowly modulated signal can be used, as long as the frequency of the signal varies across the full bandwidth over time. Multiple targets at different distances correspond to multiple tones, and can be easily distinguished by applying a Fourier transform to the received IF data.

## 2.3.2 Modulation Techniques for Digital Communication

The most basic modulation technique, and perhaps the first modulation technique to ever be used [20], is on-off keying. This simply consists of turning on and off the RF signal in time:

$$v(t) = A(t)\cos(\omega t) \tag{2.1}$$

Where:

$$A(t) = \sum_{n=-\infty}^{\infty} [u(t - nT) - u(t - (n+1)T)] a[n]$$

$$a[n] \in \{0, 1\}$$

and u(t) is the unit step function, which is used to mathematically model the zero-order hold interpolation of the discrete-time digital data sequence a[n].

Note that this inherently assumes that the digital data is sampled at a regular interval T. Since this waveform transmits one new bit of information every T seconds, we can say that the data rate is 1/T bits/second.

#### 2.3.2.1 Amplitude Modulation

To improve the data rate, instead of transmitting only a one or a zero, more signal levels can be used to convey more information per bit period. For example, if there are four possible signal levels instead of two,  $\log_2(4) = 2$  bits can be transmitted every T seconds. In this case, a[n] can take a broader range of values. If k bits per period are desired:

$$a[n] \in \left\{0, \frac{1}{2^k - 1}, \frac{2}{2^k - 1}, \dots, \frac{2^k - 2}{2^k - 1}, 1\right\}$$

(2.2)

Without even doing any math, it's obvious that there is a tradeoff for doing this: Shannon's equation (Equation 1.1) says that if the channel bandwidth is the same (which it approximately is, if T is held constant), then the signal to noise ratio needs to increase in order to provide increased capacity. So, in order to actually acheive the increase in data rate, we can deduce that the SNR has to increase proportionally.

#### 2.3.2.2 Phase Modulation

Other than by changing the amplitude of a sinusoid, the only other way to send data is by modulating the phase or frequency of the wave. In an analog communication system, these are essentially the same thing: since frequency is the derivative of phase, in a continuous-time system it makes little difference for modulation and demodulation if the signal of interest is the phase or its derivative. For a sampled, digital communication system, there is in fact a meaningful distinction, because the phase and frequency now have to change in discretized steps rather than smoothly.

Although it has been demonstrated at mm-Wave [21], digital frequency modulation suffers from poor bandwidth efficiency [22] and would be extremely challenging to implement in a broadband, coherent link. Because of this, mm-Wave transceivers generally have used almost exclusively phase modulation rather than frequency modulation.

The simplest version of phase modulation is binary phase shift keying (BPSK). Mathematically, this takes the form of a sinusoid that alternates between inverted and non-inverted phase.

$$v(t) = \cos(\omega t + \phi(t)) \tag{2.3}$$

Where:

$$\phi(t) = \sum_{n = -\infty}^{\infty} [u(t - nT) - u(t - (n+1)T)] \phi[n]$$

$$\phi[n] \in \{0, \pi\}$$

The concept can be extended to k bits per symbol by increasing the number of possible values that  $\phi[n]$  can take:

$$\phi[n] \in \left\{0, \frac{2\pi}{2^k}, 2 \cdot \frac{2\pi}{2^k}, \dots, (2^k - 1) \cdot \frac{2\pi}{2^k}\right\}$$

This technique has the advantage of being constant envelope, which (as discussed in Section 2.3.1.3) eases some implementation challenges arising from nonlinearity of the transmitter. Similarly to the amplitude modulation case, there is a tradeoff between SNR requirement and bandwidth efficiency of the modulation scheme.

#### 2.3.2.3 Quadrature Amplitude Modulation

By applying both phase and amplitude modulation, arbitrary linear combinations of sine and cosine can be transmitted. One of the most useful implementations of that idea is known as quadrature amplitude modulation (QAM). In this modulation scheme, both sine and cosine are scaled independently by signed amplitude values.

Typically the case of interest is when sine and cosine share the same set of possible amplitude values, that the amplitude levels are evenly spaced, and there are a power of two levels in total (Equation 2.4, where k is the bits per symbol):

$$v(t) = I(t)\cos(\omega t) + Q(t)\sin(\omega t) \tag{2.4}$$

Where:

$$I(t) = \sum_{n=-\infty}^{\infty} [u(t - nT) - u(t - (n+1)T)] a_I[n]$$

$$Q(t) = \sum_{n = -\infty}^{\infty} [u(t - nT) - u(t - (n+1)T)] a_Q[n]$$

$$a_I[n], a_Q[n] \in \left\{-1, -\frac{2^{k/2}-3}{2^{k/2}-1}, -\frac{2^{k/2}-5}{2^{k/2}-1}, \dots, -\frac{1}{2^{k/2}-1}, \frac{1}{2^{k/2}-1}, \dots, \frac{2^{k/2}-5}{2^{k/2}-1}, \frac{2^{k/2}-3}{2^{k/2}-1}, 1\right\}$$

In a completely linear system, it can be shown that for the same data rate, power level, and bandwidth efficiency, QAM can provide the same bit error rate at lower SNR than the equivalent PSK modulation [22]. On the other hand, if the transmitter has strong nonlinearity, the variable amplitude levels of the QAM signal will be distorted. This lowers the effective SNR at the receiver.

Due to the complexity in implementing PSK vs QAM at mm-Wave frequencies, QAM is used far more frequently. One exception is 4-QAM, which is also equivalent to 4-PSK (otherwise known as quadrature phase shift keying - QPSK).

# 2.4 Phased Array Techniques

The main challenge in any mm-Wave system design is meeting link budget requirements, in light of the large free space path loss at high frequencies. One way of efficiently addressing the link budget problem is by leveraging phased-array techniques to reduce the total transceiver DC power [23]. For an N-element phased array, transmitter EIRP is increased by a factor of  $N^2$ , since electric and magnetic fields, not power, are summed, and power density is proportional to  $\vec{E} \times \vec{H}$ . Due to reciprocity, for the receiver array there will also be a benefit of  $N^2$  in conversion gain.

Receiver SNR will increase as well, but only proportional to N: since the noise in each receiver element is uncorrelated<sup>1</sup>, the total noise at the output will increase proportional to N, resulting in an SNR increase of  $N^2/N = N$ . Because these system-level performance metrics are improved in a phased-array compared to the single-element case, it is possible to reduce performance (and correspondingly, DC power) while still meeting system requirements derived from the link budget.

Consider an RF power amplifier output stage, designed to operate close to saturation, and optimized to drive a load impedance of  $Z_0$ . If the device sizes in the power amplifier are reduced by half, the power amplifier should be able to achieve the same efficiency at saturation while driving a load impedance of  $2Z_0$ , and delivering half of the power to that load. This scaled-down power amplifier can be used along with a matching network with an impedance transformation ratio of 2 (or if a matching network is already present, modifying its impedance transformation ratio) to drive the original load impedance of  $Z_0$ , while delivering half of the power at the same efficiency. With a real matching network, there will be some additional losses, so the efficiency and output power will in practice be degraded somewhat. In a phased-array system, this strategy can be used to reduce DC power and per-element performance without sacrificing efficiency.

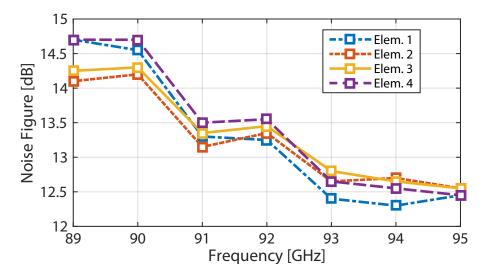

A similar scaling approach can be used on the receiver side. Consider an LNA designed for power and noise matching to an impedance  $Z_0$ . Because the current density for minimum noise figure is largely invariant of emitter length [25] (or similarly, transistor width in CMOS technologies), the LNA device sizes can be reduced by half, resulting in an LNA with the same  $NF_{min}$  matched to an impedance of  $2Z_0$ . As in the transmitter case, a matching network can be used to match the LNA back to the original  $Z_0$  input impedance. The new LNA has half of the DC power consumption, and slightly higher noise figure due to the added matching network losses. Of course, due to matching network complexity, added losses, and the bandwidth narrowing effect of high-Q matching networks, it is not possible to continue this scaling arbitrarily. Architecture or circuit topology changes must then be used to reduce power consumption further.

<sup>&</sup>lt;sup>1</sup>In general, correlated noise across receiver elements will mitigate some of this SNR improvement (refer to [24] for a more detailed discussion). However, if the receiver elements are well isolated, and the noise of the combiner is small relative to the noise from the individual receivers, the factor of N scaling will hold.

# Chapter 3

# FMCW Radar Phased-Array Transceiver Design

Highly integrated millimeter-wave transceivers, enabled by advances in CMOS and SiGe BiCMOS process technology over the last decade, have found what is seemingly a perfect niche in automotive radar. With many GHz of absolute bandwidth available, and a compact antenna size due to the small wavelength at mm-wave, the W band matches up well with the requirements for adaptive cruise control and similar technologies [26]. The development of mature, low-cost SiGe and CMOS technologies with  $f_t$  and  $f_{max}$  of 150GHz and beyond has brought down the cost of such driver-assist technology and with it, widespread adoption.

More recently, mm-wave radar has also received increasing attention for short-range applications such as gesture recognition, occupancy detection, and remote heart-rate monitoring [27][28][29][30][31]. However, existing mm-wave radar solutions intended for automotive use are power-hungry and often bulky. These drawbacks pose a problem for mobile, power-constrained applications. Towards this goal, in this work, a compact antenna-in-package FMCW radar phased array solution at 94GHz with record-low per-element power consumption is proposed and demonstrated.

Although some promising progress has been made on gesture recognition radar at 60GHz[30], the higher frequency at 94GHz allows the possibility for larger sweep bandwidths (which improves depth resolution of the radar) and smaller antenna sizes. However, the higher frequency also presents a challenge from the circuit design point of view, which has a negative impact on efficiency and achievable SNR.

# 3.1 Proposed System Architecture

Several works have demonstrated state-of-the-art synthesizers with integrated frequency modulation using a digital-PLL-based architecture [19][32][33][34]. The focus of this work is on energy-efficient array implementation and FMCW radar demonstration, so an external synthesizer is used to generate the frequency-modulated LO waveform. The chip includes

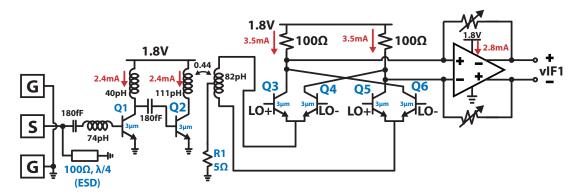

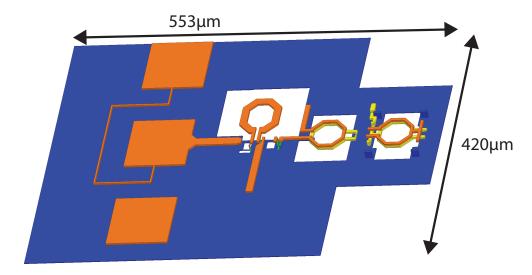

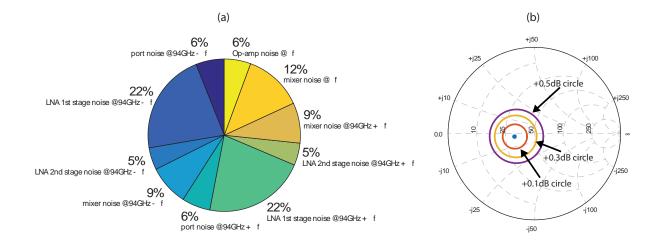

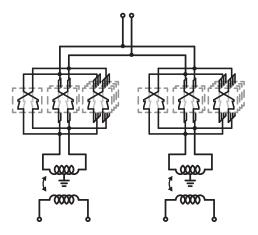

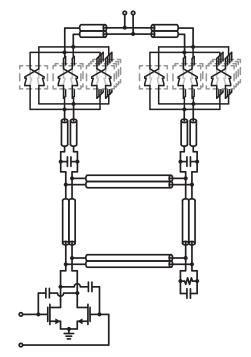

**Figure 3.1:** Complete phased-array transceiver block diagram. mm-wave IOs use a single-ended, ground-signal-ground (GSG) pad configuration. Ground pads are shared between adjacent phased-array elements to reduce die area.

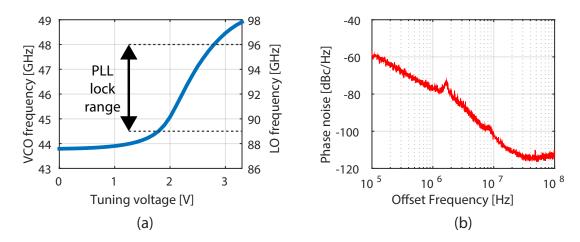

a 47GHz VCO and 32× frequency divider, and the PLL feedback is completed externally using a discrete off-the-shelf IC with a phase-frequency detector (PFD) and charge pump, along with an on-board active loop filter. Most of the power consumption of the PLL is likely to come from the high-speed dividers, so if the PLL were fully integrated, the added power consumption would be fairly small and have little impact on the per-element power.

Because it is critical to minimize TX-RX leakage for an FMCW radar, an architecture with separate TX and RX antennas was selected. Although it is possible to use an integrated isolating coupler to acheive some degree of isolation [35][36], even an ideal coupler will have 3dB insertion loss due to the power-splitting nature of the coupler.

The block diagram of the full 4-TX, 4-RX phased array transceiver is shown in Figure 3.1. To simplify routing in the antenna-in-package module, a small 4-element array size was selected, for both the transmit and receive arrays. LO generation circuitry is shared between the transmit and receive elements, and consists of a VCO, frequency multiplier, and integrated frequency dividers. A PLL was implemented off-chip for LO tuning and to enable FMCW ramp generation. A single, combined differential receiver output is fed off-chip.

For phase shifting, LO path phase shifters are used [37]. LO path phase shifting is attractive here because it removes phase shifter degradations such as nonlinearity and noise from the signal path. This increases efficiency because amplifiers on the LO path can be designed to operate close to compression, as the LO signal is constant envelope. Baseband phase shifting is also attractive from a power consumption perspective, but requires two mixers for complex downconversion. This is not necessary for a linear FMCW system; since the TX and RX frequencies are always slightly offset, the mixer strictly speaking is not truly

operating as a direct conversion mixer, and therefore power can be saved by only using a single mixer.

### 3.2 Transmitter

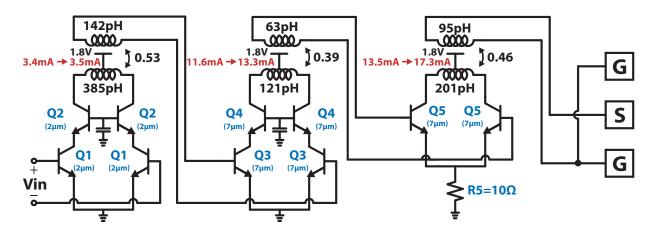

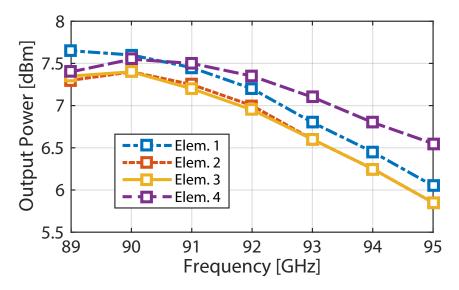

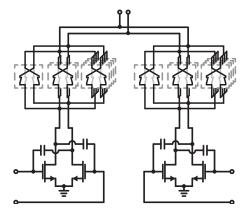

To meet link budget requirements, a power amplifier was designed to provide approximately +9dBm of output power to a single-ended  $50\Omega$  antenna port. A single-ended antenna interface was selected to minimize mm-Wave IO count, which keeps the die area small and relaxes routing constraints within the antenna module.

The main PA gain stage is based on a cascode amplifier. Because of the high output impedance of the cascode, it is hard to achieve a good power-added efficiency (PAE) using a cascode output stage – the load-line impedance is significantly different from the small-signal impedance. However, the per-stage gain is still quite high relative to a simple common emitter amplifier, which has high PAE, but low gain when driven close to saturation. The amplifier core uses a differential topology to reduce sensitivity to modeling errors associated with the impedance seen at the cascode node. The bases of the cascode devices in a differential pair can be shorted directly together using local routing only, and therefore present a virtual short circuit in differential mode. In common mode, gain is not a concern, so low-Q bypass capacitors are used to prevent any common-mode stability problems associated with the impedance at the base of the cascode device.

To get both high gain and moderate efficiency, two cascode driver stages are used to drive a common-source output stage (see Fig. 5.30). A minimum supply voltage of 1.8V is needed to get good cacsode performance, but is slightly above the open-base  $V_{CE}$  breakdown voltage

Figure 3.2: Three-stage power amplifier schematic.  $R_5$  is chosen to result in an emitter voltage of about 100mV under small-signal bias conditions. The annotated DC currents correspond to the operating points in small-signal (left of arrow) and saturated large-signal (right of arrow) conditions.

of a single device. For the non-cascoded output stage, a moderate impedance is provided to the base via the bias network to extend the  $V_{CE}$  breakdown range beyond the open-base limit of  $BV_{CEO}$  and allow operation from a single 1.8V PA supply [38]. For additional robustness to  $V_{CE}$  breakdown with the 1.8V supply voltage, a small series emitter degeneration resistor is added at the tail. This helps improve reliability issues and has no impact on gain since it appears only in common-mode.

It is difficult to power match at the output of the cascode due to the high real part of the output impedance, on the order of  $1k\Omega$ . Additionally, the real part of the input impedance of the cascode amplifiers is fairly small (tens of ohms), leading to a large required transformation ratio. The available area for matching networks is constrained due to the phased-array element pitch and the internal power-supply flip-chip bumps in between the phased-array lanes, making it impossible to fit a transmission-line based matching network into the small area available for the PA. So, for a moderate impedance transformation ratio given the area constraints, coupling between PA gain stages is best achieved using 2:1 transformers with moderate to low coupling factors.

Because of the low coupling factor, the effective turns ratio is slightly less than 2:1 in practice, reducing the impedance transformation ratio. However, the leakage inductance of the transformer primary can be used to increase the impedance transformation ratio of the transformer, by treating it as an additional inductance in series with the transformer, which acts to increase the impedance seen at the ports of the primary transformer. The output stage does not use neutralization because of the extra capacitive load it would present to the output balun, which is also a 2:1 transformer. The output balun also provides ESD protection to the signal pad, as at low frequencies it provides a low impedance path to ground for the signal pads through the center tap of the secondary.

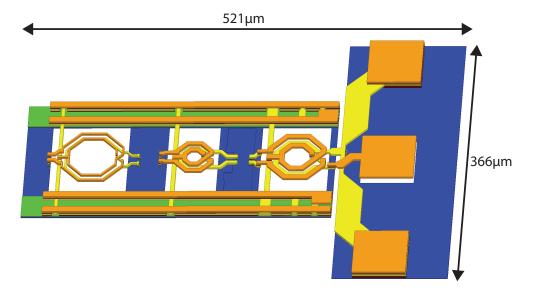

Figure 3.3: Full 3D EM model of PA interstage and output transformers.

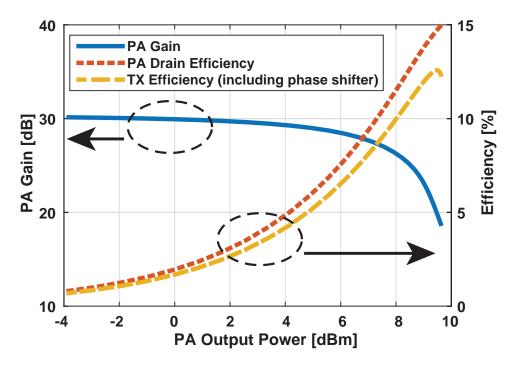

**Figure 3.4:** Simulated PA power gain and power-added efficiency at 94GHz, plotted versus output power.

A 3D HFSS model of the full PA, including the output GSG pads and the three stages of transformers, is shown in Figure 3.3. The individual transformers were first designed separately using HFSS. As a final verification, all three transformers were simulated together along with the output pads. When incorporated back into circuit-level simulations, this PA-scale EM model predicted nearly identical performance when compared to the simulations using separately modeled transformers.

At the intended carrier frequency of 94GHz, simulations show a small-signal power gain of 31dB, and a peak PAE of 15% at an output power of 9.6dBm (Fig. 3.4). If the DC power of the phase shifter driving the PA is included in the efficiency calculation, the PAE of the full chain drops to 12%. Because of the high small-signal gain of the cascode amplifiers, the gain starts to compress well before the output stage is fully saturated. As a result, the peak PAE is reached well beyond the  $P_{-1dB}$  of the amplifier.

Large-signal simulations show that the saturated output power and efficiency are relatively flat across frequency (Fig.3.5) with  $P_{sat}$  above 10dBm from 85GHz to 98GHz, and the peak PAE of the PA is nearly a constant 15% from 85GHz to 95GHz. The peak small-signal gain is 30.8dB at 93GHz, and the small-signal 3dB bandwidth is 12GHz (from 86GHz to 98GHz).

**Figure 3.5:** Simulated PA saturated output power, power gain, and peak power-added efficiency vs. frequency.

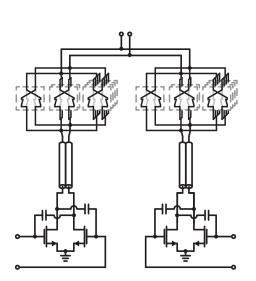

## 3.3 Phase Shifter

Passive reflection type phase shifters are an attractive option for low-power design, as they do not consume any DC power and multiple stages can be cascaded to achieve the desired phase-steering range [39][40]. However, this also implies the insertion loss trades off with phase shift range. To overcome this loss, an additional amplifier stage is needed, which consumes DC power.

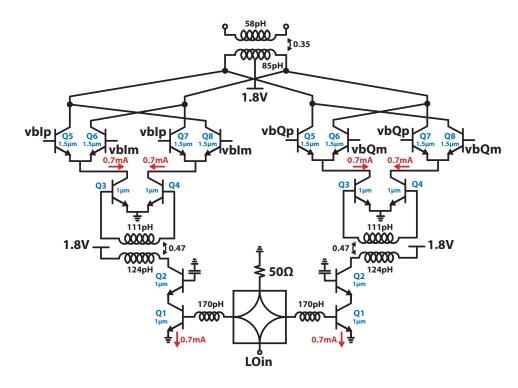

Instead, in this design, a Cartesian architecture is used to ensure a full 360 degrees of phase shift. Weighted combinations of the I and Q LO waveforms are current-combined at the phase shifter output, meaning that the phase should be the same regardless of process variations (provided the input quadrature matching is sufficiently accurate). The VGA functionality is achieved by current-steering using the cascode devices (Q5 through Q8) rather than the  $g_m$  devices of the Gilbert cell. This ensures a more constant input impedance vs code. As the hybrid is single-ended, not differential, a balun stage is needed to drive the phase shifter LO inputs. A single-ended cascode amplifier with transformer load provides single-ended to differential conversion, and further isolates the hybrid from any variations in phase-shifter input impedance.

#### 3.3.0.1 Quadrature Coupler

The quadrature coupler is designed based on the approach in [41] to provide good phase accuracy over a broad bandwidth. It consists of three high-impedance transmission lines

Figure 3.6: Phase shifter schematic.

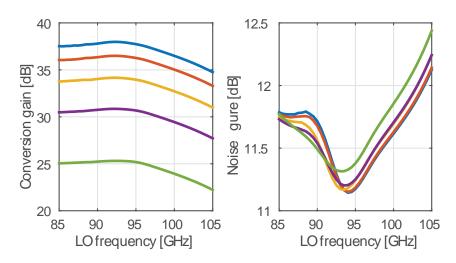

connected in parallel at each end with MIM capacitors. The complete structure, including MIM capacitors, was EM simulated to verify the final design. Simulations show a quadrature phase accuracy within 5 degrees of 90 degrees from 87 to 105 GHz. The amplitude imbalance is within  $\pm$ 1dB from 85 to 102GHz.

#### 3.3.0.2 Phase Interpolator Simulated Results

The phase shifter and transmitter power amplifier were simulated together to characterize the effects of gain compression on the phase shifter resolution. The phase shifter control voltages are driven by differential voltages on the I and Q input terminals. Each I and Q voltage is controlled by a 4-bit DAC, so there are 256 possible codes that can be used in the phase shifter. In practice, only the largest amplitude codes will be used. The constellation of available gain and phase combinations at the PA output is shown in Figure 3.9a. Gain and phase errors are then computed for each possible desired phase angle. The worst-case phase error is about 4.5°, and the worst-case amplitude error 0.55dB, which both occur when both the differential I and Q voltages are at their largest (45° phase shift). This is because at the highest/lowest DAC codes, the the differential pairs (Q5-Q8 in Figure 3.6) are no longer in the linear range.

Figure 3.7: Quadrature hybrid HFSS model. The dimensions of the simulated region are  $197\mu m$  by  $124\mu m$ .

Figure 3.8: Quadrature hybrid simulated IQ mismatch.

## 3.4 LO Distribution

The LO generation circuitry includes an integrated VCO, frequency multiplier, frequency dividers, and LO buffers. The integrated VCO is designed to operate at half of the RF frequency, and is buffered and sent to a frequency doubler to generate the RF carrier waveform. The frequency-doubled LO waveform is buffered and distributed to the phased-array elements.

There is a routing penalty in distributing the LO signal after the frequency multipler,