# **Dynamic Verification Library for Chisel**

Yuan-Cheng Tsai

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-132 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-132.html

May 15, 2021

# Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Acknowledgement

I would first like to thank my research advisor, Professor Borivoje Nikolic, for giving me the opportunity to join ADEPT and BWRC during my undergraduate and graduate years. He has supported me throughout these years and has offered great guidance in my research projects. I have learned many things since, and the experience has given me more inspiration to pursue a career in digital hardware.

I would also like to thank my mentor, Vighnesh Iyer, for his mentorship throughout the research project. Whenever I had questions on the project, debugging, or even other work, he was always very helpful.

Last but not least, I would like to thank my family, friends, and peers for their continuous support throughout these remote times.

### **Dynamic Verification Library for Chisel**

by Yuan-Cheng (Anson) Tsai

#### **Research Project**

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, in partial satisfaction of the requirements for the degree of **Master of Science**, **Plan II**.

Approval for the Report and Comprehensive Examination:

Professor Borivoje Nikolić

Research Advisor

5 | 4 | 202 |

(Date)

\*\*\*\*\*\*

Professor Krste Asanović

Second Reader

5/14/2021

(Date)

#### Dynamic Verification Library for Chisel

by

Yuan-Cheng (Anson) Tsai

A thesis submitted in partial satisfaction of the requirements for the degree of

Masters of Science

in

Electrical Engineering Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Krste Asanović

Spring 2021

#### Abstract

Dynamic Verification Library for Chisel

by

Yuan-Cheng (Anson) Tsai

Masters of Science in Electrical Engineering Computer Science

University of California, Berkeley

Professor Borivoje Nikolić, Chair

As Chipyard (Berkeley's open-source SoC development framework) and Chisel (Berkeley's open-source hardware description language) are rapidly growing in popularity within both academia and industry, the need of a compatible verification library is stronger than ever. The industry standard UVM is not suitable with Chisel circuits, as although the generated Verilog can be verified, readability and debuggability is challenging for large designs. Moreover, as Chisel is built upon Scala, a general multi-purpose programming language, special high-level constructs such as type classes and generics that Chisel circuits are parameterized by are very difficult to represent in SystemVerilog. The open-source Chisel Verification Library remedies this disconnect between Chisel and UVM by providing high level verification constructs for Chisel testbenches. It is modeled off of UVM to contain the benefits of the test component abstractions such as the driver and monitor, and it also supports common interfaces such as the Decoupled and TileLink interface. Moreover, the library includes a SVA-like specification language eDSL that enable users to write property assertions on output traces. The library has been used in several applications, such as the verification of a RAM module, L2 cache, as well as an AES cryptography accelerator.

# Contents

| Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | i   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| List of Listings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | iii |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | v   |

| Listings         iii           Figures         v           Tables         v           aground and Project Introduction         1           Background         1           Dynamic Verification Library for Chisel         12           Component Library         15           Core Interfaces         15           Core Interfaces         15           Core Fransactions         16           Core Sequencers         18           Core Drivers         18           Core Monitors         20           Core Scoreboards         21           Example Testbench         22           TileLink Test Components         23           -like Specification Language as an eDSL         34           Introduction         34           Abstract Syntax Tree         36           Sequences         40           Properties         42           Memory Model         44           Application Examples         45           ary Applications         46           Library Test Components         52           Clusion and Future Work         57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 1 Background and Project Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1   |

| 1.1 Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 2 Test Component Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15  |

| 2.1 Core Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| To The Billing Tools Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 3 SVA-like Specification Language as an eDSL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34  |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| U Company of the Comp |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 3.7 Application Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45  |

| 4 Library Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46  |

| v = v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 4.2 Specification Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 5 Conclusion and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57  |

| 5.1 VIP Determinism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57  |

| 5.2 VIP Synthesizability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58  |

|                               | ii |

|-------------------------------|----|

| Bibliography                  | 59 |

| A Test Component Library Code | 60 |

# List of Listings

| 1.1  | Verilog-like Chisel for 3-point moving average (FIR Filter) 1  |

|------|----------------------------------------------------------------|

| 1.2  | N-FIR Filter generator 1                                       |

| 1.3  | Various types of FIR Filters 1                                 |

| 1.4  | Example of accumulate function                                 |

| 1.5  | Generated FIRRTL                                               |

| 1.6  | Generated Verilog.                                             |

| 1.7  | Adder test code.                                               |

| 1.8  | ChiselTest enqueue                                             |

| 1.9  | ChiselTest expectDequeue                                       |

| 1.10 | Naive ChiselTest QueueModule testbench                         |

| 1.11 | Naive ChiselTest QueueModule testbench with rate throttling    |

| 2.1  | FIR Filter IO, Taken from Listing 1.1                          |

| 2.2  | DecoupledTX implementation                                     |

| 2.3  | QueueModule implementation                                     |

| 2.4  | DecoupledTX example                                            |

| 2.5  | Generic driver implementation                                  |

| 2.6  | Decoupled driver slave implementation                          |

| 2.7  | Generic monitor implementation                                 |

| 2.8  | Decoupled monitor implementation                               |

| 2.9  | Queue testbench with rate throttling and backpressure          |

| 2.10 |                                                                |

| 2.11 | TLBundleA transaction example                                  |

| 2.12 | TLTransactionGenerator configuration options                   |

| 2.13 | TLDriverMaster implementation - simplified                     |

|      | TLSlaveFunction trait - simplified                             |

| 2.15 | TLDriverSlave implementation - simplified                      |

|      | TLMemoryModel "Get" implementation                             |

| 2.17 | TLMonitor implementation - simplified                          |

|      | TLRAM standalone block implementation - simplified             |

| 3.1  | SVA property example                                           |

| 3.2  | SpecLang AST                                                   |

| 3.3  | Atomic proposition for TileLink "Get" request                  |

| 3.4  | Time operator example: TileLink "Get" handshake sequence       |

| 3.5  | Implication example: TileLink "Get" handshake sequence pt. 2 4 |

| 3.6  | Sequence creation and operators                                |

| 3.7  | PropSet grouping visualization                                 |

| 3.8  | SpecLang property example                                      |

| 3.9  | Coverage example code - simplified                                 |

|------|--------------------------------------------------------------------|

| 3.10 | Coverage output                                                    |

| 3.11 | SLMemoryModel trait                                                |

| 3.12 | SLMemoryState trait                                                |

| 3.13 | Generic UInt SLMemoryState example                                 |

| 4.1  | TLSLProtocolChecker field properties code snippet - simplified     |

| 4.2  | TLSLProtocolChecker handshake properties code snippet - simplified |

| 4.3  | Optimized TLSLMemoryState for TileLink                             |

| 5.1  | Deterministic API prototype                                        |

| A.1  | DecoupledDriverMaster implementation                               |

| A.2  | TLDriverMaster implementation                                      |

| A.3  | TLDriverSlave implementation                                       |

| A.4  | TLMemoryModel "PutPartial/Full" implementation                     |

| A.5  | TLMonitor implementation                                           |

# List of Figures

| 1.1       | Chipyard flows. Adapted from Chipyard paper 3 | 1  |

|-----------|-----------------------------------------------|----|

| 1.2       | N-FIR Filter.                                 | 2  |

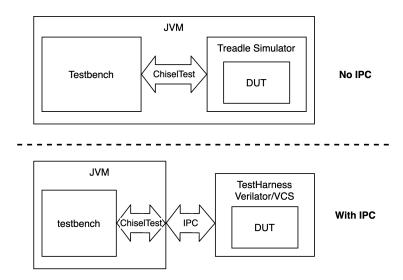

| 1.3       | ChiselTest API overview                       | 6  |

| 1.4       | Adder test wave.                              | 7  |

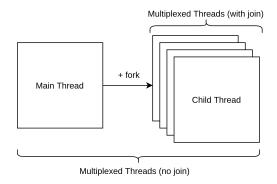

| 1.5       | ChiselTest fork/join diagram                  | 8  |

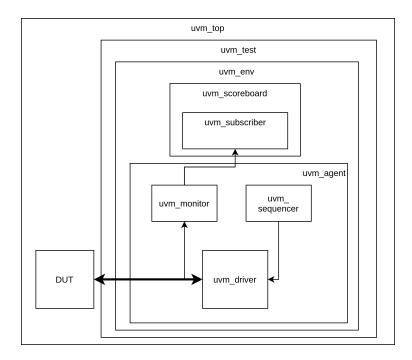

| 1.6       | UVM testbench layout                          | 10 |

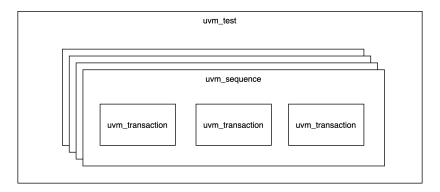

| 1.7       | UVM transactions                              | 11 |

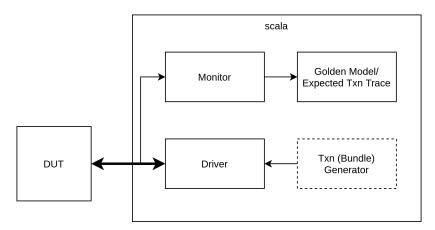

| 1.8       | Generic library testbench diagram.            | 13 |

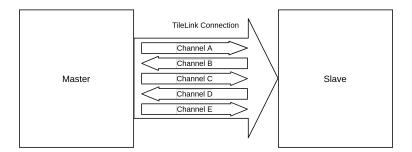

| 2.1       | TileLink connection diagram.                  | 23 |

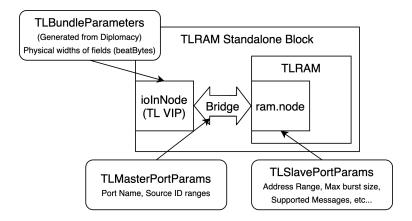

| 2.2       | TLRAM standalone block diagram                | 33 |

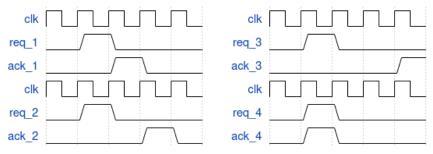

| 3.1       | Example waveforms for Req-Ack property        | 35 |

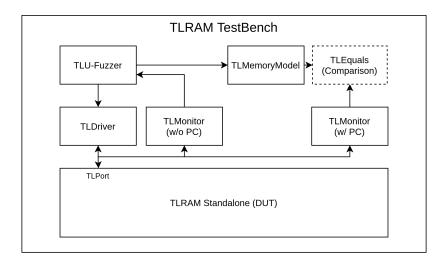

| 4.1       | TLRAM test setup.                             | 47 |

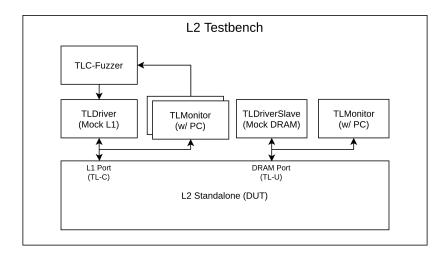

| 4.2       | SiFive's InclusiveCache (L2) test setup       | 48 |

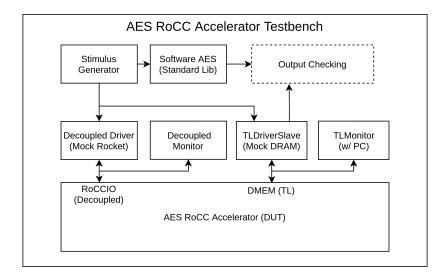

| 4.3       | AES RoCC Accelerator test setup.              | 50 |

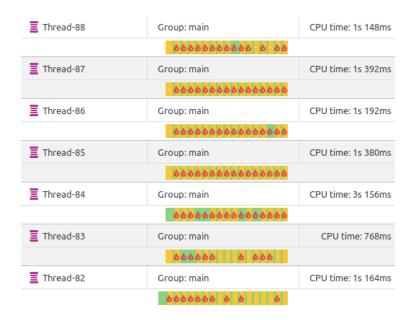

| 4.4       | Thread execution of TLRAM test - YourKit      | 52 |

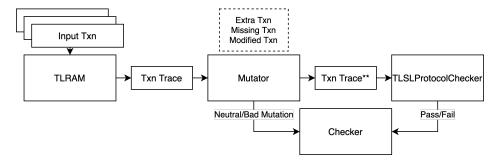

| 4.5       | TLRAM trace mutation test setup               | 56 |

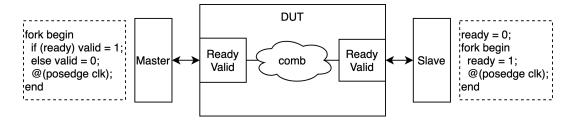

| 5.1       | VIP race condition with combinational logic   | 57 |

| ${f L}$ i | ist of Tables                                 |    |

| 2.1       | TLBundleA fields.                             | 24 |

| 2.2       | TLBundleD fields.                             | 24 |

| 2.3       | TL-UL handshake protocols                     | 25 |

| 2.4       | Added TL-UH handshake protocols.              | 26 |

| 2.5       | Added TL-C handshake protocols - simplified   | 26 |

| 1 1       | TIDAM                                         | ۲1 |

### Acknowledgments

I would first like to thank my research advisor, Professor Borivoje Nikolić, for giving me the opportunity to join ADEPT and BWRC during my undergraduate and graduate years. He has supported me throughout these years and has offered great guidance in my research projects. I have learned many things since, and the experience has given me more inspiration to pursue a career in digital hardware.

I would also like to thank my mentor, Vighnesh Iyer, for his mentorship throughout the research project. Whenever I had questions on the project, debugging, or even other work, he was always very helpful.

Last but not least, I would like to thank my family, friends, and peers for their continuous support throughout these remote times.

# Chapter 1

# Background and Project Introduction

# 1.1 Background

#### 1.1.1 Chipyard

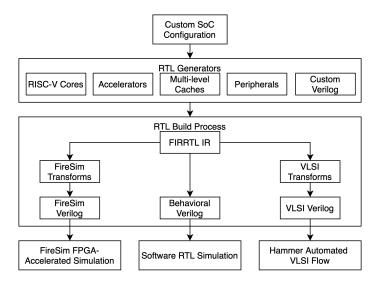

Developed at Berkeley, Chipyard 2 is a framework for building Chisel-based SoCs (systems-on-chip). It is a collection of open-source Chisel generators such as the Rocket Chip SoC generator and other Berkeley projects that together enable the generation of RISC-V SoCs. Figure 1.1 shows the design flows supported by Chipyard.

Chipyard lacks unit or subsystem-level verification infrastructure, and as such individual components are rarely tested at unit-level. Instead, the SoC is tested as a whole via software tests running on its CPU cores. This can result in situations where a working design can fail if parameterized differently, as previously hidden bugs are now exposed under a different configuration. As Chipyard has grown substantially in usage across both academia and industry, there is a stronger need for infrastructure to support unit-level testing of Chisel RTL to ensure that individual components and subsystems are bug-free. The next sections describe how Chisel-generated RTL is different from Verilog from the perspective of verification, and why the current industry verification practices are inadequate for Chisel RTL.

Figure 1.1: Chipyard flows. Adapted from Chipyard paper 3.

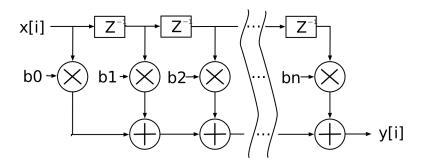

Figure 1.2: N-FIR Filter.

#### 1.1.2 Chisel

Chisel is a Berkeley-made domain specific language (DSL) that adds hardware construction primitives to the Scala programming language. Embedded in a general-purpose programming language, Chisel supports metaprogramming facilities such as parameterization that allows designers to create circuit generators that can be re-used in many designs. In the backend, Chisel emits FIRRTL, or Flexible Internal Representation for RTL, that can be further compiled into the standard Verilog or SystemVerilog (SV) that can then be used with the standard toolchains for synthesis, place and route, etc. To see Chisel in action, consider the following FIR filter example that is adapted from the Chisel website [1]. Figure 1.2 displays the general block diagram of a N-FIR filter that performs convolution operations.

Using only the Chisel primitives similar to that of synthesizable Verilog, Listing 1.1 displays the implementation for a 3-point moving average implemented in a FIR filter style.

```

case class FIRIO(bitWidth: Int) extends Bundle {

val in = Input(UInt(bitWidth.W))

2

val out = Output(UInt(bitWidth.W))

3

}

4

5

class MovingAverage3(bitWidth: Int) extends Module {

6

val io = IO(FIRIO(bitWidth))

7

8

9

val z1 = RegNext(io.in)

val z2 = RegNext(z1)

10

11

io.out := (io.in * 1.U) + (z1 * 1.U) + (z2 * 1.U)

12

}

13

```

Listing 1.1: Verilog-like Chisel for 3-point moving average (FIR Filter) 1.

Starting at the top, the IO of the FIR filter is defined as a Chisel Bundle, a struct-like object that groups together fields of varying types. Within the Bundle, two fields, in and

out, are defined as **UInt** types (unsigned integer hardware type) that have a parameterizable width of **bitWidth**. The directionality of the fields are indicated by **Input** and **Output**.

The circuit is defined on line 6 via a class that inherits from Module to declare that this object is a hardware module. Line 7 instantiates the FIRIO and wraps it within a IO function to declare it as the IO. On lines 9 and 10, two registers defined with the constructors RegNext combine together to create a shift register chain that stores the values from the previous two cycles. Note that the clock and reset ports are implicitly defined and connected to the registers when the module is elaborated. Lastly, the Chisel := operator on line 10 connects the sum of the multiplication operations with unsigned integers (denoted by .U) to io.out, implementing the 3-point moving average circuit.

However, if we utilize Chisel's strengths in that it is embedded within Scala, we can write a generator that can create a generalized N-FIR filter defined by a list of input coefficients:

```

// Generalized FIR filter parameterized by the convolution coefficients

class FirFilter(bitWidth: Int, coeffs: Seq[UInt]) extends Module {

3

// FIRIO specified in previous example

val io = IO(FIRIO(bitWidth))

4

5

6

// Create the serial-in, parallel-out shift register

7

val zs = Reg(Vec(coeffs.length, UInt(bitWidth.W)))

zs(0) := io.in

9

for (i <- 1 until coeffs.length) {</pre>

zs(i) := zs(i-1)

10

}

11

12

// Perform the multiplications

13

14

val products = VecInit.tabulate(coeffs.length)(i => zs(i) * coeffs(i))

15

// Sum up the products

16

io.out := products.reduce(_ + _)

17

18

}

```

Listing 1.2: N-FIR Filter generator 1.

The above implementation utilizes Scala constructs to create a generalizable FIR Filter circuit. Specifically, it uses a for loop to create the shift register chain, tabulate on line 14 to create a vector of multiplications, and reduce on line 17 for the final sum. Now, additional variants can now be defined without having to implement separate circuits:

```

// same 3-point moving average filter as before

val movingAverage3Filter = Module(new FirFilter(8, Seq(1.U, 1.U, 1.U)))

// 1-cycle delay as a FIR filter

val delayFilter = Module(new FirFilter(8, Seq(0.U, 1.U)))

// 5-point FIR filter with a triangle impulse response

val triangleFilter = Module(new FirFilter(8, Seq(1.U, 2.U, 3.U, 2.U, 1.U)))

```

Listing 1.3: Various types of FIR Filters 1.

Moreover, there is no limit on which Scala constructs can be used. For example, the FIR filter could have parameterized the sum function to take on different data types. The function could be more expressive with the use of higher-order functions, typeclasses and type generics, as shown below with an example implementation of an accumulate function for Ring values:

```

1  def accumulate[T <: Data : Ring](v: Vec[T]): T = {

2    val ring = implicitly[Ring[T]]

3    v.foldLeft(ring.zero)((a, b) => ring.add(a, b))

4  }

```

Listing 1.4: Example of accumulate function.

Even with these software constructs, the circuit can still be generated into functional Verilog. As mentioned earlier, Chisel can emit FIRRTL which is an RTL intermediate representation that can then be compiled to Verilog/SystemVerilog. For simplicity, let's consider the FIRRTL and generated Verilog for the simple FIR circuit implemented in Listing 1.1:

```

circuit FirFilter :

module FirFilter :

2

3

input clock : Clock

input reset : UInt<1>

4

5

output io : {flip in : UInt<8>, out : UInt<8>}

6

reg zs : UInt<8>[3], clock

7

zs[0] \ll io.in

8

zs[1] \ll zs[0]

9

10

zs[2] \ll zs[1]

node _T = mul(zs[0], UInt<1>("h01"))

11

node _{T_1} = mul(zs[1], UInt<1>("h01"))

12

node _{T_2} = mul(zs[2], UInt<1>("h01"))

13

wire products : UInt<9>[3]

14

products[0] <= _T</pre>

15

products[1] <= _T_1</pre>

16

products[2] <= _T_2</pre>

17

node _T_3 = add(products[0], products[1])

18

node _T_4 = tail(_T_3, 1)

19

node _{T_5} = add(_{T_4}, products[2])

20

21

node _T_6 = tail(_T_5, 1)

22

io.out <= _T_6

```

Listing 1.5: Generated FIRRTL.

Above is the generated FIRRTL of the 3-point moving average FIR filter. From brief inspection, the structure can be seen to be very similar to that of listing Listing 1.1 Next, Listing 1.6 displays the Verilog generated from the FIRRTL code.

```

module FirFilter(

1

input

2

clock,

input

3

reset,

4

input

[7:0] io_in,

output [7:0] io_out

5

);

6

reg [7:0] zs_0;

7

reg [7:0] zs_1;

8

9

reg [7:0] zs_2;

10

wire [8:0] products_0 = zs_0 * 1'h1;

wire [8:0] products_1 = zs_1 * 1'h1;

11

wire [8:0] products_2 = zs_2 * 1'h1;

12

wire [8:0] _T_4 = products_0 + products_1;

13

wire [8:0] _T_6 = _T_4 + products_2;

14

assign io_out = _T_6[7:0];

15

16

always @(posedge clock) begin

zs_0 <= io_in;</pre>

17

zs_1 <= zs_0;

18

zs_2 \ll zs_1;

19

20

end

21

endmodule

```

Listing 1.6: Generated Verilog.