## Circuits and Systems for Decentralized Power Conversion

Jason Poon

### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-220 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-220.html

December 1, 2021

Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Circuits and Systems for Decentralized Power Conversion

by

Jason Poon

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Seth R. Sanders, Chair Associate Professor Robert C. N. Pilawa-Podgurski Associate Professor Duncan Callaway

Summer 2019

Circuits and Systems for Decentralized Power Conversion

Copyright 2019

by

Jason Poon

#### Abstract

#### Circuits and Systems for Decentralized Power Conversion

by

Jason Poon

Doctor of Philosophy in Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Seth R. Sanders, Chair

This dissertation explores circuit, control, and optimization techniques for power electronics with the objective of enabling high performance electric networks for a variety of important applications. The motivation for this work is driven in part by societal-scale trends towards systems that are increasingly dominated by power electronics, including applications such as renewable energy integration, vehicle electrification, power management for mobile devices, and data center power delivery. A key approach demonstrated in this dissertation is the design of switching power converter circuits that naturally coordinate with larger networks in order to achieve system-level benefits, whether with respect to efficiency, power quality, or reliability. A central goal of this work is to have this coordination realized in a decentralized or autonomous fashion, such that scalability, modularity, and resiliency can be achieved inherently. In the first part of this dissertation, we explore techniques for improving the power quality of electric networks with high penetrations of switching power converters, in particular, techniques that can minimize aggregate power converter harmonics in an optimal sense while also eliminating the need for communication between distributed converters. In the second part of this dissertation, we explore methods for improving the reliability and fault tolerance of such networks, in particular, model- and estimation-based strategies that transform power converters into active probes that can detect, identify, and diagnose faults in real-time. Together, these contributions demonstrate how power electronics can be designed and collectively controlled and optimized to enable highly efficient, robust, and resilient electric networks.

# Contents

| Co | ontents                                                                                                                                                                                                    | i                                                                                                          |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Li | st of Figures                                                                                                                                                                                              | iii                                                                                                        |

| Li | st of Tables                                                                                                                                                                                               | ix                                                                                                         |

| 1  | Introduction         1.1       Primary Contributions         1.2       Outline and Previously Published Work                                                                                               | <b>1</b><br>4<br>5                                                                                         |

| Ι  | Control Techniques for Improved Power Quality                                                                                                                                                              | 7                                                                                                          |

| 2  | State-of-the-Art Techniques and Key Limitations         2.1       Series- and Parallel-Connected Multistage Architectures         2.2       Conventional Interleaving Techniques         2.3       Summary | <b>8</b><br>8<br>14<br>22                                                                                  |

| 3  | Optimization & Control of Distributed Power Converters3.1Overview of Minimum Distortion Point Tracking                                                                                                     | <ul> <li>23</li> <li>25</li> <li>31</li> <li>33</li> <li>39</li> <li>42</li> <li>46</li> <li>48</li> </ul> |

| 4  | Architectures for Decentralized Control4.1Overview of Interleaving4.2System Description and Modeling4.3Equilibria and Stability4.4Experimental Validation                                                  | <b>49</b><br>50<br>52<br>57<br>64                                                                          |

|    | 4.5 Summary                                                                                                                                                                                    | 70                                                                                       |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Π  | Reliability Considerations                                                                                                                                                                     | 72                                                                                       |

| 5  | Fault Diagnosis: Landscape and Motivation5.1 Applications of Interest5.2 State-of-the-Art Strategies for Fault Diagnosis5.3 Summary                                                            | <b>73</b><br>73<br>79<br>83                                                              |

| 6  | Modeling and Estimation Framework6.1Converter and Fault Modeling Framework6.2Estimation Framework6.3Summary                                                                                    | <b>84</b><br>84<br>88<br>91                                                              |

| 7  | State Estimation-Based FDI Techniques7.1FDI Algorithm Design                                                                                                                                   | <b>92</b><br>93<br>98<br>102<br>105<br>109                                               |

| 8  | Parameter Estimation-Based FDI Techniques8.1Adaptive Parameter Identifier Design8.2Simulation and Analysis8.3Hardware Implementation and Experimental Testbed8.4Experimental Results8.5Summary | <ul> <li>111</li> <li>112</li> <li>114</li> <li>121</li> <li>122</li> <li>125</li> </ul> |

| 9  | Conclusions                                                                                                                                                                                    | 126                                                                                      |

| Bi | ibliography                                                                                                                                                                                    | 127                                                                                      |

| A  | Uncovering the dependence of $\mathcal{D}$ on $\theta$                                                                                                                                         | 147                                                                                      |

| В  | Monte Carlo simulation setup                                                                                                                                                                   | 149                                                                                      |

| С  | Equivalence of $(4.6)-(4.7)$ to $(4.9)-(4.10)$                                                                                                                                                 | 150                                                                                      |

| D  | Derivation of (4.13)                                                                                                                                                                           | 153                                                                                      |

ii

# List of Figures

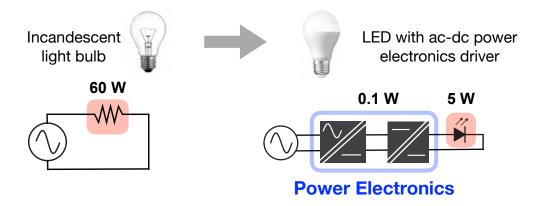

| 1.1 | An incandescent light bulb (left) produces the same amount of light as a light-<br>emitting diode (LED) (right), but requires an order-of-magnitude more power.<br>However, LEDs, unlike incandescent light bulbs, require power electronics in order                                                                                                 |        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.2 | for a precisely regualted voltage and current                                                                                                                                                                                                                                                                                                         | 2      |

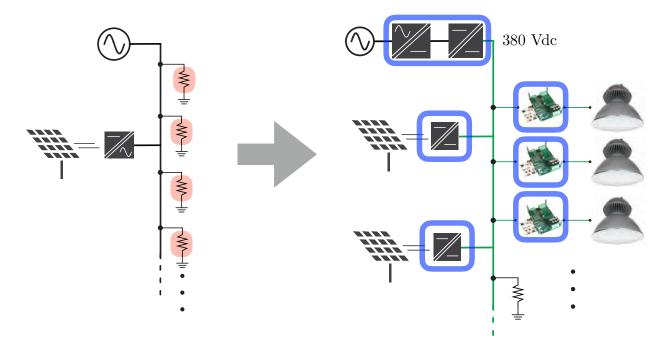

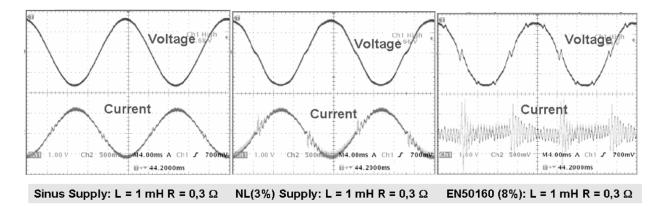

| 1.3 | both electrical sources and loads (right)                                                                                                                                                                                                                                                                                                             | 3<br>3 |

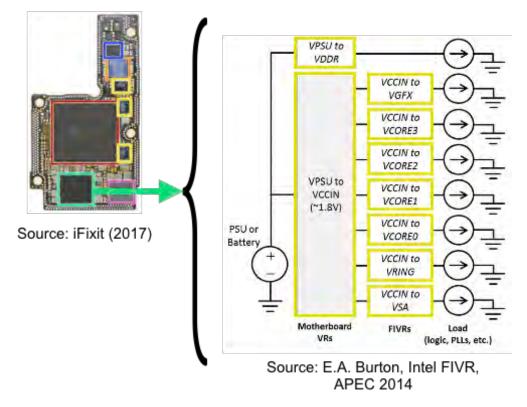

| 2.1 | Illustration of an example power management integrated circuit within a mobile phone.                                                                                                                                                                                                                                                                 | 9      |

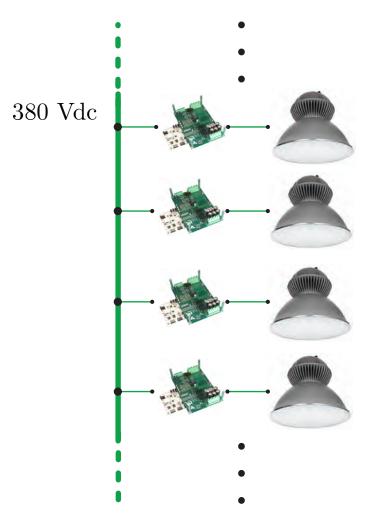

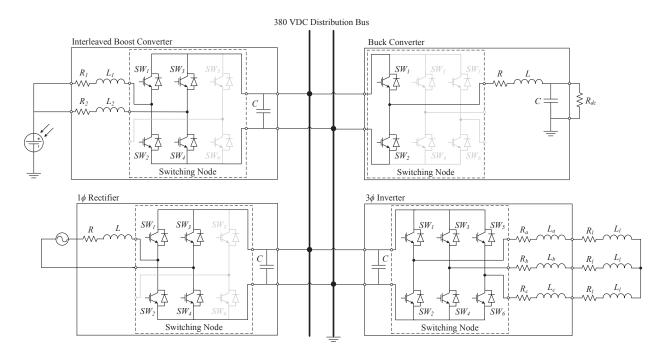

| 2.2 | A candidate 380 Vdc distribution architecture with LED loads.                                                                                                                                                                                                                                                                                         | 11     |

| 2.3 | Parallel-connected ac microinverter-based architecture for photovoltaic systems                                                                                                                                                                                                                                                                       | **     |

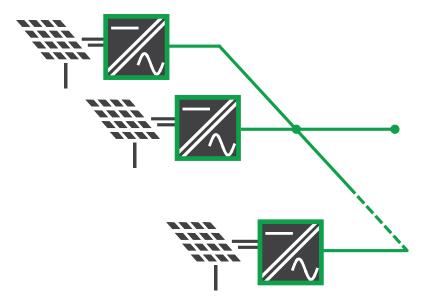

|     | integration.                                                                                                                                                                                                                                                                                                                                          | 12     |

| 2.4 | Teardown of a 250W Ubiquiti Energy SM-MI-250 sunMAX Microinverter. As shown, components related to EMI and filtering comprise the majority of the size of the overall converter.                                                                                                                                                                      | 12     |

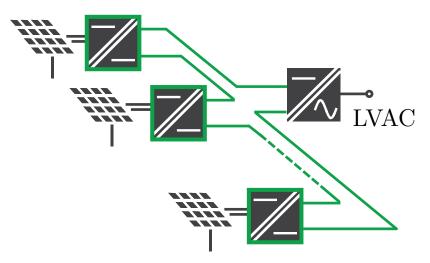

| 2.5 | Series-connected dc power optimizer-based architecture for photovoltaic systems integration.                                                                                                                                                                                                                                                          | 13     |

| 2.6 | N input-parallel connected dc-dc buck converters with independent output volt-                                                                                                                                                                                                                                                                        | 10     |

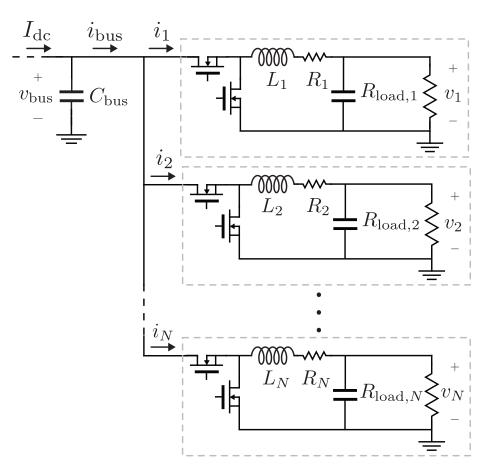

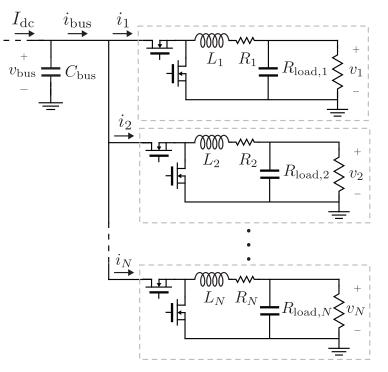

|     | ages $v_1, \ldots, v_N$ and load resistances $R_{\text{load},1}, \ldots, R_{\text{load},N}, \ldots, \ldots, \ldots, \ldots$                                                                                                                                                                                                                           | 14     |

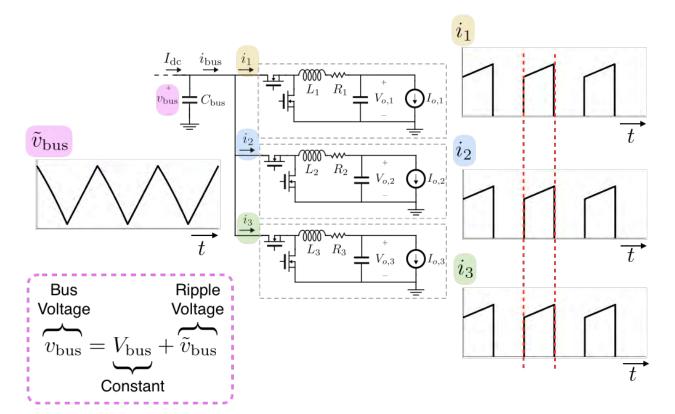

| 2.7 | Illustration of converter waveforms when loads $I_{o,1}$ , $I_{o,2}$ , and $I_{o,3}$ are identical and                                                                                                                                                                                                                                                |        |

|     | switch timing is synchronized to be in-phase.                                                                                                                                                                                                                                                                                                         | 15     |

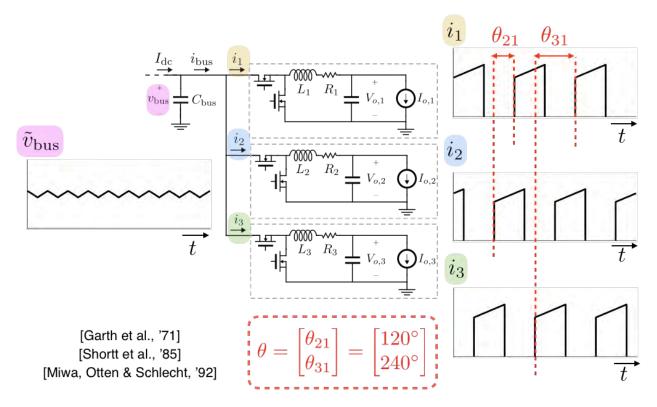

| 2.8 | Illustration of converter waveforms when loads $I_{o,1}$ , $I_{o,2}$ , and $I_{o,3}$ are identical and                                                                                                                                                                                                                                                |        |

|     | switch timing is interleaved.                                                                                                                                                                                                                                                                                                                         | 16     |

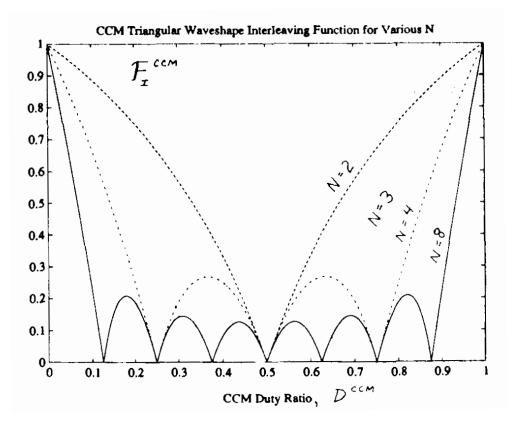

| 2.9 | Result from [22] which illustrates the "normalized interleaving function" $\mathcal{F}$ as the number of interleaved converters is varied from $N = 2$ to $N = 8$ and plotted as a function of the duty ratio. Of note is that the value never exceeds one-that is, applying symmetric interleaving to a symmetric circuit will never result in a net |        |

|     | current ripple that is higher than the current ripple of a single converter                                                                                                                                                                                                                                                                           | 17     |

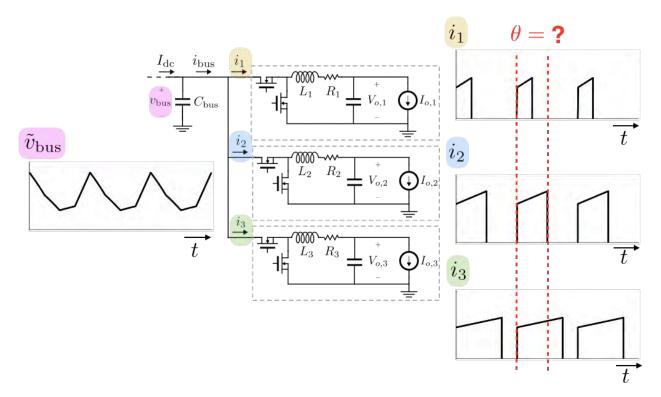

|      | Illustration of converter waveforms when loads $I_{o,1}$ , $I_{o,2}$ , and $I_{o,3}$ are not identical<br>and switch timing is synchronized to be in-phase.                                                                                                                                                                                                                                                                                                                             | 19 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

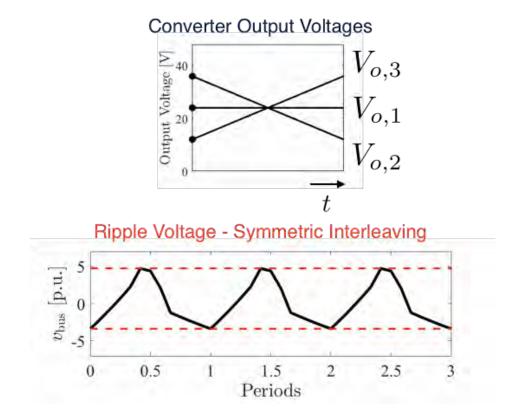

| 2.11 | An illustration of three periods of $v_{\text{bus}}$ when the output voltages of each converter<br>are swept as shown in the top subfigure and the circuit is operated with symmetric<br>interleaving. $v_{\text{bus}}$ is normalized to the magnitude of $v_{\text{bus}}$ when the output voltages<br>are identical (the symmetric operating scenario).                                                                                                                                | 20 |

| 2.12 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 |

| 3.1  | ${\cal N}$ input-parallel connected dc-dc buck converters with independent output volt-                                                                                                                                                                                                                                                                                                                                                                                                 |    |

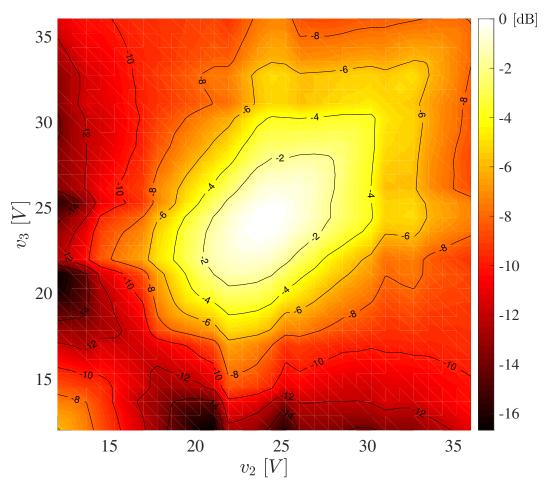

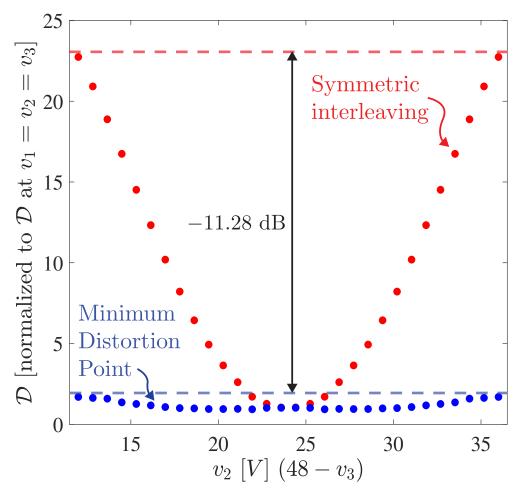

| 3.2  | ages $v_1, \ldots, v_N$ and load resistances $R_{\text{load},1}, \ldots, R_{\text{load},N}, \ldots, \ldots, \ldots$<br>Achievable reduction in $\mathcal{D}$ (in dB) when operating at the MDP compared to<br>operating at the symmetric interleaved state. Plot shows reduction in $\mathcal{D}$ when<br>$v_1 = 24 V$ and $v_2$ and $v_3$ are independently swept from 12 V to 36 V with identical<br>fixed resistive loads on the output of each converter. The darker areas indicate | 25 |

|      | regions where greater reductions in $\mathcal{D}$ are possible                                                                                                                                                                                                                                                                                                                                                                                                                          | 28 |

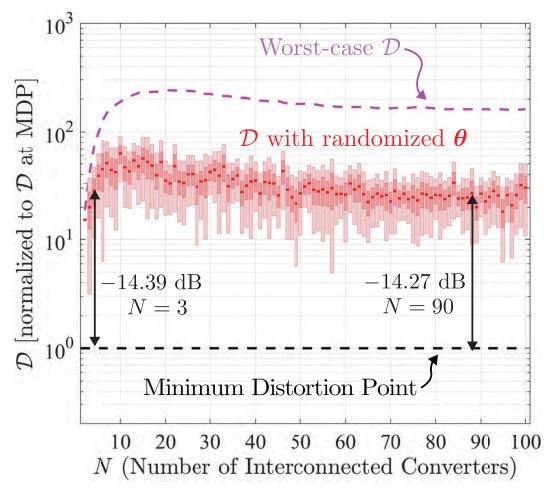

| 3.3  | Reduction in $\mathcal{D}$ between the symmetric interleaved state and the MDP when                                                                                                                                                                                                                                                                                                                                                                                                     | 20 |

| 3.4  | $v_1 = 24 V$ and $v_3 = 48 - v_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29 |

| 0.4  | scenarios, including the MDP (dashed black line), the worst-case phase shifting                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | (dashed magenta line), and at a uniformly distributed random phase spacing across the $N$ converters (red box plot indicating median, $25^{\text{th}}$ percentile, and $75^{\text{th}}$                                                                                                                                                                                                                                                                                                 |    |

|      | percentile). For each $N$ , one hundred Monte Carlo scenarios are simulated, and<br>the output voltage, the average output current, and the inductor size of each of                                                                                                                                                                                                                                                                                                                    |    |

|      | the N converters are randomized variables. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                 | 30 |

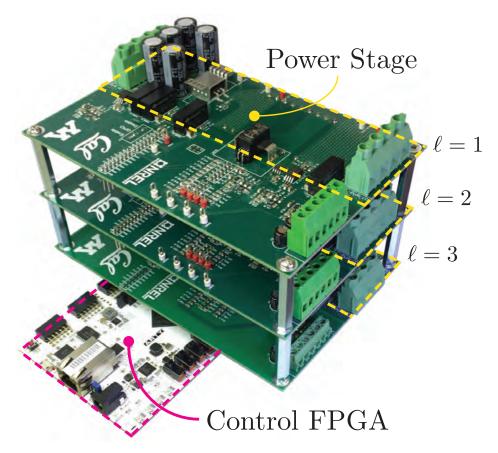

| 3.5  | Hardware prototype consisting of three 600 W input-parallel connected dc-dc                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 26   | buck converters with 48 Vdc input bus                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33 |

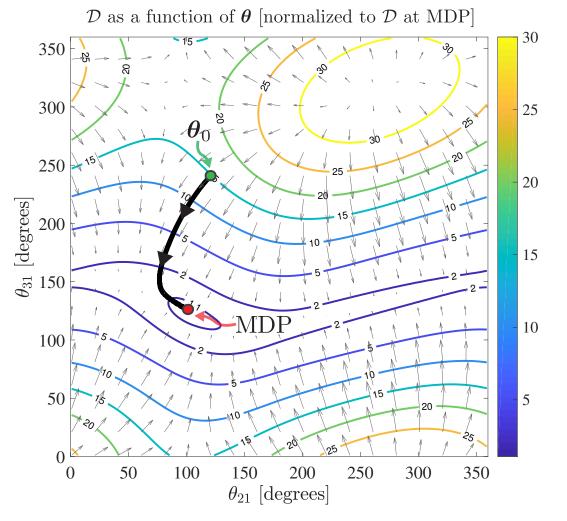

| 3.6  | Numerical simulation of the gradient-based MDPT algorithm. Contour lines of $\mathcal{D}$ (normalized to $\mathcal{D}$ at the MDP) and arrows depicting $\nabla \mathcal{D}$ are shown                                                                                                                                                                                                                                                                                                  | 34 |

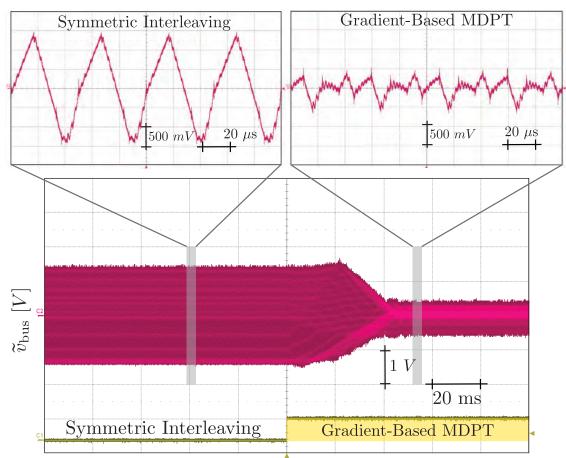

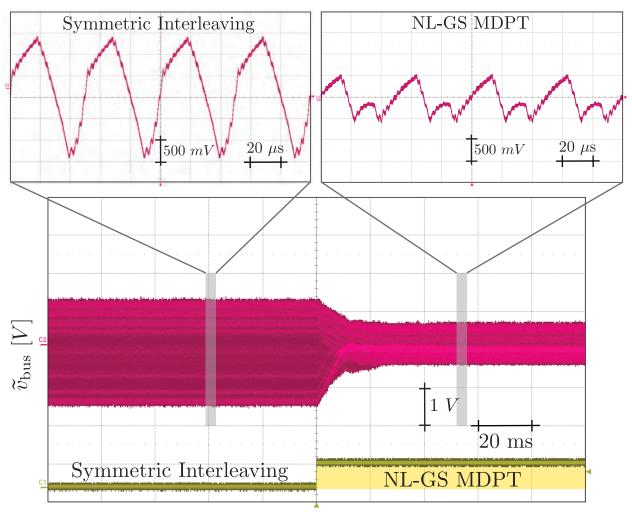

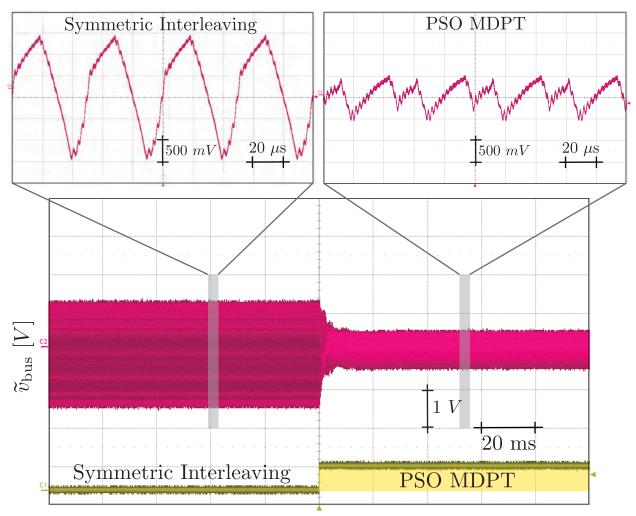

| 3.7  | Experimental validation of the convergence speed and performance of the gradient-                                                                                                                                                                                                                                                                                                                                                                                                       | 01 |

|      | based MDPT algorithm. As shown, the algorithm converges in approximately 100                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|      | iterations (40 ms) and enables a $2.91 \times$ reduction in the peak-to-peak ripple of                                                                                                                                                                                                                                                                                                                                                                                                  | 25 |

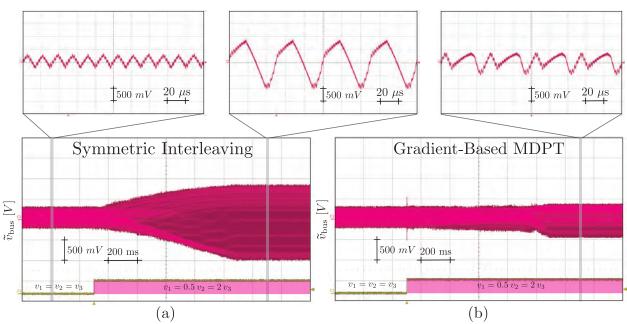

| 3.8  | $\tilde{v}_{\text{bus}}$ compared to the peak-to-peak ripple at the symmetric interleaved state<br>Experimental validation of the tracking capability of the gradient-based MDPT                                                                                                                                                                                                                                                                                                        | 35 |

|      | algorithm. When asymmetries in the output voltages are introduced, (a) sym-                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | metric interleaving results in a 3.28× larger peak-to-peak ripple of $\tilde{v}_{\text{bus}}$ at the wavet ease, while (b) the gradient based MDPT algorithm applies ripple mini-                                                                                                                                                                                                                                                                                                       |    |

|      | worst case, while (b) the gradient-based MDPT algorithm enables ripple minimization throughout the asymmetric loading transient and results in only $1.48 \times$                                                                                                                                                                                                                                                                                                                       |    |

|      | larger peak-to-peak ripple of $\tilde{v}_{\text{bus}}$ at the worst case                                                                                                                                                                                                                                                                                                                                                                                                                | 36 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

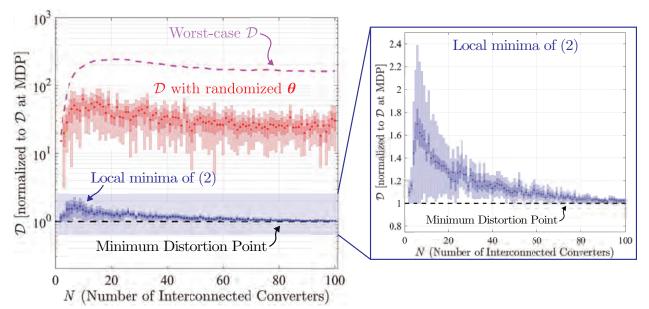

| 3.9        | A Monte Carlo simulation that illustrates $\mathcal{D}$ obtained at the worst-case phase<br>shifting (dashed magenta line), at a uniformly distributed random phase spacing<br>across the N converters (red), and at various local minima of the non-convex<br>function $\mathcal{D}(\boldsymbol{\theta})$ (blue), all normalized to $\mathcal{D}$ at the MDP, and plotted as a function<br>of the number of interconnected power converters N. For each N, one hundred<br>scenarios are simulated, and the 25th and 75th percentile values of $\mathcal{D}$ are shown                |          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

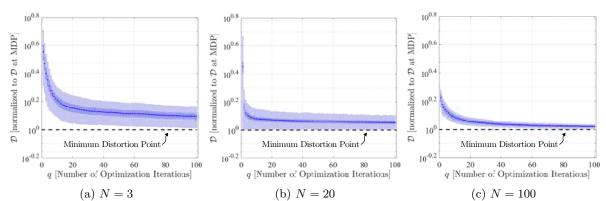

| 3.10       | with shaded bars                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38       |

| 3.11       | tified in Section 3.4.3, while increasing the number of interconnected converters $(N)$ yields a more optimal steady state solution                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40       |

| 3.12       | symmetric interleaved state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42<br>44 |

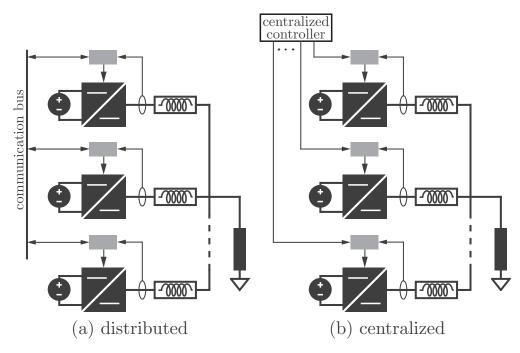

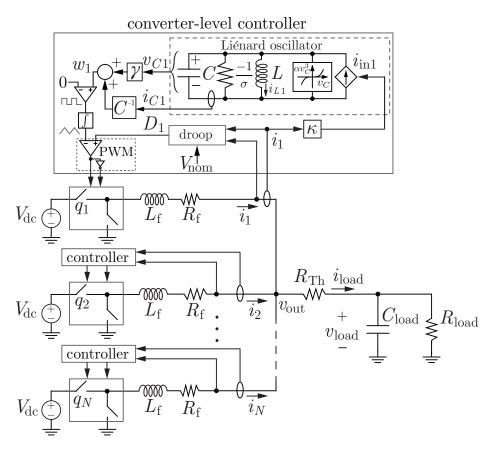

| 4.1        | System of parallel-connected buck converters with local controllers. The proposed controller has the dynamics of a nonlinear Liénard-type oscillator circuit which takes the converter output current as feedback and generates the triangular PWM carrier at each converter by using a linear combination of its states. Droop control ensures decentralized power sharing.                                                                                                                                                                                                          | 52       |

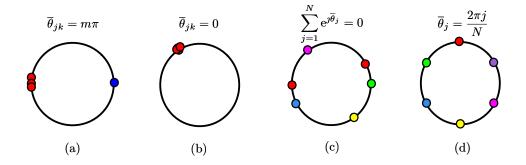

| 4.2        | Equilibria for the coupled oscillator dynamics (4.22): a) bi-cluster synchronous state, b) phase-synchronous state, c) generalized interleaved state, and d) symmetric-interleaved state. Recall that $\overline{\theta}_j$ is the averaged phase-angle offset (with respect to a nominal reference frame rotating at the switching frequency) corresponding to the voltage of the virtual capacitor, $v_{Cj}$ (and hence of its corresponding carrier waveform) for the <i>j</i> -th oscillator. Furthermore, $\overline{\theta}_{jk} = \overline{\theta}_j - \overline{\theta}_k$ . | 59       |

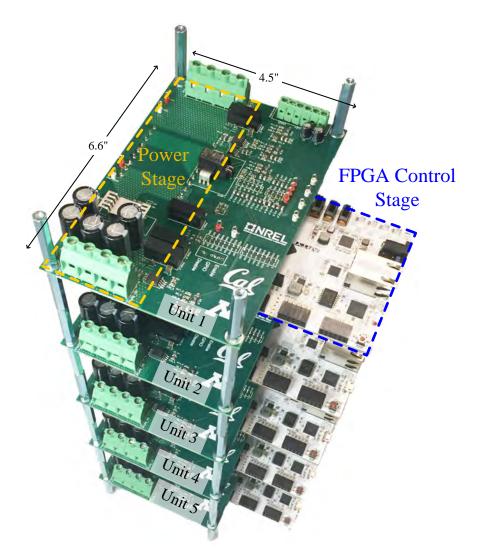

| 4.3<br>4.4 | Photograph of the experimental prototype: five dc-dc converters and associated controller boards. Note that there is no communication between controllers Circuit diagram illustrating experiments performed: (a) start up from arbitrary initial conditions, (b) addition of one converter to system, (c) load step, (d) unit addition in non-symmetric network with parasitics (in this case, converters continue to sense local output voltages for droop control even though this is not                                                                                          | 65       |

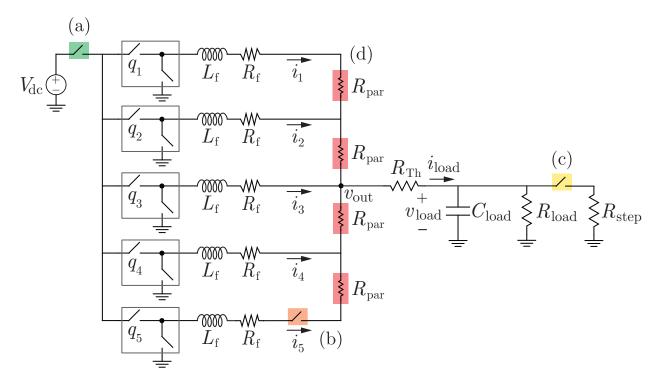

|            | explicitly depicted in the figure).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66       |

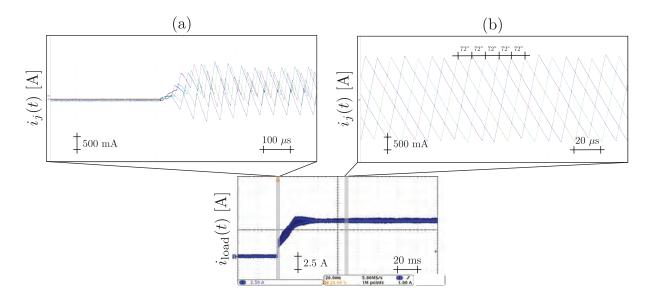

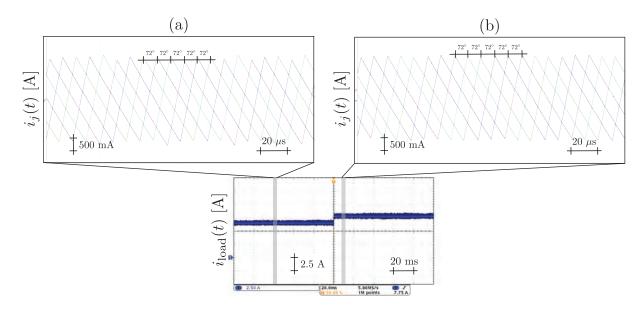

| 4.5                                       | Five buck converters are started from arbitrary initial conditions with the de-<br>signed oscillator-based controllers (a). The system achieves symmetric interleav-<br>ing with $72^\circ = 360^\circ/5$ phase spacing and the droop controller maintains balanced                                                                                                               | 67                  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

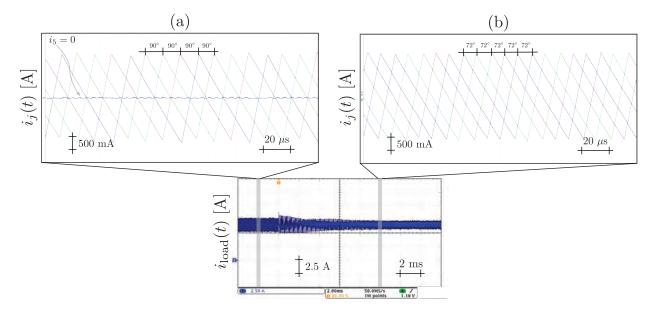

| 4.6                                       | currents in each of the five units in steady state (b)                                                                                                                                                                                                                                                                                                                            | 67<br>68            |

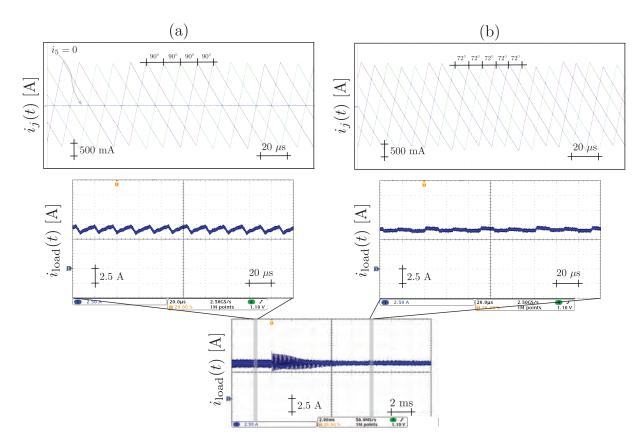

| 4.7                                       | To evaluate the robustness to load variations, a load step from $R_{\text{load}} = 1.6 \Omega$<br>(a) to $R_{\text{load}} = 1.3 \Omega$ (b) at $t = 0$ is introduced with five units in steady state.<br>The convergence to the new steady state is almost instantaneous and the system maintains the symmetric interleaved state with $72^{\circ} = 360^{\circ}/5$ phase spacing |                     |

| 4.8                                       | between converters                                                                                                                                                                                                                                                                                                                                                                | 69<br>69            |

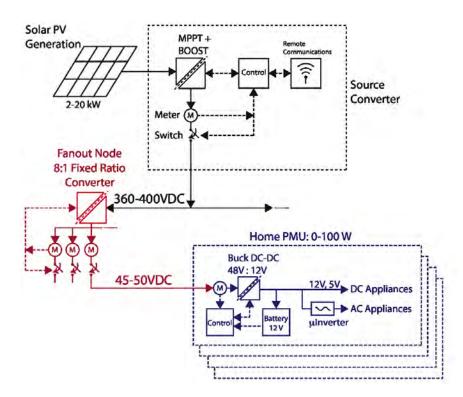

| $5.1 \\ 5.2 \\ 5.3$                       | A DC-based power distribution nanogrid                                                                                                                                                                                                                                                                                                                                            | 74<br>74            |

| 5.4                                       | (PMUs)                                                                                                                                                                                                                                                                                                                                                                            | 77<br>78            |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Boost converter topology                                                                                                                                                                                                                                                                                                                                                          | $\frac{85}{86}$     |

| $7.1 \\ 7.2$                              | Boost converter model with switch and passive component parasitics Steady state dynamics of boost converter model with switch and passive compo-                                                                                                                                                                                                                                  | 99                  |

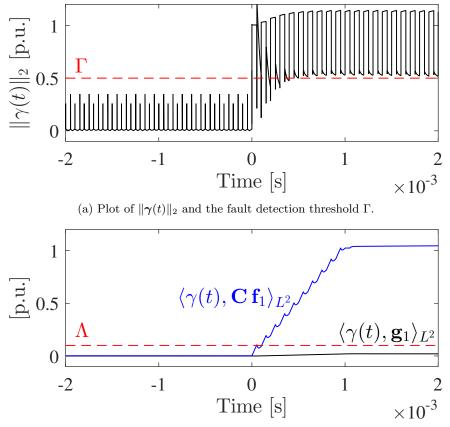

| 7.3                                       | nent parasitics (Fig. 7.1) with nominal component parameters. $\ldots$ $\ldots$ $\ldots$ Simulation of the FDI algorithm for a capacitor fault injected at $t = 0$ caus-                                                                                                                                                                                                          | 100                 |

| 7.4                                       | ing $C \to 0$ . Shown is the worst-case scenario caused by parameter variation $(\min(L_1), \max(C), \max(R_{esr}), \ldots, \ldots$<br>Simulation of the FDI algorithm for a fault in the input inductor $L_1$ current sensor injected at $t = 0$ . Shown is the worst-case scenario caused by parameter  | 101                 |

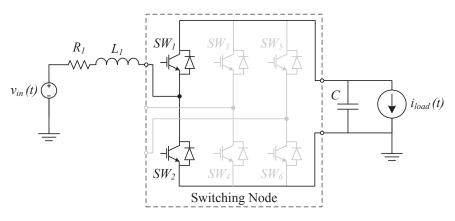

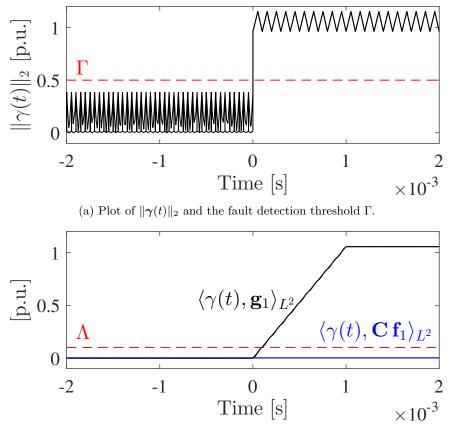

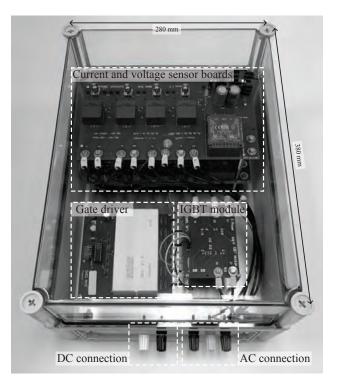

| $7.5 \\ 7.6$                              | variation $(\min(L_1), \max(C), \max(R_{esr}), \ldots, \ldots, \ldots, \ldots, \ldots, \ldots, \ldots)$<br>Photograph of the FDI computing platform and prototype nanogrid testbed. Switching node implementation.                                                                                                                                                                | $102 \\ 104 \\ 105$ |

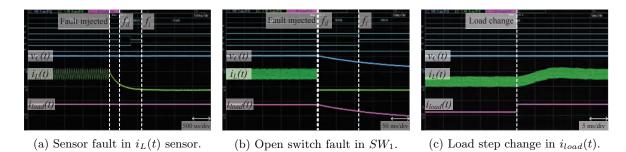

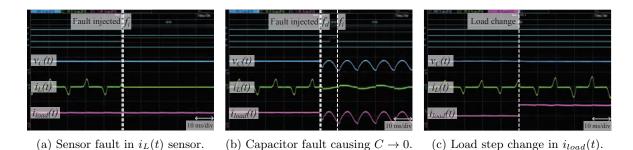

| <ul> <li>inductor current i<sub>L</sub>(t), and the load current i<sub>load</sub>(t)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.7  | Verification of the FDI method for a variety of fault and operating scenarios for<br>a buck converter. In each scenario, the fault or event is injected at the instant as<br>labeled, and the times to fault detection and fault identification are indicated by<br>the digital traces. Analog waveforms shown are the capacitor voltage $v_C(t)$ , the |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

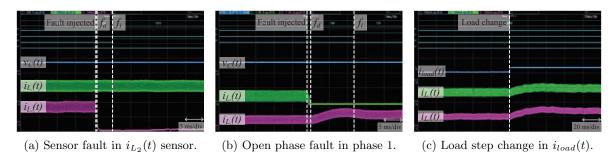

| voltage $v_C(t)$ and the inductor currents $i_{L_1}(t)$ and $i_{L_2}(t)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7.8  | inductor current $i_L(t)$ , and the load current $i_{load}(t)$                                                                                                                                                                                                                                                                                          | 106        |

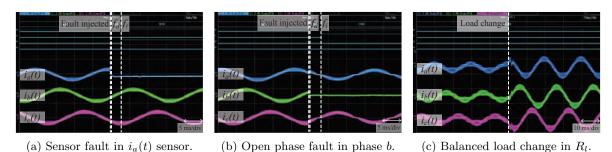

| <ul> <li>7.10 Verification of the FDI method for a variety of fault and operating scenarios for a three-phase inverter. In each scenario, the fault or event is injected at the instant as labeled, and the times to fault detection and fault identification are indicated by the digital traces. Analog waveforms shown are the three phase currents i<sub>a</sub>(t), i<sub>b</sub>(t), and i<sub>c</sub>(t)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7.9  | voltage $v_C(t)$ and the inductor currents $i_{L_1}(t)$ and $i_{L_2}(t)$                                                                                                                                                                                                                                                                                | 106        |

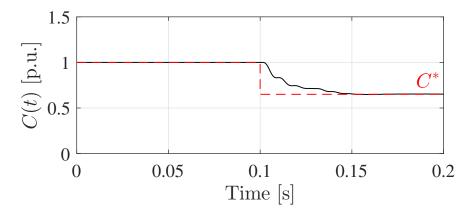

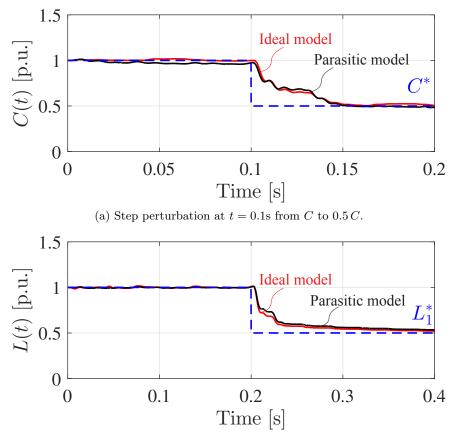

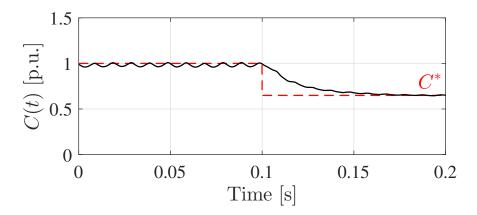

| <ul> <li>capacitance C (t = 0.1s from C to 0.65 C)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7.10 | Verification of the FDI method for a variety of fault and operating scenarios for a three-phase inverter. In each scenario, the fault or event is injected at the instant as labeled, and the times to fault detection and fault identification are indicated by the digital traces. Analog waveforms shown are the three phase currents $i_a(t)$ ,     |            |

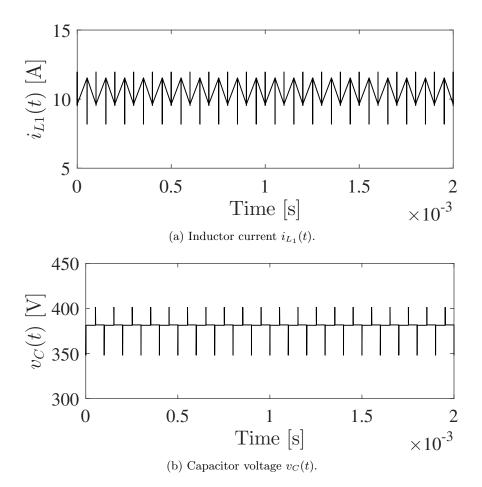

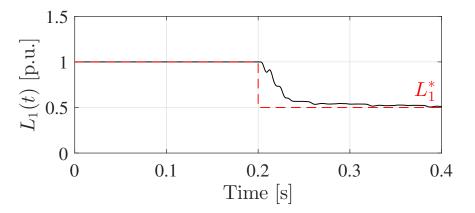

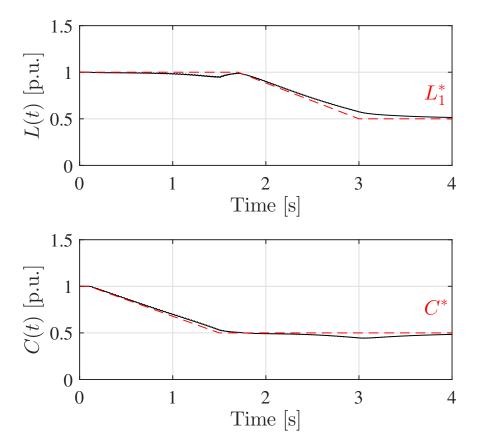

| <ul> <li>8.2 Simulation of the adaptive parameter identifier tracking a step perturbation in inductance L<sub>1</sub> (t = 0.2s from L<sub>1</sub> to 0.5 L<sub>1</sub>)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8.1  |                                                                                                                                                                                                                                                                                                                                                         | 116        |

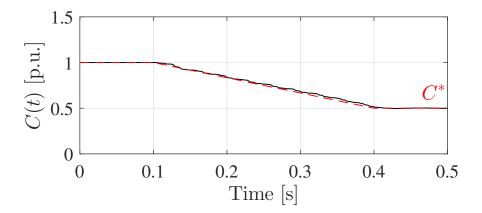

| <ul> <li>8.3 Simulation of the adaptive parameter identifier tracking a ramp perturbation in capacitance C (-166.7 μF/s from C to 0.5 C)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8.2  | Simulation of the adaptive parameter identifier tracking a step perturbation in                                                                                                                                                                                                                                                                         |            |

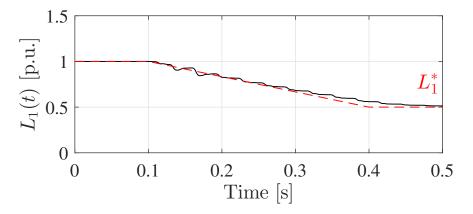

| <ul> <li>inductance L<sub>1</sub> (-16.7 mH/s at t = 0.1s from L<sub>1</sub> to 0.5 L<sub>1</sub>)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.3  | Simulation of the adaptive parameter identifier tracking a ramp perturbation in                                                                                                                                                                                                                                                                         | 117        |

| <ul> <li>bations in inductance L<sub>1</sub> (-1.9 mH/s at t = 1.75 s) and capacitance (-35.7 μF/s from C to 0.5 C at t = 0.2 s).</li> <li>8.6 A simulation of an interleaved boost dc-dc converter incorporating switch and passive component parasitics and non-idealities is used to validate the robustness of the proposed adaptive parameter identifier.</li> <li>8.7 Comparison of the adaptive parameter identifier convergence when applied to the ideal model (Fig. 6.1) versus parasitic model (Fig. 8.6a).</li> <li>8.8 Photograph of the experimental testbed, including the interleaved dc-dc converter and the Zynq-7000 SoC board.</li> <li>8.9 Experiment of adaptive parameter identifier tracking a step perturbation in ca-</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8.4  | inductance $L_1$ (-16.7 mH/s at $t = 0.1$ s from $L_1$ to $0.5 L_1$ ).                                                                                                                                                                                                                                                                                  | 117        |

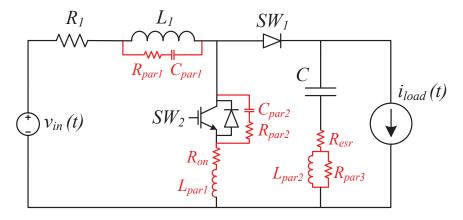

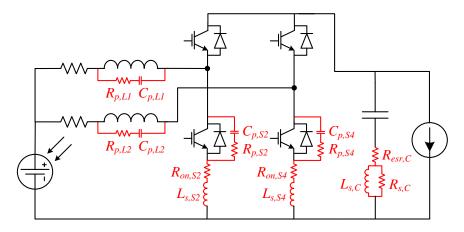

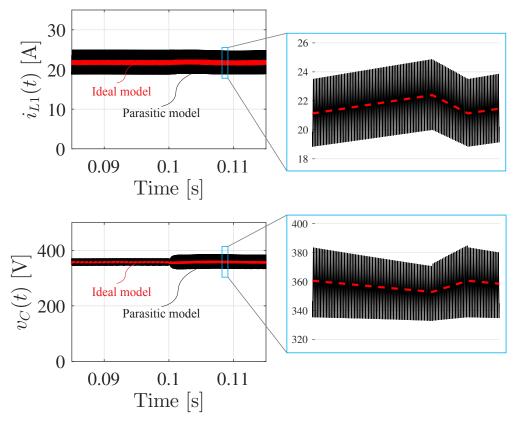

| <ul> <li>8.6 A simulation of an interleaved boost dc-dc converter incorporating switch and passive component parasitics and non-idealities is used to validate the robustness of the proposed adaptive parameter identifier</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8.5  | bations in inductance $L_1$ (-1.9 mH/s at $t = 1.75$ s) and capacitance (-35.7 $\mu$ F/s                                                                                                                                                                                                                                                                | 118        |

| <ul> <li>8.7 Comparison of the adaptive parameter identifier convergence when applied to the ideal model (Fig. 6.1) versus parasitic model (Fig. 8.6a)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8.6  | A simulation of an interleaved boost dc-dc converter incorporating switch and passive component parasitics and non-idealities is used to validate the robustness                                                                                                                                                                                        | 110        |

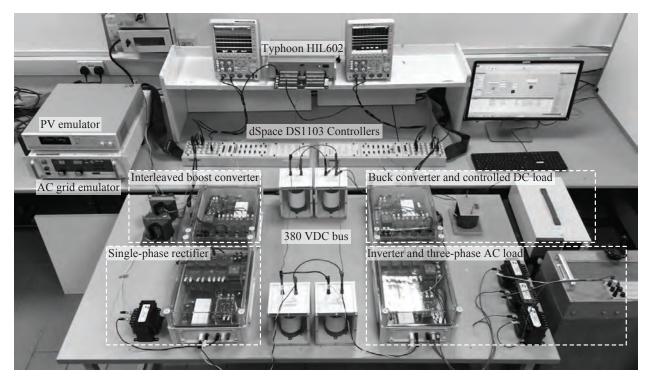

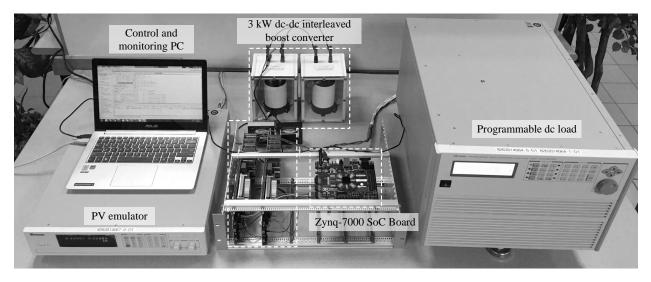

| <ul> <li>8.8 Photograph of the experimental testbed, including the interleaved dc-dc converter and the Zynq-7000 SoC board</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8.7  | Comparison of the adaptive parameter identifier convergence when applied to the                                                                                                                                                                                                                                                                         |            |

| 8.9 Experiment of adaptive parameter identifier tracking a step perturbation in ca-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8.8  | Photograph of the experimental testbed, including the interleaved dc-dc converter                                                                                                                                                                                                                                                                       |            |

| 1/0 $1/0$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ $1/1$ | 8.9  |                                                                                                                                                                                                                                                                                                                                                         | 121<br>123 |

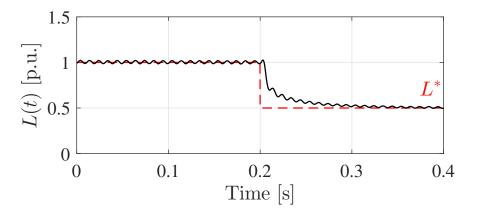

| 8.10 | Experiment of adaptive parameter identifier tracking a step perturbation in in-<br>ductance $L_1$ . Step perturbation at $t = 0.2$ s from $L$ to $0.5 L$ .              | 124 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

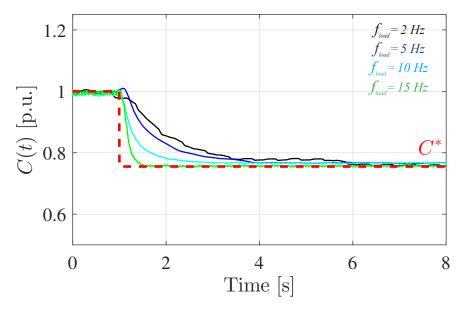

| 8.11 | Experiment of adaptive parameter identifier tracking step perturbations in capacitance $C$ for a set of $i_{load}(t)$ ripple frequencies: 2 Hz, 5 Hz, 10 Hz, and 15 Hz. |     |

|      | Step perturbation at $t = 1$ s from C to $0.65 C$ .                                                                                                                     | 124 |

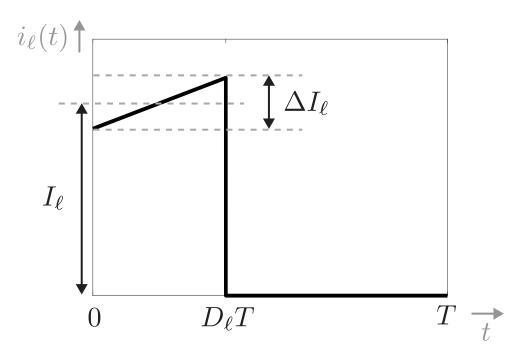

| A.1  | Time domain sketch of one period of $i_{\ell}(t)$                                                                                                                       | 147 |

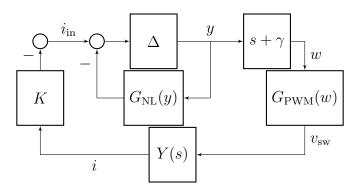

| C.1  | Block-diagram representation of interconnected system with the equivalent cou-                                                                                          |     |

|      | pled oscillator model dynamics (4.13) used in hardware implementation.                                                                                                  | 151 |

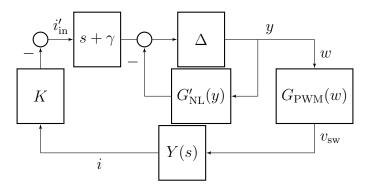

| C.2  | Block-diagram representation of interconnected system with the equivalent cou-                                                                                          |     |

|      | pled oscillator model dynamics (4.13) used in analysis.                                                                                                                 | 151 |

# List of Tables

| 3.1<br>3.2   | Parameters and components for numerical simulations and experimental proto-<br>type                                                                                  | 32  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | ter                                                                                                                                                                  | 45  |

| 4.1          | Specifications, parameters, and ratings for the experimental prototype                                                                                               | 64  |

| $5.1 \\ 5.2$ | Common failure modes in BIPV systems                                                                                                                                 | 76  |

|              | tronics systems.                                                                                                                                                     | 80  |

| 5.3          | A review of existing literature in FDI methods for multiple switch, open-phase, sensor, and passive element faults in power electronics systems.                     | 80  |

| 5.4          | Typical fault modes for capacitors (electrolytic, ceramic, and film) and inductors (air inductors, ferrites, and iron-core) in power electronics systems [80, 147].  | 83  |

| 6.1          | Possible open/close switch positions for the boost converter in continuous conduc-<br>tion mode.                                                                     | 85  |

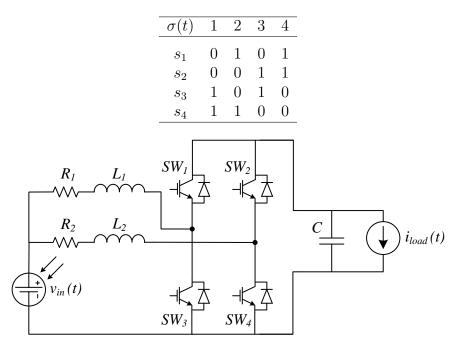

| 6.2          | Possible open/close switch positions for the interelaved boost converter in conti-<br>nous conduction mode.                                                          | 86  |

| <b>P</b> 1   |                                                                                                                                                                      |     |

| 7.1          | Component fault signature library.                                                                                                                                   | 97  |

| 7.2          | Sensor fault signature library.                                                                                                                                      | 98  |

| 7.3          | Simulation parameters for boost converter.                                                                                                                           | 99  |

| $7.4 \\ 7.5$ | Specifications and ratings for nanogrid testbed. $\dots \dots \dots$ | 103 |

| 1.0          | cation $(t_i)$                                                                                                                                                       | 108 |

| 8.1          | Simulation and experiment parameters.                                                                                                                                | 115 |

#### Acknowledgments