## **Design of Spectral Filtering Wireless Transmitters**

Bonjern Yang

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-226 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-226.html

December 1, 2021

Copyright © 2021, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Design of Spectral Filtering Wireless Transmitters

by

### Bonjern Yang

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Elad Alon, Chair Professor Borivoje Nikolic Professor Martin White

Fall 2019

## Design of Spectral Filtering Wireless Transmitters

Copyright 2019 by Bonjern Yang

#### Abstract

Design of Spectral Filtering Wireless Transmitters

by

Bonjern Yang

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Elad Alon, Chair

A frequency-flexible radio-frequency (RF) front end has long been desired, but faces a myriad of obstacles to its realization. In recent years, the use of switching power amplifiers (PA) as part of digital PAs and RF digital-to-analog converters (RFDACs) has become more common. The primary motivation of these RFDACs is to directly convert from digital baseband bits to RF output. This is useful in the realization of a frequency-flexible RF front end, but this is prevented by the generation of significant spectral emissions in the form of harmonics and quantization noise by RFDACs. These issues are both typically remedied with the usage of high-order fixed filters which are inherently not frequency flexible.

In this dissertation, we will discuss an approach to implement a frequency-flexible digital PA-based transmitter using programmable integrated filtering to suppress spectral emissions without the use of external filters. Two filtering techniques will be discussed, as well as their requirements and limitations. Additionally, design automation of core blocks within the transmitters using the Berkeley Analog Generator (BAG) framework will be discussed in detail. We will demonstrate two prototypes implemented in 65nm and 28nm processes achieving state of the art filtering performance at a peak power level of > 23 dBm across at least a 1 GHz - 2 GHz frequency range.

To my parents

# Contents

| $\mathbf{C}$ | ontents       |                                            |            |  |

|--------------|---------------|--------------------------------------------|------------|--|

| Li           | st of         | Figures                                    | iv         |  |

| Li           | st of         | Tables                                     | vii        |  |

| 1            |               | roduction                                  | 1          |  |

|              | 1.1<br>1.2    | State of the Art                           | 5<br>6     |  |

| 2            | Filt          | ering Power Amplifiers                     | 8          |  |

|              | 2.1           | Switched Capacitor Power Amplifier         | 8          |  |

|              | 2.2           | TX System Block Diagram                    | 11         |  |

|              | 2.3           | Filtering Techniques                       | 12         |  |

|              | 2.4           | Phase Resolution and Harmonic Cancellation | 20         |  |

|              | 2.5           | Resistance Mismatch and SCPA Linearity     | 22         |  |

|              | 2.6           | Carestian (IQ) Architecture                | 25         |  |

|              |               | 2.6.1 Nonlinearity from 25% Duty Cycle LOs | 28         |  |

|              | 2.7           | SCPA and Output Network Design             | 35         |  |

|              |               | 2.7.1 SCPA Design for Efficiency           | 36         |  |

|              |               | 2.7.2 SCPA Design for Linearity            | 44         |  |

|              | 2.8           | First Prototype Measurements (65 nm)       | 50         |  |

|              | 2.9           | Filtering Techniques and Output Network    | 58         |  |

|              | 2.10          | Revised TX System Block Diagram            | 66         |  |

|              | 2.11          | Revised Prototype Measurements (28 nm)     | 68         |  |

| 3            | $\mathbf{RF}$ | Circuit Generators                         | <b>7</b> 5 |  |

|              | 3.1           | SCPA Generator                             | 75         |  |

|              |               | 3.1.1 SCPA Unit Cell Generator             | 76         |  |

|              |               | 3.1.2 SCPA Array Generator                 | 80         |  |

|              | 3.2           | SCPA Generator for BAG 2.0                 | 81         |  |

|              |               | 3.2.1 SCPA Array Generator for BAG 2.0     | 84         |  |

|   |     | 3.2.2  | SCPA Column Driver Generator for BAG 2.0            | 87  |

|---|-----|--------|-----------------------------------------------------|-----|

|   |     | 3.2.3  | SCPA Unit Cell Generator for BAG 2.0                | 89  |

|   | 3.3 | Phase  | Interpolator Generator for BAG 2.0                  | 93  |

|   |     | 3.3.1  | Phase Intepolator Current DAC Generator for BAG 2.0 | 94  |

|   |     | 3.3.2  | Phase Interpolator Integrator Generator for BAG 2.0 | 100 |

|   |     |        |                                                     |     |

| 4 | Con | clusio | n                                                   | 104 |

|   | 4.1 | Summ   | ary                                                 | 104 |

|   | 4.2 | Key C  | Contributions                                       | 104 |

|   | 4.3 | Future | e Work                                              | 106 |

|   |     |        |                                                     |     |

# List of Figures

| 1.1  | Effects of TX quantization noise on nearby channels                                  |

|------|--------------------------------------------------------------------------------------|

| 1.2  | Conceptual RFFPGA top level block diagram                                            |

| 2.1  | SCPA unit cell schematic with device stacking and buffers                            |

| 2.2  | Ideal SCPA operation                                                                 |

| 2.3  | SCPA summation operation                                                             |

| 2.4  | SCPA v1 top level block diagram                                                      |

| 2.5  | Harmonic cancellation block diagram                                                  |

| 2.6  | Gilbert-cell based phase interpolator                                                |

| 2.7  | HD3 reduction with and without quantization                                          |

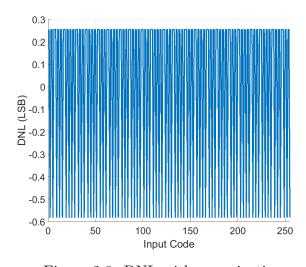

| 2.8  | DNL with quantization                                                                |

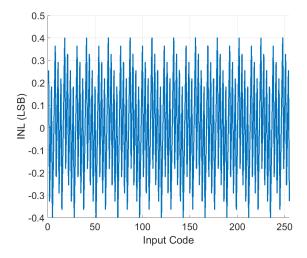

| 2.9  | INL with quantization                                                                |

| 2.10 | Harmonic cancellation block diagram                                                  |

| 2.11 | Mixed signal filter block diagram                                                    |

| 2.12 | Delay line schematic                                                                 |

| 2.13 | Ideal HD3 reduction vs phase shift                                                   |

| 2.14 | Ideal phase and phase step for a gilbert-cell based PI                               |

| 2.15 | SCPA operation during across a single period                                         |

| 2.16 | Fundamental amplitude and phase vs input code with resistance mismatch 25            |

| 2.17 | Fundamental amplitude across input code for matched resistance and a mis-            |

|      | matched resistance case                                                              |

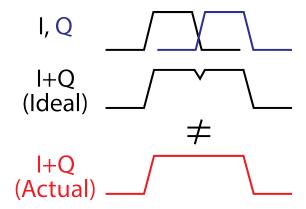

|      | IQ input combining scheme with 25% duty cycle                                        |

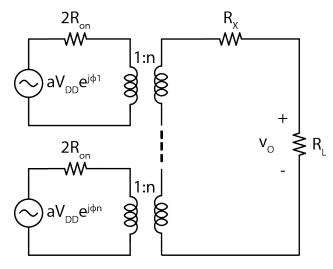

| 2.19 | Schematic for computing TX efficiency                                                |

| 2.20 | Output waveforms of PAs using 25% and 50% LOs                                        |

| 2.21 | 25% / $50%$ duty cycle nonlinearity                                                  |

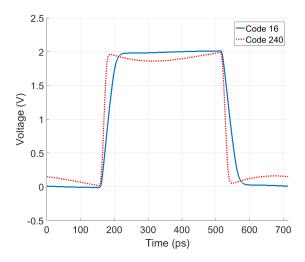

| 2.22 | Simulated SCPA drain voltage vs time for two codes                                   |

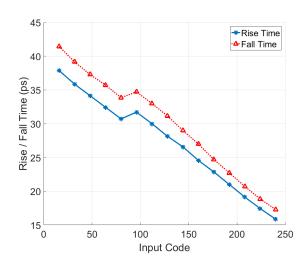

| 2.23 | Simulated SCPA drain rise and fall time across codes                                 |

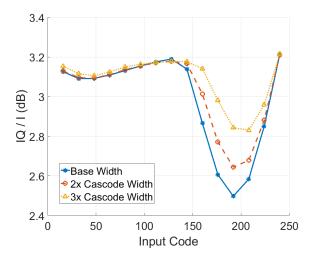

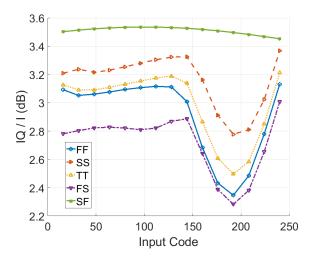

| 2.24 | Simulated IQ / I vs codes for different sizing                                       |

| 2.25 | Simulated IQ / I vs codes for across corners                                         |

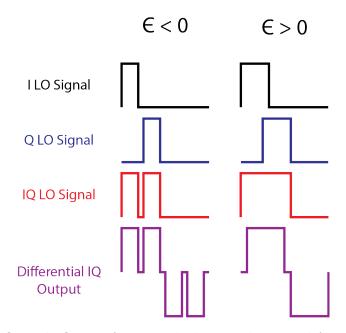

| 2.26 | I, Q, and IQ waveforms with duty cycle control for $\epsilon < 0$ and $\epsilon > 0$ |

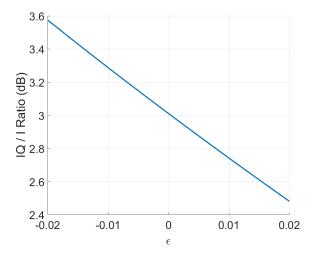

| 2.27 | IQ / I ratio vs duty cycle modification $\epsilon$                                   |

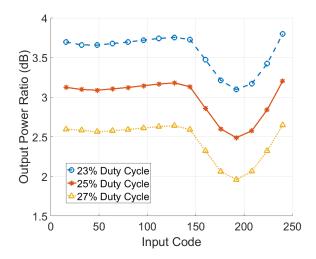

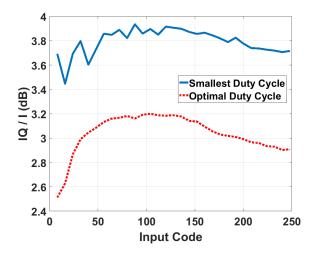

| 2.28 | Simulated IO / I ratio across input code 34                                          |

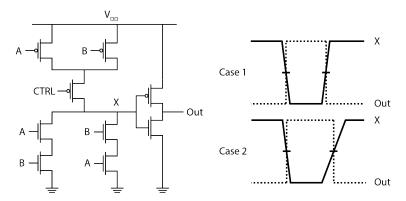

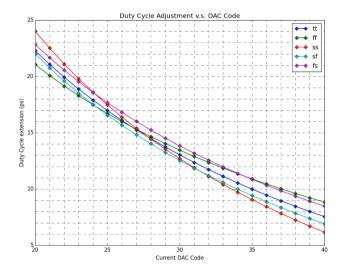

|      | Duty cycle control circuit with waveform diagrams                                      | 35 |

|------|----------------------------------------------------------------------------------------|----|

| 2.30 | Duty cycle extension versus code                                                       | 35 |

| 2.31 | Schematic to compute output current and resistive losses                               | 37 |

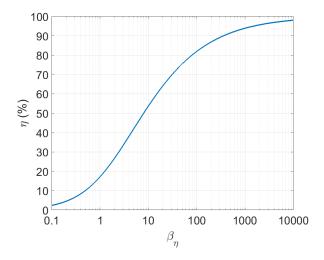

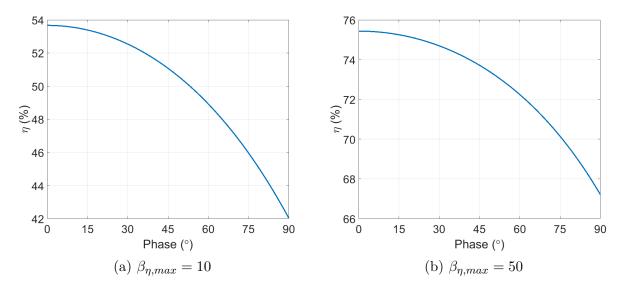

| 2.32 | Maximum system efficiency vs $\beta_{\eta}$                                            | 40 |

| 2.33 | Maximum system efficiency vs 2nd PA phase for a fixed peak $\beta_{\eta}$              | 41 |

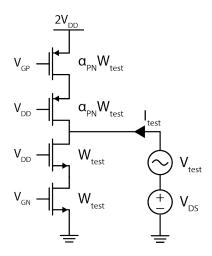

| 2.34 | Schematic to simulate $R_{on}$                                                         | 42 |

|      | Schematic to simulate $C_{sw}$                                                         | 42 |

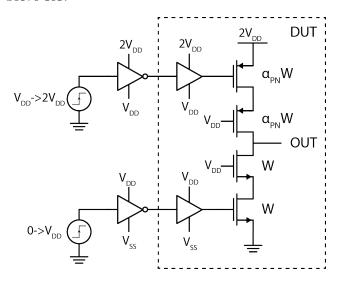

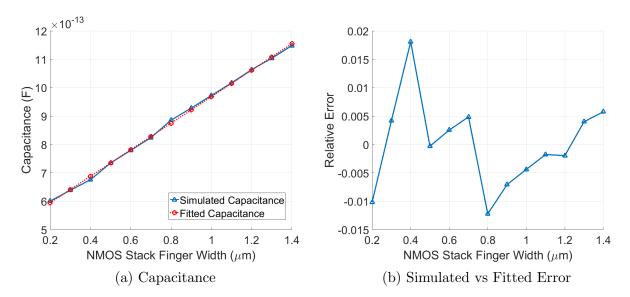

| 2.36 | Simulated vs Fitted Capacitance vs Width for $nf = 32 \dots \dots \dots$               | 43 |

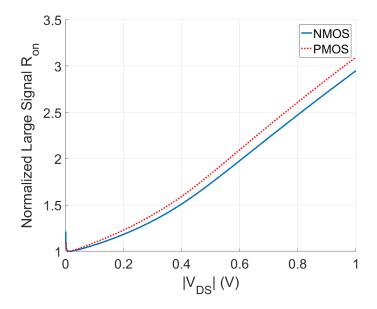

| 2.37 | Normalized large signal $R_{on}$ vs $V_{DS}$                                           | 45 |

| 2.38 | Simulated HD3 vs phase shift                                                           | 46 |

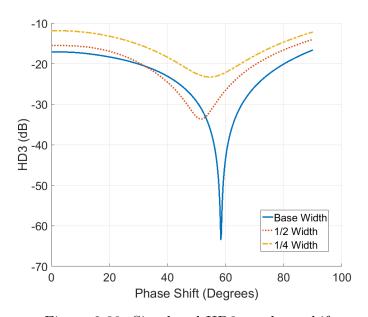

| 2.39 | Simulated SCPA drain voltage vs time (1 period)                                        | 47 |

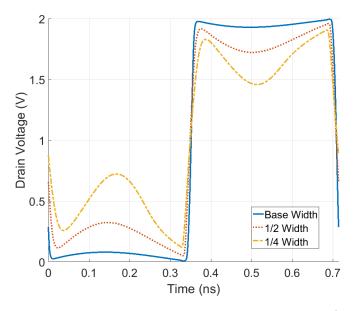

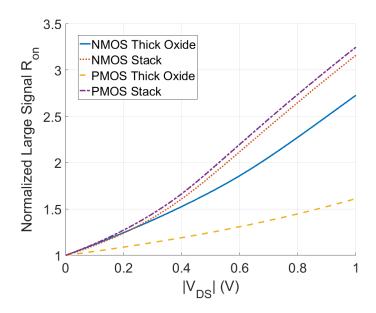

| 2.40 | Normalized large signal $R_{on}$ vs $V_{DS}$ for thick oxide and 2-stack               | 48 |

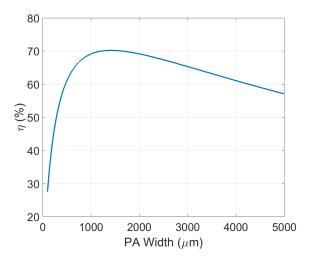

| 2.41 | System efficiency vs PA array width with $\beta_{\eta} = 31.5$                         | 49 |

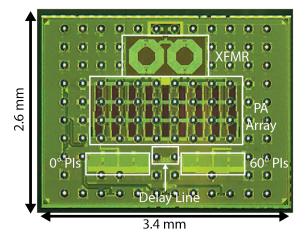

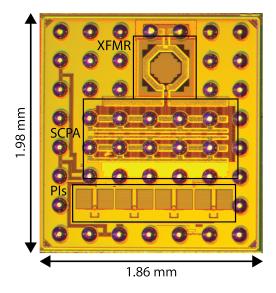

| 2.42 | TX v1 die photo                                                                        | 50 |

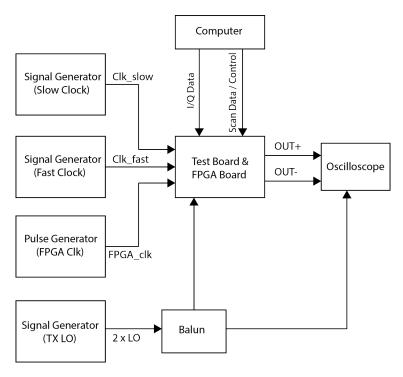

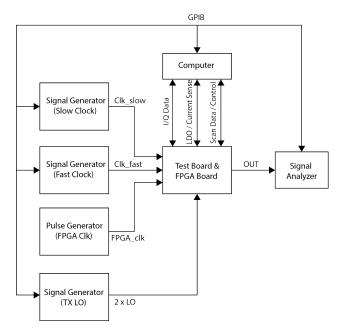

| 2.43 | Measurement block diagram                                                              | 51 |

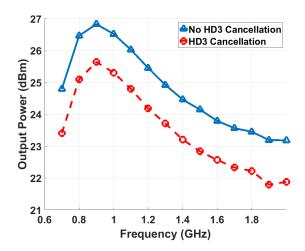

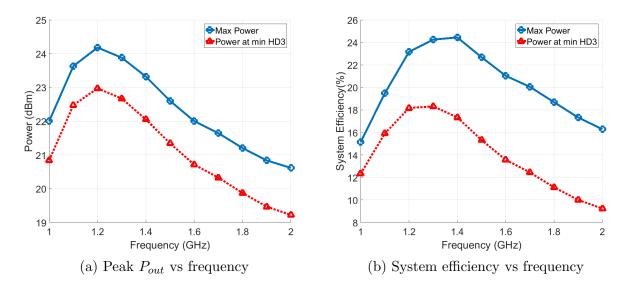

| 2.44 | Peak $P_{out}$ vs frequency                                                            | 51 |

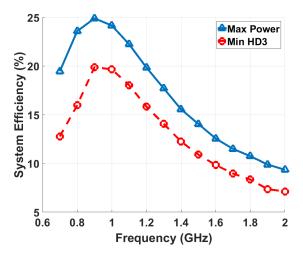

| 2.45 | System efficiency vs frequency                                                         | 52 |

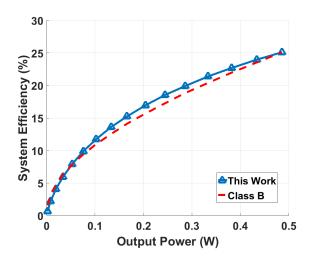

| 2.46 | System efficiency vs code                                                              | 52 |

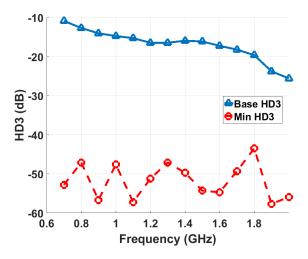

| 2.47 | HD3 vs frequency                                                                       | 53 |

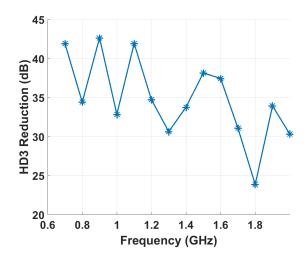

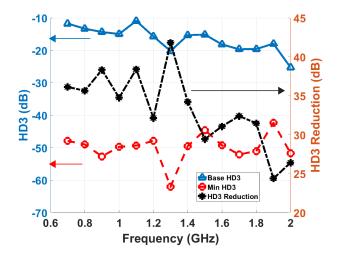

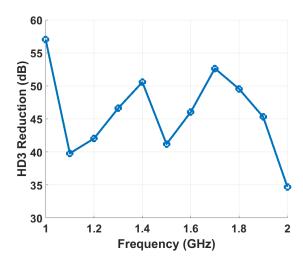

| 2.48 | HD3 reduction vs frequency                                                             | 53 |

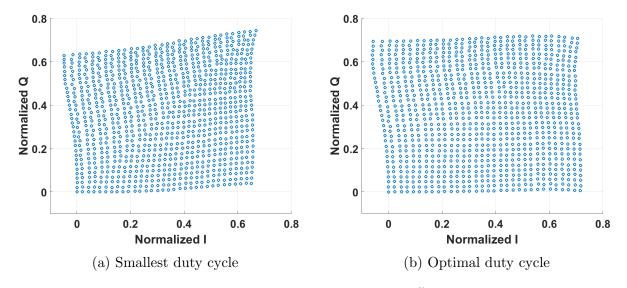

| 2.49 | IQ / I ratio vs code for different duty cycle settings                                 | 54 |

| 2.50 | Top right constellation quadrant with different duty cycle settings                    | 54 |

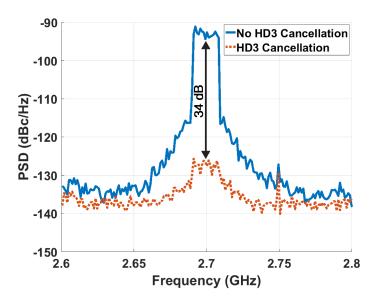

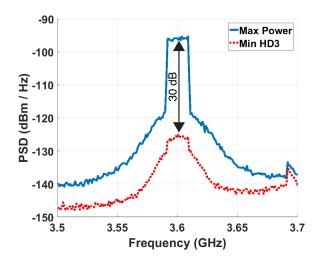

| 2.51 | Normalized $3^{rd}$ harmonic spectrum with HD3 cancellation enabled, $f_{LO} = 900MHz$ | 55 |

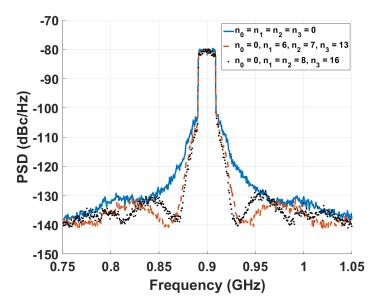

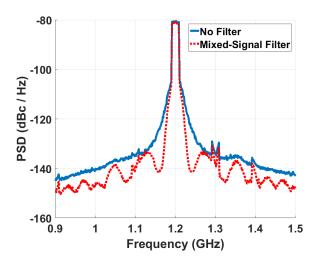

| 2.52 | Normalized spectrum with mixed-signal filtering enabled with $f_{LO} = 900MHz$ .       | 56 |

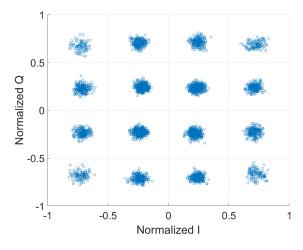

|      | EVM measurement of 16QAM constellation at 125 MS/s data rate                           | 56 |

| 2.54 | Output network for 1st board for SCPA v1                                               | 58 |

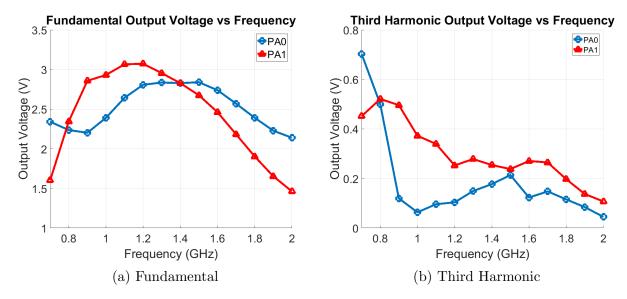

| 2.55 | PA array transfer functions                                                            | 59 |

|      | Setup for measured vs perfectly summed HD3 reduction                                   | 60 |

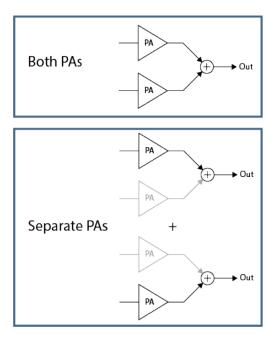

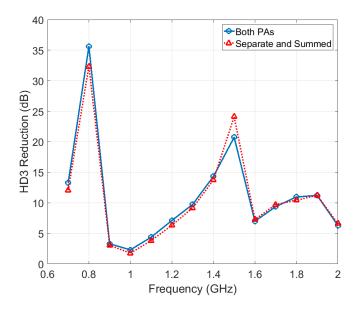

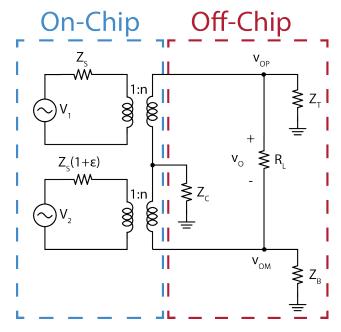

|      | HD3 reduction for both PAs vs separate and summed PAs                                  | 61 |

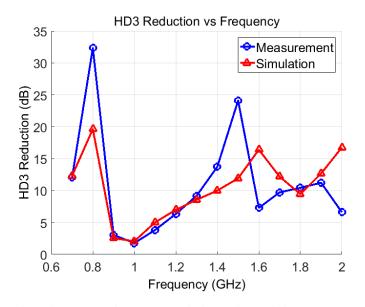

| 2.58 | Simulated HD3 reduction with board model vs measured HD3 reduction                     | 61 |

|      | Series-stacked transformer summing                                                     | 62 |

| 2.60 | Output network for 2nd board for SCPA v1                                               | 63 |

| 2.61 | HD3 reduction vs frequency for 1st board with balun                                    | 63 |

| 2.62 | Drain combining with a series-stacked transformer                                      | 64 |

| 2.63 | Drain combining with a single transformer                                              | 65 |

| 2.64 | Simulated HD3 reduction for simple transformer drain combining with different          |    |

|      | output networks with single ended output                                               | 66 |

| 2.65 | TX v2 board output network                                                             | 66 |

| 2.66 | TX v2 top level block diagram                                                          | 67 |

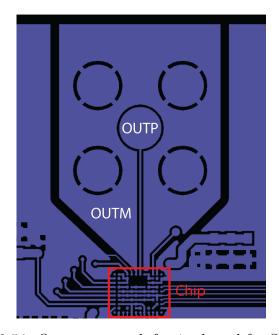

|      | TX v2 Die Photo                                                                        | 68 |

| 2.68 | TX v2 testing block diagram                                                            | 69 |

|      | CW output power and efficiency vs center frequency                                     | 00 |

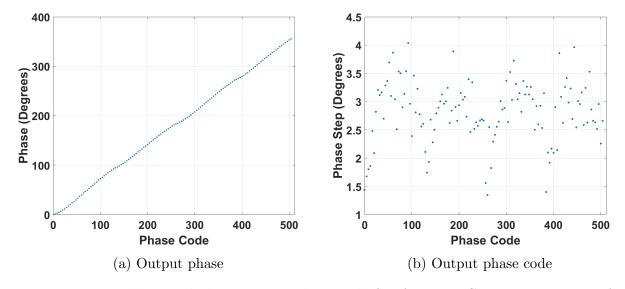

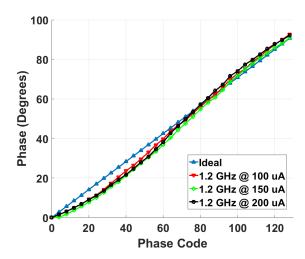

| 2.70 | Phase and phase step vs phase code for $f_{LO}=1.2GHz,I_{PI,int}=100\mu A$   | 70  |

|------|------------------------------------------------------------------------------|-----|

| 2.71 | Output phase vs phase code for $f_{LO} = 1.2GHz$ with different $I_{PI,int}$ | 71  |

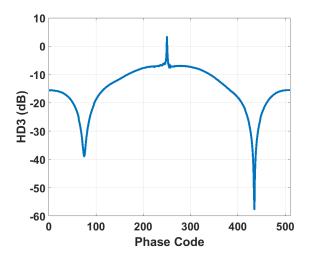

| 2.72 | HD3 vs phase code with $f_{LO} = 1.2GHz$ , $I_{PI,int} = 200\mu A$           | 72  |

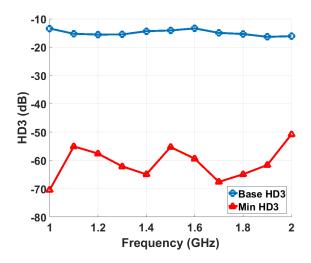

| 2.73 | CW HD3 for TX v2                                                             | 72  |

| 2.74 | CW HD3 Reduction vs $f_{LO}$ for TX v2                                       | 73  |

| 2.75 | Normalized spectrum of $3^{rd}$ harmonic with 20 MHz LTE data                | 73  |

| 2.76 | Normalized spectrum mixed-signal filtering with 20 MHz LTE data              | 74  |

| 3.1  | SCPA unit cell schematic                                                     | 76  |

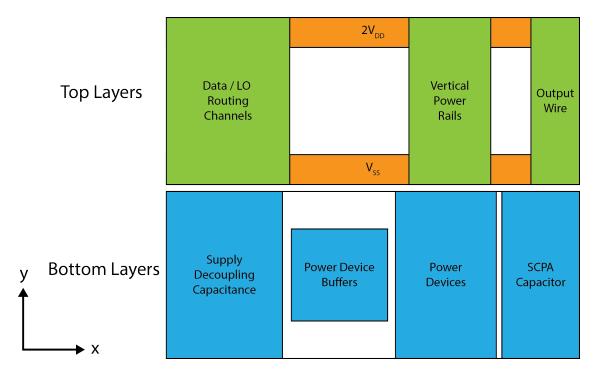

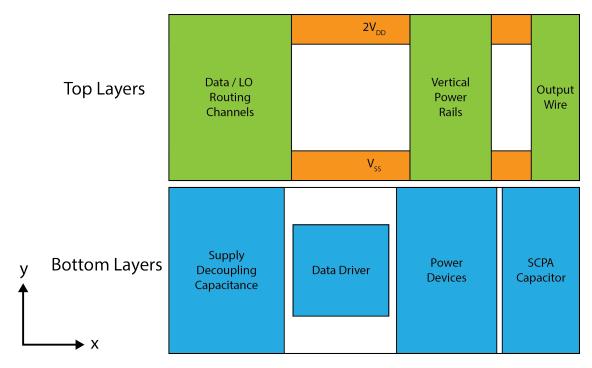

| 3.2  | SCPA unit cell layout floorplan split into top and bottom layers             | 77  |

| 3.3  | Unit capacitor layouts for normal (left) and dummy (right) cells             | 79  |

| 3.4  | SCPA unit cell layout instance                                               | 79  |

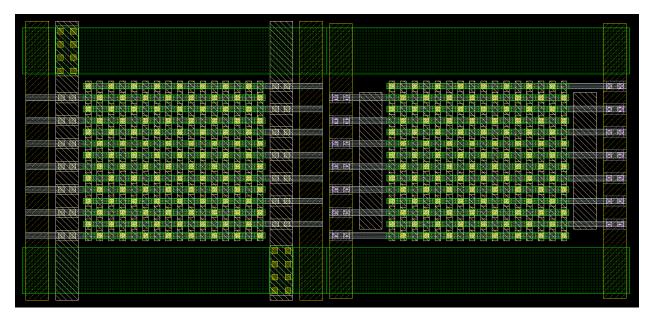

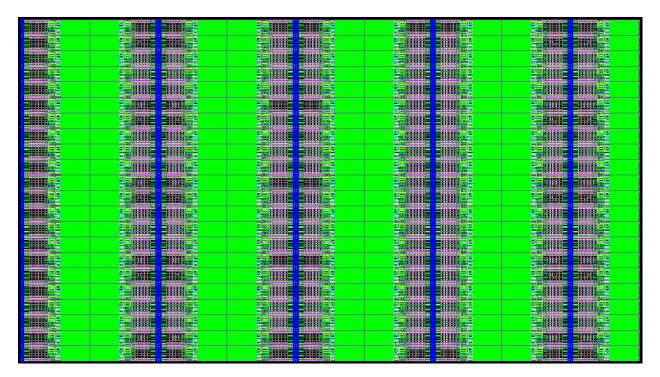

| 3.5  | SCPA array layout instance                                                   | 81  |

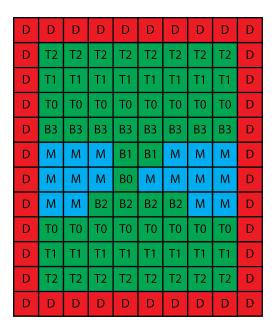

| 3.6  | SCPA array pattern file                                                      | 82  |

| 3.7  | frac_width_used values for SCPA unit cells                                   | 82  |

| 3.8  | SCPA v2 unit cell schematic                                                  | 84  |

| 3.9  | SCPA array pattern text files                                                | 85  |

| 3.10 | V I                                                                          | 86  |

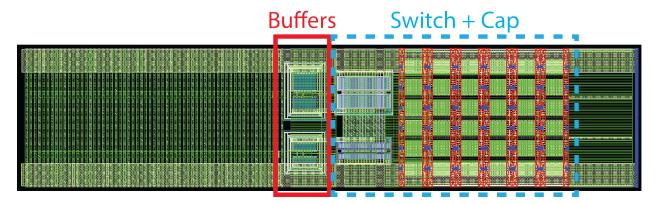

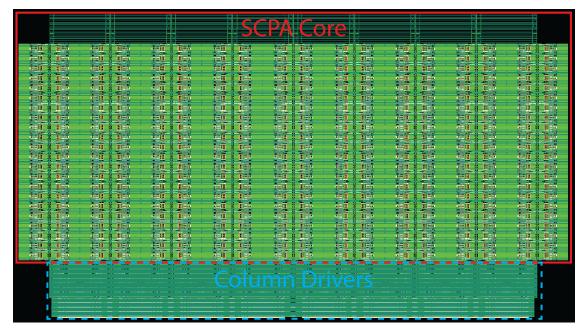

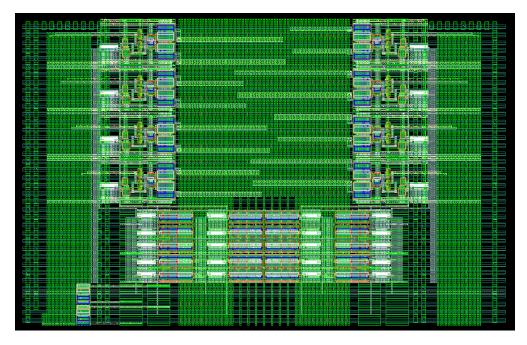

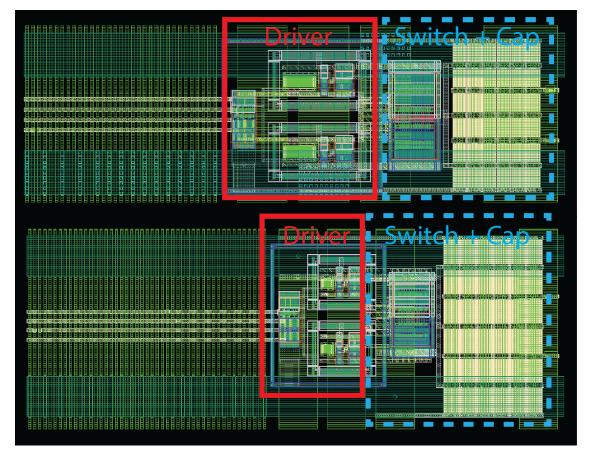

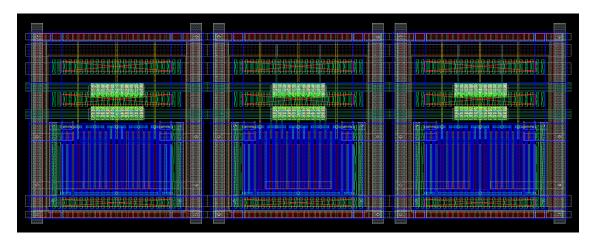

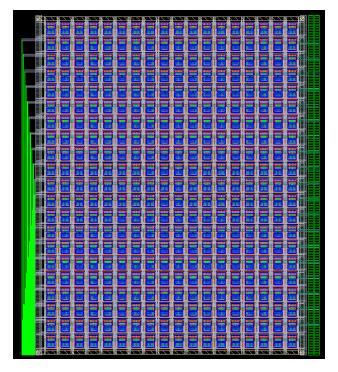

| 3.11 | SCPA top level layout instance with core and column drivers                  | 87  |

|      | SCPA column driver layout instance                                           | 88  |

| 3.13 | Column driver data driver schematic                                          | 88  |

| 3.14 | Column driver LO driver schematic                                            | 89  |

| 3.15 | SCPA unit cell layout floorplan split into top and bottom layers             | 90  |

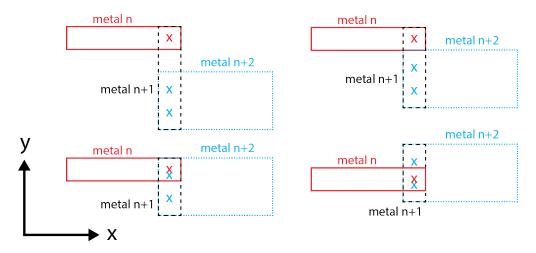

| 3.16 | Technique to connect two wires on the same layer (direction)                 | 91  |

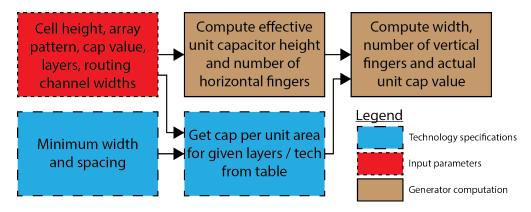

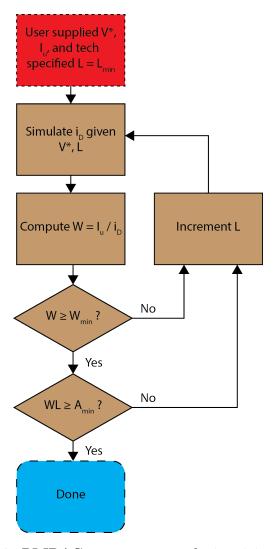

| 3.17 | Capacitor sizing flowchart                                                   | 92  |

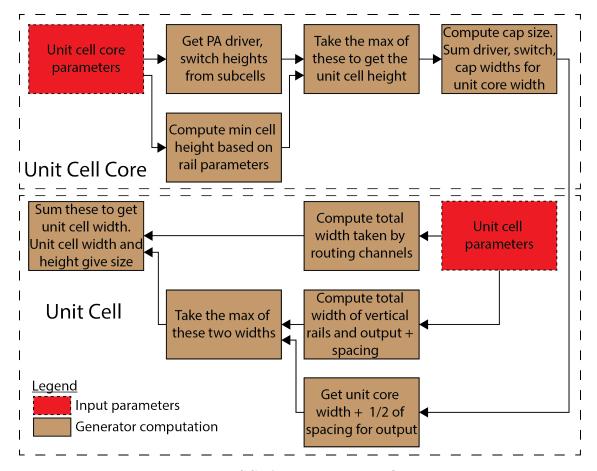

| 3.18 | SCPA unit cell sizing flowchart                                              | 94  |

|      | SCPA unit cell layout instances with two different set of parameters         | 95  |

| 3.20 | Phase interpolator core                                                      | 96  |

|      | Phase interpolator input integrator                                          | 96  |

| 3.22 | Test circuit to simulate $i_D$ vs $V^*$                                      | 97  |

|      | PI IDAC current source device sizing flowchart                               | 98  |

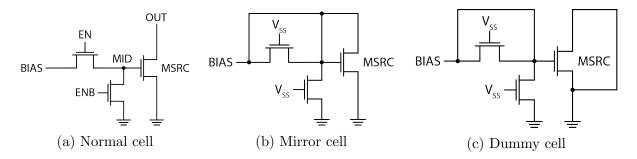

| 3.24 | PI IDAC normal, mirror, and dummy unit cells from left to right              | 99  |

| 3.25 | PI IDAC patterns with different number of bits and bias rows                 | 100 |

| 3.26 | PI IDAC pattern with multi-row inputs                                        | 101 |

| 3.27 | PI IDAC layout                                                               | 102 |

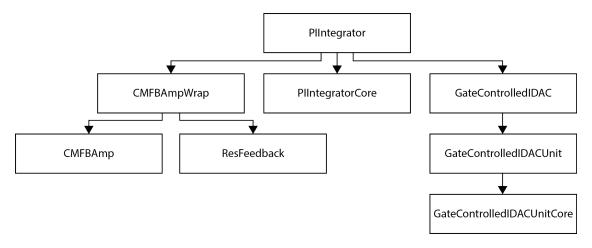

| 3.28 | PI integrator layout template hierarchy                                      | 102 |

| 3.29 | PI integrator bias IDAC unit cell types (NMOS)                               | 103 |

# List of Tables

| 2.1 | HD3 reduction vs number of bits                             | 21 |

|-----|-------------------------------------------------------------|----|

| 2.2 | Simulated HD3 reduction for different sizings               | 46 |

| 2.3 | Simulated peak drain voltage swing for NMOS and PMOS stacks | 46 |

| 2.4 | Comparison table for the TX v1                              | 57 |

#### Acknowledgments

Graduate school has been a longer and more arduous journey than I could have ever imagined. It's been a thoroughly humbling experience constantly interacting with extremely intelligent and hardworking people on a regular basis, but the same people have pushed me to grow both as a researcher and a person. I'd like to take this space to convey my gratitude towards all these people and those who supported me throughout my graduate studies.

First, I would like to thank my advisor Elad Alon. My path towards conducting research began when I first approached Elad during office hours to ask for research work as an undergraduate. I didn't think at the time that it would lead to years of working together. I'm always impressed with how quickly you can assess a problem that you've never seen before and come up with a reasonable solution, or at least something that would lead to a solution. There were at least a few times where I hit a wall in research which was resolved by one of your suggestions. Lastly, I'd like to thank you for being encouraging and keeping my spirits up even when I felt like I wasn't making meaningful progress. After writing this dissertation, I can definitely look back and be proud of what I accomplished over these last 7.5 years, largely in part to the research guidance you've given me.

Borivoje Nikolic and Ali Niknejad both provided me invaluable advice both in research topics and more broadly for my future career, as well as serving on my quals committee. I'd especially like to thank Bora for providing extra advising when I really needed it, especially in the final stretch of my PhD, and for serving on my dissertation committee as well. Both professors gave me valuable alternative perspectives, pushing me to become a more well-rounded researcher. I would also like to thank Professor Martin White for serving on my quals and dissertation committees.

Next, I'd like to acknowledge the people who've contributed most directly to the chips that I've worked on, Nai-Chung Kuo and Eric Chang. Nai-Chung is simultaneously one the hardest working and kindest people I've met in graduate school. The fact that he is always willing to help others even when he is swamped with his own work is truly admirable and reflects upon his character. I appreciate all the discussions and help he's given me on various RF topics and measurement methodologies even long after our collaboration on the first RFFPGA chip.

Eric is the person I've met who most closely embodies that mythical engineer who does 10 times the work of the average engineer. The first version of this transmitter would have been significantly delayed without your contributions. The story that best encapsulates working with you was how after one day of using the existing measurement framework for testing the first chip, you went home and completely rewrote a much better framework in a single night. It was so useful I even continued to use to test the second version of the transmitter. Thanks for fixing all of my issues with BAG in a speedy fashion, and for all the random trivia you've dispensed upon me throughout the years.

I want to thank Andrew, Lorenzo, Emily, Meng, Angie, and Charles for their help in tapeouts either in reusing their blocks, measurement setup, or overall general aid. Special thanks to Andrew for helping me, along with many other graduate students, in the deep, dark hours leading to the tapeout deadline, whether it was through helping to run tools or providing another set of eyes to debug last minute issues.

I would not have made it through graduate school without the friends I've made along the way. First, I want to thank Sameet and Phil for being loyal friends from undergraduate through graduate school. I always could rely on you two to have discussions about anything, whether it be technical discussion or rambling about life struggles. The countless hours of talking and laughing about incredibly inane topics are irreplaceable memories that took the edge off of the stress of graduate school. I know there's been a lull recently, but I look forward to years of continued friendship.

Nathan, I couldn't have asked for a better cubicle neighbor. Not only have you helped me out countless times with research, you've been a great friend who bore all my venting. Even through your own struggles, I could rely on you to help me out in times of need, and I hope I can return the favor in the future.

Ozzy, thanks for being a great friend and my designated basketball (watching) buddy. Our technical discussions throughout the years has been extremely helpful, and I am indebted to you for your help on the second version of the transmitter. Thanks for all the moral support, and dealing with (or enjoying) my random rants. I appreciate the weirdness you bring to BWRC and into my life, even if I don't participate in your schemes often.

Luke, you are an odd person in the best possible way. It's been great discussing music with you throughout the years, and it's definitely helped to push the boundaries of what I enjoy, even if not everything you suggest clicks. Your out of the box thinking rubbed off on me just a little bit, making me a little more open to very outwardly outlandish ideas.

Thanks to the Antonio, John, Emily, Keertana, Krishna, and George for being part of the lunch squad and contributing to a variety of odd lunch discussions. Being able to lighten things up everyday kept me chugging along. I'd like to thank my BWRC colleagues Ali Moin, Nima, Sashank, Pengpeng, Seobin, Zhongkai, Yi-An, Filip, Nick, Sean, Kourosh, Ayan, and Bob for various technical discussions and their friendship.

I may not have even been on this path if it wasn't for my graduate student mentors Lingkai Kong and John Crossley. Thank you for taking a confused undergrad under your wing and nurturing my interest in research, eventually leading me to continue into graduate school. I am thankful for all the advice in both research and navigating graduate school in general. Lingkai, I'm glad I listened to your advice all those years back to stick with BAG even though I've never been a primary developer, it's been amazing to see it grow and move closer to the lofty initial ideal of what it could be. I would also like to thank Hanh-Phuc, Alberto, Matt Spencer, Yue, Yida, and Chintan for being welcoming and helpful seniors in the EEIS group during my undergraduate and early PhD years.

I want to thank the BWRC staff for doing an incredible amount of work behind the scenes to ensure that students can focus on research. In particular, the support of Candy, Ajith, and James have been absolutely critical to me finishing my graduate studies, whether it came in the form of pushing and organizing tapeouts, helping with tech and lab issues right before a major deadline, or miscellaneous issues in the case of Candy. I think the three of you have looked out for the students far beyond what anyone could reasonably expect. I'd

also like to thank Fred, Sarah, Olivia, Yessica, Mikaela, Bira, Brian, and Greg for helping to keep BWRC afloat.

I'd like to thank Aritra Banerjee for the helpful discussions regarding cellular transmitters, as well as providing the LTE data I've used for measurements of both chips. The insight from someone currently in industry was extremely valuable, and gave me a sense of validation of my research work. Also on the industry side, I'd like to thank Simone Gambini for mentoring me during my internship at Apple. Thanks for making my first experience working a pleasant one, and for giving an idea of what to expect working in industry.

My graduate studies would not have been possible without the funding provided by DARPA RFFPGA, DARPA CRAFT, and the GAANN fellowship.

I want to thank two friends outside of BWRC who were constants in my life, and helped me through my toughest times in graduate school. Ryan, we've known each other and lived together for so many years that you're essentially family to me. Those who know me know how seriously I value family, and how much weight that statement carries. Despite our divergent paths in life, I always appreciated how we stay connected based on our starting points. Your activism in undergrad and your ongoing focus on helping underserved communities inspired me to learn more about my own roots. I wish you luck in completing your PhD, and hope you'll be back in California soon.

Steven, you're one of my oldest and most loyal friends. Thank you for constantly taking trips to come hang out throughout the years. I know I don't make enough of an effort to stay connected with friends, so thank you for bearing with that and putting in the work to keep our friendship strong. The most extreme example of this when you flew to Japan to sit in on my VLSI talk to show your support. You did this without being prompted - if that's not true friendship, I don't know what is.

I want to thank my extended family and my brothers for their support. Wilton, thanks for always being my rival in fighting games, and being my equal, even though I'm the older brother. Thanks for taking care of the family the last few years - hopefully soon I can step in and help out. Hans, I'm always impressed with how sharp your wit is. I'm excited to read your future works, whether it be in the form of a novel or a script. Hudson, it's been great seeing you grow into a passionate and principled young man. I know you're gonna reach your dream of making amazing video games. The three of you drive me to be the best person I can be - I have to set the standard high as the eldest brother.

None of this would have been possible without the support of my parents. Despite having a tough life, you fought through it to carve out a decent life for us. Growing up poor wasn't easy, but you did everything you could to make it feel alright. Thanks Dad, for being my role model growing up. You worked hard every day for the sake of our family so that we could live a better life. Thanks Mom, for dealing with four lazy boys. I don't know how you didn't go crazy dealing with our antics, but you did it so we could focus on education for the final goal of living a more comfortable life than you did. I know you wished you could have completed your education, but I hope my PhD will be an adequate substitute. It would have been impossible to get through graduate school without the constant and unwavering love and support from the both of you. I hope I've made you proud.

# Chapter 1

## Introduction

The current cellular landscape of the world consists of a plethora of coexisting standards with varying bandwidths, center frequencies, and specifications. Standards from different generations such as 3G (GSM) and 4G (LTE) exist within the same regions despite starkly different requirements in output power and channel bandwidth. Even within a single standard such as long term evolution (LTE), frequency bands of operation can vary from country to country. For example, LTE band B2, centered at 1900 MHz, is used in the USA and not the UK, while LTE band B7, centered at 2600 MHz, is used in the UK and not the USA [1]. This means that the same product will be designed with different hardware for different parts of the world, increasing engineering costs. The ubiquity of smart phones and the powerful functionality they provide also requires the inclusion of hardware supporting non-cellular standards such as WiFi and Bluetooth.

It makes sense to have separate radios for cellular, WiFi, and Bluetooth so they can operate simultaneously. However, there may even be multiple cellular radios for extra coverage and functionality, such as if the phone is intended to support multiple standards like CDMA and LTE. All of these additional radios increase the overall cost of the system, since separate hardware will be required to implement a radio compliant with each standard.

Each of these radios include a transmitter which will generate spectral emissions, primarily harmonics and quantization noise, which must be suppressed in order to meet spectrum mask requirements. This is typically done using a fixed, high-order passive filter, such as surface acoustic wave (SAW), bulk acoustic wave (BAW), or film bulk acoustic resonator (FBAR). These filters have very good out of band rejection, but are physically bulky and add insertion loss. These filters are relatively large, comparable in size to the TX integrated circuits (IC). Two examples covering different LTE bands measure 3 mm x 3 mm x 1.02 mm [2] and 1.1 mm x 1.4 mm x 0.85 mm [3]. These also add 2.0 dB and 2.3 dB of insertion loss respectively. Since these filters are not configurable, each new band will require a filter in addition to the transmitter ICs, increasing the cost and complexity of the product.

The goal of DARPA's RFFPGA program was to propose commercial and government solutions which would tackle the issue of many different standards by implementing a single design which could be reconfigured to meet different standards. Our approach to achieving

this configurability is to use a wideband digital PA combined with integrated, programmable filtering techniques to reduce harmonics and quantization noise. The purpose of the wideband PA is to allow for operation across a wide frequency range using a single TX. An integrated solution to the spectral issues is needed to avoid the bulky, off-chip filters. We will define a digital PA and its benefits, as well as their drawbacks in generating strong harmonics and quantization noise.

Digital PAs have become increasingly attractive in recent years due to advances in semi-conductor processes, with many works demonstrating competitive results [4][5][6][7][8][9]. The core of a digital PA is a switching PA topology, which requires a square wave input with relatively sharp edges, or short rise and fall times. Slow edge rates will degrade efficiency or even fundamentally alter operation in the extreme case. Improved transistors in modern CMOS processes can easily generate these square waves at cellular frequencies, enabling the operation of efficient digital PAs. Transmit data is generally digitized for ease of use, allowing for easy modification of input levels as well as bandwidth. Digital PAs also combine DAC and PA functionality into a single block, directly converting from digital bits to RF output, while systems with linear PAs require a separate DAC.

However, these digital PAs have two major issues when it comes to spectral emissions: harmonics and quantization noise. Digital PAs generate very strong harmonics due to fundamentally operating as switching PAs. Switching PAs typically operate by generating square waves either in voltage or current which drives a tuned load to achieve a sinusoidal output. A square wave x(t) with amplitude  $\alpha$  can be written as a sum of harmonically related sinusoids with Fourier series decomposition (Eq. 1.1). The  $k^{th}$  harmonic in a square wave only falls off as 1/k in voltage relative to the fundamental, which places strict requirements on the output network. For example, without any output filtering, the  $3^{rd}$  harmonic is only 9.5 dB lower than the fundamental.

$$x(t) = \frac{\alpha}{j\pi} \sum_{|k| \text{ odd}}^{\infty} \frac{e^{jk\omega_0 t}}{k} = \frac{2\alpha}{\pi} \sum_{k=1,3,5,\dots}^{\infty} \frac{\sin(k\omega_0 t)}{k}$$

$$(1.1)$$

This is a major issue in our case since we cannot rely on the output network alone to suppress the harmonics since we are opting to implement a wideband PA. A different and programmable solution is required to suppress these harmonics.

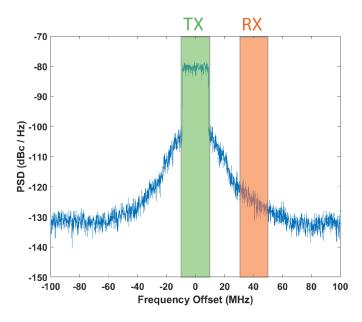

Quantization noise in digital PAs is generated due to DAC behavior, and is a consequence of the input data being digital. This quantization noise is an issue for nearby out-of-band channels, and could potentially desensitize receivers in these bands in extreme cases. The plot in Fig. 1.1 shows a case in which the quantization noise from a TX can bleed into a receiver (RX) channel spaced 40 MHz away. The quantization noise floor can be lowered either by adding additional bits to the digital PA or using a larger oversampling ratio, but this is very expensive from a power perspective. If we know what frequency band a nearby receiver may be operating in, it can be more energy efficient to reduce the quantization noise only in that band.

Figure 1.1: Effects of TX quantization noise on nearby channels

Our solution to these two problems of harmonics and quantization noise is to use filtering techniques which divide the PA into smaller pieces, driving each piece with different input signals, and combines the pieces at the output. Depending how the input signals are modified, different parts of the spectrum can be cancelled. We will implement two types of filtering using this general technique, which we will call harmonic cancellation and mixed-signal filtering. These notch out the harmonics and specific bands of nearby spectrum, respectively. In particular, we will focus on the third harmonic since it will be the largest harmonic in our differential TX. Both filtering techniques are frequency flexible, meaning they are able to operate across a wide frequency range, and are programmable on chip. These do not depend on off-chip components to operate, and all our prototypes do not use external components in the output network.

Another reason digital PAs were chosen were due to how technology scaling-friendly they are. These advanced processes give us transistors with better switching performance, but come with the drawback of rapidly growing design complexity. In addition to this, a great deal of effort is expended porting designs from one process to another. Design automation is critical in helping to manage this growing design complexity, which is already commonplace in the case of large scale digital design [10]. This is much less common with regards to analog, mixed-signal, and RF design, with much design and layout still being done completely manually. Several attempts have been made at trying to automate analog design [11][12][13], but in our case we felt the generator-based approach of Berkeley Analog Generator (BAG) [14][15] fit our needs best. Originally, this framework was designed with the goal of process portability in mind, which was further refined in later versions.

BAG is not intended to be analog synthesis, but is a framework in which users can

codify their designs into schematic and layout generators written in the Python programming language. Once complete, these generators take in user parameters to generate specific instances of these circuits. These generators have been used as key parts of fabricated prototypes, including serial links [16][17] and RF transceivers [18] across 16 nm and 65 nm processes. The latter is the first RFFPGA chip prototype which had the PA layout generated by BAG. This first chip is not the focus of this work, but we will give background on it to motivate the use of design automation in this work.

The initial approach for the first RFFPGA system was to create a transceiver capable of operating from 800 MHz - 6 GHz. This was to be done by splitting this into three bands of 800 MHz - 1.5 GHz, 1.5 GHz - 3 GHz, and 3 GHz - 6 GHz, with each band covered by a wideband PA. These would then be connected to an interposer containing a transformer for each frequency band (1.2). Optimizing each PA for each band would require significant effort, so the approach we took was to build a single BAG generator and supply it with three sets of parameters to generate a different instance for each band. Writing a generator is more effort than manually generating a single instance of a PA, but the generator saves time and effort once multiple differing instances are required, such as in this case. In the end, the first RFFPGA system [18] consisted of only a single chip used for multiple bands instead of multiple chips with different PA designs, but a fully functioning class  $D^{-1}$  PA generator was implemented and used to create the layout of the PA used in this single chip.

Figure 1.2: Conceptual RFFPGA top level block diagram

For this work, our primary reason for using BAG is to allow more rapid design iteration. The primary goal in terms of design automation is to capture the core PA's design in schematic and layout generators capable of implementing a variety of instances based on sets of parameters provided by the user. Other key blocks are also automated using BAG, which will be discussed in detail. The usage of BAG also allows for design reuse of smaller blocks once a large enough library of generators has been developed.

To summarize, this work aims to tackle the issue of a reconfigurable TX by implementing an integrated, wideband PA with on-chip harmonic cancellation and mixed-signal filtering to reduce undesired spectral emissions. In order to implement such a complex system, we use the BAG framework to automate large portions of our design. These transmitters are demonstrated to be effective with both simulation results and measurements from fabricated designs.

### 1.1 State of the Art

There are a variety of approaches to more versatile transmitters, capable of meeting more than a single standard. Integrated multi-standard CMOS transmitters have been presented as a way of implementing a frequency-flexible transmitter [19][20][21]. However, these transmitters generally have output power levels < 10 dBm, well below what is required for cellular handsets. These transmitters are generally intended to be used with external PAs. Even if the transmitters produce low distortion and out-of-band noise, the external PA will generate its own distortion, which can create a need for an external filter in addition to the PA's output network. This is further exacerbated by the fact the transmitters supporting multiple bands have physically separate output ports for different bands, meaning multiple external PAs are required.

Multiple integrated circuit (IC) multi-standard PAs outputting cellular handheld levels of power have also been demonstrated [22][23][24]. While these works have very good performance and reach our power target, they do not achieve the level of integration targeted in this work. For example, the PA cores of [22][23] are implemented a InGaP/GaAs heterojunction bipolar transistor process instead of a standard CMOS process. Both [22][23] use multiple ICs on a single printed circuit board (PCB) and utilize a large number of off-chip passive components to implement the output filtering. In contrast, [24] doesn't use off-chip components explicitly, but has a separate die for the two power amplifiers, for passives consisting of power combining and filtering, and for a RF power switch, integrated onto a single package. While this is an impressive level of integration, it does not achieve the single die level of integration we are aiming for.

Another approach in building more versatile transmitters is by implementing high power multi-mode / multi-mode CMOS PAs on a single IC [8][25][26][27]. These meet our target power levels and are relatively well integrated, but don't quite satisfy our goals for different reasons. The work in [8] demonstrates separate 2 GHz and 5 GHz digital PAs on a single die, with WiFi, LTE, and Bluetooth measurements shown for the 2 GHz PA. The 2 GHz PA is shown to operate at least across a 2.3 GHz - 2.6 GHz band given the standards measured, but we want to implement a TX covering an even wider band. The other three works [25][27][26] present integrated PAs reaching cellular handheld levels of output power, but all three do not implement integrated amplitude control. In particular, [26] includes many off-chip passive components in its output network. However, [27] is highly frequency flexible design due to implementing an integrated, programmable output network with a center frequency tuning

range of 1.8 GHz - 2.2 GHz resulting in a 3-dB bandwidth ranging at least between 1.6 GHz - 2.6 GHz. A drawback to this approach is that it requires high power switches and supply voltages for the programmable output network.

Effective techniques to suppress harmonics in switching PAs have been demonstrated in recent years. These utilize a variety of techniques, such as conduction angle calibration [28], duty-cycle control [29], and harmonic cancellation [30]. Several of these works [28][30] implement PAs targeting low power standards (< 10 dBm) which do not employ amplitude modulation. Due to this, they only demonstrate results with either single tone, continuous wave (CW) tests or simple modulations like BSPK at a fixed frequency. The work of [30] utilizes the same technique we seek to implement in this work, but we wish to demonstrate that this technique is effective at higher powers, with modulated data, and across a wide frequency range when implemented carefully.

The mixed-signal filtering technique has been demonstrated in CMOS TXs utilizing digital PAs to varying degrees of effectiveness [31][32]. In particular, [32] demonstrates good filtering results at watt-class output power. Both demonstrate high levels of integration, with both using only a few off-chip passive components. Our goal is to demonstrate that this technique can work in conjunction with harmonic cancellation.

## 1.2 Scope of the Dissertation

This dissertation will discuss the implementation of two prototype TXs which combine two filtering techniques, harmonic cancellation and mixed-signal filtering, in order to control spectral emissions in a programmable fashion. First, we will introduce the switched-capacitor power amplifier (SCPA), the topology used in both versions of the TX. An overview of the TX system will be given.

The two filtering techniques will be described in detail, with both the mathematical representation discussed as well as practical implementation. We will cover the overall TX architecture and how the final choice of a cartesian architecture was driven by the implementation requirements of the two filtering techniques. The choice of PA topology will also justified by examining the key requirements of the filtering techniques and how the SCPA satisfies those.

The delay and phase shift elements of the filtering techniques will be covered, with special attention paid to the implementation of the harmonic cancellation. We will discuss the why the phase shift implementation matters, and the gilbert-cell based phase interpolator (PI) was chosen. An analysis of the relationship between PI phase resolution to harmonic cancellation will be presented.

The usage and purpose of IQ combining using 25% duty cycle local oscillator (LO) signals in our cartesian TXs will be discussed. We will also look into how 25% duty cycle LO signals can cause nonlinearity in the TX output constellation which is code dependent, which will be demonstrated both mathematically and with simulation results. Duty cycle

control is presented as a way of fixing this nonlinearity, backed by simulation results and with a practical implementation shown and implemented.

We will transition into an depth analysis on designing the TXs to maximize efficiency while meeting filtering specifications. The underlying mechanisms which link the PA switch sizing to the efficiency and filtering specifications will be explained in detail. This culminates in a design algorithm being presented for the PA and its output network given high level specifications and system level parameters.

We will present a prototype along with a wide variety of measured results verifying the effectiveness of the techniques. However, the implementation of the harmonic cancellation was not very robust in the first version, and was extremely reliant on symmetry in the output network. This will be analyzed in detail, with the proposed hypothesis validated by measurements and simulation setups. A solution to this issue will be proposed, analyzed, and verified in the prototype of the second version of the TX. The measured results of this version will be presented to verify the efficacy of the changes between the first and second versions.

In the final portion of this dissertation, the design automation which was core to this work will be covered. The Berkeley Analog Generator (BAG) framework will be introduced, with benefits and disadvantages clearly outlined. Layout generation of key blocks in both versions of the TX will be discussed in great detail, consisting of the SCPA generator for version 1, and the SCPA and PI generators for version 2. The SCPA generator section covers both array level and unit cell designs, as well as floorplanning for more optimal layout. Design methodology within BAG will be elaborated upon, with examples for both layout sizing and circuit design demonstrated.

An introduction to the changes of BAG 2.0 as well as its benefits will be presented, as well as the way in which manufacturable designs can be ensured. Changes and improvements to the 2nd version of the SCPA for the second (revised) version of the TX will be discussed, with specific details regarding modifications to the unit cell in order to improve overall layout and circuit performance. The PI generator will be discussed, with the current DAC (IDAC), and integrator covered in this work. In particular, an algorithm is presented to size the IDAC unit cells to meet resolution requirements, which are critical to harmonic cancellation performance.

Finally, we will conclude with a summary of the work presented, along with key contributions of this work. We close with a list of potential future work that builds upon the presented dissertation.

# Chapter 2

# Filtering Power Amplifiers

This chapter will begin by giving an introduction to the switched-capacitor power amplifier (SCPA), the PA topology used in the transmitter (TX). The overall TX system will then be introduced, after which harmonic cancellation and mixed-signal filtering will be discussed in detail, as well as why the SCPA is a natural choice for these techniques. A deep analysis of how to design and size the SCPA and overall TX will be presented, covering specifications of output power, efficiency, and linearity. Measured results from a 65 nm prototype will be shown, validating the techniques. In the latter half of the chapter, the effect of output network symmetry on the filtering techniques in the first version of the TX will be examined, and a solution will be proposed to make the techniques less dependent on this symmetry. The chapter concludes with measurements from a second prototype, this time in a 28 nm process, which validate the solution to the symmetry issue.

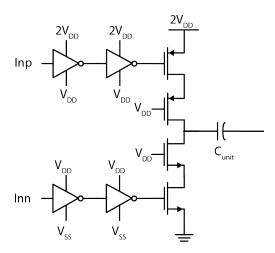

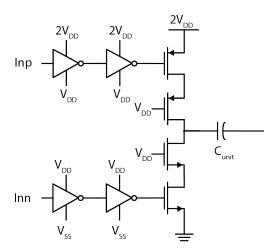

## 2.1 Switched Capacitor Power Amplifier

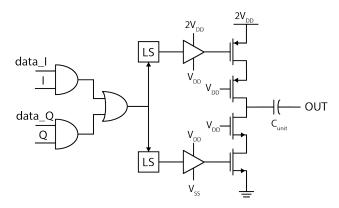

The switched-capacitor power amplifier (SCPA) topology was first demonstrated in [9]. The SCPA operates as a DAC with unit cells composed of an inverter driving a series capacitance, with the other capacitor node being shorted together between all cells. The unit cell of a stacked version with buffers is shown in Fig. 2.1. A key characteristic of the SCPA is its linear input code to output voltage transfer function under ideal operation. This stands in contrast to topologies like the Class  $D^{-1}$  [4], which are inherently nonlinear even with perfect switches. The SCPA's linearity is practically limited by device nonlinearity and device and capacitor matching, but it remains significantly more linear than other topologies.

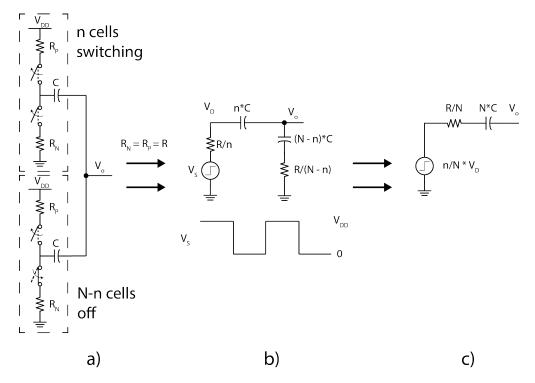

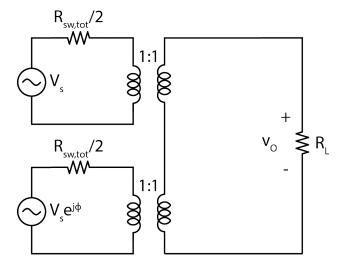

This linearity can be shown with a model of the SCPA (Fig. 2.2a) where the transistors are treated as ideal switches with a non-zero on resistance. Here, n is the number of switching unit cells while N is the total number of unit cells. These groups of unit cells are equivalent to a single cell with an impedance reduced by n. If the pull-up and pull-down resistances are the same ( $R_p = R_n$ ), the model can be further simplified (Fig. 2.2b) by replacing the switches and supplies with a single square wave voltage source with a source impedance. The

Figure 2.1: SCPA unit cell schematic with device stacking and buffers

effects of this assumption not being met will be analyzed further in section 2.5. This square wave can be decomposed into harmonics allowing for frequency domain analysis. Since this is a linear circuit, it can be further simplified using Thevenin's theorem into the form shown in Fig. 2.2c. The overall transfer function assuming a load  $Z_L$  is shown in Eq. 2.1.

Figure 2.2: Ideal SCPA operation

$$\frac{v_o}{v_s} = \frac{n}{N} \cdot \frac{NZ_L}{NZ_L + Z_s}$$

$$Z_s = R + \frac{1}{j\omega C}$$

(2.1)

This analysis can be extended to multiple sub-PAs which are drain combined, which is modeled in Fig. 2.3. For two sub-PAs with  $n_1$  and  $n_2$  switching cells and  $N_1$  and  $N_2$  total cells, we can derive the transfer function in Eq. 2.2. If we have the input  $V_s$  shown in Fig. 2.3, we can also compute a time-domain expression for  $V_o$  (Eq. 2.3). This demonstrates that under ideal operation of the SCPA, the summation is completely linear.

Figure 2.3: SCPA summation operation

$$\frac{v_o}{v_s} = \frac{n_1 + n_2}{2N + \frac{Z_S}{Z_L}} v_s = \frac{n_1 + n_2}{2N} \cdot \frac{2NZ_L}{2NZ_L + Z_s}$$

(2.2)

$$V_o(t) = \frac{V_{DD}}{2} + \frac{2V_{DD}}{\pi} \sum_{k=1,3,5,\dots}^{\infty} \frac{1}{k} \cdot \frac{n_1 + n_2}{2N + \frac{Z_s(jk\omega_0)}{Z_L(jk\omega_0)}} \cdot sin(k\omega_o t)$$

(2.3)

This linearity is a key trait of the SCPA topology, and is critical to the effectiveness of the filtering techniques presented in Section 2.3. The class  $D^{-1}$  topology was initially used, but the extremely nonlinear behavior made these techniques ineffective. Previous work utilizing a Class  $E/F_{odd}$  topology [31] has shown relatively poor filtering results, due largely to the nonlinearity of the topology.

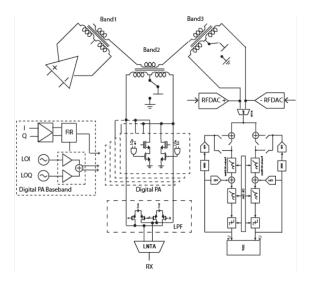

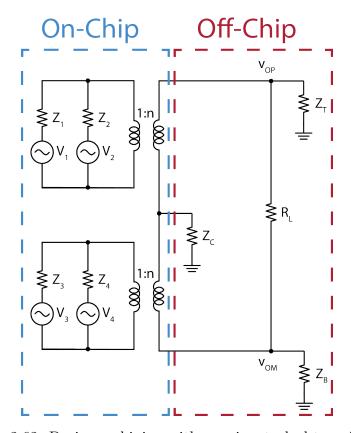

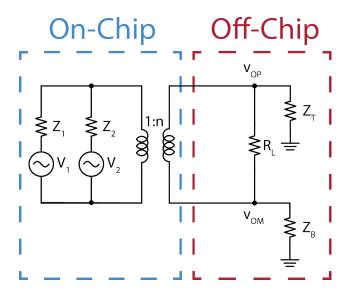

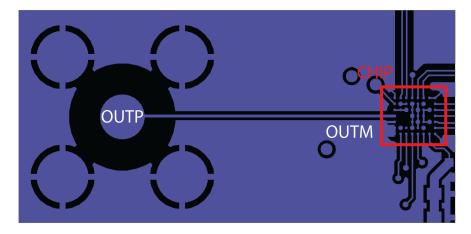

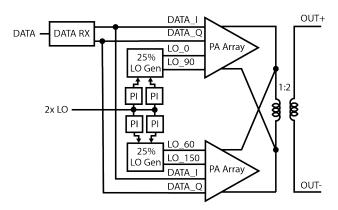

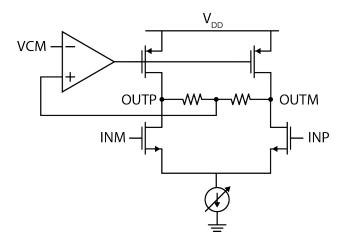

### 2.2 TX System Block Diagram

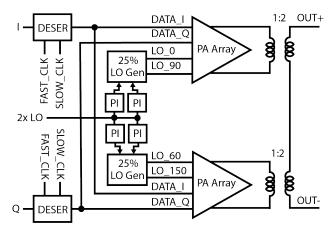

The overall system block diagram will be introduced, with the filtering techniques and design decisions explained in later sections. The top level block diagram of the TX is shown in Fig. 2.4, with all blocks depicted implemented on chip. The SCPA is split into 2 PA arrays, each consisting of 4 sub-PAs for each of the mixed-signal filter taps. There are a total of 2 PA arrays for the 2 LO phases, which means the system has a total of 8 sub-PAs. Each sub-PA is implemented as a 9-bit segmented DAC with 4 binary, 4 thermometer, and 1 sign bit. The PA arrays are summed at the output using a series stacked 1:2 transformer to provide tank inductance and increase output power.

Figure 2.4: SCPA v1 top level block diagram

The TX is implemented using a cartesian architecture, which is also referred to an IQ system since it contains real and imaginary data represented as I and Q, respectively. The I and Q data are received differentially at  $f_{clk,fast} = 2.5 GHz$ , which is describilized by a factor of 10:1. 9 of 10 bits are used, with the last bit discarded. This 10:1 ratio was chosen to allow for a simple relationship between  $f_{clk,fast}$  and  $f_{clk,slow}$ . The describilizer uses a double data-rate DDR scheme in order to allow for a lower  $f_{clk,fast}$ , and sets  $f_{clk,slow} = 500 MHz$ . A scan chain is also implemented to allow for external configuration of various settings, such as bias currents for various blocks.

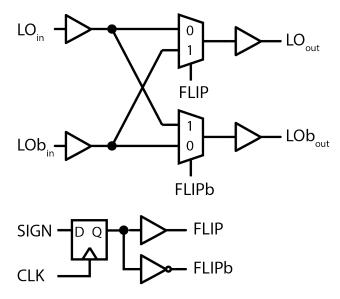

Clock receivers take the sinusoidal fast data clock, slow data clock, and  $2f_{LO}$  local oscillator (LO) signals and generate digital signals for use on chip. The  $2f_{LO}$  signal goes through a divider to generate I, Ib, Q, Qb LO signals at  $f_{LO}$ . These then are fed into pairs of phase interpolators (PIs) to generate the four sets of phases associated with a PA array, which are then used to generate 25% duty cycle versions of the same phases. This LO network comprises the harmonic cancellation portion of the TX. The harmonic cancellation will be configured to target the 3rd harmonic, as this will be the largest harmonic in our system since we use a differential PA.

Both the SCPA capacitors and transformer were implemented on chip, with no off chip passives used in the output network in order to meet the goal of having a single integrated TX. Both passive components are sized for an overall low loaded quality factor (Q) so that the overall TX is wideband.

A specific standard was not targeted, but the general specifications for the TX included a peak output power  $P_{out} > 24dBm$ , a center frequency  $f_{LO}$  of around 1 GHz with at least several hundred MHz of bandwidth. Additionally, the TX is designed to support HD3 reduction of 40 dB, with the HD3 reduction being defined as the difference in HD3 from the case where the PAs sum in phase to the cancelled case.

Now that a rundown of the TX system is given, we will discuss the implementation of the harmonic cancellation and mixed-signal filtering, starting at a high level and moving to a lower level. The choice of architecture was made based on the implementation requirements of these filtering techniques.

## 2.3 Filtering Techniques

Harmonic cancellation and mixed-signal filtering can be used to tackle the harmonic emission and quantization noise issues. Both of these techniques are active cancellation schemes which follow the same general guideline: the PA is partitioned into several sub-PAs, driven with different inputs, and summed at the output. The sub-PA inputs take in the upconverted IQ data, which has already been mixed with the LO. Harmonic cancellation is implemented by feeding sub-PAs different LO phases, while mixed-signal filtering is implemented by feeding sub-PAs different baseband data. Modern transmitters send complex-valued data, which can be represented either in a real-imaginary format (cartesian) or amplitude-phase format (polar). Since these filtering techniques rely on manipulating the input signals of each sub-PA, the implementation will differ in cartesian and polar architectures. We will first discuss the harmonic cancellation, then the mixed-signal filtering, and finally combine the two into a single system.

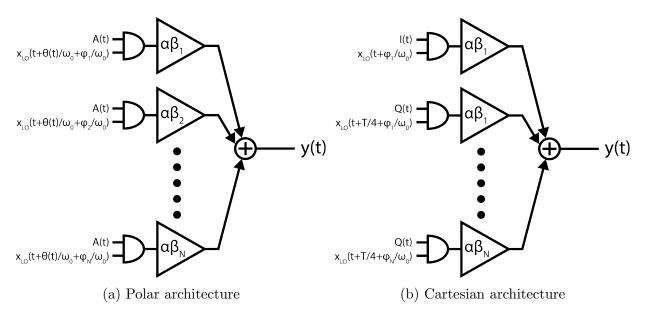

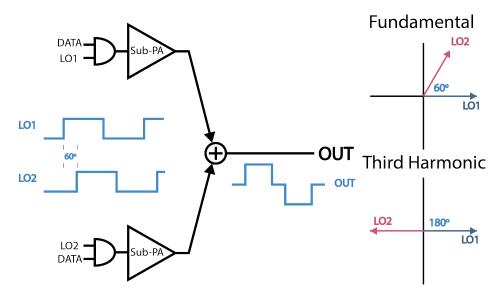

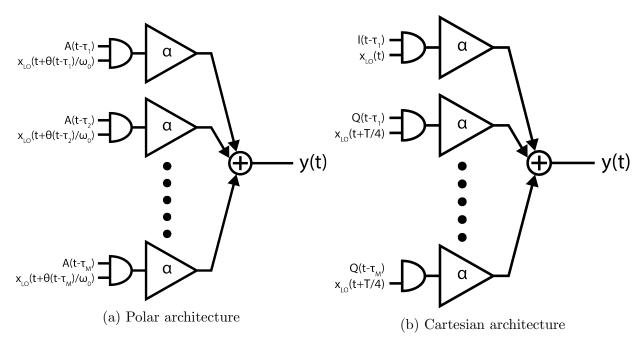

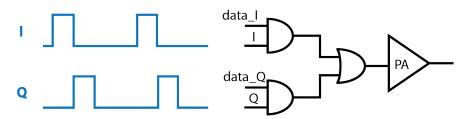

The block diagram for the harmonic cancellation technique is shown in Fig. 2.5 for both polar and cartestian architectures. This harmonic cancellation technique was primarily used in mixers for RF receivers [33][34], but has seen usage with switching PAs recently [30]. The polar architecture consists of amplitude A(t) and phase  $\theta(t)$ , while the cartesian architecture has in-phase I(t) and quadrature Q(t) components. The signals A(t),  $\theta(t)$ , I(t), Q(t), and  $x_{LO}$  are digital, with  $x_{LO}(t)$  being a square wave with period T, with  $\omega_0 = \frac{2\pi}{T}$ . The digital AND gate acts as a mixer (multiplier) for the data and LO. We are assuming that the switching PAs generate a square wave output from  $x_{LO}$  with a gain  $\alpha$ , though this analysis still holds as long as the sub-PAs outputs are periodic with period T. Each sub-PA is weighted with a scaling factor  $\beta_l$  and driven with an LO with a phase shift  $\phi_l$  at the fundamental frequency. This scheme is represented mathematically in Eq. 2.5 for the polar case and in Eq. 2.6 for the cartesian case.

$$x_{LO}(t) = \sum_{k=-\infty}^{\infty} a_k e^{jk\omega_0 t}$$

(2.4)

Figure 2.5: Harmonic cancellation block diagram

$$y(t) = \sum_{l=1}^{N_{\phi}} A(t) \cdot \alpha \beta_l x_{LO} \left( t + \frac{\theta(t)}{\omega_o} + \frac{\phi_l}{\omega_o} \right)$$

(2.5)

$$y(t) = \sum_{l=1}^{N_{\phi}} \alpha \beta_l \left[ I(t) x_{LO} \left( t + \frac{\phi_l}{\omega_o} \right) + Q(t) x_{LO} \left( t + \frac{T}{4} + \frac{\phi_l}{\omega_o} \right) \right]$$

(2.6)

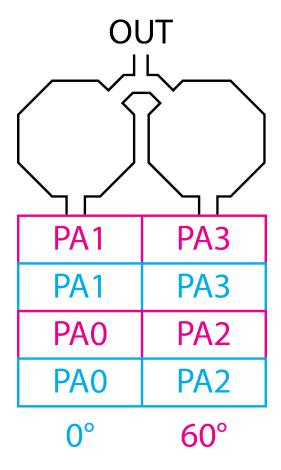

Using the fourier series decomposition of  $x_{LO}(t)$  (Eq. 2.4), the output y(t) can be rewritten as Eq. 2.8 (polar case) and Eq. 2.9 (catesian case). Proper choices of  $\beta_l$  and  $\phi_l$  can set  $\gamma_k = 0$  for certain values of k, cancelling specific harmonics with a small reduction of the fundamental. A common harmonic cancellation scheme uses three sub-PAs weighted by  $1, \sqrt{2}, 1$  with phase shifts of  $0, 45^{\circ}, 90^{\circ}$  respectively. This perfectly cancels the  $3^{rd}, 5^{th}, 11^{th}, 13^{th}$ , etc. harmonics while reducing the fundamental by 1.6 dB.

$$\gamma_k = \sum_{l=1}^N \beta_l e^{jk\phi_l}$$

$$y(t) = \alpha A(t) \sum_{k=-\infty}^\infty a_k e^{j(k\omega_0 t + \theta(t))} \sum_{l=1}^N \beta_l e^{jk\phi_l} = \alpha A(t) \sum_{k=-\infty}^\infty a_k \gamma_k e^{j(k\omega_0 t + \theta(t))}$$

$$y(t) = \alpha A(t) \sum_{k=-\infty}^\infty a_k \gamma_k e^{j(k\omega_0 t + \theta(t))}$$

(2.8)

$$y(t) = \alpha \sum_{k=-\infty}^{\infty} a_k \gamma_k e^{jk\omega_0 t} \left[ I(t) + Q(t)e^{\frac{jk\pi}{4}} \right]$$

(2.9)

There are several ways of generating the phase shift assuming we have a base LO signal either brought in externally or generated by an on chip oscillator. The phase shift can either be generated directly using a phase interpolator (PI) or using a time delay implemented by a delay line.

If we want the harmonic cancellation to work across a frequency range  $f_{min} \leq f \leq f_{max}$  with a minimum resolution  $kT_{min}$ , this imposes two major constraints on the delay line implementation. The maximum delay required depends on  $f_{min}$ , with a maximum delay  $t_{dmax} = \frac{1}{6f_{min}}$  to implement a 60° phase shift. However, the minimum time delay  $\Delta t$  depends on  $f_{max}$ , with  $\Delta t = \frac{k}{f_{max}}$ . This means that we need a much higher effective resolution if the delay line was designed for a single operating frequency. For operation across a 1 - 2GHz range, we require  $t_{dmax} = 166.7ps$  and  $\Delta t = 1.4ps$ . This increased resolution can be relaxed by using a coarse-fine delay line, such as in [35][36].

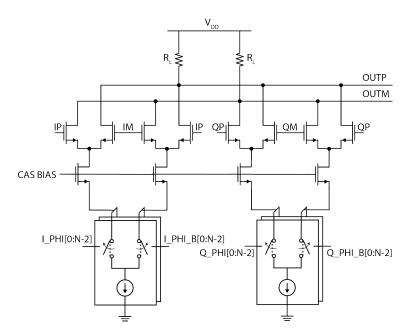

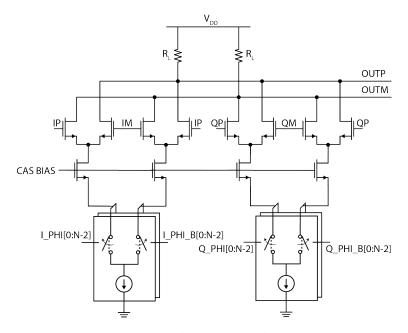

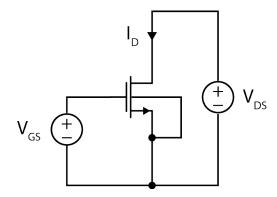

For our requirements however, and since the LO is a steady-state periodic signal, a phase interpolator (PI) provides much better phase noise performance for a given power specification than a delay line. We used a gilbert-cell based phase interpolator [18], with an N-bit implementation shown in Fig. 2.6. The output phase is set by the signals LPHI, LPHI\_B, Q\_PHI, and Q\_PHI\_B. This topology requires input integrators to shape the input LO phases into triangular waves. Frequency flexibility can be easily achieved with this topology by providing a programmable bias to the integrators in the form of a current DAC. The integrator's dominant pole can then be moved to different frequencies by modifying  $g_m$  by changing the bias current. Prior work utilized gilbert-cell based PIs operating across a 0.4 - 4.0 GHz range in a polar architecture [37], demonstrating the frequency flexibility of this PI topology.

A separate PI is required for each phase shift in both the cartesian and polar architectures. However, the polar architecture has the phase input of the PI on the high speed data path, and requires adders to implement the fixed phase shifts  $\phi_l$ . In a cartesian architecture however, the phase input of the PI can be statically set to the desired phase shift.

The phase shift  $\phi_l$  can be applied directly to the LO signal, but for a standard switching PA, the size of the PA must be scaled in order to implement the  $\beta_l$ . The LO input can't be scaled due to being a digital square wave signal. This direct scaling has been implemented in previous harmonic cancellation PA works [30]. However, this problem becomes much more difficult when each sub-PA is a DAC, as special care has to be taken to properly implement the scaling even for the smallest binary cell to ensure good matching. The layout overhead becomes even larger if the ratios between any weights are not a whole number. As an example, we can examine the harmonic cancellation setup with sub-PA weights 1, 1.4, 1 with phase shifts of 0, 45°, 90°. The value of  $\sqrt{2}$  is rounded to 1.4 to simplify the implementation of the multiplier.

Figure 2.6: Gilbert-cell based phase interpolator

In order to scale the output stage transistors, we must rely on modifying the number of transistor fingers. Though width scaling is simpler, it does not provide reliable matching in advanced planar technologies. The weights of 1, 1.4, and 1 can be implemented with ratios of 5, 7, 5 fingers. However, we generally want a finger pair to be the unit element in order to balance out biases in current flow based on direction [38], which raises this minimum number of fingers to 10, 14, 10. This sets the minimum total width of the smallest device, which forces the unit cells to be upsized if the desired size of the minimum smallest binary cell is below this.

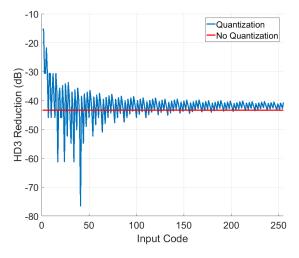

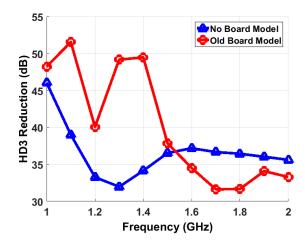

Mutiplying the digital inputs of each sub-PA by its appropriate weight  $\beta_l$  is another way of implementing the scaling, assuming each sub-PA is a DAC. Digital multipliers would be added in the data path, either for the IQ signals or the amplitude for a polar implementation. If any of the scaling factors are not whole numbers, the input codes must be rounded after multiplication, introducing input code dependent quantization error. This quantization error generates nonlinearity (DNL, INL) and input code dependent harmonic cancellation. In particular, we will use the metric of HD3 reduction  $\Delta HD_3$ , which is defined as the difference in HD3 under cancelling conditions and when the sub-PAs sum in phase.

In order to quantify this, we'll look at an example with a fixed-point multiplier with 4 bits of precision (down to  $1/16^{ths}$ ). Using the same harmonic cancellation scheme as the previous two paragraphs, this rounds sqrt(2) to 1.4375. Fig. 2.7 demonstrates the HD3 reduction across input code with and without rounding after multiplication, when we assume a maximum input code of 255. Quantization limits the HD3 reduction to 15 dB in the worst case, though we have  $\Delta HD_3 \geq 30dB$  for  $n \geq 6$ . Additionally, quantization introduces a max  $\geq 0.4$  LSB of INL, and DNL of -0.58 to 0.25 LSB. This quantization-induced nonlinearity

combines with the random mismatch induced nonlinearity to degrade the effective resolution of the DAC.

Figure 2.7: HD3 reduction with and without quantization

Given all these issues, we opted go for a more simple configuration which would still provide harmonic cancellation without requiring sub-PA scaling. The PA is split into two equally weighted sub-PAs which are fed the same IQ data but LO signals phase shifted by  $60^{\circ}$ . This shifts the fundamental of the output by  $60^{\circ}$  and the third harmonic by  $180^{\circ}$ . If the sub-PAs are perfectly matched, the  $3^{rd}$ ,  $9^{th}$ ,  $15^{th}$ , etc. harmonics will be completely cancelled while the fundamental is reduced by 1.2 dB.

The block diagram for the mixed-signal filter is shown for a polar architecture (Fig. 2.11a)

Figure 2.8: DNL with quantization

Figure 2.9: INL with quantization

Figure 2.10: Harmonic cancellation block diagram

and cartestian architecture (Fig. 2.11b). This technique has been previously demonstrated using digital PAs [31][32]. In both polar and cartesian architectures, the input data is delayed by  $\tau_m$  for the  $m^{th}$  sub-PA. This implementation makes the key restriction of implementing only real-valued filter coefficients. Additionally, the sub-PAs are equally weighted in order to avoid similar sub-PA scaling issues discussed in the harmonic cancellation section. In this case, there is a significant difference in the implementation of the mixed-signal filter in the two architectures.

The mathematical representation of this filter implementation in the polar architecture is shown in Eq. 2.11. Each sub-PA must be able to take in different delayed versions of the amplitude and phase data. The different phase data requirement causes the number of PIs needed to scale linearly with the number of sub-PAs since each sub-PA needs an LO with an arbitrary phase  $\theta(t-\tau_m)$ . In contrast, the cartesian case (Eq. 2.10) only requires delays on I(t) and Q(t), with two versions of the LO signal  $x_{LO}$  required regardless of the number of sub-PAs. The number of PIs is fixed and does not scale with the number of sub-PAs in the cartesian implementation.

This reduced number of PIs is the primary reason we chose to implement the TX using a cartesian architecture instead of a polar one. This is key because PI performance is critical to the effectiveness of our harmonic cancellation, which is analyzed more thoroughly in Section 2.4. This requirement also drives the PIs to be relatively large, so reducing the total number of PIs saves significant area. It should be emphasized that the relative simplicity of cartesian implementation only holds when we restrict the filter coefficients to being real-valued. It is comparable with the polar implementation if complex-valued filter coefficients are allowed.

Figure 2.11: Mixed signal filter block diagram

$$y(t) = \alpha \sum_{m=1}^{M} I(t - \tau_m) x_{LO}(t) + Q(t - \tau_m) x_{LO}\left(t + \frac{T}{4}\right)$$

(2.10)

$$y(t) = \alpha \sum_{m=1}^{M} A(t - \tau_m) x_{LO} \left( t + \frac{\theta(t - \tau_m)}{\omega_o} \right)$$

(2.11)

The mixed-signal filtering implemented using this technique implements an FIR filter with several restrictions. For a configuration with a total of M equally weighted sub-PAs of weight  $\alpha$ , each tap coefficient must be a multiple of  $\alpha$ , with the sum of the absolute values of the coefficients totaling  $\alpha M$ . For example, with M=4,  $y(n)=2\alpha x(n)+2\alpha x(n-n_1)$  and  $y(n)=\alpha x(n)-2\alpha x(n-n_1)-\alpha x(n-n_2)$  are valid configurations while  $y(n)=\frac{3\alpha}{2}x(n)+\alpha x(n-n_1)$  is not.

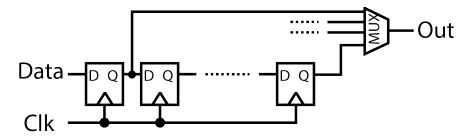

The choice of delay line topology is set primarily by the maximum delay needed. For the cellular standards targeted in our designs, the nearest channel will likely be 20 MHz or 40 MHz away, such as in LTE. With 4 sub-PAs, we can implement the double notch filter in Eq. 2.12, with the time-domain implementation shown in Eq. 2.13. A maximum delay of  $1/f_{notch}$  is needed to implement a double notch at  $f_{notch}$ . This means that we need 50 ns of delay to implement two notches at 20 MHz. Given this requirement, we chose to implement the delay line with a chain of flip-flops due to the relative simplicity as well as the relatively low power cost for a given jitter specification. This chain of flip-flops is clocked using the data clock, with the specific delayed output selected using a MUX (Fig. 2.12). In our TX,

the MUX select is set using the TX's scan chain. The delay line consisted of a total of 25 flip flops clocked at  $f_{clk,slow} = 500 MHz$ , resulting in the desired maximum delay of 50 ns. An inverter based delay line requires either a very large number of stages or large load capacitors to achieve this delay with reasonable jitter performance, which is costly both in area and power.

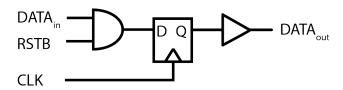

Figure 2.12: Delay line schematic

$$Y(\omega) = X(\omega) \cdot (1 + e^{-j\omega\tau_1}) \left( 1 + e^{-j\omega\tau_2} \right) = X(\omega) \cdot \left( 1 + e^{-j\omega\tau_1} + e^{-j\omega\tau_2} + e^{-j\omega(\tau_1 + \tau_2)} \right)$$

(2.12)

$$y(t) = x(t) + x(t - \tau_1) + x(t - \tau_2) + x(t - \tau_1 - \tau_2)$$

(2.13)

Harmonic cancellation and mixed-signal filtering can be implemented simultaneously, both in cartesian (Eq. 2.14) and polar (Eq. 2.15) architectures for a generic periodic signal  $x_{LO}$ . These equations assume N LO phases for harmonic cancellation and M sub-PAs for mixed-signal filtering.

$$y(t) = \alpha \sum_{l=1}^{N} \sum_{m=1}^{M} I(t - \tau_m) x_{LO} \left( t + \frac{\phi_l}{\omega_0} \right) + Q(t - \tau_m) x_{LO} \left( t + \frac{T}{4} + \frac{\phi_l}{\omega_0} \right)$$

(2.14)

$$y(t) = \alpha \sum_{l=1}^{N} \sum_{m=1}^{M} A(t - \tau_m) x_{LO} \left( t + \frac{\theta(t - \tau_m)}{\omega_0} + \frac{\phi_l}{\omega_0} \right)$$

(2.15)

A critical requirement for these techniques is that the summation of the sub-PAs must be linear. Nonlinearities can generate spectral content that "fills in" the notches generated by the cancellation. Toplogies with inherently nonlinear input code to output voltage transfer functions (such as Class  $D^{-1}$ ) are not suited to these techniques. However, even topologies with perfectly linear operation in the ideal case can exhibit nonlinear summation. The most obvious source is from nonlinearity in the switch devices used, but nonlinear summation can also be casued by not matching the resistance of pull-up and pull-down networks. The latter will be discussed in more detail in Section 2.5. First, we will discuss how PI phase resolution impacts harmonic cancellation.

### 2.4 Phase Resolution and Harmonic Cancellation

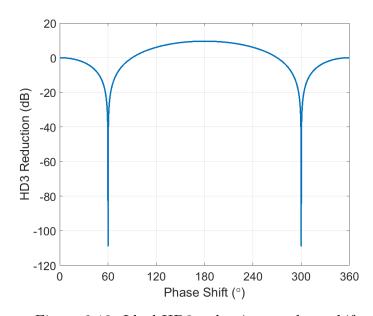

Even with perfect amplitude matching, harmonic cancellation will be limited by phase matching, which is impacted primarily by phase interpolator resolution and phase noise. In order to understand how the phase resolution affects HD3, we first need to look at the transfer function with harmonic cancellation scheme, shown in Eq. 2.16, where  $\phi$  is the phase shift. This can be used to compute the HD3 in Eq. 2.17, which can then be normalized to the HD3 reduction  $\Delta HD_3$  in Eq. 2.18, with the latter plotted in Fig. 2.13.  $HD_{3,0}$  is defined as the HD3 measured when the PAs sum in phase ( $\phi = 0$ ).

$$H(\omega) = 1 + e^{-j\omega t_0} = 1 + e^{-j\phi} \tag{2.16}$$

$$HD_3(\phi) = \left| \frac{H(3\phi)}{H(\phi)} \right| = (HD_{3,0}) \cdot \left| \frac{1 + e^{-j3\phi}}{1 + e^{-j\phi}} \right|$$

(2.17)

$$\Delta H D_3(\phi) = \frac{H D_3(\phi)}{H D_{3,0}} = \left| \frac{1 + e^{-j3\phi}}{1 + e^{-j\phi}} \right|$$

(2.18)

Figure 2.13: Ideal HD3 reduction vs phase shift

Perfect cancellation can be attained with a 60° phase shift but this impossible to guarantee in practice. Instead, we can design to ensure a minimum HD3 reduction, assuming perfect amplitude matching. This can be done by noting that there are exactly two phase shifts  $\phi_a$  and  $\phi_b$  that correspond with a given HD3 reduction, and that any value of phase shift between those two will exceed that HD3 reduction. If we have a phase step  $\phi_{step} \leq \phi_b - \phi_a$ ,

| Min HD3 Reduction | Phase Step | $n_{bits}$ |

|-------------------|------------|------------|

| 20 dB             | 6.623°     | 5.8        |

| 30 dB             | 2.092°     | 7.4        |

| 40 dB             | 0.661°     | 9.1        |

| 50 dB             | 0.209°     | 10.7       |

| 60 dB             | 0.066°     | 12.4       |

Table 2.1: HD3 reduction vs number of bits

we will be able to guarantee that we can land within the desired phase shift interval and guarantee our minimum HD3 reduction. This is the phase step required for our PI, which can then be mapped to the required number of bits (or phase resolution) in the PI for a given full range.

Table 2.1 lists the phase steps and number of bits required to ensure different minimum HD3 reduction values. A full scale of 360° is assumed here, which is the case for a gilbert-cell based PI. The number of bits required to ensure higher HD3 reduction grows quickly, which is problematic because high resolution DACs are costly in area. Given this, we have chosen to target an HD3 reduction of 40 dB, which corresponds to about 9 bits of phase resolution for the PI.

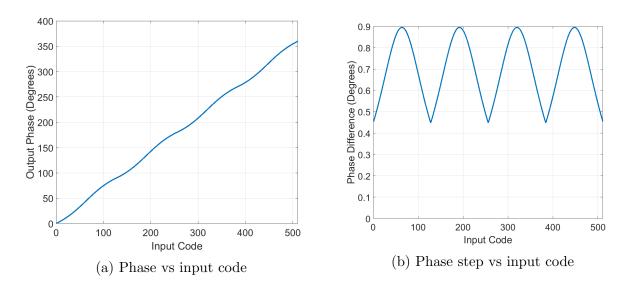

This TX implements gilbert-cell based PIs, which operate by weighing the four phases (I, IB, Q, QB) and summing them in current (Fig. 2.6). Though the current summation is generally very linear, the ideal output phase vs input code transfer function is inherently nonlinear since it relies on a  $tan^{-1}$  function. This relationship is plotted for a 9-bit PI in Fig. 2.14a, with the phase step for each code given in Fig. 2.14b.

$$\phi(n) = \begin{cases} \tan^{-1} \left( \frac{\frac{N}{2} - 2n - 1}{2n + 1} \right) & 0 \le n < \frac{N}{4} \\ \tan^{-1} \left( \frac{-2\left(n - \frac{N}{4}\right) - 1}{\frac{N}{2} - 2\left(n - \frac{N}{4}\right) - 1} \right) & \frac{N}{2} \le n < \frac{N}{2} \\ \tan^{-1} \left( \frac{-\frac{N}{2} + 2\left(n - \frac{N}{2}\right) - 1}{-2\left(n - \frac{N}{2}\right) - 1} \right) & \frac{N}{2} \le n < \frac{3N}{4} \\ \tan^{-1} \left( \frac{2\left(n - \frac{3N}{4}\right) + 1}{-\frac{N}{2} + 2\left(n - \frac{3N}{4}\right) + 1} \right) & \frac{3N}{4} \le n < N \end{cases}$$

$$(2.19)$$

From Fig. 2.14b, we can deduce that the phase steps are largest at  $(2k-1) \cdot 45^{\circ}$  and smallest at  $k \cdot 90^{\circ}$  for gilbert-cell based PIs. The phase step ranges between 0.45° and 0.9° across input codes for an ideal 9-bit PI. The phase steps near 60° are about 0.84° as compared to 0.7° for a perfectly linear PI. This reduction in phase resolution causes a slight drop in minimum HD3 reduction from 39.5 dB to 37.9 dB, 2 dB less than the target 40 dB cancellation. Since practical issues such as DAC nonlinearity will degrade the minimum HD3 reduction, we deem this to be an acceptable loss.

Figure 2.14: Ideal phase and phase step for a gilbert-cell based PI

# 2.5 Resistance Mismatch and SCPA Linearity

The introductory analysis of SCPA operation in Section 2.1 assumed equal pull-up resistance  $R_p$  and pull-down resistance  $R_n$ . Mismatch in  $R_n$  and  $R_p$  will generate nonlinearity in the SCPA, degrading the linear summation which is critical to the filtering techniques discussed in Section 2.3. Furthermore, it is difficult to ensure  $R_n = R_p$  across voltage swing in practical implementations, since the switches will be implemented with transistors.

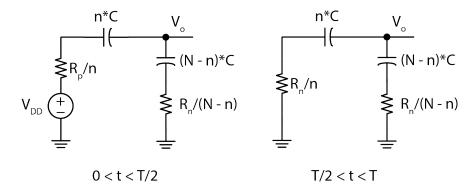

To analyze the effect of this nonideality on the output, we can analyze the schematic in Fig. 2.15, in which we assume non-switching cells are pulled to ground. The eventual goal is to compute the fundamental frequency component of the output  $V_o(t)$ . The load is being omitted to simplify the analysis. We have a time-varying resistance, which makes frequency domain analysis difficult, as it would require the use of Volterra series. In this case, it is much simpler to compute the time domain output and apply a Fourier series decomposition. The results of the first step give us the piecewise time domain expression in Eq. 2.20 for a single switching period. From this it is clear that any mismatch in the  $R_n$  and  $R_p$  introduces an error term which causes deviation from the ideal  $\frac{n}{N}V_{DD}$ , and that this error decays over time as well. Mismatch in  $R_n$  and  $R_p$  also cause the output impedance becomes time-varying and dependent on input code n.

$$V_o(t) = \begin{cases} \frac{nV_{DD}}{N} \left[ 1 + \epsilon \cdot e^{-\frac{t}{\tau_1}} \right] & 0 < t \le \frac{T}{2} \\ 0 & \frac{T}{2} < t \le T \end{cases}$$

(2.20)

$$\tau_1 = \frac{\left(\left(N - n\right)R_p + nR_n\right)C}{N} \qquad \tau_2 = R_nC \tag{2.21}$$

Figure 2.15: SCPA operation during across a single period

$$\epsilon = \left(\frac{1 - e^{-\frac{T}{2\tau_2}}}{1 - e^{-\frac{T}{2\tau_1} - \frac{T}{2\tau_2}}}\right) \left(\frac{R_n - R_p}{\frac{n}{N-n}R_n + R_p}\right)$$

(2.22)

Eq. 2.22 demonstrates that the error depends on the switching code used, with the worst case occurring for n=1. For the other part of the error, the worst case error comes in the case where T is sufficiently larger than  $\tau_1$  and  $\tau_2$  (i.e.  $T > 4.6\tau_1$ ,  $T > 4.6\tau_2$ ), which gives the maximum value as shown in Eq. 2.23. For N=255 and  $R_p=2R_n$ , we find that  $\epsilon=-0.499$ .

$$|\epsilon| \le \left| \frac{R_n - R_p}{\frac{1}{N-1}R_n + R_p} \right| = \left| \frac{1 - \frac{R_p}{R_n}}{\frac{1}{N-1} + \frac{R_p}{R_n}} \right|$$

(2.23)

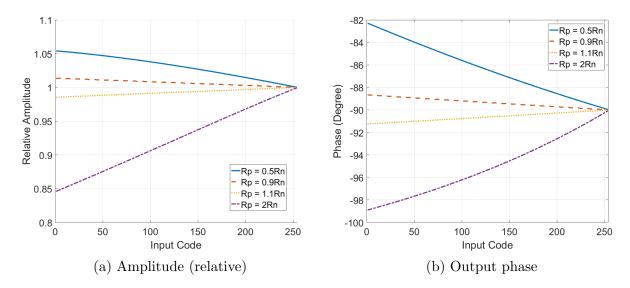

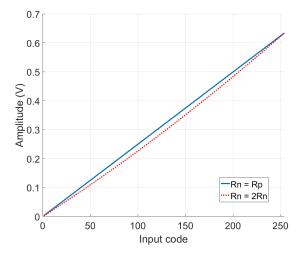

We can apply a Fourier series decomposition on the time domain expression for  $V_o(t)$  (Eq. 2.20) to write  $V_o(t)$  as a sum of complex exponentials, with coefficients  $a_k$  shown in Eq. 2.25. This form can be further manipulated into Eq. 2.26, which splits  $V_o(t)$  into real-valued DC, odd and even harmonic components. The amplitudes of the harmonics are expressed as  $b_k$  (Eq. 2.27) for odd harmonics and  $c_k$  (Eq. 2.28) for even harmonics, except for k = 0.