## Hybrid Switched-Capacitor Power Converters: Fundamental Limits and Design Techniques

Zichao Ye

### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-236 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-236.html

December 1, 2021

Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Hybrid Switched-Capacitor Power Converters: Fundamental Limits and Design Techniques

by

Zichao Ye

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Associate Professor Robert C.N. Pilawa-Podgurski, Chair Professor Seth R. Sanders Professor Kristofer Pister Associate Professor Jason T. Stauth

Fall 2020

The dissertation of Zichao Ye, titled Hybrid Switched-Capacitor Power Converters: Fundamental Limits and Design Techniques, is approved:

| Chair | Date |  |

|-------|------|--|

|       |      |  |

|       | Date |  |

|       | Date |  |

|       |      |  |

|       | Date |  |

University of California, Berkeley

Hybrid Switched-Capacitor Power Converters: Fundamental Limits and Design Techniques

Copyright © 2020 by Zichao Ye

#### Abstract

### Hybrid Switched-Capacitor Power Converters: Fundamental Limits and Design Techniques

by

Zichao Ye

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Associate Professor Robert C.N. Pilawa-Podgurski, Chair

In this dissertation, we develop and explore very-high-performance power conversion systems for emerging applications that require high efficiency and high power density simultaneously, such as large-scale data center power delivery and mobile computing on portable and wearable electronics.

This work focuses on a topological effort to drastically improve the performance of existing power electronics. In particular, a hybrid approach is adopted, in which both inductors and capacitors are used in the voltage conversion and power transfer process. Compared to conventional switched-capacitor (SC) converters, the augmenting inductors can greatly reduce or eliminate the capacitor charge sharing loss, and thus improve the energy utilization of the capacitors without sacrificing efficiency. This process is called soft-charging operation. In combination with other potential advantages such as soft switching and voltage regulation, hybrid SC converters show promise in the development of future high-performance power electronics systems.

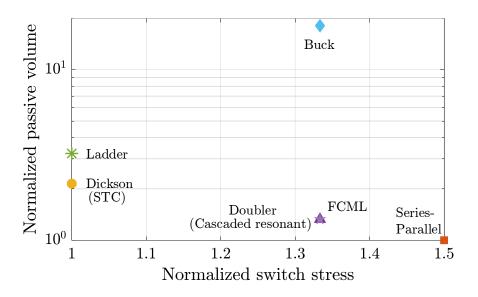

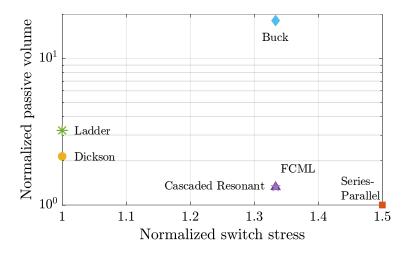

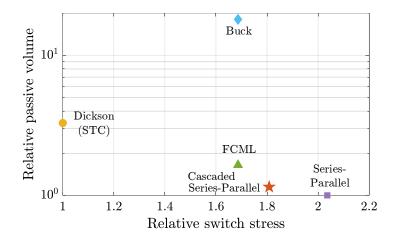

This dissertation explores hybrid SC converters from three main aspects: fundamental limits and topology comparisons, practical circuit implementation challenges, and high-performance hardware demonstrations. We start by analyzing the reactive power processed by the passive components of hybrid SC converters operating in resonant mode. This analysis is applied to express and optimize the total passive component volume of resonant switched-capacitor (ReSC) converters. To compare different ReSC topologies, a normalized passive volume parameter is proposed for simple and fair comparison. This normalized passive volume parameter, along with a normalized switch stress parameter (based on switch VA ratings), can be used to visualize and compare the passive and active component utilizations among different topologies, offering a framework to compare the relative performance of different topologies.

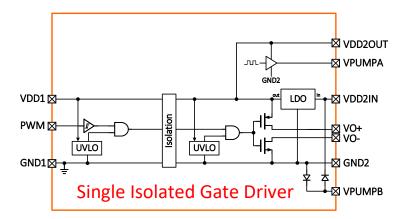

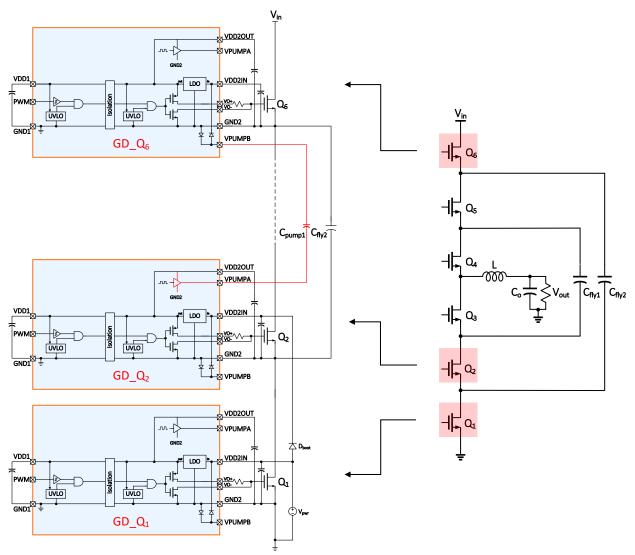

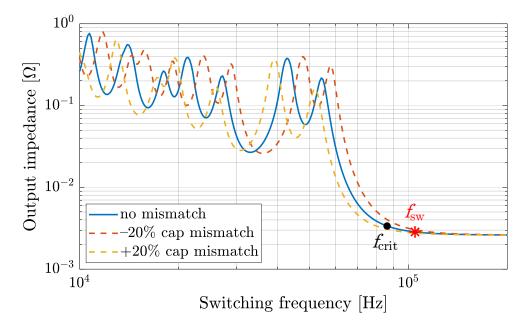

The large number of floating switches and flying capacitors pose great challenges in practical circuit implementations. Several bootstrap and charge-pump based techniques are developed to provide gate drive power to the floating switches in a compact and efficient manner. Compared to conventional isolated dc/dc power supply chips, the proposed circuits have a simple structure and operating principle, and can be implemented with a small number of diodes, capacitors, and LDOs, leading to less occupied board area and lower implementation cost. Another crucial practical challenge is flying capacitor voltage balancing. In unbalaced operation, capacitor voltages deviate from their nominal values, potentially resulting in system failure. We experimentally investigate the origins of the voltage imbalance in practical implementations of flying capacitor multilevel (FCML) converters and present corresponding solutions. It is found that an FCML converter with an even number of levels has significantly better capacitor balancing than one with an odd number of levels, due to better inherent immunity to circuit non-idealities.

With the theoretical analysis tools and the practical circuit techniques developed above, a number of high-performance discrete hardware prototypes are designed in the context of 48 V power delivery architecture for modern data centers. Based on a novel cascaded resonant topology, a 48-to-12 V, 4-to-1 fixed-ratio, intermediate bus converter is built with 99% peak efficiency and 2500 W/in<sup>3</sup> power density. To further increase the conversion ratio without increasing circuit complexity, the concept of multi-phase operation is introduced, along with a 6-to-1 cascaded series-parallel topology and an 8-to-1 multi-resonant-doubler topology. In addition to fixed-ratio ReSC converters, a regulated multi-level binary hybrid converter for direct 48 V to 1–2 V point-of-load applications is also developed. All of the hardware prototypes achieve the best in-class efficiency and power density simultaneously, reflecting the great potential of hybrid and resonant switched-capacitor converters for future power conversion systems. To my family

# Contents

| $\mathbf{C}$  | Contents                                                                                                                                                                                                                                                                                                                         | ii                           |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| $\mathbf{Li}$ | ist of Figures                                                                                                                                                                                                                                                                                                                   | iv                           |

| $\mathbf{Li}$ | ist of Tables                                                                                                                                                                                                                                                                                                                    | x                            |

| 1             | Introduction1.1Introduction1.2Organization of Thesis                                                                                                                                                                                                                                                                             |                              |

| 2             | Fundamentals of Hybrid and Resonant Switched-Capacitor Converters2.1Limitations of Conventional Topologies2.2Soft-Charging Operation2.3PWM Regulated Mode vs. Fixed-Ratio Mode2.4Inductor Placement Strategy                                                                                                                     | 10<br>11                     |

| 3             | Modeling and Comparison of Passive Component Volume3.1Background and Motivation3.2Analysis of Basic 2-to-1 Resonant Switched-Capacitor Converter3.3Design Guidelines and Comparisons with Other Solutions3.4Generalized Analysis3.5Resonant SC Topology Comparison3.6Comparison of Regulated Hybrid Converters3.7Chapter Summary | $20 \\ 25 \\ 35 \\ 41 \\ 45$ |

| 4             | Capacitor Voltage Balancing of Flying Capacitor Multilevel Converters4.1Background and Motivation                                                                                                                                                                                                                                | 54<br>55<br>70               |

| <b>5</b>      | Circuit Techniques for Powering Floating Gate Drivers                                                                                                                                                                                                                                                                            | 77                           |

|    | 5.1              | Background and Motivation                            | 77  |  |

|----|------------------|------------------------------------------------------|-----|--|

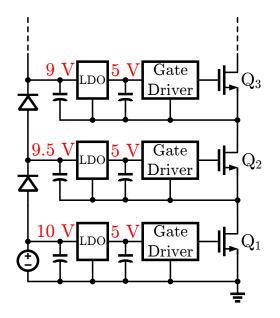

|    | 5.2              | Bootstrap at Deadtime                                | 81  |  |

|    | 5.3              | Cascaded Bootstrap with LDOs                         | 86  |  |

|    | 5.4              | Double Charge Pump                                   | 90  |  |

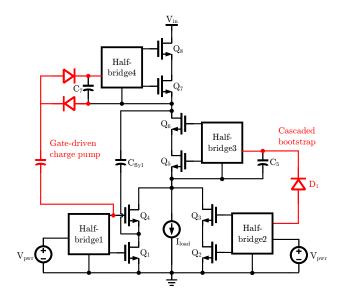

|    | 5.5              | Gate-Driven Charge Pump                              | 91  |  |

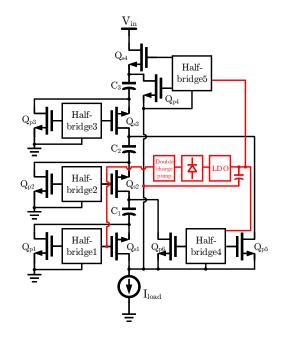

|    | 5.6              | Cascaded Synchronous Bootstrap                       | 94  |  |

|    | 5.7              | Implementation Examples                              | 96  |  |

|    | 5.8              | Design Considerations                                | 103 |  |

|    | 5.9              | Chapter Summary                                      | 104 |  |

| 6  | Cas              | caded Resonant Switched-Capacitor Converter          | 106 |  |

|    | 6.1              | Background and Motivation                            | 106 |  |

|    | 6.2              | Overview of Data Center Power Delivery Architecture  | 108 |  |

|    | 6.3              | Cascaded Resonant Converter                          | 110 |  |

|    | 6.4              | Design Guidelines and Experimental Results           | 114 |  |

|    | 6.5              | Zero Voltage Switching Technique                     | 120 |  |

|    | 6.6              | Cascading and Interleaving Strategies                | 128 |  |

|    | 6.7              | Chapter Summary                                      | 131 |  |

| 7  | Mu               | lti-Resonant Switched-Capacitor Converter            | 133 |  |

|    | 7.1              | Background and Motivation                            | 133 |  |

|    | 7.2              | Theoretical Performance Limit of SC converters       | 135 |  |

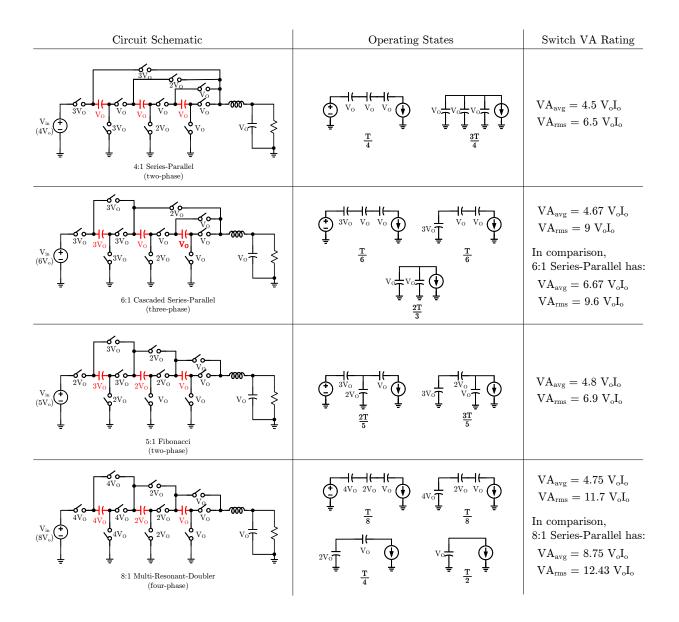

|    | 7.3              | Generation and Synthesis of Multi-Phase Topologies   | 137 |  |

|    | 7.4              | 8-to-1 Multi-Resonant-Doubler Converter              | 139 |  |

|    | 7.5              | 6-to-1 Cascaded Series-Parallel Converter            | 147 |  |

|    | 7.6              | Alternative Topology Variations                      | 151 |  |

|    | 7.7              | Chapter Summary                                      | 154 |  |

| 8  | Mu               | lti-Level Binary Hybrid Switched-Capacitor Converter | 156 |  |

|    | 8.1              | Background and Motivation                            | 156 |  |

|    | 8.2              | Proposed Topology                                    | 157 |  |

|    | 8.3              | Hardware Design and Experimental Results             | 161 |  |

|    | 8.4              | Alternative Topology Variation                       | 166 |  |

|    | 8.5              | Chapter Summary                                      | 168 |  |

| 9  | Fut              | ure Work                                             | 171 |  |

| 10 | Con              | clusions                                             | 176 |  |

| Bi | Bibliography 178 |                                                      |     |  |

|    |                  |                                                      |     |  |

# List of Figures

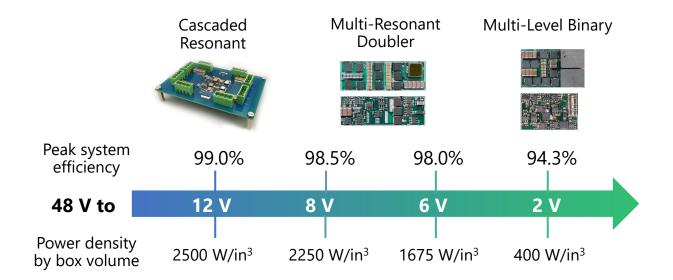

| 1.1        | Performance summary of the hybrid and resonant SC converter prototypes pre-<br>sented in this dissertation.                                                       |     |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| 2.1        | Schematic drawing of a buck converter                                                                                                                             | 5   |  |

| 2.2        | A high-performance GaN-based 48-to-12 V buck converter [1]                                                                                                        | 5   |  |

| 2.3        | Schematic drawing of a 2-to-1 SC converter.                                                                                                                       | 6   |  |

| 2.4        | A high-performance 48-to-24 V switched-capacitor converter [8]                                                                                                    |     |  |

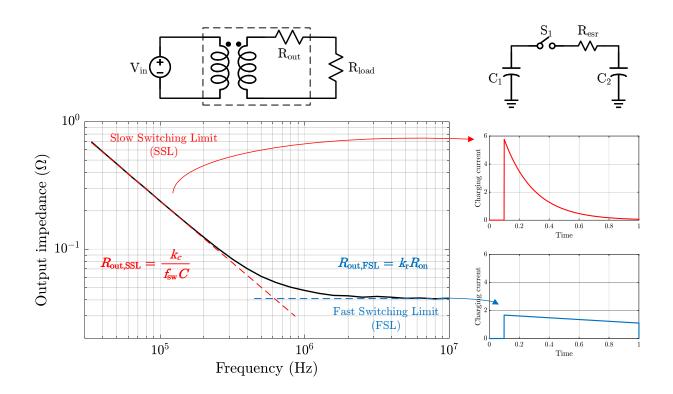

| 2.5        | Pure SC converter: ideal circuit model, output impedance vs. switching fre-<br>quency, origin of capacitor charge sharing loss (capacitor charging current at SSL |     |  |

|            | and FSL)                                                                                                                                                          | 8   |  |

| 2.6        | Soft-charging operation with ideal current load.                                                                                                                  | 10  |  |

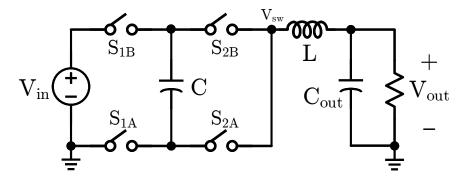

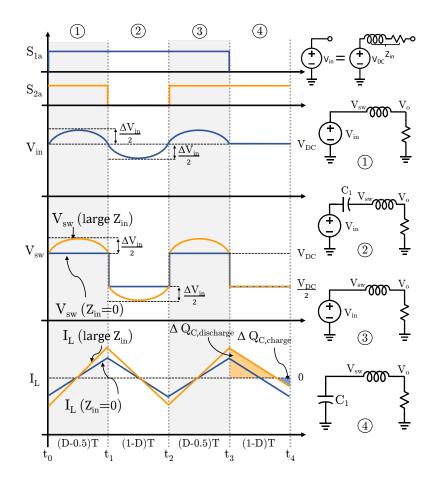

| 2.7<br>2.8 | Schematic drawing of a three-level buck converter / 2-to-1 ReSC converter<br>Key operating waveforms and circuit states of a three-level buck converter at duty   | 11  |  |

|            | ratio $> 0.5$ .                                                                                                                                                   | 12  |  |

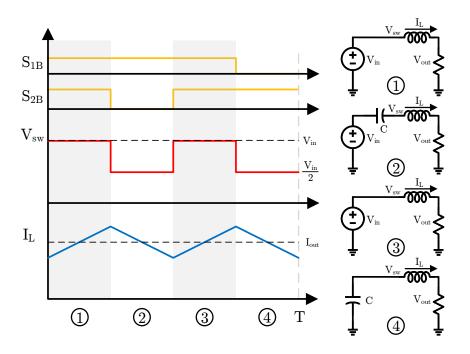

| 2.9        | Key operating waveforms and circuit states of a 2-to-1 resonant SC converter.                                                                                     | 13  |  |

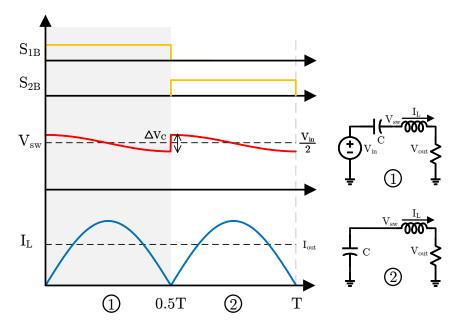

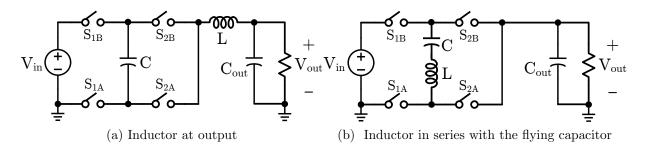

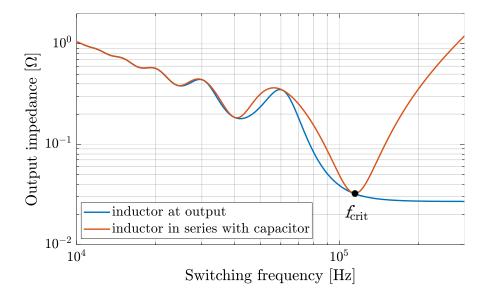

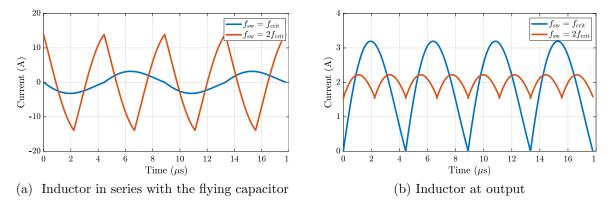

| 2.10       | 2-to-1 SC converter with different augmenting inductor locations.                                                                                                 | 14  |  |

| 2.11       | Output impedance with respect to inductor location.                                                                                                               | 15  |  |

| 2.12       | Inductor current at different locations and frequencies.                                                                                                          | 15  |  |

| 2.13       | Effect of duty ratio on rms current and output impedance                                                                                                          | 17  |  |

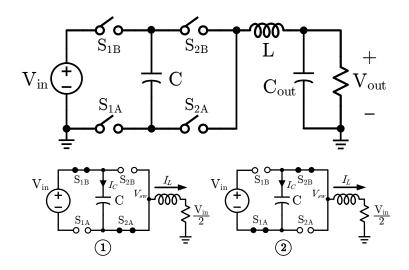

| 3.1        | Schematic drawing of a 2-to-1 resonant switched-capacitor converter and its two                                                                                   | 20  |  |

| 0.0        | operating states.                                                                                                                                                 | 20  |  |

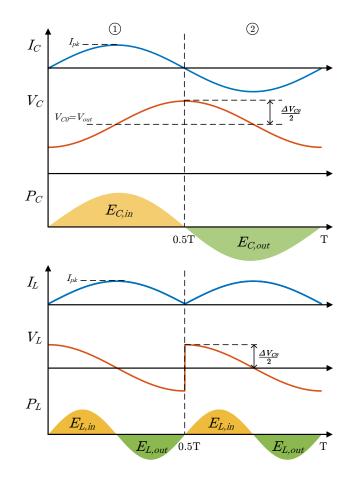

| 3.2        | Current, voltage, and power waveforms of the flying capacitor and the resonant                                                                                    | 01  |  |

| 0.0        | inductor in a 2-to-1 ReSC converter.                                                                                                                              | 21  |  |

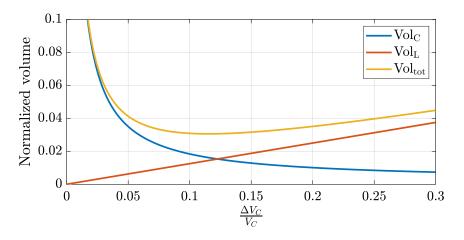

| 3.3        | The effects of flying capacitor voltage ripple on capacitor volume, inductor volume                                                                               | 0.4 |  |

| 9.4        | and overall volume for a 2-to-1 ReSC converter (assuming $\rho_{E,C}/\rho_{E,L} = 100$ ).                                                                         | 24  |  |

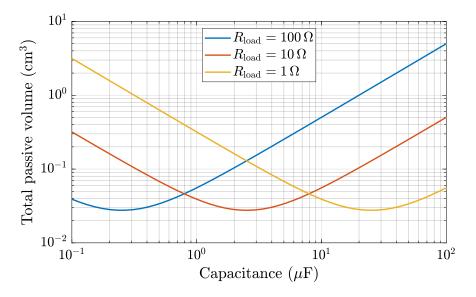

| 3.4        | Given fixed output power and switching frequency, the 2-to-1 ReSC converter can always achieve the same minimum total passive component volume. But the           |     |  |

|            | optimum capacitance (and inductance) allocation depends on the magnitude of                                                                                       |     |  |

|            | the load resistance. Parameters for the plot: $P_{\rm out} = 100$ W, $f_{\rm sw} = 100$ kHz,                                                                      |     |  |

|            | $\rho_{E,C} = 0.1 \text{ J/cm}^3, \ \rho_{E,C}/\rho_{E,L} = 100.$                                                                                                 | 25  |  |

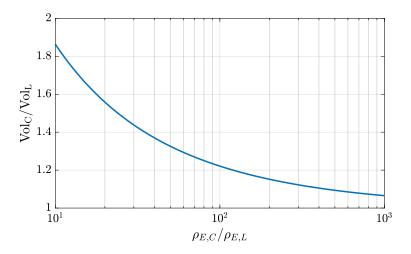

| 3.5        | The optimum volume ratio between capacitor and inductor with respect to their                                                                                     |     |  |

|            | energy density ratio.                                                                                                                                             | 26  |  |

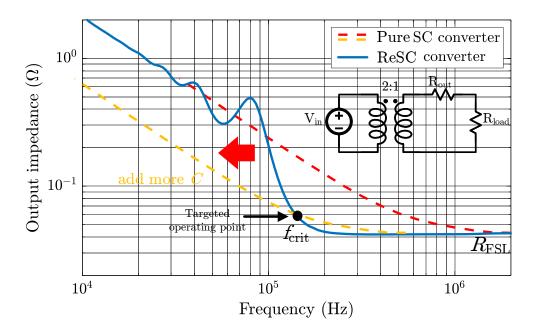

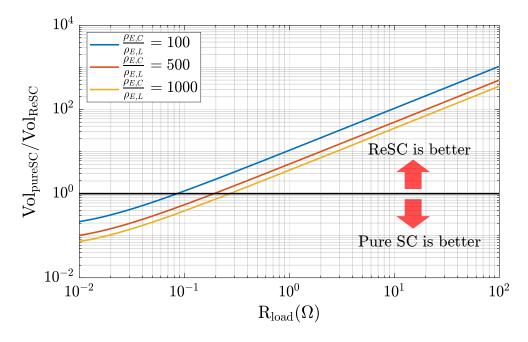

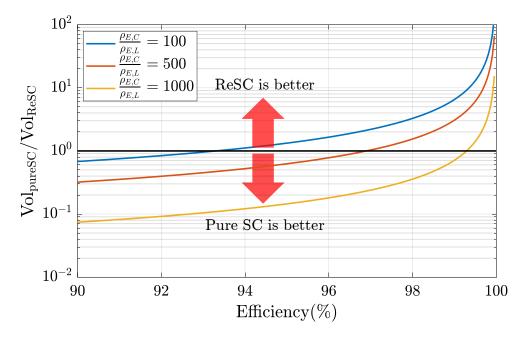

| $3.6 \\ 3.7$ | Output impedance of 2-to-1 Pure SC and ReSC converters vs. frequency Relative passive component volume comparison between 2-to-1 pure SC converter                                    | 28       |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.8          | and 2-to-1 ReSC converter (assuming converter series resistance $R_{\rm FSL} = 5 \text{ m}\Omega$ ).<br>Relative passive component volume comparison between 2-to-1 pure SC converter | 30       |

| 0.0          | and 2-to-1 ReSC converter with respect to converter efficiency.                                                                                                                       | 31       |

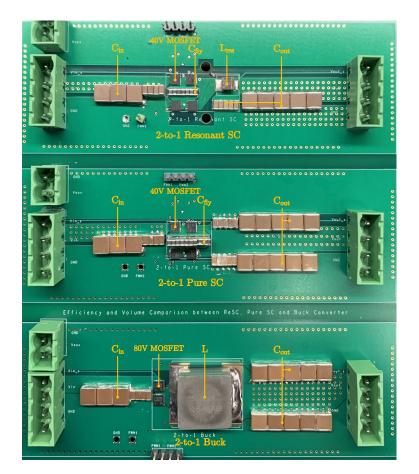

| 3.9          | Photograph of the hardware prototype for passive component volume and effi-                                                                                                           |          |

|              | ciency comparisons                                                                                                                                                                    | 32       |

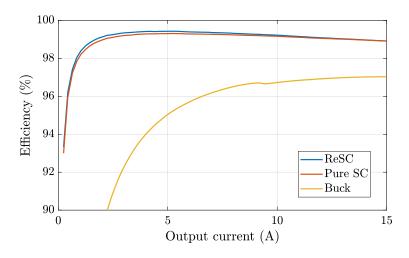

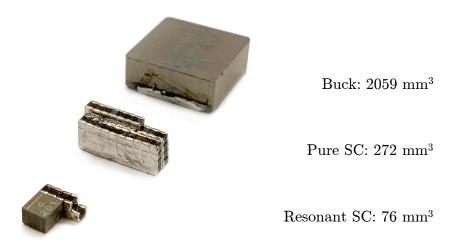

|              | <i>J</i> ( <i>J</i> 5W )                                                                                                                                                              | 34       |

| 3.11         | Required passive component volume to achieve the efficiency performance shown                                                                                                         |          |

| 0.10         | in Fig. 3.10.                                                                                                                                                                         | 35       |

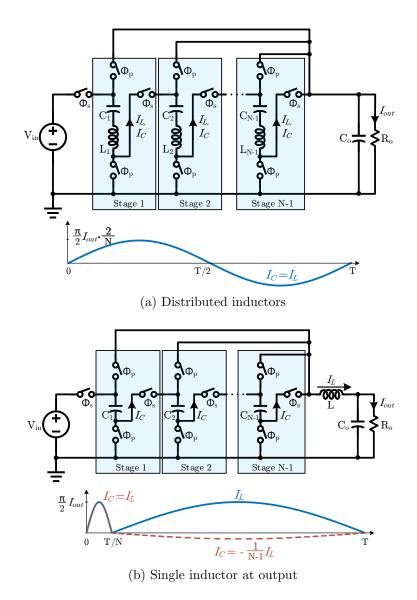

|              | N-to-1 resonant series-parallel converters with different inductor locations<br>Minimized total passive volume of N-to-1 resonant series-parallel converters with                     | 39       |

|              | different inductor locations (normalized to the 2-to-1 case)                                                                                                                          | 41       |

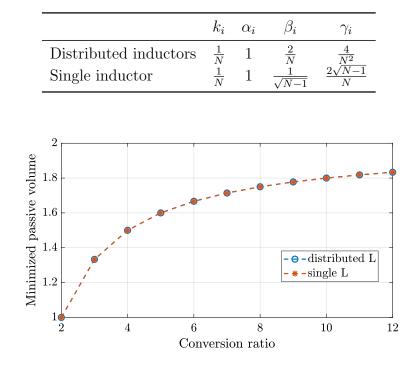

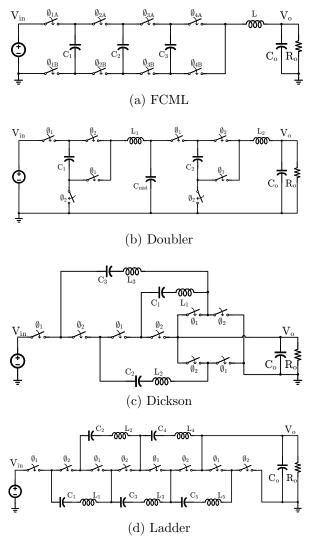

|              | 4-to-1 resonant switched-capacitor converter topologies                                                                                                                               | 43       |

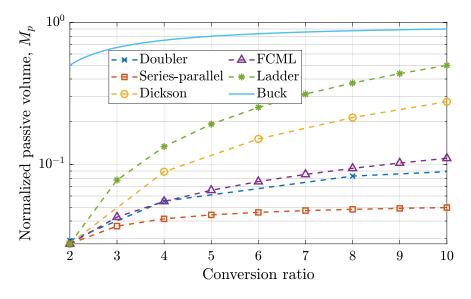

|              | Normalized passive volume (assuming $\rho_{E,C}/\rho_{E,L} = 100$ ). Lower is better                                                                                                  | 44       |

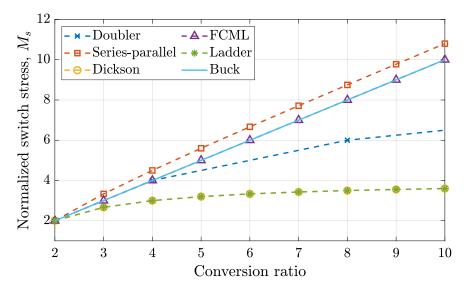

|              | Normalized switch stress. Lower is better.                                                                                                                                            | 45       |

|              | 4-to-1 ReSC topology comparison.                                                                                                                                                      | 46       |

|              | Schematic drawings of two example regulated hybrid converters. $\dots$                                                                                                                | 47       |

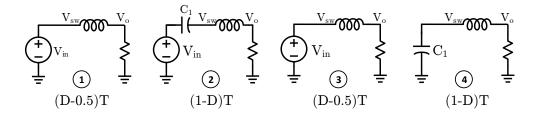

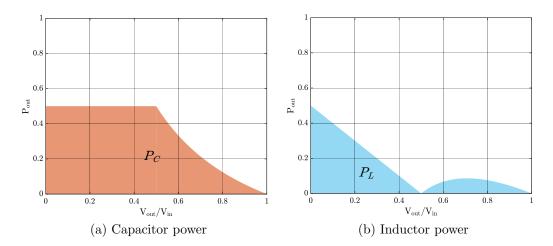

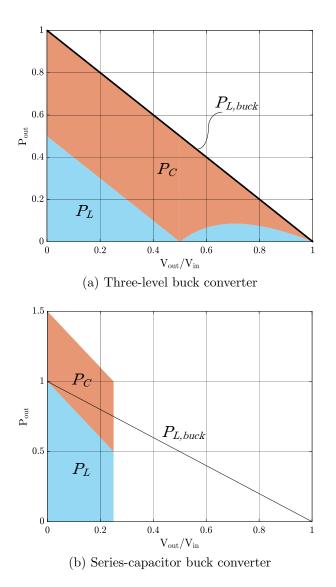

|              | Circuit operating states of a three-level buck converter at $D < 0.5$                                                                                                                 | 47<br>48 |

|              | Circuit operating states of a three-level buck converter at $D > 0.5$ Reactive power processed by the passive components of a three-level buck converter.                             | 40<br>48 |

|              | Average power processed by the passive components of a three-level back converter. Average power processed by the passive components in hybrid converters                             | 49       |

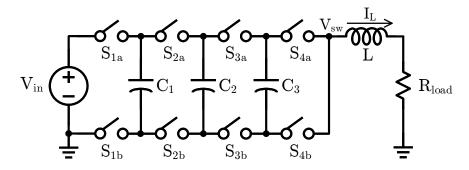

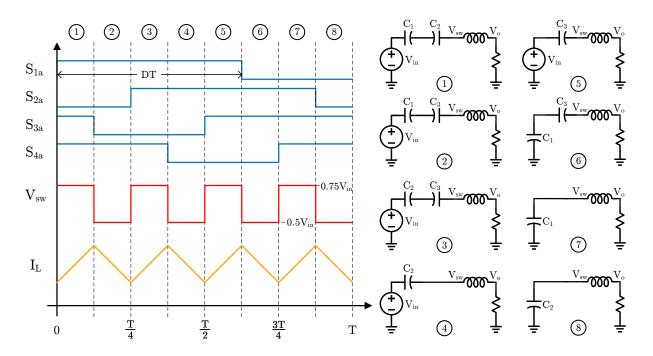

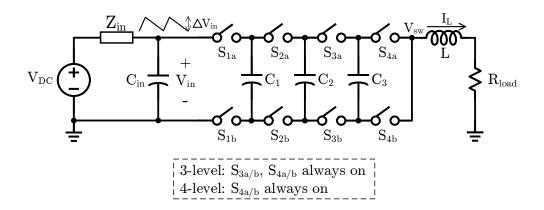

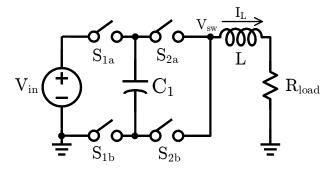

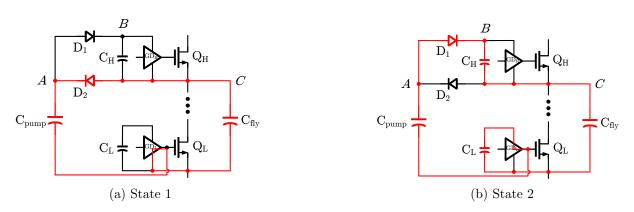

| $4.1 \\ 4.2$ | Schematic drawing of a five-level FCML buck converter                                                                                                                                 | 54       |

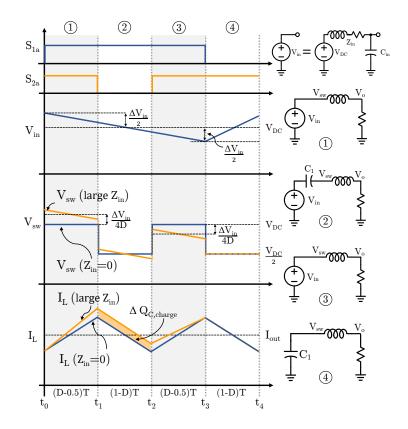

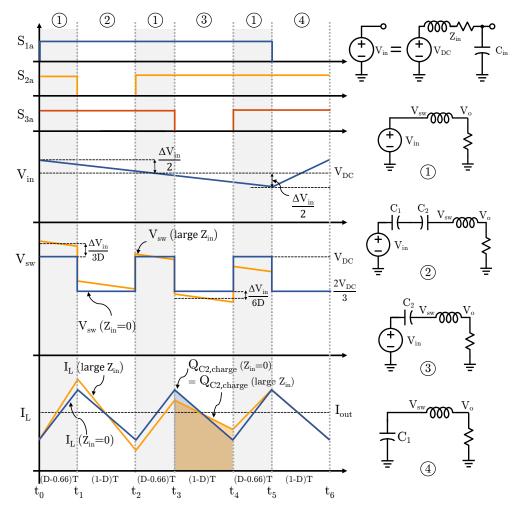

| 4.3          | buck converter at $\frac{1}{2} < D < \frac{3}{4}$                                                                                                                                     | 55       |

|              | is determined by the low-ESR low-ESL input capacitor                                                                                                                                  | 56       |

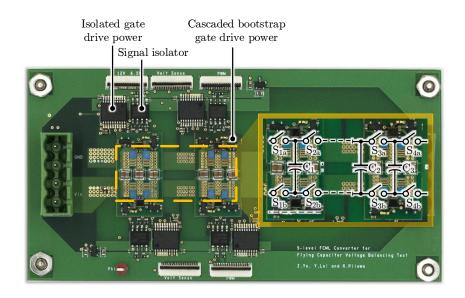

| 4.4          | Photograph of the configurable $3/4/5$ -level FCML buck converter prototype                                                                                                           | 56       |

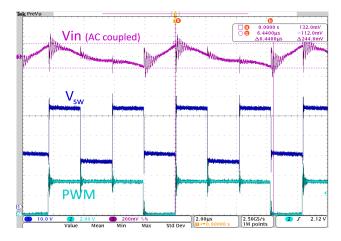

| 4.5          | Measured input voltage ripple of a three-level FCML converter                                                                                                                         | 57       |

| 4.6          | Measured flying capacitor voltage of a three-level FCML converter.                                                                                                                    | 58       |

| 4.7          | The flying capacitor voltage of a three-level FCML converter will increase in the                                                                                                     | 50       |

| 10           | presence of input voltage ripple                                                                                                                                                      | 59<br>61 |

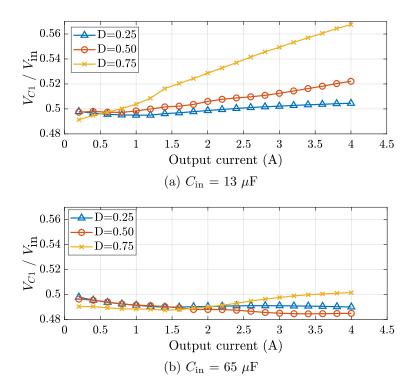

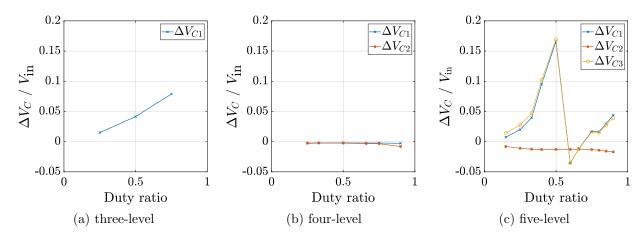

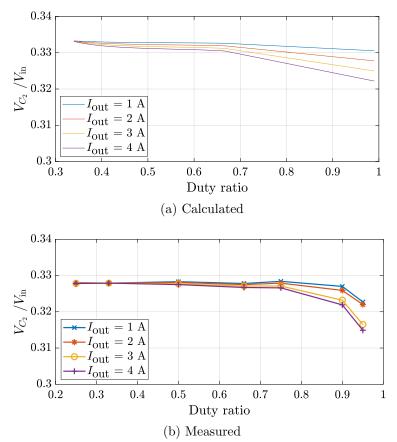

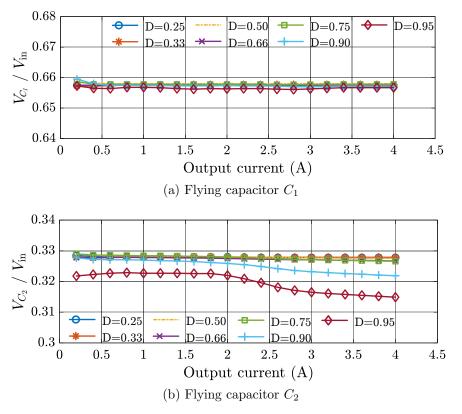

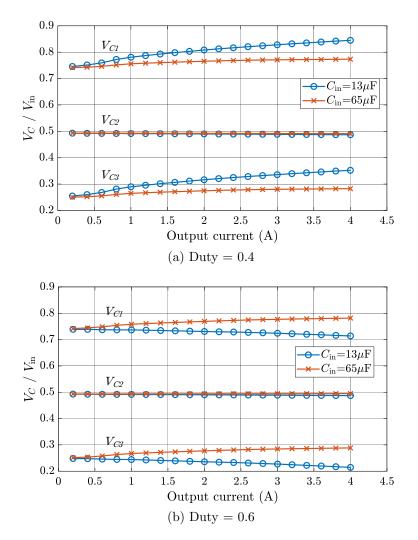

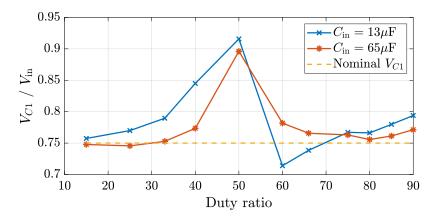

| $4.8 \\ 4.9$ | Measured flying capacitor voltage variations ( $C_{in} = 13 \ \mu F$ , $I_{out} = 4 \ A$ ) Simulated step response of the flying capacitor voltages using the proposed models         | 61       |

| 4.10         | $(\Delta V_{\text{in}} \text{ is the input})$                                                                                                                                         | 63       |

| 4.10         | of input voltage ripple.                                                                                                                                                              | 64       |

| 4.11         | The flying capacitor voltages of a four-level FCML converter can stabilize them-                                                                                                      | <u> </u> |

|              | selves in the presence of input voltage ripple.                                                                                                                                       | 65       |

|              |                                                                                                                                                                                       |          |

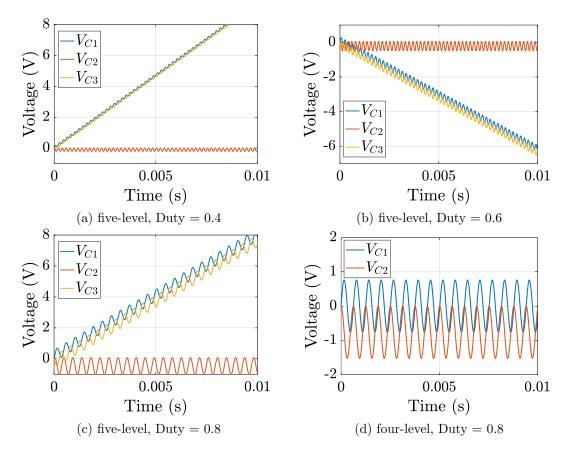

|      | Measured flying capacitor voltages of a four-level FCML covnerter ( $C_{\rm in} = 13 \ \mu {\rm F}$ ).                                                                 | 66       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | Measured flying capacitor voltages of a five-level FCML converter                                                                                                      | 67       |

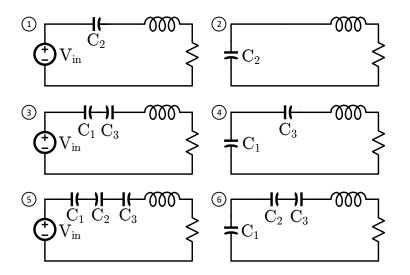

|      | Measured $C_1$ voltage of five-level FCML converter                                                                                                                    | 68       |

| 4.15 | Six possible circuit configurations that can generate the $\frac{1}{2}V_{in}$ voltage level in a                                                                       |          |

|      | five-level FCML converter. PSPWM utilizes the first four states                                                                                                        | 68       |

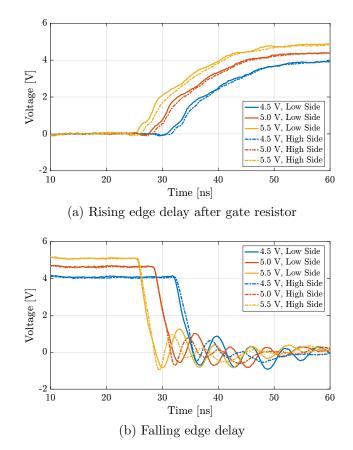

| 4.16 | Measured LM5113 gate driver propagation delay (from gate driver input to output).                                                                                      | 71       |

| 4.17 | Schematic drawing of a three-level FCML buck converter                                                                                                                 | 72       |

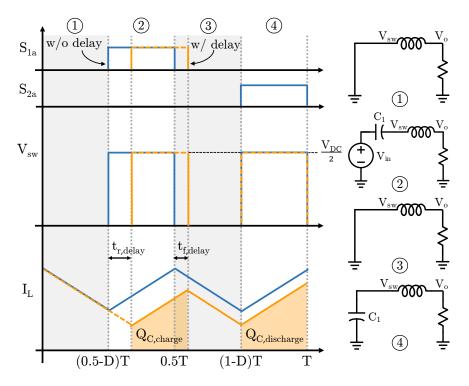

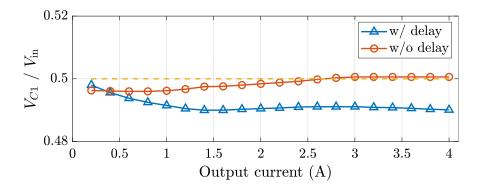

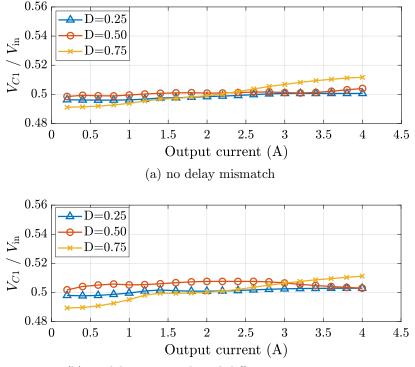

| 4.18 | The effects of gate signal delay mismatch on capacitor balancing for a three-level                                                                                     |          |

|      | FCML converter.                                                                                                                                                        | 72       |

| 4.19 | Schematic drawing of a cascaded bootstrap circuit.                                                                                                                     | 73       |

|      | Measured effect of gate delay mismatch on capacitor voltage (three-level, $C_{\rm in} =$                                                                               |          |

|      | $65 \ \mu F, D = 0.25)$                                                                                                                                                | 73       |

| 4.21 | Measured flying capacitor voltage of a three-level FCML covnerter ( $C_{\rm in} = 65 \ \mu {\rm F}$ ).                                                                 | 74       |

|      | The effect of input ripple on capacitor balancing at light-load condition of a                                                                                         | • •      |

| 1.22 | three-level converter with $D > 0.5$ .                                                                                                                                 | 75       |

| 1 23 | Switching cell design.                                                                                                                                                 | 76       |

| 4.20 |                                                                                                                                                                        | 10       |

| 5.1  | Schematic drawing of a cascaded bootstrap circuit on a four-level FCML buck                                                                                            |          |

|      | converter.                                                                                                                                                             | 79       |

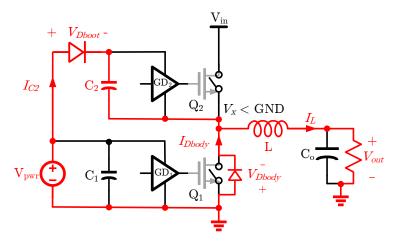

| 5.2  | Inductor current flow in a two-level buck converter during deadtime                                                                                                    | 81       |

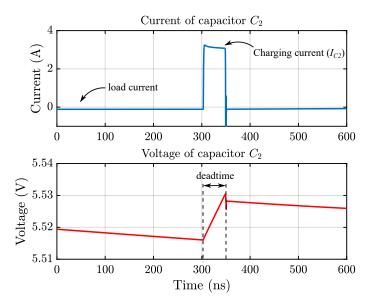

| 5.3  | Simulated cascaded bootstrap circuit during deadtime ( $V_{pwr} = 5 \text{ V}, V_{Dbody} = 2 \text{ V},$                                                               |          |

|      | $V_{Dboot} = 0.6 \text{ V})$                                                                                                                                           | 83       |

| 5.4  | Additional circuitry to observe the overcharge effect of bootstrap operation at                                                                                        |          |

|      | deadtime.                                                                                                                                                              | 84       |

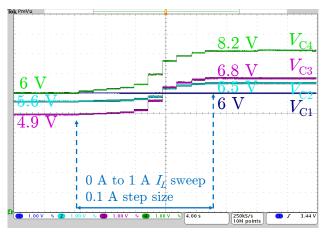

| 5.5  | Voltage on cascaded bootstrap capacitors.                                                                                                                              | 85       |

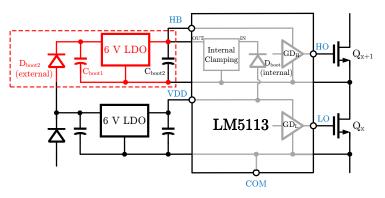

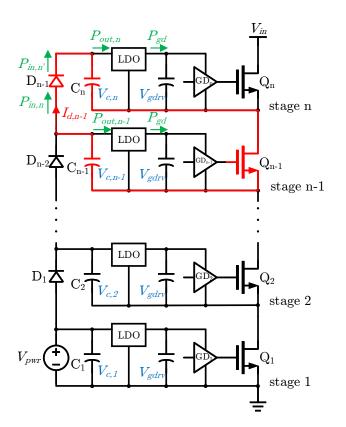

| 5.6  | Schematic drawing of a cascaded bootstrap circuit with LDOs on a string of                                                                                             | 00       |

| 0.0  | series-connected switches.                                                                                                                                             | 86       |

| 5.7  | Simulated cascaded bootstrap voltages of a six-level FCML converter under dif-                                                                                         | 00       |

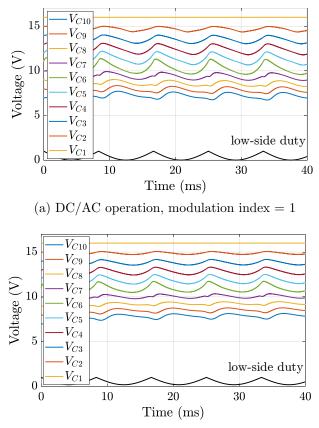

| 0.1  | ferent operating conditions ( $f_{\rm ac} = 60$ Hz, $f_{\rm sw} = 120$ kHz, $V_{\rm pwr} = 16$ V, $C_{\rm boot} =$                                                     |          |

|      | $20 \ \mu\text{F}$ , switch: GS61004B[95], GD: Si827x[96], diode: $V_f = 0.6 \text{ V}$ , $R_{on} = 5 \Omega$ ).                                                       | 89       |

| 5.8  | Schematic drawing of a double charge pump circuit. $\dots \dots \dots$ | 90       |

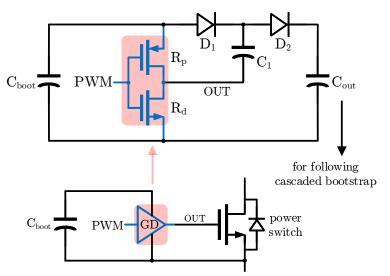

|      | Schematic drawing of a gate-driven charge pump circuit.                                                                                                                | 90<br>91 |

| 5.9  |                                                                                                                                                                        |          |

|      | Different ways to connect gate-driven charge pump                                                                                                                      | 92       |

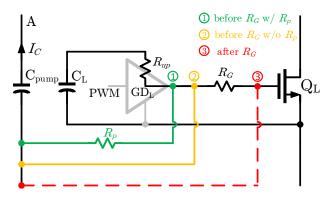

| 5.11 | Turn-on behavior of EPC 2016C GaN switch with gate-driven charge pump con-                                                                                             |          |

|      | nected (simulation parameters: $R_{\rm up} = 1 \ \Omega, R_G = R_p = 10 \ \Omega, C_L = C_H = C_{\rm pump}$                                                            | 0.0      |

| - 10 | $= 1 \ \mu F, V_{C_L} = 5 \ V). \dots \dots$                     | 93       |

|      | Schematic drawing of a synchronous bootstrap circuit.                                                                                                                  | 94       |

|      | Key switching waveform of the synchronous bootstrap circuit.                                                                                                           | 95       |

| 5.14 | Measured cascaded synchronous bootstrap voltages on a seven-level FCML buck                                                                                            |          |

|      | converter at no-load condition (switch: EPC2001C, $f_{sw} = 140 \text{ kHz}$ )                                                                                         | 95       |

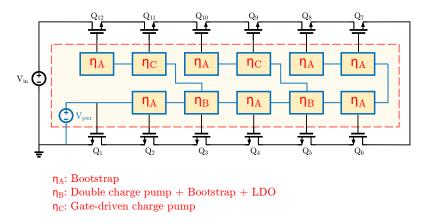

|      | Proposed gate drive power supply methods for a seven-level FCML converter                                                                                              | 96       |

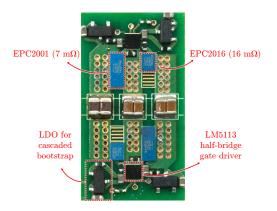

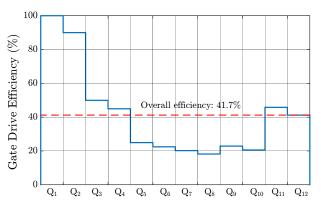

| 5.16 | Calculated efficiency of the proposed gate drive power supply circuit.                                                                                                 | 97       |

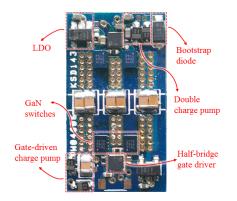

|      | Power module (switching cell) design with proposed gate drive power supply circuit.                                 |     |

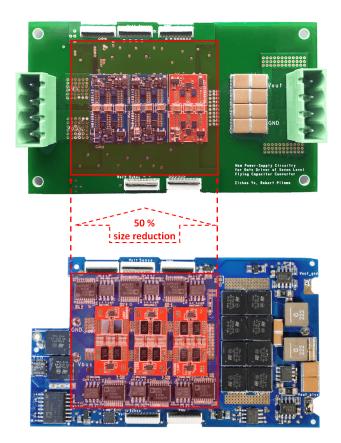

|------|---------------------------------------------------------------------------------------------------------------------|-----|

| 5.18 | Comparison of the hardware prototype with [99]                                                                      | 98  |

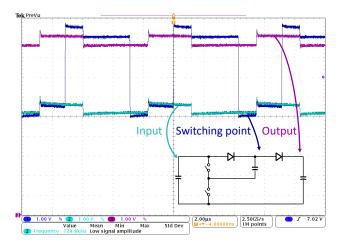

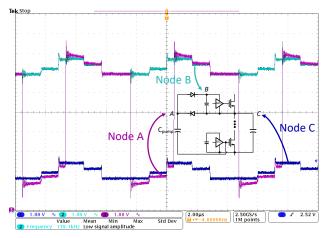

| 5.19 | Measured double charge pump operation                                                                               | 99  |

| 5.20 | Measured gate-driven charge pump operation.                                                                         | 100 |

| 5.21 | An example gate drive circuit for a 4-to-1 Dickson converter.                                                       | 101 |

| 5.22 | An example gate drive circuit for a 4-to-1 series-parallel converter                                                | 102 |

| 5.23 | Block diagram of a proposed gate driver IC with built-in LDO and self-oscillatory                                   |     |

|      | inverter for cascaded bootstrap and gate-driven charge pump operations                                              | 102 |

| 5.24 | Powering a four-level FCML converter with the proposed gate driver IC                                               | 103 |

| 6.1  | An example data center power delivery system from line to point-of-loads                                            | 108 |

| 6.2  | Comparison of different approaches to convert 48 V down to 1–2 V                                                    | 109 |

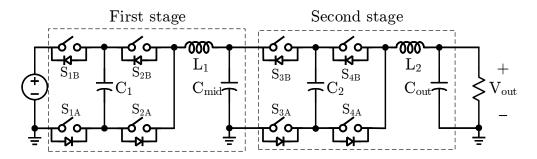

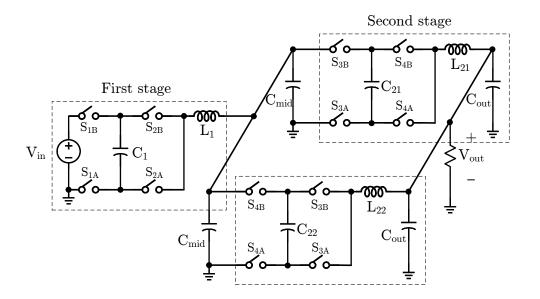

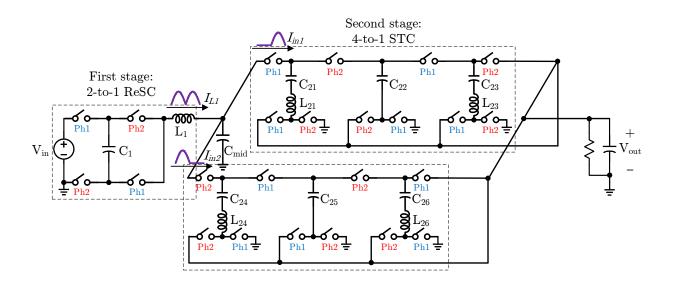

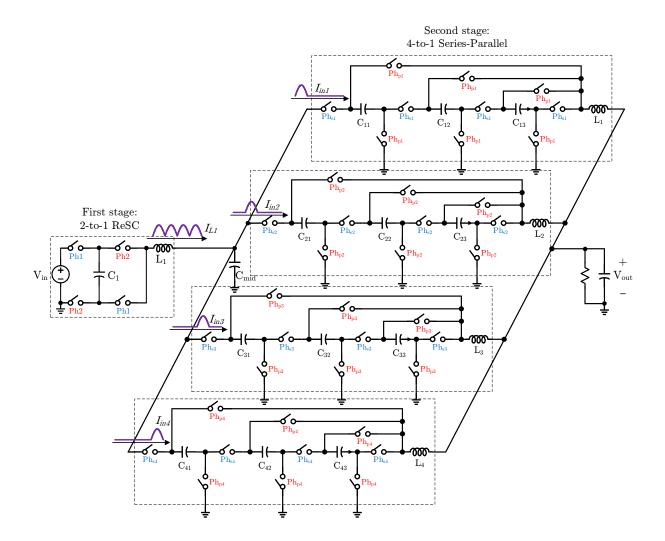

| 6.3  | Schematic drawing of a cascaded resonant converter.                                                                 | 110 |

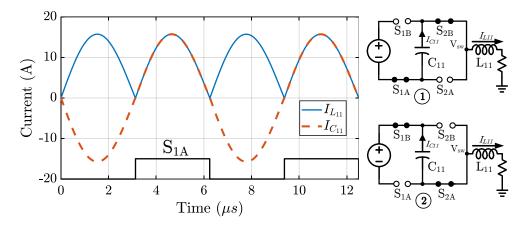

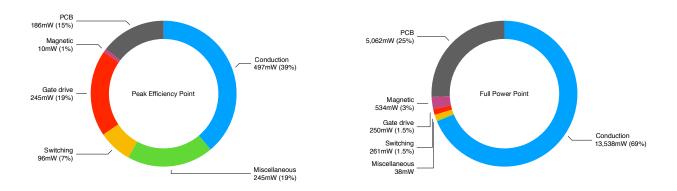

| 6.4  |                                                                                                                     | 111 |

| 6.5  |                                                                                                                     | 112 |

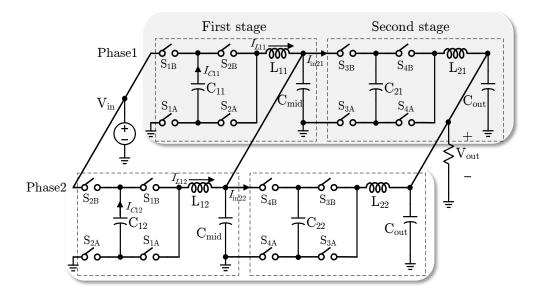

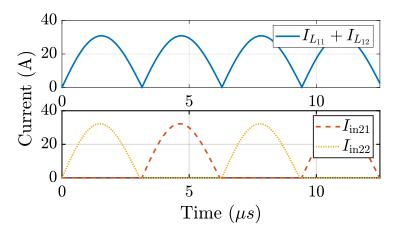

| 6.6  | Minimize $C_{\rm mid}$ with interleaved design.                                                                     | 112 |

| 6.7  | Comparison of various ReSC converters at a conversion ratio of 4-to-1.                                              | 113 |

| 6.8  |                                                                                                                     | 114 |

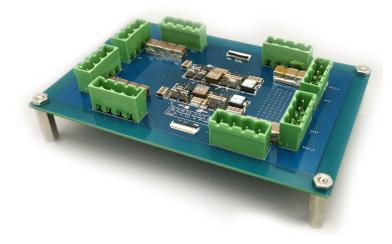

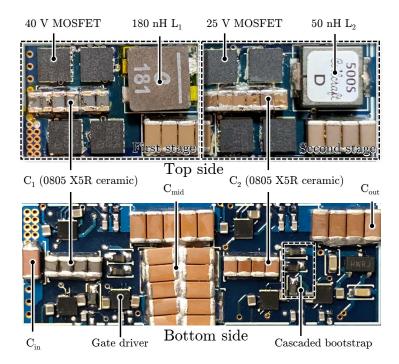

| 6.9  | Photograph of the hardware prototype (two-phase interleaved).                                                       | 116 |

| 6.10 | Annotated photograph of the converter (one phase). Dimensions: $1.38 \times 0.46 \times 0.22$                       |     |

|      | inch $(3.5 \times 1.17 \times 0.56 \text{ cm})$ .                                                                   | 117 |

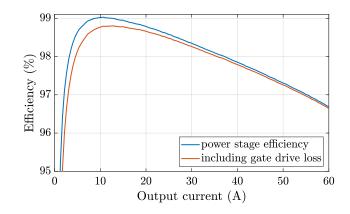

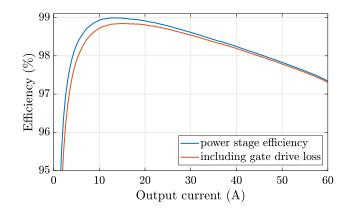

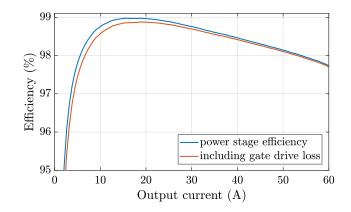

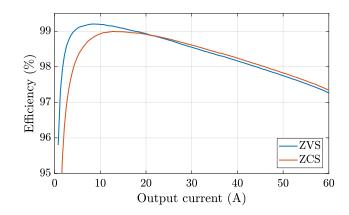

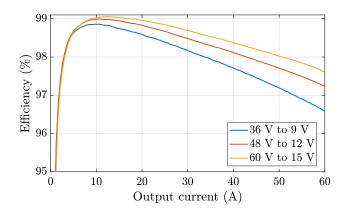

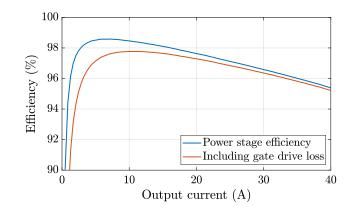

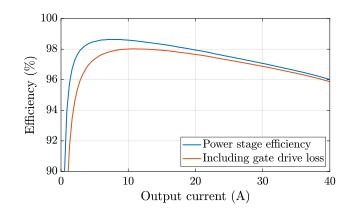

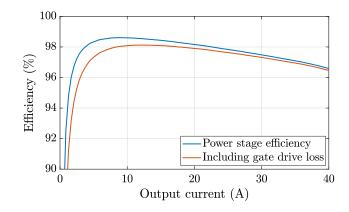

| 6.11 | Measured 36 V to 9 V efficiency $(f_{sw} = 91 \text{ kHz})$ .                                                       | 118 |

| 6.12 | Measured 48 V to 12 V efficiency $(f_{sw} = 100 \text{ kHz})$ .                                                     | 118 |

| 6.13 | Measured 60 V to 15 V efficiency $(f_{sw} = 111 \text{ kHz})$ .                                                     | 119 |

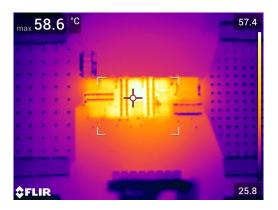

| 6.14 | Thermal performance with fan cooling only $(V_{in} = 48 \text{ V}, I_{out} = 60 \text{ A})$ .                       | 119 |

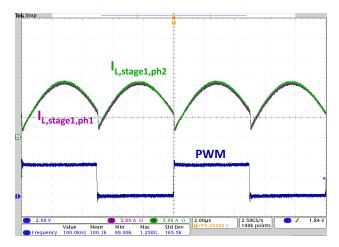

| 6.15 | The interleaved inductor currents at the first stage                                                                | 120 |

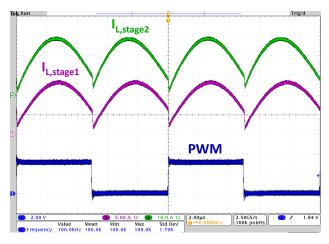

| 6.16 | The inductor currents of the two stages (one phase).                                                                | 120 |

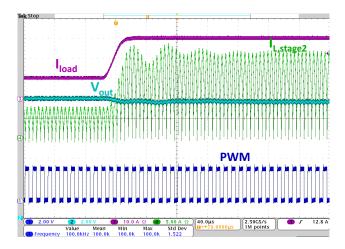

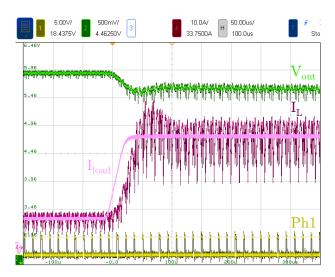

| 6.17 | Transient response of 10 A to 30 A load step.                                                                       | 121 |

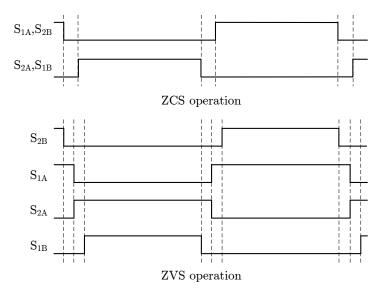

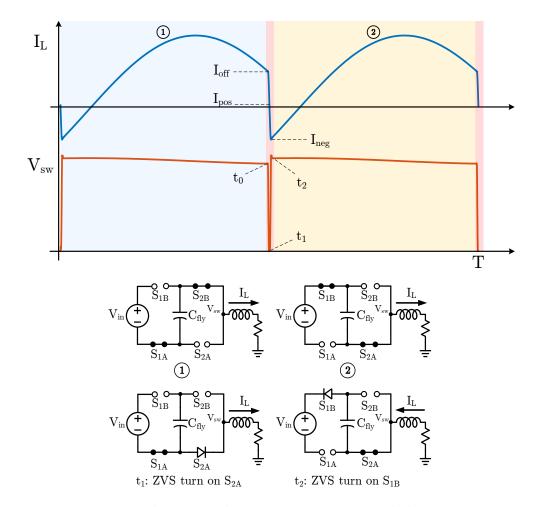

| 6.18 | Control signals for different modes of operation.                                                                   | 121 |

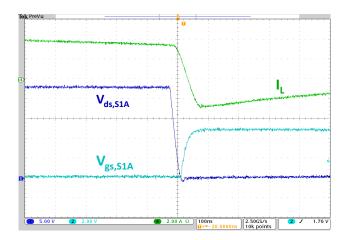

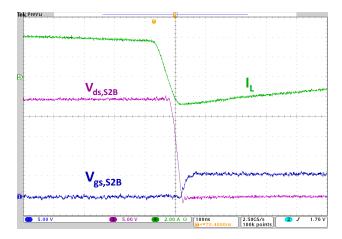

| 6.19 | Zero voltage switching operation on cascaded resonant converter.                                                    | 122 |

| 6.20 |                                                                                                                     | 123 |

| 6.21 | Effect of deadtime on the turn-on of low-side switch ( $L = 180 \text{ nH}, C_{\text{oss,tot}} = 1.5 \text{ nF}$ ). | 124 |

| 6.22 | Achieving complete ZVS at light load with the optimum deadtime                                                      | 125 |

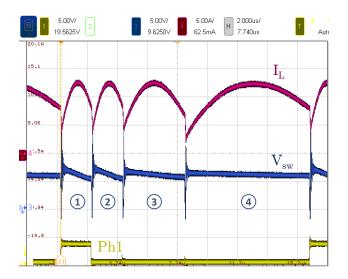

| 6.23 | $I_{\rm L}$ and $V_{\rm sw}$ under ZVS                                                                              | 125 |

|      |                                                                                                                     | 126 |

|      |                                                                                                                     | 126 |

|      |                                                                                                                     | 127 |

|      |                                                                                                                     | 127 |

|      | 1 01                                                                                                                | 128 |

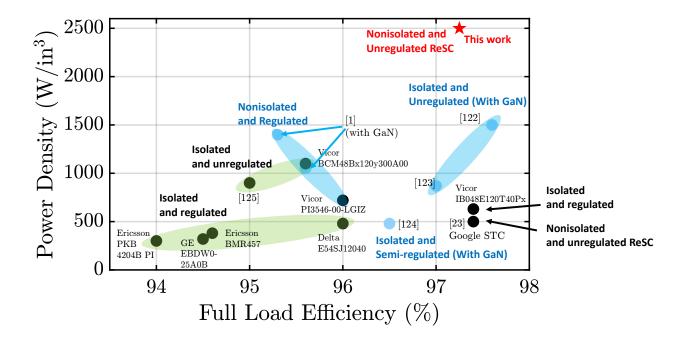

| 6.29 | Comparison of full-load efficiency and power density of state-of-the-art commer-                                    |     |

|      | cial products and previously published research                                                                     | 129 |

| 6.30 | An alternative 12-switch design of the cascaded resonant converter with single first-stage.                       | 130 |

|------|-------------------------------------------------------------------------------------------------------------------|-----|

|      | Cascading 2-to-1 ReSC with two-phase interleaved switched-tank converters (STC).                                  |     |

| 7.1  | The maximum voltage gain in two-phase SC converters follows the Fibonacci                                         | 104 |

|      | 1                                                                                                                 | 134 |

| 7.2  |                                                                                                                   | 135 |

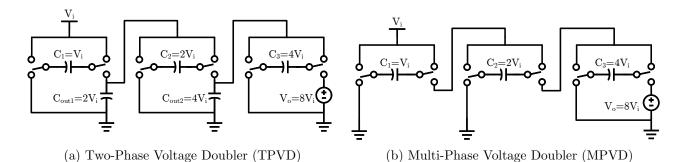

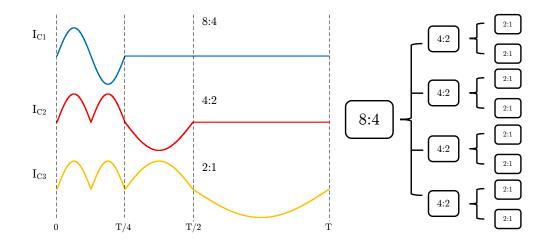

| 7.3  | 0                                                                                                                 | 138 |

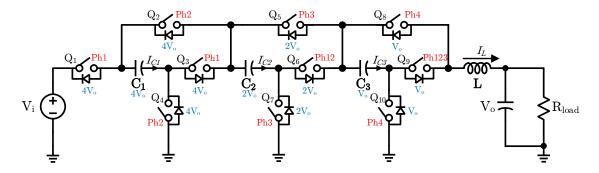

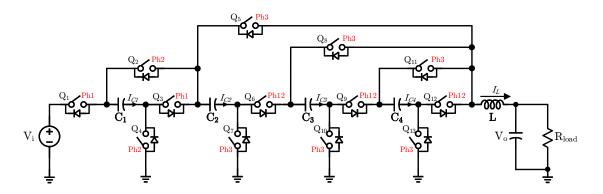

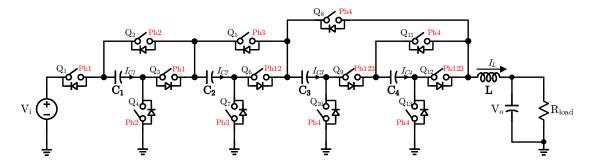

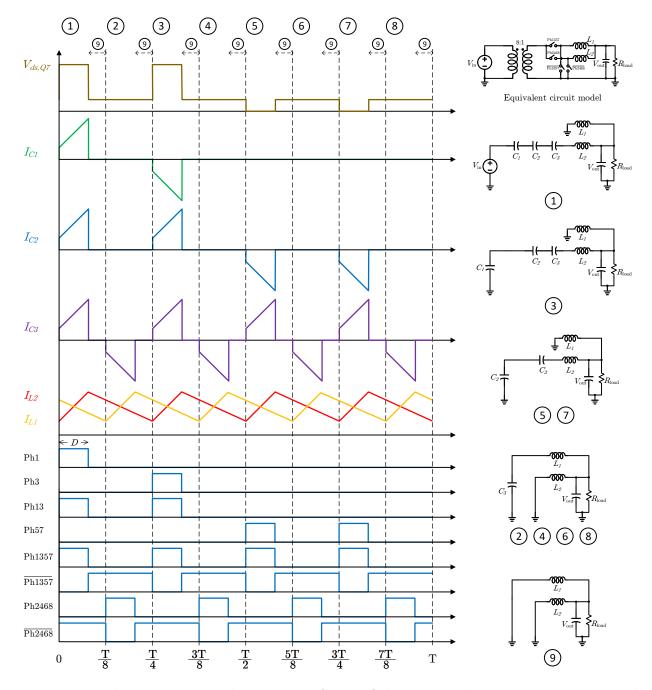

| 7.4  | Schematic drawing of the 8-to-1 multi-resonant-doubler converter with device ratings and control signals labeled. | 139 |

| 7.5  | Inductor and capacitor current waveforms, control signals, and equivalent circuits                                |     |

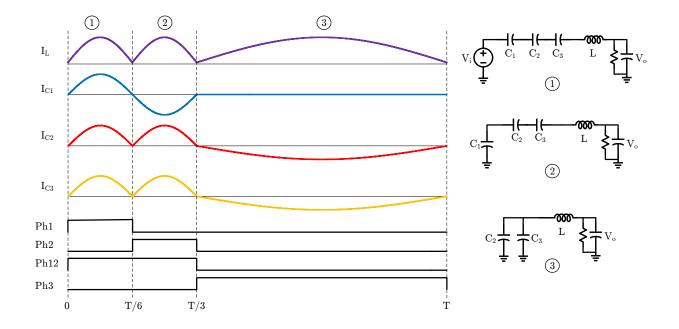

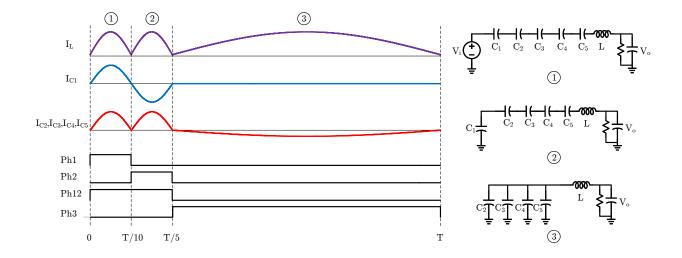

|      | of the 8-to-1 multi-resonant-doubler converter.                                                                   | 140 |

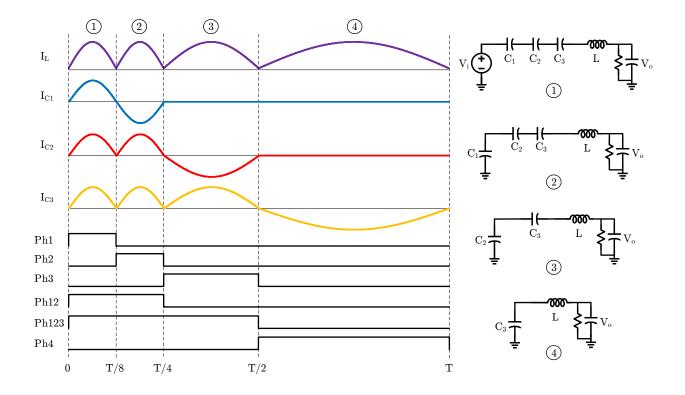

| 7.6  | Photograph of the converter prototype. Dimensions: $1.38 \times 0.46 \times 0.22$ inch (3.5                       | 140 |

|      |                                                                                                                   | 142 |

| 7.7  | 8                                                                                                                 | 144 |

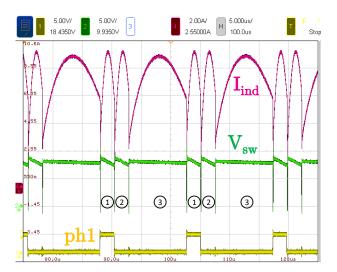

| 7.8  | 1                                                                                                                 | 144 |

| 7.9  |                                                                                                                   | 145 |

| 7.10 |                                                                                                                   | 145 |

|      |                                                                                                                   | 146 |

|      |                                                                                                                   | 146 |

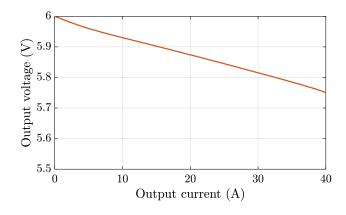

|      | Load regulation ( $V_{in} = 48 \text{ V}$ , $V_{out} = 6 \text{ V}$ )                                             | 147 |

|      | capacitors and the associated switches                                                                            | 148 |

| 7.15 | Schematic drawing of the 6-to-1 cascaded series-parallel converter with device                                    |     |

|      | ratings and control signals labeled.                                                                              | 148 |

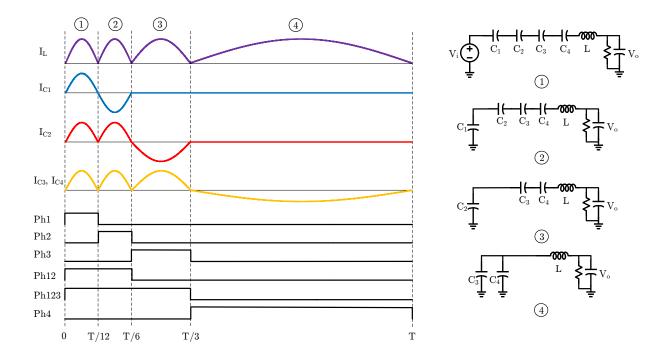

| 7.16 | Inductor and capacitor current waveforms, control signals, and equivalent circuits                                |     |

|      | 1                                                                                                                 | 149 |

| 7.17 | Theoretical performance comparison of various ReSC converters and buck con-                                       |     |

|      | verter at 6-to-1 conversion ratio                                                                                 | 150 |

|      | Inductor current and switch node voltage of the cascaded series-parallel converter.                               | 150 |

| 7.19 | Measured 48 V to 8 V efficiency of the cascaded series-parallel converter ( $f_{\rm sw} =$                        |     |

|      | 68 kHz)                                                                                                           | 151 |

| 7.20 | Fundamental building block of the multi-phase resonant SC converter                                               | 152 |

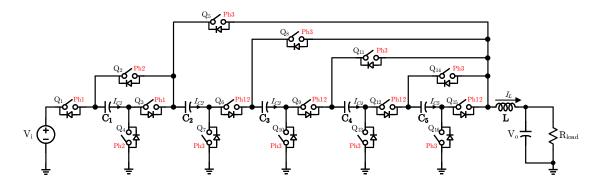

| 7.21 | Schematic drawing of an 8-to-1 cascaded series-parallel converter (three-phase).                                  | 152 |

| 7.22 | Inductor and capacitor current waveforms, control signals, and equivalent circuits                                |     |

|      | of the 8-to-1 cascaded series-parallel converter                                                                  | 153 |

| 7.23 | Schematic drawing of a 10-to-1 cascaded series-parallel converter (three-phase).                                  | 153 |

| 7.24 | Inductor and capacitor current waveforms, control signals, and equivalent circuits                                |     |

|      | 1                                                                                                                 | 154 |

| 7.25 | Schematic drawing of a 12-to-1 cascaded doubler series-parallel converter (four-                                  |     |

|      | phase)                                                                                                            | 154 |

| 7.26 | Inductor and capacitor current waveforms, control signals, and equivalent circuits of the 12-to-1 cascaded doubler series-parallel converter               |     |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

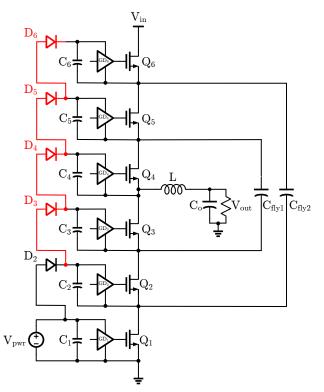

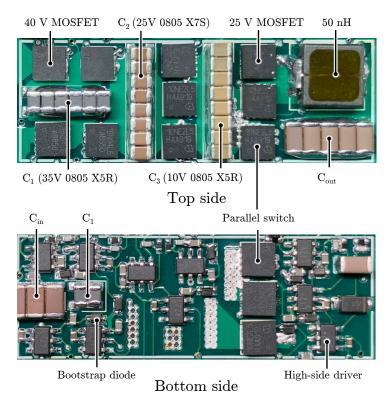

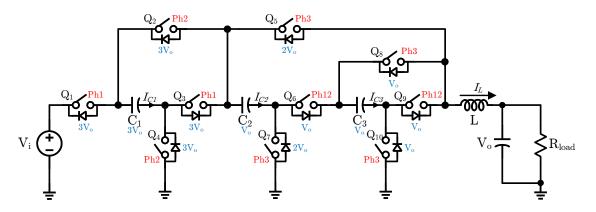

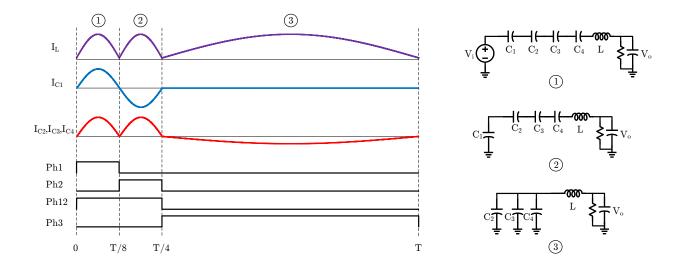

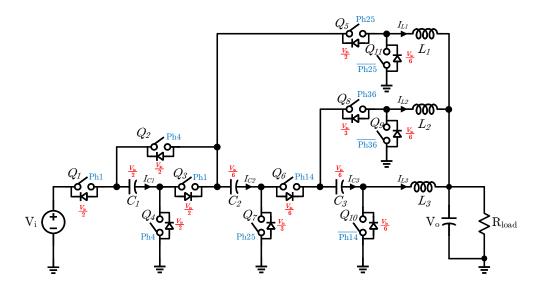

| 8.1  | Schematic drawing of the proposed MLB-PoL converter. The device voltage ratings are labeled in red and the operating phases of the switches are labeled in |     |  |

|      | blue                                                                                                                                                       | 158 |  |

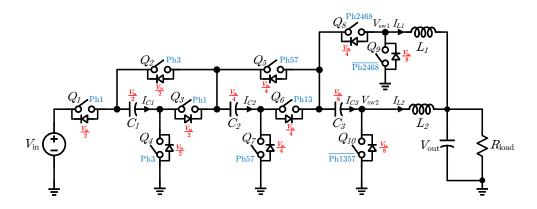

| 8.2  | Voltage, current and PWM waveforms of the proposed MLB-PoL converter and equivalent circuit models.                                                        | 159 |  |

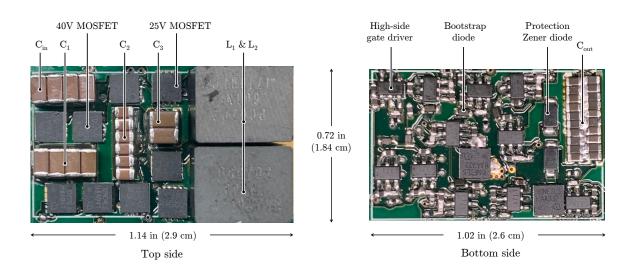

| 8.3  | Photograph of the prototype. Dimensions: $1.14 \times 0.72 \times 0.39$ inch $(2.9 \times 1.84)$                                                           |     |  |

|      | $\times$ 1.01 cm)                                                                                                                                          | 162 |  |

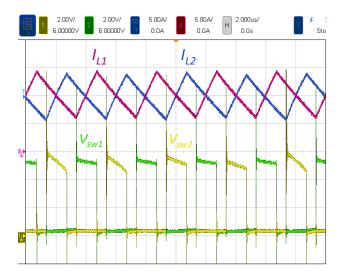

| 8.4  | Balanced interleaved inductor currents ( $V_{\text{out}} = 2 \text{ V}, I_{\text{out}} = 20 \text{ A}$ )                                                   | 164 |  |

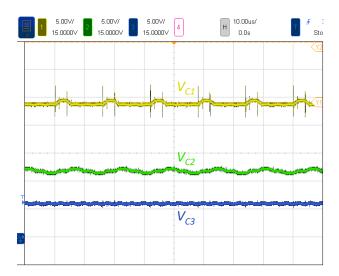

| 8.5  | Flying capacitor voltages at $V_{\text{out}} = 2$ V and $I_{\text{out}} = 20$ A                                                                            | 164 |  |

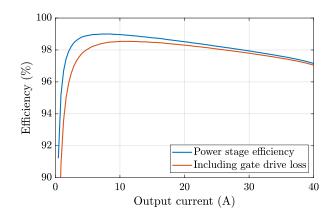

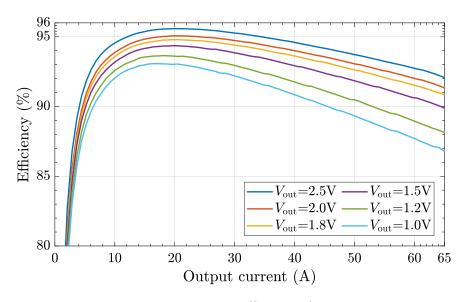

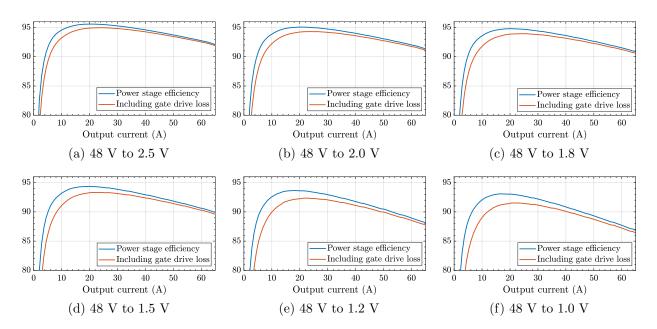

| 8.6  | Measured power stage efficiency from 48 V to 2.5–1.0 V                                                                                                     | 165 |  |

| 8.7  | Measured efficiency at various output voltages                                                                                                             | 166 |  |

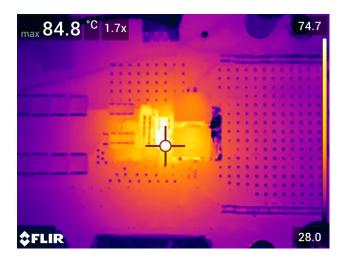

| 8.8  | Thermal performance at equilibrium with 110 CFM fan cooling only ( $V_{out} = 2.0$                                                                         |     |  |

|      | V, $I_{out} = 65$ A)                                                                                                                                       | 168 |  |

| 8.9  | Schematic drawing of a proposed multi-phase hybrid converter with a 6-to-1 SC                                                                              |     |  |

|      | stage and three interleaved output inductors. The device voltage ratings are                                                                               |     |  |

|      | labeled in red and the operating phases of the switches are labeled in blue                                                                                | 169 |  |

| 8.10 | Voltage, current, PWM waveforms, and equivalent circuit models of the proposed                                                                             |     |  |

|      | hybrid SC converter with a 6-to-1 SC stage                                                                                                                 | 170 |  |

|      |                                                                                                                                                            |     |  |

# List of Tables

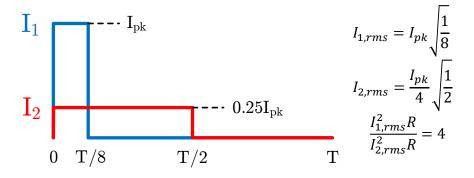

| $2.1 \\ 2.2$                              | Comparison of three-level buck converter and 2-to-1 ReSC converter Comparison of different inductor placement strategies                                                          | $\begin{array}{c} 14 \\ 17 \end{array}$ |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4                  | Key converter operating parametersMain component listing of the hardware prototypeComparison between calculation and experimentKey parameters of N-to-1 series-parallel converter | 33<br>34<br>35<br>41                    |

| $4.1 \\ 4.2$                              | Four-level converter system parameters                                                                                                                                            | 62<br>62                                |

| 5.1<br>5.2                                | Measured voltage on cascaded bootstrap capacitors with 1 A load current and different deadtimes                                                                                   | 86                                      |

|                                           | (at 250 $V_{\rm DC}$ to 100 $V_{\rm DC}$ )                                                                                                                                        | 99                                      |

| 5.3                                       | Comparison with the state of the art solution                                                                                                                                     | 100                                     |

| 5.4                                       | Key characteristics of the five proposed methods                                                                                                                                  | 104                                     |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Main component listing of the cascaded resonant converter                                                                                                                         | 116<br>129                              |

| 7.1                                       | Maximum attainable conversion ratios                                                                                                                                              | 136                                     |

| 7.2                                       | Comparison of component number of 8-to-1 SC converters                                                                                                                            | 141                                     |

| 7.3                                       | Comparison of passive and active component utilization of 8-to-1 SC converters                                                                                                    | 141                                     |

| 7.4                                       | Key prototype parameters of the MRD converter                                                                                                                                     | 143                                     |

| 7.5                                       | Main component listing of the MRD converter                                                                                                                                       | 143                                     |

| 7.6                                       | Comparison of this work and existing high-step-down bus converters                                                                                                                | 147                                     |

| $8.1 \\ 8.2$                              | Voltage rating and operating frequency of the main active and passive components<br>Comparison of the voltage conversion strategies of selected hybrid converters at              |                                         |

| 0.0                                       | 48 V to 2 V conversion                                                                                                                                                            | 161                                     |

| 8.3                                       | Main component listing of the prototype                                                                                                                                           | 163                                     |

| 8.4                                       | Key parameters of the prototype                                                                                                                                                   | 163                                     |

| 8.5 | Summary of measured efficiency and power density results at various output |     |

|-----|----------------------------------------------------------------------------|-----|

|     | voltages                                                                   | 167 |

| 8.6 | Comparison of this work and existing hybrid SC works                       | 167 |

| 8.7 | Comparison of this work and existing commercial products                   | 168 |

#### Acknowledgments

The completion of this dissertation is an important milestone in my life as it marks the closure of my graduate school journey. The young adulthood years are of singular importance and I have no regrets having spent them with a world class engineering research group. I am sincerely thankful for the many great people I have met on my journey; their mentorship, support, love, and care are the driving force that keeps me going and makes me want to better myself.

My first thank you goes to my adviser, Professor Robert Pilawa, for bringing me into his research group and for his guidance over the past six years. To this day, I have no idea how a personal statement put together in one night got his attention and marvel at how quickly I made the decision to study power electronics immediately following our first meeting in which he showed me some cool circuit boards. It was a great decision, and I could not have asked for a better adviser. I am incredibly grateful to Robert for providing me unlimited trust, freedom, and support which is everything a Ph.D. student could hope for in an adviser. Robert is a pioneer researcher of hybrid switched-capacitor technologies and brought me into this most promising field of power electronics and has guided me through cutting edge research that has a tangible impact on society. He has shown me, by example, what it means to be an enthusiastic researcher, presenter, and visionary leader. His engineering and research acumen aside, he has taught me to be a better thinker, investigator, and innovator. To quote Sir Isaac Newton: "If I have seen further, it is only because I have had the opportunity to stand on the shoulders of these giants." Robert has always encouraged me to "think outside the box," challenge prevailing thought, and look to the future. Thank you, Robert, for helping me become a more capable person and for giving me the tools to overcome the challenges that lie on the road ahead. I will forever treasure our association.

I would like to thank my committee members Professors Seth Sanders, Kristofer Pister, and Jason Stauth for their valuable suggestions and guidance throughout the course of this work. In particular, the passive component modeling work in Chapter 3 would not have been possible without the inspiration I received from Professor Sanders through our fascinating discussion on the fundamental limits of direct and indirect power in power converters. I am also grateful for the outstanding power and energy faculty of University of Illinois at Urbana-Champaign (UIUC), especially Professor Pete Sauer who served as my undergraduate adviser and sparked my first interest in power and Professor Philip Krein who taught my first power electronics class and laboratory. I much admire their dedication and humility which have deeply influenced my approach to research and life.

Thank you to all fellow members of the Pilawa group, past and present: Yutian Lei, Shibin Qin, Christopher Barth, Enver Candan, Andrew Stillwell, Ben Macy, Joseph Liu, Pourya Assem, Derek Heeger, Zitao Liao, Derek Chou, Thomas Foulkes, Yizhe Zhang, Nathan Pallo, Nathan Brooks, Pei Han Ng, Samantha Coday, Maggie Blackwell, Rose Abramson, Kelly Fernandez, Joseph Schaadt, Logan Horowitz, Yicheng Zhu, Rahul Iyer, Yong-Long Syu, Ting Ge, Nathan Ellis, Raya Mahony, and many more. The last six years would not be the same without their company and I hope our paths cross again in the future. A special thank you to Yutian and Shibin, my big brothers and role models. I am greatly indebted for the strong push they gave me at start of my graduate studies. I appreciate their wisdom, humor, and the hotwok lunch boxes we had together. Yutian's leading work on hybrid switched capacitors set a high bar for me to leap and has been the driving force behind my pursuit of excellence to this day. I also wish to thank Joseph and Pourya for being supportive peers throughout our journey. We started together in the same year and now we are finishing together. The classes we took, the circuits we drew, the snacks we shared, and the seasons we had in the sun are sure to be wonderful memories I will cherish forever. A special thanks to Zitao, the best artist among all the engineers I know, and probably the best engineer amongst all artists! Many of the figures and photos in my papers and slides would not look as good as they do without his advice and help. Moreover, Zitao and his wife Yun Hao had been with me throughout the many highs and lows of graduate school. Their presence and support were indispensable for me in navigating through the difficulties of 2020 due to COVID-19 and I cannot overstate my gratitude. Many thanks to Rose for working on multiple projects with me. Her coding and soldering were instrumental in achieving many of the records we broke together. She also provided English editing help for many of our publications. Heartfelt thanks to Nathan Pallo for building and operating a well-equipped group laboratory, and to Maggie and Sam for making birthday cakes and desserts for everyone in the group. Each of you went out of your way to make my graduate life more memorable and I am incredibly thankful for it.

It has been a privilege to work alongside some incredibly talented researchers in power electronics. I would like to thank Dr. Pradeep Shenoy for providing invaluable guidance in the early stages of my graduate study. I appreciate the inspiring bi-weekly discussions with Professor Minjie Chen and his group. I am grateful to Professor Hanh-Phuc Le for offering me the rare opportunity to present my work at the renowned IEEE PELS webinar as a graduate student. I am also thankful to Professor Jason Stauth and his group for their excellent and inspiring work in the hybrid switched-capacitor field. It was a great honor to be part of this brilliant society and to work with them in pushing the boundaries of high-performance power converters.

I want to thank the staff of EECS at Berkeley and the staff of ECE at UIUC. They played a huge role in this long journey. Special thanks to Shirley Salanio for always being so responsive and helpful in fielding every question, request, and petition. I will always remember her warm smile and friendly greetings. Thank you, Robin Smith and Joyce Mast, for managing the events and all the expenses for the power and energy group of UIUC. Being under your conscientious care made me feel I was part of a big, happy family. I would also like to acknowledge the funding and material support we received from our industry partners including Texas Instruments, Intel, Infineon, and the Advanced Research Projects Agency-Energy (ARPA-E).

Finally, and most significantly, I would like to express my deepest gratitude to my family to whom I dedicate this thesis. To my mother, Li Hui: it is because of you that I have been able to start and finish this long journey to the completion of my Ph.D. Your unconditional love and continual encouragement have given me optimism and the positive attitude necessary to face life's challenges. Your unwavering trust and support have enabled me to follow my heart and pursue my dreams. Your rigorous approach towards research and your position as professor influenced me from an early age and seeded my academic potential. I cannot express the full extent of my gratitude to my Aunt Shelly and Uncle Vern for providing me a warm and loving second home in the United States. The unparalleled view of Lake Michigan and the indefatigable "Blue Dragon" have refueled my gas tank every year and allowed me to keep going. Thanks to Shelly for always making herself a simple phone call away whenever I need her support. Her wisdom, vision, and love have led me through dark times more than once. Lastly, thanks to my father, Ye Qiang, now in heaven: I wish to share all my accomplishments with you and make you proud.

## Chapter 1

## Introduction

### 1.1 Introduction

Power converters are electrical energy processing circuits to convert and control energy flow between different voltage domains and magnitudes. Similar to the blood circulatory system in the human body, power converters manage and deliver the requisite electrical energy in computer systems, personal electronics, automobiles, and just about every possible application of electricity. The most desirable features of power converters are high reliability, high energy efficiency, high power density, and low cost.

Thanks to continued research and development in the past decades, switch-mode power supplies with two alternating voltage levels (such as buck and boost converters) have become prevalent, offering high reliability and low cost. However, a variety of applications have recently emerged with very challenging design requirements that conventional technologies cannot meet. For instance, in space- and thermally-constrained smartphone systems, the conventional buck-based battery chargers cannot support the demand of faster charging speed, owing to their limited efficiency performance. In datacenter and telecommunication systems, the explosive growth of information processing and the associated energy consumption require innovative power delivery architecture and technology with better efficiency and power density.

Due to the fundamental structure of conventional two-level designs, trends toward higher efficiency and power density have reached the point that further improvement becomes increasingly difficult. It is therefore important to rethink the whole problem and come up with new solutions which could achieve a drastic performance improvement. This dissertation focuses on a topological effort to more efficiently utilize the active and passive devices, through a hybrid switched-capacitor/inductor approach. By introducing more switches, the system can have more than two voltage levels (as in the conventional structures). This allows for the use of high-energy-density capacitors in the voltage conversion process and thus reduces the size and loss of the inductive elements. These inductive elements in turn softly charge/discharge the capacitors, reducing the capacitor charge sharing loss. We believe that increasing the system complexity can offer many advantages and is oftentimes necessary to improve performance. However, it should be done in appropriate ways, which requires a good understanding of both the fundamental limits and the practical design techniques. In this work, we analyze the theoretical benefits of hybrid and resonant switched-capacitor converters, address the important circuit implementation challenges, and design hardware prototypes with cutting-edge performance.

### **1.2** Organization of Thesis

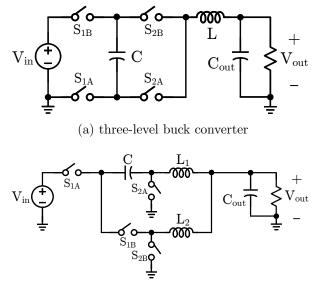

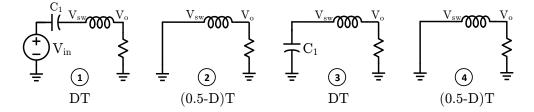

Chapter 2 starts with the fundamental limitations of conventional switched-inductor and switched-capacitor converters and details the attractive benefits of hybrid resonant switchedcapacitor converters. The concept of soft-charging operation is reviewed, together with different possible operating modes including fixed-ratio resonant mode and PWM regulated mode. The characteristics of different inductor augmenting strategies are also discussed.

Chapter 3 presents a new technique to calculate the passive component volume of hybrid resonant switched-capacitor converters, based on the fundamental processed reactive energy. Combining with the switch stress parameter (switch VA ratings), a framework to showcase the relative performance of different topologies is created, which can be used to visualize and compare the utilization of passive and active components.

Several important challenges in the practical implementation of high-performance hybrid switched-capacitor converters are addressed in Chapters 4 and 5. In Chapter 4, a number of bootstrap and charge pump based circuit techniques are developed to power the large number of floating gate drivers in these topologies, in a compact and efficient manner. In Chapter 5, the origins of flying capacitor voltage imbalance in practical flying capacitor multilevel converter designs are investigated experimentally. The presence of non-ideal source impedance and gate signal delay mismatch are found to have non-negligible impacts on capacitor balancing, and even-level designs are proved to have stronger inherent immunity to such nonidealities than odd-level designs.

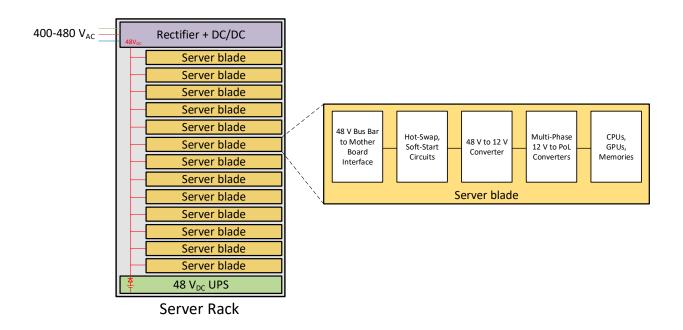

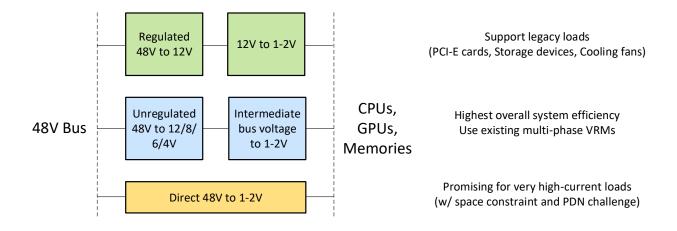

With the above theoretical and practical knowledge, a number of very high-performance discrete prototypes are designed for emerging datacenter power delivery applications in Chapters 6 through 8. Following a brief overview of different datacenter power delivery architectures, Chapter 6 presents a 48 V to 12 V intermediate bus converter design based on a novel cascaded resonant topology, with 99.0% peak efficiency and 2500 W/in<sup>3</sup> power density. The main performance-enhancing features in this design - the two-phase interleaving concept and the zero-voltage-switching control technique - can also be applied to other resonant switched-capacitor topologies.

Chapter 7 further explores the use of resonant SC converters as intermediate bus converters with high conversion ratios, as recent research suggests that a 4 - 6 V intermediate bus voltage could provide the best overall system efficiency. A major challenge in implementing these converters at high conversion ratios is the large number of circuit components. To address this challenge, we introduce a multi-operating-phase concept to greatly reduce the

Figure 1.1: Performance summary of the hybrid and resonant SC converter prototypes presented in this dissertation.

circuit complexity and present a family of multi-phase resonant SC topologies. A 48 V to 6 V multi-resonant-doubler converter is presented with 98.0% peak efficiency and 1675 W/in<sup>3</sup> power density.

Chapter 8 extends the multi-operating-phase concept from fixed-ratio resonant SC converters to regulated hybrid SC converters. A multi-level doubler topology with merged 8-to-1 SC stage and two-phase interleaved buck stage is proposed for direct 48 V to point-of-load applications. Its prototype achieves 95.1% peak efficiency from 48 V to 2V, with near 400 W/in<sup>3</sup> power density, demonstrating one of the best in-class performance. Fig. 1.1 summarizes the performance of the three hardware prototypes presented in Chapters 6 through 8.

Chapter 9 discusses some present challenges and suggests areas for future work. Finally, conclusions are given in Chapter 10.

## Chapter 2

# Fundamentals of Hybrid and Resonant Switched-Capacitor Converters

This chapter first highlights the fundamental limitations of conventional switched-inductor and switched-capacitor (SC) power converters, and then motivates the unique characteristics of hybrid and resonant SC converters. The concept of soft-charging operation is reviewed, followed by different modes of operation to achieve soft-charging. A three-level buck converter and a 2-to-1 resonant SC converter are introduced as examples. The pros and cons of different inductor augmenting strategies are also discussed.

## 2.1 Limitations of Conventional Topologies

### Switched-Inductor Converters

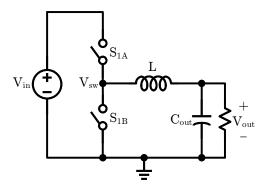

A commonly used switched-mode dc/dc power converter is a buck converter, and its circuit schematic is shown in Fig. 2.1. It can achieve voltage step-down with two switches and one inductor, by switching between two circuit states. In State 1,  $S_{1A}$  is on and  $S_{1B}$  is off, so that the switch node voltage  $V_{sw}$  sees the input voltage  $V_{in}$  and the inductor current ramps up. In State 2,  $S_{1A}$  turns off and  $S_{1B}$  turns on. Then,  $V_{sw}$  is pulled to ground and the inductor current ramps down. Through inductor volt-second analysis, it can be derived that  $V_{out} = DV_{in}$ , where D is the duty ratio defined as the time of State 1 over the total time of the two states. The reactive energy that needs to be processed in the inductor per switching cycle is  $E_L = \frac{(1-D)P_{out}}{f_{sw}}$ , where  $P_{out}$  is the output power and  $f_{sw}$  is the switching frequency. More details about the processed reactive energy of passive components are presented in Chapter 3.

There is an inherent trade-off between achievable efficiency and power density in power converter designs. Since the passive components (e.g. inductors) oftentimes contribute a

Figure 2.1: Schematic drawing of a buck converter.

Figure 2.2: A high-performance GaN-based 48-to-12 V buck converter [1].

great portion to the overall volume, it is desirable to reduce their stored energy and therefore physical size by operating at a high switching frequency. However, this will inevitably result in an increase of semiconductor switching loss, magnetic core loss and ac winding loss, as well as other frequency-dependent losses.

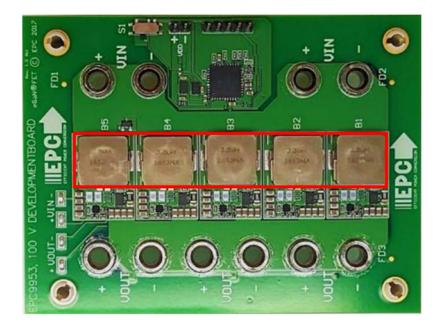

The work in [1] reports a highly optimized GaN-based buck converter design for 48-to-12 V data center applications. Owing to the relatively poor energy density of inductors, the converter is designed to operate at 500 kHz. It achieves 96% efficiency and 1000 W/in<sup>3</sup> power density. However, as can be seen in Fig. 2.2, the inductors dominate the size of the overall

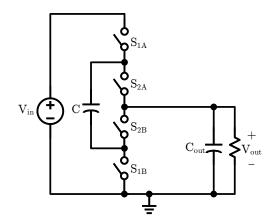

Figure 2.3: Schematic drawing of a 2-to-1 SC converter.

solution. It is difficult to further improve the power density without sacrificing the efficiency, regardless of the advancement of semiconductor technology. On the other hand, the room for efficiency improvement by operating at a lower switching frequency is also limited. Owing to the various loss mechanisms of inductors, it is very challenging to design a buck converter with greater than 98% efficiency for 48-to-12 V conversion, even at a relatively low frequency of 100 to 200 kHz.

### Switched-Capacitor Converters

In comparison to inductors, capacitors are known to have much higher energy densities (e.g., up to 100x-1000x higher) [2], [3]. Specifically, multilayer ceramic capacitors (MLCCs), with their high energy density (comparable to electrolytic capacitors) and low dissipation factor (typically less than 5%), are suitable candidates for energy transfer in power converters. Converters that use only capacitors in the energy conversion process are called switched-capacitor (SC) converters [4]–[6].

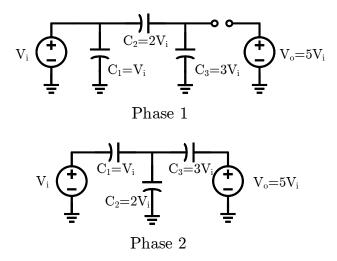

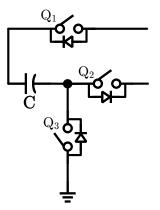

The schematic drawing of a basic 2-to-1 SC converter is shown in Fig. 2.3. In the first half switching cycle, switch  $S_{1A}$  and  $S_{2B}$  are on, and the series combination of flying capacitor C and the output is charged by the input voltage source. In the second half switching cycle,  $S_{2A}$  and  $S_{1B}$  are on. The input is disconnected and the output is powered by the flying capacitor. Through capacitor "charge multiplier vector" analysis [7], it can be found that the flying capacitor voltage and the output voltage are fixed at  $V_{\rm C} = V_{\rm out} = \frac{1}{2}V_{\rm in}$  for the no-load condition. Thanks to the additional voltage level  $(\frac{1}{2}V_{\rm in})$  provided by the flying capacitor, the voltage that needs to be blocked by each switch is only  $\frac{1}{2}V_{\rm in}$ . This allows for the use of low-voltage switches as compared to the conventional two-level switched-inductor converters (e.g., buck converters), in which the switches need to block the full high-level voltage in the system.

Figure 2.4: A high-performance 48-to-24 V switched-capacitor converter [8].

Historically, SC converters are most commonly used as low-power fully integrated converters, due to the fact that SC topologies can achieve lower switch stress at high conversion ratios and capacitors are easier to be integrated on-chip than inductors [9], [10]. In the past, they were less favored for discrete applications (> 10 W) because of the lack of lossless regulation capability, and the efficiency and electromagnetic interference (EMI) challenges associated with charge sharing loss. Recently, there has been a trend to use SC converters for high-power performance-driven applications, where the stringent efficiency and power density requirements cannot be achieved by inductor-based converters. In these applications, the voltage regulation requirement is not as important. Fig. 2.4 shows the photograph of a commercially available 48-to-24 V, 20 A SC converter [8]. It demonstrates up to 99% efficiency and 4000 W/in<sup>3</sup> power density, along with rugged start-up and protection features.

However, regardless of the dedicated design, this SC converter still suffers from the fundamental loss mechanism in pure capacitor-based converters: capacitor charge sharing loss (also known as charge redistribution loss). Here, we briefly review the origin and effects of this loss.

Fig. 2.5 shows the generic SC converter model as well as the output impedance curve with respect to the switching frequency. The generic SC model [11] consists of an ideal transformer and an output impedance  $R_{out}$ . The ideal transformer represents the nominal conversion ratio of the converter. The output impedance  $R_{out}$  incorporates both the conduction loss of the converter as well as the capacitor charge sharing loss, and is a good indication of the efficiency performance of the converter. This impedance is usually plotted against the

Figure 2.5: Pure SC converter: ideal circuit model, output impedance vs. switching frequency, origin of capacitor charge sharing loss (capacitor charging current at SSL and FSL).

switching frequency to reveal the characteristics of the SC converters. It can be seen that there are two asymptotic operating regions: the fast switching limit (FSL) and the slow switching limit (SSL) [4], [5], [7], [12], [13]. The FSL represents the lowest achievable output impedance of a SC converter. It occurs at high switching frequencies where the capacitor charge transfer is incomplete and the charging current is nearly constant per switching cycle. In this case, the dominating loss is the conduction loss due to the series resistance in the converter (e.g., switch resistance, flying capacitor ESR, PCB trace resistance) and is independent of switching frequency.

On the other hand, the SSL occurs at low switching frequencies, when the output impedance is dominated by the capacitor charge sharing loss, owing to the large instantaneous capacitor current at phase transitions. As can be seen in Fig. 2.5, when two capacitors  $C_1$  and  $C_2$  with different initial voltages are connected in parallel by closing switch  $S_1$ , the initial voltage mismatch between the two capacitors  $\Delta V_0$  can only be present across the small series resistance  $R_{esr}$  in the circuit, assuming the parasitic inductance is negligible. This will result in an exponentially decaying charging current with a high initial value of  $I_0 = \frac{\Delta V_0}{R_{esr}}$ ,

and  $R_{\rm esr}$  will dissipate a power of

$$P_{\text{loss}} = \frac{1}{T} \int_0^T R_{\text{esr}} (I_0 e^{\frac{-t}{\tau}})^2 dt$$

$$= \frac{1}{T} \int_0^T R_{\text{esr}} (\frac{\Delta V_0}{R_{\text{esr}}} e^{\frac{-t}{\tau}})^2 dt$$

$$= \frac{\Delta V_0^2}{TR_{\text{esr}}} \int_0^T e^{\frac{-2t}{\tau}} dt$$

(2.1)

where  $\tau$  is the RC time constant of the equivalent circuit. Assuming  $C_1 = C_2 = C$ , then  $\tau = \frac{R_{esr}C}{2}$ . Provided that the switching period T is sufficiently long compared to  $\tau$  (i.e. in SSL region of operation), (2.1) can be simplified to

$$P_{\rm loss} = \frac{1}{4} C \Delta V_0^2 f_{\rm sw} \tag{2.2}$$

where  $f_{sw} = \frac{1}{T}$  is the switching frequency of switch S<sub>1</sub>. It can be seen that this power loss is independent of the magnitude of  $R_{esr}$ , indicating that reducing the switch on-resistance cannot improve the efficiency when the SC converter is operating in the SSL region.

Since the initial difference in capacitor voltages in one switching cycle is due to the charge transfer  $\Delta Q_0$  in the previous cycle, which is further proportional to the output current  $I_{\text{out}}$ , we can get

$$\Delta V_0 = \frac{\Delta Q_0}{C} = \frac{k_c I_{\text{out}}}{f_{\text{sw}}C}$$

(2.3)

where  $k_c$  is a topology-dependent constant. Now we find that the power loss in (2.2) is proportional to

$$P_{\rm loss} \propto \frac{1}{f_{\rm sw}}, \frac{1}{C}, I_{\rm out}^2.$$

(2.4)

One straightforward way to reduce  $\Delta V_0$  and thereby the  $P_{\text{loss}}$  in SSL is to increase the switching frequency. However, it is often not favorable to do so, since the transistor switching losses, as well as the bottom plate capacitance losses in integrated SC converters, increase proportionally with respect to the switching frequency. Alternatively,  $\Delta V_0$  can be reduced by increasing the flying capacitance C, so that the SC converter can enter FSL at a lower switching frequency. But this method will reduce the energy utilization factor of the capacitor and lead to a larger converter size/volume. In summary, capacitor charge sharing loss undermines the energy density advantage of capacitors, resulting in an unavoidable trade-off between achievable efficiency and capacitor size. More discussion about the capacitor energy utilization factor is presented in Chapter 3.

In-between the FSL and the SSL, the output impedance can be approximated by the geometric mean of SSL impedance and FSL impedance [7], or obtained analytically [14], [15].

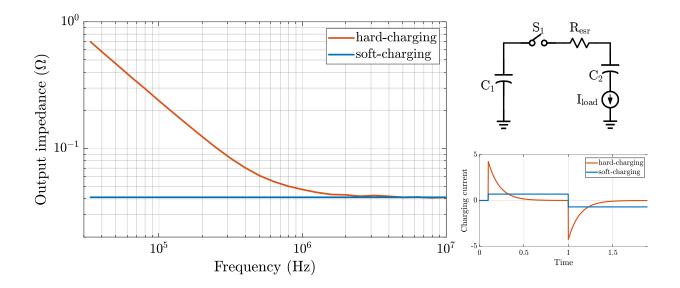

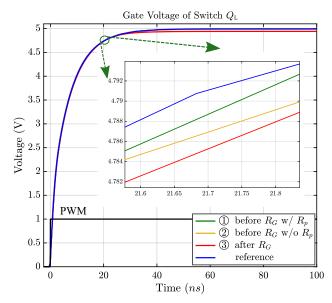

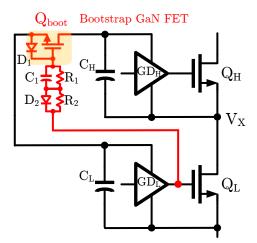

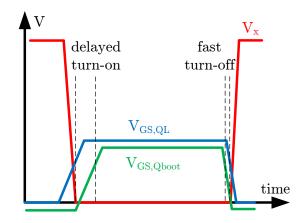

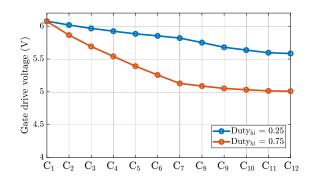

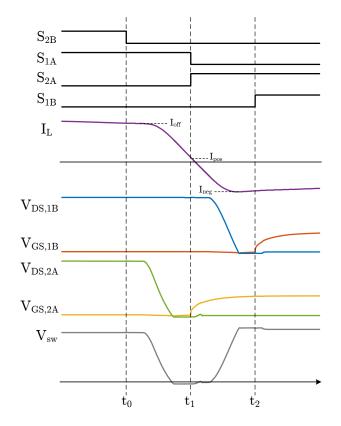

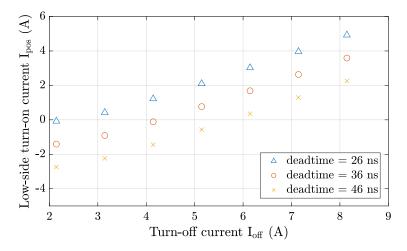

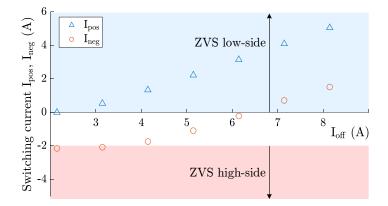

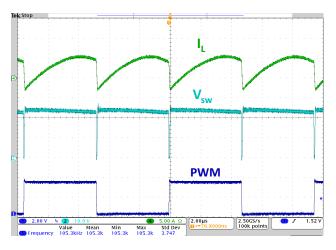

Figure 2.6: Soft-charging operation with ideal current load.