# **Systems for Using Far Memory in Datacenters**

Emmanuel Amaro

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-268 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-268.html

December 23, 2021

Copyright © 2021, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Systems for Using Far Memory in Datacenters

by

#### Emmanuel Amaro Ramirez

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Scott Shenker, Chair Professor Sylvia Ratnasamy Professor Aurojit Panda Professor Ion Stoica

Fall 2021

# Systems for Using Far Memory in Datacenters

Copyright 2021 by Emmanuel Amaro Ramirez

#### Abstract

Systems for Using Far Memory in Datacenters

by

**Emmanuel Amaro Ramirez**

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Scott Shenker, Chair

Datacenter efficiency has become increasingly relevant, as the end of Moore's Law and Dennard scaling have caused CPU and memory performance to begin plateauing. Resource disaggregation is a recent datacenter design point, where server nodes share remote resources through a fast (usually RDMA-based) network, enabling greater execution flexibility and performance in datacenters. Remote or far memory—an instance of resource disaggregation—increases flexibility because nodes can access more memory than locally available. And performance in distributed applications can improve as RDMA provides high-performance access to shared state. This dissertation describes two networked systems that allow server nodes in a data center to leverage far memory.

First, WICkit is a framework and runtime for Where-Independent Code. WICs are a location-independent abstraction representing complex remote memory accesses, *e.g.* accessing a value in a hashmap. Without code changes, the WICkit runtime can execute WICs at the client, server, and SmartNIC CPU locations. As different locations provide different performance and resource trade-offs, WICkit allows users to flexibly choose the location when execution begins while obtaining comparable performance to location-specific systems.

Second, Cluster Far Memory is a system that transparently allows existing jobs to access far memory. CFM includes a fast swapping mechanism and a far memory-aware job scheduler that enable far memory support at rack scale. Using CFM for memory-intensive workloads, a rack can improve its throughput on the order of 10% or more without increasing the total amount of memory in it.

To my family: My Parents, Ariel, Abril and Alonso.

# **Contents**

| Co | Contents                  |                                                                 |                  |  |  |  |  |  |  |  |

|----|---------------------------|-----------------------------------------------------------------|------------------|--|--|--|--|--|--|--|

| 1  | Intr<br>1.1<br>1.2<br>1.3 | duction Where-Independent Code for New Distributed Applications | 1<br>2<br>2<br>2 |  |  |  |  |  |  |  |

| 2  |                           | ground                                                          | 3                |  |  |  |  |  |  |  |

|    | 2.1<br>2.2                | RDMA                                                            | 3 4              |  |  |  |  |  |  |  |

| 3  | WIC                       | kit                                                             | 5                |  |  |  |  |  |  |  |

|    | 3.1                       | Where-Independent Code for Remote Memory Access                 | 5                |  |  |  |  |  |  |  |

|    | 3.2                       | The Desire for Location Independence                            | 7                |  |  |  |  |  |  |  |

|    | 3.3                       | Programming Model                                               | 8                |  |  |  |  |  |  |  |

|    |                           | 3.3.1 Representing WICs                                         | 9                |  |  |  |  |  |  |  |

|    |                           | 3.3.2 WIC API                                                   | 10               |  |  |  |  |  |  |  |

|    | 3.4                       | Runtime Design                                                  | 11               |  |  |  |  |  |  |  |

|    |                           | 3.4.1 Memory-Access Backends                                    | 11               |  |  |  |  |  |  |  |

|    |                           | 3.4.2 WICLocks                                                  | 14               |  |  |  |  |  |  |  |

|    |                           | 3.4.3 Scheduling WICs                                           | 15               |  |  |  |  |  |  |  |

|    | 3.5                       | Implementation                                                  | 16               |  |  |  |  |  |  |  |

|    | 3.6                       | Evaluation                                                      | 16               |  |  |  |  |  |  |  |

|    |                           | 3.6.1 Experiment Setup                                          | 17               |  |  |  |  |  |  |  |

|    |                           | 3.6.2 Benefits of Different Locations                           | 17               |  |  |  |  |  |  |  |

|    |                           | 3.6.3 WICkit vs Location-dependent Systems                      | 20               |  |  |  |  |  |  |  |

|    |                           | 3.6.4 Backends Design                                           | 22               |  |  |  |  |  |  |  |

|    | 3.7                       | Related Work                                                    | 26               |  |  |  |  |  |  |  |

|    | 3.8                       | Conclusion                                                      | 27               |  |  |  |  |  |  |  |

| 4  | Clus                      | er Far Memory                                                   | 28               |  |  |  |  |  |  |  |

|    | <b>4</b> 1                | Context                                                         | 30               |  |  |  |  |  |  |  |

| Bibliogi | raphy                          | 54 |

|----------|--------------------------------|----|

| 4.7      | Conclusion                     | 53 |

| 4.6      | Related work                   | 52 |

|          | 4.5.4 Microbenchmarks          | 49 |

|          | 4.5.3 Rack-scale Evaluation    | 46 |

|          | 4.5.2 Testbed Performance      | 44 |

|          | 4.5.1 Experimental Setup       | 42 |

| 4.5      |                                | 42 |

|          |                                | 42 |

|          |                                | 38 |

|          | 4.4.1 Job Degradation Profiles | 38 |

| 4.4      | Far Memory-Aware Scheduler     | 37 |

|          | 4.3.3 Memory Reclaim           | 36 |

|          | 4.3.2 Page Fault Handler       | 35 |

|          |                                | 34 |

| 4.3      |                                | 34 |

|          |                                | 33 |

|          |                                | 32 |

| 4.2      |                                | 32 |

|          |                                | 31 |

|          | 4.1.1 Memory Provisioning      | 30 |

### Acknowledgments

I feel lucky and proud of having been a member of the NetSys lab at Berkeley. My Ph.D. has been as collaborative as one could imagine, and I feel grateful to have learned from many wise teachers in the process, but I want to recognize four people in particular:

**Scott Shenker.** More than an advisor, he was my mentor. I vividly remember one interaction with him that has influenced me beyond research: I had just joined NetSys as a second-year graduate student, and I felt anxious by my lack of progress. He noticed and asked me to talk to him much more often, even for a few minutes, not necessarily about research, but anything I felt talking about. Spending time with him talking about research and various aspects of life helped me overcome my anxiety and enjoy the Ph.D. process. Thank you, Scott, for the vast amounts of time you dedicated to me, for your patience, your support and candor.

**Aurojit Panda.** He was my unofficial co-advisor. I want to thank him for believing in me, listening to my messy ideas, and helping me shape them. His patience and feedback allowed me to believe in myself. During my first few years, when I still struggled to discuss research during meetings (partially due to the language barrier), somehow, he usually understood what I meant and would translate my ramblings into something coherent. Thank you, Panda, for advising me and being a true friend.

**Sylvia Ratnasamy.** Although she was not my advisor, she made time for me every time I asked her to chat. I want to thank her for listening to me and giving me advice when I needed it the most. She was the person I thought I needed to talk to whenever I felt lost in research. I hope to one day emulate her capacity of asking the fundamental questions that help find clarity in everyone's messy research.

**Amy Ousterhout.** Thank you for all the feedback you gave me whenever I asked; whether I was giving a talk or attempting to write a paper, you were always willing to provide me with strong concise feedback. Thank you for showing me the importance of distilling research ideas into their fundamental pieces.

Aisha Mushtaq, Amin Tootoonchian, Anwar Hithnawi, Christopher Branner-Augmon, Lloyd Brown, Michael Chang, Murphy McCauley, Narek Galstyan, Peter Gao, Sarah McClure, Silvery Fu, Vivian Fang, Wen Zhang, Yotam Harchol, Zhihong Luo. The friends and collaborators I met at NetSys have each taught me something unique I will always keep with me. Thank you all for the conversations, the laughs, the lunches, the culture, the arguments about which food is best, and everything in between.

Last but definitely not least, I would not be finishing my Ph.D. without the support from my family. Thank you, **Abril**, my partner, for living my Ph.D. with me through the ups and downs. Thank you, **Dad** and **Mom** and **Ariel**, my brother, for all your understanding and always having my back.

# **Chapter 1**

# Introduction

Although Dennard scaling ended by 2010 and Moore's law continues to slow down, there is an ever-increasing demand for more storage and computing power in large scale clusters. Predictions say the amount of data created from 2020 to 2023 will be more than the data created over the previous 30 years. Similarly, new workloads that did not exist a decade ago, such as ML training, have impressively grown in popularity and the compute resources they require. For example, a cloud company has claimed their training requirements for their largest models grew an order of magnitude each year from 2012 to 2018 [65].

Datacenters and their users have reacted to these technological trends by breaking monolithic applications into distributed ones across server nodes. In turn, this has exacerbated the challenge of data center resource efficiency. In 2019, Google reported an average resource utilization of less than 70% for CPU and memory in their datacenters [117]. Given current technological trends, maximizing the utilization of available resources would seem ideal, so why is improving utilization challenging? The reason is twofold: first, because compute jobs are bin-packed onto the rack's physically available resources; thus, if any of the resources are lacking, the server node cannot admit the job. Second, because job schedulers usually allocate resources for a job's maximum predicted usage; hence, whenever a job uses fewer resources than its maximum, utilization decreases.

Resource disaggregation is a recent datacenter design point where server nodes share access to remote resources through a fast (usually RDMA-based) network [52, 57, 111]. Remote or far memory—an instance of resource disaggregation—enables greater execution flexibility and performance in datacenters. Flexibility increases because far memory allows server nodes to use more memory than locally available when required. At the same time, distributed applications' performance can improve as RDMA provides high-performance access to shared state.

In this dissertation, we address the question of, how do we build systems that use far memory in datacenters? We answer this question from two different perspectives; first, by looking at how new distributed applications can best use remote memory to share state; and second, by exploring mechanisms that allow existing unmodified applications to execute efficiently in them. We expand on these two perspectives next.

# 1.1 Where-Independent Code for New Distributed Applications

Many datacenter applications distribute both state and processing logic across multiple servers. Consequently, a client executing processing logic for a distributed application often needs to access and alter the state on a remote server. In many cases, accessing this state requires executing complex memory-access logic, *e.g.*, accessing a value in a hashmap. RDMA networks allow memory-access logic to be executed either at the client or the server. The emergence of SmartNICs means that memory-access logic can also be executed on the server's SmartNIC. However, it is not easy to determine which of these locations to use because they provide different performance and cost trade-offs. Worse, these trade-offs can vary over time, and as a result, no single location is always best for an application.

In Chapter 3, we argue that users should be able to change memory-access logic execution locations without changing the code. To this end, Chapter 3 proposes a new Where-Independent Code (WIC) abstraction that allows users to decide where an application's memory-access logic executes flexibly. We implement the WIC abstraction in a system called WICkit and demonstrate that WICkit applications have performance comparable to applications whose memory-access logic executes in fixed locations.

# 1.2 Rack-scale Far Memory for Existing Applications

Chapter 4 presents Cluster Far Memory (CFM), a faster swapping mechanism, and a far-memory aware cluster scheduler that enables using far memory at rack scale. The chapter examines the conditions under which using far memory with CFM can increase job throughput. We find that, while far memory is not a panacea, for memory-intensive workloads it can provide performance improvements on the order of 10% or more even without changing the total amount of memory available.

# 1.3 Previously Published Work

In this dissertation, the material in Chapter 3 is based on [5] but the content presented here significantly extends the programming model and the runtime design. The material in Chapter 4 is an adaptation from [4].

# Chapter 2

# **Background**

In this chapter we provide a brief overview of RDMA and SmartNICs.

#### **2.1 RDMA**

Remote-direct memory access (RDMA) is a set of network technologies where most of the network stack is implemented in the network interface card (NIC) or within the network. As a result, in RDMA networks, no CPU cycles are spent on providing reliable message delivery, implementing congestion control, or packetizing data, thus reducing network I/O overheads. Over the last decade, RDMA networks have seen wide adoption and use in datacenters [96, 100, 131]. A variety of applications, including key-value stores [40, 80, 83, 98], machine learning [129], and graph processing [112], have been shown to benefit from the use of RDMA.

To benefit from RDMA, applications need to use an specific network API, *e.g.* the IB Verbs API [95]. The logic for many of the functions exposed by these RDMA-specific network APIs, *e.g.* functions that send or receive data, are implemented entirely in the NIC hardware. This allows greater flexibility when designing networked applications. RDMA applications can be structured either as traditional client-server applications or as *one-sided applications*, where application logic is implemented entirely at the client.

Concretely, RDMA provides two types of operations: 1-sided and 2-sided operations. Client-server RDMA applications are implemented using **2-sided operations** and they require processes to be run on both at the client and the server. The client and server processes communicate with each other by sending and receiving messages using 2-sided operations. On the other hand, application logic in one-sided RDMA applications is implemented entirely at the client. The client process uses **1-sided RDMA operations** to read or modify data stored in the server's memory. These operations are executed by the server's RDMA NIC, and as a result, the NIC hardware dictates what operations can be performed on remote memory. Consequently, as prior work [67, 71] has observed, implementing complex application logic in a one-sided application might require several network round-trips.

When deciding whether to structure an application as a client-server application or a one-sided

application, a developer needs to navigate a resource and performance trade-off: client-server applications require more CPU cores but fewer network round-trips while one-sided applications require fewer CPU cores but more network round-trips. Furthermore, how an application should be structured depends not on the functionality that it provides but on the algorithms and data structures used, workloads considered, and where it is deployed. For example, several prior projects have described transaction key-value stores built using RDMA. Some of these projects are structured as one-sided applications (*e.g.* early versions of FaRM [40] and Pilaf [98]), some are structured as client-server applications (*e.g.* eRPC [67] and FaSST [71]), while yet others are hybrid applications combining both options (*e.g.* Dr. TM+H [125] and newer versions of FaRM [41]). In each case these systems are designed to provide high performance, and the core difference lies in whether they use existing off-the shelf datastructures and algorithms [91] or develop specialized RDMA specific algorithms.

### 2.2 SmartNICs

SmartNICs are NICs that contain programmable processing elements, usually FPGAs or embedded CPU cores. These processing elements are commonly used to implement virtual switches [47] or other systems responsible for enforcing network policies. SmartNICs have been adopted by most cloud providers [6,47,127] because they reduce the isolation overheads in multi-tenant datacenters. Chapter 3, assumes the use of CPU-based SmartNICs.

# Chapter 3

# **WICkit**

In this chapter we present WICkit, a framework and runtime for Where-Independent Code. WICs are a location-independent abstraction to represent complex remote memory accesses; *e.g.* accessing a value in a hashmap. WICs are flexible, as they can be executed at client (similarly to 1-sided RDMA operations), at the server (similarly to 2-sided RDMA operations), and at new locations such as SmartNICs. Our design makes the cost of the WIC abstraction low, as client and server locations provide performance comparable to previous location-specific systems.

# 3.1 Where-Independent Code for Remote Memory Access

Most datacenter applications, including transactional data stores, in-memory storage, and machine learning systems, are distributed applications whose state and processing logic spans multiple servers [40, 82, 126]. Many operations in these applications require accessing state on remote servers, *e.g.* a transactional datastore [40, 123] might need to acquire locks and read and update tuples on multiple servers. In many cases these remote memory accesses are not just simple loads and stores, and as a result these accesses can require executing complex application-dependent *memory-access logic*.

Today this memory-access logic can run in many different locations. Traditional RPC based applications send messages and execute memory-access logic on a remote CPU core [67]. On the other hand, applications built using 1-sided RDMA, can execute memory-access logic at a local CPU using memory-access primitives provided by the RDMA NIC.

Which location is best depends on the application and workload. Previous research has shown that for some applications [40, 71, 123], running memory-access logic on client CPUs and using 1-sided operations can improve resource efficiency and performance. The resource efficiency gains are from not using CPU cores on the server, while the performance gains are because there is no notification delay (*e.g.* via interrupts) or processing cycles spent at the server. On the other hand, other work [40, 71] has shown that using 1-sided RDMA to implement memory-access logic that performs multiple dependent memory accesses yields suboptimal latency because each memory access requires a network round-trip. As a result, the choice of where memory-access logic should

be executed depends on the complexity of the memory-access logic: client-based implementations perform best when the memory-access logic accesses a single memory location, and server based implementations are better otherwise. Where memory-access logic is implemented has an impact not just on performance but also on deployment costs. However, when implementing complex memory-access logic a 1-sided application can require more network bandwidth. Thus, the relative cost of client-based memory access-logic and server-based memory-access logic varies depending on the relative cost of CPU cores and network bandwidth. Thus, the location that provides the best performance and lowest cost varies depending on workload, application logic, and deployment environment. Indeed, prior work [125], has shown the benefit of carefully choosing between these options for different operations.

Modern datacenters also include SmartNICs and other locations where memory-access logic can be executed. These new locations offer different performance and cost trade-offs. While SmartNIC cores generally have lower clock frequencies than host cores, a SmartNIC located on the server can access server memory without needing to traverse the network. Therefore, in many cases memory-access logic executed on the SmartNIC can outperform the same logic when executed by the client. Similarly, most cloud providers [47] do not sell SmartNIC cores, while they do offer host CPU cores to tenants. As a result, providers such as Azure have previously stated that running compute on SmartNIC cores is cheaper than running compute on host cores, and consequently executing memory-access logic on SmartNIC cores is currently cheaper than executing on server CPU cores.

We can thus observe that the best location for memory-access logic varies depending on the application, workload, and deployment environment (which dictates resource costs). Furthermore, all of these factors change over time: application logic and workload vary as a result of changes in user demands, while resource costs vary depending on what other applications are executing in the datacenter. As a result, in this chapter, we argue that it is better to determine where memory-access logic is executed at *application start-up time* rather than when designing an application. Additionally, users should be able to choose the location from a wide array of options, including client CPUs, server CPUs, and even SmartNIC CPUs.

Unfortunately, current RDMA network APIs [95] and frameworks [67,71] require applications to choose where memory-access logic is executed at development time rather than at start-up time. Building a framework that allows this presents two challenges: First, how do we represent memory-access logic in a location-independent manner? Second, how do we provide reasonable throughput and latency comparable to existing location-specific approaches?

We address the first challenge, by proposing *Where-Independent Code* (WIC), a location-independent abstraction that encapsulates remote memory accesses and their surrounding logic. WICs access memory using a unified API, and a *WIC runtime* adapts the underlying memory-access mechanism, leveraging 1-sided RDMA or local memory accesses, depending on where the WIC executes. Thus, our runtime allows WICs to be written once and then executed in any of the supported locations: client, server, or SmartNIC CPUs.

We address the second challenge, *i.*e., providing latency and throughput comparable to location-specific approaches by designing a new runtime. This runtime builds on the observation that WIC execution time is dominated by the cost of memory access and that these access costs vary de-

pending on where the WIC is run. For example, accessing memory from the server CPU takes about 100ns, while accessing the same memory location from the client can take between 1.5-10µs. Memory access latencies affect how WICs access memory: to maximize throughput WICs running on the server should access memory synchronously, while those running at the client should access memory asynchronously. Therefore, the runtime needs to support both synchronous and asynchronous memory accesses, and must be able to switch between WICs performing asynchronous memory accesses. As a result, the WIC runtime needs to support both asynchronous and synchronous memory accesses and rapidly switch between different WICs when performing asynchronous memory accesses.

In this chapter, we describe WICkit, a framework and runtime that provides applications with the WIC abstraction. WICkit supports both synchronous and asynchronous memory accesses and implements WICs using C++ stackless coroutines to minimize switching costs. We demonstrate the efficacy and generality of WICkit by implementing and evaluating two distributed applications: a key-value store and a remote-shared log. Additionally, we also evaluate WICkit's performance using microbenchmarks. We show, using a linked list traversal microbenchmark (§3.6) that when memory-access logic is executed on the server, WICkit can achieve comparable throughput and latency to an application written using eRPC. Similarly, we show for the same benchmark that when memory-access logic is run on the client, WICkit achieves throughput and latency comparable to that achieved by an application that directly uses 1-sided RDMA operations.

We thus demonstrate that WICkit provides an efficient mechanism for deciding the location of an application's memory-access logic when it is first executed. In §3.6, we demonstrate WICkit's utility by showing that there are performance and cost benefits to executing memory-access logic at all three locations. We currently do not address the question of how to decide where memory-access logic should be located, nor the question of how to move WICs between locations at runtime. We plan to address these questions in future work.

# 3.2 The Desire for Location Independence

WICkit is designed so that programs can be written once and configured to operate in three distinct modes: (a) a client-only configuration in which WICs execute on client cores; (b) a SmartNIC configuration in which WICs execute on cores on the server's SmartNIC; and (c) a server configuration in which WICs execute on server cores (WICs are invoked from client cores in all configurations). As we noted above, existing work on RDMA has largely focused on comparing the client-only configuration (one-sided RDMA applications) and server configuration (client-server applications) and in showing that one or the other is more desirable for different applications. Given this, one might wonder: why is the ability to choose between the three at deployment time desirable?

As prior work has shown [67,71,125], the relative performance and resource requirements for these configurations vary depending on application logic, workload, and deployment environment. However, beyond these factors, deployment costs can also vary significantly for these different configurations. This is because clients and servers generally face different scaling requirements and can be deployed on different instance types with different costs. Additionally, many cloud

Function

Awaitable Backend::read\_host(uintptr\_t raddr, uint32\_t sz)

Awaitable Backend::write\_host(uintptr\_t raddr, void \*data, uint32\_t sz)

Write sz bytes from host's address raddr.

Write sz bytes from data to host's address raddr.

Uintptr\_t Backend::get\_rbaseaddr()

Gets remote base address.

Void Backend::reply(void \*data, uint32\_t sz)

Write sz bytes from data to host's address raddr.

Send data of size sz as reply to the client.

WICCoro WICLock::lock(Backend &b)

WICCoro WICLock::unlock(Backend &b)

Unlock WICLock using Backend b.

Table 3.1: WICkit's location-agnostic API.

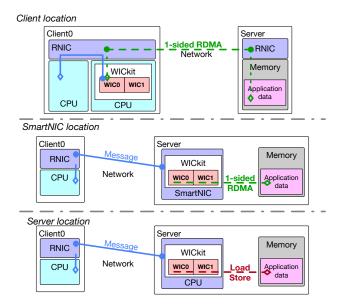

Figure 3.1: The three supported locations for WICkit and how each location accesses application data in server memory.

providers, including Microsoft [47], argue that processing resources on a SmartNIC cost less than on host CPUs because host CPUs can be more easily sold to tenants. Furthermore, instance costs vary over time, and we expect that SmartNIC core costs are also likely to vary over time. When deploying an application, developers and administrators need to consider not just performance but also costs, and it is thus easy to see that the best configuration can vary over time and across deployment environments. A framework such as WICkit provides developers and administrators with greater flexibility when responding to changing workload, application logic, or costs and thus enables more efficient application deployments.

# 3.3 Programming Model

The core abstraction provided by WICkit is Where-Independent Code (WIC). A WIC encapsulates the logic surrounding and including related memory accesses. For example, when implement-

ing a key-value store application, a user might decompose their application logic into WICs for GET(K), UPDATE(K,V), SCAN(K), etc. With a tree-based index [123], the GET(K) WIC would traverse the index, specifying how to select each subsequent node to read in the tree, and issuing memory accesses to read each node. While WICs can execute at client CPUs, server CPUs, or SmartNIC CPUs, we assume that the main *application data* always resides at the server, as shown in Figure 3.1. Thus, when WICs issue memory accesses, these are primarily to server memory.

The WIC programming model specifies how a user expresses a WIC and the APIs between WICs and the WICkit runtime (§3.4). The runtime's job is to invoke and manage WICs and provide two APIs: the API the runtime uses to invoke WICs and the API functions that WICs can call (*e.g.* to access application data). The programming model should provide four key properties:

- 1. The code in a WIC should remain the same, regardless of where the WIC is executed.

- 2. The WIC abstraction should be amenable to good performance (low latency and high throughput).

- 3. WICs should be convenient to program.

- 4. WICs should provide the same functionality (e.g., locks) as existing frameworks.

WICkit provides these properties using two techniques. First, WICkit expresses WICs using a thread-like abstraction. This enables WICs to support both synchronous and asynchronous memory accesses (for high performance regardless of where a WIC executes) in a programmer-friendly way (§3.3.1). Second, WICkit provides a single unified API for WICs to use to access application data and features such as locks, regardless of where the WIC executes. The runtime then uses a different underlying mechanism depending on where the WIC is currently executing (§3.3.2).

# 3.3.1 Representing WICs

There are several possible ways to represent WICs. For example, each WIC could be represented as a single run-to-completion function [21, 37, 104] or as a thread that can suspend and resume. However, not all approaches enable high performance for WICs, regardless of where they execute.

The key challenge is that the latency to access application data differs significantly depending on where a WIC executes. For example, when WICs execute at the server, each local access to application data can complete in about 100ns. In contrast, when WICs execute at a client or SmartNIC CPU, they access application data over RDMA, which can take 1.5-10µs. While a run-to-completion approach can perform well at the server, it would yield poor throughput at the client and SmartNIC locations, because every access to application data would stall a CPU core for a few microseconds while waiting for the data to arrive. At those locations, WICs with outstanding memory accesses must yield the CPU to other WICs. Thus the WIC programming model must support both run-to-completion and suspend-and-resume models.

There are two main ways to implement a suspend-and-resume programming model: callbacks and threads. To implement WICs with callbacks, a WIC would need to specify which callback

function to call after each memory access is completed; this is similar to eRPC's completion handler functions, which execute when a recursive RPC request completes [67]. In WICkit, this would mean that a loop that iterates over n nodes, reading each from memory, would need to be split into n+1 chained callbacks. Furthermore, the programmer would need to explicitly specify what execution state to pass from callback i to callback i+1. As this is not a convenient programming model for users, WICkit instead represents each WIC using a thread-like abstraction. Threads work well because they support both run-to-completion and suspend-and-resume models for accessing application data.

As we describe in more detail in §3.4.3, WICkit implements WICs using C++20 stackless coroutines [106]. Coroutines behave similarly to threads, except they are able to suspend and be resumed later, transparently allowing the state before suspension to be available after the resumption. In addition, coroutines yield control at least an order of magnitude faster than existing thread implementations, enabling better performance.

#### **3.3.2** WIC API

WICkit provides a single unified API for tasks such as accessing application data and acquiring locks, so that users can write each WIC once and execute it at any location without modification. WICkit's API is summarized in Table 3.1.

A distributed application that uses WICkit is comprised of mainly three components: a server component, the runtime, and the application that sends WIC request executions to the runtime. The server component holds and initializes the application data that will be accessible to the runtime. When the runtime begins execution, it connects to the server, and they exchange information about the available memory regions.

**WICCoro.** WICCoro is the type our runtime uses to define WICs [93]. Internally, it defines the suspension and resumption behavior of our coroutines, and it keeps the internal coroutine handle and any other per-WIC internal state [66, 106].

Invoking WICs and replies. Clients in a distributed application request WIC executions by sending an execution message with a specific WIC id to the current runtime's location. Besides the id, requests include parameters that must be passed to the requested WIC. When a WIC completes, it can send a reply back to the client that requested the execution by using reply(void \*data, uint32\_t sz).

Memory Accesses. The WIC API provides two basic low-level functions for accessing application data: read\_host() and write\_host(). Rather than providing functions for fixed-size accesses, our functions accept variable buffer sizes. As shown in Table 3.1, both functions return an Awaitable object type, which means the type supports the co\_await() operator [17]. In other words, Awaitable types define points at which a WIC could be suspended. For example, this allows us to suspend WICs when they access memory through RDMA and not suspend if the access is made synchronously to local memory. The memory-access functions take server virtual addresses, and the base remote address can be obtained by a WIC with get\_rbaseaddr(). Both functions access application data on the server, but the WICkit runtime implements them differently depending on

CHAPTER 3. WICKIT

```

WICCoro traverse_linkedlist(Backend &b, void* param0) {

1

2

int num_nodes = *(reinterpret_cast<int*>(param0));

uintptr_t addr = b.get_rbaseaddr();

3

4

LLNode *node = nullptr;

5

for (int i = 0; i < num_nodes; ++i) {</pre>

6

7

node = co_await reinterpret_cast<LLNode *>

(b.read_host(addr, sizeof(LLNode)));

8

addr = node->next;

9

10

11

b.reply(&node->value, sizeof(node->value));

12

13

}

```

Listing 1: A WIC that performs traverses a remote linked list.

where the WIC is executed. As described in Section 3.4.1, WICkit supports three different backends for accessing memory. Backends are selected at compile time and passed to every WIC as an argument. When WICs call read\_host or write\_host, they call these functions on the specified backend.

**Locks.** WICkit provides simple exclusive locks to WICs through a WICLock class. The class provides two methods that can be used regardless of the runtime's location: lock(Backend &) and unlock(Backend &). We describe the design of locks and why they return WICCoro in Section 3.4.2.

Listing 1 shows a WIC that performs a remote linked list traversal. The number of nodes to traverse is specified as an execution argument by the client (*i.e.*, param0 in Line 1). The WIC gets the base remote virtual address by calling get\_rbaseaddr() and then proceeds to traverse the linked-list by issuing read\_host() calls. When the WIC has traversed the number of requested nodes, it issues a reply back to the client that requested the execution.

# 3.4 Runtime Design

# 3.4.1 Memory-Access Backends

WICkit's memory-access APIs (§3.3.2) are implemented by location-specific backends. Our implementation provides three backends: a 1-sided RDMA backend that is used in the client and SmartNIC configurations, a synchronous local-memory backend used by the server configuration when running WICs to completion, and an asynchronous local-memory backend which is also used by the server configuration. The asynchronous local-memory backend prefetches cache lines before accesses and provides better performance for some applications. We describe each of these backends below.

#### 1-sided RDMA

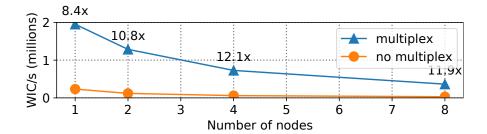

The main challenge of the 1-sided RDMA backend is providing high memory-access throughput for client and SmartNIC locations. Our design addresses this challenge using two techniques: first, our design uses multiple cores allowing multiple simultaneous RDMA memory accesses, and second, our design batches RDMA operations, thus reducing the cost of communicating with the RDMA adapter. Multiplexing improves throughput by  $8.4-12.1 \times$  relative to not multiplexing, and batching can improve throughput by  $2.1 \times$  and decrease latency at high loads (§3.6.4).

**Multiplexing memory accesses.** The RDMA backend uses multiple cores and queues simultaneously, and can thus issue multiple memory accesses at a time. As we explain below our design avoids cross-core synchronization but does not balance load across cores. We will investigate approaches [102, 104] to balance load in the future.

RDMA's *queue pairs* are used by CPUs to submit work requests to the RDMA adapter. In Bluefield-2, each queue pair has a limit of 16 outstanding RDMA reads. Conversely, *completion queues* are used by the RDMA adapter to signal cores that work requests have completed. Using 1 queue pair per core would only allow WICkit to maintain 16 outstanding reads per core at most.

The RDMA backend uses multiple queue pairs per CPU to increase memory-access multiplexing and improve throughput (§3.6.4). However, we configure the queue pairs to aggregate all completions into a single completion queue. This enables each core to have more outstanding operations and improves efficiency when polling for completion, since each core can poll from 1 CQ. By default we use 4 QPs per core at the SmartNIC and 16 QPs per core at the client; we evaluate the tradeoffs of different numbers of QPs in §3.6.4.

**Reducing CPU cost of RDMA.** We batch RDMA operations to reduce CPU cycles spent issuing new RDMA requests. Previous research has shown that reducing communication frequency to the RDMA adapter can result in better CPU efficiency and RDMA throughput [69]. This is of particular concern when using SmartNIC cores which can be significantly slower than x86 cores. For example, when comparing the performance of a 2.6GHz Haswell core<sup>2</sup> to the performance of the 2GHz ArmV7 A7 core on a Bluefield-2 [115] NIC using STREAM [94] and Coremark [51] we found that the ARM core achieves at most 64% of an x86 cores performance (Table 3.3).

Batching requests allows a core to issue multiple work requests with a single MMIO write, reducing the number of cylces spent issuing RDMA requests. Our runtime creates batches of memory accesses for WICs by using the new verbs work request API ibv\_wr\_start() and ibv\_wr\_end(). These two functions establish a code region in which a core can more efficiently post work requests, compared to the previous ibv\_post\_send() API [116]. Once a code region is open, RDMA operations can be posted inside, for example, by using ibv\_wr\_rdma\_read(). These operations are buffered and only delivered to the RDMA adapter when ibv\_wr\_end() is called. Each batch is submitted to a single queue pair.

Listing 2 shows how WICkit implements batching. We first select the queue pair we create the batch for and call ibv\_wr\_start() on it (Line 3). Next we pop a WIC from the runqueue (Line

<sup>&</sup>lt;sup>1</sup>To the best of our knowledge other RDMAs impose the same limit.

<sup>&</sup>lt;sup>2</sup>Intel Xeon CPU E5-2640 v3.

CHAPTER 3. WICKIT

```

1

void execute_interleaved() {

2

for q in qps {

3

ibv_wr_start(q.qp);

while (len(runqueue)>0 && q.outstanding<MaxInFlight) {</pre>

4

5

wic = runqueue.pop();

wic.resume();

6

7

if (wic.issued_mem_access)

q.pending.push(wic);

8

9

10

}

11

ibv_wr_end(q.qp);

12.

13

}

```

Listing 2: Pseudocode showing how application data accesses are batched in RDMA backend using multiple queue pairs.

| Stateful execution context | BF2 latency | x86 latency |

|----------------------------|-------------|-------------|

| pthread                    | 1583.2ns    | 342.4ns     |

| user thread [102]          | -           | 52.0ns      |

| boost coroutine            | 48.7ns      | 17.4ns      |

| boost coroutine2           | 40.2ns      | 7.2ns       |

| stackless coroutine        | 3.0ns       | 1.9ns       |

| function call              | 1.5ns       | 0.9ns       |

Table 3.2: Yield latencies of different stateful execution contexts.

4) and resume it. The resumed WIC eventually issues a new application data access on queue pair q, which causes the WIC to yield back to Line 7. We keep selecting WICs from the runqueue and resuming them, until the runqueue is empty, or the current queue pair has MaxInFlight=16 outstanding requests (Line 4). Lastly, we end the current batch by calling ibv\_wr\_end(), which posts the work requests to the RDMA adapter (Line 11). Therefore, our batching is dynamic as it does not wait for a fixed batch size to be reached before posting the batch.

We further reduce the number of CPU cycles needed by using *unsignaled RDMA work requests*. RDMA-based systems typically use signaled requests, where each request generates a completion when it finishes. Unsignaled RDMA requests do not generate completions, and leveraging them for some requests can reduce the number of PCIe transactions [69] performed by the RDMA adapter and the number of completions the CPU polls for. Thus our backend only uses a signaled work request for the last access in each batch.

The challenge to only signaling the last request in a batch is identifying what unsignaled WICs have completed. Signaled work requests in RDMA include an 8-byte identifier that is included with the completion event, and this can be used to identify the corresponding coroutine to resume. However, the RDMA adapter provides no information about which unsignaled requests have com-

| Microbenchmark      | Armv8 A72 | Xeon E5-2640 v3 | Armv8/x86 |

|---------------------|-----------|-----------------|-----------|

| STREAM copy (MB/s)  | 7119.3    | 13494.1         | 53%       |

| STREAM scale (MB/s) | 7116.5    | 8735.5          | 81%       |

| STREAM add (MB/s)   | 6392.3    | 9986.6          | 64%       |

| STREAM triad (MB/s) | 6400.8    | 10180.3         | 63%       |

| Coremark            | 11426.6   | 18995.4         | 60%       |

Table 3.3: Two microbenchmarks showing the performance ratio achieved by 1 ARM CPU in Bluefield-2 relative to a Haswell x86 core. The ARM CPU offers only 64% performance of the x86 core.

pleted or when.

Fortunately, our runtime can leverage the fact that queue pairs complete work requests in order to identify which unsignaled request have completed. To do this, the runtime maintains a per-queue pair software pending queue to track WICs that have issued a memory access and suspended (Line 8 in Listing 2). When we submit a batch of memory accesses, we use the last memory access' identifier to encode the id of the corresponding pending queue and the batch size. When we receive a completion, WICkit can pop batch\_size WICs from the corresponding pending queue and add these WICs to the current core's runqueue.

#### Local memory

The WICkit's server location uses one of two local memory backends to access application data directly with CPU instructions. The first backend accesses local memory synchronously, and a second one behaves asynchronously and uses prefetching instructions before load-stores.

As we discuss in more detail in §3.4.3, WICkit uses coroutines to implement logical threads. Such coroutines need to be initialized before they are invoked; thus, the runtime pays for additional CPU-memory traffic and CPU cycles for every invoked WIC. Our asynchronous memory backend attempts to compensate for the additional latency and CPU-memory traffic by multiplexing local memory access using prefetchnta instructions [64], similar to our RDMA backend. As we show in §3.6.3, the asynchronous backend can significantly improve throughput relative to run-to-completion in microbenchmarks where every access generates a CPU last level cache miss.

#### 3.4.2 WICLocks

The runtime provides exclusive locks to WICs through a WICLock class with two methods: lock(Backend &) and unlock(Backend &). WICLocks are designed so they can work at all three locations. Doing so requires ensuring that the runtime does not block when a WIC cannot acquire a lock. To achieve this, the lock function yields to the runtime when a lock cannot be acquired.

Additionally, we need to ensure that the lock itself is accessible to all executing WICs. One approach to doing so would be to always place the lock on the server, and we adopt this approach when using the server or client backend. In this case the client backend acquires and releases locks

using 1-sided RDMA atomic verbs, while the server backend uses atomic instructions. When using the SmartNIC backend we optimize the lock further by placing its state in SmartNIC memory. This allows us to use atomic instructions to acquire and release locks when using the SmartNIC backend. We plan to investigate approaches to further optimizing these locks and implement other synchronization primitives in the future.

#### 3.4.3 Scheduling WICs

Thus far, we have described the design of our backends and the design of our where-independent WICLocks. We now focus on a crucial aspect of our design: our coroutine-based logical threads. Context switch latency of logical threads is a major concern for WICkit's performance, and our runtime uses C++ stackless coroutines to minimize these costs; we refer to these simply as coroutines. As Table 3.2 shows, switching coroutines in SmartNICs is three orders of magnitude faster than switching pthreads, and in x86, it is  $27 \times$  faster than switching user threads.

Writing a WIC is similar to writing a function: statements are executed sequentially, and local variables can be defined at any point inside the WIC body. However, coroutines extend functions by adding support for preemption, or *suspension points*, defined inside the coroutine body by using the co\_await operator; see Listing 1. After suspending, coroutines can either return control to the caller or can transfer control to another coroutine;name makes use of both kinds of control transfer. For example, the runtime returns control to the scheduler (*i.e.*, the caller) after issuing an asynchronous memory access and transfers control to another coroutine when taking a lock. The runtime can also choose to not transfer control at a suspension point, and WICs do not yield control when performing synchronous memory accesses. In both cases, after a coroutine is resumed by the scheduler, execution resumes at the statement following the previous suspension point. Coroutines provide very fast switch latencies as the compiler generates the switching code and stores the coroutine's local variables and execution context on the heap rather than on the stack. Our implementation uses a custom allocator to reuse previously allocated WICs, but a recycled buffer must still be initialized every time a new WIC is instantiated.

Although all backends invoke WICs in FCFS order, they must also decide when to resume a suspended WIC. For example, a WIC that issued a 1-sided RDMA asynchronous operation should not be resumed until after its memory access completes. Thus, to improve WIC throughput, each memory access backend includes a scheduling policy to better target the memory performance characteristics available at each location. We describe them next.

RDMA scheduler. The scheduler of the 1-sided RDMA backend executes WICs as follows. First, a client sends a WIC execution request which is received on a SmartNIC core's request queue. The runtime polls the request queue and uses the received request's WIC id to instantiate a specific WIC. Newly created WICs are immediately suspended when they are created and added to the back of the runqueue. Next, the scheduler resumes WICs from the runqueue's front, and every resumed WIC runs until it finishes or suspends. The runtime continues removing and resuming WICs from the runqueue as long as the runqueue is not empty and the current queue pair has less than 16 outstanding memory accesses. Eventually, WICkit checks for completed memory accesses

by polling the completions queue, and all WICs that have a completed memory access are added back to the front of the runqueue (in order to ensure FCFS processing).

**Local memory schedulers.** The synchronous local memory backend runs individual WICs to completion; therefore, memory accesses do not suspend a WIC, and when an WIC finishes, another one is selected from the runqueue in FCFS order.

In our asynchronous local memory backend, the scheduler first selects a *window* of WICs from the runqueue in FCFS order. Instead of running a single WIC to completion, the scheduler executes the window-to-completion (similar to [64]). When WICs access application data, the backend issues prefetchnta instructions to bring the cache line close to the CPU and suspends. Once prefetch instructions have been issued for every WIC in the window, the scheduler resumes WICs in the order in which prefetches were issued. This time, the backend issues load-store instructions, completing the memory access for each. The same process repeats until all WICs within a window finish. We evaluate the effect different window sizes have in §3.6.4.

# 3.5 Implementation

We implemented our WICkit prototype in 4770 lines of C++20. We use GCC 10.2, and we cross compile to generate ARM binaries for Bluefield-2. After a developer writes a WIC, they use the WICkit build system to produce 5 binaries: a server binary that holds the application data for the RDMA backends, and 4 runtime binaries. One of the runtime binaries targets the client location thus comes with the RDMA backend; the SmartNIC binary is equivalent, except cross compiled for ARM. The last two binaries target the server location, one using the synchronous local memory backend, and the last one the asynchronous one.

**Limitations.** We now discuss the limitations of our prototype. These limitations are not fundamental, and we plan to address them in the future. First, our prototype assumes no failures. Second, our implementation requires one request and reply queue per connection. This is because we use 2-sided RDMA RC queues rather than raw ethernet queues as is done by eRPC [67]. Third, our prototype runtime currently assumes the client and SmartNIC have sufficient memory to hold all application data and the RDMA backend maps server memory one-to-one. A better implementation would not make this assumption, and instead allow WICs to manage their location-local memory.

# 3.6 Evaluation

Our evaluation of WICkit focuses on three main questions:

- 1. Are there scenarios where users would prefer each of the locations supported by WICkit? (§3.6.2)

- 2. How does the performance of WICs compare to systems that are customized to run at a specific location? (§3.6.3)

3. What impact do the design decisions described in §3.4.1 have on WIC performance? (§3.6.4)

### 3.6.1 Experiment Setup

We use two load generators in our experiments: a closed-loop load generator to understand maximum WIC throughput, and an open-loop load generator with exponentially distributed inter-arrival times to analyze latency under load. Our testbed system consists of two two-socket servers with Intel Xeon E5-2640 v3 CPUs. We disable hyperthreading and turbo boost and fix the CPU frequency at 2.6Ghz. Our servers are connected through 100GbE Bluefield-2 MBF2M516A Smart-NICs which include a ConnectX-6 Dx RDMA adapter and 8 Armv8 A72 cores running at 2Ghz. We refer to the NIC simply as BF2. The BF2s are connected through an Arista 7160S-32CQ 100GbE switch. Both hosts and SmartNICs use Linux kernel 5.4 and we use isolcpus to isolate CPUs from kernel SMP balancing and scheduling disturbance. We also customize the SmartNIC's kernel to enable nohz\_full [75] which prevents interrupt timers in cores the runtime uses, as we found these induced significant jitter. We use three workloads to evaluate WICkit:

**Linked-list traversal.** Our first workload creates a randomized linked-list in application data and uses a traverse(num\_nodes) WIC to walk the linked-list starting from a random node. num\_nodes is a request parameter, and each linked-list node is 16-bytes. Traversing a linked-list is equivalent to issuing multiple-dependent memory accesses.

Remote shared log. The second workload is a remote shared log with two WICs: readtail() and append(value); we use a request composition of 50% readtail and 50% append. Shared logs are a core component in distributed protocols such as consensus and leader election [18]. Our shared log's application data is a buffer that holds 8-byte values, and its WICs maintain a head and tail pointer. As the names suggest, readtail reads the value currently pointed by tail, and append increments the tail pointer and sets a new value. We use a single exclusive WICLock to protect the pointers and the buffer's consistency under concurrent requests.

**Key value store.** For our last workload we evaluate a key value store based on a cuckoo hash table that we ported to WICkit [25]. We implement two WICs: query(key) and update(key, value), and use a request composition of 50% queries and 50% updates. We use an exclusive WICLock to protect the table during updates and queries.

Unless specified otherwise, to serve the load, all experiments use one server x86 core when WICkit is located at the server, and one client x86 core when WICkit is located at the client. Depending on the experiment, for SmartNIC locations we show results for 1, or 1 and 7 cores.

#### 3.6.2 Benefits of Different Locations

The main benefit of using WICkit in a distributed application is the ability to write the WIC once, and decide at application start-up time whether to execute it at client, server, or SmartNIC CPUs, where each location offers specific performance and resource trade-offs. In this subsection we use our three workloads to explore such trade-offs, and we synthesize our observations in §3.6.2.

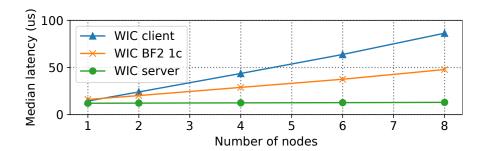

Figure 3.2: Unloaded latency of linked-list traversal as we vary the number of traversed nodes at all WICkit locations.

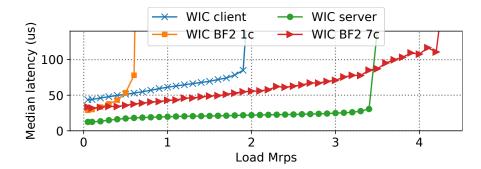

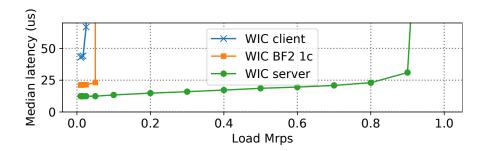

Figure 3.3: 4-node linked-list traversal latency under load at all WICkit locations. The server and client locations use 1 x86 CPU to serve load and the BF2 location uses 1 and 7 SmartNIC CPUs.

#### **Linked-list Traversal**

To understand the location trade-offs for this workload, we first evaluate how unloaded latency across locations changes as the number of traversed nodes in a WIC increases. Then, we measure latency across locations when traversing 4 nodes.

As shown in Figure 3.2, across WICkit's locations, the server provides lowest latency, and BF2 performs better than client when traversing two or more nodes. When traversing one node, a WIC located at the server takes  $12.1\mu$ s to complete, whereas at the client it takes  $14.4\mu$ s, and at BF2 it takes  $16.1\mu$ s. Client is 19% slower than server because the client location pays for a loopback message from the load generator to its runtime on the same machine, plus the network round trip for reading the node with RDMA (see Figure 3.1). BF2 latency is higher than client when reading 1 node as the location pays for the latency of a request message over the network to the SmartNIC, plus the latency of an RDMA read over PCIe. However, once each WIC traverses 2 nodes, BF2 achieves a latency of  $20.2\mu$ s and client's latency is 19% higher as it pays the full network round trip latency for both RDMA reads. As the benefits of reading nodes directly through PCIe apply for every memory access, reading 8 nodes is 93% faster in BF2 relative to client.

Next we analyze loaded latency while traversing 4 nodes. As Figure 3.3 shows, different locations saturate at distinct loads. The server location provides lowest latency until its maximum

Figure 3.4: Remote shared log latency under load at all WICkit locations. To serve load, client and server locations use 1 x86 core, and BF2 location uses 1 SmartNIC CPU.

throughput of 3.4M WIC/s. The better choice between client and BF2 depends on the load and the number of cores used by BF2. At low loads, BF2 using 1 core achieves lower latency than client, but at 0.5M WIC/s, the software overheads accrue in the one BF2 core and client latency is better beyond this point. However, by leveraging 7 BF2 cores the SmartNIC location can serve a load of 4.2M WIC/s, 7× the throughput achieved with 1 SmartNIC core.

#### **Remote Shared Log**

We now explore the benefits of each location in our remote shared log application by evaluating latency under load. As Figure 3.4 shows, server provides the lowest unloaded latency with a median request latency of 11.6µs. The workload is amenable to the server location, as WICLock uses CPU atomics to local memory, and the shared log's array of values provides good locality for the server CPU's cache. BF2 also keeps the WICLock in NIC-memory, but must access values through RDMA, resulting in 44% higher latency than server. Client has the highest latency because, besides having to read the values through the network, WICLock uses RDMA atomics to lock. Using an exclusive WICLock to implement critical sections that issue RDMA memory accesses significantly reduces the throughput of the client and SmartNIC locations (§3.4.2). This is because the WICLock is kept locked while RDMA memory accesses complete. Since the server location accesses memory locally, the time a lock is taken significantly reduces. Thus, throughput is highest at the server and achieves 1.3M WIC/s. BF2 achieves a throughput of 100K WIC/s, and additional BF2 cores do not improve throughput as the contended lock prevents maintaining multiple outstanding memory accesses at once.

#### Remote Key-value Store

In our last location trade-off exploration we evaluate our key value store's latency under load. Similarly to the shared log application, this cuckoo hash table uses one exclusive WICLock to protect the table during updates and queries, so the same throughput limitations apply. However, as shown in Figure 3.5, overall latencies are higher than in shared log, because both update and query need to compute the hash of the requested key, which is compute intensive.

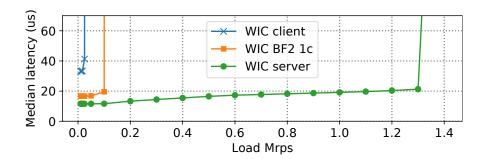

Figure 3.5: Remote cuckoo hash table latency under load at all WICkit locations. To serve load, client and server locations use 1 x86 core, and BF2 location uses 1 SmartNIC CPU.

#### **The Best Location**

For each location we support, are there scenarios in which users would prefer to run WICs in that location? Yes, but there are different factors that play a role in deciding which location is best for a given workload at a given time. The type and quantity of resources an application might want to use has an effect in the possible locations to consider. For instance, although the server location provides low latency and high throughput, it might not be ideal in scenarios where CPU availability is low, or when CPU cost is high. As we showed, the number of memory accesses a WIC issues can also be a factor in choosing a best location for latency. Similarly, offered load is a workload-specific factor that should be considered as well. A distributed application using WICkit is able to navigate the trade-off between remote memory access locations by writing WICs in a where-independent manner and choosing whichever is best at application start-up time.

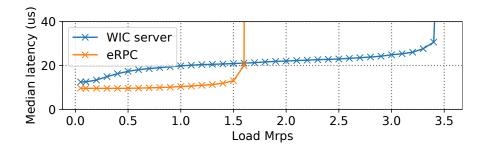

# 3.6.3 WICkit vs Location-dependent Systems

We now evaluate how WICkit's performance compares to location-specific approaches using the linked-list traversal workload. We first evaluate the performance of server-located approaches by comparing WICkit's asynchronous local memory backend and eRPC, the state-of-the-art RPC system for communicating between hosts [67]. To maximize eRPC performance, we set session credits to 2048, set the session request window size to 2048, and the max inline message to 512. We then compare WICkit's client location and an optimized 1-sided RDMA linked-list traversal implementation. Finally, no current system uses SmartNICs and we instead compare WICkit's SmartNIC location to both the eRPC and the 1-sided RDMA optimized implementation.

#### **Server Location**

We evaluate server-located approaches when traversing a 4-node linked-list as shown in Figure 3.6. WICkit uses the asynchronous local memory backend with a window size of 8 (§3.4.3).

We find that eRPC achieves best latency under load until the CPU serving the load saturates, and WICkit provides better throughput due to prefetching and very fast context switching of WICs. eRPC achieves an unloaded latency of 9.6µs per request, whereas WICkit takes 12.5µs per WIC.

Figure 3.6: Comparison of server locations on a 4-node linked-list traversal. Both approaches use one x86 server core. WIC server uses the asynchronous backend.

Figure 3.7: Comparison of client locations on a 4-node linked-list traversal.

The reason for eRPC's lower latency is due to its use of call backs, which are cheaper to invoke than coroutines since they do not have to be initialized. WICkit's asynchronous backend is able to achieve a throughput of 3.4M WIC/s,  $2.1 \times$  higher than eRPC. However, we note that the improvements of the asynchronous backend brought by prefetching local memory depends on the specific workload. Linked-list traversal is amenable to prefetching because every read node produces a last-level cache miss. We leave for future work exploring in more detail the benefits of the asynchronous backend.

#### **Client Location**

We now compare client-located approaches: WICkit's client, and an optimized 1-sided RDMA linked-list traversal implementation, which we refer to as opt-1s 1c when using one core. opt-1s is both a load generator and a location where memory-access logic executes. In contrast, WICkit's client location uses one core for the runtime, and another core for the load generator, both in the same machine (see Figure 3.1). Although WICkit's load generator does not access remote memory, we report opt-1s 2c as well. To maximize RDMA throughput, both systems 16 QPs in total to remote application data, where opt-1s 2c uses 8 QPs per-core.

Overall, as Figure 3.7 shows, opt-1s achieves better latency while WICkit's client location achieves higher throughput for one core. The unloaded latency to read 4-nodes through the network with opt-1s 2c is  $35\mu$ s whereas WICkit takes  $43.6\mu$ s, a 25% increase. WICs have a higher latency as

Figure 3.8: Latency for a 16-node linked-list traversal under load using WICs at BF2, an optimized 1-sided implementation, and eRPC.

opt-1s does not pay for loopback requests and replies between load generator and WICkit runtime, which take 1.4µs each way, and because it uses call backs instead of coroutines. The client location with one core achieves a throughput of 1.9M WIC/s, 72% higher than opt-1s using one core due to WICkit's batching mechanism described in §3.4.1. Finally, the client location using one core achieves 15% lower throughput than opt-1s 2c.

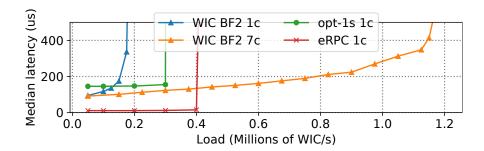

#### **SmartNIC Location**

We now compare the SmartNIC location to eRPC and opt-1s for context. Figure 3.8 shows the comparison where each request, or WIC, traverses 16 nodes.

eRPC provides lowest unloaded latency while BF2 1c is faster than opt-1s (similarly to Figure 3.2). However, BF2 1c saturates quickly with increased load whereas using more cores allows BF2 to maintain lower latency for larger loads. Although BF2 1c takes  $94.7\mu s$  per WIC when reading 16 nodes, it is 54% faster than opt-1s, and represents a software overhead of only  $1.5\mu s$  per memory access on top our baseline hardware latencies. In our hardware, each request from client to NIC takes  $4.9\mu s$ , each RDMA read takes  $3.8\mu s$ , and each message from NIC to client takes  $4.9\mu s$  as well. In terms of throughput, Blufield-2 using 1 core (*i.e.*, BF2 1c) achieves 58% of opt-1s's throughput, however, by using 7 cores BF2 achieves  $6.5\times$  higher throughput than when using 1.

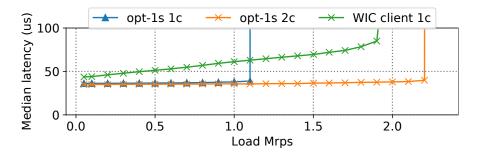

# 3.6.4 Backends Design

We now evaluate how our backend designs contribute to WICs performance across locations. We first explore the 1-sided RDMA backend performance by focusing on SmartNICs, as no previous system has leveraged them as a memory-access logic location. We evaluate our design decisions to (§3.4.1): multiplex memory accesses, use multiple RDMA queue pairs, use coroutines-based logical threads, and issue memory accesses in dynamic batches. Then, we evaluate our local memory backends in §3.6.4.

Figure 3.9: Comparison of multiplexing and not multiplexing RDMA accesses in a linked-list traversal WIC located at BF2. The labels above the marks show improvement of multiplex over no multiplex.

Figure 3.10: Throughput improvement as we increase the number of queue pairs, relative to using 1 queue pair. We show improvements for 1, 4 and 8 linked-list node traversals per WIC.

#### **Multiplexing RDMA Application Data Access**

We use our linked-list workload to measure WIC throughput as we increase the number of traversed nodes with two backends: our baseline 1-sided RDMA backend that multiplexes memory accesses, and a backend that does not multiplex accesses and runs WICs to completion. As shown in Figure 3.9, multiplexing memory accesses improves WIC throughput by 8.4-12.1× relative to not multiplexing when using one BF2 core. By using fast-yielding contexts, WICs efficiently relinquish the CPU after they issue an RDMA access and switch to a ready-to-run WIC, enabling multiple outstanding memory accesses at a time. We explore the impact of using slower yielding contexts later in this section.

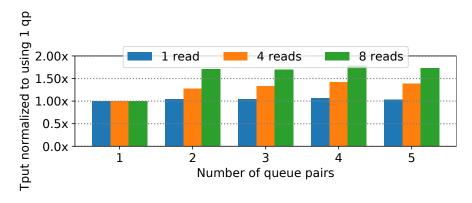

#### **RDMA Multiple Queue Pairs**

We evaluate how the use of multiple queue pairs impacts maximum throughput and latency in our linked-list workload. As discussed before, our BF2 RDMA adapter has a limit of 16 outstanding RDMA reads per queue pair. Using multiple queue pairs per-core provides the potential for WICkit to maintain additional outstanding reads, increasing throughput. However, it's unclear if

Figure 3.11: Throughput degradation when we add x-axis delay to coroutine yield, relative to baseline coroutine yield of 3ns.

our SmartNIC cores will be able to handle additional queue pairs and whether more queue pairs will negatively impact latency.

As Figure 3.10 shows, using multiple queue pairs per-core increases throughput. Using 4 queue pairs per-core improves throughput by 6% when traversing 1 node, and by 78% when traversing 8 nodes, relative to using 1 queue pair. Across 1, 4 and 8-node traversals, using 4 queue pairs increases latency at most by 1.7%, relative to using 1 queue pair. Therefore, our SmartNIC WICkit runtime uses 4 queue pairs per-core to increase memory access throughput to application data.

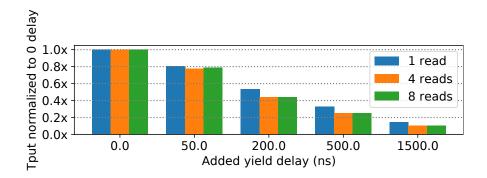

#### **Performance Impact of Yield Latency**

We now evaluate the performance impact of using alternative execution contexts to show coroutines, and their fast yielding latencies, are necessary for WICkit. We simulate the performance impact of execution contexts with higher yield latency by adding delays on top of coroutine yields. We use our linked-list traversal workload to traverse 1, 4 and 8 nodes.

We find that if our logical threads experienced yield latencies similar to user threads, SmartNIC throughput would degrade by 24% at best, and pthreads would cause the throughput to degrade at least 6.8×. Figure 3.11 shows simulated throughput degradation in BF2 when matching alternative execution contexts' yield latency; see Table 3.2. We make three observations. First, a 50ns delay represents a best case for user thread's yield latency in BF2, and we find the throughput in such a case would degrade by 24-29%. This represents a best case since user threads [102] take 52ns to yield in x86 cores. Second, a more realistic user thread yield latency in BF2 would be about 200ns. This would correspond to 4× the x86 latency, similarly to the BF2-pthread-yield latency being 4.5× the pthread-x86-yield latency (we measured both). In such a case, throughput would degrade by 1.87-2.27×. Finally, the 1500ns delay corresponds to the cost of using pthread yields and this would degrade throughput by 6.8-9.8×. Therefore, coroutines enable high WIC and memory access throughput by providing very fast yielding contexts. Alternative logical threads with higher yield latencies would lead to reduced throughput.

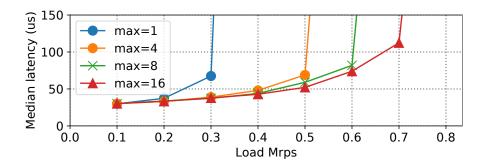

Figure 3.12: 4-node linked-list traversal WIC latency under load using 1 SmartNIC core and 4 QPs while varying the memory access maximum batch size.

Figure 3.13: Local memory backends comparison for server location.

#### **RDMA Dynamic Unsignaled Batching**

We evaluate our batching design described in  $\S 3.4.1$ . Traditionally, systems that batch observe increased latency as elements within a batch wait for longer before being submitted for processing. Thus, here we explore the effect different batch sizes have on latency under load for 4-node linked-list traversal WICs. As our batching is dynamic, a maximum batch size of m only guarantees that no batch will be larger than m, but does not guarantee that all batches will be of size m.

Counter intuitively, as Figure 3.12 shows, a batch size of 16 improves latency under load (e.g. at 0.3Mrps) relative to no batching. In addition, max=16 improves throughput relative to max=1 by  $2.3 \times$ . This is for three reasons: First because larger batch sizes reduce communication frequency between CPU and the RDMA adapter. Second, due to the dynamic nature of our batching, accesses within a batch stay pending for short enough time such that median latency does not increase. And third, because given our use of intra-batch unsignaled accesses, signaling a completion of a large batch costs the same for the RDMA adapter, and for the CPU, than a completion for a smaller batch.

#### **Local Memory Backends**

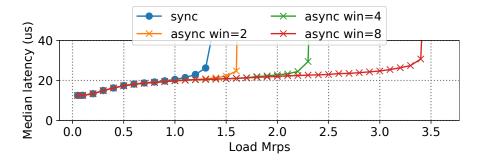

We evaluate our two local memory backends described in §3.4.1 with our linked-list traversal workload. sync refers to the synchronous backend that runs WICs to completion, and async win=x refers to the asynchronous backend using a window of size x. As shown in Figure 3.13, we find that async achieves higher throughput than sync without affecting latency at low loads. In particular, a window of 8 provides  $2.6 \times$  higher throughput than sync. However, we also observe that larger windows increases latency at high loads.

### 3.7 Related Work

Accessing remote state. Many existing systems enable applications to access and modify state on a remote server. Some systems such as FaRM [40], Pilaf [98], and DrTM [126] achieve this by executing memory-access logic on clients using 1-sided RDMA. Other systems such as FaSST [71], HERD [68], and eRPC [67] execute memory-access logic on servers using 2-sided RDMA or messages over commodity network hardware. Finally, DrTM+H [125], XStore [124], and Octopus [88] combine both 1-sided and 2-sided RDMA in order to implement a specific application, such as a distributed transaction system or a key-value store. However, none of these approaches provide a general abstraction that enables arbitrary applications to execute at different locations without modification; this is what WICkit aims to do.

**More expressive RDMA.** Several prior works have attempted to bridge the gap between 1-sided and 2-sided RDMA by augmenting 1-sided RDMA with more expressive operations, such as chained operations. These efforts propose implementing more complex operations directly in NIC hardware [3,26,38], in FPGAs [80,113], or in SoC-based SmartNICs [5], or extending the IOMMU to trigger handler functions on the CPU [22].

WICkit expands on the proposal in [5] by designing a programming model and runtime system, and showing that these can be used to execute memory-access logic at different locations throughout a datacenter. WICkit can be deployed today on existing hardware, and does not require deploying additional FPGAs or SmartNICs or waiting for new NICs to be developed. In addition, if these new technologies are adopted, future work could explore compiling WICs to execute on them as well.

**SmartNICs.** In recent years, many systems have explored utilizing SoC-based, FPGA-based, or ASIC-based SmartNICs in distributed applications. These systems typically focus on offloading application logic [43, 56, 87, 103] or network processing [47, 61, 101, 105] to a server-attached SmartNIC. Other systems have proposed using SmartNICs for load balancing [35] or disaggregated storage [97]. These efforts focus primarily on offloading computation from servers to SmartNICs, and none provides a general framework that allows application logic to be executed at different locations throughout a datacenter, as WICkit does.

**Shipping compute.** Several prior works have studied questions of when to move compute to memory or storage and when the alternative—shipping data to compute—is preferable. For example, near-memory compute [114] considers CPU architectures that push computation to memory,

AIFM enables users to register specific code to execute on remote memory servers [108], and other work proposes adding compute capabilities to SSDs [39].

Splinter [23,76] proposes a system that enables transactions to either execute at a datastore or be "pushed back" to execute on clients instead. It is designed to ensure serializability and targets latencies in the 100s of microseconds. In contrast, WICkit focuses on accessing memory rather than storage, with target latencies of 10s of microseconds. This imposes new challenges in designing a high-performance runtime, and yields a different runtime design (§3.4). Kayak [130] builds on Splinter to dynamically adjust what fraction of requests are executed locally vs. on a remote storage device; in the future, WICkit may be able to adopt a similar approach to dynamically decide which location to run WICs at.

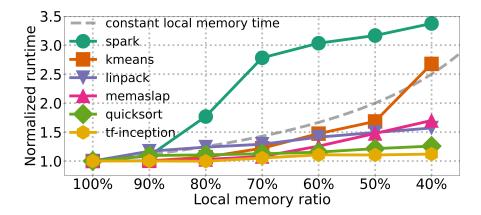

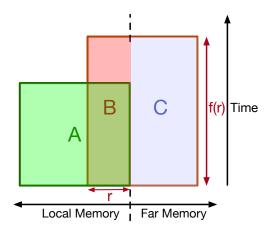

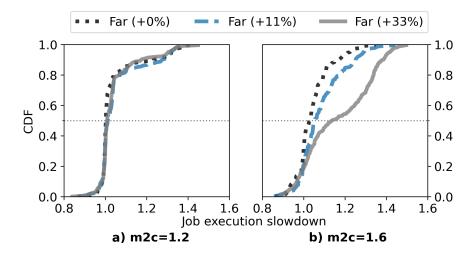

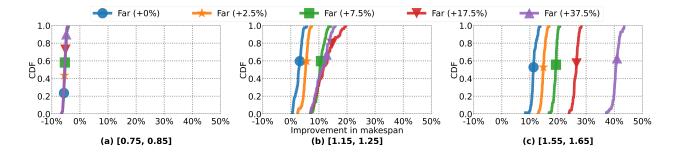

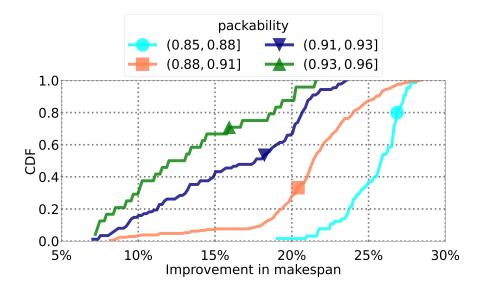

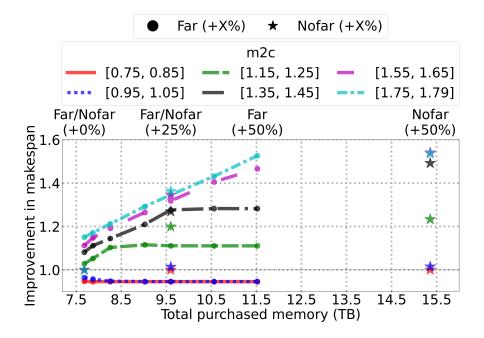

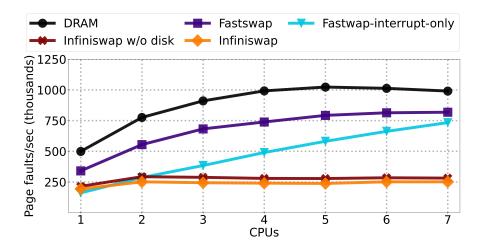

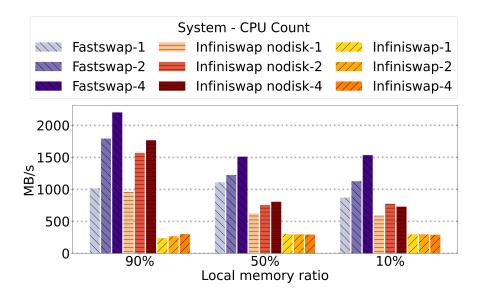

Computation migration. Prior work has also looked at migrating computation running in distributed shared memory (DSM) clusters [24,62]. These efforts are similar to ours in that they focus on developing mechanisms that allow memory-access logic to run at different locations, and operate on a common pool of application memory. However, these works assume that all processors access memory using a common DSM API. By contrast, our setting requires the use of different logic for accessing application memory from different locations. Additionally, the difference in latencies also requires us to assume synchronous accesses at some locations and asynchronous accesses at others. As we showed in §3.6, not doing so can carry a performance penalty. As a result, approaches to migrating computation in DSM clusters cannot directly be used to build WICs.