# Milli-Volt Micro-Electro-Mechanical Relay Technology for Energy-Efficient Computing

Benjamin Osoba

## Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-27 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-27.html

May 1, 2021

Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Milli-Volt Micro-Electro-Mechanical Relay Technology for Energy-Efficient Computing

By

Benjamin O. Osoba

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Kristofer Pister Professor Junqiao Wu

Summer 2020

## Milli-Volt Micro-Electro-Mechanical Relay Technology for Energy-Efficient Computing

Copyright ©2020

By

Benjamin O. Osoba

#### Abstract

#### Milli-Volt Micro-Electro-Mechanical Relay Technology for Energy-Efficient Computing

By

Benjamin O. Osoba

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

#### University of California, Berkeley

Professor Tsu-Jae King Liu

The proliferation of information and communication devices over the past few decades has been enabled by continual advancement of semiconductor manufacturing technology to steadily miniaturize semiconductor switching devices – most notably, metal-oxide-semiconductor field effect transistors (MOSFETs) - to increase the number of transistors in the most advanced integrated circuit (IC) products, at a pace set by Moore's Law, for enhanced chip functionality and performance. In recent years, however, the incremental benefit of transistor scaling has diminished largely because the Boltzmann energy distribution of electrons in a semiconductor results in switching steepness (subthreshold swing) proportional to the thermal voltage  $\left(\frac{kT}{a}\right)$ , which does not scale. As a result, conventional MOSFETs cannot switch ON/OFF more abruptly than 60 mV/decade at room temperature, which limits the extent to which the transistor threshold voltage  $(V_{\rm T})$  can be reduced for a given OFF-state leakage current specification ( $I_{\rm OFF}$ ). As the operating voltage  $(V_{DD})$  of a digital IC is reduced with increasing transistor density to meet power density constraints (set by chip cooling limitations), then, the gate overdrive voltage  $(V_{DD} - V_T)$  is disproportionately reduced, limiting the transistor ON-state current and hence IC performance. With the advent of the Internet of Things, the need for more energy-efficient electronics has emerged; alternative switching devices that can be operated at much lower voltage than the MOSFET will be required. Micro-electro-mechanical (MEM) relays are promising candidate switching devices for low-voltage digital ICs, since they can achieve immeasurably low  $I_{OFF}$  and abrupt switching behavior across a wide range of operating temperatures. Since MEM relays exhibit hysteretic switching behavior (*i.e.*, the value of the control/gate voltage at which a relay switches ON is different than that at which it switches OFF) the hysteresis voltage sets a lower limit for their operating voltage.

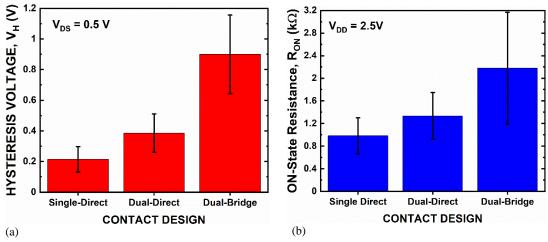

This dissertation discusses approaches and challenges for realizing milli-Volt MEM relay technology for energy-efficient computing. First the application of self-assembled molecular (SAM) anti-stiction coatings to reduce contact adhesive force and thereby the hysteresis voltage is investigated, and stable sub-50 mV operation is demonstrated. Next the issue of variability in relay performance parameters over many switching cycles and from device to device is systematically studied, and SAM coating is found to improve stability. Then the effects of contacting electrode design and body-biased operation on relay ON-state resistance ( $R_{ON}$ ) are investigated. The direct

source/drain contact design provides for lowest and least variable  $R_{ON}$ . Ultra-low-voltage relay operation facilitated by body-biasing results in lower contact velocity, which mitigates the need for a wear-resistant contacting electrode material while necessitating a contacting electrode material that is not susceptible to oxidation.

For my family, past, present and future

## TABLE OF CONTENTS

| Chapter 1: | Introduction1                                                       |

|------------|---------------------------------------------------------------------|

| 1.1        | Brief History of Integrated Circuit (IC) Computing Devices          |

| 1.2        | CMOS Technology and Digital Logic1                                  |

| 1.3        | CMOS Energy Efficiency Limit                                        |

| 1.4        | MEM Relay Structure and Operation                                   |

| 1.5        | Relay Fabrication Process                                           |

| 1.6        | Dissertation Objectives                                             |

| 1.7        | References                                                          |

| Chapter 2: | Sub-50 milli-volt NEM Relay Operation Enabled by Self-Assembled     |

|            | Molecular Coating 13                                                |

| 2.1        | Introduction                                                        |

| 2.2        | Body-Bias Effect for Versatile Pass Gate Logic                      |

| 2.3        | Self-Assembled Monolayer (SAM) Molecular Coating 15                 |

| 2.4        | Effects of Molecular Coating on Relay Switching Characteristics     |

| 2.5        | Discussion                                                          |

| 2.6        | Summary                                                             |

| 2.7        | References                                                          |

| Chapter 3: | Variability Study for Low-Voltage Micro-Electro-Mechanical Relay    |

|            | Operation 23                                                        |

| 3.1        | Introduction                                                        |

| 3.2        | Relay Switching Voltage Variability                                 |

|            | 3.2.1. Body-biased switching voltage stability                      |

|            | 3.2.2. Process-induced variations                                   |

| 3.3        | Effects of Anti-Stiction Coating                                    |

| 3.4        | Discussion                                                          |

| 3.5        | Summary                                                             |

| 3.6        | References                                                          |

| Chapter 4: | Study of MEM Relay Contact Design and Body-Bias Effects on ON-state |

|            | Resistance Stability    31                                          |

| 4.1        | Introduction                                                        |

| 4.2        | Relay Design and Operation                                          |

| 4.3        | Relay Fabrication Process                                           |

| 4.4        | Comparison of Relay Contact Design                                  |

| 4.5        | Effects of Supply Voltage Scaling and Body-Bias |    |

|------------|-------------------------------------------------|----|

| 4.6        | Discussion                                      |    |

| 4.7        | Summary                                         |    |

| 4.8        | References                                      |    |

| Chapter 5: | Conclusions and Future Work                     | 39 |

| 5.1        | Summary of Research Contributions               |    |

| 5.2        | Possible Directions of Future Work              |    |

| 5.3        | References                                      |    |

| Appendix   |                                                 |    |

## LIST OF FIGURES

#### **Chapter 1: Introduction**

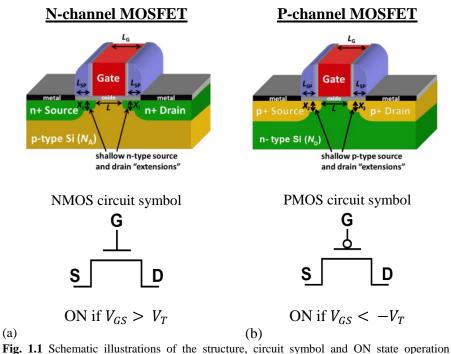

- Fig. 1.1 Schematic illustrations of the structure, circuit symbol and ON state operation conditions of (a) NMOS and (b) PMOS field effect transistors

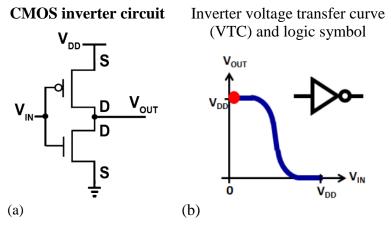

- Fig. 1.2 CMOS inverter (a) circuit diagram (b) voltage transfer curve

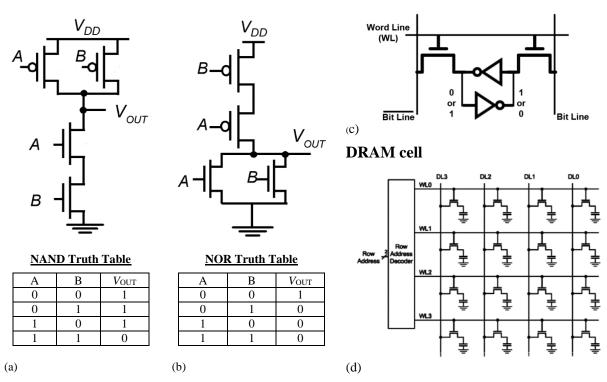

- Fig. 1.3 CMOS logic and memory circuits (a) 2-input NAND gate (b) 2-input NOR gate and(c) Static Random Access Memory (SRAM) cell and (d) Dynamic Random AccessMemory (DRAM) cell array

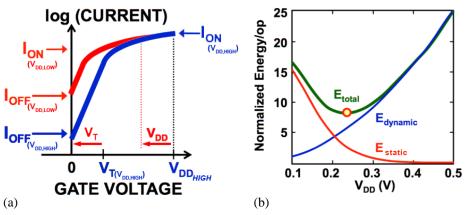

- Fig. 1.4 Conceptual illustrations of (a) MOSFET transfer characteristic and (b) normalized energy per digital CMOS operation

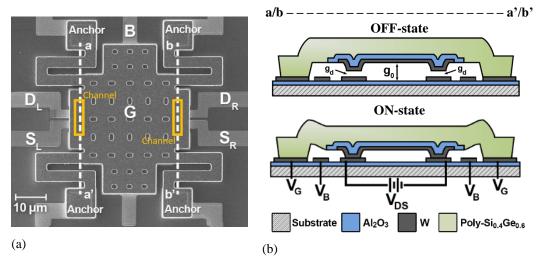

- Fig. 1.5 (a) Plan-view scanning electron micrograph (SEM) image of a fabricated 6-terminal MEM relay and (b) Schematic cross-section A-A' in the OFF-state and ON-state

- Fig. 1.6 (a) Illustration of electrostatic actuation and spring restoring forces in the MEM relay and (b) measured *I-V* characteristics

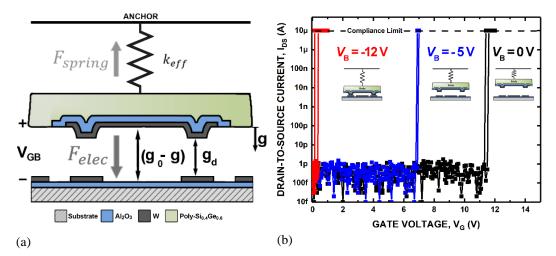

- Fig. 1.7 CoventorWare MEMS+ simulated relay fabrication process

### Chapter 2: Sub-50 milli-volt NEM Relay Operation Enabled by Self-Assembled Molecular Coating

- Fig. 2.1 (a) Measured relay *I-V* characteristics showing the effect of body-biasing, which is utilized to achieve low-voltage operation for (b) pull-down (N-relay) operation and (c) pull-up (P-relay) operation

- Fig. 2.2 (a) Relay inverter circuit and (b) measured voltage waveforms for inverter circuit in which a non-coated relay is configured as a pull-down device

- Fig. 2.3 (a) Molecular structure of PFDTES and (b) qualitative illustration of PFDTES coating

- Fig. 2.4 (a) photograph and (b) qualitative illustration of the vapor phase molecular coating process

- Fig. 2.5 Contact-angle measurements (a) pre- and (b) post- SAM-coating

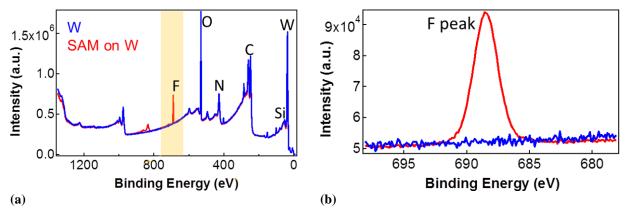

- Fig. 2.6 (a) Characteristic peaks from X-ray Photoelectron Spectroscopy (XPS) measurements and (b) the fluorine peak

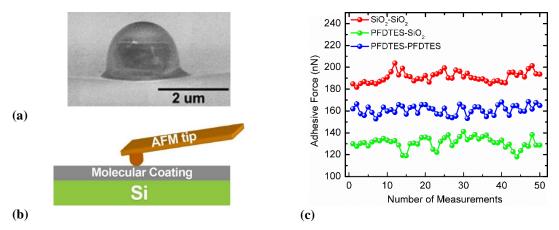

- Fig. 2.7 (a) SEM image of SiO<sub>2</sub> AFM tip, (b) illustration of Atomic Force Microscope (AFM) adhesion force measurement and (c) empirical measurements indicating that surface adhesion is decreased with PFDTES coating

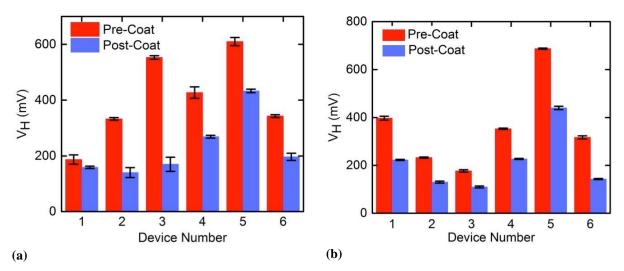

- Fig. 2.8 Summary of measured data, pre- and post-PFDTES coating

- Fig. 2.9 Measured R<sub>ON</sub> data for L = 15  $\mu$ m relays operated at  $V_{\rm B}$  = -9 V and  $V_{\rm IN} = V_{\rm DD}$  = 3 V

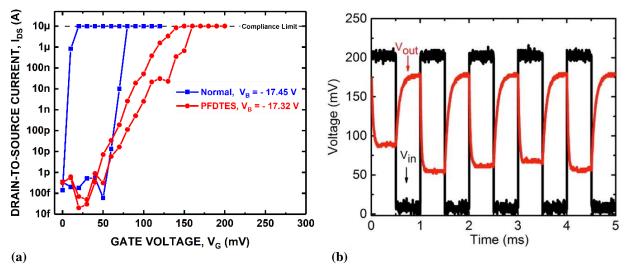

- Fig. 2.10 (a) Measured  $L = 8 \mu m$  relay *I-V* characteristics (pre- and post- PFDTES coating) and (b) measured voltage waveforms for inverter circuit in which a relay coated with PFDTES is configured as a pull-down device

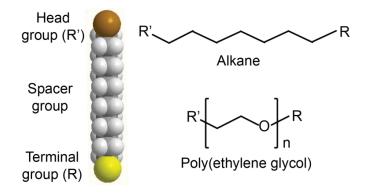

- Fig. 2.11 An alkane molecule with Young's modulus in the GPa regime and poly(ethylene glycol) with Young's modulus in the MPa regime, shown as examples of chemical synthesis

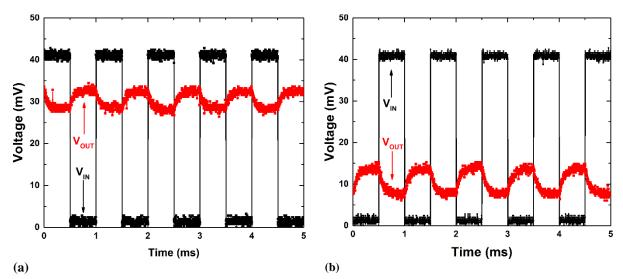

- Fig. 2.12 Measured voltage waveforms demonstrating sub-50 mV relay-based inverter circuit operation

- Fig. 2.13 Molecular structure of PFOTES

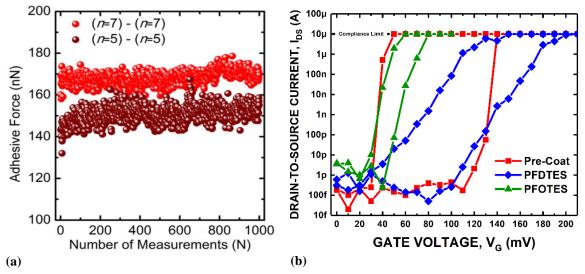

- Fig. 2.14 (a) AFM-based measurements of coated contact adhesive force and (b) measured relay *I-V* characteristics, comparing the effects of PFOTES and PFDTES anti-stiction coatings

#### Chapter 3: Variability Study for Low-Voltage Micro-Electro-Mechanical Relay Operation

- Fig. 3.1 Stable low voltage operation over 100 DC sweeps enabled by body-biasing

- Fig. 3.2 Evolution of (a) relay switching voltages and (b) hysteresis voltage for a body-biased relay operated with various values of drain-to-source voltage  $V_{DS}$

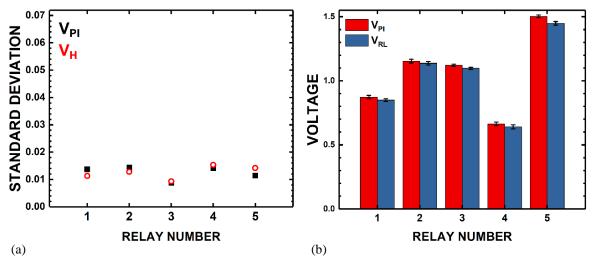

- Fig. 3.3 Measured variability in (a)  $V_{\rm PI}$  and (b)  $V_{\rm H}$  for multiple relays operated at varying  $V_{\rm B}$

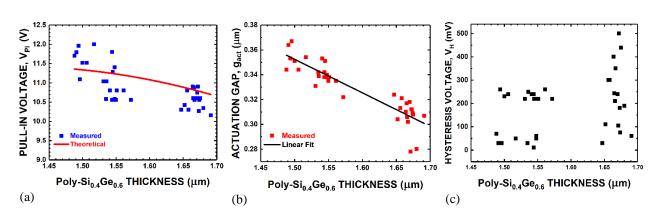

- Fig. 3.4 Measured impact of process-induced variations in Poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> thickness on (a)  $V_{\rm PI}$  (b) actuation gap g and (c)  $V_{\rm H}$

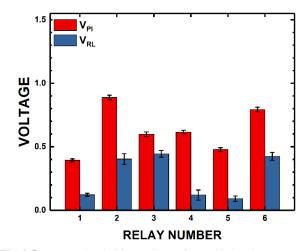

- Fig. 3.5 Measured switching voltages for multiple relays operated at  $V_{DS} = 1$  V and  $V_B = -14.5$  V

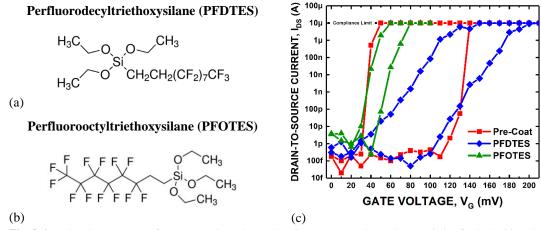

- Fig. 3.6 Molecular structure of (a) PFDTES vs. (b) PFOTES (c) measured *I-V* characteristics for body-biased relays, showing the effects of anti-stiction coatings

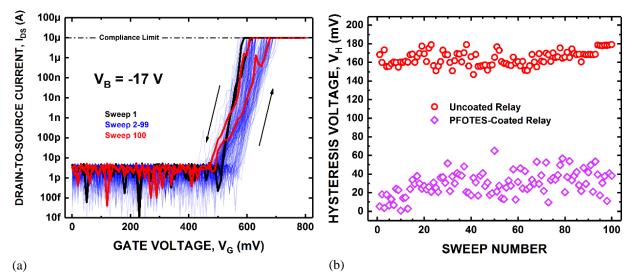

- Fig. 3.7 (a) Measured *I-V* characteristics and (b) evolution of measured  $V_{\rm H}$  for PFOTES-coated MEM relay operated over 100 gate voltage sweeps at  $V_{\rm DS} = 1$  V and body-biased conditions

- Fig. 3.8 Measured (a) variability in  $V_{PI}$ ,  $V_H$  and (b) switching voltages for multiple PFOTES relays operated at  $V_{DS} = 1$  V and  $V_B = -16$  V

### Chapter 4: Study of MEM Relay Contact Design and Body-Bias Effects on ON-state Resistance Stability

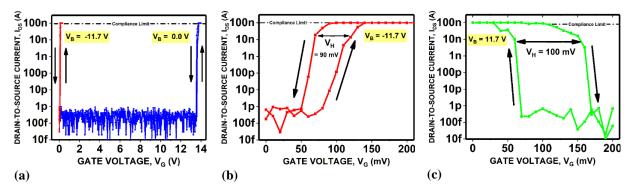

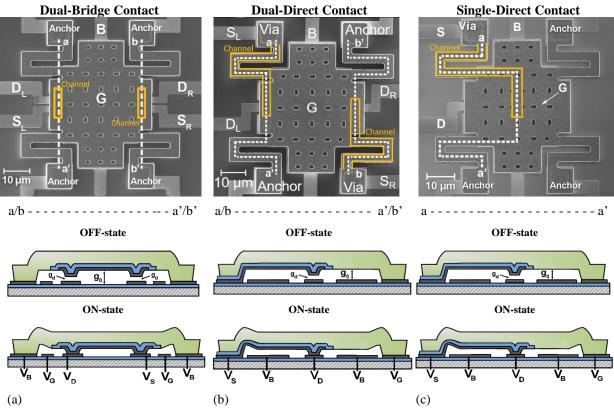

- Fig. 4.1 SEM micrograph images (top) and schematic cross-sections (bottom) of relays with different contacting electrode designs in the OFF state and in the ON state: (a) dual bridge source/drain contact, (b) dual direct source/drain contact, and (c) single direct source/drain contact

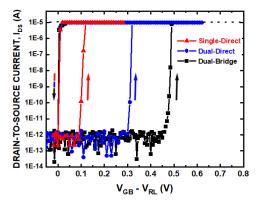

- Fig. 4.2 Measured I-V characteristics for body-biased relays of various contact designs

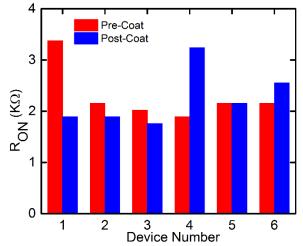

- Fig. 4.3 Average measured values of (a)  $V_{\rm H}$  and (b)  $R_{\rm ON}$  for 10 relays of each contact design with  $V_{\rm B} = 0$ V

- Fig. 4.4 Relay-based inverter circuit utilized for R<sub>ON</sub> characterization

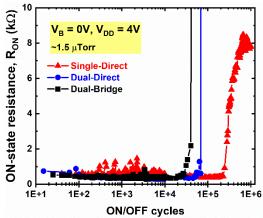

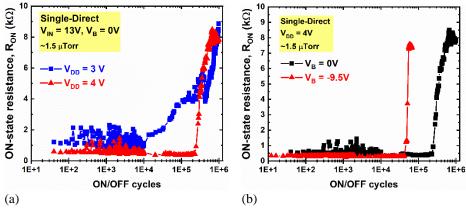

- Fig. 4.5 Measured R<sub>ON</sub> as a function of the number of ON/OFF switching cycles, for MEM relays of varying contact design

- Fig. 4.6 Measured  $R_{ON}$  as a function of the number of ON/OFF switching cycles, for a singledirect contact relay measured with varying (a)  $V_{DD}$  and (b)  $V_{B}$

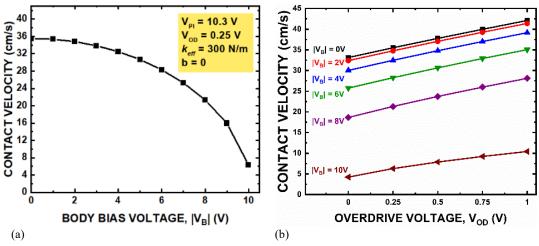

- Fig. 4.7 Numerically simulated relay contact velocity under varying (a)  $V_{\rm B}$  and (b)  $V_{\rm OD}$  operating conditions

### ACKNOWLEDGMENTS

"It was all a dream..." These words certainly ring true as it pertains to this academic milestone and I have to begin by giving all glory to God for allowing me to see it through. There have been many highs and lows throughout my graduate school experience and I would be remiss if I did not express my appreciation to those who have proven pivotal in my matriculation. I feel that this dissertation and my graduation experience in general are testaments to the Yoruba proverb *A kò lè tìtorí pé ònà jìn kí a wá padà séhìn*, meaning "Because the destination is far, is no reason to stop a journey." Despite the often challenging times, my support system was always there to provide the advice, comfort, and guidance that has helped me to transverse this journey and ultimately succeed.

I would like to give gratitude to my advisor, Professor Tsu-Jae King Liu, for her continuous guidance and support throughout my graduate studies at Berkeley. Through your example of technical innovation, research acumen and vision, I feel that I have grown leaps and bounds as an academic and scholar. I appreciate your willingness to not only mentor me as a researcher, but also as a leader and member of the greater campus community. You believed in me even when I did not believe in myself and it is your steadfast support which truly made the difference in my development as an engineer. I hope one day to not only continue your legacy of technical achievement, but also impact younger generations of engineers just as you have done for me.

I would also like to thank Prof. Kristofer Pister for meaningful conversations about interesting applications for mechanical devices, improvements on quantitative research methodology, and analog circuits. I am grateful for your willingness to serve as the chair of my qualifying exam committee, and for also serving on my thesis committee. Furthermore, I would like to thank Profs. Ana Arias and Junqiao Wu for also serving on these committees and providing frequent advice throughout the various stages of graduate school. I would like to thank Prof. Jeffrey Bokor for taking the extra time to work with me on quantum mechanics and other advanced engineering concepts outside of class. I would also like to thank Profs. Chenming Hu, Sayeef Salahuddin, Vivek Subramanian, Clark Nguyen, Boubacar Kanté, Ali Javey, and Seth Sanders for their instruction and career advice in the field of electrical engineering.

I would also like to thank all of the EECS department and College of Engineering faculty/staff who were involved in helping me administratively and technically. This includes Charlene Hughes, Dahlia Case, Audrey Sillers, Susanne Kauer, Tiffany Reardon, Meltem Erol, Lea Marlor, Charlotte Jones, Dr. Josephine Yuen, Dr. Kedrick Perry, Dr. Sharnnia Artis (now at UC Irvine), Prof. Oscar Dubon, Prof. Kara Nelson, and many others, all of whom helped provide me with a strong foundation at Berkeley. I would especially like to thank Shirley Salanio for her continuous advice and encouragement, especially in the times of adversity. I would like to thank Dr. Sheila Humphrey as well for her kindness and willingness to share insight and literature about Berkeley history.

I would like to thank my friends, classmates and colleagues, who all provided both levity amidst the often difficult work of research and motivation in form of community. To my entering class cohort – including Drs. Carlos Biaou, Juan Pablo Llinas, Akshay Pattabi, Jodi Loo, Mahsa

Sadeghi, Oladapo Afolabi, Howard Mao, and Jane Yu – I love you and thank you for helping me to get through the tough times. Thank you to Dr. William Tarpeh, Dr. Pierce Gordon, Dr. Kene Akametalu, Dr. Frances Roberts-Gregory and other Black student leaders for helping me to learn different ways to serve my community. I appreciate the Black Graduate Engineering and Science Students (BGESS) for allowing me to serve as a student leader and learn in greater detail about the systemic obstacles facing African and African-American students; I hope to use this knowledge to break down barriers for Black engineers who will be following behind me. Thank you to my friends Robert Baker, Juan Lascano, Sam Owens, Jaime Hinckson, Chad Evans, Candace Gilchrist, Khalia Braswell, Dr. Racheida Lewis, Joshua Sherfield, Dr. Sara Awartani, Azzedin Jackson, Christiane Stachl, Opeyemi Ogedengbe and Aaron McFall for a consistent listening ear and for providing a support system outside of academics.

I must also express my deep gratitude to the King Liu research group and my collaborators for this thesis project: Urmita Sikder, Zhixin Alice Ye, Tsegereda Esatu, Lars Tatum, Xiaoer Hu, Jatin Patil, Laura Brandt, Maurice Roots, Edgar Acosta, Liam Dougherty, Jane Edgington, Kathy Le, Dr. Nuo Xu, Dr. I-Ru Chen, Dr. Yenhao Chen, Dr. Bivas Saha, Dr. Sergio Almeida, Dr. Kimihiko Kato, Dr. Sangwan Kim, Dr. Fei Ding, Dr. Chuang Qian, Dr. Xi (Robin) Zhang, Dr. Thomas Rembrandt, Dr. Daniel Connelly, Dr. Rebecca Mih, Dr. Alexis Peschot, and Dr. Farnaz Niroui. Without all of your expertise and frequent discussions, I would not have learned as much nor improved to this degree as an academic. I've all of our group picnics and outings as well, you all are the best!

Thank you to Dr. Bill Flounders for access to the Marvell Nanofabrication Laboratory, where much of this work was completed. I would also like to thank nanolab staff – including Richelieu Hemphill, Brian McNeil, Danny Pestal, Ryan Rivers, and Dr. Jeffrey Clarkson – for helping me learn the various fabrication and lab maintenance processes.

Thank you to Bishop J.W. Macklin, Elder Michael Head, Elder Marcus Williams, and my entire church family at Glad Tidings International Church of God in Christ for all of your support and spiritual guidance.

Thank you to the National Science Foundation, Ford Foundation, and National GEM Consortium for offering fellowship support and funding for my graduate education.

I would also like to thank my various mentors for providing unwavering guidance throughout my life. This includes Dr. Frances Williams, Dr. Demetris Geddis, Dr. Jeremy Waisome, Dr. Aliecia McClain, and Jelece Morris, each of whom has been directly responsible for my interest in engineering to begin with.

Finally, I would like to give all of my love and gratitude to my family, especially my loving wife, Charise Osoba. I could not have overcome the many obstacles of completing graduate school without the steadfast support and foundation you provided for me. To my parents Babajide and Teresa Osoba, I am indebted to the sacrifices and efforts you made for me when I was young. To my sisters Omoniyi Obioha, Folakemi Okeowo and my Godbrother Quinn Andrews, thank you for your love and support. Without each of you, I would not have been able to stay grounded and motivated to complete this journey. I dedicate this document to you.

## **CHAPTER 1:**

## Introduction

#### **1.1 BRIEF HISTORY OF INTEGRATED CIRCUIT (IC) COMPUTING DEVICES**

Since the late 1950s, the electronics industry has rapidly advanced and proliferated throughout the world, bringing about the digital information age that has transformed various aspects of life in modern society. Examples include the Apollo Guidance Computer that facilitated the successful Apollo space program in the 1960s [1], and computer control of sound synthesizers via the Musical Instrument Digital Interface (MIDI) invented in 1982 [2] that revolutionized music performance, production and recording. The development of the integrated circuit (IC) [3] and steady advancement in planar semiconductor processing technology [4] to enable ever higher levels of component integration on an IC "chip" following Moore's Law [5] has provided for continual reductions in cost per function and increases in computing performance (operations per second). Today, state-of-the-art ICs comprise billions of semiconductor devices known as transistors. The Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is the predominant type of transistor used for computational ICs, and act as switches that either allow current to flow (in the ON state) or prevent current from flowing (in the OFF state) to implement digital logic functions [6][7].

#### **1.2 CMOS TECHNOLOGY AND DIGITAL LOGIC**

Schematic illustrations of n-channel (NMOS) and p-channel (PMOS) field-effect transistor structures are shown in **Fig. 1.1**. The ON/OFF state of a MOSFET is controlled via voltage applied to the Gate electrode ( $V_G$ ) relative to the voltage applied to the heavily doped (electrically conductive) Source region ( $V_S$ ). The Gate voltage is capacitively coupled to the electric potential of the semiconductor Channel region under the Gate electrode, and thereby controls the height of the potential barrier between the heavily doped (electrically conductive) Source region and the Channel region. When a driving voltage  $(V_{DS})$  is applied between the Source and Drain regions, the rate of thermionic emission of mobile charge carriers from the Source region into the Channel region (which is doped of opposite conductivity type as the Source and Drain regions) increases exponentially as the height of this source injection barrier is reduced linearly with increasing  $V_{\rm GS} \equiv V_{\rm G} - V_{\rm S}$ . When  $|V_{\rm GS}|$  is increased beyond a certain threshold voltage ( $V_{\rm T}$ ), transistor current flow is no longer limited by thermionic emission; an inversion layer of mobile charge ("channel") forms at the surface of the semiconductor under the Gate electrode, allowing electric current to easily flow between the Source region and the heavily doped Drain region if  $V_{DS} \neq 0$ , limited by carrier drift velocity. For NMOS devices,  $V_{\rm G}$  must be higher than  $V_{\rm S}$  by at least  $V_{\rm T}$  (*i.e.*,  $V_{\rm GS} > V_{\rm T}$ ) in order for an inversion layer of electrons to form at the surface of the semiconductor so that electrons can flow from the n-type Source region through the channel to the n-type Drain region. For PMOS devices,  $V_{\rm G}$  must be lower than  $V_{\rm S}$  by at least  $V_{\rm T}$  (*i.e.*,  $V_{\rm GS} < -V_{\rm T}$ ) in order for an inversion layer of positively charged holes to form at the surface of the semiconductor so that holes can flow from the p-type Source region through the channel to the p-type Drain region. NMOS and PMOS FET symbols used for circuit diagrams, and their switching requirements, are also shown in Fig. 1.1.

conditions of (a) NMOS and (b) PMOS field effect transistors. Critical dimensions are indicated: gate length ( $L_G$ ), spacer length ( $L_{SP}$ ), source/drain extension junction depth ( $X_J$ ), and bulk dopant concentration ( $N_A$ ,  $N_D$ ).

(a)

NMOS and PMOS field-effect transistors are fabricated and electrically connected together to form ICs [4] that perform a variety of digital logic operations [6][7]. The simplest logic circuit is the inverter, illustrated in Fig. 1.2, comprising a pair of NMOS and PMOS transistors. As shown in Fig. 1.2(a), the transistor Gate electrodes are connected together to form the input node, while the transistor Drain electrodes are connected together to form the output note; the NMOS Source is biased at the lowest voltage (ground, or 0 V) while the PMOS Source is biased at the highest

voltage (the power supply voltage,  $V_{DD}$ ). The transistors operate in a complementary manner, *i.e.*, when one turns ON the other turns OFF, and *vice versa*: The NMOS transistor is ON when the input voltage is high (*e.g.*,  $V_{DD}$ ), connecting the output node to ground; hence it is referred to as a "pull-down" device. The PMOS transistor is ON when the input voltage is low, connecting the output node to  $V_{DD}$ ; hence it is referred to as a "pull-up" device.

When the input node is charged so that the input voltage ( $V_{IN}$ ) changes from 0 V to  $V_{DD}$ , the NMOS transistor turns ON while the PMOS transistor turns OFF, *i.e.*, the output node is discharged through the NMOS transistor so that the output voltage ( $V_{OUT}$ ) is "pulled down" to 0 V, following the voltage transfer characteristic (**Fig. 1.2(b**)). The time required for this operation depends on the NMOS transistor ON-state "drive" current and the capacitance of the output node; the larger the drive current and/or the smaller the output node capacitance, the faster the output node discharges to ground. Similarly, the time required for  $V_{OUT}$  to transition from 0 V to  $V_{DD}$  after  $V_{IN}$  transitions from  $V_{DD}$  to 0 V depends on the PMOS transistor drive current and the capacitance of the output node.

Note that when the inverter is static (*i.e.*, not transitioning from one state to the other), one transistor is ON while the other is OFF. Moreover, the transistor that is OFF sustains a large voltage difference between the Source and Drain regions ( $V_{DS}$ ), resulting in OFF-state leakage current ( $I_{OFF}$ ) – which the other transistor readily allows to flow since it is ON. Therefore, power is continuously dissipated ( $V_{DD} \times I_{OFF}$ ) when a CMOS logic circuit is static.

Fig. 1.2 CMOS inverter (a) circuit diagram (b) voltage transfer curve [7].

More complex logic functions are implemented with complementary pairs of NMOS and PMOS transistors that serve as pull-down and pull-up devices, respectively; hence the term "CMOS" logic technology. Examples include NAND (**Fig. 1.3(a**)) and NOR (**Fig. 1.3(b**)) digital logic gates. A static memory (SRAM) cell is implemented with two cross-coupled inverters and an additional two NMOS transistors used to pull-down their respective storage nodes during a write or read operation. A more compact but dynamic (*i.e.*, requiring periodic refreshing) memory (DRAM) cell comprises a single NMOS transistor and a capacitor to store charge (**Fig. 1.3(c-d**)) [8].

#### **CMOS NAND gate**

**CMOS NOR gate**

**Fig. 1.3** CMOS logic and memory circuits (a) 2-input NAND gate (b) 2-input NOR gate and (c) Static Random Access Memory (SRAM) cell and (d) Dynamic Random Access Memory (DRAM) cell array [8]. Logic '1' corresponds to high voltage; logic '0' corresponds to low voltage.

#### **1.3 CMOS ENERGY EFFICIENCY LIMIT**

Traditionally, transistor miniaturization (*i.e.*, dimensional scaling) was accompanied by commensurate reduction in operating voltage ( $V_{DD}$ ) to maintain a constant peak electric field (desirable for ensuring long-term reliability of transistor operation), a trend known as "Dennard Scaling" [9]. This scaling methodology provided for improved circuit operating speed at a constant chip power density. Since the 2000s, however, voltage scaling slowed down even as transistor scaling continued, because the  $V_{T}$  of a MOSFET cannot be scaled too close to 0 V because  $I_{OFF}$  increases exponentially (**Fig. 1.4(a**)) and hence the static power dissipation of a CMOS circuit increases exponentially with decreasing  $V_{T}$ . The operating speed of a CMOS circuit is dependent on transistor on-state drive current ( $I_{ON}$ ), which in turn is dependent on the gate overdrive voltage ( $V_{DD} - V_{T}$ ); a reduction in  $V_{DD}$  would result in smaller  $I_{ON}$  and hence slower circuit operation, if  $V_{T}$  cannot also be reduced.

The emergence of the "Internet of Things" in recent years has led to the need for more energyefficient computing devices. Any CMOS-based digital logic circuit has a fundamental energy efficiency limit, however, due to non-zero transistor leakage current. This can be understood by considering the dynamic component (due to capacitive charging/discharging, proportional to the square of  $V_{DD}$ ) and static component (due to transistor OFF-state leakage, proportional to  $V_{DD}$  and also to  $t_{delay}$ ) of energy consumed per operation by a generic combinational logic circuit comprising a cascade of logic gates [10]:

$$E_{total} = \alpha L_d f C V_{DD}^2 + L_d f I_{OFF} V_{DD} t_{delay}$$

(1.1)

$$t_{delay} = L_d f C V_{DD} / (2I_{ON}) \tag{1.2}$$

where  $\alpha$  is the activity factor,  $L_d$  is logic depth, f is fanout, C is capacitance per logic stage, and  $t_{delay}$  is the time required to complete the logic operation.

As the time required to complete the digital operation increases (or, equivalently, circuit operating speed decreases), the energy that is wasted due to  $I_{OFF}$  increases, eventually to the point of making further reduction in  $V_{DD}$  counterproductive in terms of energy efficiency. This point corresponds to  $V_{DD} = V_{T}$ .

**Fig. 1.4** Conceptual illustrations of (a) MOSFET transfer characteristic (for different values of  $V_{DD}$  with  $V_T$  adjusted to achieve the same ON-state drive current,  $I_{ON}$ ) and (b) normalized energy per digital CMOS operation, showing how the total energy consumed per operation has a minimum due to transistor leakage current ( $I_{OFF}$ ) [10].

In order to reduce the minimum energy per operation (*i.e.*, to improve energy efficiency),  $V_{\rm T}$  must be reduced without increasing  $I_{\rm OFF}$ . This means that the steepness of the transistor transfer characteristic (**Fig. 1.4(a**)) in the region where the gate voltage is smaller than the threshold voltage, *i.e.*, the "subthreshold swing" (SS) must be steeper. SS for a MOSFET is fundamentally limited to be no smaller than  $\left(\frac{kT}{q}\right)(\ln 10)$ , which is approximately 60 mV/decade at room temperature, due to the Boltzmann energy distribution of electrons in the Source region of the transistor [7]. For this reason, alternative solid-state switching devices have been investigated [11]. Although alternative transistor designs such as the tunnel field-effect transistor (TFET) [12] and negative capacitance FET (NC-FET) [13] can achieve steeper switching characteristics than the MOSFET, they also can be more sensitive to process-induced variations and device operating conditions, which practically limits their benefit. For example, switching abruptness can be degraded by trap-assisted tunneling due to interfacial defects in a TFET [14] and by polarization screening in a NC-FET [15].

Micro-electro-mechanical (MEM) switches (relays) can achieve immeasurably low *I*<sub>OFF</sub> and abrupt switching behavior across a wide range of temperatures [16]; in principle, they can be operated with much lower voltage than can any type of transistor. (Although they switch more slowly than do transistors, circuit design optimization to minimize the number of mechanical switching delays per function can compensate for this [17].) Thus, MEM switches are of keen interest for digital IC applications for which energy efficiency is paramount. In this dissertation, challenges for achieving reliable millivolt relay operation are investigated. While piezoelectric MEM relays have also been studied for millivolt switching [18], this dissertation focuses on electrostatically actuated relay designs because they can be fabricated with a simpler process flow. Nevertheless, insights for achieving reliable millivolt operation of electrostatic relays should also apply for piezoelectric relays.

#### **1.4 MEM RELAY STRUCTURE AND OPERATION**

**Fig. 1.5(a)** shows a plan-view scanning electron microscope (SEM) image of a 6-terminal (6-T) relay developed for digital logic IC applications [19]. This device comprises a movable gate electrode suspended by four folded-flexure beams (nominal length  $L = 12 \mu m$ ) over a fixed body electrode. As shown in the schematic cross-section of the relay in **Fig. 1.5(b)**, with nominal as-fabricated actuation air gap (g<sub>0</sub>) of 220 nm and nominal as-fabricated contact air gap (g<sub>d</sub>) of 60 nm in the OFF state, narrow strips of W (50 nm thick) are attached to the underside of the gate insulating layer (50 nm thick). These "channels" serve to bridge their respective S/D electrodes when the relay is in the ON state, allowing current ( $I_{DS}$ ) to flow in response to a source-drain voltage difference, as also illustrated in **Fig. 1.5(b)**.

To switch ON the relay, a voltage ( $V_{GB}$ ) is applied between the gate and the body, inducing electrostatic force ( $F_{elec}$ ) that actuates the gate downward (**Fig. 1.6(a)**). Simultaneously, as the structure's displacement from its equilibrium position increases, the spring restoring force  $F_{spring}$  of the deformed suspension beams increases linearly (in the opposite direction). Balancing these opposing forces, one can see that the displacement *g* of the structure rapidly increases with increasing  $V_{GB}$ :

$$g = g_0 - \frac{\varepsilon_0 A V_{GB}^2}{2k_{eff} g^2} \tag{1.3}$$

where  $g_0$  is the initial (as-fabricated) actuation gap,  $k_{\text{eff}}$  is the effective spring constant of the suspension beams,  $\varepsilon_0$  is the vacuum permittivity, and *A* is the effective actuation area. If *g* is reduced by  $\frac{1}{3}g_0$ , the inherent positive feedback within this system causes the structure to become unstable and collapse downward – a phenomenon known as pull-in [20].

**Fig. 1.5** (a) Plan-view scanning electron micrograph (SEM) image of a fabricated 6-terminal MEM relay [26] and (b) Schematic cross-section A-A' in the OFF-state and ON-state. In the ON-state, surface adhesive force exists, resulting in hysteretic switching behavior.

When the magnitude of  $V_{GB}$  is increased to be equal to or greater than that of the pull-in voltage  $(V_{PI})$ , the channels come into physical contact with their respective S/D electrodes, allowing an abrupt increase in current conduction. Subsequently when  $|V_{GB}|$  is reduced below the magnitude of the release voltage  $(V_{RL})$ , the spring restoring force  $(F_{spring})$  of the suspension beams is sufficient to overcome  $F_{elec}$  and the contact adhesive force  $(F_A)$  so that the channels are separated from their respective S/D electrodes and the relay turns off. As explained in [21], high device manufacturing yield can be achieved by designing relays to have relatively stiff structures and large air gaps as fabricated; subsequently they can be made to operate with a small gate voltage  $(V_G)$  swing by applying a body bias voltage  $(V_B)$  (**Fig. 1.6(b**)).

**Fig. 1.6** (a) Illustration of electrostatic actuation and spring restoring forces in the MEM relay and (b) measured *I-V* characteristics for a relay operated with  $V_{DS} = 1$  V and various body bias voltages  $V_B$ . The current is limited to be 10  $\mu$ A to avoid contact welding due to Joule heating.

It should be noted that relays can be designed to be normally off (*i.e.*, actuated into the ON state via  $V_{\text{GB}}$ ) or to be normally on (*i.e.*, actuated into the OFF state via  $V_{\text{GB}}$ ). Furthermore, a normally-off relay can be designed to avoid the pull-in phenomenon by making the as-fabricated contact gap smaller than  $\frac{1}{3}g_0$ , *i.e.*,  $g_0 > 3g_d$ . While previous energy-delay analyses [21-23] indicate that it is energetically favorable for relays to operate in non-pull-in mode, practical challenges (*e.g.*, variations in the fabrication process, non-zero strain gradient in the structural material) make this difficult to achieve in practice [24-26]. As such, the relays utilized in this study were designed for pull-in mode operation. Based on the aforementioned electrostatic and mechanical force-balancing with respect to  $V_{\text{GB}}$ , the formulae for  $V_{\text{PI}}$  and  $V_{\text{RL}}$  of a pull-in mode relay are as follows:

$$V_{PI} = \sqrt{\frac{8k_{eff}g_0{}^3}{27\varepsilon_0 A}}$$

(1.4)

$$V_{RL} = \sqrt{\frac{2(k_{eff}g_d - F_A)(g_0 - g_d)^2}{\varepsilon_0 A}}$$

(1.5)

where  $F_A$  is the contact surface adhesive force. Adhesive force is due primarily to van der Waals forces in the contact dimple regions in the ON state [27].

#### **1.5 RELAY FABRICATION PROCESS**

Details of the MEM relay fabrication process flow are provided in [19]. For the relays studied in this dissertation, the two sets of conducting source and drain (S/D) electrodes are coplanar with the body electrode, formed from the same layer of 50 nm-thick tungsten (W) deposited by sputter deposition (**Fig. 1.7(b**)) over the insulating substrate (**Fig. 1.7(a**)). LPCVD SiO<sub>2</sub> (**Fig. 1.7(c**)) was used as the sacrificial material so that the relays could be released using vapor-phase hydrofluoric acid (HF). Al<sub>2</sub>O<sub>3</sub> deposited by atomic layer deposition (ALD) is used as the body (**Fig. 1.7(e**)) and substrate (**Fig. 1.7(a**)) insulator material because of its resistance to vapor-HF treatment. The structural (gate and suspension beams) material is  $1.75 \mu$ m-thick *in-situ* boron doped polycrystalline silicon-germanium (poly-Si<sub>0.4</sub>Ge<sub>0.6</sub>) deposited by low-pressure chemical vapor deposition (LPCVD) (**Fig. 1.7(f**)). The aforementioned relay dimensions are summarized in Table 1.1.

| Design Parameter                                        | Value                |

|---------------------------------------------------------|----------------------|

| Poly-Si <sub>0.4</sub> Ge <sub>0.6</sub> Thickness, $t$ | 1.75 µm              |

| Beam Width, W                                           | 2 µm                 |

| Beam Length, L                                          | {8, 12} µm           |

| Actuation Area, A                                       | 1236 µm <sup>2</sup> |

| Actuation Gap, $g_0$                                    | 220 nm               |

| Contact Dimple Gap, $g_d$                               | 60 nm                |

| Contact Area, A <sub>CONT</sub>                         | 1 μm <sup>2</sup>    |

TABLE 1.1 Nominal design parameter values for relays used in this study

Fig. 1.7 CoventorWare MEMS+ simulated relay fabrication, showing deposition and patterning of (a) Al<sub>2</sub>O<sub>3</sub> substrate dielectric, (b) W body/source/drain fixed electrodes, (c) sacrificial low temperature oxide and contact dimples, (d) W channel, (e) gate dielectric and structural anchor regions, and (f) Poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> structure (after HF vapor release). [19]

The relays in this work were released using a uEtch Primaxx anhydrous HF vapor process, in order to avoid catastrophic pull-in and stiction due to capillary forces. The release recipe, noted in Table 1.2, consists of 15-17 cycles of stabilization, etching, and pumping; the respective durations (per cycle) of each of these steps is also shown in Table 1.2. Further information regarding this tool and etch process are available in the Marvell Nanofabrication Laboratory equipment manual [28].

| Primaxx HF Vapor release recipe utilized in this study |           |             |           |            |  |  |  |

|--------------------------------------------------------|-----------|-------------|-----------|------------|--|--|--|

|                                                        | N2 (sccm) | EtOH (sccm) | HF (sccm) | Time (min) |  |  |  |

| Stabilize                                              | 1250      | 350         | 0         | 2          |  |  |  |

| Etch                                                   | 1250      | 350         | 310       | 5          |  |  |  |

| Pump                                                   | 0         | 0           | 0         | 0.5        |  |  |  |

|                                                        | TABLE 1.2. |  |              |  |  |  |

|--------------------------------------------------------|------------|--|--------------|--|--|--|

| Primaxx HF Vapor release recipe utilized in this study |            |  |              |  |  |  |

|                                                        |            |  | <b>T</b> • ( |  |  |  |

In this work, MEM relays were electrically characterized using a Lakeshore TTPX cryogenic vacuum probe station at ~1.5  $\mu$ Torr. Prior to collecting data, a native-oxide breakdown process was performed by applying 100 voltage pulses (~5 V, f = 10 kHz) between the source and drain electrodes with the relay in the ON-state, to achieve a reasonably low (less than 1 k $\Omega$ ) initial ON-state resistance [10].

#### **1.6 DISSERTATION OBJECTIVES**

This dissertation discusses approaches and challenges for realizing reliable millivolt MEM relay operation for energy-efficient computing. The hysteresis voltage caused by surface adhesive force at the contact dimples during operation is the primary bottleneck for  $V_{DD}$  scaling for relay-based ICs, therefore possible methods to resolving this issue are investigated.

In chapter 2, post-fabrication treatment of the contacting electrode surfaces with a selfassembled molecular (SAM) anti-stiction coating is demonstrated to effectively reduce surface adhesive force  $F_A$ . This process is shown to enable stable sub-50 mV operation.

In chapter 3, the issue of variability in relay performance parameters over many switching cycles and from device to device is systematically studied with respect to operating conditions and contact treatment. SAM coating is found to improve switching stability for a single device and to reduce variation in hysteresis voltage from device to device.

In chapter 4, the effects of contacting electrode design and body-biased operation on relay ONstate resistance ( $R_{ON}$ ) are investigated. A direct source/drain contact design provides for lowest and least variable  $R_{ON}$ . Ultra-low-voltage relay operation facilitated by body-biasing results in lower contact velocity, which mitigates the need for a wear-resistant contacting electrode material while necessitating a contacting electrode material that is not susceptible to oxidation.

Chapter 5 discusses key findings of this work and suggests possible directions of future research.

#### **1.7 REFERENCES**

- [1] "Computers on board the Apollo spacecraft," *Computers in Space Flight: the NASA Experience*, NASA, https://history.nasa.gov/computers/Ch2-5.html

- [2] "MIDI is born 1980-1983," *MIDI History*, MIDI Association. https://www.midi.org/articles/midi-history-chapter-6-midi-is-born-1980-1983

- [3] From concept to cosmos: How Jack Kilby's integrated circuit transformed the electronics industry, Texas Instruments, 2019. https://news.ti.com/blog/2019/09/17/from-concept-to-cosmos-how-jack-kilbys-integrated-circuit-transformed-electronics-industry

- [4] R.C. Jaeger, Introduction to Microelectronic Fabrication, 2<sup>nd</sup> Ed. Prentice-Hall, Inc. 2002.

- [5] G.E. Moore, "Cramming more components onto integrated circuits," *Electronics*, vol. 38, no. 8, 1965

- [6] R.F. Pierret, Semiconductor Device Fundamentals, Addison-Wesley Publishing Co., 1996.

- [7] Y. Taur and T. H. Ning, *Fundamentals of Modern VLSI Devices*, 2<sup>nd</sup> Ed., Cambridge University Press, 2009

- [8] B.J. LaMeres, Introduction to Logic Circuit and Logic Design with Verilog. 1<sup>st</sup> Ed. Springer Nature, 2017.

- [9] R.H. Dennard, F.H. Gaensslen, H.-N. Yu, V.L. Rideout, E. Bassous, A.R. Leblanc, "Design of ion-implanted MOSFETs with very small physical dimensions," *IEEE Journal of Solid-State Circuits*, Vol. 9, 1974

- [10] B. Calhoun, A. Wang, and A. Chandrakasan, "Modeling and sizing for minimum energy operation in subthreshold circuits," *IEEE Journal of Solid-State Circuits*, Vol. 40, No. 9, pp. 1778-1786, 2005.

- [11] A.M. Ionescu, "Energy efficient computing and sensing in the Zettabyte era: from silicon to the cloud,"

- [12] A.M. Ionescu and H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches," *Nature*, Vol. 479, pp. 329-337, 2011.

- [13] S. Salahuddin and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," ACS Nano Letters, Vol. 8, pp. 405-410, 2008

- [14] R. N. Sajjad, W. Chern, J. L. Hoyt, and D. A. Antoniadis, "Trap assisted tunneling and its effect on subthreshold swing of tunnel field effect transistors," in *Cond-Mat.Mes-Hall*, Mar. 2016.

- [15] K. Ng, S. J. Hillenius, and A. Gruverman, "Transient nature of negative capacitance in ferroelectric field-effect transistors," Solid State Communications, Vol. 265, pp. 12-14, 2017.

- [16] H. Kam, V. Pott, R. Nathanael, J. Jeon, E. Alon, and T. J. King Liu, "Design and reliability of a micro-relay technology for zero-standby-power digital logic applications," *IEEE IEDM Tech. Dig.*, pp. 809-811, 2009.

- [17] F. Chen, H. Kam, D. Markovic, T. J. King Liu, V. Stojanovic, E. Alon, "Integrated circuit design with NEM relays," *Proc. IEEE/ACM ICCAD*, pp. 750-757, 2008.

- [18] U. Zahloul and G. Piazza, "10-25 nm piezoelectric nano-actuators and NEMS switches for millivolt computational logic," Sub-1-volt piezoelectric nanoelectromechanical relays with millivolt switching capability," *IEEE 26<sup>th</sup> Int'l. Conf. MEMS*, 2013

- [19] R. Nathanael *et al.*, "Multi-input/multi-output relay design for more compact and versatile implementation of digital logic with zero leakage," *Proceedings of Technical Program of 2012 VLSI Technology, System and Application*.

- [20] H. Nathanson *et al.*, "The resonant gate transistor," *IEEE Trans. on Elec. Devices*, vol. ed-14 No. 3, 1967.

- [21] C. Qian, A. Peschot, D. J. Connelly, and T. J. King Liu, "Energy-delay performance optimization of NEM logic relay," *IEEE IEDM Tech. Dig.*, pp. 475-478, 2015.

- [22] C. Qian *et al.*, "Effect of body biasing on the energy-delay performance of logic relays," *IEEE Electro Device Letters*, 2015.

- [23] C. Qian, "Electro-mechanical devices for ultra-low-power electronics," Ph.D. dissertation, University of California, Berkeley, 2017.

- [24] C. Low, "Characterization of polycrystalline silicon-germanium film deposition for modularly integrated MEMS applications," *Proc. Jour. of MEMS*, Vol. 16, No. 1, Feb. 2007.

- [25] C. Low, "Novel processes for modular integration of silicon-germanium MEMS with CMOS electronics," Ph.D. dissertation, University of California, Berkeley, 2007.

- [26] B. Osoba et al., "Variability study for low-voltage microelectromechanical relay operation,"

IEEE Trans. on Elec. Devices, Feb. 2018

- [27] J. Yaung, L. Hutin, J. Jeon, and T.-J. King Liu, "Adhesive force characterization for MEM logic relays with sub-micron contacting regions," *IEEE JMEMS*, Vol. 23, No. 1, 2014

- [28] "uEtch HF Vapor Release System," *Equipment Manual*, Marvell Nanofabrication Laboratory, UC Berkeley. https://nanolab.berkeley.edu/public/manuals/equipment\_manual.shtml

## **CHAPTER 2:**

## Sub-50 milli-volt NEM Relay Operation Enabled by Self-Assembled Molecular Coating

#### **2.1 INTRODUCTION**

Due to the aforementioned limitations of conventional semiconductor transistors – particularly the Boltzmann distribution of electrons that is exponentially dependent on the thermal voltage  $\frac{kT}{q}$ , which limits the subtreshold swing (SS) of transistors to be no steeper than approximately 60 mV/dec at room temperature – nanometer-scale electro-mechanical (NEM) switches (relays) are of keen interest for ultra-low-power digital logic integrated circuit (IC) applications [1]. This is because a mechanical switch can achieve the ideal property of zero OFF-state leakage current, in turn providing for zero static power consumption [1][2]. To minimize active power consumption, the operating voltage ( $V_{DD}$ ) of a digital IC should be minimized.

$V_{\text{DD}}$  scaling for a NEM relay is limited by the switching hysteresis voltage that is caused by contact stiction [3]. When a relay is in the ON-state, surface adhesive force exists in the contact dimple regions, so that the electrostatic force required to maintain the relay in the ON-state is smaller than the electrostatic force required to actuate the relay into the ON-state. Thus, the turn-off voltage is smaller than the turn-on voltage, resulting in the aforementioned hysteresis voltage. For this reason, it is of paramount importance to investigate how to mitigate – and ultimately eliminate – surface adhesion in the relay contact regions. In this chapter, reduction in contact adhesive force via the application of an anti-stiction molecular coating is investigated.

#### **2.2 BODY BIAS EFFECT FOR VERSATILE PASS GATE LOGIC**

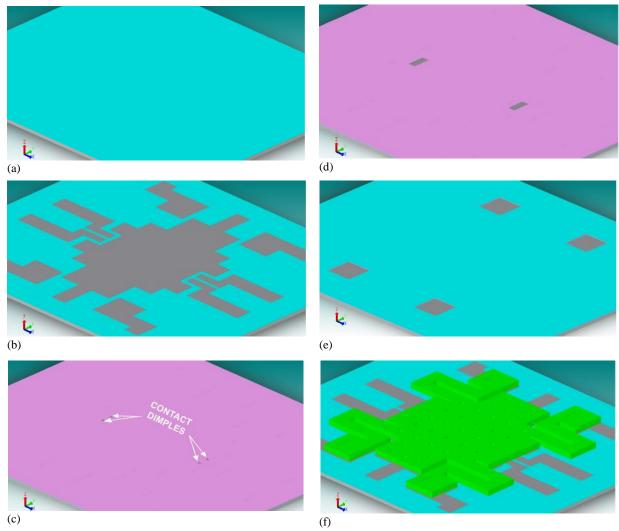

The 6T relays [4] in this work were tested at room temperature using a vacuum probe station (1.5 µTorr) to minimize oxidation of the W electrode surfaces which is undesirable because WOx is electrically insulating, resulting in high ON-state resistance [5]. Measured current-vs.-voltage (*I*-V) characteristics for forward and reverse sweeps of the gate voltage ( $V_G$ ) are shown in **Fig. 2.1(a**). By applying a negative body voltage ( $V_B$ ), the positive value of  $V_G$  that is required to turn ON the relay ( $V_{DD}$ ) can be decreased to  $V_{PI} - |V_B|$ . The maximum value of  $|V_B|$  that can be applied (while ensuring that the relay is OFF at  $V_G = 0$  V) is  $V_{RL}$ , so that the minimum  $V_{DD}$  is the hysteresis voltage  $V_H \equiv V_{PI} - V_{RL}$ . Sub-200 mV operation with negative body biasing is demonstrated in **Fig. 2.1(b**). In a digital logic circuit, the switching devices are used not only to pass low voltage (0 V) as in a "pull-down" device but also to pass high voltage ( $V_{DD}$ ) as in a "pull-down" device, it must switch ON with *decreasing*  $V_G$ . In this case, to achieve ultra-low-voltage operation, a positive body bias should be used as demonstrated in **Fig. 2.1(c**).

**Fig. 2.1** (a) Measured relay I-V characteristics showing the effect of body-biasing, which is utilized to achieve low-voltage operation for (b) pull-down (N-relay) operation and (c) pull-up (P-relay) operation.  $I_{DS}$  is artificially limited to 100 nA in order to prevent Joule heating and subsequent W welding at the relay contacts.

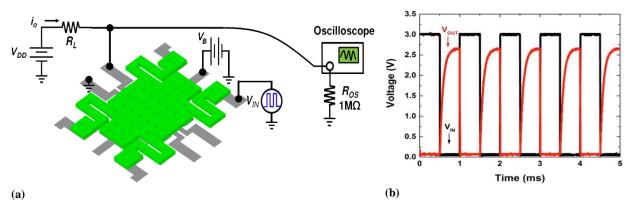

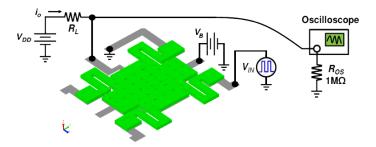

**Fig. 2.2(a)** illustrates an inverter circuit in which the body-biased relay is used as a pull-down device, and **Fig. 2.2(b)** shows measured input and output voltage waveforms for this circuit.

**Fig. 2.2.** (a) Relay inverter circuit and (b) measured voltage waveforms for inverter circuit in which a non-coated relay is configured as a pull-down device.  $R_L = 123 \text{ k}\Omega$ ,  $V_{DD} = V_{IN,max} = 3 \text{ V}$ ,  $V_B = -11.75 \text{ V}$ , and f = 1 kHz. (*v*<sub>OUT</sub> does not reach  $V_{DD}$  due to oscilloscope internal resistance  $R_{osc} = 1 \text{ M}\Omega$ .)

This inverter circuit is used to extract the value of relay ON-state resistance (R<sub>ON</sub>) via the voltage divider formula:

$$V_{OUT} \cong \left(\frac{R_{ON}}{R_{ON} + R_L}\right) V_{DD} \tag{2.1}$$

$$R_{ON} \cong \left(\frac{V_{OUT}}{V_{DD} - V_{OUT}}\right) R_L \tag{2.2}$$

Because the oscilloscope internal resistance ( $R_{osc} = 1 M\Omega$ ) is relatively large in comparison to  $R_{ON}$ , it can be considered negligible in the voltage division estimation. However, the load resistance  $R_L$  is significant compared to  $R_{osc}$  so that it cannot be ignored:

$$V_{OUT} = \begin{cases} \left(\frac{R_{osc}}{R_L + R_{osc}}\right) V_{DD} & , for V_{IN} = 0 V \end{cases}$$

(2.3)

$$\left[ \frac{R_{ON}R_{osc}}{R_{ON}R_{osc} + (R_{ON} + R_{osc})R_L} \right] V_{DD} , for V_{IN} = V_{DD}$$

(2.4)

The value of  $R_L$  affects the current flowing through the relay contacts. As such, this parameter can be tuned in order to obtain optimal circuit performance. A low value of  $R_L$  facilitates *in situ* electrical breakdown of native oxide formed on the surfaces of the contacting asperities during ON-state conduction, and reduces the effect of  $R_{osc}$  when the relay is in the OFF state. However if  $R_L$  is too low, excessive Joule heating could resulting in micro-welding, causing the relay to be stuck in the ON state.  $R_L = 123 \text{ k}\Omega$  was chosen for the tests conducted in this chapter.

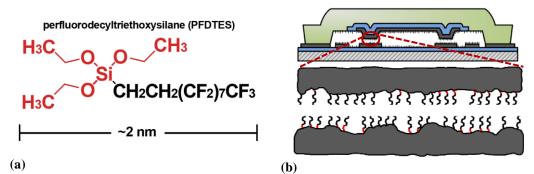

#### 2.3 SELF-ASSEMBLED MONOLAYER (SAM) MOLECULAR COATING

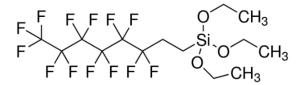

Hydrophobic 1H,1H,2H,2H-Perfluorodecyltriethoxysilane (PFDTES, **Fig. 2.3(a)**) was selected as the relay coating material in this work. The silane functional group of this molecule allows its assembly onto oxidized surfaces [14] and hence facilitates self-assembly onto native  $WO_x$  on the contact surfaces (**Fig. 2.3(b**)) while the fluorinated backbone lowers the surface energy and reduces adhesive force [17-19] as shown quantitatively in **Fig. 2.7(c)**.

**Fig. 2.3** (a) Molecular structure of PFDTES and (b) qualitative illustration of PFDTES coating, which adheres well to W surfaces due to its silane end-group.

Utilizing Atomic Force Microscopy (AFM) and the Derjaguin, Muller and Toporov (DMT) model for an adhesive contact [14, 15, 19]

$$F_{ADH} = W_{ADH} \cdot 2\pi R_{tip} \tag{2.5}$$

where  $W_{ADH}$  is the measured work of adhesion with respect to the normal plane and  $R_{tip}$  is the radius of the AFM tip, the effect of PFDTES coating was first characterized.

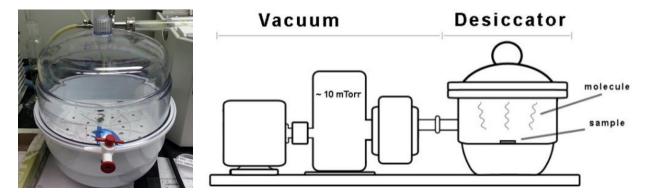

In this work, PFDTES was deposited using a vapor-phase process as shown in **Fig. 2.4**. A few drops of the liquid-phase molecules were placed in close proximity to the samples to be coated, inside a vacuum desiccator where the pressure was reduced to vaporize the molecules. The samples were left in this environment for  $\sim$ 24 hours to ensure full coverage.

**Fig. 2.4** (a) photograph and (b) qualitative illustration of the vapor phase molecular coating process, during which the molecules self-assemble onto the sample surfaces.

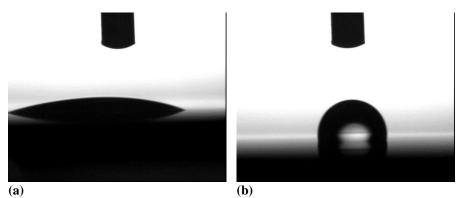

Contact angle measurements were conducted on samples before and after in order to confirm that the silane functional group assembled effectively. Because fluorinated molecules are hydrophobic, a drop of water on a coated surface results in a higher contact angle than a non-coated surface, as shown in **Fig. 2.5**. As such, self-assembly of PFDTES on W electrode material was confirmed.

**Fig. 2.5** Contact-angle measurements (a)  $30^{\circ}$  pre-coating and (b)  $97^{\circ}$  post-coating indicate successful deposition of the fluorinated molecule.

In addition, X-ray Photoelectron Spectroscopy (XPS) measurements confirm successful coating of W with PFDTES, as indicated in **Fig. 2.6**.

**Fig. 2.6** (a) Characteristic peaks from XPS measurements and (b) the fluorine peak, indicating the successful self-assembly of PFDTES onto the W surface.

To provide reference data, a silicon-dioxide AFM tip (**Fig. 2.7(a**)) was brought into and out of contact with the surface of an oxidized silicon wafer, 10 times at each of 5 different locations on the surface for a total of 50 measurements of adhesive force [14 - 16]. This test was then conducted for a PFDTES-coated AFM tip to PFDTES-coated wafer (**Fig. 2.7(b**)). The results of these tests as shown in **Fig. 2.7(c**) indicate that PFDTES effectively decreases surface adhesive force.

Fig. 2.7 (a) SEM image of  $SiO_2$  AFM tip, (b) illustration of Atomic Force Microscope (AFM) adhesion force measurement and (c) empirical measurements indicating that surface adhesion is decreased with PFDTES coating.

#### 2.4 EFFECTS OF MOLECULAR COATING ON RELAY SWITCHING CHARACTERISTICS

After initial testing, relays were coated with PFDTES using the vapor-phase growth process and then retested. For 6 relays of identical design,  $I_{DS}$ - $V_G$  characteristics were measured multiple times (*i.e.* with multiple forward and reverse  $V_G$  sweeps) to obtain the average value of  $V_H$ . The results shown in **Fig. 2.8(a)** indicate that the PFDTES coating significantly reduces  $V_H$ , by 41% on average both for zero body bias and non-zero body bias. It also reduces  $V_H$  variation from one device to another, from 8.3 mill-volt to 7.4 milli-volt (standard deviation) for body-biased relays. From **Fig. 2.8(b)** it is evident that relays operated with body biasing generally have lower  $V_{\rm H}$  and variability due to lower contact velocity; molecular coating is as effective for reducing  $V_{\rm H}$  in this case.

**Fig. 2.8** Summary of measured data, pre- and post-PFDTES coating, showing decrease in switching hysteresis voltage  $V_H$  for (a) zero body bias, (b)  $V_B = -9$  V.

**Fig. 2.9** shows that the PFDTES does not substantially change the relay ON-state resistance ( $R_{ON}$ ). This is likely because any PFDTES at the small number of contacting asperities (cf. Fig. 2.3(b)) is electrically broken down or ablated due to local Joule heating.

**Fig. 2.10(a)** shows measured  $I_{DS}$ -V<sub>G</sub> characteristics for a coated relay with body biasing. Note that although  $V_{\rm H}$  (measured at a current level of 10 nA) is reduced by the PFDTES coating, the transitions between OFF and ON states are less abrupt, *i.e.* the subthreshold swing is increased to ~15 mV/dec. Therefore, a larger gate voltage swing is needed to fully switch the relay ON. However, if a smaller ON/OFF current ratio (*e.g.* 10<sup>4</sup>) is sufficient, then the coated relay can be operated

**Fig. 2.9** Measured R<sub>ON</sub> data for L = 15  $\mu$ m relays operated at V<sub>B</sub> = -9 V and V<sub>IN</sub> = V<sub>DD</sub> = 3 V. These data show no significant increase in relay ON-state resistance with PFDTES coating. Notably, the V<sub>IN</sub> value was chosen to account for process-induced variation in V<sub>PI</sub> for the given set of relays.

with a smaller gate voltage swing. This is in contrast to an abruptly switching relay, which cannot be operated with a gate voltage swing that is smaller than  $V_{\rm H}$ . By applying a body bias to bring the molecular coatings on the S/D and channel electrodes into contact, a metal-molecule-metal "squitch" [17][18] is effectively achieved. The molecular material can be engineered for more abrupt switching behavior, through chemical synthesis techniques, to modify the functional end group and/or the spacer backbone. For example, a lower Young's modulus molecular layer can be achieved by changing the spacer group.

**Fig. 2.10** (a) Measured L = 8  $\mu$ m relay *I-V* characteristics showing that PFDTES coating can provide for smaller V<sub>H</sub>. (b) Measured voltage waveforms for inverter circuit in which a relay coated with PFDTES is configured as a pull-down device. R<sub>L</sub> = 123 kΩ, R<sub>osc</sub> = 1 MΩ, V<sub>DD</sub> = V<sub>IN</sub> = 200 mV, V<sub>Bn</sub> = -12.34 V, and *f* = 1 kHz.

**Fig. 2.11** shows an example of shorter alkane molecule with Young's modulus in the GPa regime compared to longer chain poly(ethylene glycol) which exhibits a Young's modulus as low as a few MPa [17-19].

**Fig. 2.11** Through chemical synthesis, molecules can be designed with particular head, terminal and spacer groups to exhibit desired surface selectivity for device functionalization, surface adhesive properties, and electromechanical performance. Here, an alkane molecule with Young's modulus in the GPa regime and poly(ethylene glycol) with Young's modulus in the MPa regime are shown as examples.

Fig. 2.12(b) shows measured voltage waveforms for an inverter circuit in which the body-biased coated relay is used as a pull-down device (cf. Fig. 2.2(a)). As the input voltage ( $V_{IN}$ ) amplitude decreases, the relay ON state current is reduced so that it cannot fully discharge the output node

and hence the minimum output voltage ( $V_{OUT,MIN}$ ) rises. Fig. 2.12 shows voltage waveforms for relay-based inverter circuits, demonstrating sub-50 milli-volt operation ( $V_{IN} = V_{DD}$ ).

**Fig. 2.12** Measured voltage waveforms demonstrating sub-50 mV relay-based inverter circuit operation: (a) N-relay configuration with  $V_{Bn} = -14.96$  V, and (b) P-relay configuration with  $V_{Bp} = 14.1$  V.  $R_L = 123$  k $\Omega$ ,  $R_{osc} = 1$  M $\Omega$ ,  $V_{DD} = V_{IN} = 40$  mV, and f = 1 kHz.

#### **2.5 DISCUSSION**

The experimental results show that PFDTES is effective for reducing surface adhesion and hence V<sub>H</sub>, thereby enabling reliable sub-50 milli-volt relay operation for both pull-up and pulldown operation (cf. **Fig. 2.12**). This comes at the tradeoff of reduced switching abruptness, however, resulting in degraded ON/OFF ratio for the same (small) gate-voltage swing. Effectively,  $R_{ON}$  for low- $V_{DD}$  operation is increased, resulting in significantly degraded output voltage swing. This issue is exacerbated by the softer contacting force for body-biased operation [6-8]. For  $V_{DD} = V_{IN} = 40$  mV, the pull-down and pull-up relays have effective  $R_{ON_{N-relay}} \approx 369$  k $\Omega$  and  $R_{ON_{P-relay}} \approx 205$  k $\Omega$ , respectively.

Perfluorooctyltriethoxysilane (PFOTES)

Fig. 2.13 Molecular structure of PFOTES

Alternative fluorinated molecules, such as perfluorooctyltriethoxysilane (PFOTES, **Fig. 2.13**), could be used as anti-stiction coating material [11]. The quantity *n* of difluoromethane (CF<sub>2</sub>) within

the larger fluorinated chain affects the overall length of the molecule. Measurements of PFOTEScoated relays indicate that the shorter molecule (n = 5) results in lower surface adhesive force (**Fig. 2.14 (a)**) and smaller  $V_{\rm H}$  (**Fig. 2.14 (b)**) in comparison with PFDTES.

**Fig. 2.14** (a) AFM-based measurements of coated contact adhesive force and (b) measured relay *I-V* characteristics, comparing the effects of PFOTES and PFDTES anti-stiction coatings.

#### 2.6 SUMMARY

Reduction of the hysteresis voltage  $V_{\rm H}$  is key to minimizing the gate voltage swing of a relay and thereby the active power consumption of relay-based digital ICs. Self-assembled monolayer PFDTES coating is found to be effective for reducing  $V_{\rm H}$  (by more than 41%) without significantly affecting ON-state resistance, enabling lower voltage operation. Further work is needed to optimize the molecular coating material to achieve more abrupt switching behavior, to fully realize the benefit of lower  $V_{\rm H}$  for lower the operating voltage and hence for improving MEM relay operating energy efficiency.

#### **2.7 REFERENCES**

- [1] F. Chen et al., "Integrated circuit design with NEM relays," 2008 IEEE/ACM Int'l Conf. Computer-Aided Design, pp. 750-757, 2008.

- [2] A. Peschot *et al.*, "Nanoelectromechanical switches for low-power digital computing," *Micromachines*, vol. 6, no. 8, pp. 1046-1065, 2015.

- [3] C. Pawashe *et al.*, "Scaling limits of electrostatic nanorelays," *IEEE Trans. Elec. Dev.*, vol. 60, pp. 2936-2942, 2013.

- [4] R. Nathanael *et al.*, "Multi-input/multi-output relay design for more compact and versatile implementation of digital logic with zero leakage," *Proceedings of Technical Program of 2012 VLSI Technology, System and Application*.

- [5] Y. Chen et al., "Reliability of MEM relays for zero leakage logic," Proc. SPIE 8614, Reliability, Packaging, Testing, and Characterization of MOEMS/MEMS and Nanodevices XII, p. 861404, 2013.

- [6] C. Qian *et al.*, "Effect of body biasing on the energy-delay performance of logic relays," *IEEE Electro Device Letters*, 2015.

- [7] C. Qian *et al.*, "Energy-delay performance optimization of NEM logic relay," 2015 IEEE International Electron Devices Meeting, paper 18.1.

- [8] C. Qian, "Electro-mechanical devices for ultra-low-power electronics," Ph.D. dissertation, University of California, Berkeley, 2017.

- [9] C. Low, "Characterization of polycrystalline silicon-germanium film deposition for modularly integrated MEMS applications," *Proc. Jour. of MEMS*, Vol. 16, No. 1, Feb. 2007.

- [10] C. Low, "Novel processes for modular integration of silicon-germanium MEMS with CMOS electronics," Ph.D. dissertation, University of California, Berkeley, 2007.

- [11] B. Osoba *et al.*, "Variability study for low-voltage microelectromechanical relay operation," *IEEE Trans. on Elec. Devices*, Feb. 2018

- [12] J. Yaung, "NEM relay scaling for ultra-low power digital logic," Ph.D. dissertation, University of California, Berkeley, 2014.

- [13] R. Maboudian *et al.*, "Self-assembled monolayers as anti-stiction coatings for MEMS: characteristics and recent developments," *Sensors and Actuators* 82, pp. 219 223, 2000.

- [14] G. Binning et al., "Atomic Force Microscopy," Phy. Rev. Lett. 56, pp. 930 933, 1986.

- [15] F. Leite *et al.*, "Theoretical models for surface forces and adhesion and their measurement using atomic force microscopy," *Int. J. Mol. Sci.*, 2012.

- [16] K. Cooper *et al.*, "Substrate morphology and particle adhesion in reacting systems," *JCIS* 228, pp. 213-219, 2000.

- [17] F. Niroui et al., "Nanoelectromechanical tunneling switches based on self-assembled molecular layers," 2014 IEEE 27th International Conference on Micro Electro Mechanical Systems, pp. 1103-1106.

- [18] F. Niroui *et al.*, "Tunneling nanoelectromechanical switches based on compressible molecular thin-films," *ACS Nano*, vol. 9, no. 8, pp. 7886-7894, 2015.

- [19] F. W. DelRio *et al.*, "Elastic and adhesive properties of alkanethiol self assembled monolayers on gold," *Appl. Phys. Lett.*, vol. 94, p. 131909, 2009.

## CHAPTER 3:

## Variability Study for Low-Voltage Micro-Electro-Mechanical Relay Operation

#### **3.1 INTRODUCTION**

In order to overcome the inherent switching energy efficiency limitation of conventional transistors [1], there have been many efforts to develop alternative solid-state switch designs that can achieve more ideal (*i.e.*, abrupt) switching characteristics [2-6]. Micro/nano-electro-mechanical (M/NEM) switches are a promising alternative to conventional transistors for applications in which energy efficiency is paramount, primarily because the former can achieve immeasurably low OFF-state leakage current ( $I_{OFF}$ ) and abrupt switching behavior across a wide range of temperatures [7]. In principle, NEM relays can be operated with much lower voltage than can any type of transistor. (Although they switch more slowly than do transistors, circuit design optimization to minimize the number of mechanical switching delays per function can compensate for this [8].) A body-biased MEM relay design was previously developed for digital IC applications [9] and shown to provide for improved energy efficiency [10].

In Chapter 2, an anti-stiction self-assembled monolayer (SAM) coating was demonstrated to reduce the relay switching hysteresis voltage ( $V_{\rm H} \equiv V_{\rm PI} - V_{\rm RL}$ ) so that the relay can be switched ON/OFF with sub-50 milli-volt gate voltage ( $V_{\rm G}$ ) swing; therefore, in principle, the operating voltage ( $V_{\rm DD}$ ) of a relay-based integrated circuit (IC) can be less than 50 mV. However, due to variations in turn-on/pull-in voltage ( $V_{\rm PI}$ ) and release voltage ( $V_{\rm RL}$ ) values from device to device,  $V_{\rm DD}$  must include voltage margin for these variations. In this chapter, variability in relay switching voltages and the impact of SAM coating on variability are investigated.

#### **3.2 RELAY SWITCHING VOLTAGE VARIABILITY**

Switching voltage variations practically limit the extent to which  $V_{DD}$  can be reduced, because in practice a single negative value of  $V_B$  should be used for all of the "pull-down" relays within a circuit block, while another single positive value of  $V_B$  should be used for all of the "pull-up" relays within a circuit block. In order for a relay-based IC to operate properly, then, the magnitude of the applied body bias voltage ( $|V_B|$ ) cannot be larger than the minimum value of release voltage ( $V_{RL low}$ ), to guarantee that each relay turns OFF properly; also,  $V_{DD}$  must be at least equal to the maximum value of  $V_{PI}$  ( $V_{PI high}$ ) minus  $V_{RLlow}$ , to guarantee that each relay turns ON properly. Therefore,  $V_{DD}$  scaling is constrained by the maximum and minimum values of  $V_{PI}$  and  $V_{RL}$ , respectively:

$$V_{DD} \ge V_{PI_{high}} + V_B \tag{3.1}$$

$$|V_B| \le V_{RL_{low}} \tag{3.2}$$

#### 3.2.1. Body-biased switching voltage stability

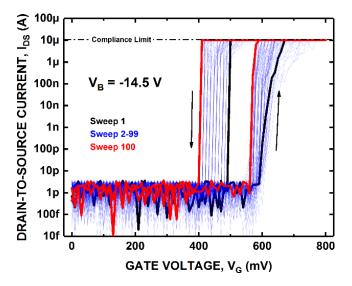

Process-induced variations in relay dimensions, as well as random variations in  $F_A$  from device to device and over the device operating lifetime, result in switching voltage variations. Fig. 3.1 shows measured switching voltages for 100 sequential DC measurements made on a single bodybiased relay.

**Fig. 3.1** Stable low voltage operation is enabled by body-biasing, with less than 100 mV variation in  $V_{PI}$  and  $V_{RL}$  over 100 gate voltage sweeps. The ON-state current was artificially limited to 10  $\mu$ A, to prevent excessive Joule heating resulting in micro-welding. L = 8  $\mu$ m.

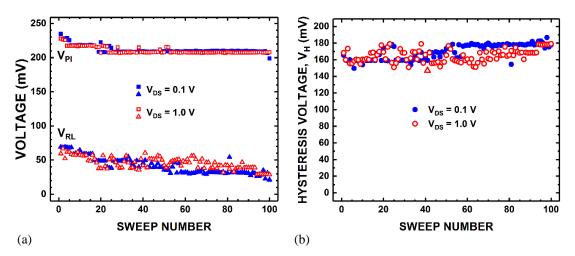

The plotted data in **Fig. 3.2** show that  $V_{PI}$  is very stable after the first ~20 sweeps, while  $V_{H}$  increases slightly (by ~20 mV) over time, possibly due to initial contact wear-in, stabilizing after ~50 sweeps. Weak dependence on the drain-to-source voltage ( $V_{DS}$ ) is seen. The relays in this work were tested at room temperature under vacuum (~1.5 µTorr).

**Fig. 3.2** Evolution of (a) relay switching voltages and (b) hysteresis voltage for a body-biased relay operated with various values of drain-to-source voltage  $V_{DS}$ . L = 8  $\mu$ m. The current compliance limit was set to 10  $\mu$ A.

**Fig. 3.3** shows that body biasing is generally advantageous for improving switching voltage stability (i.e., reducing variability in  $V_{\text{PI}}$  and  $V_{\text{H}}$ ). This is likely due to the reduction in impact velocity enabled by increased  $|V_{\text{B}}|$  [10].

**Fig. 3.3** Measured variability in (a)  $V_{PI}$  and (b)  $V_{H}$  for multiple relays operated at  $V_{DS} = 1$  V with  $V_B = 0$  V or  $V_B = -14.5$  V. Body biasing generally decreases variability in  $V_{PI}$  and  $V_H$ . L = 8 µm. The current compliance limit was set to 10 µA.

#### 3.2.2. Process-induced variations

The LPCVD processes used to deposit the sacrificial SiO<sub>2</sub> and structural poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> layers in this work resulted in significant systematic variations across a wafer (*i.e.*, die to die) and random variations from device to device, in the thicknesses of the actuation and contact gaps and the movable structure, as determined using an Olympus LEXT OLS4000 3D confocal laser microscope. Notably, the structural thickness of these relays was 1.6  $\mu$ m, as opposed to the nominal thickness listed in Table 1.1.

**Fig. 3.4(a)** shows how  $V_{\rm PI}$  varies with poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> thickness. Utilizing Eqn. 1.4 and noting that  $k_{eff} \propto t^3$ , the theoretical change in  $V_{\rm PI}$  relative to its nominal value due to a change in poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> thickness *t* and actuation gap *g* thickness is given by the following relationship:

$$V_{PI} = \left(\frac{g * t}{g_0 * t_0}\right)^{3/2} * V_{PI_0}$$

(3.3)

**Fig. 3.4** Measured impact of process-induced variations in Poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> thickness on (a) pull in voltage  $V_{PI}$  (b) actuation gap g and (c) hysteresis voltage  $V_{H}$ . L = 12 µm. The negative correlation between structural layer thickness and actuation gap size is due to reduced out-of-plane deflection for a stiffer structure.

By comparing the measured  $V_{\text{PI}}$  values against the theoretically predicted trend based on Eqn. 3.3, indicated by the solid red line in **Fig. 3.4(a)**, taking into account the negative correlation between structural layer thickness and actuation gap size shown in **Fig. 3.4(b)**, it can be seen that random sources of variation are predominant. (Measured values  $g_0 = 0.35 \,\mu\text{m}$ ,  $t_0 = 1.5 \,\mu\text{m}$ , and  $V_{PI_0} = 11.9 \,\text{V}$  were used to calibrate the theoretical curve.) The systematic variation is relatively small and can be further reduced in a relatively straightforward manner with improved LPCVD process control. **Fig. 3.4(c)** shows that there is significant random variation in  $V_{\text{H}}$ , which depends on local contact properties that vary from device to device.

**Fig. 3.5** Measured switching voltages for multiple relays operated at  $V_{DS} = 1$  V and  $V_B = -14.5$  V. The error bars correspond to switching variation measured for each relay over 100 gate voltage sweeps. L = 8 µm.

Fig. 3.5 shows the variation in switching voltages for relays located side-by-side on a single die, with the same value of  $V_{\rm B}$  that was chosen to guarantee proper IC functionality. Although  $V_{\rm H}$  can be less than 100 mV, random variability limits  $V_{\rm DD}$  to be no less than ~0.9 V for this die. More uniform (device to device) switching voltages are necessary to overcome this issue, to fully realize the benefit of relay technology for ultra-low-voltage integrated circuits.

#### **3.4 EFFECTS OF ANTI-STICTION COATING**

In the previous chapter it was demonstrated that a hydrophobic coating of Perfluorodecyltriethoxysilane (PFDTES) is effective for reducing  $V_{\rm H}$ , but at a tradeoff of increased sub-threshold swing, *i.e.* less abrupt switching behavior [11]. As seen in **Fig. 3.6**, a molecular coating with a shorter perfluoro chain, Perfluorooctyltriethoxysilane (PFOTES), was used in this work to mitigate the aforementioned tradeoff (cf. Sec. 2.5).

**Fig. 3.6** Molecular structure of (a) PFDTES vs. (b) PFOTES, (c) measured *I-V* characteristics for body-biased relays, showing the effects of anti-stiction coatings.  $L = 12 \mu m$ .

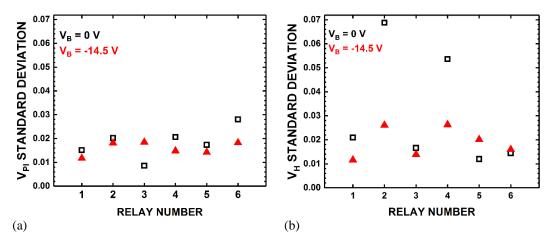

As can be seen from **Fig. 3.6(c)**, a PFOTES-coated relay can be fully switched between ON and OFF states with sub-50 mill-volt  $V_G$  swing. **Fig. 3.7** shows that low  $V_H$  is stably maintained with PFOTES coating over many switching cycles.

**Fig. 3.7** (a) Measured *I-V* characteristics and (b) evolution of measured  $V_{\rm H}$  for PFOTES-coated MEM relay operated over 100 gate voltage sweeps at  $V_{\rm DS} = 1$  V and body-biased conditions. These data indicate significantly decreased value and variability in  $V_{\rm H}$  due to the PFOTES coating. L = 8 µm.

The data in **Fig. 3.8(a)** affirm that relay switching voltage stability is improved with the antistiction coating. **Fig. 3.8(b)** shows that device to device variation in  $V_{\rm H}$  is also significantly improved, indicative of more uniform contact stiction for the coated relays.

**Fig. 3.8** Measured (a) variability in  $V_{PI}$ ,  $V_H$  and (b) switching voltages for multiple PFOTES relays operated at  $V_{DS} = 1 \text{ V}$ ,  $V_B = -16 \text{ V}$ . L = 8  $\mu$ m.

#### **3.5 DISCUSSION**

The results of this study indicate that process-induced random variations in  $V_{PI}$  will practically limit  $V_{DD}$  reduction for relay-based ICs. Because the microstructure of the LPCVD poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> structural film is highly non-uniform [13], out-of-plane deflection due to non-zero strain gradient is significant and varies from device to device, resulting in large random variation in  $V_{PI}$  as seen in **Fig. 3.4**. This issue can be mitigated by using a much thicker (stiffer) poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> film, but at a trade-off of a much larger gate-to-body voltage required to turn on the relay, *i.e.*, larger  $|V_B|$ . Alternatively, a structural film with zero strain gradient could be developed. For instance, multitarget DC magnetron sputtering has been demonstrated to effectively and controllably grow amorphous metal thin films [14, 15].

#### **3.6 SUMMARY**

Variability and stability of relay switching voltages practically limits reductions in operating voltage for relay-based integrated circuits and hence was investigated in this work. Tight control  $(\pm 1\%)$  of the structural layer thickness and the actuation and contact gap thicknesses is necessary to reduce random variability and thereby enable sub-100 milli-volt relay IC operation. In this regard, a structural layer material with low residual stress and an amorphous microstructure may be necessary to minimize random out-of-plane deflection. An optimized anti-stiction coating is effective for reducing hysteresis and random variation thereof, and hence is expected to facilitate the practical implementation of sub-100 milli-volt relay-based circuits.

#### **3.7 REFERENCES**

- B. Calhoun, A. Wang, and A. Chandrakasan, "Modeling and sizing for minimum energy operation in subthreshold circuits," *IEEE Journal of Solid-State Circuits*, Vol. 40, No. 9, pp. 1778-1786, 2005.