### Compact and Efficient Power Electronics System Design for Automotive, Solar, and Aerospace Applications

Derek Chou

#### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-88 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-88.html

May 14, 2021

Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Acknowledgement

I would like to thank my advisor, Professor Robert Pilawa, for his support and guidance through the years. Thank you to the Pilawa group team members for the collaborations and friendships throughout the years. I would also like to thank Profs. Seth Sanders, Duncan Callaway, and Alexandra von Meier for their valuable advice in writing this dissertation. Finally, I would like to thank my family and friends for always staying by me and keeping me motivated through the years.

#### Compact and Efficient Power Electronics System Design for Automotive, Solar, and Aerospace Applications

by

Derek Chou

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Associate Professor Robert C. N. Pilawa-Podgurski, Chair Professor Seth R. Sanders Associate Professor Duncan Callaway

Spring 2021

Compact and Efficient Power Electronics System Design for Automotive, Solar, and Aerospace Applications

Copyright © 2021 by Derek Chou

#### Abstract

#### Compact and Efficient Power Electronics System Design for Automotive, Solar, and Aerospace Applications

by

Derek Chou

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Associate Professor Robert C. N. Pilawa-Podgurski, Chair

In this dissertation, methods of improving overall power electronic system density are developed and explored. Using a Level II single-phase bidirectional electric vehicle charger as a demonstration system, this work focuses on strategies that promote minimization of passive component sizes through the application of different electrical topologies, as well as the mechanical and thermal implications of such applications.

A conventional system design is presented as the baseline for improvement: in a single-phase ac-dc converter system, there exists two major functions that must be performed. First, the input ac current must be shaped to match both the shape and the phase of the input ac voltage, the power factor correction (PFC) function. Second, because the input ac current and voltage multiply and result in a twice-line frequency power pulsation, this pulsation must be managed with an energy buffer. The prototypical conventional system discussed in this work consists of a rectifier followed by a two-switch power converter shaping the input current through a physically-large boost inductor; the power ripple is then buffered by a physically-large electrolytic capacitor bank. Running these functions in reverse provides inverter (dc-ac) functionality, where the rectifier and boost PFC stage is now acting as a rectified sine-wave generator and unfolder inverter stage.

This work proposes the use of the flying-capacitor multilevel (FCML) topology in order to greatly shrink the boost inductor, which is then integrated with the series-stacked buffer (SSB) topology to greatly shrink the buffer capacitors. The FCML topology is verified at Level II charging power levels. In order to achieve the required power level, an interleaved 6-level FCML is designed and built. Mechanical design and thermal management implications are considered in the construction of the FCML prototype, which achieved Level II power levels with a custom-designed air-cooled heatsink prototype. The SSB topology is then added to the system in a full redesign that integrates all of the components into a package with high utilization of 3-D space. Again, the Level II power level necessitated a parallel design,

which we prefer to interleave, so the resultant bidirectional electric vehicle charger design has two FCML stages in parallel as the boost PFC stage as well as two SSB stages in parallel as the energy buffer stage. The system is then verified operational in both the PFC and the inverter modes. In the full system prototype, a power level of 6.1 kW is achieved, running in the dc-ac mode from 400  $V_{dc}$  to 240  $V_{ac}$  and a system density of 201 W/in<sup>3</sup> (12.3 W/cm<sup>3</sup>) is reported, which includes the cold plate in a liquid-cooled thermal management system. All of the major power boards in this system are designed to be constructed with commercial parts and conventional manufacturing techniques. Therefore, they are able to be contractmanufactured, yet still achieve excellent power density figures. Finally, an exploration of the boundary condition of converter start-up is performed. The FCML topology can be heavily optimized to utilize switches with ratings lower than the dc bus voltage. This performs well at periodic steady-state, but requires extra circuitry to insulate the switches from excess voltage at start-up. An ac-side start-up technique is implemented and tested, demonstrating a start from a completely discharged state with the converter running in the ac-dc mode.

The hardware prototypes presented herein boast excellent power density figures owing mainly to the heavy degree of mechanical and thermal integration. Both air cooling and liquid cooling solutions are explored, as each have their merits in different electric power systems. Operating at Level II charging power levels, the prototypes in this work did not heat up beyond reasonable commercial part temperature limits. Overall, the FCML and SSB topologies are presented as a strategy to more fully utilize capacitors for their superior energy density as compared to inductors. Mechanical and thermal considerations are factored in at every stage of the design process, which provides more ways to balance the performance of the electrical system with the overall system density. To my family and friends.

# Contents

| Co | ontents                                                                                                                                                                                                                                                                                          | ii                                                                                             |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Li | st of Figures                                                                                                                                                                                                                                                                                    | iv                                                                                             |

| Li | st of Tables                                                                                                                                                                                                                                                                                     | vii                                                                                            |

| 1  | Introduction         1.1 Organization of this Dissertation                                                                                                                                                                                                                                       | <b>1</b><br>1                                                                                  |

| 2  | <ul> <li>Electric Vehicle Charger System Architecture</li> <li>2.1 Single-Phase ac-dc Rectifier and dc-ac Inverter Fundamentals</li> <li>2.2 Conventional Design of Single-Phase ac-dc and dc-ac Converter Systems</li> </ul>                                                                    | <b>5</b><br>6<br>7                                                                             |

| 3  | Theory of Improving Power Density of Power Electronic Systems3.1Energy Storage Density of Passive Components3.2Flying Capacitor Multilevel Converter3.3Series-Stacked Buffer3.4Proposed Design of High Power Density ac-dc Rectifier / dc-ac Inverter Stage3.5Mechanical and Thermal Integration | <ol> <li>9</li> <li>10</li> <li>11</li> <li>12</li> <li>13</li> </ol>                          |

| 4  | Validation of the Power Stage4.1Introduction                                                                                                                                                                                                                                                     | <ol> <li>14</li> <li>14</li> <li>15</li> <li>18</li> <li>24</li> <li>28</li> <li>28</li> </ol> |

| 5  | Electric Vehicle Charger System Design5.1Introduction                                                                                                                                                                                                                                            | <b>30</b><br>30<br>31<br>34<br>35                                                              |

| 6   | Vali<br>6.1<br>6.2<br>6.3<br>6.4      | dation of the Electric Vehicle Charger System         Hardware Implementation         Experimental Results         Conclusions         Acknowledgement                              | <b>37</b><br>38<br>45<br>52<br>52 |

|-----|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 7   | <b>On</b><br>7.1<br>7.2<br>7.3<br>7.4 | the Exploration of Converter Start-up         Flying Capacitor Multilevel Converter Start-up         Proposed Solution         Hardware Results         Conclusions and Future Work | <b>53</b><br>53<br>56<br>59<br>62 |

| 8   |                                       | clusions<br>Conclusions                                                                                                                                                             | <b>64</b><br>64<br>65             |

| Bil | bliog                                 | raphy                                                                                                                                                                               | 67                                |

# List of Figures

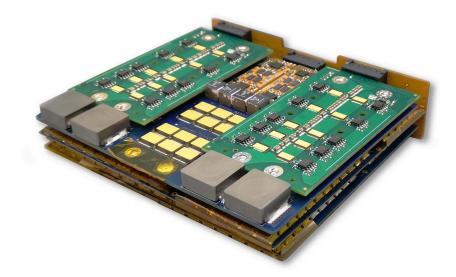

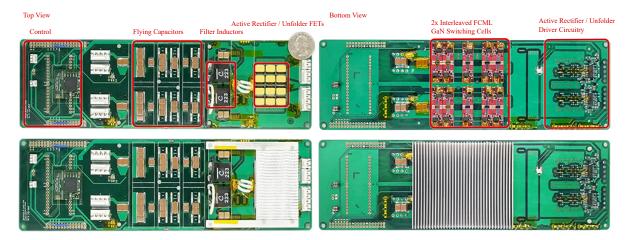

| 1.1                                  | High power density 7 kW dual-interleaved 6-level FCML inverter / rectifier hard-<br>ware prototype                                                                                                                                                                                    | 2               |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <ol> <li>1.2</li> <li>1.3</li> </ol> | Electrical portion of the high power density electric vehicle charger system pro-<br>totype incorporating dual-interleaved 6-level FCML modules, dual-interleaved<br>series-stacked buffer modules, and unfolder / rectifier. (Image created in collab-<br>oration with Zitao Liao.)  | 2<br>3<br>4     |

| 2.1<br>2.2<br>2.3                    | System architecture diagram detailing a single-phase ac-dc rectifier System architecture diagram detailing a single-phase dc-ac inverter Conventional single-phase ac-dc rectifier or dc-ac inverter. Bidirectional capability is contingent on the usage of active switching devices | 6<br>7<br>8     |

| 3.1<br>3.2<br>3.3                    | <i>N</i> -level FCML schematic                                                                                                                                                                                                                                                        | 11<br>11<br>12  |

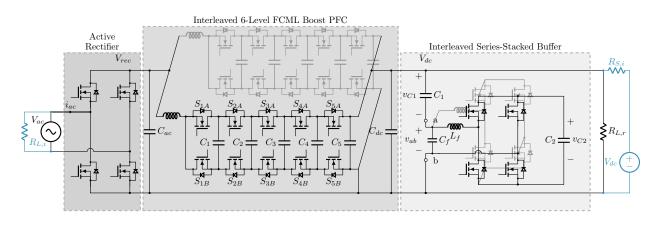

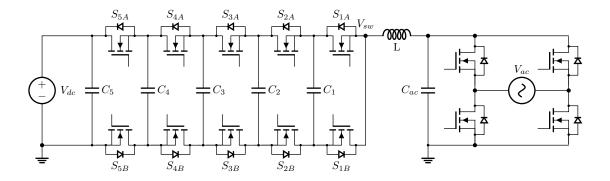

| 4.1                                  | Schematic drawing of the bidirectional ac-dc converter, comprising dual inter-<br>leaved 6-level flying capacitor multi-level stages, along with a single active recti-<br>fier/unfolder stage.                                                                                       | 16              |

| 4.2                                  | 6-level FCML control waveforms                                                                                                                                                                                                                                                        | 17              |

| 4.3                                  | Converter prototype photographs, with and without heatsinks                                                                                                                                                                                                                           | 18              |

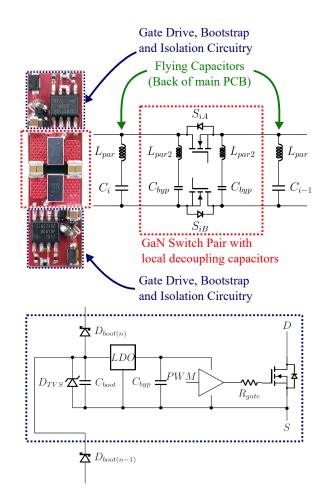

| 4.4                                  | Top: Switching cell daughterboard pair design. Bottom: Switching cell daugh-<br>terboard schematics.                                                                                                                                                                                  | 20              |

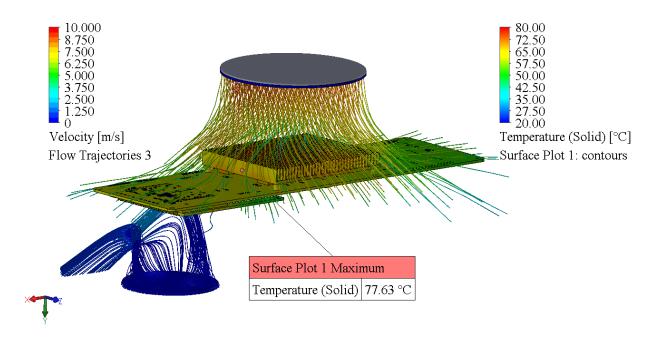

| 4.5                                  | SolidWorks Flow Simulation model with estimated temperature assuming 25 °C ambient.                                                                                                                                                                                                   | 20<br>22        |

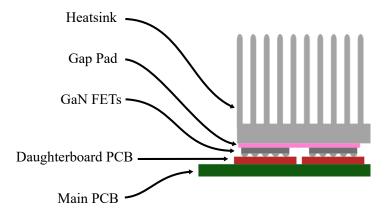

| 4.6                                  | Diagram of stackup for heatsink interface. (Image created in collaboration with Kelly Fernandez)                                                                                                                                                                                      | 23              |

| 4.7                                  | Power stage prototype.                                                                                                                                                                                                                                                                | $\frac{23}{24}$ |

| 4.8                                  | Side view of converter prototype.                                                                                                                                                                                                                                                     | $\frac{21}{25}$ |

|                                      |                                                                                                                                                                                                                                                                                       |                 |

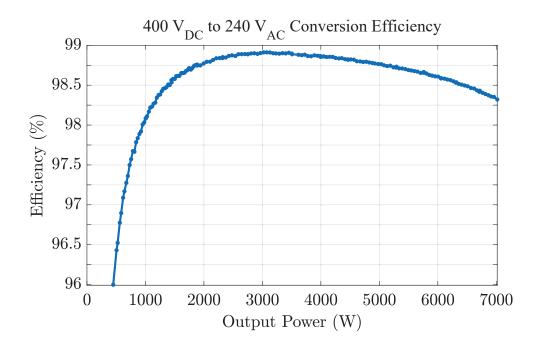

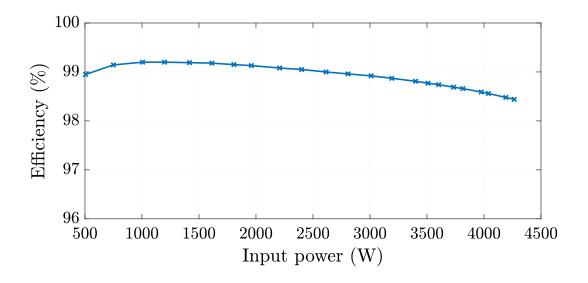

| 4.9          | Converter efficiency plot, with heatsink, up to 7 kW, including all control and gate drive losses.                                                                        | 26              |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

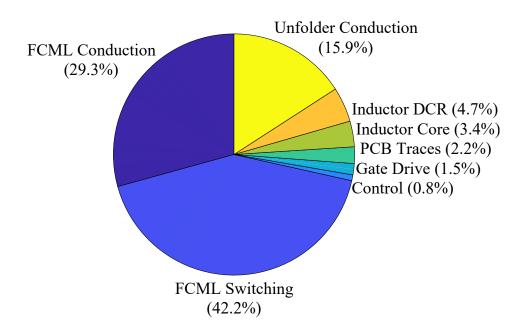

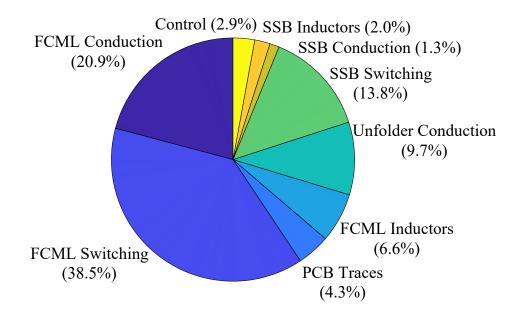

| 4.10<br>4.11 | Estimated loss breakdown at 7 kW                                                                                                                                          | 26<br>26        |

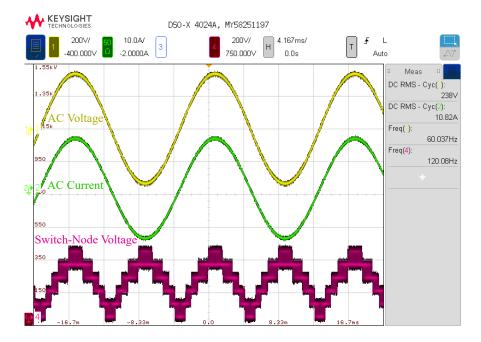

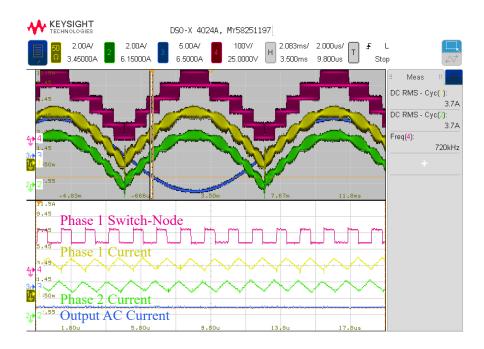

|              | switch-node voltage waveform                                                                                                                                              | 27<br>28        |

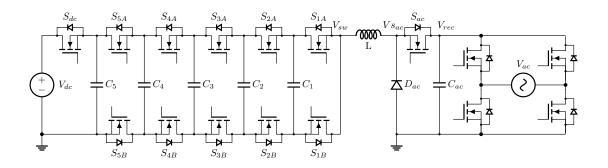

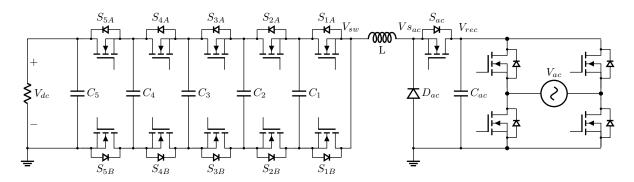

| 5.1          | Schematic of the overall system with active rectifier (unfolder), interleaved FCML, and series-stacked buffer. The dc source and load in the inverter mode are shown      |                 |

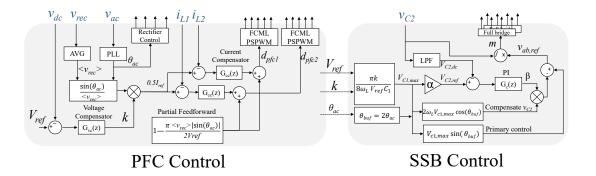

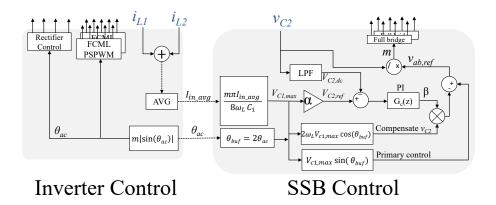

| 5.2          | in blue                                                                                                                                                                   | 31              |

|              | sensed parameters are in blue font. (Plot created in collaboration with Zitao Liao)                                                                                       | 32              |

| 5.3          | Overall control system in inverter mode. (Plot created in collaboration with Zitao Liao)                                                                                  | 33              |

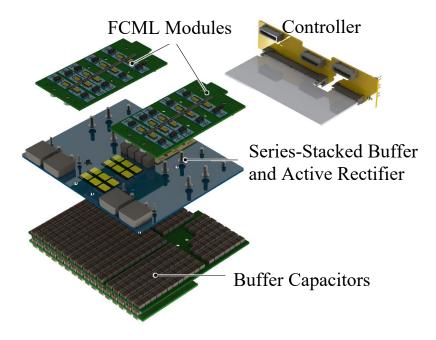

| $5.4 \\ 5.5$ | Exploded view render of the electric vehicle charger assembly                                                                                                             | $\frac{35}{36}$ |

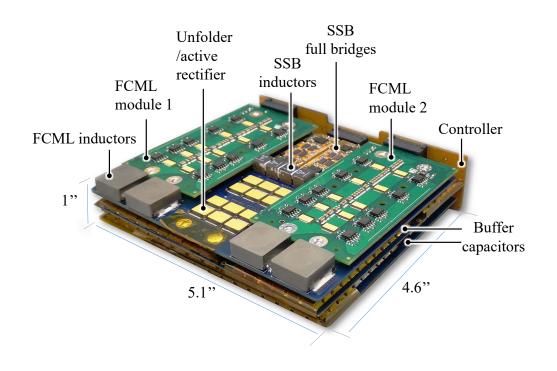

| 6.1          | The EV charger assembly, not including thermal management. Key subsystems are labeled. (Image created in collaboration with Zitao Liao)                                   | 39              |

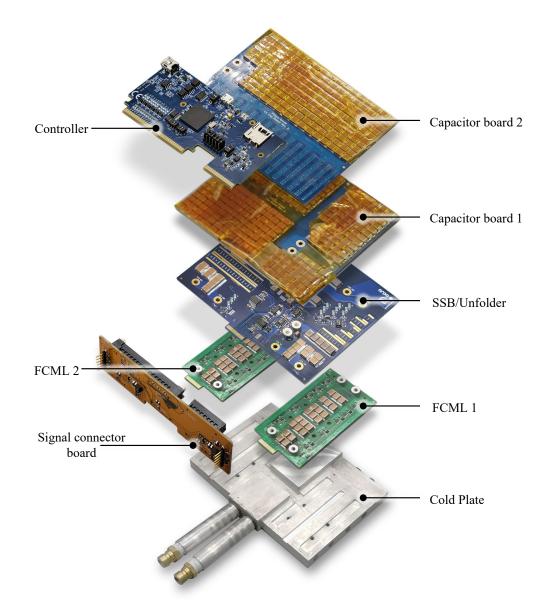

| 6.2          | Exploded view of the hardware assembly. (Image created in collaboration with Zitao Liao)                                                                                  | 40              |

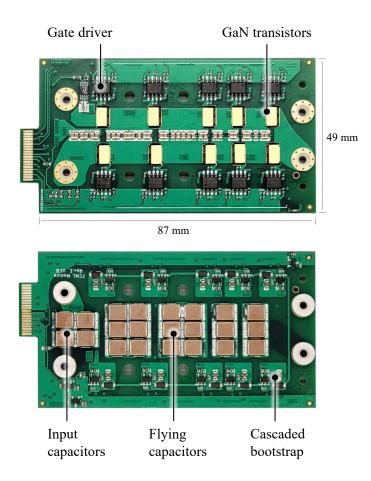

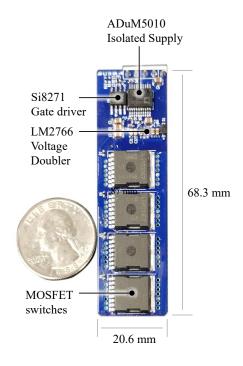

| 6.3          | Single FCML module with key components annotated.                                                                                                                         | 41              |

| 6.4          | Single FCML module with air-cooled heatsink attached. (Image created in col-<br>laboration with Zitao Liao and Kelly Fernandez)                                           | 42              |

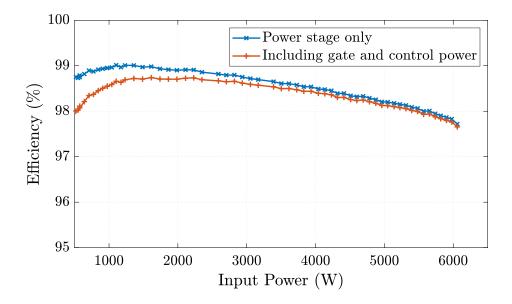

| 6.5          | The efficiency of the FCML module, running from 400 $V_{dc}$ to 260 $V_{dc}$ . (Image                                                                                     |                 |

| 6.6          | created in collaboration with Zitao Liao and Kelly Fernandez)                                                                                                             | 42              |

| a <b>-</b>   | detail.                                                                                                                                                                   | 43              |

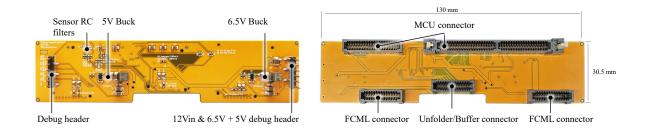

| $6.7 \\ 6.8$ | The low-voltage power distribution diagram of the electric vehicle charger<br>The signal connectors board of the electric vehicle charger system                          | 44<br>45        |

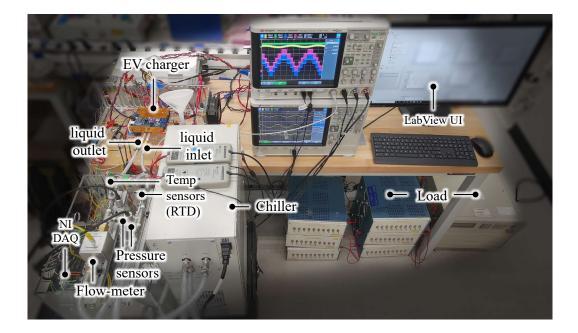

| 0.8<br>6.9   | Experimental bench setup. (Image created in collaboration with Zitao Liao and                                                                                             | 40              |

| 0.5          | Kelly Fernandez)                                                                                                                                                          | 46              |

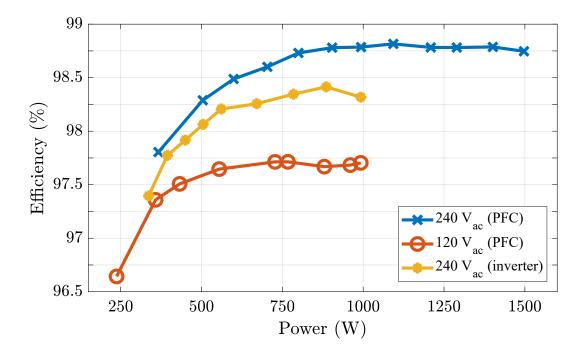

| 6.10         | The efficiency of the system, PFC mode from 120 and 240 $V_{ac}$ to 400 $V_{dc}$ , and                                                                                    |                 |

|              | inverter mode from 400 $V_{dc}$ to 240 $V_{ac}$ .                                                                                                                         | 47              |

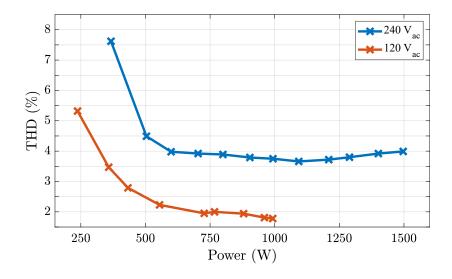

| 6.11         | The THD of the system, PFC mode from 120 and 240 $V_{ac}$ to 400 $V_{dc}$ . (Plot                                                                                         | 10              |

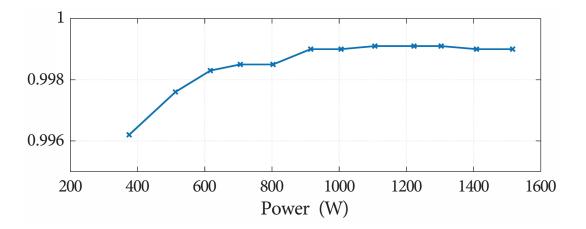

| 6.12         | created in collaboration with Zitao Liao)                                                                                                                                 | 48              |

|              | created in collaboration with Zitao Liao)                                                                                                                                 | 48              |

| 6.13         | Typical SSB voltage waveforms for $v_{c2}$ and $v_{ab}$ , dc bus voltage ripple (ac coupled),                                                                             |                 |

| 6 14         | and FCML switch-node of the system, PFC mode from 240 $V_{ac}$ to 400 $V_{dc}$ , 1.5 kW. Typical current waveforms of the interleaved FCML, PFC mode from 240 $V_{ac}$ to | 49              |

| 0.11         | 400 $V_{dc}$ , 375 W                                                                                                                                                      | 49              |

v

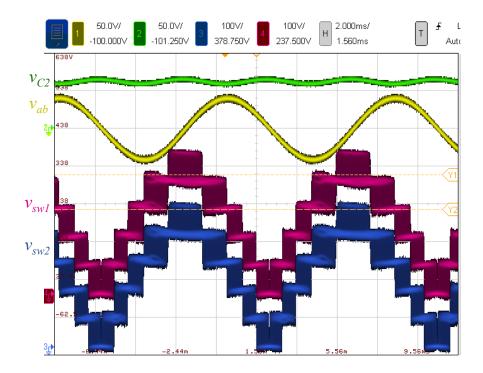

| 6.15 | Typical SSB voltage waveforms for $v_{c2}$ and $v_{ab}$ , and FCML switching node voltages                                                                                                                   |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | from 400 V <sub>dc</sub> to 240 V <sub>ac</sub> , 6.1 kW. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                              | 51 |

| 6.16 | The efficiency of the 6.1 kW inverter test, 400 V <sub>dc</sub> to 240 V <sub>ac</sub>                                                                                                                       | 51 |

| 6.17 | Estimated loss breakdown at 6.1 kW                                                                                                                                                                           | 52 |

| 7.1  | 6-level FCML and unfolder / rectifier schematic                                                                                                                                                              | 54 |

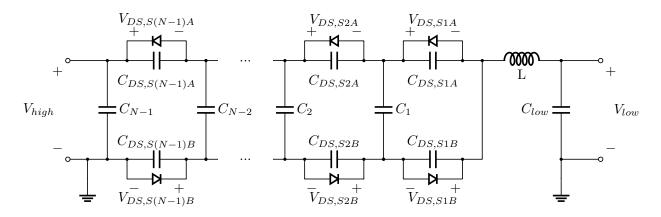

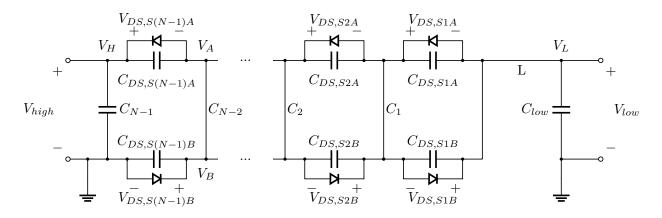

| 7.2  | Schematic of N-level FCML start-up boundary condition, assuming all switches                                                                                                                                 |    |

|      | are inactive                                                                                                                                                                                                 | 54 |

| 7.3  | Schematic of N-level FCML start-up boundary condition, assuming all switches                                                                                                                                 |    |

|      | are inactive, with assumption that the flying capacitors $C_{N-2}$ $C_1$ have a                                                                                                                              |    |

|      | much higher capacitance value than the drain-source capacitances of the power                                                                                                                                |    |

|      | semiconductor switches.                                                                                                                                                                                      | 55 |

| 7.4  | MOSFETs and supporting circuitry for floating switch implementation                                                                                                                                          | 57 |

| 7.5  | 6-level FCML and unfolder / rectifier schematic with added start-up switches and                                                                                                                             |    |

|      | supporting circuitry.                                                                                                                                                                                        | 57 |

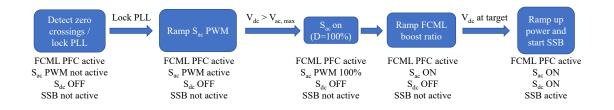

| 7.6  | FCML ac-dc converter ac side start-up logic                                                                                                                                                                  | 58 |

| 7.7  | 6-level FCML and unfolder / rectifier demonstration with added ac-side start-up                                                                                                                              |    |

|      | switch and supporting circuitry.                                                                                                                                                                             | 59 |

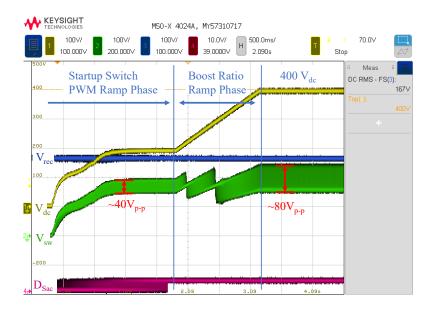

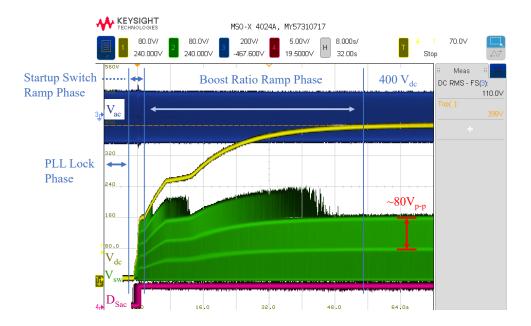

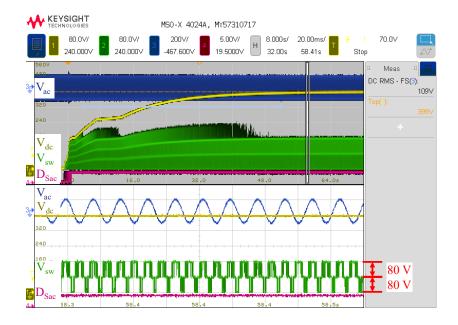

| 7.8  | dc start-up waveforms from 170 V <sub>dc</sub> to 400 V <sub>dc</sub> $\ldots \ldots \ldots$ | 60 |

| 7.9  | ac start-up waveforms from 110 $V_{ac}$ to 400 $V_{dc}$ .                                                                                                                                                    | 61 |

| 7.10 | ac start-up waveforms from 110 $V_{ac}$ to 400 $V_{dc}$ , stepped waveform detail                                                                                                                            | 62 |

# List of Tables

| 4.1 | Level II charger design specifications.                                         | 15 |

|-----|---------------------------------------------------------------------------------|----|

| 4.2 | Component listing                                                               | 19 |

| 4.3 | Flying capacitor component detail using TDK 2.2 $\mu$ F 450 V X6S capacitors in |    |

|     | parallel                                                                        | 21 |

| 4.4 | Key Performance Specifications                                                  | 25 |

| 6.1 | Overall system component listing                                                | 38 |

| 6.2 | Logic-level components listing                                                  | 45 |

| 6.3 | Data Acquisition and Thermal Management Equipment. (Thermal data acqui-         |    |

|     | sition system created in collaboration with Kelly Fernandez and Raya Mahony)    |    |

|     | · · · · · · · · · · · · · · · · · · ·                                           | 46 |

| 6.4 | Key performance specifications for the 6.1 kW inverter test                     | 50 |

| 7.1 | Component listing                                                               | 58 |

#### Acknowledgments

I will start with thanking my advisor, Professor Robert C. N. Pilawa-Podgurski, who accepted me into his group based on perhaps only my acceptance to UIUC, my resume, and a single phone call discussing what the group did and how I could contribute. I made an equally rash decision to move all the way to Illinois from California, which kicked off an amazing journey which appears to have brought me back to California again for the time being – a strange twist of fate as a friend put it. I noticed immediately as I met Robert in person that he manages to give people the advice that they need to make meaningful progress in their studies, yet he also allows for an amazing amount of freedom in the pursuit of the Ph.D. I hadn't touched any serious academic publication writing nor any particularly research-oriented work in the field of power electronics prior to my graduate studies, yet here I am today writing my personal capstone publication in a world-class power electronics research group. Robert has encouraged me to dream big and also achieve big things while I'm at it, and for that and many other things, I am grateful of the time we have spent together.

I would like to thank Professors Seth Sanders, Duncan Callaway, and Alexandra von Meier for being on my committees for higher education and providing valuable guiding advice for the direction of research and the relevance to current events. Thank you to Professor Arijit Banerjee for a jovial time at Illinois and discussions about the power electronics course set as well as general topics of interest.

Thank you to all fellow members of the Pilawa group, past and present: Yutian Lei, Shibin Qin, Christopher Barth, Enver Candan, Andrew Stillwell, Joseph Liu, Pourya Assem, Zitao Liao, Thomas Foulkes, Yizhe Zhang, Nathan Pallo, Tomas Modeer, Nathan Brooks, Pei Han Ng, Samantha Coday, Maggie Blackwell, Rose Abramson, Kelly Fernandez, Joseph Schaadt, Rahul Iyer, Yong-Long Syu, Mads Graungaard, Ting Ge, Nathan Ellis, Raya Mahony, Amanda Jackson, Logan Horowitz, Rod Bayliss III, Yicheng Zhu, Francesca Giardine and many more. My immediate partners in the lab, Zitao and Kelly, have put up with my antics of precision and followed me through the successes and failures of progress. They have oftentimes helped me manage through the darkest times I have experienced. Thank you for the countless hours of hardware, software, and life debugging that we have gone through in the lab, the office, and outside. Thank you to Sam, Maggie, Rose, and Nathan Pallo in lab administrative and social functions, which kept the sanity and atmosphere during tough times. Thank you to my collaborators at the University of Illinois at Urbana-Champaign: Danny Lohan in Prof. James Allison's group, George Popovic, and Tarek Gebrael in Prof. Nenad Miljkovic's group, and the University of Arkansas at Fayetteville: Robert Murphree in Prof. Alan Mantooth's group. Thanks to the different funding sources for making this work possible, including from the Power Optimization of Electro-Thermal Systems (POETS) National Science Foundation Engineering Research Center with support through Toyota, as well as the Advanced Research Projects Agency - Energy (ARPAE), U.S. Department of Energy.

Thank you to the staff at UC Berkeley: Shirley Salanio of the graduate affairs office for always being easy to talk to and ever-present over email. Dennis Lee of the Etcheverry Hall machine shop for the extremely valuable machine shop training and mechanical know-how advice through the years.

And, thank you to two amazing solar vehicle teams at UC Berkeley and UIUC that I have had the privilege of working with throughout my entire undergraduate and graduate careers. The goals of member enrichment in addition to the intense but rewarding design, build, and test cycles have taught me countless skills in both engineering and non-engineering that I have applied to my studies and my life throughout the years. They provided the opportunities for a dizzying amount of travel across the United States and Australia. The names are too numerous to list, though I would give a shout out to a few long-standing members, who have provided "unfiltered technical" advice at the oddest hours of the day (and night!): Richard "Ducky" Lin, Tristan Lall, Jean-Étienne Tremblay, Byron Hopps, Amalia Dungey, Harrison Zheng, Daniel Gay, Devan Lai, Geoffrey Ding, Rami Hijab, and many more.

Certainly, thank you to my parents, Martin Chou and Summer Chen, for their unwavering support throughout this entire journey. Thank you to my sister, Derina Chou, also for your support throughout these years at the most unexpected hours of the day. I could not have done this without you all.

# Chapter 1 Introduction

Design of energy delivery systems is becoming an increasingly complex and multi-disciplinary field. In emerging applications such as renewable energy delivery, electric vehicle powertrains and charging, and grid interface systems, the power electronics are becoming more sophisticated and more densely-packed than ever before. This work discusses considerations of such power electronics systems design given the prototypical application of an on-board singlephase ac-dc electric vehicle charger, as well as some techniques for keeping the heat losses manageable in extremely compact packaging. For a typical single-phase ac-dc electric vehicle on-board charger, there are two major energy processing steps: ac-dc rectification, and energy buffering of the twice-line-frequency energy mismatch. This work discusses methods of significantly reducing passive component sizes typical to these converters while maintaining a high efficiency. Furthermore, the implication of co-development of a thermal management system for such a compact converter is explored, as the electrical, mechanical, and thermal aspects heavily influence each other. These techniques are demonstrated in hardware prototypes achieving record power densities including a 7 kW, 400  $V_{dc}$  / 240  $V_{ac}$  single-phase air-cooled inverter / power factor correction (PFC) power stage, and 6 kW, 400  $V_{dc}$  / 240  $V_{ac}$ single-phase liquid-cooled inverter / PFC plus energy buffering system, among others.

### 1.1 Organization of this Dissertation

This work is organized as follows:

- Chapter 2: Electric Vehicle Charger System Architecture

- An on-board electric vehicle charger is an example power electronic system involving a multitude of interrelated pieces. This chapter presents a prototypical on-board single-phase ac-dc electric vehicle charger system architecture with a focus on the electrical system. Since the system may be run in reverse (dc-ac) as an inverter, the bidirectional nature of such a design is also discussed. A single-phase ac-dc rectifier or dc-ac inverter is comprised of two major stages: the power-processing power factor correc-

tion or inverter stage, and the energy buffering stage. A solution is proposed using a conventional design.

• Chapter 3: Theory of Improving Power Density of Power Electronic Systems The conventional design presented in the previous chapter has the major shortfall of possibly requiring the usage of physically large passive components for filtering purposes. Overarching concepts of improving power density in power electronic systems are introduced and discussed in this chapter. Recurring themes of improved passive component utilization and minimization are discussed. The general architecture of the flying capacitor multilevel (FCML) converter is introduced, as is the series-stacked buffer (SSB). A high power density approach to building a single-phase ac-dc rectifier or dc-ac inverter system is proposed.

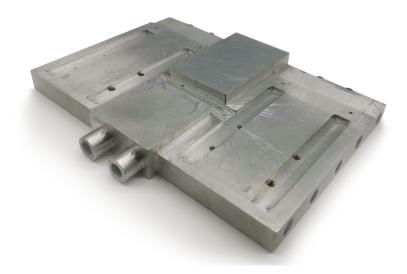

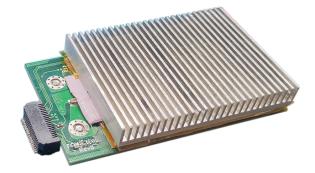

Figure 1.1: High power density 7 kW dual-interleaved 6-level FCML inverter / rectifier hardware prototype.

• Chapter 4: Validation of the Power Stage

In this chapter [1], the electrical architecture and hardware of the inverter (dc-ac) or rectifier (ac-dc) power processing stage is verified at high power. A dual-interleaved 6-level GaN multilevel converter is designed and built to achieve extreme power density figures, and thermal considerations for such a converter are discussed. A custom-milled heatsink prototype is designed, built, and tested with this hardware prototype. The prototype built (Fig. 1.1) achieves a power level of 7 kW, and an efficiency exceeding 98% throughout most of its power output range, well within the Level II charging power range. The power stage achieves a volumetric power density figure of 785 W/in<sup>3</sup> (47.9 W/cm<sup>3</sup>), which exceeds previous research demonstrations of power stage density by  $2 \times [2]$ , [3].

#### CHAPTER 1. INTRODUCTION

• Chapter 5: Electric Vehicle Charger System Design

In this chapter [4], [5], the system architecture of the electric vehicle charger is integrated into a single design. Prior work on the power stage of Chapter 4 as well as a series-stacked energy buffer are combined into an electric vehicle charger system design. Design of this charger involves electrical, mechanical, and thermal considerations which influence each other. Therefore, all of the above factors were considered at every point of the design in an attempt to produce a more-optimal system power density, with the explicit knowledge that the design would not pursue the most extreme electrical efficiency, mechanical packaging, or thermal performance, but rather a harmonious combination of the three.

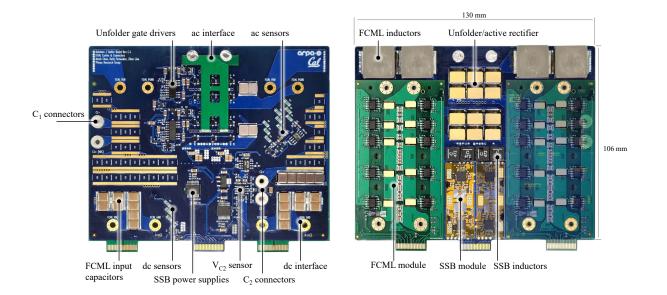

Figure 1.2: Electrical portion of the high power density electric vehicle charger system prototype incorporating dual-interleaved 6-level FCML modules, dual-interleaved series-stacked buffer modules, and unfolder / rectifier. (Image created in collaboration with Zitao Liao.)

- Chapter 6: Validation of the Electric Vehicle Charger System

- The electric vehicle charger system (Fig. 1.2) is constructed and validated in ac-dc PFC mode, as well as dc-ac inverter mode [4], [5]. A maximum power level of 6.1 kW is tested, well within the Level II charging power range. A custom-manufactured cold plate is used as the main thermal management system, which is verified along with the dual-interleaved FCML and dual-interleaved series-stacked energy buffer stage assemblies. The PCB assemblies are all designed to be compatible with conventional manufacturing techniques, thus improving the practicality overall. A system power density of 201 W/in<sup>3</sup> (12.3 W/cm<sup>3</sup>) is reported. This density figure exceeds the industrial state-of-the-art by an order of magnitude, and matches leading research figures

while employing conventional manufacturing and assembly techniques in the bulk of the system [6]-[12].

• Chapter 7: On the Exploration of Converter Start-up

Transient situations are of interest in a flying-capacitor multilevel converter due to its reliance on capacitor balancing. Depending on the design margin, capacitor balancing can be critical to proper converter behavior. For a highly-optimized FCML converter, the maximum operating bus voltages often exceed the switch voltage ratings, so the system relies on good capacitor voltage balancing to keep all of the core power semiconductors operating within these ratings. In this chapter, a start-up sequence for the electric vehicle system is proposed and explored. The addition of a pair of semiconductor switches and some filtering elements (Fig. 1.3) creates a voltage and current limiting structure not unlike a four-switch buck-boost converter, which is used to limit the voltage across the FCML converter switches during a start-up sequence.

Figure 1.3: 6-level FCML and unfolder / rectifier schematic with added start-up switches and supporting circuitry.

• Chapter 8: Conclusions

This chapter concludes this work and comments on the future direction of this research.

### Chapter 2

# Electric Vehicle Charger System Architecture

Electric vehicles have become an increasingly popular and feasible alternative to conventional gas-powered vehicles in the past decade. However, battery electric vehicles continue to face such challenges as range anxiety, long charging times, and public perception of safety. Improving such metrics would require infrastructure upgrades, improved charging architecture for increased charging rate, and improved energy density in the batteries themselves [13]. A conventional gasoline-powered automobile requires only minutes to refuel fully, while an electric vehicle would require hours to recharge fully [14]–[17]. Therefore, along with improving battery capacity and charging rate capabilities of the physical battery itself, it is desirable for electric vehicle chargers to handle higher charging power levels, to minimize battery charge times. This must be balanced with keeping charging hardware volume and weight to a minimum, as such energy conversion systems interfacing between grid ac and battery dc voltages are carried on-board for Level I or Level II charging power levels. Electric vehicle batteries may additionally be viewed as a mobile battery backup source for the grid, meaning that bi-directional operational capabilities are desirable to include in such an on-board system [14], [17], [18].

An on-board single-phase ac-dc electric vehicle charger is used as the prototypical power electronic system for this work. This work explores the implications and methods of improving power density in power electronic systems, taking a holistic approach which considers electrical, mechanical, and thermal aspects.

In this chapter, the high-level electrical architecture of an on-board charger is presented and discussed. The design of such converters can allow for bidirectional operation, so both the ac-dc rectifier and dc-ac inverter functionality is discussed. A conventional solution to the ac-dc or dc-ac conversion problem is presented.

### 2.1 Single-Phase ac-dc Rectifier and dc-ac Inverter Fundamentals

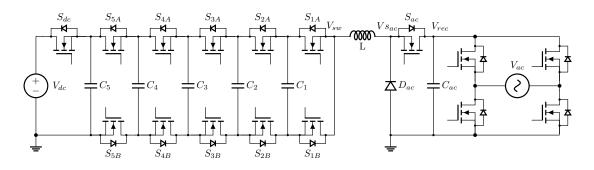

Given a single-phase ac grid-interfaced system that is connected to a dc battery (Figs. 2.1 and 2.2), we can define the grid voltage and grid current as sinusoidal functions, which then multiply together to form an ac power function:

$$V_{ac} \propto \sin(\omega t) \tag{2.1}$$

$$I_{ac} \propto \sin(\omega t) \tag{2.2}$$

$$P_{ac} = V_{ac} \cdot I_{ac} \propto \sin^2(\omega t) = \frac{1}{2} - \frac{\cos(2\omega t)}{2}$$

$$\tag{2.3}$$

In steady-state conditions, the dc power is approximately constant. Therefore, the ac and dc power will almost always be mismatched except for singular points along the line cycle. Given the above, a single-phase grid-tied system charging a dc battery must perform two major functions:

- Provide power factor correction (PFC) support to keep grid voltage and current similarlyshaped and in-phase with each other in accordance with regulatory standards on total harmonic distortion that is experienced by the grid side of the converter.

- Provide energy buffering to mitigate the 120 Hz (twice-line frequency,  $\omega$ ) energy ripple that occurs as a natural result of ac-dc or dc-ac conversion.

Figure 2.1: System architecture diagram detailing a single-phase ac-dc rectifier.

In a rectifier system (Fig. 2.1), the power factor correction stage shapes the current waveform of the input ac to be sinusoidal and in phase with the ac voltage. The energy

Figure 2.2: System architecture diagram detailing a single-phase dc-ac inverter.

buffer power,  $P_{buf}$  is subtracted from the ac power,  $P_{ac}$ , which ideally cancels out the twiceline frequency ripple of the ac power, to produce a constant dc power,  $P_{dc}$ .

In an inverter system (Fig. 2.2), the dc source provides a constant power,  $P_{dc}$ , which is then added to the energy buffer power,  $P_{buf}$ ; this is run through an inverter stage which is synchronized with the grid ac voltage, pushing electric current at high power factor,  $P_{ac}$ .

### 2.2 Conventional Design of Single-Phase ac-dc and dc-ac Converter Systems

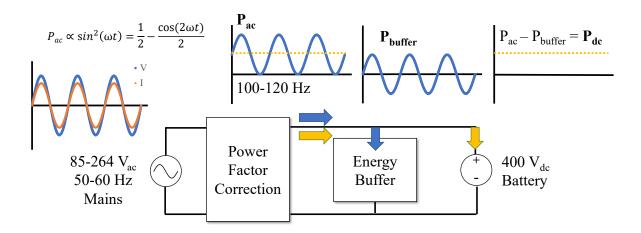

A conventional solution to constructing the system presented in Figs. 2.1 and 2.2 is shown in Fig. 2.3.

It consists of an ac full-bridge rectifier or unfolder stage connected to a boost PFC stage, the output of which is buffered with a large DC-link capacitor to smooth the ac power ripple. The two major functionalities of the above-discussed rectifier or inverter system are implemented here.

In the rectifier mode:

- The full-bridge rectifier stage is connected to a boost power factor correction stage, which provides the ac power processing capability.

- The energy buffer is a bank of dc-link capacitors, which smooths out the energy ripple to provide approximately dc power.

In the inverter mode:

Figure 2.3: Conventional single-phase ac-dc rectifier or dc-ac inverter. Bidirectional capability is contingent on the usage of active switching devices.

- The boost PFC stage is run in reverse as a buck stage, to produce a rectified sine waveform, which is then fed to the full-bridge stage running in reverse as an unfolder stage, which produces a full sine waveform. This provides the ac power back to the grid.

- The energy buffer, the bank of dc-link capacitors, compensates for any power mismatch between the dc and ac sides.

### Chapter 3

# Theory of Improving Power Density of Power Electronic Systems

Major drawbacks to a conventional ac-dc or dc-ac system design such as the one presented in Chapter 2 include the relatively large passive component elements required to provide satisfactory power factor and dc voltage ripple filtering. The boost inductor of the boost PFC stage and the dc-link capacitor are commonly physically the largest elements in such a design.

This chapter discusses the fundamental principles dictating the physical size of converter systems. The energy storage capability of inductors and capacitors are discussed, and a proposed high power density solution is explained in two parts. The first, the flying-capacitor multilevel converter power stage, is implemented to reduce the boost inductor size [19], [20]. The second, the series-stacked buffer [21]–[23], is used to reduce the energy buffer capacitor size.

#### **3.1** Energy Storage Density of Passive Components

Power converters leverage the usage of switches and temporary energy storage in capacitors and inductors to convert energy efficiently. In a conventional two-level buck converter design, this is commonly achieved with the usage of MOSFETs as the blocking switch elements, a large filter inductor as magnetic energy storage, and capacitors as the ripple filter elements. The drawbacks to such a design are apparent in the relatively large size of the magnetic element: since the inductor has a significantly lower energy storage density than that of capacitors, it tends towards being one of the largest physical elements in these designs [24]. For example, on a boost power factor correction stage, the boost inductor is larger than all of the power devices combined. Noted from the energy storage capability of inductors:

$$\Delta E \propto L \cdot (\Delta I)^2 \tag{3.1}$$

To realize a high energy storage usage, either a large current ripple must be allowed (and then filtered), or a large inductance value must be used. Since larger inductance values tend

to result in larger physical devices, the two above factors are frequently traded off with each other, as well as with the filter capacitor sizing, to obtain an optimal system design.

In a capacitor energy buffer implementation for single-phase ac-dc converters, a conventional solution is to use a bank of electrolytic capacitors. Capacitors have superior energy density compared to inductors [24], but the energy utilization percentage is poor as they are often limited by external constraints defining voltage and current ripple figures. The energy buffering capability that a capacitor bank can source is noted:

$$\Delta E \propto C \cdot (\Delta V)^2 \tag{3.2}$$

In an electrolytic capacitor energy buffer implementation,  $\Delta V$  is commonly a small percent of the dc bus voltage, superimposed on top of a comparatively large dc bias.  $\Delta V$  is commonly externally defined in the single-digit percent values, which drives up the required buffer capacitance value. The dc bias,  $\frac{1}{2} \cdot C \cdot V_{bias}^2$ , can be considered as unused potential buffering capability, as it does not change and therefore does not contribute to energy buffering in the system it is used in. This is further limited by the relatively high equivalent series resistance of electrolytic capacitors, which limits the available electric current buffering capability. Different capacitor technologies, such as film and ceramic capacitors, may be used to improve electric current buffering capability, but these technologies are not as volume- or cost-efficient as electrolytic capacitors.

This work aims to improve the power density of these implementations of energy conversion and buffering for a single-phase ac-dc converter system by utilizing the flying-capacitor multilevel converter in conjunction with the series-stacked energy buffer.

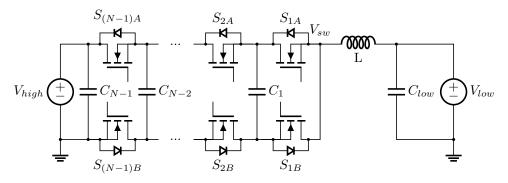

#### 3.2 Flying Capacitor Multilevel Converter

The flying-capacitor multilevel converter (FCML) [19] is a well-explored converter topology with a high potential for dramatically reducing passive component volume and weight. This has been demonstrated in inverter [10], [25] and PFC applications [26], [27]. It takes advantage of the high energy density of capacitors when compared to inductors, [24] as the use of high energy density ceramic capacitors and reduced voltage stress on inductors can reduce the overall inductor size by a factor of  $(N - 1)^2$ , where N is the number of levels in the FCML. An N-level FCML is shown in figure 3.1. Note that the converter topology lends itself to a highly modular design, as the switches and capacitors are arranged in repeating units. Not only does this allow for possibly improved design and manufacturing techniques, it also allows for losses to be spread out across the entire set of power devices, rather than concentrating all of the losses into two devices like a conventional two-level converter would. Thus, a high power processing capability can be realized even if the overall converter volume is reduced, as the heat loss density can be managed with this topology.

Figure 3.1: N-level FCML schematic.

#### 3.3 Series-Stacked Buffer

The series-stacked buffer topology [21], [28]–[30] is considered as a remedy to the low energy utilization of the electrolytic dc-link capacitor bank. It is implemented to mimic the behavior of a notch filter at the line frequency, but again uses capacitors as the main energy storage element.

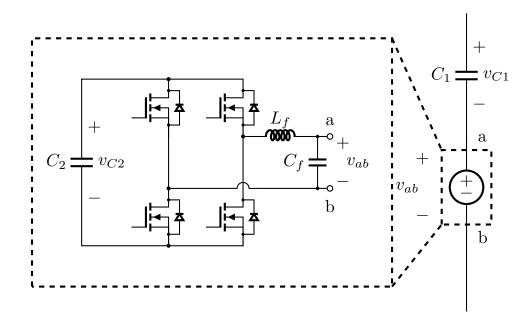

Figure 3.2: Series-stacked buffer (SSB) topology for buffering twice-line frequency ripple in single-phase ac-dc and dc-ac systems.

Fig. 3.2 shows an implementation of the series-stacked buffer topology. Capacitor  $C_1$

is allowed to ripple at a much higher  $\Delta V$  than would normally be allowed for a dc-link capacitor. This ripple is exactly canceled with voltage  $v_{ab}$ , which is generated by a fullbridge converter from a voltage source, in this case  $C_2$ . This entire structure is controlled to approximate an RLC circuit, which draws real power into the circuit to prevent the voltage across  $C_2$  from decaying [21]. The increased voltage ripple across  $C_1$  allows for the buffer dc-link capacitor to be greatly reduced in size, with the tradeoffs of needing to construct a converter to store and utilize the energy on  $C_2$ , as well as the physical size of  $C_2$  itself.

### 3.4 Proposed Design of High Power Density ac-dc Rectifier / dc-ac Inverter Stage

A system architecture featuring the flying-capacitor multilevel (FCML) converter as the inverter or power factor correction (PFC) stage, and a series-stacked buffer (SSB) as the energy buffer stage, is used to improve gravimetric and volumetric power density as compared to conventional designs, as shown in Fig 3.3. A previous hardware demonstration of such a combination of the two topologies is presented in [10]. This work aims to improve upon the previous art by improving the manufacturability of system elements, increasing the maximum power level to Level II electric vehicle charger levels, and enhancing the integration of electrical, mechanical, and thermal aspects.

Figure 3.3: Proposed high power density single-phase ac-dc rectifier or dc-ac inverter

The above system topology allows for significantly higher power density because of the higher utilization of capacitors for energy transfer. In the FCML stage, the capacitors are used to hold a dc bias, which allows for lower-voltage semiconductor switches to be used. Since lower-voltage rated semiconductor switches can potentially have a higher figure-of-merit (defined as gate charge  $Q_g$  multiplied by the on-state resistance  $R_{ds,on}$ ), the efficiency of such a converter could potentially be improved. Furthermore, compared to a conventional two-level boost PFC, the FCML topology has the benefit of dividing the total losses of

the switching elements into potentially many different elements, which can simplify thermal management.

In the SSB stage, the capacitor  $C_1$  is allowed to ripple at a  $\Delta V$  larger than would be allowed for a bank of dc-link electrolytic capacitors; this ripple is canceled with a waveform generated at  $v_{ab}$  with the full-bridge converter structure.

Previous industrial and research applications of both the inverter power stage as well as the integrated inverter plus energy buffer yield a comparison point for this work: State-of-the-art industrial designs [6]–[9], [11] achieve densities of up to about 10-50 W/in<sup>3</sup> (0.61- $3.1 \text{ W/cm}^3$ ) for system density, while state-of-the-art research designs [10], [12] are achieving 80-250 W/in<sup>3</sup> (4.9-15.3 W/cm<sup>3</sup>) with highly-specialized production and assembly techniques. If considering the power stage alone, research designs [2], [3], [31] appear to achieve up to 200-375 W/in<sup>3</sup> (12.2-22.9 W/cm<sup>3</sup>) of power stage density.

#### 3.5 Mechanical and Thermal Integration

Often cited as an addendum to conventional designs, mechanical and thermal integration of power electronic systems are becoming increasingly important at earlier stages of the design process [10], [32], [33]. In this work, the overall assembly maximizes the utilization of the 3-D space with a low-profile and modular design philosophy, enabled by the use of high energy density ceramic capacitors and the reduced inductor size in both FCML and SSB stages. The heat-generating components are placed in groups to allow for simple thermal circuit routing and higher thermal efficiency for automotive cooling systems. Overall, this work aims to achieve the state-of-the-art research design power densities while keeping provisions for the usage of more-conventional techniques of manufacturing and assembly.

### Chapter 4

### Validation of the Power Stage

This chapter discusses the design and implementation of a high power density Level II charger power stage converting between 400 V<sub>dc</sub> and 240 V<sub>ac</sub>, utilizing two interleaved flying-capacitor multilevel converter stages combined with a full H-bridge unfolder or active rectifier. The focus of this chapter is the ac-dc/dc-ac power stage, with the goal of a combined high efficiency and power density. Thus, power factor correction (PFC) control and twice-line-frequency buffering are not discussed or implemented in this chapter. Experimental results show a peak system efficiency of greater than 98.9%, a power output of 7 kW, and an effective switching frequency at the inductor switch nodes of 720 kHz.

#### 4.1 Introduction

Conventional approaches to constructing the ac-dc stage for power conversion between grid ac and battery dc voltages encounter the problem of requiring large filter inductors and capacitors for energy buffering. A possible solution to this involves increasing the switching frequency of the active devices in the converter to reduce passive component sizes, but this reduces overall system efficiency and increases thermal management requirements. The bridgeless PFC topology [34], and converter interleaving [35] are examples of optimizations which reduce conduction path losses, but they still require the usage of high-frequency highvoltage blocking switches. Reducing the maximum power design specification can reduce the passive component sizes, but will increase the charging time requirement.

It has been shown that the flying capacitor multilevel (FCML) topology [19], [20], [36], [37] has the potential to dramatically reduce passive component volume and weight in inverter [10], [25] and PFC applications [26], [27], [38], [39]. The characteristic frequency multiplication and voltage division effects of the FCML topology allow for the usage of lower-voltage switching devices as well as smaller magnetic components. By leveraging the higher energy density of capacitors, the FCML topology has been shown to improve the power density of such converters by over an order of magnitude from the industrial state-ofthe-art. This chapter aims to improve gravimetric and volumetric power density figures of a Level II bidirectional electric vehicle charger ac-dc/dc-ac power stage. We note here that for single-phase ac-dc converters, twice-line frequency energy buffering is another important consideration, but is not the focus of this chapter, as it is discussed in the following chapters (5 and 6). Likewise, power factor correction (PFC) control, grid synchronization, and other high-level control considerations are not addressed in this chapter as they are also discussed in the following chapters (5 and 6). SAE J1772 standards describe Level II charging as less than 80 amperes of current at a standard 208 V or 240 V single-phase ac voltage, representing a maximum power of 19.2 kW [40]. However, since many of these chargers are designed to plug into household dryer outlets, the realistic current limit is lower, between 15–30 A, which represents a power level between 3.1–7.2 kW [41]. Table 4.1 details sample design criteria generated for the purposes of this system platform design.

| Parameter           | Notes   | Value                |

|---------------------|---------|----------------------|

| DC Voltage          | Nominal | uc                   |

| AC Voltage          | Nominal | $240 V_{ac}$         |

| Power Processed     | Max     | 6.6 kW               |

| Ambient Temperature | Max     | 60 °C                |

| Physical Location   |         | Under passenger seat |

Table 4.1: Level II charger design specifications.

The key contributions of this chapter [1] are the combination of the converter topology, logic supply and gate drive, and heatsinking of the FCML and inverter devices.

The remainder of this chapter is organized as follows: Section 4.2 presents the overall system topology design and operational principles. Section 4.3 describes the hardware design and implementation of the system described in the previous section and Section 4.4 discusses experimental results obtained from the hardware prototype. Section 4.5 provides concluding remarks.

### 4.2 Principles of Operation

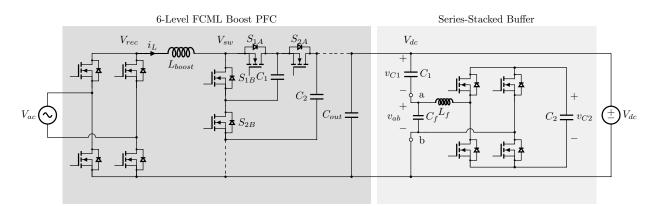

The hardware platform presented in this work is an interleaved implementation of the FCML converter topology, connected to a full H-bridge active rectifier or unfolder stage. Figure 4.1 is a schematic drawing of the core power conversion stage design. To operate the system as an inverter, the FCML dc-dc converter stage generates a rectified sine wave, which is then converted to a full sine wave by the full H-bridge unfolder. The interleaving operation of the FCML converter portion reduces voltage ripple at the rectified sine wave node,  $V_{rec}$ . To operate the system as a rectifier, the H-bridge acts as an active rectifier, and the FCML dc-dc conversion stage steps up the rectified sine wave voltage to the dc bus voltage.

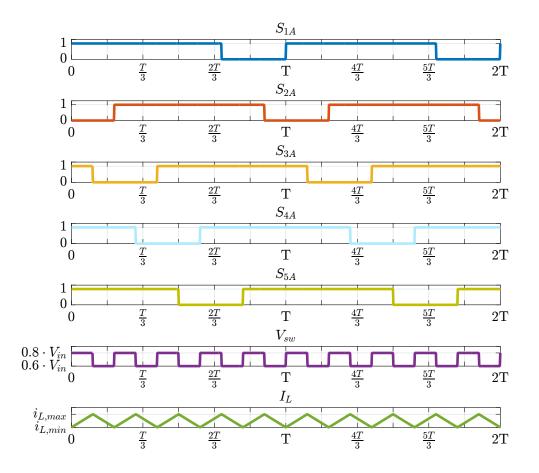

Figure 4.1: Schematic drawing of the bidirectional ac-dc converter, comprising dual interleaved 6-level flying capacitor multi-level stages, along with a single active rectifier/unfolder stage.

#### Multilevel DC-DC Conversion

The flying capacitor multilevel topology uses a combination of capacitors and inductors to transfer energy. A major advantage of this topology that is leveraged in this work is its ability to generate high effective switching frequency waveforms at the filter inductor switch-node  $(V_{sw}, Fig. 4.1)$ . Detailed operational principles for the FCML converter topology can be found in [19], [10], and [42].

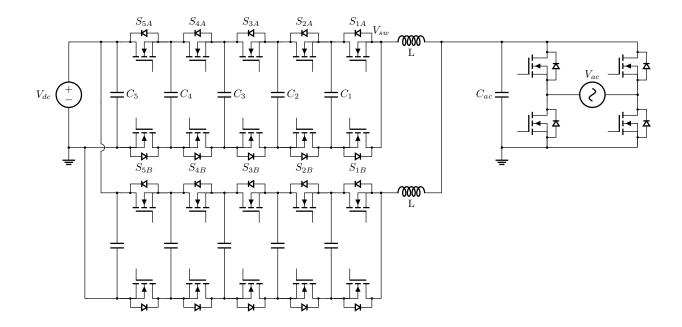

The hardware platform presented in this work consists of two interleaved 6-level FCML stages, phase-shifted 180 degrees with respect to each other to reduce current ripple the rectified sine wave node,  $V_{rec}$ . To illustrate the operation of a single FCML power stage, switching signals and voltage nodes of interest are shown in Fig. 4.2, for an example single 6-level FCML converter operating at 70% duty ratio. Switch control and capacitor balancing are achieved through usage of the phase-shifted PWM (PSPWM) method, which are described in more detail in [19], [43] and [44]. The 6-level topology was chosen for its inherent natural capacitor voltage balancing effect [45]. Of note is the frequency multiplication effect inherent to the FCML topology, where the frequency,  $f_{ind}$ , seen by the inductor switch-node,  $V_{sw}$ , is:

$$f_{ind} = f_{sw} \cdot (N-1) \tag{4.1}$$

where N is the number of voltage levels in the FCML converter and  $f_{sw}$  is the individual switch switching frequency. In a 6-level FCML converter, the frequency seen by the inductor

Figure 4.2: 6-level FCML control waveforms

is 5× the base switching frequency. Moreover, the inductors experience a maximum ripple voltage of the smallest voltage across the flying capacitors,  $V_{DC}/(N-1)$ . This results in an overall  $(N-1)^2$  reduction in filtering inductor size, as compared to a conventional two-switch non-isolated converter design (N = 2) [46]. For a 6-level FCML converter, this is roughly a 25× decrease in the filter inductor size requirement for the same base switching frequency.

As noted, switching signals for each of the FCML stages are phase-shifted by 180 degrees. Therefore, the ac portions of the output current waveforms of the two inductors in the system partially (or fully, for certain duty ratios) cancel, resulting in a current waveform with very low ripple at the rectified sine wave node ( $V_{rec}$ , Fig. 4.1). Even though the interleaved stages may not be perfectly matched for current sharing, since they are constructed with the same components, the benefits of lower current ripple due to interleaved operation are still generally achieved. In this work, only the effects of natural current sharing between stages are explored; interleaved stage balancing, load shedding at light-load operating points, and other more advanced techniques may be implemented in software but are not explored further.

The FCML topology utilizes capacitors to block dc voltages, and the switches see only a fraction of the input voltage:

$$V_{switch} = \frac{V_{dc}}{N-1} \tag{4.2}$$

Since lower-voltage switching devices tend to have a more favorable figure of merit, defined as the product of gate charge by on-state resistance, the overall efficiency of the system can be improved through selection of such devices. The combination of frequency multiplication effects and increased design space for switching devices allows for some design versatility: the more-favorable figure-of-merit may be leveraged in the way of extreme reduction of filtering capacitors and inductors through high-frequency switching [47], or it may be optimized to provide a balance between switching and conduction losses. In this work, EPC2033 GaN devices are selected for usage in the FCML stage to provide a balance between switching and conduction losses, taking into account the somewhat increased conduction losses due to dynamic on-state resistance [48], [49].

#### 4.3 Hardware Design and Implementation

The hardware prototype has been designed, constructed and tested, using the guidelines set forth in Table 4.1. Figure 4.3 shows annotated photographs of the converter as built, including the control, interleaved FCML, and active rectifier / unfolder stages, as well as of the converter with heatsinks attached. Table 4.2 provides a listing of the major components used in the converter prototype.

Figure 4.3: Converter prototype photographs, with and without heatsinks.

The main power devices in the FCML stage are EPC 2033 GaN FETs, driven by Silicon Labs Si8271 single-channel isolated gate drivers. To address the challenge of supplying a floating gate drive voltage to each GaN FET, several solutions may be used. In this

| Component                   | Part No.              | Parameters                              |

|-----------------------------|-----------------------|-----------------------------------------|

| Interleaved 6-Level FCML    |                       |                                         |

| GaN FETs                    | EPC 2033              | 150 V, 7 $m\Omega$                      |

| Isolated Gate Drivers       | Si8271GB-IS           | Silicon Labs Si827x Series              |

| Flying Capacitors           | TDK C5750X6S225K250KA | $2.2 \ \mu F \times 2-5$                |

|                             |                       | (parallel, $\sim 2.6 \mu F$ effective)  |

| Inductors                   | Coilcraft XAL1510-223 | 22 $\mu {\rm H}$ (2 total; 1 per phase) |

| Active Rectifier / Unfolder |                       |                                         |

| GaN FETs                    | GaN Systems GS66516T  | 650 V, 25 $m\Omega \times 3$ (parallel) |

| Isolated Gate Drivers       | Si8274GB1-IS1         | Silicon Labs Si827x Series              |

| Control                     |                       |                                         |

| FPGA                        | Altera 10M16SCU169C8G | MAX10 Series                            |

Table 4.2: Component listing

work, individual gate drive power supplies are achieved through cascaded bootstrap stages with low-dropout (LDO) regulators attached to each bootstrap capacitor to provide a stable drive voltage to each FET (Fig. 4.4). Reverse conduction of the GaN devices can cause the bootstrap capacitors to be charged to a voltage higher than the input logic voltage. An electrostatic discharge (ESD) protection diode rated for 12 V standoff voltage and 13.5 V breakdown voltage is placed in parallel with the bootstrap capacitors of each stage, to protect the LDOs from any overvoltage conditions during higher-current operations of the converter. To ensure that the highest-side FET gets at least 5 V of gate drive voltage, the lowest-side gate driver bootstrap capacitor is fed 12 V of gate drive voltage, which is then regulated down to the 5 V gate drive voltage through an LDO. For each cascaded bootstrap stage, there is a small diode drop from the bootstrap diode, resulting in a voltage of about 6.1 V at the highest-side bootstrap capacitor. The method outlined here achieves a 40+% gate drive supply efficiency, which outperforms a similar solution using small isolated dc-dc converters, the ADuM5010, which would achieve less than 27% gate drive supply efficiency [50]. Reducing the gate drive voltage margin, or using small step-down switching converters can improve the gate drive supply efficiency, but is not explored further in this work. Reference [50] provides more information regarding a multitude of possible solutions to providing the necessary floating supplies for each gate driver.

The step-up / step-down conversion of the ac-dc / dc-ac stage is accomplished with two parallel 6-level FCML converters, using interleaved switching signals to reduce ripple at the converter rectified sine wave node,  $V_{rec}$ . In the FCML converter topology, there are many repeating switch pairs. Therefore, to streamline construction, the supplementary circuitry for each switch is built on a GaN "switching cell" daughterboard. As shown in Fig. 4.4, each "switching cell" consists of an EPC 2033 GaN device, a Silicon Labs Si8271 isolated gate driver, an LDO, bootstrap capacitors, a transient voltage suppression (TVS) diode, a bootstrap diode, and all supporting passive components for filtering and bypass. This

Figure 4.4: Top: Switching cell daughterboard pair design. Bottom: Switching cell daughterboard schematics.

has the advantage of breaking up a large converter into a construction of many smaller switching units, with the additional benefit of reducing parasitic ringing effects through the local bypass capacitors. These smaller capacitors are connected in parallel with the larger flying capacitors on the opposite side of the larger circuit board. The parasitic inductances associated with the current commutation loops of the various components are highlighted in Fig. 4.4. Here,  $L_{par2}$  represents the inductance associated with the current commutation loop between the two GaN devices and the local decoupling capacitors, and  $L_{par}$  represents the inductance of commutation loop involving the larger flying capacitors on the backside of the PCB. Since the local bypass capacitors are physically very close to the switch pairs, the value of  $L_{par2}$  is less than  $L_{par}$ , reducing switch voltage overshoot during commutation [10], [25].

In the active rectifier / unfolder H-bridge stage, each of the switches in Fig.4.1 is three

GaN Systems GS66516T GaN FETs in parallel, designed to handle the high currents that are switched by the active rectifier / unfolder stage. Compared to a conventional silicon MOSFET implementation, the GaN Systems GS66516T 650 V, 25 m $\Omega$  GaN FETs have a significantly lower  $R_{DS,on}$  for the same volume, and therefore provides an attractive power density increase [51], [52]. Silicon Labs Si8274 dual-channel complementary isolated gate drivers are used to drive the power switches, and a conventional bootstrap stage is used to power the high-side gate drivers and FETs. Deadtime between the switching devices in the H-bridge legs is generated internally by the Si8274 gate driver chip.

The frequency multiplication and voltage division effect of the FCML topology is evident in the size of the passive components selected for use in the system. The GaN FETs in the FCML power stage are switched at 144 kHz, resulting in a 720 kHz ripple frequency at the filter inductor. Each flying capacitor is ~  $2.6\mu$ F in value, and a single 22  $\mu$ H inductor per FCML stage is used. The TDK online datasheet for the 2.2  $\mu$ F 450 V X6S capacitors was consulted to account for the voltage de-rating effect of ceramic capacitors, where the effective capacitance is noted using manufacturer supplied data points [53], and using a linear interpolation where the voltage of a certain node falls between data points; the number of capacitors in parallel used per flying capacitor is shown in Table 4.3, referencing the capacitors in Fig. 4.1.

| Node  | $\begin{array}{c} \mathbf{V_{node}} \\ (V) \end{array}$ | $\begin{array}{c} {\bf Capacitance \ / \ Capacitor} \\ (nF) \end{array}$ | # Caps | Total Capacitance<br>(nF) |

|-------|---------------------------------------------------------|--------------------------------------------------------------------------|--------|---------------------------|

| $C_1$ | 80                                                      | 1471                                                                     | 2      | 2942                      |

| $C_2$ | 160                                                     | 924                                                                      | 3      | 2772                      |

| $C_3$ | 240                                                     | 665                                                                      | 4      | 2660                      |

| $C_4$ | 320                                                     | 524                                                                      | 5      | 2622                      |

Table 4.3: Flying capacitor component detail using TDK 2.2  $\mu F$  450 V X6S capacitors in parallel.

Due to the expected losses of the main FCML power stage – over 4 W per device – custom heatsinks were designed for the power stage components. Simulations were done with SolidWorks thermal and flow simulation tools, as well as ANSYS, to calibrate heatsink performance (Fig 4.5). The FCML stage was expected to dissipate the most power, and therefore is designed and simulated with forced-air convection in mind. The unfolder / active rectifier stage was expected to dissipate minimal power, and so the heatsink designed for that stage assumes largely natural convection or incident but not forced airflow. Mechanical mounting holes and fixtures were designed concurrent to the PCB electrical design, to ensure that the devices could be heatsunk properly and not exceeding any mechanical stress limits. To stay within the manufacturer recommended pressure of 30 PSI per EPC GaN device [54], heatsink standoffs were milled to precise tolerances such that a gap filler material (Alphacool Eisschicht 17 W/mK, 1 mm thickness) would be compressed by ~ 15% when fully interfaced [46]. Furthermore, when attaching the heatsink to the converter, torque wrenches were used

to ensure that the heatsink was exerting the proper amount of force. Figure 4.6 shows the stackup of the thermal interfaces between the FCML GaN devices and heatsink. The unfolder stage utilizes GaN Systems GS66516T top-cooled GaN FETs, and has a similar stackup, though the devices are soldered directly to the main PCB, and so do not require a daughterboard PCB. The GaN Systems devices have a much larger surface area for cooling and a package construction that does not expose the bare die, and therefore are not as sensitive to pressure applied.

Figure 4.5: Solid Works Flow Simulation model with estimated temperature assuming 25  $^{\circ}\mathrm{C}$  ambient.

Figure 4.6: Diagram of stackup for heatsink interface. (Image created in collaboration with Kelly Fernandez)

Control of this converter is achieved with an Altera MAX10 series FPGA, which generates all of the interleaved complementary FCML PSPWM control signals with deadtime, as well as the unfolder / active rectifier H-bridge control signals. The PSPWM method combined with the 6-level FCML architecture achieves good natural flying capacitor voltage balancing [19], [50], [55]. To verify power stage operations, the system is run as an inverter, converting from 400 V<sub>dc</sub> to 240 V<sub>ac</sub>. The load is a reconfigurable resistor bank representing different power output levels. The board design also includes provisions for attaching further control systems, such as a microcontroller, to interface with the FPGA.

Figure 4.7: Power stage prototype.

### 4.4 Experimental Results

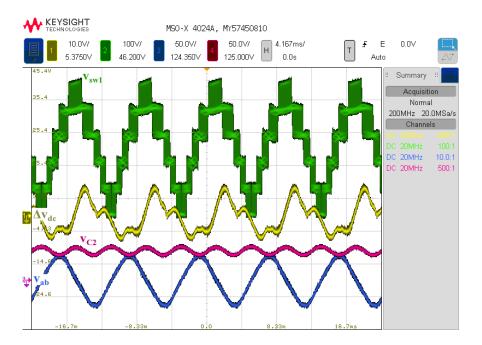

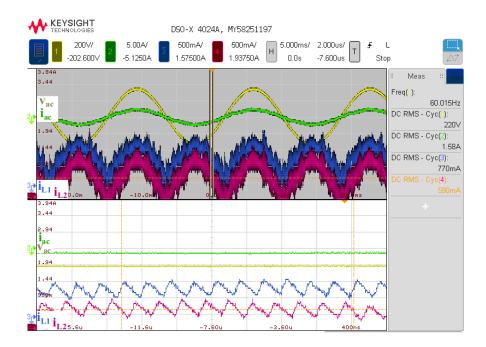

The full system (Fig. 4.7) has been tested to a power processing capability of 7 kW, converting from 400  $V_{dc}$  to 240  $V_{ac}$ . Table 4.4 details the performance of the converter as measured. The converter achieves a volumetric power stage density of 785  $W/in^3$  (47.9  $W/cm^3$ ) and a gravimetric power density of 24.6 kW/kg. Since the maximum height of the converter is dictated by the heatsinks and the inductors, and the component volume is much smaller than the volume bounded by the maximum component dimensions in each direction, the power density figure is calculated using the composite volume of a prism bounding the FCML stage, a prism bounding the inductors, and a prism bounding the unfolder stage, as shown in the side view of Fig. 4.8. Figure 4.9 shows the efficiency of the system as a function of output power, with liberal airflow ( $\sim 150$  CFM) and with heatsinks on the main power devices. Furthermore, Figure 4.10 is an estimated loss breakdown of the converter operating at full power (7 kW). Out of a total estimated 121 W of losses at full power, the FCML stage accounts for the bulk, about 71.5%, and the active rectifier / unfolder stage is about 15.9%. The inductors are about 8.1% while the PCB, gate drive, and control are about 4.5%. We note that the fan cooling solution is not included in the power density figure nor the loss breakdown, but also that the thermal management system may be adjusted to accommodate different operating conditions and environments. For this design, including the fan cooling losses may drop the maximum power efficiency by about  $0.1 \sim 0.2\%$ ; this can be optimized further or replaced with a completely different design. For example, a liquid cooling loop may be available and the design could be adjusted to accommodate such a system. The power stage efficiency was measured with a Keysight PA2201A Power Analyzer, and the efficiency plot accounts for all control and gate drive losses as measured through a Keysight E36312A supply; the full system achieves a peak efficiency of 98.9% at 3.3 kW and an efficiency of 98.3% at 7 kW. During testing, the heatsinks remained below 85 °C as measured by a FLIR T540 thermal camera, which is within the rated temperature of most commercially-available electronic parts.

Figure 4.8: Side view of converter prototype.

| Parameter                 | Value                                      | Notes                            |

|---------------------------|--------------------------------------------|----------------------------------|

| dc Voltage                | $400 V_{dc}$                               | Tested                           |

| ac Voltage                | $240 V_{ac}$                               | Tested                           |

| ac Current                | 29.8 A                                     | Tested                           |

| ac Power                  | 7 kW                                       | Tested                           |

| Efficiency                | 98.9%                                      | Peak Eff. (At $3.3 \text{ kW}$ ) |

|                           | 98.37%                                     | At 7 kW                          |

| THD                       | $\leq 0.3\%$                               | Measured at $7 \text{ kW}$       |

| Switching Frequency       | 144 kHz                                    | Per switch                       |

| Effective Frequency       | 720 kHz                                    | At inductor                      |