## Nanoelectromechanical Switch Design and Implementation in Back-End-of-Line Technology

Urmita Sikder

### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2022-20 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-20.html

May 1, 2022

Copyright © 2022, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Nanoelectromechanical Switch Design and Implementation in Back-End-of-Line Technology

by

Urmita Sikder

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering- Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Vladimir Stojanović Professor Junqiao Wu

Spring 2021

Nanoelectromechanical Switch Design and Implementation in Back-End-of-Line Technology

Copyright 2021 by Urmita Sikder

#### Abstract

Nanoelectromechanical Switch Design and Implementation in Back-End-of-Line Technology

by

Urmita Sikder

Doctor of Philosophy in Engineering- Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

The emergence of the Internet of Things (IoT) has made energy efficiency a key requirement for integrated electronic systems. Nanoelectromechanical (NEM) switches have the ideal characteristics of zero OFF-state leakage and small subthreshold swing, making them promising candidates for ultra-low-power digital computing applications. IoT has also motivated the development of new computing architectures that are more energy-efficient than the classic von Neumann architecture. An "in-memory computing" architecture avoids the need for data communication between separate processing and memory units, and hence achieves more energy-efficient operation. For such a computing architecture, it is desirable to have compact non-volatile (NV) memory cells that can be programmed and read with very low energy.

Utilization of back-end-of-line (BEOL) metallic interconnect layers to implement non-volatile NEM switches is an attractive approach for monolithic integration with CMOS transistors, which can enable enhanced chip functionality with relatively low incremental manufacturing cost. This dissertation addresses the fabrication challenges for realizing BEOL NEM switches and demonstrates their suitability for implementation of new computing architectures. Etch recipes and cleaning techniques are developed and optimized to successfully achieve BEOL NEM switches using standard 65 nm and 16 nm CMOS manufacturing processes, for the first time.

This dissertation also presents a new, vertically oriented NEM switch design implemented using multiple BEOL layers to achieve a more compact footprint. Design trade-offs are investigated, and design constraints for reliable and energy-efficient operation are discussed. A design optimization framework is presented to minimize the energy-delay product associated with the programming operation of a NEM switch.

Prototype reconfigurable hybrid CMOS-NEM circuits comprising arrays of BEOL NV-NEM switches are experimentally demonstrated for the first time, showing their promise for compact, energy-efficient and fast memory-based data searching and look-up table operation.

Scaling of NV-NEM switches to smaller dimensions is projected to lower their operating voltage, in order to be compatible with standard CMOS transistors, as well as to improve their energy-delay performance. The read/ write energy and read delay of the vertically oriented NV-NEM switch are projected to compare very favorably against the same performance parameters of other emerging embedded NV memory technologies. To Moomy

# Contents

| Co            | ontents                                                                                                                                                                                       | ii                                   |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Li            | st of Figures                                                                                                                                                                                 | iv                                   |

| $\mathbf{Li}$ | st of Tables                                                                                                                                                                                  | viii                                 |

| 1             | Introduction1.1IC Technology Advancement1.2NEM Switches for the Beyond CMOS Era1.3CMOS-NEM Hybrid Circuits1.4References                                                                       | . 4<br>. 10                          |

| 2             | BEOL NEM Switch Design2.1Introduction2.2Reconfigurable NV-NEM Switch Design2.3CMOS BEOL Layers for NEM Design2.4Lateral BEOL NEM Switches2.5Vertical BEOL NEM Switches2.6Summary2.7References | . 19<br>. 22<br>. 24<br>. 28<br>. 31 |

| 3             | Optimzation of BEOL NEM Switches3.1Introduction3.2Process Challenges3.3Release-Etch Process Optimization3.4Design Optimization3.5Summary3.6References                                         | . 37<br>. 39<br>. 44<br>. 52         |

| 4             | CMOS-NEM Hybrid Circuits         4.1       Introduction         4.2       Reconfigurable Circuits                                                                                             |                                      |

|          | $\begin{array}{c} 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \end{array}$ | Data Searching Operation with NV-NEM Array           | 57<br>60<br>63<br>64 |

|----------|---------------------------------------------------------|------------------------------------------------------|----------------------|

| <b>5</b> | Sca                                                     | ling Trend and Performance Analysis                  | 65                   |

|          | 5.1                                                     | Introduction                                         | 65                   |

|          | 5.2                                                     | BEOL Switch Design at Advanced CMOS Technology Nodes | 66                   |

|          | 5.3                                                     | Scaling Challenges                                   | 78                   |

|          | 5.4                                                     | Reliability and Endurance                            | 81                   |

|          | 5.5                                                     | Performance Benchmarking                             | 87                   |

|          | 5.6                                                     | Summary                                              | 88                   |

|          | 5.7                                                     | References                                           | 88                   |

| 6        | Cor                                                     | nclusion                                             | 94                   |

|          | 6.1                                                     | Contributions of This Work                           | 94                   |

|          | 6.2                                                     | Suggestions for Future Work                          | 95                   |

|          | 6.3                                                     | References                                           | 97                   |

iii

# List of Figures

| 1.1 | Evolution of CMOS technology over the years (adapted from [1, 2] showing the scaling trends of (a) gate length and minimum metal pitch (MMP). (b) Number of total transistors per unit area and density of Static Random Access Memory (SRAM) transistors, showing the density of transistors advancing by $2 \times$ on |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | average per generation.                                                                                                                                                                                                                                                                                                  | 2  |

| 1.2 | (a) Illustration of the switching current-voltage characteristics of an n-channel MOSFET for different threshold voltages; (b) dynamic, static, and total energy                                                                                                                                                         |    |

|     | consumption of a CMOS-based digital logic circuit. The lower limit for CMOS energy efficiency exists due to MOSFET OFF-state leakage (reproduced from [3]).                                                                                                                                                              | 3  |

| 1.3 | Schematic cross-section of a three-terminal electrostatic NEM switch (a) in non-<br>contacting OFF-state (b) in contacting ON-state, showing various forces exerted                                                                                                                                                      | 0  |

|     | on the movable beam.                                                                                                                                                                                                                                                                                                     | 6  |

| 1.4 | Schematic cross-section of a four terminal NEM logic switch (a) in OFF-state with higher drain-source resistance (b) in ON-state, with lower drain-source resistance.                                                                                                                                                    |    |

|     | (c) Typical switching current-voltage characteristics of a NEM logic for switch bidirectional voltage sweep.                                                                                                                                                                                                             | 7  |

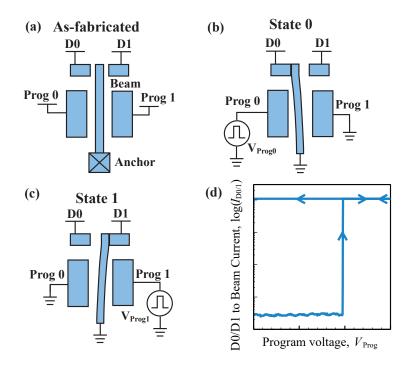

| 1.5 | Schematic of a non-volatile NEM memory cell (a) in as-fabricated neutral state<br>(b) programmed in state "0", and (c) reprogrammed to state "1."(d) Switching<br>current-voltage characteristics of a typical NV-NEM memory cell is shown for                                                                           | 1  |

|     | bidirectional voltage sweep.                                                                                                                                                                                                                                                                                             | 9  |

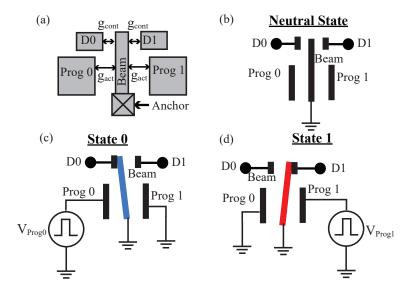

| 2.1 | Schematic illustrating (a) design parameters of a bistable NEM switch, (b) a NEM switch in neutral state, (c) programming operation to state "0", and (d)                                                                                                                                                                |    |

| 0.0 |                                                                                                                                                                                                                                                                                                                          | 19 |

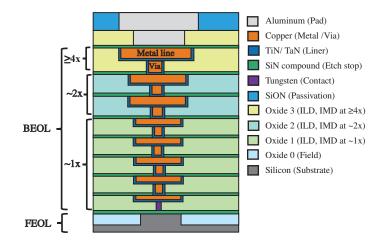

| 2.2 | Schematic cross-section illustrating BEOL metallic interconnect layers formed<br>in a standard CMOS IC manufacturing process, including metal and via layers,                                                                                                                                                            |    |

|     |                                                                                                                                                                                                                                                                                                                          | 22 |

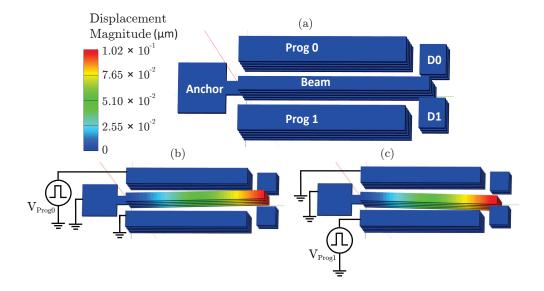

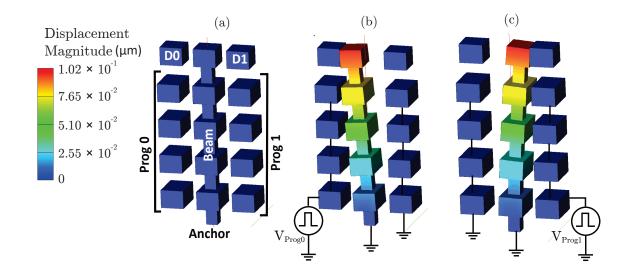

| 2.3 | Simulated lateral NEM switch: (a) as-fabricated, (b) in state "0", and (c) in state "1", modeled using MEMS+. The color scale indicates displacement due to                                                                                                                                                              |    |

|     | electrostatic actuation.                                                                                                                                                                                                                                                                                                 | 25 |

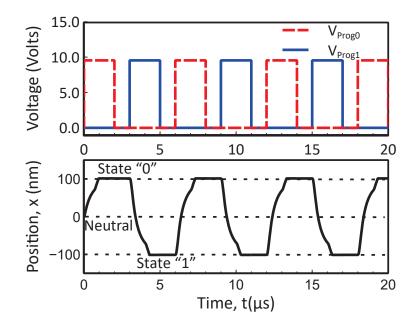

| 2.4 | Simulated transient response of a lateral NEM switch: program voltage wave-<br>forms and beam tip position <i>vs.</i> time showing non-volatile and reprogrammable                                  | 05       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.5 | characteristics                                                                                                                                                                                     | 25       |

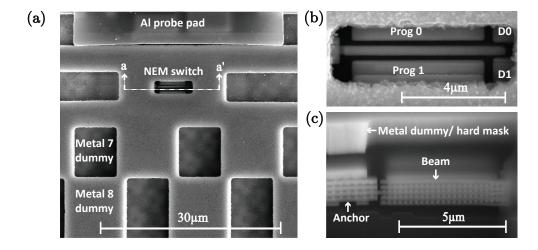

| 2.6 | etch process and (c) after isotropic etch process                                                                                                                                                   | 27       |

| 2.7 | sectional view along cutline a-a'<br>Simulated vertical NEM switch: (a) as-fabricated, (b) in state "0" and (c) in<br>state "1", modeled using MEMS+. The color scale indicates displacement due to | 27       |

| 2.8 | electrostatic actuation                                                                                                                                                                             | 29       |

| 2.9 | anisotropic release etch process                                                                                                                                                                    | 29<br>30 |

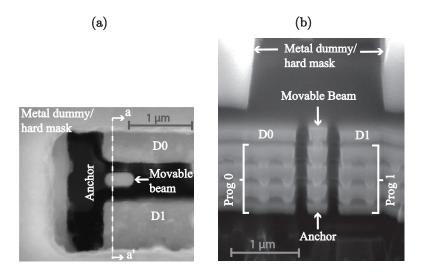

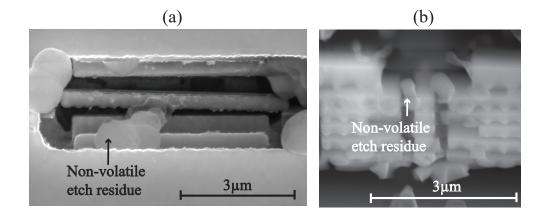

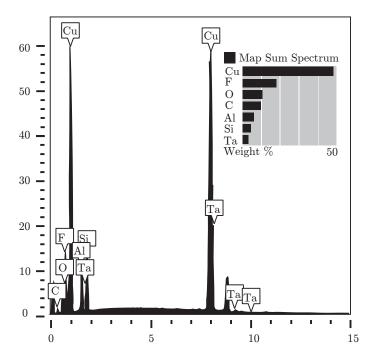

| 3.1 | (a) Planar and (b) cross-sectional SEM images of a fabricated lateral NEM switch<br>showing non-volatile etch residue resulting from exposure to anhydrous HF vapor                                 | 90       |

| 3.2 | and ethanol                                                                                                                                                                                         | 38       |

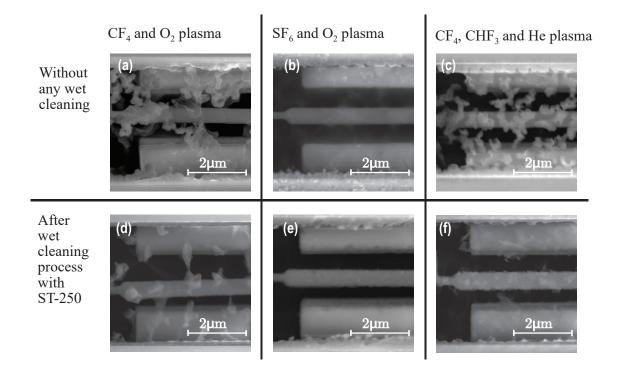

| 3.3 | plasma recipes                                                                                                                                                                                      | 39       |

| 3.4 | NEM switch after etch with $CF_4$ - $CHF_3$ -He CCP                                                                                                                                                 | 40       |

|     | section of a BEOL NEM switch after etch with CF <sub>4</sub> -CHF <sub>3</sub> -He CCP                                                                                                              | 41       |

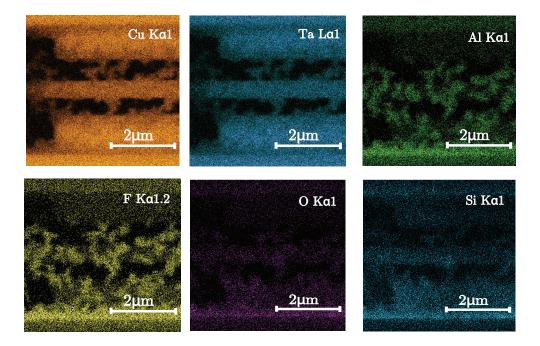

| 3.5 | (a) SEM image of a lateral BEOL NEM switch in as-fabricated neutral state after the release-etch process, (b) corresponding current vs. voltage characteris-                                        |          |

| 3.6 | tics showing programming to state "1" from state "0", and SEM images of the programmed switch in (c) state "0" and (d) state "1"                                                                    | 42<br>44 |

| 3.7 | (a) Schematic plan view and (b) 3D model of a laterally actuated NEM switch showing different dimensions.                                                                                           | 45       |

v

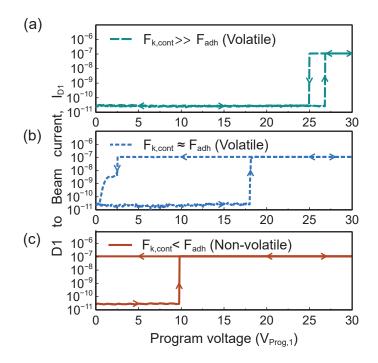

| 3.8  | Measured current vs. voltage characteristics for three different lateral BEOL<br>NEM switches showing volatile or non-volatile switching behavior                                                                                                                | 46       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

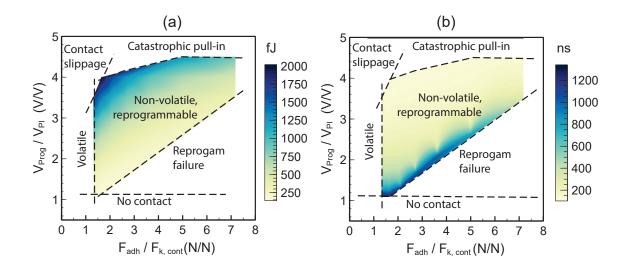

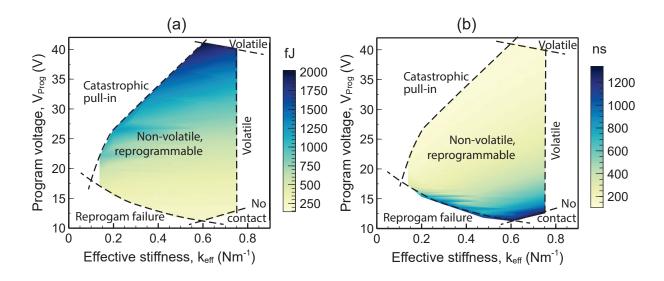

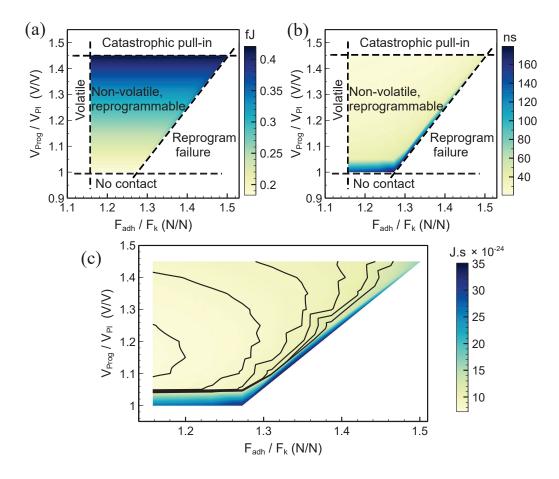

| 3.9  | Simulated (a) energy and (b) delay contour plots as functions of $V_{\text{Prog}}/V_{\text{PI}}$ and $F_{\text{adh}}/F_{\text{k, cont}}$ , showing various regions of operation delineated by the dashed lines.                                                  | 47       |

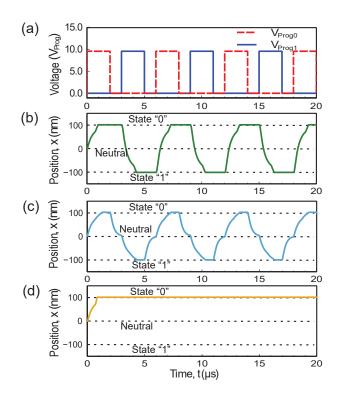

| 3.10 | Simulated transient response of lateral BEOL NEM switches showing (a) program voltage waveforms, and the corresponding position of the beam tip for (b) non-volatile and re-programmable operation, (c) volatile operation, and (d) reprogram                    | 10       |

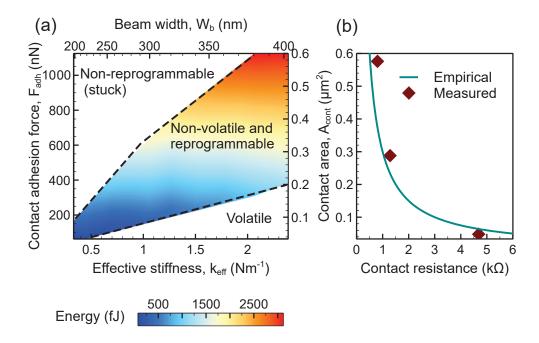

| 3.11 | failure                                                                                                                                                                                                                                                          | 48<br>49 |

| 3.12 | (a) Minimum reprogramming energy contour plot as a function of effective stiffness or beam width and contact adhesive force or contact area and (b) contact                                                                                                      |          |

| 3.13 | resistance $R_{\text{cont}}$ as a function of contact area [11]                                                                                                                                                                                                  | 50<br>51 |

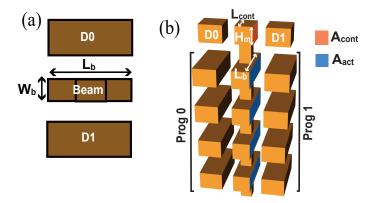

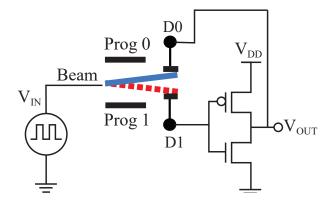

| 4.1  | Schematic diagram of a hybrid CMOS-NEM circuit consisting of a lateral NV-<br>NEM switch and a CMOS inverter.                                                                                                                                                    | 56       |

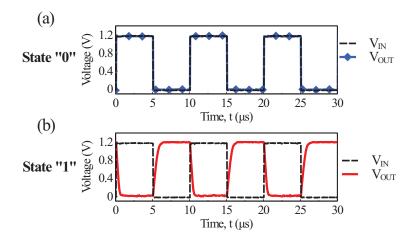

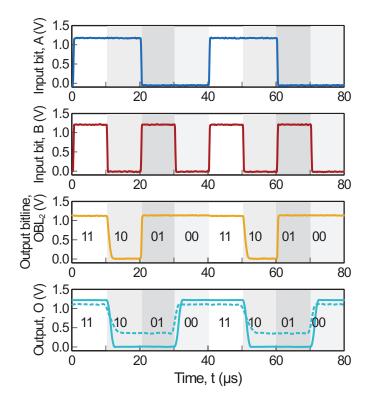

| 4.2  | Input and output voltage waveforms showing signal transmission in (a) state "0" and (b) state "1"                                                                                                                                                                | 57       |

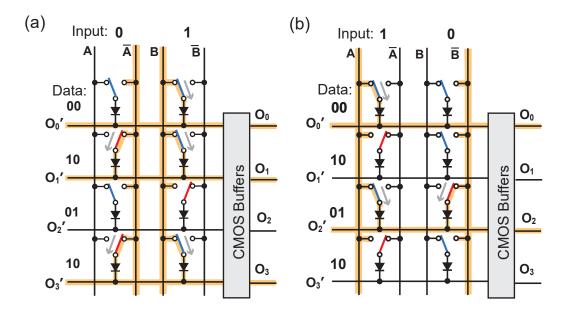

| 4.3  | <ul><li>(a) Circuit diagram of a lateral NV-NEM switch array for memory-based parallel data searching. Data string matching operations are shown for input string "01" and (b) input string "10". The highlighted lines show the wires that are driven</li></ul> | 58       |

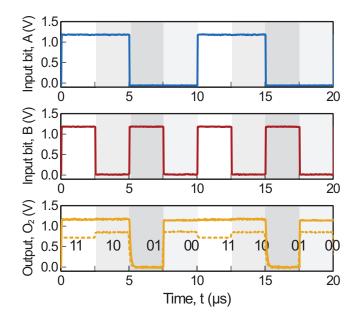

| 4.4  | to high voltage                                                                                                                                                                                                                                                  | 00       |

| 4.5  | CMOS buffer to line $O_2$ .)                                                                                                                                                                                                                                     | 59       |

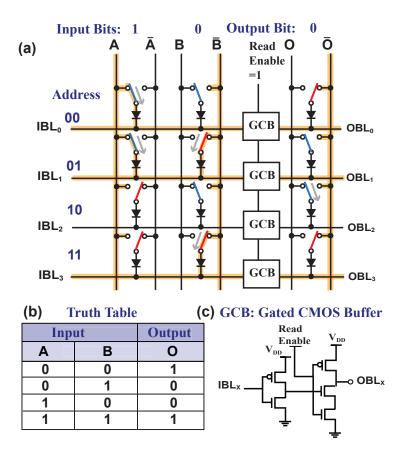

| 4.6  | readout. (b) Truth table for the LUT, and (c) the gated CMOS buffer used to discharge the output bit line, O                                                                                                                                                     | 61<br>63 |

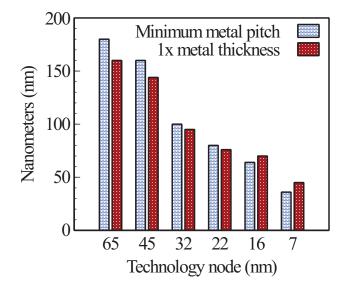

| 5.1  | Scaling trend of BEOL minimum metal pitch (MMP) and thickness of the 1x metal layer ( <i>i.e.</i> minimum pitch metal layer).                                                                                                                                    | 67       |

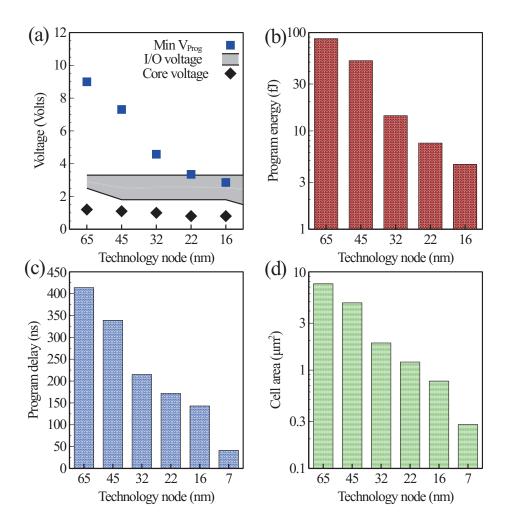

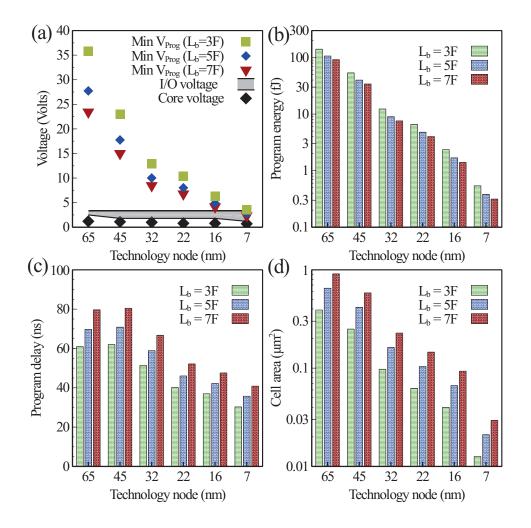

| 5.2   | Simulated values (using Coventor MEMS+) of (a) minimum programming voltage<br>of an optimized lateral NEM switch for different CMOS technology nodes, and          |     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | corresponding (b) minimum program energy, (c) mechanical program delay in high vacuum and (d) footprint of a cell.                                                 | 69  |

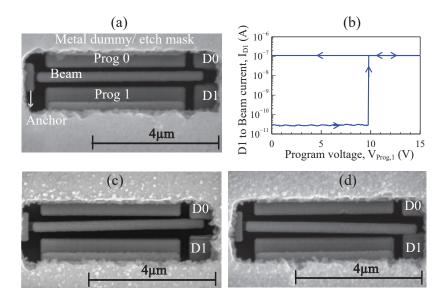

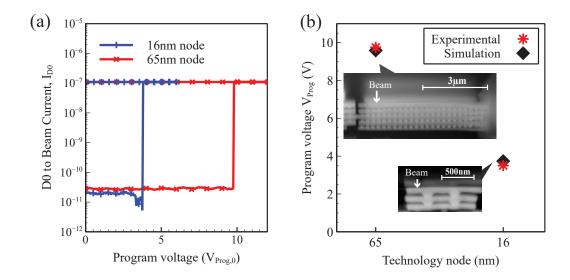

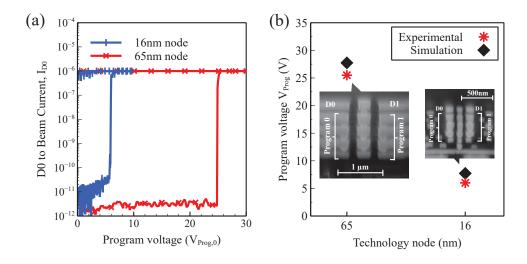

| 5.3   | (a) Quasi-static current-voltage characteristics of laterally actuated NV-NEM                                                                                      | 09  |

|       | switches programmed to state "0" from state "1", fabricated using 65 nm and                                                                                        |     |

|       | 16 nm process technologies. (b) Experimentally extracted program voltages are                                                                                      |     |

|       | compared to the simulated voltages for 65 nm and 16 nm NEM switches. Cross-                                                                                        |     |

| F 4   | sectional SEM images of the fabricated devices are shown in the insets.                                                                                            | 70  |

| 5.4   | Simulated values (using Coventor MEMS+) of (a) minimum programming voltage<br>of optimized vertical NEM switches with different lengths for various CMOS           |     |

|       | process technology nodes, and corresponding (b) minimum program energy, (c)                                                                                        |     |

|       | mechanical program delay in high vacuum and (d) cell footprint.                                                                                                    | 72  |

| 5.5   | Contour plots of (a) program energy, (b) mechanical program delay assuming                                                                                         |     |

|       | 7 nm process technology, showing various regions of operation delineated by the                                                                                    |     |

| FC    | dashed lines. (c) Contour showing the minimum energy-delay product                                                                                                 | 73  |

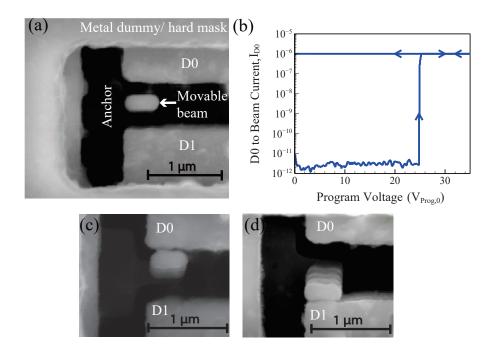

| 5.6   | (a) Quasi-static current-voltage characteristics of vertical NV-NEM switches pro-<br>grammed to state "0" from state "1", fabricated using 65 nm and 16 nm process |     |

|       | technologies. The currents through $D0/D1$ terminals are artificially limited to                                                                                   |     |

|       | 1µA to avoid contact degradation due to Joule heating. (b) Experimentally                                                                                          |     |

|       | extracted program voltages are compared to the simulated voltages for NEM                                                                                          |     |

|       | switches fabricated using 65 nm and 16 nm process technologies. Cross-sectional                                                                                    |     |

| 5 7   | SEM images of the fabricated devices are shown in the insets                                                                                                       | 75  |

| 5.7   | Measured input and output voltage waveforms showing signal transmission in<br>(a) state "0" and (b) state "1" for a reconfigurable circuit employing a vertical    |     |

|       | NV-NEM switch in 16nm process technology.                                                                                                                          | 76  |

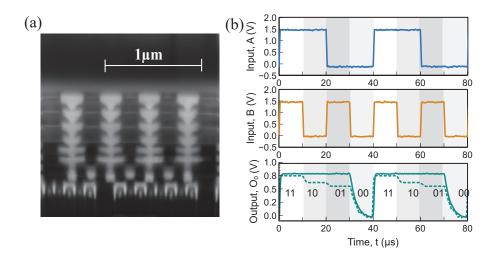

| 5.8   | (a) Cross-sectional SEM image showing a column in a $4 \times 2$ array of vertical                                                                                 |     |

|       | NEM switches fabricated using 16 nm process technology. (b) Measured input                                                                                         |     |

|       | and output voltage waveforms demonstrating data search operation using the                                                                                         |     |

|       | circuit in Fig. 4.3 at 16 nm node. Voltage waveform of output line $O_0$ goes low to show the presence of data string "00"                                         | 77  |

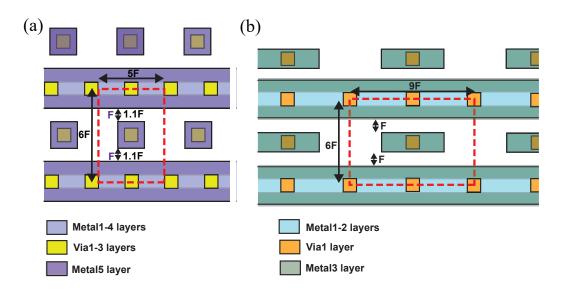

| 5.9   | to show the presence of data string "00"<br>Layout view showing the minimum NV-NEM switch cell size for (a) 65 nm tech-                                            | 11  |

| 0.0   | nology node and (b) 16 nm technology node                                                                                                                          | 81  |

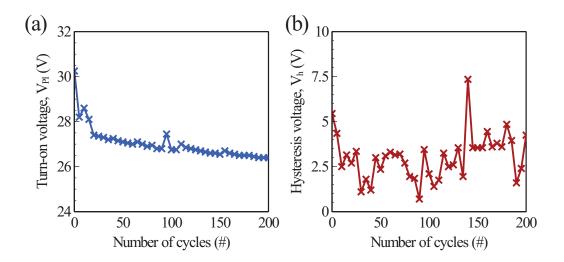

| 5.10  | Measured (a) pull-in voltage $V_{\rm PI}$ and (b) hysteresis voltage $V_{\rm H}$ as a function of the                                                              |     |

|       | number of ON/OFF switching cycles. The characteristics are obtained through                                                                                        |     |

|       | quasi-static current-voltage measurements of a volatile lateral NEM switch fab-                                                                                    | 0.0 |

| 5 1 1 | ricated using 65 nm process technology                                                                                                                             | 83  |

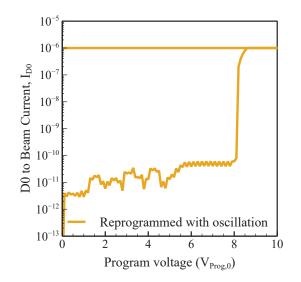

| 0.11  | vibrations of the movable beam                                                                                                                                     | 84  |

|       |                                                                                                                                                                    | ~ - |

# List of Tables

| 3.1 Optimized process for post-CMOS-fabrication release of lateral BEOL NEM |                                                                                                                                                           | 5. |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                             | The etch tool used for this process is a <i>Plasma-Therm PK-12 RIE</i>                                                                                    | 42 |

| 3.2                                                                         | Optimized process for post-CMOS-fabrication release of vertical BEOL NEM switches. The etch tool used for this process is a <i>Plasma-Therm PK-12 RIE</i> | 43 |

| 5.1                                                                         | Design parameters used in the simulation for Fig. 5.2. Here $F$ is the minimum                                                                            |    |

|                                                                             | metal half-pitch and $H_m$ is the thickness of M2 metal layer.                                                                                            | 68 |

| 5.2                                                                         | Design parameters used in the simulation for Fig. 5.4. Here $F$ is the minimum                                                                            |    |

|                                                                             | metal half-pitch.                                                                                                                                         | 71 |

| 5.3                                                                         | Effects of scaling. $\gamma$ , $\gamma_1$ , $\gamma_2$ are scaling constants which are greater than 1                                                     | 78 |

| 5.4                                                                         | Mechanical and electrical properties of metals and compounds compatible with                                                                              |    |

|                                                                             | BEOL metallization process $[2, 28-32]$                                                                                                                   | 85 |

| 5.5                                                                         | Performance benchmarking of vertical NEM switches against embedded non-                                                                                   |    |

|                                                                             | volatile memory technologies                                                                                                                              | 87 |

|                                                                             |                                                                                                                                                           |    |

#### Acknowledgments

First of all, I would like to express my sincere gratitude to my advisor, Prof. Tsu-Jae King Liu. It would not have been possible to navigate the difficulties of my PhD research project without her continuous guidance, encouragement and resourcefulness. I truly appreciate how she always managed time to discuss research problems or manuscripts and provide guidance on teaching, despite her very busy schedule. I would like to especially thank her for her optimistic outlook, even in difficult situations, and giving me hope.

I am indebted to all my contemporaries from King Group for helping me with measurements in the Device Characterization Lab, wafer processing in the Marvell Nanofabrication Lab and coming up with new ideas for research. I am especially thankful to Dr. Benjamin Osoba, Dr. Zhixin Alice Ye and Lars P. Tatum for successful collaborations. I am thankful to the former postdoctoral researchers Dr. Sergio F. Almeida, Dr. Kimihiko Kato and Dr. Alexis Peschot for their generous mentorship. I also appreciate all the life and career advice from Dr. Xi (Robin) Zhang and Dr. Sergio Almeida. I am also thankful to Tsegereda K. Esatu, Xiaoer Hu, Dr. Fei Ding, Dr. Chuang Qian, Dr. Peng Zheng, Dr. Jaeseok Jeon, Dr. Thomas Rembrandt, Dr. Daniel Connelly, Dr. Yi-Ting (Dennis) Wu, Dr. Yenhao (Philip) Chen, and Dr. I-Ru (Tim) Chen for many helpful discussions. Lastly, I would like to thank King Group members not only for being great colleagues, but also for being absolutely amazing friends - exploring food with Dr. Zhang, discussing anime with Dr. Osoba, and debating pros and cons of RV life with Dr. Ye will be some of my most fond memories from graduate school.

I thank Prof. Junqiao Wu and Prof. Vladimir Stojanović for serving on my dissertation committee and PhD qualification committee and providing me with constructive feedback and generous advice over the years. Dr. Alice Ye and I had the good fortune of having Prof. Stojanović as a mentor when we applied for Qualcomm Innovation Fellowship and I truly appreciate his immense help with our project proposal. I am thankful to Prof. Clark T.-C. Nguyen for not only serving on my PhD qualification committee, but also for teaching the courses on microfabrication and microelectromechanical (MEM) design, which provided the fundamental knowledge for this project. I worked closely with several members from Stojanović Group - Dr. Rawan Naous, Dr. Qichen Zhang, and Dr. Sajjad Moazeni - to design the devices for this work on multi-project wafers. I appreciate their help in guiding me through the *tape-out* process and troubleshooting various design problems. I also thank Dr. Bivas Saha and Dr. Sara Fathipour from Wu Group for many helpful discussions on device properties.

The 65 nm CMOS chips from this work were fabricated at Texas Instruments (TI), while the 16 nm chips were fabricated using MOSIS service in collaboration with Berkeley Wireless Research Center (BWRC). I am thankful to everyone from TI and BWRC, who aided me in accessing the multi-project wafer *shuttles* in order to design the circuits from this work. I am immensely grateful to Dr. Ting-Ta (Ernest) Yen from TI, whose help was pivotal to the completion of this work. A major part of this work was hinged upon accessing the wafer *shuttles* at TI Santa Clara, which would not have been possible without Dr. Yen's sponsorship and support.

I am very thankful for the fruitful collaborations with Dr. Louis Hutin, and Dr. Giulia Usai from CEA-Leti. I owe them for many useful discussions, brainstorming towards an optimized process and constructive input on my manuscripts. I would also like to thank Dr. Rebecca Mih for sharing her valuable expertise on cleanroom processes and her vision on the big picture.

This work was funded in part by NSF Center for Energy Efficient Electronics Science (E<sup>3</sup>S) under Award 0939514 and in part by the France-Berkeley Fund. I would like to thank the administrative team of E<sup>3</sup>S, especially Dr. Michael Bartl, Dr. Kedrick Perry, Lea Marlor, and Nicole McIntyre, for providing me with many opportunities for professional development. I would also like to thank Kelsey Horace-Herron, Emily Iwanski, and Mariana Martinez, who worked with me under E<sup>3</sup>S summer undergraduate research internship programs, for contributing to this work.

A large part of this work was done in Marvell Nanofabrication Laboratory (Nanolab). I

would like to express my gratitude to the entire Nanolab staff, especially Dr. Bill Flounders, Dr. Allison Dove, Dr. Joanna Bettinger, and Ryan Rivers, for helping me with understanding the tools, optimizing my processes and often accommodating special requests. I would also like to thank the Biomolecular Nanotechnology Center (BNC) staff, especially Dr. Naima Azgui, and AJ Gubser, for helping with the imaging required for this work. I am also greatly indebted to the EECS Director for Graduate Affairs, Shirley Salanio, and the Research Support Assistant, Charlotte Jones, for helping me on numerous occasions.

During my graduate studies, I got the opportunity to be a Graduate Student Instructor for an introductory Electrical Engineering undergraduate class, developed and taught by Prof. Gireeja Ranade. I experienced Prof. Ranade's relentless efforts towards creating a comfortable learning environment for the students and boosting the course staff morale. I would like to wholeheartedly thank her for the invaluable learning experience and also for giving me the opportunity to instruct the same class during the Summer session. I very much appreciate my co-instructors- Grace Kuo, and Panagiotis Zarkos- for the genuine camaraderie and their utmost dedication towards the students.

I am grateful to two of my best friends, Dr. Mohammad Asif Zaman, and Dr. Naznin Sultana, for being my sources of inspiration and motivating me to do my best. I would like to also thank Dr. Mahsa Sadeghi, Dr. Sifat Sharmin Muin, Dr. Yasser Khan, Dr. Asif Islam Khan, Nadia Nusrat, Sifat-E-Tanzim Chowdhury, Maruf Ahmed, Israt Jahan Eshita and Zunaid Omair, for their generosity and friendship; their company is what makes Berkeley a place I can call home. And last but not the least, I would like to express my heartfelt gratitude to my family members, especially my parents, who had been always there for me with their unwavering love and support.

## Chapter 1

## Introduction

## 1.1 IC Technology Advancement

### 1.1.1 CMOS Scaling

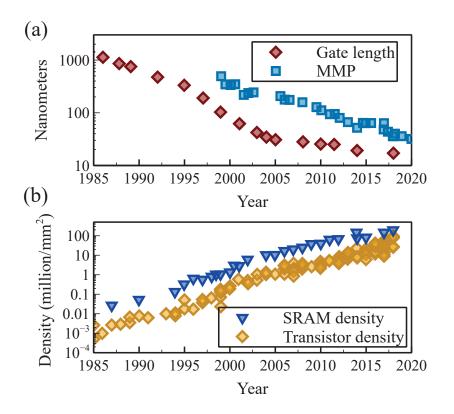

For the past several decades, technology advancement in the semiconductor industry has been driven by Moore's Law. Complementary metal-oxide-semiconductor (CMOS) transistors have been scaled down in dimensions to enable doubling of the number of transistors in the most advanced integrated circuit (IC) chip every two years. This aggressive pace of technology advancement, illustrated in Fig. 1.1, has provided for exponential pace of improvement in computational speed while reducing the cost and energy consumed per function.

Reductions in CMOS digital IC operating voltage  $(V_{\rm DD})$  have not kept pace with miniaturization of transistor dimensions since the 90 nm technology node, however. The sluggish scaling of  $V_{\rm DD}$  poses a fundamental challenge because of limitations in chip cooling technology that limit the maximum chip power density. The dynamic power consumption of a CMOS IC is proportional to  $V_{\rm DD}^2$ ; so reduction in  $V_{\rm DD}$  is desirable for improving energy efficiency. Ideally the gate overdrive voltage  $V_{\rm DD}$ - $V_{\rm TH}$  (where  $V_{\rm TH}$  is the transistor threshold voltage) should be maintained with  $V_{\rm DD}$  scaling, in order to maintain high transistor ON-

Figure 1.1: Evolution of CMOS technology over the years (adapted from [1, 2] showing the scaling trends of (a) gate length and minimum metal pitch (MMP). (b) Number of total transistors per unit area and density of Static Random Access Memory (SRAM) transistors, showing the density of transistors advancing by  $2 \times$  on average per generation.

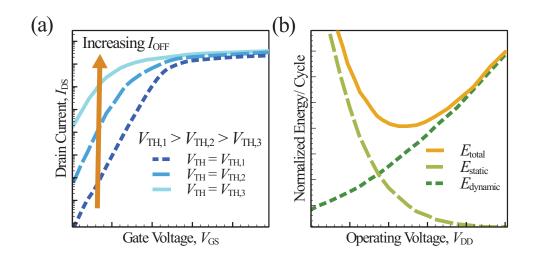

state current  $(I_{\rm ON})$  for fast circuit operation. This means that  $V_{\rm TH}$  should be reduced along with  $V_{\rm DD}$ . However, the OFF-state leakage current  $(I_{\rm OFF})$  increases exponentially with the reduction of  $V_{\rm TH}$ , as shown in the drain current  $(I_{\rm DS})$  vs. gate voltage  $(V_{\rm GS})$  characteristics in Fig. 1.2 (a):

$$I_{\rm OFF} \propto \exp(-V_{\rm TH}/SS),$$

(1.1)

where SS is the subthreshold swing, which is the inverse of the slope of the log( $I_{\rm DS}$ ) vs.  $V_{\rm GS}$  curve in the subthreshold region of operation. Increased  $I_{\rm OFF}$  is undesirable, because it results in increased static power consumption in CMOS ICs. Therefore a trade-off exists between dynamic power consumption and static power consumption for CMOS digital ICs,

Figure 1.2: (a) Illustration of the switching current-voltage characteristics of an n-channel MOSFET for different threshold voltages; (b) dynamic, static, and total energy consumption of a CMOS-based digital logic circuit. The lower limit for CMOS energy efficiency exists due to MOSFET OFF-state leakage (reproduced from [3]).

which is illustrated in Fig. 1.2 (b). The total energy consumed per digital operation is minimized when  $V_{\text{DD}}$  is reduced to  $V_{\text{TH}}$ .

For a fixed value of  $I_{\text{OFF}}$ ,  $V_{\text{TH}}$  can be decreased to facilitate  $V_{\text{DD}}$  scaling if SS can be reduced, *i.e.*, if the transistor switches ON/OFF more steeply with changing gate voltage. The fundamental lower limit of SS for CMOS devices is 60 mV/dec at room temperature, which is not practically achievable with planar CMOS transistor structures for very short (sub-25 nm) gate lengths. This led to the adoption of the three-dimensional (3D) FinFET structure for improved gate control (hence steeper SS), beginning at the 22 nm technology node. The 2017 edition of International Roadmap for Devices and Systems (IRDS) predicted FinFET to be a viable candidate for high-performance digital logic applications until technology scaling diminishes the fin width to practical limits [4]. The 2020 edition of the IRDS anticipates a transition to gate-all-around (GAA) transistor structures around 2025, for improved gate control at sub-10 nm gate lengths [5]. As transistor miniaturization approaches ultimate limits, the adoption of *Beyond CMOS* technologies will be needed to achieve further improvements in chip functionality and energy efficiency.

#### 1.1.2 Beyond CMOS Scaling

The emergence of the Internet of Things (IoT) has driven *Beyond CMOS* technological innovations, as more steeply switching devices and new computing architectures are needed to improve information processing speed and energy efficiency beyond the limits of CMOS technology. Spin-FETs, negative capacitance FETs (NCFETs), nano-electro-mechanical (NEM) switches and 2D topological insulator devices are emerging alternative switching devices for ultra-low-voltage digital computation. Neuromorphic computing architectures and quantum computing using alternative digital/multi-level/entangled state variables potentially offer performance advantages over the conventional von Neumann computing architecture, for specific applications.

Monolithic integration of emerging new devices with CMOS circuitry enables implementation of hybrid circuits that can achieve functionality and energy efficiency beyond the limits of CMOS technology. A major technological challenge is the development of nanometerscale non-volatile (NV) memory devices that can be monolithically integrated (*i.e.*, embedded) with CMOS circuitry. Phase-change RAM (PCRAM), resistive RAM (ReRAM), spin-transfer torque magnetic RAM (STT-MRAM), ferroelectric RAM (FeRAM) and novel selector devices have shown promise in overcoming this challenge.

### 1.2 NEM Switches for the Beyond CMOS Era

The operating principle of a micro/nano-electromechanical (M/NEM) switch is the making and breaking of mechanical contact between two conductive electrodes. After the demonstration of the first MEM relay in 1979 [6], electro-mechanical switches of different actuation mechanisms have been demonstrated; these include electrostatic, electrothermal, magnetic and piezoelectric switches/relays. Electrothermal relays employ pre-buckled beams or cantilevers comprising a bi-layer stack of materials with different thermal expansion coefficients that result in bending under the effect of heating [7–9]. Their switching speed is usually slow (milliseconds) and their switching energy is high due to the current required for Joule heating. Recently, a non-volatile Phase Change NEM Relay (PCNR) was proposed based on the mechanical expansion of a heated phase change material [10]. Magnetic relays use ferromagnetic materials in the movable electrode to actuate it with the application of a magnetic field. Piezoelectric switches use an electric field to physically deform a piezoelectric material. A beam constructed of a stack of ultra-thin piezoelectric AlN layers sandwiched between two metallic electrodes was demonstrated to actuate with  $520 \,\mathrm{mV}$ ; the actuation voltage was decreased to as low as  $10 \,\mathrm{mV}$  with a body bias voltage applied [11–14]. However, the footprint of a piezoelectric relay is comparatively large. Electrostatic M/NEM switches functioning as digital logic devices or non-volatile reconfigurable interconnects have been reported in the literature. Digital logic NEM switches have been demonstrated to switch with sub-1 V voltage signals [15-17], while reconfigurable interconnects have been shown to operate with CMOS-compatible operating voltage [18]. Electrostatic MEM relays can operate reliably across a wide temperature range  $(-150 \,^{\circ}\text{C} \text{ to } 300 \,^{\circ}\text{C})$  [19]. They also have been demonstrated to operate with sub-25 mV signals at temperatures below 100 K [20].

#### **1.2.1** Electrostatically Actuated NEM Switch

In a NEM switch the conducting electrodes are separated physically by an air gap in the OFF-state; hence no current flows between them, resulting in zero OFF-state leakage current. Switching between OFF-state and ON-state occurs abruptly, *i.e.*, the effective subthreshold swing is very small. These properties enable NEM switch based digital ICs to be operated with very low  $V_{\rm DD}$ . The prospect of improved energy efficiency has renewed interest in mechanical switches for logic and memory applications [21–23].

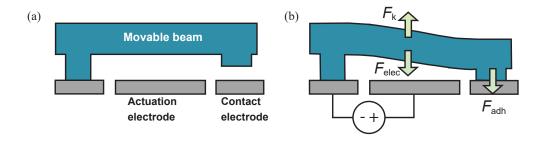

The simplest form of an electrostatic NEM switch has three terminals, consisting of a movable cantilever beam, a fixed actuation electrode and a fixed contact electrode (as

Figure 1.3: Schematic cross-section of a three-terminal electrostatic NEM switch (a) in noncontacting OFF-state (b) in contacting ON-state, showing various forces exerted on the movable beam.

illustrated in Fig. 1.3). In the OFF-state (Fig. 1.3(a)), an air gap exists between the tip of the cantilever beam and the contact electrode, preventing any current flow, if a voltage difference exists between them. If a voltage is applied between the fixed actuation electrode and the cantilever beam, an electrostatic force ( $F_{\rm elec}$ ) is exerted on the beam towards the direction of the fixed electrode. When the applied voltage exceeds a certain threshold, the electrostatic force becomes large enough to pull the tip of the cantilever into contact with the contact electrode (Fig. 1.3(b)). The physical contact between the contact electrode and the cantilever allows current to flow, if a voltage difference is applied across them. The sharp turn-on characteristics *i.e.*, the steep subthreshold slope, potentially enables low-voltage operation without the penalty of higher static power consumption.

Meanwhile, the displacement of the beam from its equilibrium position produces a spring restoring force  $(F_k)$  opposing the electrostatic force  $(F_{elec})$ , which has a magnitude governed by Hooke's Law:

$$F_{\mathbf{k}} = kx,\tag{1.2}$$

where k is the spring stiffness of the beam and x is the displacement of the beam from its original position. When the beam and contact electrode are in physical contact, adhesive force ( $F_{adh}$ ) exists between the contacting surfaces, which acts against breaking the contact. The adhesive force is due to a combination of Van der Waals force, electrostatic force, and chemical bonding at the material surfaces [24]; therefore the magnitude of the adhesive force depends on the contact materials and contact area.

When the actuation voltage is removed after contact is established, the relation between  $F_{\rm k}$  and  $F_{\rm adh}$  determines whether the contact breaks or not. If  $F_{\rm k} < F_{\rm adh}$ , contact is maintained when  $F_{\rm elec}$  goes to zero; this results in a non-volatile switch that can be leveraged to implement non-volatile memory, reconfigurable interconnects or sticky logic [18, 25–27]. Conversely, if  $F_{\rm k} > F_{\rm adh}$ , contact is broken when the actuation voltage goes to zero; this results in a volatile switch that can be used for digital computing and power gating [28–32].

#### **1.2.1.1** Electrostatic NEM Logic Switches

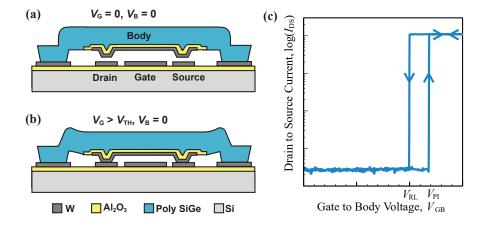

In a digital logic circuit, the voltages applied to the conductive electrodes are not fixed; therefore it is not desirable to have the state of a NEM switch be dependent on these applied voltages. A NEM logic switch, comprising four terminals: gate, body, drain and source, can solve this issue [29, 33]. Fig. 1.4(a) shows the schematic cross-section of a four-terminal logic switch with a poly-SiGe movable electrode structure. The movable structure is referred to as the body, while the underlying fixed electrode is referred to as the gate. A voltage

Figure 1.4: Schematic cross-section of a four terminal NEM logic switch (a) in OFF-state with higher drain-source resistance (b) in ON-state, with lower drain-source resistance. (c) Typical switching current-voltage characteristics of a NEM logic for switch bidirectional voltage sweep.

difference between the gate and body terminals ( $V_{\rm GB} = V_{\rm G} - V_{\rm B}$ ) generates electrostatic force ( $F_{\rm elec}$ ) attracting the body towards the gate. A conductive strip of metal, which functions as the "channel," is physically attached to the movable body with an intermediary dielectric insulating layer (Al<sub>2</sub>O<sub>3</sub> for this example). The drain and source terminals are physically separated in non-contacting OFF-state, as shown in Fig. 1.4(a), leading to zero drain-source current  $I_{\rm DS}$ . If  $V_{\rm GB}$  exceeds a certain threshold called the pull-in voltage ( $V_{\rm PI}$ ), a path for current flow is established between the drain and source terminals through the channel strip, as shown in Fig. 1.4(b). Hence current  $I_{\rm DS}$  can flow between these terminals, if a non-zero drain-to-source voltage ( $V_{\rm DS}$ ) is applied. When  $V_{\rm GB}$  is reduced below a certain level such that  $F_{\rm k} > F_{\rm elec} + F_{\rm adh}$ , the physical contacts between the channel and the source/drain terminals will break and  $I_{\rm DS}$  will drop to zero. This voltage is called the release voltage ( $V_{\rm RL}$ ). Due to the existence of  $F_{\rm adh}$  between the contacting surfaces,  $V_{\rm RL}$  is always smaller than  $V_{\rm PI}$ . The difference between these two voltages is called the hysteresis voltage:

$$V_{\rm H} = V_{\rm PI} - V_{\rm RL}.\tag{1.3}$$

Fig. 1.4(c) illustrates a typical current-voltage characteristics for a four-terminal logic switch, labelling the pull-in and release voltages. A negative bias voltage can be applied to the body to reduce the value of  $V_{\rm G}$  required and hence the switching energy required to operate a logic NEM relay [34, 35]. If  $V_{\rm B} = -V_{\rm RL}$ , the logic switch can be turned ON and OFF by varying  $V_{\rm G}$  between 0 Volt and  $V_{\rm H}$ .

#### 1.2.1.2 Electrostatic NEM Non-Volatile Memory Devices

A non-volatile NEM switch can be achieved by tailoring the geometry of the movable structure so that the spring restoring force in the contacting state is lower than the contact adhesive force. The basic structure and operation of a NEM memory cell is illustrated in Fig. 1.5. The single-pole-double-throw (SPDT) design comprising two opposing actuation electrodes ensures reprogrammability. The cell consists of five terminals: a movable cantilever beam, two actuation/ *program* electrodes (Program 0 and Program 1) and two

Figure 1.5: Schematic of a non-volatile NEM memory cell (a) in as-fabricated neutral state (b) programmed in state "0", and (c) reprogrammed to state "1."(d) Switching current-voltage characteristics of a typical NV-NEM memory cell is shown for bidirectional voltage sweep.

conducting/data electrodes (D0 and D1). In the as-fabricated neutral state (Fig. 1.5(a)), the free tip of the cantilever beam does not contact either of the two data electrodes. The cell can be programmed into state "0" or "1" by applying a voltage pulse to the Program 0 or Program 1 electrode, respectively. To program the cell into state "0," a voltage higher than  $V_{\rm PI}$  is applied to Program 0, to establish contact between the tip of the beam and D0 electrode (Fig. 1.5(b)). Since the cantilever beam spring restoring force satisfies the condition for non-volatility, the contact does not break when the applied voltage is dropped to zero. In order to change the programmed state of the memory cell, a voltage must be applied to the opposite program electrode. The condition for reprogrammability dictates that the program voltage should generate enough electrostatic force so that the combination of the electrostatic force and spring restoring force can overcome the contact adhesive force. For this example, the voltage applied to the Program 1 electrode will cause the tip of the beam to break contact with D0 and bring it into contact with D1 (Fig. 1.5(c)). Reprogramming to a non-volatile contacting state results in the typical current-voltage characteristics illustrated in Fig. 1.5(d).

### **1.3 CMOS-NEM Hybrid Circuits**

Hybrid CMOS-NEM technologies have been demonstrated for CMOS power gating [32], field programmable gate arrays (FPGAs) [36], reconfigurable logic circuits [37] and energy-efficient look-up tables (LUTs) [26].

The negligibly low OFF-state leakage of M/NEM switches makes them attractive for usage as power gates, which can reduce the total energy consumption of a chip. M/NEM switches acting as power-gates for CMOS circuitry have been reported in the literature: Fariborzi *et al.* demonstrated power-gating of a functional CMOS chip with 4-terminal MEM logic relays [32]. Henry *et al.* compared the effectiveness of CMOS and NEM switch power gates for different power-gating schemes [31].

Dadgour *et al.* proposed hybrid NEM/CMOS dynamic-OR gates, placing NEM switches in the pull-down network in order to reduce the leakage current [38, 39]. A hybrid NEMS/CMOS SRAM cell was also proposed by them, replacing the NMOS pull-down transistors and the PMOS pull-up transistors with their NEM switch counterparts. Chong *et al.* also proposed a NEM/CMOS hybrid SRAM cell architecture with NEM relays replacing only the pull-down NMOSFETs, predicting considerable increase in the hold and read static noise margins of SRAM cells [40].

A new FPGA architecture utilizing NEM logic relays for programmable routing was proposed by Chen *et al.* [36]. Specifically, the hysteretic switching behavior of NEM switches was leveraged to replace a FPGA routing switch and the corresponding routing SRAM cell entirely with a single NEM relay. The simulation results predicted 28% reduction in critical path delay, 37% reduction in leakage power and 43.6% reduction in area compared to a CMOS-only FPGA at the 22 nm technology node. Sirigir *et al.* predicted similar improvements at the 180 nm node [41].

Xu *et al.* proposed leveraging multiple back-end-of-line (BEOL) metallic layers for fabricating compact NEM switches in a standard CMOS process [25]. Additionally, hybrid CMOS/BEOL-NEMS circuits were proposed for a digital logic buffer, a non-volatile SRAM cell and a Content Addressable Memory (CAM) cell. A new hybrid CMOS-NEM neuron circuit was reported by Moradi *et al.* for mixed-signal neuromorphic computing, and was predicted to be 35% more energy-efficient than existing CMOS designs.

Kato *et al.* proposed fast and energy-efficient parallel data searching operation for processing of large data sets based on non-volatile NEM switches [27]. Additionally, energy efficient look-up tables (LUTs) implemented with arrays of BEOL NEM switches were proposed by Kato *et al.* [26]. Choi and Kim experimentally demonstrated 3D CMOS-NEM hybrid reconfigurable circuits for the first time by utilizing the BEOL metallic layers in a standard CMOS process to fabricate non-volatile NEM routing switches over CMOS logic circuits [42]. Kwon *et al.* demonstrated operation of similar hybrid reconfigurable circuits at a CMOS compatible operating voltage of 1.2 V [18]. Recently Kwon *et al.* have demonstrated island-style CMOS–NEM reconfigurable logic circuit blocks and proposed monolithically integrated switch blocks and connection blocks implemented with BEOL NEM switches for fast and energy-efficient FPGAs [37].

#### 1.3.1 Dissertation Overview

This dissertation focuses on implementation of NEM switches with standard CMOS fabrication processes using multiple BEOL metallic interconnect layers, and their application in hybrid CMOS-NEM circuits. A large part of the research work involves process development and optimization to fabricate multi-layered NEM switches with high manufacturing yield. The other part is devoted to optimizing the design of BEOL NEM switches for lowvoltage operation and to demonstrating hybrid CMOS-NEM circuits. The remainder of this dissertation is organized as follows.

Chapter 2 describes the geometry and operating principles of BEOL NEM switches. Different topologies of the BEOL switch are also introduced. Chapter 3 discusses the challenges associated with the BEOL NEM switch fabrication process and presents solutions. A design optimization methodology is presented to achieve device functionality and meet design specifications. Chapter 4 covers the experimental demonstration and characterization of hybrid CMOS-NEM circuits for different applications. NEM switches fabricated together with CMOS circuitry using a standard 65 nm manufacturing process are utilized to demonstrate reconfigurable logic circuits, specifically a parallel data searching circuit and a reconfigurable LUT.

Chapter 5 discusses the benefits of technology scaling on various BEOL NEM switch performance parameters. Experimental results for BEOL NEM switches fabricated using a standard 16 nm manufacturing process are presented. Scaling challenges are also outlined, including the impact of scaling on contact resistance and contact adhesive force. The chapter also considers the impact of technology scaling trends for BEOL NEM switches. BEOL NEM switches are benchmarked against other embedded non-volatile memory devices in terms of read/write delay and energy. Chapter 6 summarizes the key findings and contributions of this dissertation. Suggestions for future work are also presented in this chapter.

### 1.4 References

- M. L. Rieger, "Retrospective on VLSI value scaling and lithography," Journal of Micro/Nanolithography, MEMS, and MOEMS, vol. 18, no. 4, p. 040902, 2019.

- [2] S. B. Samavedam, J. Ryckaert, E. Beyne, E. Ronse, N. Horiguchi, Z. Tokei, I. Radu, M. G. Bardon, A. Spessot, M. H. Na, and J. Biesemans, "Future logic scaling: Towards atomic channels and deconstructed chips," in 2020 IEEE International Electron Devices Meeting (IEDM). IEEE, 2020, pp. 1.1.1–1.1.10.

- [3] I.-R. Chen, "Novel material integration for reliable and energy-efficient NEM relay technology," Ph.D. dissertation, UC Berkeley, 2014.

- [4] 2017. [Online]. Available: https://irds.ieee.org/editions/2017/executive-summary

- [5] 2020. [Online]. Available: https://irds.ieee.org/editions/2020/executive-summary

- [6] K. Petersen, "Micromechanical membrane switches on silicon," *IBM Journal of Research and Development*, vol. 23, no. 4, pp. 376–385, 1979.

- W. Riethmuller and W. Benecke, "Thermally excited silicon microactuators," *IEEE Transactions on Electron Devices*, vol. 35, no. 6, pp. 758–763, 1988.

- [8] J. Qui, J. H. Lang, A. H. Slocum, and R. Strumpler, "A high-current electrothermal bistable MEMS relay," in *The Sixteenth Annual International Conference on Micro Electro Mechanical Systems*, 2003. MEMS-03 Kyoto. IEEE, 2003, pp. 64–67.

- [9] Jin Qiu, J. H. Lang, A. H. Slocum, and A. C. Weber, "A bulk-micromachined bistable relay with U-shaped thermal actuators," *Journal of Microelectromechanical Systems*, vol. 14, no. 5, pp. 1099–1109, 2005.

- [10] J. T. Best, M. A. Masud, M. P. de Boer, and G. Piazza, "Phase change NEMS relay," in 2019 IEEE International Electron Devices Meeting (IEDM), 2019, pp. 34.1.1–34.1.4.

- [11] U. Zaghloul and G. Piazza, "10–25 nm piezoelectric nano-actuators and NEMS switches for millivolt computational logic," in 2013 IEEE 26th International Conference on Micro Electro Mechanical Systems (MEMS), 2013, pp. 233–236.

- [12] G. Piazza, "Aluminum nitride piezoelectric NEMS resonators and switches," in *Micro-and Nanotechnology Sensors, Systems, and Applications II*, vol. 7679. International Society for Optics and Photonics, 2010, p. 76791L.

- [13] J. Best and G. Piazza, "Electrostatic actuation of the pulse-activated piezo-NEMS shuttle relay," in 2018 IEEE Micro Electro Mechanical Systems (MEMS), 2018, pp. 638–641.

- [14] U. Zaghloul and G. Piazza, "Sub-1-volt piezoelectric nanoelectromechanical relays with millivolt switching capability," *IEEE Electron Device Letters*, vol. 35, no. 6, pp. 669–671, 2014.

- [15] J. O. Lee, Y.-H. Song, M.-W. Kim, M.-H. Kang, J.-S. Oh, H.-H. Yang, and J.-B. Yoon, "A sub-1-volt nanoelectromechanical switching device," *Nature nanotechnology*, vol. 8, no. 1, p. 36, 2013.

- [16] B. Osoba, B. Saha, L. Dougherty, J. Edgington, C. Qian, F. Niroui, J. H. Lang, V. Bulovic, J. Wu, and T.-J. K. Liu, "Sub-50 mV NEM relay operation enabled by self-assembled molecular coating," in 2016 IEEE International Electron Devices Meeting (IEDM). IEEE, 2016, pp. 26–8.

- [17] Z. Ye, S. Almeida, M. Rusch, A. Perlas, W. Zhang, U. Sikder, J. Jeon, V. Stojanović, and T.-J. Liu, "Demonstration of 50-mV digital integrated circuits with microelectromechanical relays," in 2018 IEEE International Electron Devices Meeting (IEDM). IEEE, 2018, pp. 4–1.

- [18] H. S. Kwon, S. K. Kim, and W. Y. Choi, "Monolithic three-dimensional 65-nm CMOSnanoelectromechanical reconfigurable logic for sub-1.2V operation," *IEEE Electron De*vice Letters, vol. 38, no. 9, pp. 1317–1320, 2017.

- [19] R. Gaddi, C. Schepens, C. Smith, C. Zambelli, A. Chimenton, and P. Olivo, "Reliability and performance characterization of a MEMS-based non-volatile switch," in 2011 International Reliability Physics Symposium. IEEE, 2011, pp. 2G–2.

- [20] X. Hu, S. F. Almeida, Z. A. Ye, and T.-J. K. Liu, "Ultra-low-voltage operation of MEM relays for cryogenic logic applications," in 2019 IEEE International Electron Devices Meeting (IEDM). IEEE, 2019, pp. 34–2.

- [21] O. Y. Loh and H. D. Espinosa, "Nanoelectromechanical contact switches," *Nature nan-otechnology*, vol. 7, no. 5, p. 283, 2012.

- [22] J. E. Jang, S. N. Cha, Y. J. Choi, D. J. Kang, T. P. Butler, D. G. Hasko, J. E. Jung, J. M. Kim, and G. A. Amaratunga, "Nanoscale memory cell based on a nanoelectromechanical switched capacitor," *Nature Nanotechnology*, vol. 3, no. 1, p. 26, 2008.

- [23] S. W. Lee, S. J. Park, E. E. Campbell, and Y. W. Park, "A fast and low-power microelectromechanical system-based non-volatile memory device," *Nature communications*, vol. 2, p. 220, 2011.

- [24] R. Maboudian and R. T. Howe, "Critical review: Adhesion in surface micromechanical structures," Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, vol. 15, no. 1, pp. 1–20, 1997.

- [25] N. Xu, J. Sun, I.-R. Chen, L. Hutin, Y. Chen, J. Fujiki, C. Qian, and T.-J. K. Liu, "Hybrid CMOS/BEOL-NEMS technology for ultra-low-power IC applications," in 2014 IEEE International Electron Devices Meeting. IEEE, 2014, pp. 28–8.

- [26] K. Kato, V. Stojanović, and T.-J. K. Liu, "Embedded nano-electro-mechanical memory for energy-efficient reconfigurable logic," *IEEE Electron Device Letters*, vol. 37, no. 12, pp. 1563–1565, 2016.

- [27] —, "Non-volatile nano-electro-mechanical memory for energy-efficient data searching," *IEEE Electron Device Letters*, vol. 37, no. 1, pp. 31–34, 2015.

- [28] M. Spencer, F. Chen, C. C. Wang, R. Nathanael, H. Fariborzi, A. Gupta, H. Kam, V. Pott, J. Jeon, T.-J. K. Liu *et al.*, "Demonstration of integrated micro-electromechanical relay circuits for VLSI applications," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 1, pp. 308–320, 2010.

- [29] V. Pott, H. Kam, R. Nathanael, J. Jeon, E. Alon, and T.-J. K. Liu, "Mechanical computing redux: Relays for integrated circuit applications," *Proceedings of the IEEE*, vol. 98, no. 12, pp. 2076–2094, 2010.

- [30] J. Fujiki, N. Xu, L. Hutin, I.-R. Chen, C. Qian, and T.-J. K. Liu, "Microelectromechanical relay and logic circuit design for zero crowbar current," *IEEE Transactions on Electron Devices*, vol. 61, no. 9, pp. 3296–3302, 2014.

- [31] M. B. Henry and L. Nazhandali, "NEMS-based functional unit power-gating: Design, analysis, and optimization," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 60, no. 2, pp. 290–302, 2012.

- [32] H. Fariborzi, M. Spencer, V. Karkare, J. Jeon, R. Nathanael, C. Wang, F. Chen, H. Kam, V. Pott, T.-J. K. Liu *et al.*, "Analysis and demonstration of MEM-relay power gating," in *IEEE Custom Integrated Circuits Conference 2010*. IEEE, 2010, pp. 1–4.

- [33] R. Nathanael, V. Pott, H. Kam, J. Jeon, and T.-J. K. Liu, "4-terminal relay technology for complementary logic," in 2009 IEEE International Electron Devices Meeting (IEDM). IEEE, 2009, pp. 1–4.

- [34] C. Qian, A. Peschot, D. J. Connelly, and T.-J. K. Liu, "Energy-delay performance optimization of NEM logic relay," in 2015 IEEE International Electron Devices Meeting (IEDM). IEEE, 2015, pp. 18–1.

- [35] C. Qian, A. Peschot, B. Osoba, Z. A. Ye, and T.-J. K. Liu, "Sub-100 mV computing with electro-mechanical relays," *IEEE Transactions on Electron Devices*, vol. 64, no. 3, pp. 1323–1329, 2017.

- [36] C. Chen, R. Parsa, N. Patil, S. Chong, K. Akarvardar, J. Provine, D. Lewis, J. Watt, R. T. Howe, H.-S. P. Wong *et al.*, "Efficient FPGAs using nanoelectromechanical relays," in *Proceedings of the 18th annual ACM/SIGDA international symposium on Field programmable gate arrays.* ACM, 2010, pp. 273–282.

- [37] H. S. Kwon, J. W. Ko, and W. Y. Choi, "Island-style monolithic three-dimensional CMOS-nanoelectromechanical logic circuits," *IEEE Electron Device Letters*, vol. 41, no. 8, pp. 1257–1260, 2020.

- [38] H. F. Dadgour and K. Banerjee, "Design and analysis of hybrid NEMS-CMOS circuits for ultra low-power applications," in *Proceedings of the 44th annual Design Automation Conference.* ACM, 2007, pp. 306–311.

- [39] —, "Hybrid NEMS-CMOS integrated circuits: a novel strategy for energy-efficient designs," *IET computers & digital techniques*, vol. 3, no. 6, pp. 593–608, 2009.

- [40] S. Chong, B. Lee, K. B. Parizi, J. Provine, S. Mitra, R. T. Howe, and H.-S. P. Wong, "Integration of nanoelectromechanical (NEM) relays with silicon CMOS with functional CMOS-NEM circuit," in 2011 International Electron Devices Meeting. IEEE, 2011, pp. 30–5.

- [41] V. K. Sirigir, K. Alzoubi, D. G. Saab, F. Kocan, and M. Tabib-Azar, "Ultra-low-power ultra-fast hybrid CNEMS-CMOS FPGA," in 2010 International Conference on Field Programmable Logic and Applications. IEEE, 2010, pp. 368–373.

- [42] W. Y. Choi and Y. J. Kim, "Three-dimensional integration of complementary metaloxide-semiconductor-nanoelectromechanical hybrid reconfigurable circuits," *IEEE Electron Device Letters*, vol. 36, no. 9, pp. 887–889, 2015.

## Chapter 2

## **BEOL NEM Switch Design**

## 2.1 Introduction

For Internet of Things (IoT) applications, energy efficiency is a key requirement. Nanoelectromechanical (NEM) switches are considered an attractive option for IoT applications due to their negligible OFF-state power consumption, non-volatile (NV) switching capability and abrupt switching characteristics [1–8]. As compared with resistive NV memory devices, NV-NEM switches offer a very large resistance ratio between programmed states. As a result, NEM switches can enable longer battery life for IoT devices, *e.g.*, used in wireless sensor networks. NEM devices used in conjunction with CMOS circuitry can provide for enhanced chip functionality and/or energy efficiency [9–15]. However, the larger footprint of NEM switches as compared with transistors, as well as the incremental cost of their integration with CMOS circuitry, pose a barrier for their adoption. Monolithic integration of NEM switches using a conventional state-of-the-art IC manufacturing process can enable compact NEM switches at low incremental cost. Specifically, the back-end-of-line metallic interconnect layers in a conventional CMOS process can be leveraged to implement NEM switches [6, 16–23].

In this chapter, the operating principle of a NEM switch is introduced in Section 2.2. Section 2.3 describes the the process of leveraging the back-end-of-line metallic layers to build NEM switches. Two different topologies of NEM switch, *i.e.* the lateral and the vertical switch designs are introduced in sections 2.4 and 2.5 respectively. Section 2.6 summarizes this chapter.

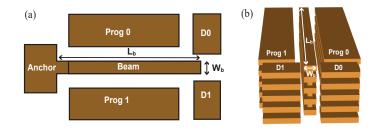

## 2.2 Reconfigurable NV-NEM Switch Design

A bistable single-pole-double-throw (SPDT) NEM switch can be programmed into either of two contacting states. The switch comprises five terminals:two fixed actuation/program electrodes (labeled "Prog0" or "Prog1") on either side of the movable beam, and two corresponding fixed contact/data (conducting) electrodes (labeled "D0" or "D1"). The movable beam can be modeled as a cantilever beam with a spring stiffness of  $k_{\text{eff}}$ . In an unprogrammed as-fabricated state, the beam stays in the neutral position without making any physical contact, as shown in Fig. 2.1(a). All the electrodes are separated physically by air gaps at this neutral OFF-state; so no current flows through the gaps at normal operating voltages, resulting in zero OFF-state leakage current.

Figure 2.1: Schematic illustrating (a) design parameters of a bistable NEM switch, (b) a NEM switch in neutral state, (c) programming operation to state "0", and (d) state "1".

The actuation electrodes Prog0/1 on either side of the beam can electrostatically actuate the beam into contact with either of the contacting electrodes D0/D1. When a program voltage  $V_{Prog0}$  is applied to electrode Prog0, an attractive electrostatic force  $F_{elec}$  is induced between the beam and Prog0.  $g_{0/1}$  is the size of the variable air gap between the beam and Prog0/1. Without an applied voltage, the switch is in neutral state (Fig. 2.1(b)) and the gap between the beam and either Prog0 or Prog1 is equal to the actuation gap size,  $g_{act}$ . In this state, the gap between the beam and either D0 or D1 is equal to the contact gap size,  $g_{cont}$ . With a voltage applied to Prog0/1, the electrostatic force exerted on the beam is given by

$$F_{\rm elec} = \frac{\epsilon_0 A_{\rm act} V_{\rm Prog0/1}^2}{2g_{0/1}^2},$$

(2.1)

where  $A_{\text{act}}$  is the effective actuation area,  $\epsilon_0$  is the vacuum permittivity. The electrostatic force is counteracted by the spring restoring force given by Hooke's law:

$$F_{\rm k} = k_{\rm eff} x = k_{\rm eff} (g_{\rm act} - g_{0/1}).$$

(2.2)

Here  $x = g_{act} - g_{0/1}$  is the displacement of the beam from the neutral position towards the program electrode with applied voltage. Hence the net force on the beam is given by

$$F_{\rm net} = F_{\rm elec} - F_{\rm k}.\tag{2.3}$$

When  $F_{\text{elec}} > F_{\text{k}}$ , the net force moves the movable beam towards the corresponding program electrode. As a result, the actuation gap shrinks below  $g_{\text{act}}$ . The decrease of actuation gap boosts  $F_{\text{elec}}$  and consequently  $F_{\text{net}}$ , which causes the gaps to shrink even further through a positive feedback effect. The minimum voltage required for  $F_{\text{elec}}$  to overcome  $F_k$ is called the pull-in voltage  $V_{\text{PI}}$ . If  $V_{\text{Prog0}} \geq V_{\text{PI}}$ , the beam tip actuates into contact with the corresponding contact electrode D0, which is denoted by state "0", as shown in Fig. 2.1(c). Alternatively, the NEM switch could have been programmed into state "1" by applying a voltage  $V_{\text{Prog1}}$  to electrode Prog1. The pull-in voltage  $V_{\text{PI}}$  can be minimized by maximizing the net force  $F_{\text{net}}$ , which can be done by either maximizing the actuation area  $A_{\text{act}}$  and/or reducing the actuation gap  $g_{\text{act}}$  and contact gap  $g_{\text{cont}}$ . When the beam comes in contact with the contact electrodes, contact adhesive force  $F_{adh}$ , which is a function of contact area, contact material and surface roughness, exists between the contacting surfaces, opposing the spring restoring force  $F_k$ . If  $F_k$  at the contacting position is larger than  $F_{adh}$ , when  $V_{Prog0/1}$  is reduced below  $V_{PI}$ , at a critical value of  $V_{Prog0/1} = V_{RL}$ ,  $F_k$  overcomes  $F_{elec} + F_{adh}$  and contact breaks, where  $V_{RL}$  is the release voltage. In this case, the switch is *volatile* and has a hysteresis voltage  $V_H$ , as described in the previous chapter. The switch is *non-volatile* when the spring restoring force  $F_k$  of the movable beam during contact, is designed to be lower than  $F_{adh}$ , *i. e.*

$$F_{\rm k}|_{x=g_{\rm cont}} = F_{\rm k,\ cont} = k_{\rm eff}g_{\rm cont} < F_{\rm adh}.$$

(2.4)

The non-volatile switch remains in the contacting position even when  $V_{\text{Prog}0/1}$  drops to zero. For  $V_{\text{Prog}0/1} = 0$  V, the net force on the beam at the contacting position towards the equilibrium position is given by

$$F_{\rm k,\ cont} - F_{\rm adh} = k_{\rm eff} g_{\rm cont} - F_{\rm adh} < 0.$$

(2.5)

To reprogram the switch, electrostatic force is required to make sure the net force towards the opposite contact is positive:

$$F_{\rm elec} + k_{\rm eff}g_{\rm cont} - F_{\rm adh} > 0 \tag{2.6}$$

It is to be noted that the spring restoring force assists the reprogramming process by pulling the beam towards the equilibrium position. Hence the voltage required to program the switch from state "0" to state "1" should satisfy the condition:

$$\frac{\epsilon_0 A_{\rm act} V_{\rm Prog1}^2}{2g_1^2} + k_{\rm eff} g_{\rm cont} > F_{\rm adh}.$$

(2.7)

Here  $g_1 > g_{act}$ , *i. e.* the gap between Prog1 and the movable beam at state "0" is larger than the as-fabricated value. Fig. 2.1(d) shows the reprogramming of the NEM switch from state "0" to state "1." The minimum  $V_{Prog}$  required to reprogram the switch from state "0/1" to state "1/0" is higher than the voltage required to program the switch from the neutral state. The non-volatile NEM switch can function as a reprogrammable non-volatile memory cell or a reconfigurable interconnect.

# 2.3 CMOS BEOL Layers for NEM Design

A CMOS IC manufacturing process can be broadly divided into two parts: front-end-ofline (FEOL) process and back-end-of-line (BEOL) process. The FEOL process forms the semiconductor devices, while the BEOL process forms the metallic wires interconnecting the semiconductor devices to determine chip functionality and to form input/output ports for the chip.

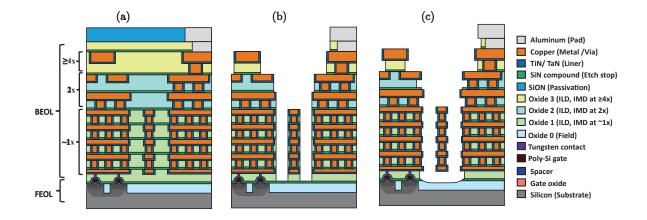

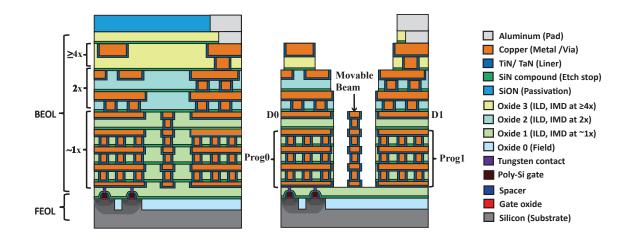

The BEOL material stack comprises layers of metallic wire and via features embedded in low-permittivity (low- $\kappa$ ) dielectric insulating material. The schematic cross-sectional diagram from Fig. 2.2 shows a typical BEOL stack for the 65 nm process technology generation. The BEOL process comprises the following main steps:

Firstly, photolithography and etching processes are used to pattern trenches for vias/ metal lines in the low-κ dielectric layer. Low-κ dielectrics are usually chosen as intermetal dielectric (IMD) and inter-layer dielectric (ILD) materials because their low permittivity helps to reduce the parasitic capacitances between interconnects, leading

Figure 2.2: Schematic cross-section illustrating BEOL metallic interconnect layers formed in a standard CMOS IC manufacturing process, including metal and via layers, inter-metal dielectric (IMD) and inter-layer dielectric (ILD) layers.

to faster voltage signal propagation speed.

- Afterwards a few nanometers of liner material is conformally deposited, followed by the deposition of a thin copper film. The copper film acts a seed layer for subsequent copper electroplating process.

- The next step is electroplating copper to conformally fill out the trenches. Copper is commonly chosen as the interconnect material due to its high electrical conductivity. Because copper a highly diffusive material, the liner layer acts as a diffusion barrier between the copper and the low- $\kappa$  dielectric. Often BEOL processes involve depositing a separate barrier layer before the liner layer, which can function as a diffusion barrier between the copper and the low- $\kappa$  dielectric. TiN and TaN are good barrier materials; hence they are usually preferred as the liner material.

- Finally, chemical mechanical polishing (CMP) is used to planarize the surface in preparation for the formation of the next layer. Dummy metal structures are used to maintain uniform metal density all over the chip, improving the uniformity of the CMP process.

The number of metal/via layers have been increasing with the continuous scaling of device dimensions. State-of-the-art 10 nm and 7 nm process technologies provide up to 12 BEOL metal layers [24], [25]. The pitch of any metal layer, *i.e.* the minimum feature size/spacing of corresponding structures, depend on the position of the layer within the stack. The *minimum metal pitch* (MMP) is available for the lowermost layer of the stack, which means the feature size is the smallest at the bottom of the stack and it becomes increasingly larger towards the top of the stack. In Fig. 2.2, the ~1x metal layers offer tightest metal pitches close to the MMP. The ~2x metal layers have pitches close to twice the MMP, while  $\geq 4x$ layers have the largest pitches. The tight-pitch metallic layers at the bottom of the BEOL stack are advantageous for facilitating small gaps for NEM structures, resulting in increased electrostatic force and lower-voltage operation.