# Automated, FPGA-Based Hardware Emulation of Dynamic Frequency Scaling

David Biancolin

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2022-21 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-21.html

May 1, 2022

Copyright © 2022, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Automated, FPGA-Based Hardware Emulation of Dynamic Frequency Scaling

by

#### David Thomas Biancolin

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Krste Asanović, Co-chair Adjunct Assistant Professor Jonathan Richard Bachrach, Co-chair Professor Sanjit Seshia Professor Robert Leachman

Spring 2021

# Automated, FPGA-Based Hardware Emulation of Dynamic Frequency Scaling

$\begin{array}{c} \text{Copyright 2021} \\ \text{by} \\ \text{David Thomas Biancolin} \end{array}$

#### Abstract

Automated, FPGA-Based Hardware Emulation of Dynamic Frequency Scaling

by

#### David Thomas Biancolin

Doctor of Philosophy in Electrical Engineering and Computer Science

University of California, Berkeley

Professor Krste Asanović, Co-chair

Adjunct Assistant Professor Jonathan Richard Bachrach, Co-chair

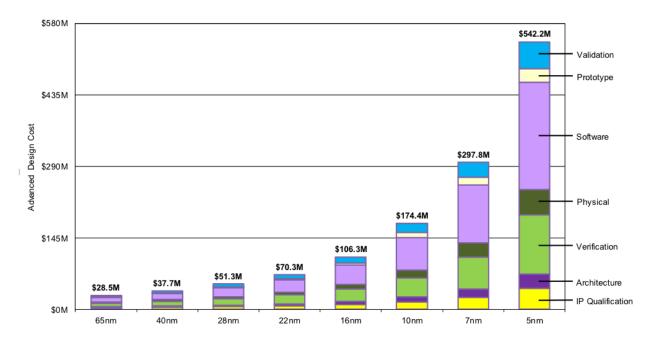

The simultaneous growth of new applications and death of transistor scaling trends is driving an explosion in custom silicon projects spanning all domains of computing. However, the enormous non-recurring engineering (NRE) cost of designing a modern system-on-a-chip (SoC) remains a major barrier to the wider adoption of custom silicon. Of concern to this dissertation is the lack of a good full-system simulation technology, a key driver of presilicon verification and validation costs. While field-programmable gate arrays (FPGAs) can be fast and relatively inexpensive hosts for simulation, mapping SoC clocking structures onto an FPGA such that they are represented accurately and deterministically is challenging. For this reason and others, many SoC designers turn to expensive hardware emulation platforms and their proprietary compilers. To radically reduce the cost of doing fast and accurate full-system simulation, the ADEPT Lab designed FireSim: an open-source, FPGA-based hardware emulation framework hosted in the public cloud.

In this dissertation, we begin by introducing FireSim's compiler infrastructure, called Golden Gate, which is capable of performing general multi-cycle resource optimizations in order to fit large SoCs on a single FPGA. Here we extend Golden Gate to present non-invasive, optimization-compatible schemes for simulating SoC clocking structures. First, we describe a simple approach for simulating systems with multiple fixed-frequency clocks. We then generalize this to support a general class of clock and reset structures, which can be composed to simulate dynamic frequency scaling, using an approach based on prior work in conservative parallel discrete-event simulation. The resulting work differs from prior academic FPGA-based projects in that it supports a much larger space of input designs, is easier to deploy to other FPGAs, and, like any good simulator, is deterministic—all while supporting simulation rates fast enough to productively boot operating systems and run real applications.

For Ivan Blunno (1973 - 2016)

# Contents

| C               | onter        | $\mathbf{nts}$    |                                                     | ii         |

|-----------------|--------------|-------------------|-----------------------------------------------------|------------|

| List of Figures |              |                   |                                                     | vi         |

| Li              | st of        | Table             | S                                                   | vii        |

| $\mathbf{G}$    | lossa        | ry of T           | Terms                                               | viii       |

| A               | ckno         | wledge            | ements                                              | ix         |

| 1               | <b>Int</b> r | roducti<br>Previo | ion ous Publication, Collaboration, and Funding     | <b>1</b> 6 |

| 2               | Full         | -Syste            | m Simulation of SoCs                                | 7          |

|                 | 2.1          | A Tou             | ur of Full-System Simulation for SoC Design         |            |

|                 |              | 2.1.1             | CPU-Hosted Simulation for Prototyping               |            |

|                 |              | 2.1.2             | CPU-Hosted Simulation for Verification              | . 8        |

|                 |              | 2.1.3             | FPGA Prototyping                                    | . 9        |

|                 |              | 2.1.4             | Hardware Emulation                                  | . 10       |

|                 | 2.2          | Hardy             | vare-Accelerated Microarchitecture Simulation       | . 12       |

|                 |              | 2.2.1             | Research Accelerator For Multiple Processors (RAMP) | . 12       |

|                 |              | 2.2.2             | FAME Taxonomy                                       | . 13       |

|                 |              | 2.2.3             | FAME-1: Host Decoupling                             | . 13       |

|                 |              | 2.2.4             | FAME-2: Abstract RTL                                | . 14       |

|                 |              | 2.2.5             | FAME-4: Multithreading                              | . 14       |

|                 |              | 2.2.6             | RAMP Retrospective                                  | . 15       |

|                 | 2.3          | Recen             | t Work at Berkeley                                  | . 15       |

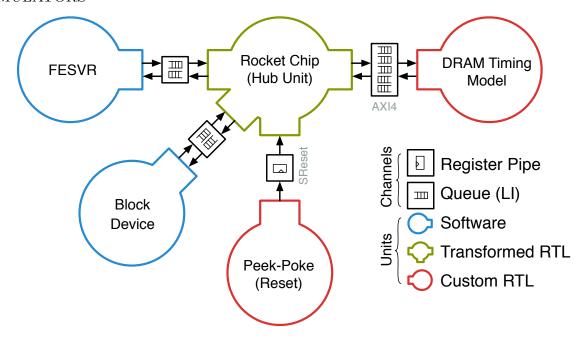

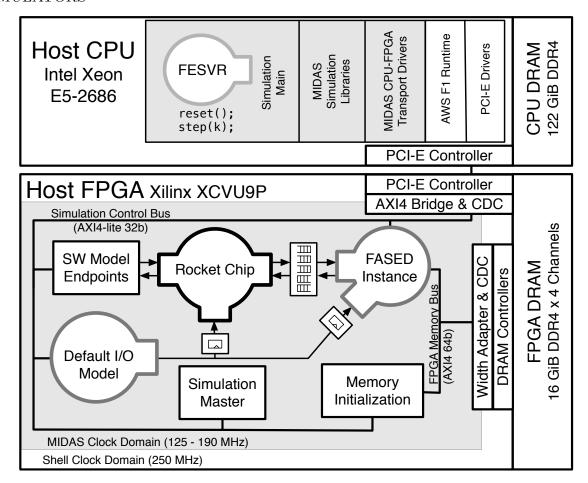

|                 |              | 2.3.1             | Strober and MIDAS                                   | . 16       |

|                 |              | 2.3.2             | FireSim                                             | . 18       |

|                 | 2.4          | Motiv             | ations for Golden Gate (MIDAS II)                   | 19         |

| 3               | On           |                   | Design of FPGA-Based Discrete-Event Simulators      | 20         |

|                 | 3.1          | An Iro            | on Law For FPGA-Based Simulator Performance         | 21         |

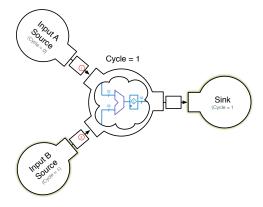

|   | 3.2 | Centrally Controlled (CC) Simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22 |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 3.3 | Distributed Control (DC) Simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24 |

|   |     | 3.3.1 A Primer on Parallel Discrete-Event Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24 |

|   |     | 3.3.2 Considerations for FPGA-Hosted PDES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25 |

|   |     | 3.3.3 ASIC Emulation As Domain-Specific PDES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26 |

|   |     | 3.3.4 Target Formalisms for ITDC Simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27 |

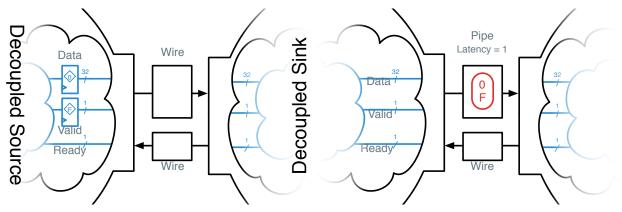

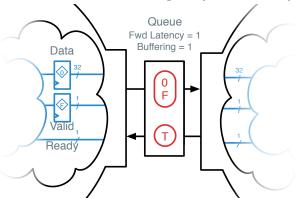

|   |     | 3.3.5 Channel-Bootstrapped Formalisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27 |

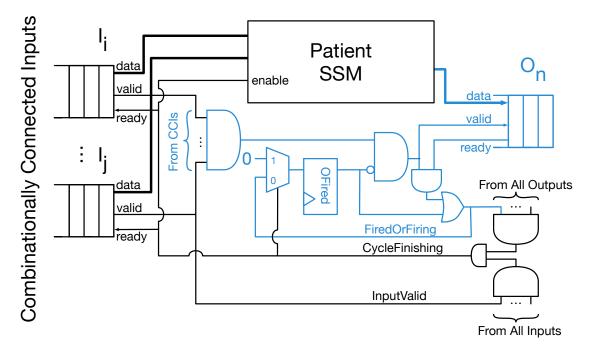

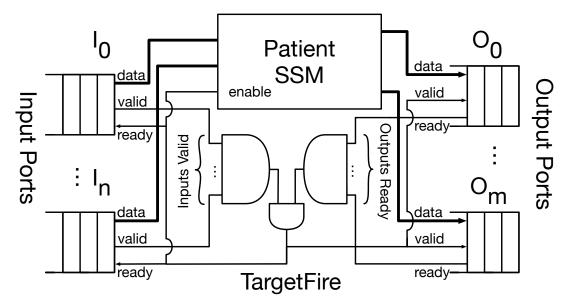

|   |     | 3.3.6 Latency-Insensitive Bounded-Dataflow Networks (LI-BDN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 29 |

|   | 3.4 | The MIDAS Compiler & Generated Simulator Microarchitecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35 |

|   |     | 3.4.1 Endpoint Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36 |

|   |     | 3.4.2 Simulation Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38 |

|   |     | 3.4.3 Time Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38 |

|   |     | 3.4.4 MIDAS's Generator Side Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39 |

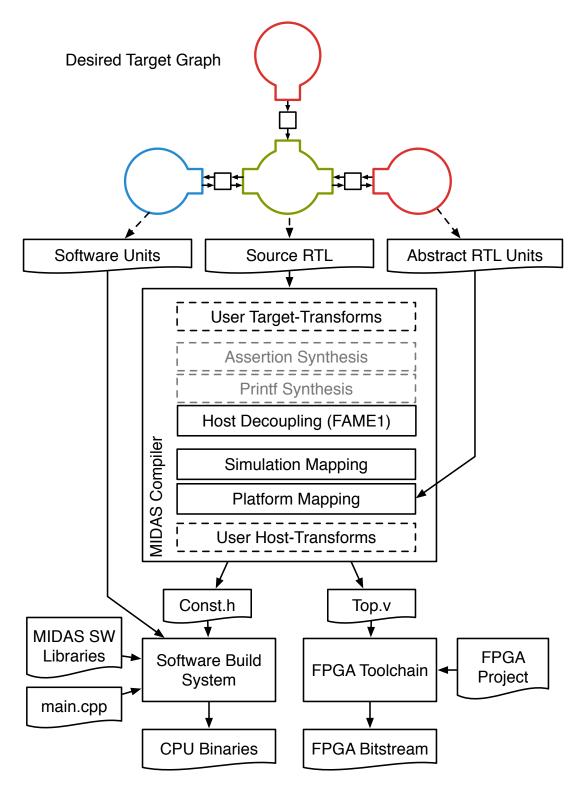

|   |     | 3.4.5 The MIDAS Compiler Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39 |

|   | 3.5 | Reviewing MIDAS's Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42 |

|   | 0.0 | 100,100,1112,112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,000,1112,0000,1100,1100,1100,1100,1100,1100,1100,1100,1100,1100,1100,1100,110 |    |

| 4 | Gol | den Gate: An Optimizing FAME Compiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43 |

|   | 4.1 | Design Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43 |

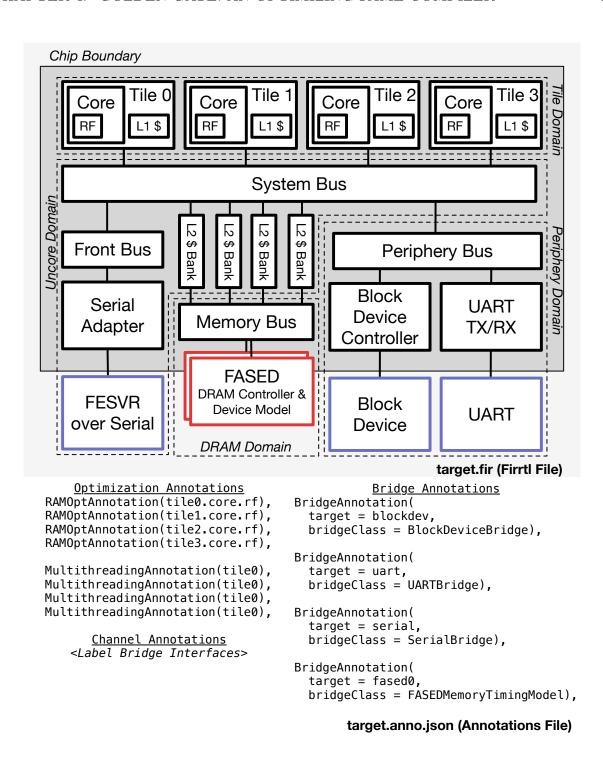

|   | 4.2 | Compiler Input & Target Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45 |

|   | 4.3 | Updated Compiler Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46 |

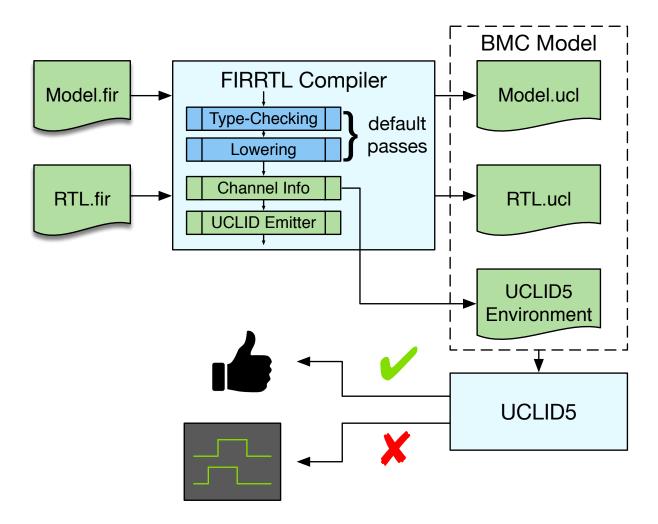

|   |     | 4.3.1 Annotations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49 |

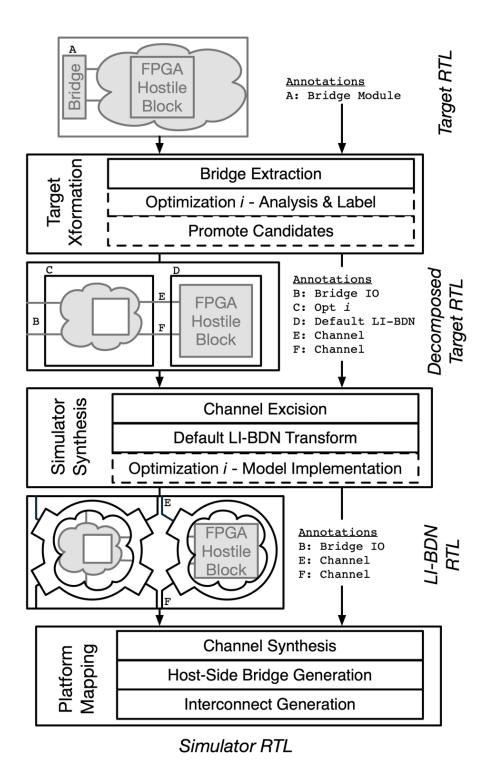

|   | 4.4 | Target Transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50 |

|   | 4.5 | Simulator Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51 |

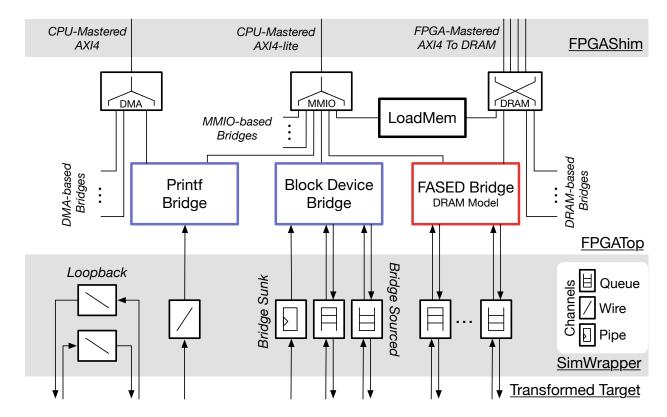

|   | 4.6 | Platform Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52 |

|   |     | 4.6.1 Channel Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52 |

|   |     | 4.6.2 Bridge Instantiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53 |

|   |     | 4.6.3 Platform Wrapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54 |

|   | 4.7 | ICCAD 2019 Golden Gate Publication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 5 | _   | port for Systems With Multiple Fixed-Frequency Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56 |

|   | 5.1 | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58 |

|   |     | 5.1.1 Simplifying Assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58 |

|   |     | 5.1.2 Annotation Modifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59 |

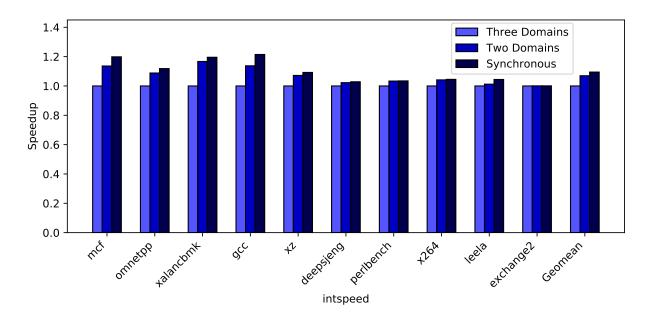

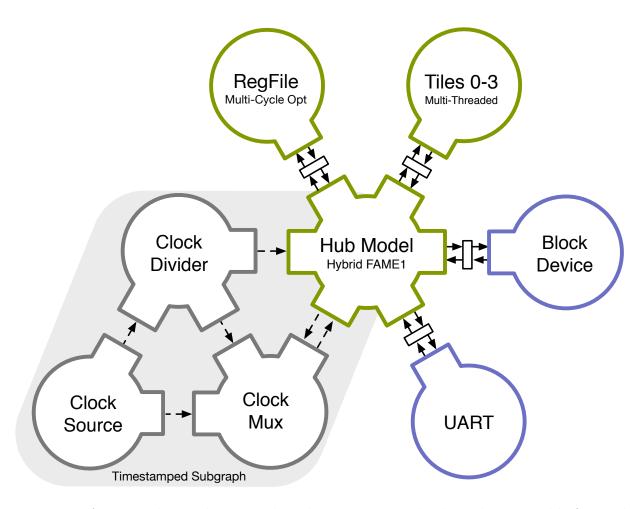

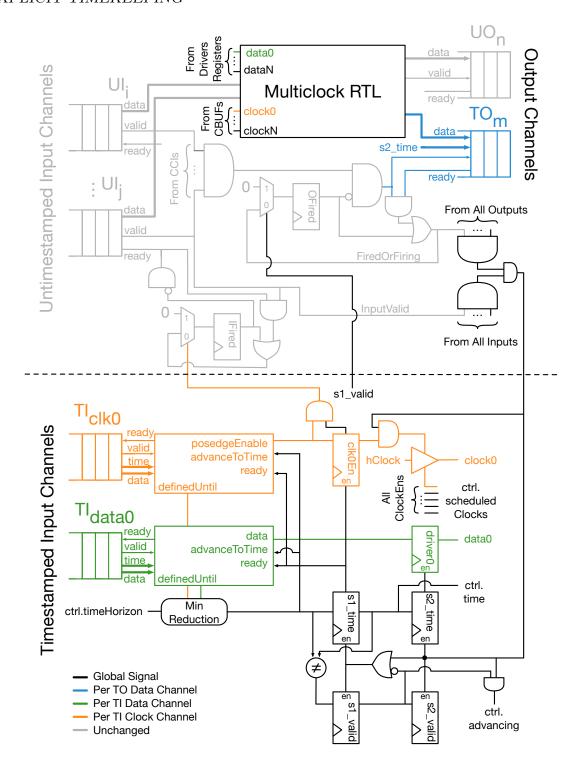

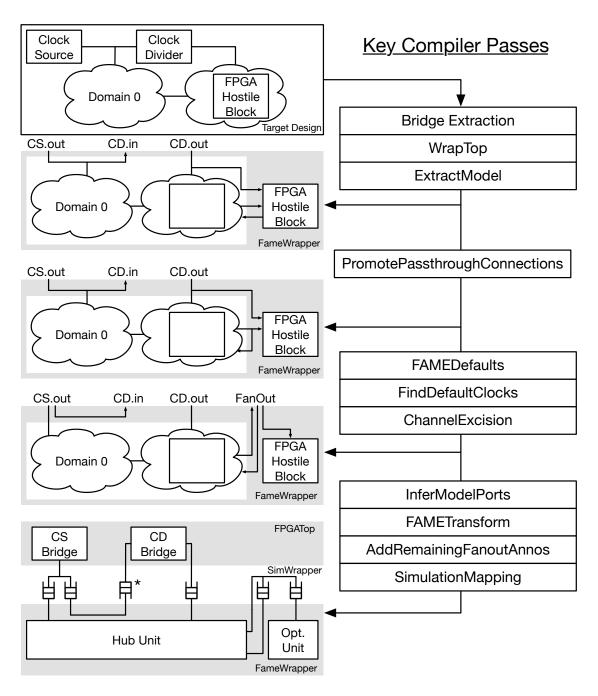

|   |     | 5.1.3 Modified FAME Transform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 59 |