### Integrated Hybrid Switched-Capacitor Converters for Point of Load Power Delivery

Pourya Assem Robert Pilawa-Podgurski, Ed.

#### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2022-243 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-243.html

December 1, 2022

Copyright © 2022, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Integrated Hybrid Switched-Capacitor Converters for Point of Load Power Delivery

by

Pourya Assem

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

$_{\mathrm{in}}$

Engineering- Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

#### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Accociate Professor Robert Pilawa-Podgurski, Chair Professor Seth R. Sanders Accociate Professor Duncan Callaway

Fall 2020

Integrated Hybrid Switched-Capacitor Converters for Point of Load Power Delivery

Copyright © 2020

by

Pourya Assem

#### Abstract

#### Integrated Hybrid Switched-Capacitor Converters for Point of Load Power Delivery

by

Pourya Assem

Doctor of Philosophy in Engineering- Electrical Engineering and Computer Sciences

University of California, Berkeley

Accociate Professor Robert Pilawa-Podgurski, Chair

The Hybrid Switched-Capacitor (SC) converters have shown potentials for higher efficiency and power-density compared with magnetic and pure SC converters. These advantages have driven new architectures and control schemes suitable for power converters integration in advanced CMOS technology nodes by alleviating the device stress and size. This work focuses on integration of the popular hybrid Dickson SC and cascaded resonant SC converters for high efficiency and power-density DC-DC conversion in datacenter and embedded applications covering few mW to hundreds of W load range.

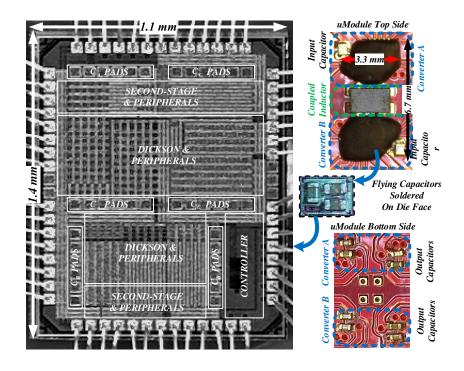

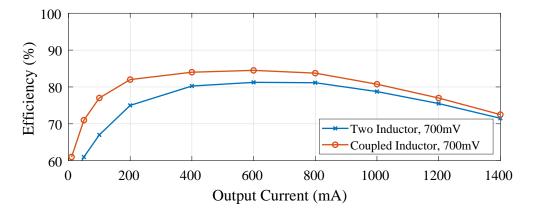

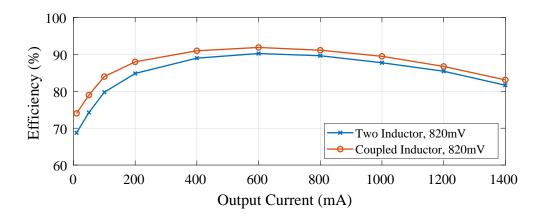

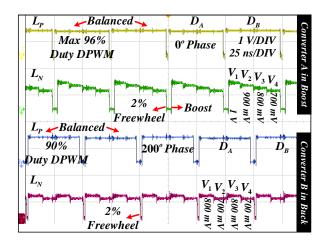

The first test chip is a hybrid Dickson SC converter for battery powered embedded and mobile applications where the demand focuses on high efficiency and power-density across a large conversion ratio of 3.4 V - 4.2 V for Lithium-ion batteries down to 0.3 V - 0.9 V with load range up to 1.5 A for digital processors and peripherals in advanced CMOS technology nodes. The second test chip is dual-phase time-interleaved extension of the hybrid Dickson SC converter designed with coupled-inductor and multiple outputs for application in multi-core processors with dynamic voltage scaling. The focus of the second test chip is improved efficiency through time-based control and dual-phase operation as well as a higher power-density through compact die-stacked packaging of passive components. The converter is designed for input voltage range of 3.2 V - 3.6 V DC bus conversion down to load voltage of 0.7 V - 1 V with load range up to 1.4 A. The third test chip integrates gate-driver, bootstrap and control peripherals of the cascaded discrete resonant SC converter for higher power conversion from 48 V DC bus down to 6 V intermediate bus. The focus of the start-up and shutdown peripherals enables hot swapping in datacenter applications.

Accociate Professor Robert Pilawa-Podgurski Dissertation Committee Chair

To my parents for all their support.

## Contents

| $\mathbf{C}$  | onter | nts          |                                                      | ii   |

|---------------|-------|--------------|------------------------------------------------------|------|

| $\mathbf{Li}$ | st of | Figur        | es                                                   | iv   |

| $\mathbf{Li}$ | st of | <b>Table</b> | s                                                    | viii |

| A             | ckno  | wledge       | ements                                               | ix   |

| 1             | Intr  | roducti      | ion                                                  | 1    |

| 2             | Hyl   | brid D       | ickson SC Converter with Split-Phase Control         | 4    |

|               | 2.1   | Introd       | $\operatorname{luction}$                             | 4    |

|               | 2.2   | Hybrie       | d Dickson SC Converter                               | 5    |

|               | 2.3   | Imple        | mentation                                            | 8    |

|               |       | 2.3.1        | Power Switch Sizing and Floorplan                    | 10   |

|               |       | 2.3.2        | Regulation and Capacitor Voltage Balancing           | 11   |

|               |       | 2.3.3        | Deadtime Controller                                  | 17   |

|               |       | 2.3.4        | Gate-Driver and Voltage Borrowing                    | 17   |

|               |       | 2.3.5        | Level-Shifter                                        | 20   |

|               |       | 2.3.6        | Scan-Chain and External Control                      | 21   |

|               | 2.4   | Exper        | imental Results and Measurements                     | 22   |

|               |       | 2.4.1        | Voltage Regulation and Balancing                     | 24   |

|               |       | 2.4.2        | Efficiency versus Variable $V_{IN}$                  | 25   |

|               |       | 2.4.3        | Efficiency versus Variable $f_{SW}$                  | 26   |

|               |       | 2.4.4        | Efficiency versus Two-Phase and Split-Phase Controls | 27   |

|               |       | 2.4.5        | Converter Performance Characterization               | 28   |

|               | 2.5   | Conclu       | usion                                                | 30   |

| 3 |     |        | e Hybrid Asymmetric Dickson SC Converter with Multiple Outputs<br>led-Inductor | 32 |

|---|-----|--------|--------------------------------------------------------------------------------|----|

|   | 3.1 | Introd | uction                                                                         | 32 |

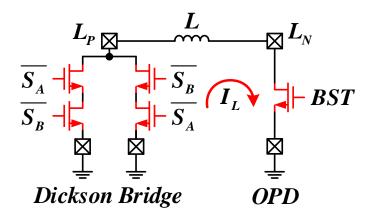

|   | 3.2 | Opera  | tion Principle                                                                 | 34 |

|   |     | 3.2.1  | Boost Mode                                                                     | 37 |

|   |     | 3.2.2  | Buck Mode                                                                      | 38 |

|   |     | 3.2.3  | Transient Handling                                                             | 39 |

|   | 3.3 | Impler | nentation                                                                      | 40 |

|   |     | 3.3.1  | Asymmetric Gate-Driver                                                         | 41 |

|   |     | 3.3.2  | Fast Level-Shifter                                                             | 41 |

|   |     | 3.3.3  | Dickson Controller                                                             | 41 |

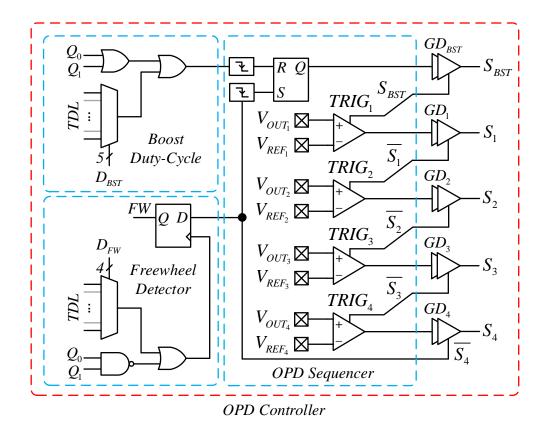

|   |     | 3.3.4  | OPD Controller                                                                 | 45 |

|   |     | 3.3.5  | Packaging                                                                      | 46 |

|   | 3.4 | Measu  | rements                                                                        | 47 |

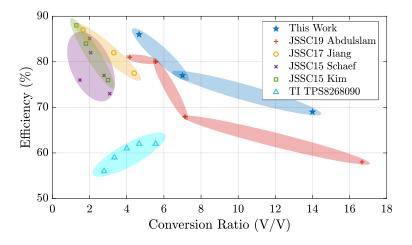

|   | 3.5 | Compa  | arison with State-of-the-Art                                                   | 51 |

| 4 | ΑG  | Quad G | ate-Driver for Cascaded Resonant Converter                                     | 52 |

|   | 4.1 | Introd | uction                                                                         | 52 |

|   | 4.2 | Resona | ant 2:1 SC Converter                                                           | 53 |

|   | 4.3 | Impler | nentation                                                                      | 56 |

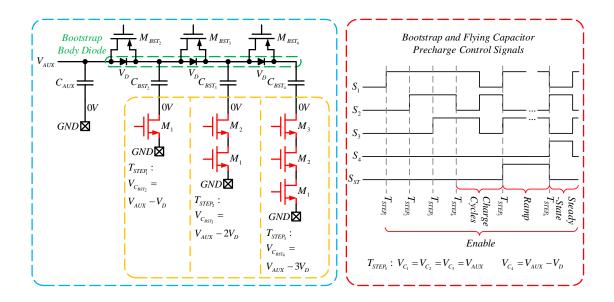

|   |     | 4.3.1  | Active Bootstrap                                                               | 57 |

|   |     | 4.3.2  | Asymmetric Gate-Driver                                                         | 58 |

|   |     | 4.3.3  | Fast Level-Shifter                                                             | 59 |

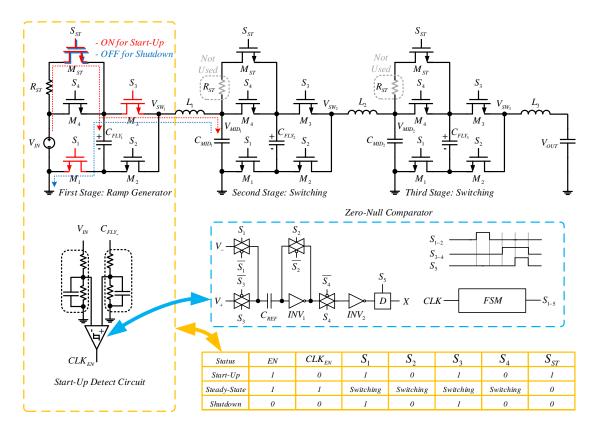

|   |     | 4.3.4  | Start-Up and Shutdown                                                          | 61 |

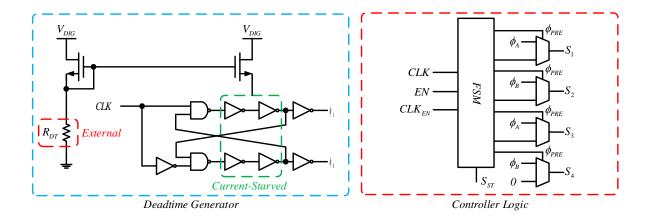

|   |     | 4.3.5  | Controller                                                                     | 64 |

|   |     | 4.3.6  | ESD & and High-Voltage Latch-Up Protection                                     | 65 |

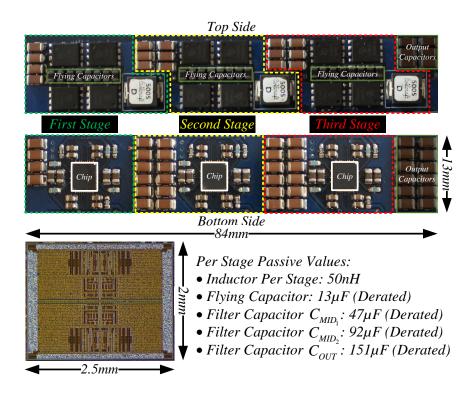

|   |     | 4.3.7  | Packaging and Three-Stage Converter                                            | 65 |

|   | 4.4 | Three- | Stage Cascaded SC Resonance Converter                                          | 66 |

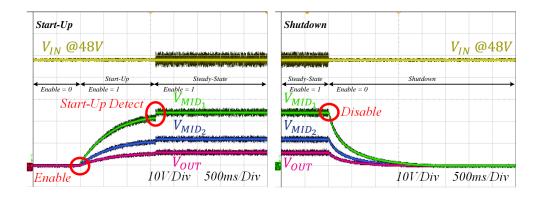

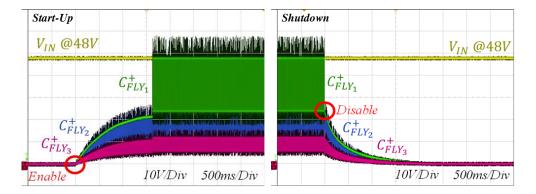

|   |     | 4.4.1  | Start-Up and Shutdown Measurements                                             | 66 |

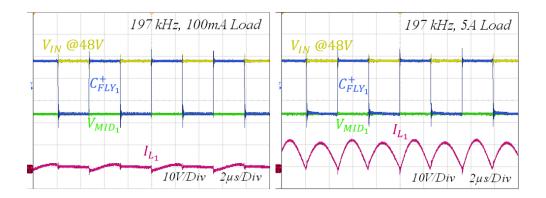

|   |     | 4.4.2  | Steady-State Resonance Measurements                                            | 67 |

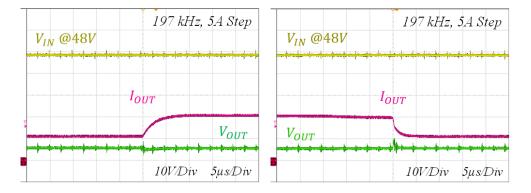

|   |     | 4.4.3  | Transient Measurements                                                         | 67 |

|   |     |        |                                                                                |    |

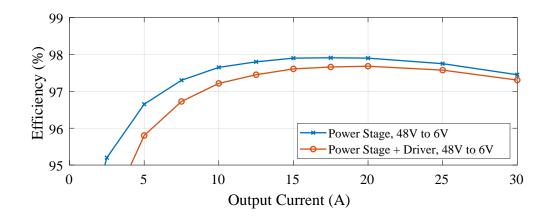

|   |     | 4.4.4  | Efficiency Measurements                                                        | 68 |

# List of Figures

| 1.1  | The two-stage power management system for 48 V bus to PoL delivery                                                                                                                                                                                                     | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | The hybrid Dickson SC converter.                                                                                                                                                                                                                                       | 6  |

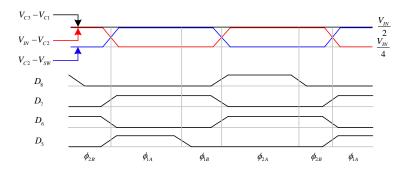

| 2.2  | Gate control signals for 50% duty-cycle of (a) two-phase control and (b) split-phase control of the hybrid Dickson converter.                                                                                                                                          | 6  |

| 2.3  | Operating phases of the hybrid Dickson converter (a) phase $\phi_{1A}$ , (b) phase $\phi_{1B}$ , (c) phase $\phi_{2A}$ , (d) phase $\phi_{2B}$ and (e) phase $\phi_3$                                                                                                  | 7  |

| 2.4  | Simulated voltage and current waveforms of the hybrid Dickson SC converter in SSL region for 100% duty-cycle. (a) Two-phase control voltages, (b) split-phase control voltages, (c) two-phase control $I_{C_2}$ current and (c) split-phase control $I_{C_2}$ current. | 7  |

| 2.5  | The steady-state voltage and current stresses for each power switch. $\ldots$                                                                                                                                                                                          | 8  |

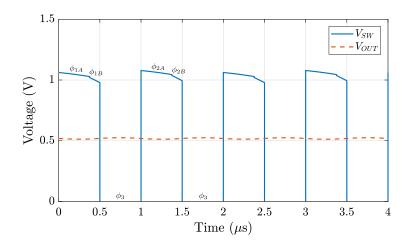

| 2.6  | Simulated switching node $V_{SW}$ and output voltage $V_{OUT}$ for 50% duty-cycle of split-<br>phase control                                                                                                                                                           | 9  |

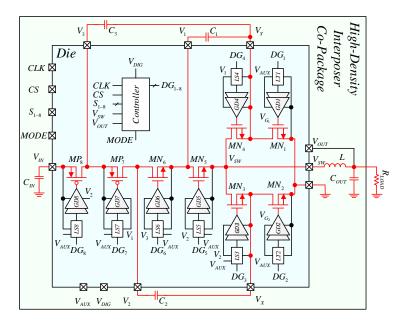

| 2.7  | Converter top-level implementation and co-packaging of passive components. $\ldots$ .                                                                                                                                                                                  | 9  |

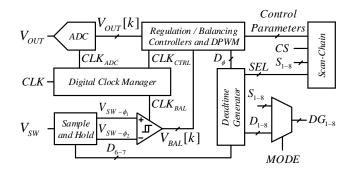

| 2.8  | Converter controller high-level diagram.                                                                                                                                                                                                                               | 10 |

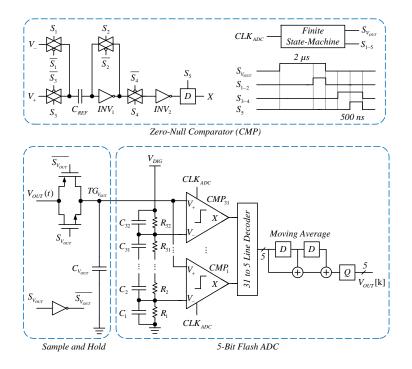

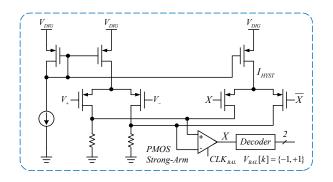

| 2.9  | The 5-bit flash ADC                                                                                                                                                                                                                                                    | 12 |

| 2.10 | Balancing hysteresis comparator and decoder                                                                                                                                                                                                                            | 13 |

| 2.11 | Sample and hold circuit for comparator                                                                                                                                                                                                                                 | 13 |

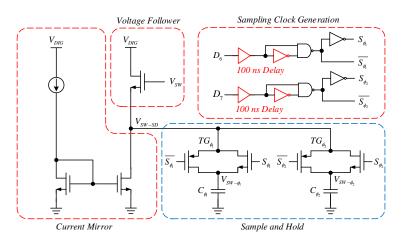

| 2.12 | Regulation and active flying capacitor voltage balancing PI compensators and DPWM generation                                                                                                                                                                           | 15 |

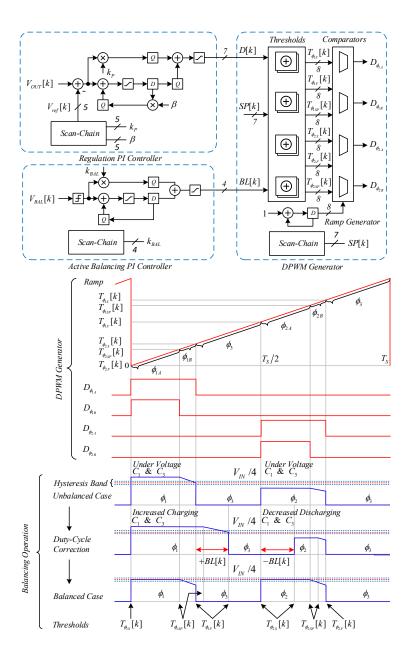

| 2.13 | Deadtime detector and controller                                                                                                                                                                                                                                       | 17 |

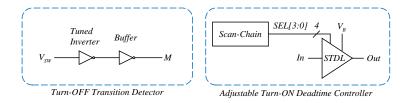

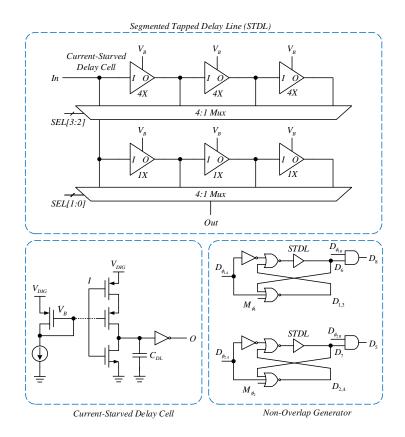

| 2.14 | Segmented tapped delay line and non-overlap clock generator                                                                                                                                                                                                            | 18 |

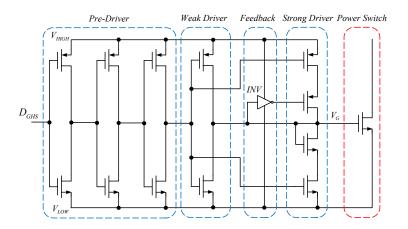

| 2.15 | Segmented gate-driver design with weak and feedback activated strong driver                                                                                                                                                                                            | 19 |

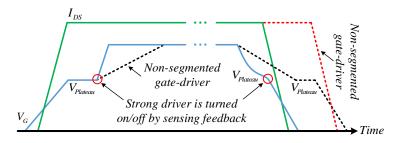

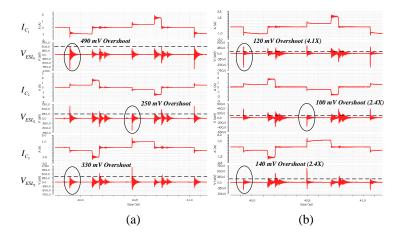

| 2.16 | Segmented gate-driver vs. non-segmented voltage and current profile                                                                                                                                                                                                    | 19 |

| 2.17 | The ringing simulation results (a) without segmented gate-driver, (b) with segmented gate-driver.                                                                                                                                                                      | 19 |

| 2.18 | Gate-driver voltage borrowing in the time domain and corresponding gate drive signals.                                                                                                                                                                                 | 20 |

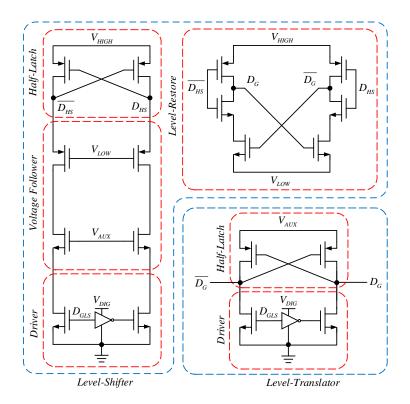

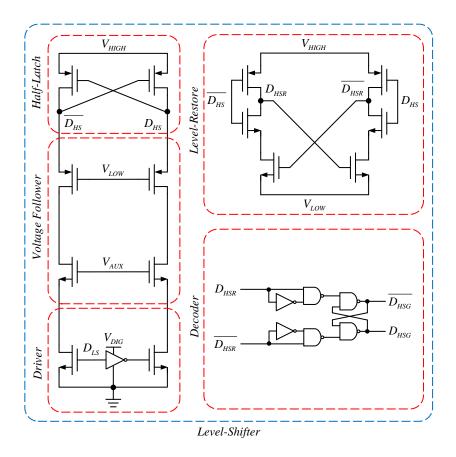

| 2.19 | Static level-shifter and level-translator circuits with delay compensation                                                                                                                                                                                             | 21 |

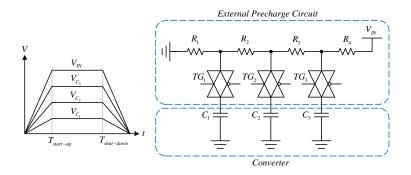

| 2.20 | External start-up circuit and shut-down circuit.                                                                                                       | 22 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

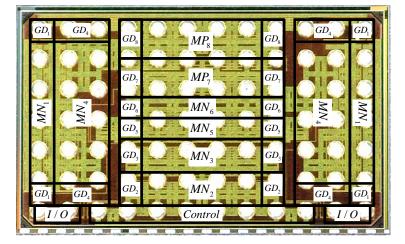

| 2.21 | Die micrograph and system components                                                                                                                   | 22 |

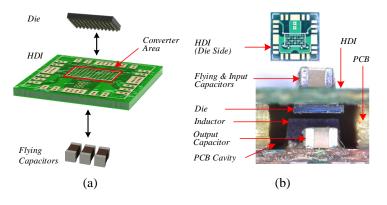

| 2.22 | The co-packaging of FC die. (a) HDI breakout board and (b) cutaway view of the die assembly.                                                           | 23 |

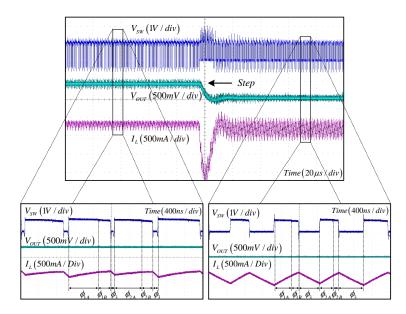

| 2.23 | Measured transient waveforms of output voltage $V_{OUT}$ regulation for 0.9 V to 0.5 V step                                                            | 25 |

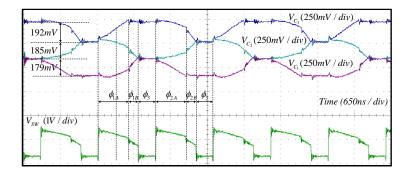

| 2.24 | Measured flying capacitor voltage swing to show effective capacitance matching                                                                         | 25 |

| 2.25 | Measured $V_1$ to $V_3$ nodes to show effective flying capacitor voltage balancing                                                                     | 26 |

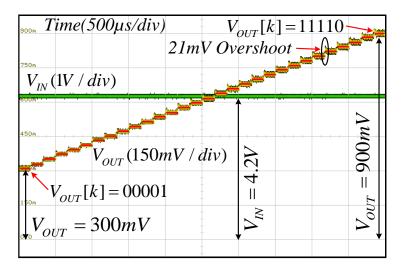

| 2.26 | Measured regulated output voltage in closed-loop across the designed voltage range.                                                                    | 26 |

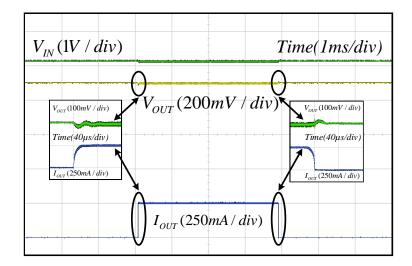

| 2.27 | Measured regulated output voltage in closed-loop under load step                                                                                       | 27 |

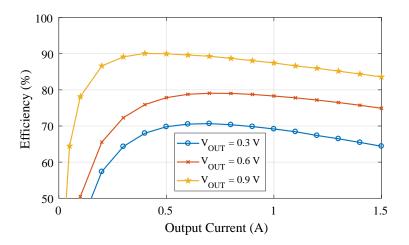

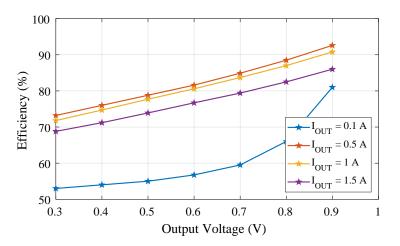

| 2.28 | Measured efficiency for full output current range at $V_{IN} = 4.2$ V and $f_{SW} = 400$ kHz for various $V_{OUT}$ values.                             | 27 |

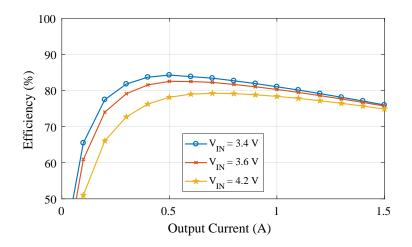

| 2.29 | Measured efficiency for full output current range at $V_{OUT} = 0.6$ V and $f_{SW} = 400$ kHz for various $V_{IN}$ values.                             | 28 |

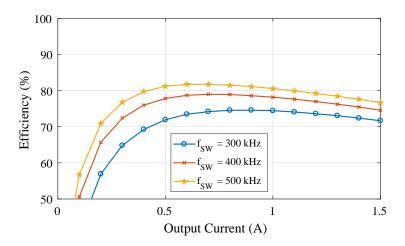

| 2.30 | Measured efficiency for full output current range at $V_{IN} = 4.2$ V and $V_{OUT} = 0.6$ V for various $f_{SW}$ values.                               | 28 |

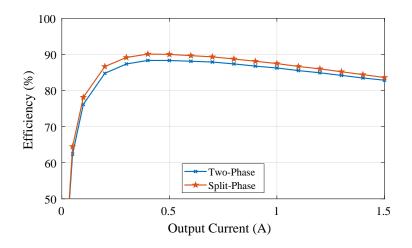

| 2.31 | Measured efficiency for full output current range at $V_{IN} = 4.2$ V, $V_{OUT} = 0.9$ V and $f_{SW} = 400$ kHz for two-phase and split-phase controls | 29 |

| 2.32 | Measured efficiency for the regulated $V_{OUT}$ continuous range at $V_{IN} = 4.2$ V and $f_{SW} = 500$ kHz                                            | 29 |

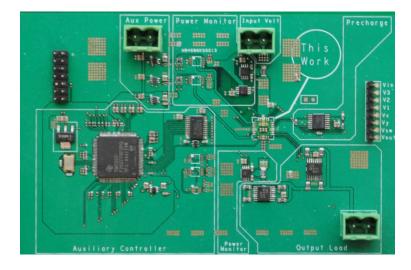

| 2.33 | Prototype converter test board                                                                                                                         | 30 |

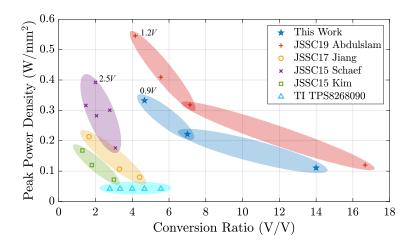

| 2.34 | Peak power density at conversion ratio comparison from die area                                                                                        | 31 |

| 2.35 | Efficiency comparison corresponding to Fig. 2.34 data points                                                                                           | 31 |

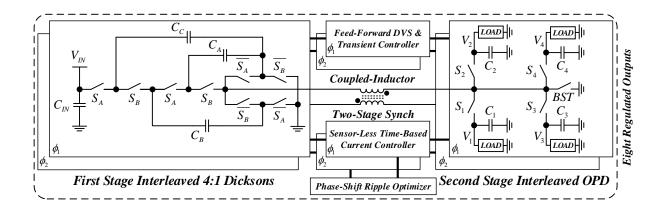

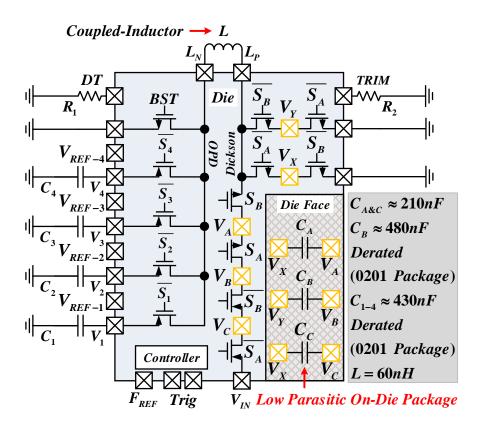

| 3.1  | The dual-phase time-interleaved SIMO converter with coupled-inductor and sensor-<br>less time-based control.                                           | 33 |

| 3.2  | The two-stage converter top-level.                                                                                                                     | 34 |

| 3.3  | The freewheel operation of inductor through ground loop.                                                                                               | 37 |

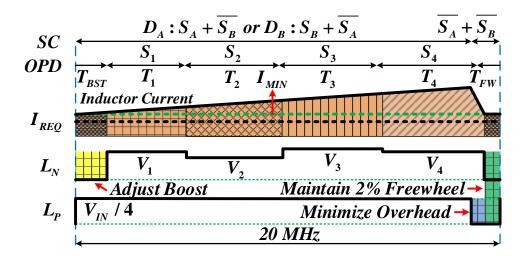

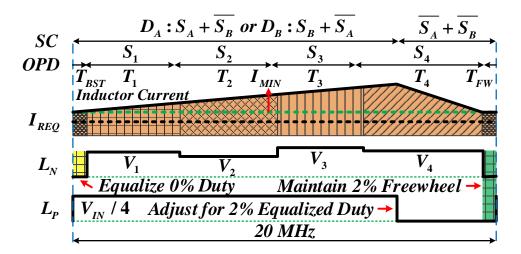

| 3.4  | The boost mode operation principle                                                                                                                     | 38 |

| 3.5  | The buck mode operation principle.                                                                                                                     | 38 |

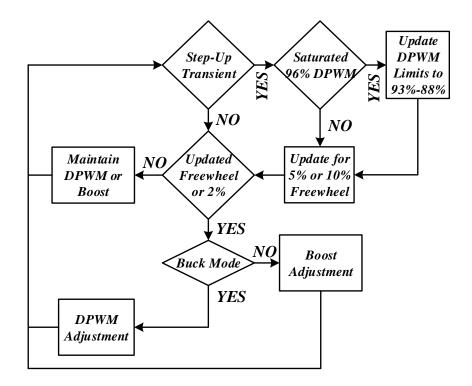

| 3.6  | The flow chart for transients handling of buck and boost modes.                                                                                        | 39 |

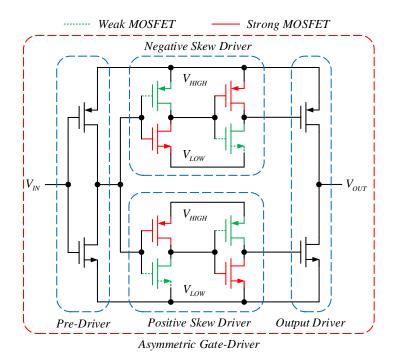

| 3.7  | The asymmetric gate-driver.                                                                                                                            | 40 |

| 3.8  | The fast level-shifter.                                                                                                                                | 42 |

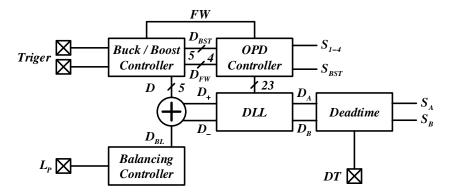

| 3.9  | The SIMO controller top level diagram.                                                                                                                 | 42 |

| 3.10 | The hybrid DPWM generator for first-stage Dickson SC                                                                                                   | 43 |

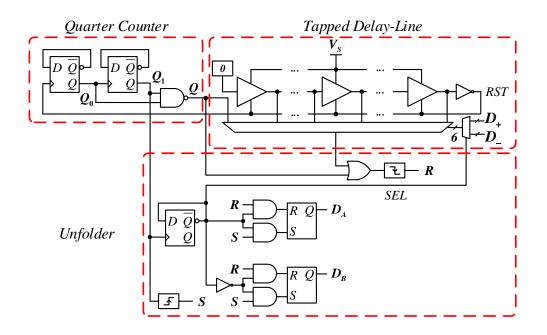

| 3.11 | The DLL controller of DPWM generator.                                                                                                                  | 43 |

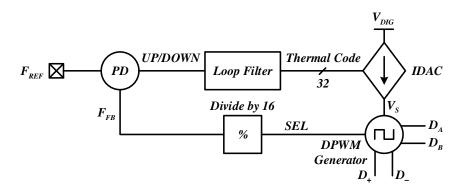

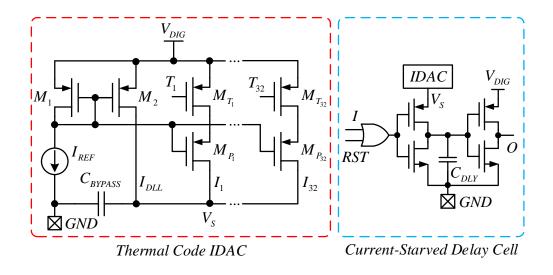

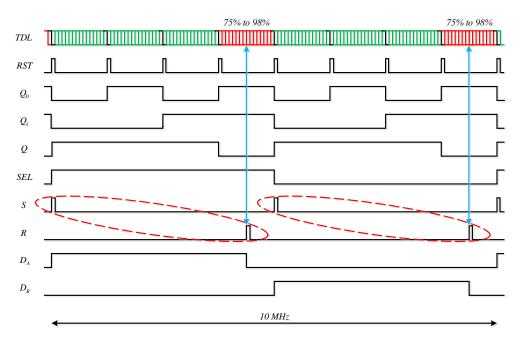

| 3.12 | The IDAC and current-starved delay cell of DPWM generator                                                                            | 44 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.13 | The hybrid DPWM generator operation                                                                                                  | 44 |

| 3.14 | The OPD output controller                                                                                                            | 46 |

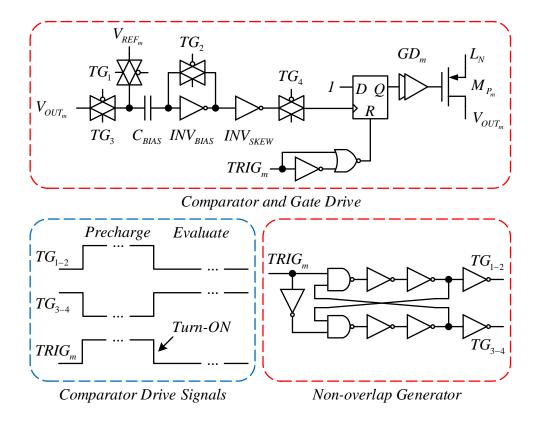

| 3.15 | The OPD inverter-based comparator                                                                                                    | 47 |

| 3.16 | The SIMO converter die and the stacked capacitor packaging                                                                           | 48 |

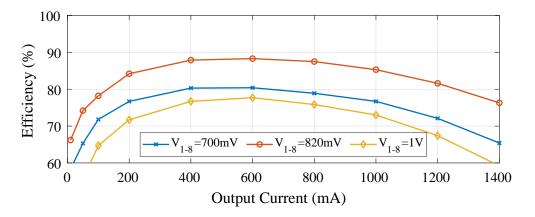

| 3.17 | The efficiency measurement of Dickson SC converter with and without coupled-<br>inductor at 700mV output.                            | 48 |

| 3.18 | The efficiency measurement of Dickson SC converter with and without coupled-<br>inductor at 820mV output.                            | 49 |

| 3.19 | The first-stage and second-stage controller measurements for converter A running in boost mode and converter B running in buck mode. | 49 |

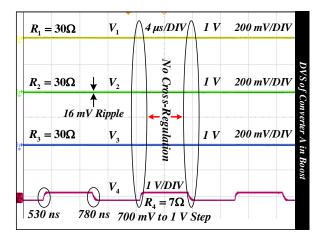

| 3.20 | The single output channel DVS step loading with cross-regulation elimination at 10% freewheel.                                       | 50 |

| 3.21 | The SIMO converter efficiency.                                                                                                       | 50 |

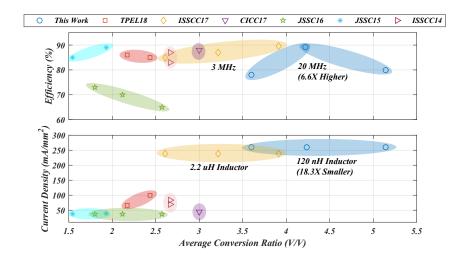

| 3.22 | The SIMO converter efficiency and current-density comparison with prior works                                                        | 51 |

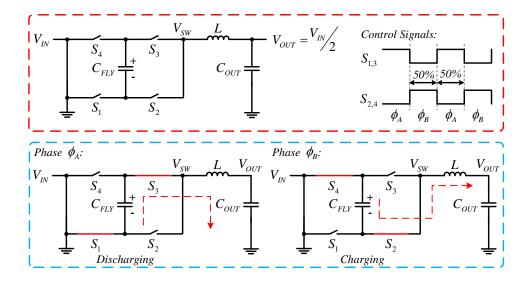

| 4.1  | The 2:1 SC converter cell.                                                                                                           | 53 |

| 4.2  | The conventional diode-based bootstrap method used for 2:1 SC resonant converter cell.                                               | 54 |

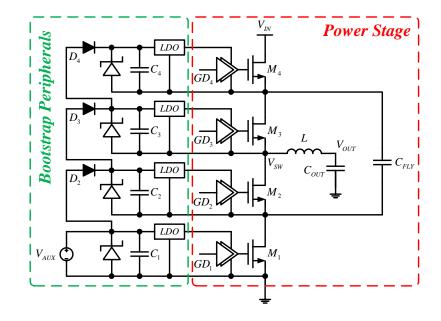

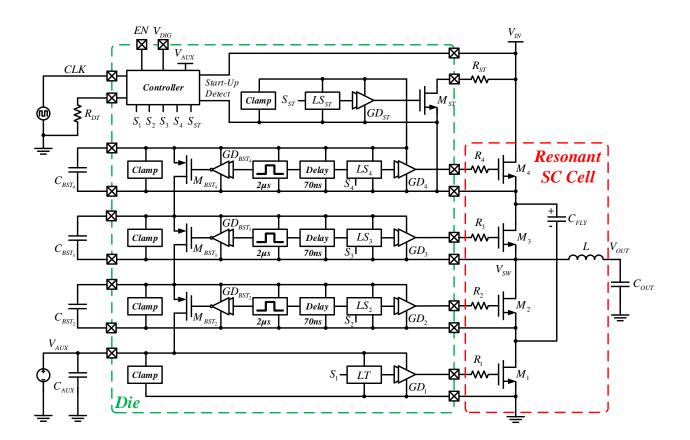

| 4.3  | The quad gate-driver IC top level system schematic diagram. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                      | 55 |

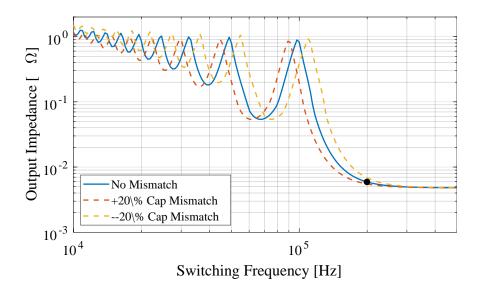

| 4.4  | The $C_{FLY}$ mismatch effect on the output impedance with $f_R = 200 k H z$ , $C_{FLY} = 12.7 \mu$ F and $L = 50 n H$               | 56 |

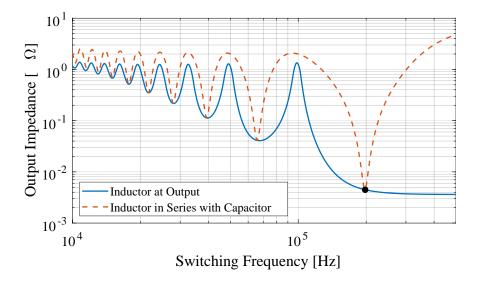

| 4.5  | The inductor placement effect on the output impedance with $f_R = 200 k H z$ , $C_{FLY} = 12.7 \mu$ F and $L = 50 n H$               | 56 |

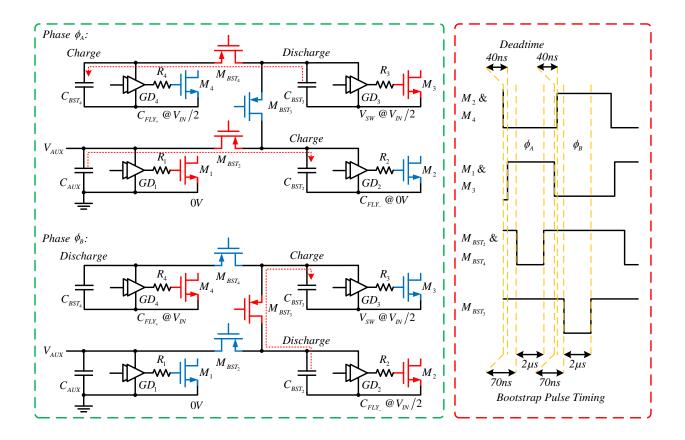

| 4.6  | The active bootstrap working principle and control signals                                                                           | 58 |

| 4.7  | The active bootstrap driver circuit and control signals                                                                              | 59 |

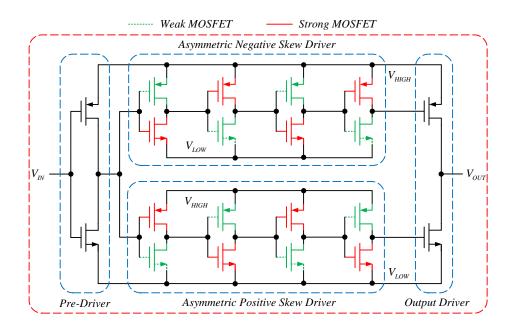

| 4.8  | The asymmetric gate-driver architecture                                                                                              | 60 |

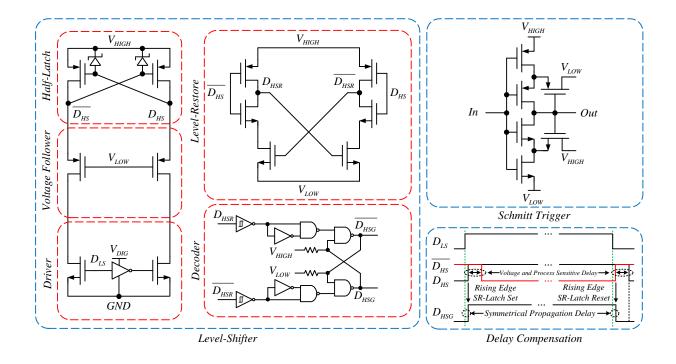

| 4.9  | The level-shifter used for the floating gate-driver $GD_{2-4}$                                                                       | 61 |

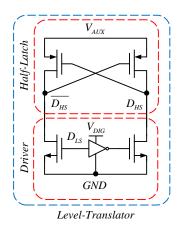

| 4.10 | The level-translator used for the ground refereed gate-driver $GD_1$                                                                 | 61 |

| 4.11 | The bootstrap pre-charge diagram during the start-up phase. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                      | 63 |

| 4.12 | The pre-charge of three-stage converter.                                                                                             | 63 |

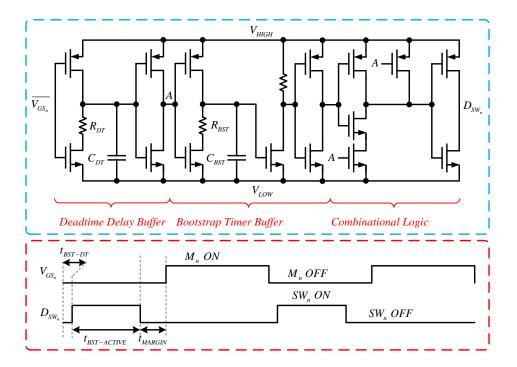

| 4.13 | The controller and deadtime non-overlap clock generator. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                | 64 |

| 4.14 | The three-stage converter with quad gate-driver in 40 lead QFN package and the die micrograph                                        | 65 |

| 4.15 | The three-stage output voltage measurement at start-up phase                                                                         | 66 |

| 4.16 | The three-stage flying capacitor voltage measurement at start-up phase                                                               | 66 |

| 4.17 | The resonance operation at steady-state                      | 67 |

|------|--------------------------------------------------------------|----|

| 4.18 | The three-stage output voltage measurement at start-up phase | 67 |

| 4.19 | The two-stage efficiency measurements.                       | 68 |

| 4.20 | The three-stage efficiency measurements                      | 69 |

# List of Tables

| 2.1 | Converter specifications                                     | 10 |

|-----|--------------------------------------------------------------|----|

| 2.2 | The $q_{SW}$ and power switch sizing for split-phase control | 11 |

| 2.3 | Gate-driver voltage borrowing technique                      | 20 |

| 2.4 | The die area breakdown                                       | 23 |

| 2.5 | Active and passive component footprints                      | 23 |

| 2.6 | Flying Capacitor Matching.                                   | 24 |

| 2.7 | Comparison with prior state-of-the-art work.                 | 29 |

| 2.8 | Estimated power loss breakdown                               | 30 |

| 3.1 | Comparison with prior state-of-the-art work.                 | 51 |

| 4.1 | Comparison with prior state-of-the-art work.                 | 68 |

|     |                                                              |    |

#### Acknowledgements

First and foremost, I like to thank my advisor for his support. It was a pleasure to work and collaborate with my colleagues Wen-Chuen Liu and Yutian Lei on development of the work presented in the Chapter 2 and Zichao Ye on development of the work presented in Chapter 4. I also like to thank Christopher Barth, Shibin Qin, Zitao Liao, Nathan Pallo, Charles Hill, Kelly Fernandez, Samantha Coday, Margaret Blackwell, Rose Abramson, Derek Chou, Nathan Brooks and all the current and past group members for friendship and support and our industry sponsors and collaborators from Texas Instruments.

### Chapter 1

### Introduction

The power management system for point-of-load power delivery (PoL) from the 48 V bus has gained attention in several large scale applications from which the data centers and telecommunication industry can be pointed out. A typical power management system with growing popularity, as shown in Fig. 1.1, consists of a two-stage topology. The first stage is designed to convert the 48 V DC bus to an intermediate bus voltage feeding a number of the second stage converters for PoL power delivery. The first stage topology should be selected to be highly efficient and achieving high power density, as it performs the bulk of voltage conversion, while the loading transient and regulation can be relaxed by operating in open-loop. Meanwhile, the second stage converters should add a high bandwidth transient handling for line and load regulation with the PoL voltage domain residing in the typical 0.7 V to 3.3 V interval for advanced CMOS processes. The first stage is typically occupying a larger area as the high voltage passive and active components can be bulky. Hence, from a physical design stand point and power-density consideration it is the most optimal to have a single first stage in the system hierarchy design. Thus, the two-stage architecture enables modular and flexible physical design of the PoL power delivery systems by placing the more compact second stage converters throughout the system and close to the load. However, the increased physical distance between the two stages should be treated carefully as the parasitic elements of the long PCB traces delivering large current values can introduce efficiency loss and noise coupling to sensitive signal lines with potential signal integrity issues.

The long PCB traces with undesired resistive and inductive parasitic elements can limit the efficiency and transient performance of the power management systems. A conventional approach to this design challenge is development of the system around a current regime at a intermediate voltage which ensures the efficiency and transient response of the system is not impacted by the physical design constraints as well as meeting the voltage and current stress limits of both stages of the converter in advanced CMOS processes. Hence, it is important to note that the practical selection of intermediate voltage is critical to the application. Selection of a low intermediate voltage leads to distribution of large DC currents from the first stage in order to maintain the rated power delivery. This in turn introduces additional conduction loss because of PCB traces parasitic resistance and decreases the efficiency of power management systems. In addition large steps of DC currents can lead to a significant ESR transient at this unregulated node. Furthermore, the parasitic inductance of long PCB traces can introduce additional undesired ringing transients as

Figure 1.1. The two-stage power management system for 48 V bus to PoL delivery.

the intermediate voltage goes through large DC current load steps. On the other hand, selection of a large mid-point voltage increase the voltage stress on the second stage converter, where it was primarily designed to perform a high-bandwidth regulation. A large voltage stress requires selection of high voltage and bulky devices which reduces the bandwidth of the second stage converters, which are typically designed with either a high-frequency bulk converter, linear regulator or a hybrid of the two. In addition, the second stage converters designed with linear regulator architecture will take a heavy toll on efficiency as the dropout voltage increases. Hence, most systems are designed with intermediate voltage in the 3 V - 6 V range.

This works investigates the advantages of hybrid switched-capacitor (SC) converters in the design of the both converter stages as higher efficiency and power-density can be achieved compared with the conventional magnetic and pure SC converter topologies. These advantages have driven new architectures and control schemes suitable for power converters integration in advanced CMOS technology nodes by alleviating the device stress and size. This work focuses on integration of the popular hybrid Dickson SC and hybrid cascaded resonant SC converters for DC-DC conversion in datacenter and embedded applications covering few mW to hundreds of W load range.

The first CMOS integrated power converter is a hybrid Dickson SC converter for battery powered embedded and mobile application where the demand focuses on high efficiency and powerdensity across a large conversion ratio of 3.4 V - 4.2 V for Lithium-ion batteries down to 0.3 V - 0.9 V with load range up to 1.5 A for digital processors and peripherals in advanced CMOS technology nodes. A power-density of  $330 \text{ mW/mm}^2$  and a peak efficiency of 92.6% with effective switching frequency of 1 MHz. The converter is packaged using flip-chip in 65 nm CMOS technology with passive devices co-packaged through a high-density interposer to minimize the packaging parasitics and volume. A segmented gate-driver is used to enhance the converter efficiency and reliability by maintaining low voltage ringing across the power switches. The converter is integrated with closed-loop output voltage regulation, deadtime control and active capacitor voltage balancing to maximize the active and passive device utilization. The short comings of the first test chip design, such as large RMS current, expensive packaging and a single regulated output is improved and redesigned in a second test chip.

The second CMOS integrated hardware prototype is a dual-phase time-interleaved extension of the hybrid Dickson SC converter designed with coupled-inductor and multiple outputs for application in multi-core processors with dynamic voltage scaling. The focus of the second converter design is improved efficiency through utilization of coupled-inductor for reduced RMS current and time-based control in a dual-phase operation as well as higher power-density through a compact die-stacked packaging of passive components. The converter is designed for input voltage range of 3.2 V - 3.6 V DC bus conversion down to load voltage of 0.7 V - 1 V for digital processors conversion and load range up to 1.4 A. The two-stage topology of each converter phase is comprised of firststage hybrid Dickson switched-capacitor 4:1 step-down converter and second-stage ordered power delivery operating at 20MHz with four regulated outputs. The increased switching frequency enables utilization of smaller inductor values as well as improved transient handling of the converter. An all-digital sensor-less current-mode control, replacing sensitive analogs, synchronizes the energy flow between the two stages of each converter phase to maintain the inductor steady-state current. The active flying capacitor balancing peripherals is utilized for reliable operation of the first-stage. The modulator, controller peripherals and the power stage switches are integrated and only external flying capacitors and coupled-inductor are required. The stacked on-die flying capacitors and chip-on-board packaging reduces the converter footprint and improves the power density as well efficiency by reducing parasitic losses. The converter is designed in 65 nm bulk CMOS technology. A peak efficiency of 88.3% and power density of  $450 \text{mW}/\text{mm}^2$  is measured.

With the first two test chip focusing on the second stage converter, as shown in Fig. 1.1, the third focus of this dissertation is designed to investigate the first stage converter. The third test chip integrates gate-driver and support peripherals of a discrete converter for higher power conversion from 48 V DC bus down to 6 V intermediate bus. The focus of the third test chip is design of a single-package peripheral for the hybrid resonant SC 2:1 switching cell. A quad gate-driver is proposed to improve the power-density and efficiency of the existing architecture. The designed chip integrates the controller, level-shifter, an active bootstrap and gate-driver along with start-up and shutdown peripherals to reduce the parts count. The power stage active and passive components are implemented using discrete components. A three-stage cascaded resonant SC converter with 8:1 conversion ratio from 48V DC bus is designed using the custom quad gate-driver chip with pick efficiency of 97.8% and 30A load range. The next three chapter of the dissertation focuses on design of each test chip in detail with hardware measurements and comparison to the state-of-the-art prior works.

### Chapter 2

# Hybrid Dickson SC Converter with Split-Phase Control

#### 2.1 Introduction

Emerging technologies like the internet of things, wearable electronics and embedded biomedical devices can greatly improve quality of life, but the limited capacity of energy sources and power converters remains a challenge. In such applications, digital circuits operate at low voltages, typically below 1 V, in order to reduce the power consumption. In addition, memories [1, 2], near-threshold and subthreshold digital processors [3, 4] operating in the 0.3-0.9 V range have shown a promising figure-of-merit in energy efficient computation in advanced CMOS processes. Capturing this opportunity is challenged by the fact that Lithium-ion battery cells are commercially available in the 3.4-4.2 V voltage range. Recent designs for mobile computing also incorporate dynamic frequency voltage scaling technique [5, 6] for more active and aggressive power saving, which motivates the need for compact power converters capable of large conversion ratios with wide and efficient voltage regulation across the full load range.

Conventional buck converters [7, 8, 9] employ an inductor as intermediate energy storage, which dominates the size and leads to low power density because of the relatively low energy density of inductors compared to capacitors [10]. It is also challenging for conventional buck converters to simultaneously achieve high power density and efficiency at large conversion ratios, due to the large device voltage stress, i.e. full input voltage, relative to the output voltage. This causes poor device utilization, because higher voltage devices with larger on-resistance ( $R_{DS}$ ) per area are required and may not be available in advanced low voltage bulk CMOS processes. Another option, the SC converters [11, 12, 13] achieve improved device utilization [14]. However, the inherent charge sharing loss within SC converters has limited their achievable power density and efficiency, in particular for large conversation ratios. In [15, 16] high capacitance density processes, e.g., deep trench or ferroelectric capacitors, and high switching frequency are employed in order to reduce charge sharing loss, but these processes are expensive and not commercially available. Moreover, the conventional SC converters suffer from poor efficiency when operated outside the native fixed ratios, or under output voltage regulation. Although adjustable conversion ratio SC converters [17, 18, 19] enable a wider output voltage range, with somewhat improved efficiencies, they inevitably require more power switches and sacrifice of the power density. Recent hybrid SC converters such as the merged two-stage converter [20], three-level buck converter [21, 22], resonant SC converter (ReSC) [23] and hybrid Dickson converter [24, 25] have eliminated charge sharing loss and increased the capacitor utilization by allowing larger capacitor voltage ripple through soft-charging operation [27, 28]. which increases the power density by either increasing the current or reducing the capacitor size. This increase in power density comes at the cost of more challenging capacitor voltage balancing, which may require active balancing techniques, or - in many cases - can be addressed through design choices that enable natural balancing. Compared to the SC converters, hybrid SC converters achieve higher device utilization by taking advantage of the SC converter cascaded topology, while also achieving high efficiency under continuous output voltage regulation. In addition, the hybrid SC converters offer increased power density by reducing the inductor size through increased effective switching frequency and reduced voltage magnitude seen by the inductor compared to the conventional buck converters. This work presents an integrated hybrid SC converter based on the Dickson SC topology with an LC output filter and split-phase control to achieve complete soft-charging operation [24] across a continuously regulated [29] output voltage.

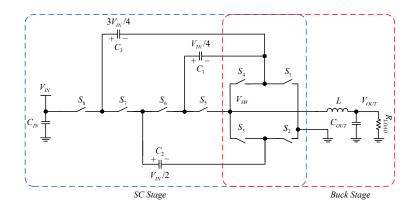

#### 2.2 Hybrid Dickson SC Converter

The Dickson SC converter achieves good device utilization, by reducing the required blocking voltage of power switches to  $V_{OUT}$  and  $2V_{OUT}$ , where  $V_{OUT} = V_{IN}/N$  given  $V_{IN}$  and N are the input voltage and the native conversion ratio of the Dickson SC converter. This allows the use of lower voltage rating devices with lower  $R_{DS}$  per area, and hence the potential to achieve high efficiency and high power density. However, the inherent charge sharing loss in conventional Dickson converters leads to poor capacitor utilization, where the voltage ripple, and subsequent charge transfer to the output from the capacitors must be limited [24]. The hybrid Dickson converter, as shown in Fig. 2.1, eliminates the charge sharing loss by addition of an inductor, L, to the output of the conventional Dickson converter. However, the conventional two-phase control of the hybrid Dickson SC converter still results in a residual charge sharing loss.

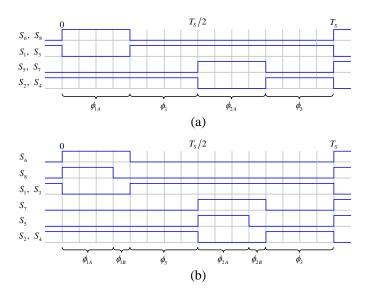

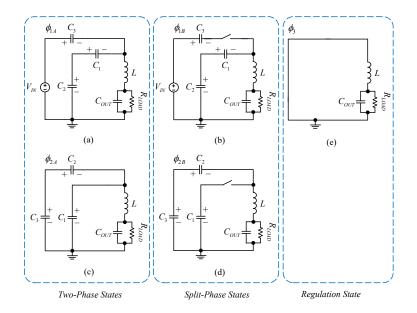

The gate control signals for the conventional two-phase control and the split-phase control are shown in Fig. 2.2(a) and 2.2(b), respectively. All possible switching phases of the hybrid Dickson converter are given in Fig. 2.3, where flying capacitors  $C_1$ ,  $C_2$  and  $C_3$  are either charged or discharged through the inductive current source load, yielding a smooth current to charge or discharge the capacitors (soft-charging). On the contrary, in conventional operation (hard-charging), the flying capacitors are directly connected to the large output capacitor,  $C_{OUT}$ , which acts as a voltage source load. Therefore, a large current transient is expected during the phase switching instances due to the capacitor voltages mismatch in hard-charging operation, which results in significant charge sharing loss [24].

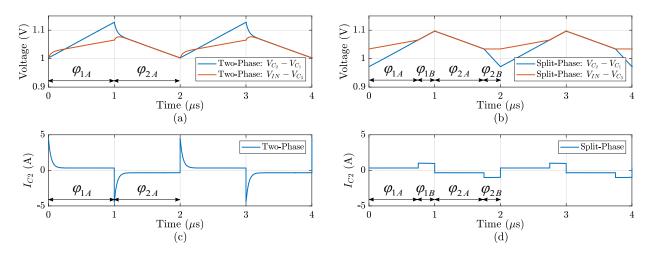

As can be seen from Fig. 2.4(a) simulation results with all equal flying capacitor value of 4  $\mu$ F and 20 m $\Omega$  switch resistance, for the two-phase control soft-charging operation the KVL constraint of  $V_{IN} - V_3 = V_2 - V_1$  in phase  $\phi_{2A}$  cannot be satisfied during the transition from phase  $\phi_{1A}$  to

Figure 2.1. The hybrid Dickson SC converter.

Figure 2.2. Gate control signals for 50% duty-cycle of (a) two-phase control and (b) splitphase control of the hybrid Dickson converter.

phase  $\phi_{2A}$ . This leads to incomplete soft-charging operation with residual charge sharing loss in capacitors, which can be observed from the spiky capacitor current, as shown in Fig. 2.4(c). In the split-phase control operation, buffer phases  $\phi_{1B}$  and  $\phi_{2B}$  are added to reconfigure the capacitor branches of the hybrid Dickson converter to be selectively charged or discharged, so that there is no voltage mismatch during phase transitions and KVL constraint are met, as shown in Fig. 2.4(b). As a result, with the same simulation parameters, smooth capacitor current can be observed, as shown in Fig. 2.4(d). The split-phase control technique achieves complete soft-charging operation by eliminating the charge sharing loss, which is a major source of power loss in the conventional SC converters. The RMS and large peak current stress through the capacitors and power switches are greatly reduced, and hence the converter efficiency, reliability and aging can be improved. The steady-state voltage and current stresses for each power switch are shown in Fig. 2.5. The steady state voltages across  $C_1$ ,  $C_2$  and  $C_3$  are  $V_{IN}/4$ ,  $V_{IN}/2$  and  $3V_{IN}/4$  respectively as shown in Fig. 2.1.

Figure 2.3. Operating phases of the hybrid Dickson converter (a) phase  $\phi_{1A}$ , (b) phase  $\phi_{1B}$ , (c) phase  $\phi_{2A}$ , (d) phase  $\phi_{2B}$  and (e) phase  $\phi_3$ .

Figure 2.4. Simulated voltage and current waveforms of the hybrid Dickson SC converter in SSL region for 100% duty-cycle. (a) Two-phase control voltages, (b) split-phase control voltages, (c) two-phase control  $I_{C_2}$  current and (c) split-phase control  $I_{C_2}$  current.

The output referred impedance  $R_{SC}$  of a SC converter [14], considering both the capacitor charge sharing loss and the conduction loss, can be modeled by:

$$R_{SC} = \frac{\frac{V_{IN}}{N} - V_{OUT}}{I_{OUT}} \tag{2.1}$$

where N is the conversion ratio and  $I_{OUT}$  is the output current. It is important to note that this model does not capture the switching loss of gate drivers and related control peripheral circuits.

| Phase<br>Switch | $\phi_{1A}$                                | $\phi_{_{1B}}$      | $\phi_{2A}$                                              |                     | $\phi_3$                    |

|-----------------|--------------------------------------------|---------------------|----------------------------------------------------------|---------------------|-----------------------------|

| $S_1 \& S_3$    | $V_{IN}$ / 4                               | $V_{\rm IN}$ / 4    | <i>I</i> <sub>OUT</sub> &<br><i>I</i> <sub>OUT</sub> / 2 | I <sub>OUT</sub>    | <i>I</i> <sub>OUT</sub> / 2 |

| $S_2 \& S_4$    | I <sub>OUT</sub> / 2<br>& I <sub>OUT</sub> | I <sub>OUT</sub>    | $V_{\rm IN}$ / 4                                         |                     | $I_{OUT}$ / 2               |

| $S_5$           | $V_{IN}$ / 4                               | $V_{\rm IN}$ / 4    | $I_{OUT}$ / 2                                            | $V_{\rm IN}$ / 4    | $V_{\rm IN}$ / 4            |

| $S_6$           | <i>I</i> <sub>OUT</sub> / 2                | I <sub>OUT</sub>    | V <sub>IN</sub> / 2                                      | V <sub>IN</sub> / 2 | V <sub>IN</sub> / 2         |

| S <sub>7</sub>  | V <sub>IN</sub> / 2                        | V <sub>IN</sub> / 2 | $I_{OUT}$ / 2                                            | I <sub>OUT</sub>    | V <sub>IN</sub> / 2         |

| S <sub>8</sub>  | <i>I</i> <sub>OUT</sub> / 2                | $V_{\rm IN}$ / 4    | $V_{IN}$ / 4                                             | $V_{\rm IN}$ / 4    | $V_{\rm IN}$ / 4            |

Figure 2.5. The steady-state voltage and current stresses for each power switch.

It is desirable to minimize  $R_{SC}$  to increase the efficiency of the converter. The split-phase control for complete soft-charging operation yields a low  $R_{SC}$  independent of the switching frequency, because the frequency dependent charge sharing loss is eliminated [24]. The significant reduction of  $R_{SC}$  in the slow switching limit (SSL) compared with the hard-charging operation enables the hybrid Dickson SC converter to operate with a larger capacitor voltage ripple in SSL without compromising the efficiency. Increasing the capacitor utilization can potentially increase the power density by reducing the capacitor size or switching loss in the SSL region.

For the hybrid Dickson SC converter, the output voltage regulation can be achieved by the addition of phase  $\phi_3$  after  $\phi_{1B}$  and  $\phi_{2B}$  phases. By simultaneously turning on  $S_1$  to  $S_4$  to achieve phase  $\phi_3$ , the switching-node voltage  $V_{SW}$  can be momentarily connected to ground to resemble a buck converter operation. The adjustable duty-cycle, D, enables a continuous  $V_{OUT}$  range after the LC output filtering, as shown in Fig. 2.6. The output voltage is calculated using the equation below:

$$V_{OUT} = \frac{DV_{IN}}{N} \tag{2.2}$$

where D is calculated from phases  $\phi_{1A} + \phi_{1B}$  and phases  $\phi_{2A} + \phi_{2B}$  over the  $T_S$  period. In Fig. 2.6, it should be noted that the regulation phase  $\phi_3$  appears twice in each complete switching cycle, effectively doubling the pulse frequency seen by the inductor, without increasing the switching frequency of individual power switches and peripheral circuits. The slight difference between the magnitude of phases  $\phi_{1A} + \phi_{1B}$  and  $\phi_{2A} + \phi_{2B}$  is a result of active capacitor voltage balancing hysteresis band for full system simulation shown in Fig. 2.6. Details of the hysteresis band and control are provided in Section 2.3.

#### 2.3 Implementation

The hybrid Dickson SC converter was implemented in 65 nm bulk CMOS process, which enables application of the proposed on-chip power management compatible with the most advanced systemon-chip and mixed signal designs to be co-integrated on the same process. The process offers CMOS transistors suitable for the converter operating range. The low density and Q-factor of integrated

Figure 2.6. Simulated switching node  $V_{SW}$  and output voltage  $V_{OUT}$  for 50% duty-cycle of split-phase control.

Figure 2.7. Converter top-level implementation and co-packaging of passive components.

passive capacitors and inductors present a challenge for practical implementation of the power converter to achieve high power density and efficiency. Therefore, co-packaging of discrete passive components was employed in this work to meet the performance targets. Figure 2.7 shows the high-level schematic diagram of the hybrid Dickson SC converter with power switches and passive components. A high-level schematic drawing of controller shown in Fig. 2.8. Each sub-block design is discussed in the following subsections. Table 2.1 shows the converter design specifications.

The flying capacitors  $C_1$ ,  $C_2$  and  $C_3$  as well as input decoupling capacitor  $C_{IN}$ , output filter capacitor  $C_{OUT}$  and output inductor L are assembled through the high density interposer co-package solution. The power switches  $MN_1$ - $MP_8$  are fully integrated along with the gate-drivers  $GD_1$ - $GD_8$ and level-shifters  $LS_3$ - $LS_8$ . The ground referred gate-drivers  $GD_1$ - $GD_2$  use level-translators. The

Figure 2.8. Converter controller high-level diagram.

| Specification                          | Rated                             |

|----------------------------------------|-----------------------------------|

| Input voltage $V_{IN}$                 | 3.4-4.2 V                         |

| Output voltage $V_{OUT}$               | 0.3-0.9 V                         |

| Output regulation step                 | 20  mV                            |

| Output current $I_{OUT}$               | 0.1-1.5 A                         |

| Power density                          | $330 \ \mathrm{mW}/\mathrm{mm}^3$ |

| Switching frequency $f_{SW}$           | 500  kHz                          |

| Output voltage ripple $\Delta V_{OUT}$ | < 4% (10  mV)                     |

Table 2.1. Converter specifications.

converter was implemented with a fully on-chip controller and ADC for closed-loop output voltage regulation as well as deadtime controller and active flying capacitor voltage balancing controller. The digital pulse width modulator (DPWM) is clocked via the CLK pin to generate the control signals  $D_{1-8}$  for the power switches. The digital clock manager (DCM) is embedded within the DPWM block and generates the working clocks of controllers, scan-chain and peripheral circuits. Additionally, the converter can be operated using an external controller via the  $S_{1-8}$  pins by bypassing the internal controllers. The scan-chain is used for debugging and externally adjusting the converter control parameters. The internal controllers are powered through the digital voltage  $V_{DIG}$  provided by an external supply. In addition,  $V_{AUX}$  supplies the level-shifters and ground referred gate-drivers. The flying capacitors precharge circuit was implemented externally. Below, the circuit design and implementation of each system block is presented.

#### 2.3.1 Power Switch Sizing and Floorplan

The power switches sizing and floorplan optimization of the converter are constrained by the efficiency and power density, given a fixed active die area for a compact co-packaging solution. In this design, we limited the active die area to the combined footprint areas of the capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_{IN}$ . The power switches and flip-chip (FC) pins floorplan are designed to minimize the parasitic inductance and resistance in the current loops, to and from the flying capacitors, as a measure to reduce the ringing overshoots. The normalized power switches size for the switches for the split-phase control can be used to determine the relative power switches size for the switches  $R_{DS}$  values in order to optimize the loss and area. The switch charge vector  $q_{SW}$ , relative power

| Power Switch | $q_{SW}$   | $V_{GS}$   | $V_{DS}$   | Relative Size        |

|--------------|------------|------------|------------|----------------------|

| $MN_1$       | $\sqrt{3}$ | $V_{IN}/2$ | $V_{IN}/4$ | $\sqrt{3}$           |

| $MN_2$       | 1          | $V_{IN}/2$ | $V_{IN}/4$ | 1                    |

| $MN_3$       | 1          | $V_{IN}/2$ | $V_{IN}/4$ | 1                    |

| $MN_4$       | $\sqrt{3}$ | $V_{IN}/4$ | $V_{IN}/4$ | $2.5 	imes \sqrt{3}$ |

| $MN_5$       | 1          | $V_{IN}/2$ | $V_{IN}/4$ | 1                    |

| $MN_6$       | 1          | $V_{IN}/2$ | $V_{IN}/2$ | 1                    |

| $MP_7$       | 1          | $V_{IN}/2$ | $V_{IN}/2$ | 3                    |

| $MP_8$       | 1          | $V_{IN}/2$ | $V_{IN}/4$ | 3                    |

Table 2.2. The  $q_{SW}$  and power switch sizing for split-phase control.

switch size, gate driving voltage  $V_{GS}$  and voltage stress  $V_{DS}$  of the power switches are shown in Table 2.2. The power switch sizes are adjusted for the applied  $V_{GS}$  under the  $V_{IN} = 3.4$  V minimum operating voltage of the Lithium-ion battery cell. To avoid bootstrap circuits for gate driving, the power switches  $MP_7$  and  $MP_8$  are chosen to be the PMOS type devices, which requires 3X channel width to match the  $R_{DS}$  of the NMOS type devices. This trade-off yet saves significant area when compared with the required area for on-chip or external bootstrap capacitors for gate drivers. In addition, the power switch  $MN_4$  gate-driver is supplied by  $V_{GS}/4$ , which requires additional 2.5X increase in channel width to match the  $R_{DS}$  value.

#### 2.3.2 Regulation and Capacitor Voltage Balancing

The output voltage regulation controller consists of a flash ADC and a digital PI compensator. The regulation signal chain and DPWM blocks are co-designed with the active flying capacitor voltage balancing controller which consists of sample and hold circuit, hysteresis comparator and a P/I compensator. The design and circuit implementation of these blocks are discussed below:

#### ADC

The ADC is designed for 32 linear steps over the range of  $V_{min} = 0.28$  V to  $V_{max} = 0.92$  V, which covers the required output voltage regulation range of 0.3-0.9 V as specified in Table 2.1. The 5-bit ADC was designed using a flash architecture given the low number of quantization levels as well as providing only a single clock-cycle conversion latency. The circuits and functional block of the designed flash ADC is shown in Fig. 2.9. The 5-bit resolution requires 31 comparators and 32 resistive elements to provide the reference voltage values evenly spaced in the  $V_{min} - V_{max}$ range. The resistive voltage reference ladder was compensated with MOS capacitors  $C_1 - C_{32}$  in order to provide stable reference voltage values with maximum quiescent current of 15  $\mu$ A. The inverter-based comparator was designed using the zero-null architecture. The operation of a zeronull comparator is based on biasing the  $INV_1$  inverter at its meta-stability condition, where any offset signal applied to its input triggers  $INV_1$  toward the corresponding stable condition at either high or low states. Hence, the operation of the zero-null comparator is divided into charging and evaluate phases. In the charging phase, the  $C_{REF}$  capacitor is charged to the voltage difference between ADC reference voltage of corresponding level,  $V_-$ , and meta-stability voltage of  $INV_1$ . In

Figure 2.9. The 5-bit flash ADC.

the evaluate phase, the biased  $INV_1$  is triggered into its corresponding stable condition with  $V_+$  applied at input. The  $S_{1-2}$  signals are used to initiate the charging phase by shortening input and output of  $INV_1$  through transmission gate  $S_2$  to force meta-stability condition and charging the other plate of  $C_{REF}$  to  $V_-$  via transmission gate  $S_1$ . The  $S_{3-4}$  signals are used to initiate the evaluation phase by applying sampled input voltage,  $V_+$ , via transmission gate  $S_3$  and driving the register buffer  $INV_2$  via transmission gate  $S_4$ . The comparison results are latched at the output register with rising edge of  $S_5$  signal. The long-channel design of  $INV_1$  and short  $S_{1-2}$  pulse period minimize power consumption of the comparator cell. The thermal code at the output of the comparator is converted to its binary equivalent using a synthesized 31 to 5 line decoder. A moving average digital filter was used at the output of the flash ADC to improve the sensed voltage integrity. The sample and hold circuit was designed using a transmission gate  $TG_{V_{OUT}}$  and sampling capacitor  $C_{V_{OUT}}$ . The sample and hold control signal  $S_{V_{OUT}}$  is timed to activate for a sampling duration of 2  $\mu$ s with 500 ns setup time before the clock-edges of  $CLK_{ADC}$  generated by the DCM rotator block as shown in Fig. 2.9.

#### Comparator with Sample and Hold Circuit

A hysteresis comparator with sample and hold circuit is used to compare the  $V_{SW}$  during phases  $\phi_{1A}$  and  $\phi_{2B}$  at  $f_{CLK_{BAL}} = f_{SW}$  rate for active flying capacitor voltage balancing. Figure 2.10 shows the circuit diagram of the hysteresis comparator and its decoder. The hysteresis comparator is supplied by  $V_{DIG}$  and implemented using a pre-amplifier in cascade with a dynamic latch [31]. The hysteresis is set through  $I_{HYST}$  value. The output of hysteresis comparator is decoded to generate the  $V_{BAL}[k]$  values -1 and +1, which are directly passed to the active capacitor voltage balancing PI compensator.

Figure 2.10. Balancing hysteresis comparator and decoder.

Figure 2.11. Sample and hold circuit for comparator.

The sample and hold circuit is shown in Fig. 2.11. A common drain amplifier is used to track and level shift  $V_{SW-SD}$  from  $V_{SW}$ . In addition, the common drain amplifier prevents the negative body-diode conduction voltage at  $V_{SW}$  from propagating through and discharging the sampling capacitors  $C_{\phi_1}$  and  $C_{\phi_2}$ . The  $V_{SW-SD}$  voltage is sampled at the phases  $\phi_{1A}$  and  $\phi_{2A}$  through the transmission gates  $TG_{\phi_1}$  and  $TG_{\phi_2}$ , respectively. The sampling signals  $S_{\phi_1}$  and  $S_{\phi_2}$  are generated by the DCM block with single-shot circuits of 100 ns pulse-width from the 100 ns delayed D5 and D6 signals, respectively. The low-pass RC filter formed by the sampling capacitors and transmission gate resistance damps any ringing artifacts at the  $V_{SW-SD}$  node.

#### **Compensator for Balancing and Regulation**

Unbalanced flying capacitor voltage levels can lead to a critical voltage stress across the power switches and gate-drivers, which decreases the reliability and can lead to breakdown of the converter. The unbalanced flying capacitor voltage  $\Delta V_{BL}$  is a direct consequence of unbounded deviations of the  $V_{C_1}$  and  $V_{C_3}$  from steady-state operation, while  $V_{C_2} = V_{IN}/2$  stays constant in this topology. This phenomenon can be shown through the KVL relations in phases  $\phi_{1A}$  and  $\phi_{2A}$ , assuming equal charge transfer into and from  $C_2$  in phases  $\phi_{1B}$  and  $\phi_{2B}$ , for the split-phase control operation as shown by the equations below:

$$\phi_{1A}: V_{IN} - V_{C_3} = V_{C_2} - V_{C_1} \tag{2.3}$$

$$\phi_{2A}: V_{C_3} - V_{C_2} = V_{C_1} \tag{2.4}$$

where the  $V_{C_1}$  and  $V_{C_3}$  do not have a unique solution and  $V_{C_2} = V_{IN}/2$  is a single solution. Therefore, the initial conditions of  $V_{C_1} = V_{IN}/4$  and  $V_{C_1} = 3V_{IN}/4$ , set through the precharge at start-up, should be preserved via an active voltage balancing technique. This behavior is unique to the soft-charging operation as the flying capacitors are charged and discharged through a current source, whereas in the case of hard-charging the output capacitor provides a single solution of  $V_{C_1} = V_{IN}/4$  and  $V_{C_1} = 3V_{IN}/4$  for a voltage balanced operation. Hence, any mismatch in the timing and charge transfer between the flying capacitors, through the soft-charging load current source, can lead to a deviation from the  $V_{C_1}$  and  $V_{C_3}$  initial conditions. This relation is shown by the equations below:

$$\Delta V_{C_3} C_3 = I_{OUT} \Delta t_{C_3} \tag{2.5}$$

$$\Delta V_{C_1} C_1 = I_{OUT} \Delta t_{C_1} \tag{2.6}$$

where the output current  $I_{OUT}$  is assumed to be constant as well as  $C_1 = C_3$  effective values. In addition, the KVL equations in phases  $\phi_{1A} + \phi_{1B}$  and  $\phi_{2A} + \phi_{2B}$  imply that any mismatch in the flying capacitor voltages in steady-state operation should converge to the condition  $\Delta V_{BL} =$  $\Delta V_{C_1} = \Delta V_{C_3}$ . Therefore, any voltage deviation  $\Delta V_{BL}$  caused by the switching time mismatch, loss, transient load or even  $I_{OUT}$ ,  $C_1$  and  $C_3$  variations can be corrected through applying a timing correction  $\Delta t_{BL} = \Delta t_{C_1} = \Delta t_{C_3}$  to the control phases of  $\phi_{1A} + \phi_{1B}$  and  $\phi_{2A} + \phi_{2B}$ , as shown in Fig. 2.12 to achieve an amp-second balancing operation [32, 33, 34] for the flying capacitors  $C_1$ and  $C_3$ . Therefore, the duty-cycle corrections  $d_{\phi_{1A}+\phi_{1B}}$  and  $d_{\phi_{2A}+\phi_{2B}}$  are applied to the phases of duty-cycle  $D_{\phi_{1A}+\phi_{1B}}$  and  $D_{\phi_{1A}+\phi_{1B}}$  as shown by the equations below:

$$D_{\phi_{1A} + \phi_{1B}} \pm d_{\phi_{1A} + \phi_{1B}} = \frac{T_{\phi_{1A}} + T_{\phi_{1B}}}{T_s} \pm \frac{\Delta t_{BL}}{T_s}$$

(2.7)

$$D_{\phi_{2A}+\phi_{2B}} \mp d_{\phi_{2A}+\phi_{2B}} = \frac{T_{\phi_{2A}} + T_{\phi_{2B}}}{T_s} \mp \frac{\Delta t_{BL}}{T_s}$$

(2.8)

where the plus and minus signs are determined based on the voltage deviation  $\Delta V_{BL}$  sign to decrease or increase the  $C_1$  and  $C_3$  effective charging or discharging times  $T_{\phi_{1A}} + T_{\phi_{1B}}$  and  $T_{\phi_{2A}} + T_{\phi_{2B}}$  in the control phases  $\phi_{1A} + \phi_{1B}$  and  $\phi_{2A} + \phi_{2B}$ , receptively. The active capacitor voltage balancing extracts the information about voltage deviations  $\Delta V_{C_1}$  and  $\Delta V_{C_3}$  through sampling and comparing the switching node voltages  $V_{SW-\phi_{1A}} = V_{C_2} - V_{C_1} - V_{TH}$  and  $V_{SW-\phi_{2A}} = V_{C_3} - V_{C_2} - V_{TH}$ at phases  $\phi_{1A}$  and  $\phi_{2A}$ , respectively. Therefore, the value of  $V_{BAL}[k]$  which is determined by the sign of  $\Delta V_{BL}$  is calculated by:

$$V_{BAL}[k] = \begin{cases} +1, V_{SW-\phi_{1A}} < V_{SW-\phi_{2A}} \\ -1, V_{SW-\phi_{1A}} > V_{SW-\phi_{2A}} \end{cases}$$

(2.9)

Figure 2.12. Regulation and active flying capacitor voltage balancing PI compensators and DPWM generation.

where  $V_{BAL}[k] = +1$  implies that  $C_1$  and  $C_3$  are overcharged and a negative duty-cycle correction is applied to the charging phases  $\phi_{1A} + \phi_{1B}$  and a positive duty-cycle correction to the discharge phases  $\phi_{2A} + \phi_{2B}$  in order to reduce  $V_{C_1}$  and  $V_{C_3}$ . Similarly,  $V_{BAL}[k] = -1$  implies that  $C_1$  and  $C_3$  are undercharged, and complementary duty-cycle corrections are applied. Therefore, the control law for duty-cycle correction to achieve an amp-second balancing of the flying capacitors can be implemented through a compensator to compute the duty-cycle correction factor BL[k] as shown in Fig. 2.12. The active balancing compensator was implemented to operate in integral mode during the steady-state operation and in proportional mode during the load transients. This design choice prevents the integrator error accumulation during the load transients where the flying

capacitor can take several clock cycles to become balanced. In addition, the proportional mode gain can help to decrease the settling time. The integrator is disabled by clock-gating the integrator feedback register and the proportional mode is enabled by setting a non-zero value assigned to  $k_{BAL}$  via scan-chain. The integrator clock-gating is performed in a feed-forward configuration via scan-chain using the external microcontroller to synchronize the load transients with the balancing controller. However, the balancing controller can always be operated in stand-alone configuration with the integrator engaged, which only leads to longer balancing settle time in presence of severe unbalance due to heavy load transients. The BL[k] correction factor is applied to the  $\phi_{1A} + \phi_{1B}$ falling edge and  $\phi_{2A} + \phi_{2B}$  rising edge to achieve a symmetric duty-cycle. In addition, the BL[k] value is added and subtracted from the overall  $\phi_{1A} + \phi_{1B}$  and  $\phi_{2A} + \phi_{2B}$  periods in order the to keep the switching period T constant as shown in equations (7) and (8). The  $\phi_A$  and  $\phi_B$  of each phase are then scaled and calculated accordingly based on SP[k] value by including the offset inserted by BL[k] value as shown by equations (10)-(15). It is important to note that the balancing BL[k]introduces minimal adjustments and asymmetry to  $\phi_{1A} + \phi_{1B}$  and  $\phi_{2A} + \phi_{2B}$  periods and induces minimal effects on the split-phase steady-state operation. Hence a constant SP[k] is used. The only scenario with required large BL[k] offset, and thus inducing significant effect on timing of the split-phase operation, is during the heavy load transients which will take several clock cycle for the flying capacitor to re-enter their balanced steady-state for a minimal BL[k]. Hence minimal efficiency degradation for violation of split-phase timing might occur during the load transients. The DPWM block was designed using a digital counter-based ramp generator, and its threshold computation and comparator blocks of the DPWM are synthesized arithmetic units. The control signal chain and DPWM has a 10mV regulation resolution to prevent limit-cycle given the 5-bit ADC linear steps. The threshold values for start and stop of the split and non-split control signals, as shown in Fig. 2.12, are computed using the discrete time equations below:

$$\Gamma_{\phi_{1S}}[k] = 0 \tag{2.10}$$

$$T_{\phi_{1SP}}[k] = T_{\phi_{1F}}[k] \times SP[k]$$

(2.11)

$$T_{\phi_{1F}}[k] = D[k] - BL[k] \tag{2.12}$$

$$T_{\phi_{2S}}[k] = T_S/2 + BL[k] \tag{2.13}$$

$$T_{\phi_{2SP}}[k] = T_{\phi_{2S}}[k] \times (1 - SP[k]) + T_{\phi_{2F}} \times SP[k]$$

(2.14)

$$T_{\phi_{2F}}[k] = T_S/2 + D[k] \tag{2.15}$$

Figures 2.12 also shows the architecture of the PI compensator and DPWM blocks. The proportional coefficient  $k_P$ , integrator gain  $\beta$  and regulation voltage reference  $V_{ref}[k]$  control parameters as well as the split-phase coefficient  $SP[k] \leq 1$  are programmable through the scan-chain. The regulation PI controller transfer function is shown in the equation below:

$$H[z] = \frac{D[z]}{E[z]} = \frac{1}{1 - \beta z^{-1}} + k_P$$

(2.16)

where  $E[z] = V_{OUT}[z] - V_{ref}[z]$ . The  $k_P = 3$  and  $\beta = 1$  were used for the final measurements. The duty-cycle corrections in steady-state operation are continuously adjusted at each switching cycle based on the comparator's output state. The signal chain design does lead to slight dithering of the output switching node, but its effects are less than the ADC LSB/2 and no limit-cycle

Figure 2.13. Deadtime detector and controller.

behavior is observed. In addition, the regulation controller is running at a slower bandwidth to make the two controllers operation as independent as possible. The SP[k] coefficient was fine tuned in an open loop near the 0.75 theoretical value [24] for both  $\phi_1$  and  $\phi_2$  phases to maximize the efficiency across the converter operating range. Anti-wrapping and limiter blocks are used in the implementation of the integrator loops and PI compensator output, respectively.

#### 2.3.3 Deadtime Controller

Minimizing the deadtime can improve the converter efficiency through reduction of body-diode conduction and charge recovery loss, especially at larger conversion ratios where the shorter dutycycle becomes comparable to the deadtime period. In addition, minimizing the deadtime can improve the flying capacitor balancing at shorter duty-cycle or higher  $f_{SW}$  by providing better ampsecond matching of the converter operating phases. Therefore, an adjustable deadtime controller was implemented in this work.

The two phase operation of hybrid Dickson SC converter requires independent deadtime controllers at each phase, as different set of gate drive signals are in control of deadtime at each phase. The deadtime controller consists of independent adjustable delay line for turn-ON transition, automated turn-OFF transition detectors and a non-overlap generator. The deadtime controller was designed to minimize the body-diode conduction at both transitions. The turn-OFF transition is detected using a tuned inverter with its input connected to the switching node  $V_{SW}$  as shown in Fig. 2.13. The tuned inverter is designed with a 300 mV threshold for a proper deadtime turn-OFF timing. The inverter output is inverted and buffered prior to get connected to the masking signal M of the non-overlap generator as shown in Fig. 2.14. The 20 ns resolution of the DPWM signal is insufficient for deadtime generation of turn-ON transition, as the deadtime can have sub nanosecond periods. Therefore a segmented tapped delay line (STDL) is used to generate the deadtime with 500 ps resolution over a 4-bit control range to cover maximum of 7.5 ns of deadtime for the full load range as shown in Fig. 2.13 and Fig. 2.14. The STDL delay elements are designed using current-starved inverter. The bias current is supplied externally for course tuning and the turn-ON transition deadtime is controlled for fine tuning via the scan-chain at each phase.

#### 2.3.4 Gate-Driver and Voltage Borrowing

The low breakdown voltage of the power switch devices in the available CMOS process places a hard constraint on the maximum allowable power switches voltage stress, including ringing overshoots at the switching transitions. The ringing is a by-product of parasitic inductance in the

Figure 2.14. Segmented tapped delay line and non-overlap clock generator.

conduction current loop. In order to decrease the ringing amplitude and thus the overall voltage stress across the power switches, it is desired to reduce both the di/dt and the parasitic inductance L. The parasitic inductance can be reduced through careful layout and packaging while di/dt can be reduced using circuit and control techniques. The segmented gate-driver works on the principle of limiting the di/dt through shaping the  $V_G$  profile for a slow switching of the MOSFET until most of the current  $I_{DS}$  is conducted across the drain-source terminals. When the  $V_G$  reaches the plateau voltage and slightly above, the MOSFET is nearly conducting the full  $I_{DS}$  current. The reminder of the transition period doesn't involve large di/dt. Therefore, a plateau voltage detector can be used to increase the remaining  $V_G$  profile transition rate to reduce the overall transition period and hence the overlap loss. The proposed segmented gate-driver for achieving low ringing and overlap loss is shown in Fig. 2.15 along with the described operation principle in Fig. 2.16. As shown in Fig. 2.16, the turn-ON and turn-OFF transitions of the power switches are divided into two regions. The region boundary is defined by the plateau voltage  $V_{Plateau}$  of the switches. As shown in Fig. 2.15 a weak gate-driver is used to turn-ON the power switch device with a slow rising  $V_G$  profile up to the plateau voltage to limit di/dt, therefore reducing the ringing overshoot. The  $V_{Plateau}$  is then detected through a tuned feedback inverter from  $V_G$  to enable the strong driver and increase the  $V_G$  profile transition rate, therefore reducing the overall transition period and overlap loss. The tuned inverter is designed with the threshold slightly above the  $V_{Plateau}$  of its corresponding power switch. The worst-case equivalent series inductance (ESL) parasitic of 1 nH, obtained through multiphysics simulation of die floorplan and co-packaging solution, is considered in the design of the segmented gate-driver. The ESL parasitic includes series combination of the

Figure 2.15. Segmented gate-driver design with weak and feedback activated strong driver.

Figure 2.16. Segmented gate-driver vs. non-segmented voltage and current profile.

Figure 2.17. The ringing simulation results (a) without segmented gate-driver, (b) with segmented gate-driver.

power switch, layout interconnects, FC and high-density interposer (HDI) package as well as ESL of the flying capacitors in the conduction current loop. Figure 2.17 compares the current through each flying capacitor and the voltage ringing across the ESL parasitic of each conduction current loop with and without employing the segmented gate-driver. The simulation results shown in Fig. 2.17 indicate a minimum of 2.4X ringing reduction with the segmented gate-driver.

Figure 2.18. Gate-driver voltage borrowing in the time domain and corresponding gate drive signals.

| Gate-Driver | Supply Source       |  |  |

|-------------|---------------------|--|--|

| $GD_{1-2}$  | $V_{AUX}$           |  |  |

| $GD_3$      | $V_{C_2}$           |  |  |

| $GD_4$      | $V_{C_1}$           |  |  |

| $GD_5$      | $V_{C_2} - V_{sw}$  |  |  |

| $GD_{6-7}$  | $V_{C_3} - V_{C_1}$ |  |  |

| $GD_8$      | $V_{IN} - V_{C_2}$  |  |  |

Table 2.3. Gate-driver voltage borrowing technique.

The gate-driver requires a stable voltage to operate reliably. The traditional way of providing power to a floating gate-driver is by use of bootstrap technique. The bootstrap techniques [35, 36] requires a large capacitor, typically an order of magnitude larger than the gate capacitance to avoid large voltage droop at the switching instances. Given the low capacitor density in 65 nm bulk CMOS process, addition of the bootstrap capacitor on-die can occupy a large area and decrease the power density of the converter significantly. The circuit topology of the Dickson SC converter makes it possible to use the flying capacitors to also serve as the source for gate driving. Therefore, a voltage borrowing technique [38] was adopted to supply the gate-driver by selection of proper voltage nodes in the converter as shown in Fig. 2.7. Table 2.3 provides a listing of the voltage borrowing sources. The time domain borrowed voltages and corresponding gate drive signals are shown in Fig. 2.18, where the required gate drive voltage of  $V_{IN}/2$  is available during the active periods of  $GD_5$  and  $GD_8$  as well as a constant voltage of  $V_{IN}/2$  for  $GD_3$ ,  $GD_6$  and  $GD_7$ . The voltage borrowing technique imposes a negligible voltage imbalance across the flying capacitors as charges are being asymmetrically redirected for gate-driving. However, the charge recycling due to the embedded connectivity across capacitors and gate-drivers in addition to the active balancing circuit makes the converter operates on a fully balanced state.

#### 2.3.5 Level-Shifter

The higher complexity SC converter with floating power switches and gate-drivers requires control signal level shifting. In addition, the charge flow should be precisely timed for a balanced flying capacitor voltage in steady state operation. Therefore, a reliable level-shifter with minimized delay and transient response is a crucial specification in the design of hybrid SC converters. The

Figure 2.19. Static level-shifter and level-translator circuits with delay compensation.

level-shifter should also have minimum performance variations over the  $V_{IN}$  voltage range. The static level-shifter and level translator used in this work are shown in Fig. 2.19. The power switches  $MN_1$  and  $MN_2$  are directly driven from the controller using the level translator. The power switches  $MN_3$  to  $MP_8$  are controlled using level-shifters. The level-shifter consist of the bottom-side driver, the voltage follower, the high-side latch and the level restorer. The bottom side driver and voltage follower should be designed stronger than the high side latch for minimum delay [37]. The propagation delay matching among level-shifter/translator is maintained through equal  $V_{HIGH} - V_{LOW}$  and individual device sizing.

#### 2.3.6 Scan-Chain and External Control

The scan-chain was designed for direct access to control signals  $DG_{1-8}$  for debugging and external control through pins  $S_{1-8}$ , as shown in Fig. 2.7 by bypassing the internal controller. The scan-chain was synthesized and operates at 100 kHz provided by the DCM block. The external controller was also used during the precharge start-up and shut-down sequences. The start-up and shut-down sequences are initiated by disabling the internal controller and activating the  $MN_1$  and  $MN_2$  ground referred power switches. The voltage on the flying capacitors are then ramped-up or ramped-down through an external resistive voltage divider and transmission gates as shown in Fig. 2.20.

Figure 2.20. External start-up circuit and shut-down circuit.

Figure 2.21. Die micrograph and system components.

#### 2.4 Experimental Results and Measurements