# Physically Aware Design of Generated Systems-on-Chip

John Wright

# Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2022-248 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-248.html

December 1, 2022

Copyright © 2022, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

Acknowledgement

This work was supported by the following grants:

- NASA ESTO IIP grant number NNX12AK39G.

- DARPA PERFECT award HR0011-12-2-0016.

- Intel ISTC on Agile Design.

- STMicroelectronics.

- DARPA CRAFT grant HR0011-16-C0052

- NSF grant number 2016662.

- Other BWRC, ASPIRE, and ADEPT sponsors

Physically Aware Design of Generated Systems-on-Chip

by

John Charles Wright

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Elad Alon Professor Robert Leachman

Summer 2021

Physically Aware Design of Generated Systems-on-Chip

Copyright 2021 by John Charles Wright

#### Abstract

### Physically Aware Design of Generated Systems-on-Chip

by

John Charles Wright

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

Generator-based integrated-circuit design flows are crucial for meeting the aggressive systemon-chip development timelines demanded by rapidly changing modern workloads. Generators allow chip designers to develop complex solutions to classes of problems rather than individual instances, allowing significant design changes late in the development cycle and enabling incremental improvements to existing solutions. The philosophies of welcoming changing requirements and steady, incremental development have been embraced by the software development community for some time, but have only recently been incorporated into hardware development. While this adoption of proven software development philosophies has decreased the turnaround time of systems-on-chip, productivity has been limited by hard-to-automate tasks like physical design. Each generated design instance requires a new human-generated floorplan or other changes to the physical design flow, limiting the throughput of design space exploration by the available engineering resources. Automation of physical design is therefore critical for state-of-the-art generator-based system-on-chip design.

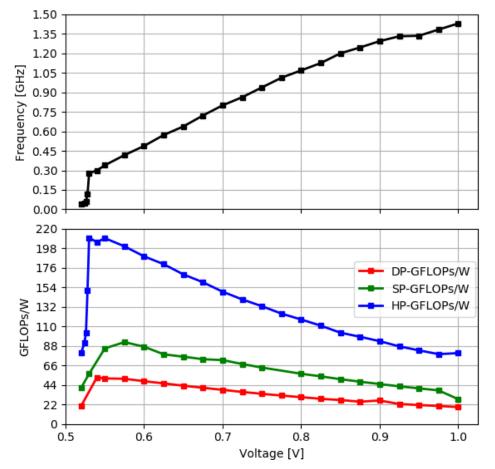

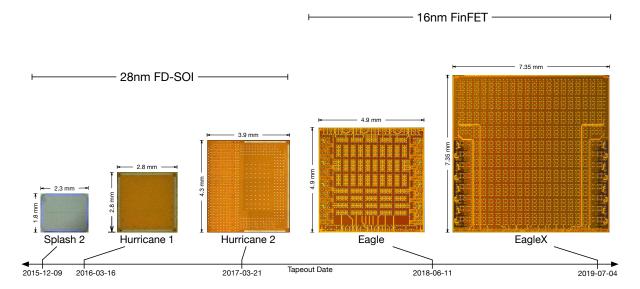

This work describes a series of generator-based integrated circuits manufactured in 28nm FD-SOI and 16nm FinFET, outlines the physical design challenges encountered in their development, and presents a physical design methodology purpose-built to solve these challenges. The integrated circuits presented include an 8192-point digital spectrometer in 28nm FD-SOI, a dual-core RISC-V vector processor with on-chip fine-grain power management in 28nm FD-SOI, a dual-lane RISC-V vector processor with a dedicated on-chip power management core in 28nm FD-SOI, an eight-core RISC-V vector machine in 16nm FinFET, and a 21-core RISC-V vector machine with a systolic array accelerator in 16nm FinFET. The eight-core chip achieves a state-of-the-art energy efficiency of 209.5 GFLOPS/W on a half-precision matrix multiplication (GEMM) kernel.

The physical design methodology presented uses a framework, Hammer, to provide reusable physical design deliverables by decoupling the design-specific, tool-specific, and technologyspecific aspects of back-end design along with a novel floorplan generation framework for Chisel designs. This physical design methodology has been incorporated into the Chipyard framework, an open-source RISC-V system-on-chip development platform leveraging the Chisel hardware construction language. The floorplan generation framework allows Chisel programs, which generate RTL, to specify composable floorplans without modifying the original source code. The flow solves common challenges associated with floorplanning generated RTL, such as SRAM mapping and placement, demonstrating the efficacy of floorplan generation in reducing the overhead and cycle times of generator-based design.

To my wife, Xuân, and our unborn son.

# Contents

| Co            | onter | nts    |                                                        | ii           |

|---------------|-------|--------|--------------------------------------------------------|--------------|

| $\mathbf{Li}$ | st of | Figure | es                                                     | $\mathbf{v}$ |

| $\mathbf{Li}$ | st of | Tables | 5                                                      | vii          |

| $\mathbf{Li}$ | st of | Listin | gs                                                     | viii         |

| 1             | Intr  | oducti | on                                                     | 1            |

|               | 1.1   | Motiva | ation                                                  | 1            |

|               | 1.2   | Backg  | round                                                  | 2            |

|               |       | 1.2.1  | Fundamentals of VLSI design                            | 2            |

|               |       | 1.2.2  | Impact of technology scaling on system architecture    | 6            |

|               |       | 1.2.3  | Generator-based design                                 | 9            |

|               |       | 1.2.4  | Chipyard: An Agile generator-based SoC flow            | 9            |

|               |       | 1.2.5  | Challenges with generator-based design                 | 13           |

|               |       | 1.2.6  | Floorplanning concepts                                 | 14           |

|               |       | 1.2.7  | State-of-the-art placement and floorplanning           | 17           |

|               | 1.3   | Disser | tation scope and outline                               | 17           |

| <b>2</b>      | Inte  | grated | l Circuit Designs in 28nm FD-SOI                       | 19           |

|               | 2.1   | Splash | 12: Digital ASIC Spectrometer                          | 20           |

|               |       | 2.1.1  | Background                                             | 20           |

|               |       | 2.1.2  | Architecture                                           | 21           |

|               |       | 2.1.3  | Results                                                | 24           |

|               |       | 2.1.4  | Physical design challenges                             | 24           |

|               | 2.2   | Hurric | cane1: A Dual-Core RISC-V SoC with DVS                 | 28           |

|               |       | 2.2.1  | Background                                             | 28           |

|               |       | 2.2.2  | Architecture                                           |              |

|               |       | 2.2.3  | Results                                                | 33           |

|               |       | 2.2.4  | Physical design challenges                             | 36           |

|               | 2.3   | Hurric | cane2: A RISC-V SoC with Dual-Lane Vector Unit and DVS | 38           |

|   |                                                | $2.3.1 \\ 2.3.2 \\ 2.3.3 \\ 2.3.4$                                                 | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38<br>39<br>40<br>44                                                                                                                                                                  |

|---|------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 | Gen<br>3.1<br>3.2                              | Eagle:<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                         | Multicore Systems-on-Chip in 16nm FinFET         An 8-core Generated RISC-V SoC         Background         Architecture         Results         Physical design challenges         Signound         Architecture         Background         An 21-core Generated RISC-V SoC         Background         Architecture         Background         Architecture         Background         Architecture         Physical design challenges         Results and future work | 47<br>48<br>49<br>53<br>55<br>66<br>66<br>66<br>67<br>69<br>76                                                                                                                        |

| 4 | Han<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5         | Motiva<br>Hamm<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Techno<br>4.4.1              | A Physical Design Generator Platform<br>tion                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li><b>79</b></li> <li><b>79</b></li> <li><b>80</b></li> <li><b>80</b></li> <li><b>82</b></li> <li><b>83</b></li> <li><b>90</b></li> <li><b>91</b></li> <li><b>92</b></li> </ul> |

| 5 | Floc<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Archite<br>Floorp<br>5.2.1<br>5.2.2<br>Floorp<br>5.3.1<br>5.3.2<br>Chisel<br>Examp | Floorplan IR design                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>96</b><br>97<br>101<br>104<br>105<br>107<br>109<br>111<br>112<br>115<br>120                                                                                                        |

6 Conclusion

iii

|         | Summary of contributions |     |

|---------|--------------------------|-----|

| Bibliog | raphy                    | 124 |

# List of Figures

| 1.1  | An example of metal layer design rules                                       | 5 |

|------|------------------------------------------------------------------------------|---|

| 1.2  | Cost per 100 million gates across process technologies as of 2016            | 7 |

| 1.3  |                                                                              | 8 |

| 1.4  | A comparison of Agile vs. waterfall development methodologies                | 0 |

| 1.5  | An example of a simple floorplan                                             | 5 |

| 1.6  | An example of a hierarchical floorplan                                       | 6 |

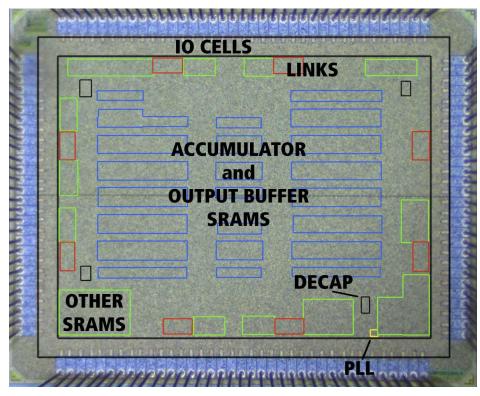

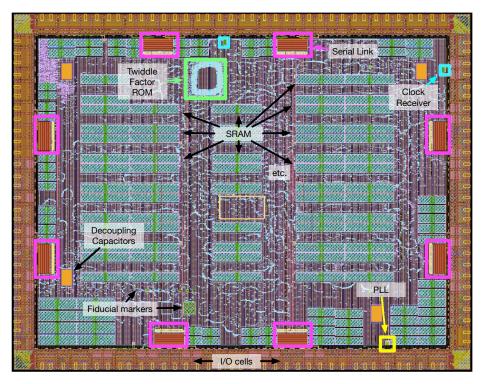

| 2.1  | Annotated Splash2 die micrograph                                             | 0 |

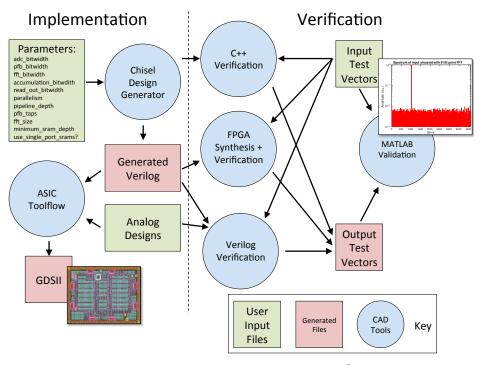

| 2.2  | The Splash2 generator flow                                                   | 1 |

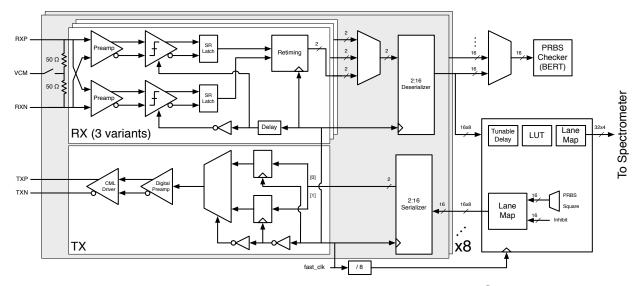

| 2.3  | The Splash2 ADC interface using serial links                                 | 2 |

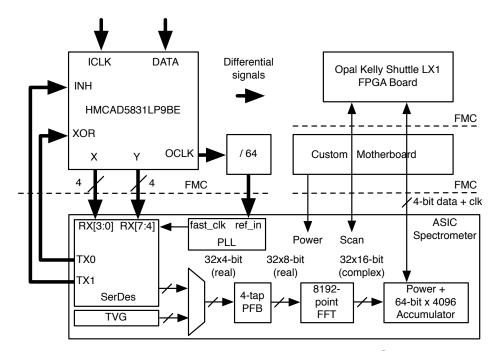

| 2.4  | The Splash2 system block diagram                                             | 3 |

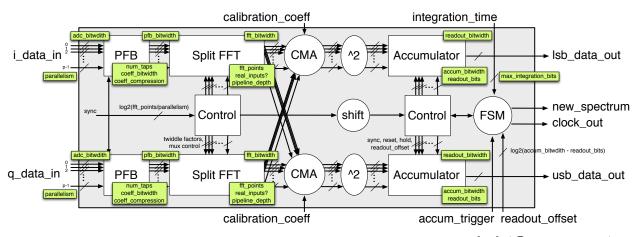

| 2.5  | The Splash2 spectrometer generator microarchitecture                         | 3 |

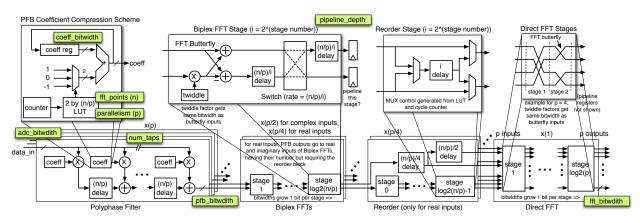

| 2.6  | The Splash2 polyphase filter and streaming FFT generator microarchitecture 2 | 4 |

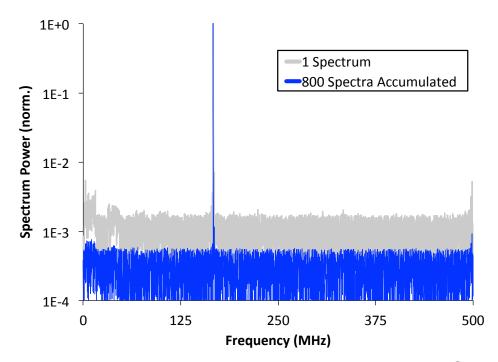

| 2.7  | Splash2 measured spectra at a 1 GHz sample frequency                         | 5 |

| 2.8  | Splash2 floorplan showing the highly congested twiddle factor ROM and SRAM   |   |

|      | macro placement                                                              | 7 |

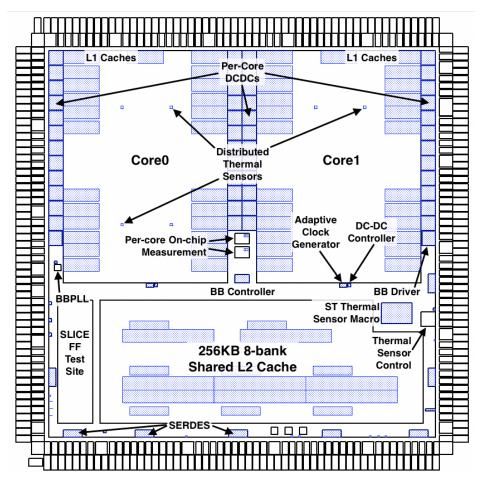

| 2.9  | Annotated Hurricane1 die micrograph                                          | 8 |

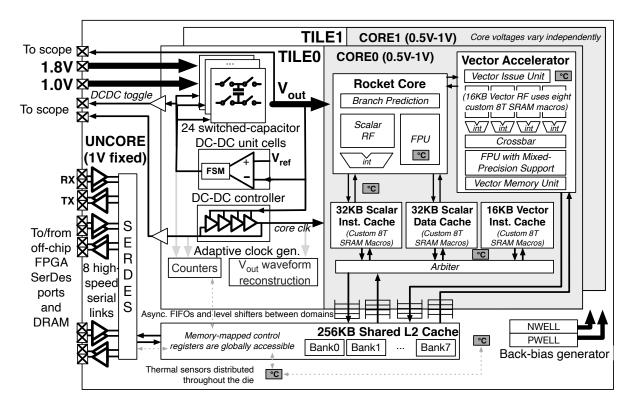

| 2.10 | Hurricane1 block diagram                                                     | 0 |

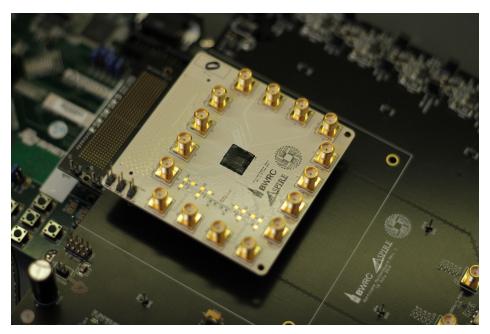

| 2.11 | Hurricanel board photo                                                       | 1 |

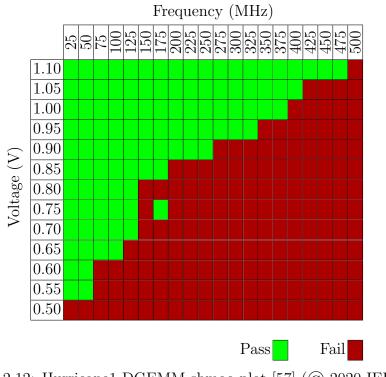

| 2.12 | Hurricane1 DGEMM shmoo plot                                                  | 2 |

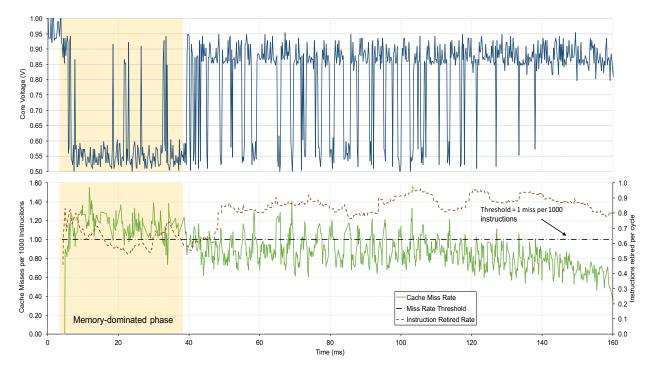

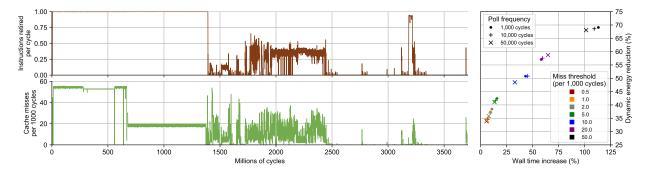

| 2.13 | Hurricane1 DC-DC mode transitions in response to cache activity for a matrix |   |

|      | multiplication workload                                                      | 3 |

| 2.14 | Hurricane1 architectural simulation of Linux boot and energy analysis at     |   |

|      | 0.9V/250MHz and $0.55V/50MHz$ operating modes                                | 4 |

| 2.15 | Annotated Hurricane1 floorplan                                               | 6 |

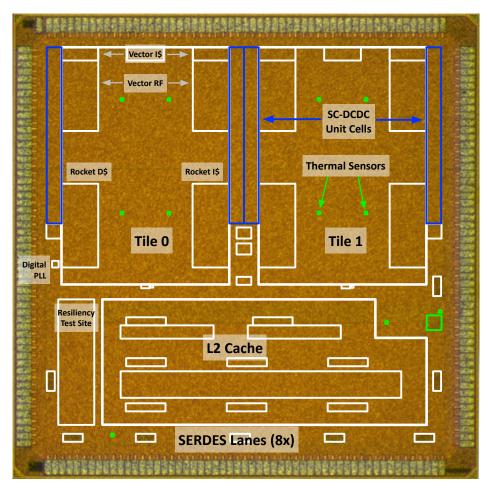

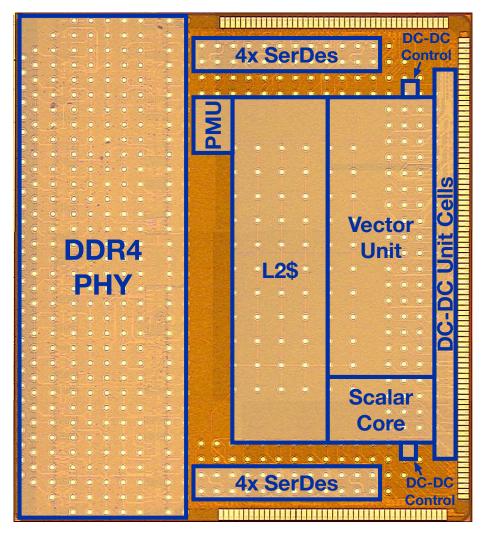

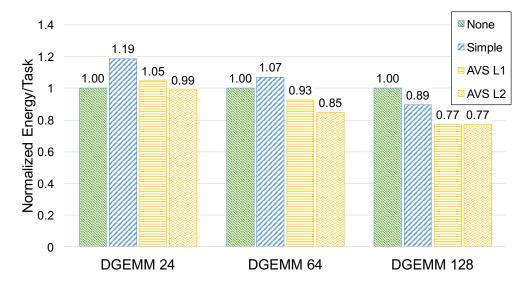

| 2.16 | Annotated Hurricane2 die micrograph 3                                        | 8 |

|      | Hurricane2 block diagram                                                     | 1 |

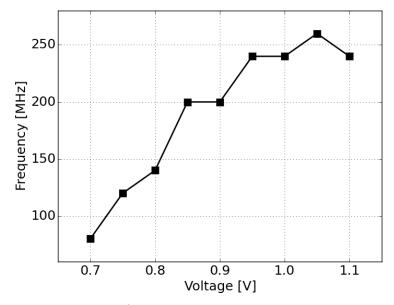

| 2.18 | Maximum operating frequency versus core supply voltage on Hurricane2 4       | 3 |

| 2.19 | Comparison of Hurricane2 AVS algorithms                                      | 4 |

| 2.20 | Annotated Hurricane2 floorplan                                               | 6 |

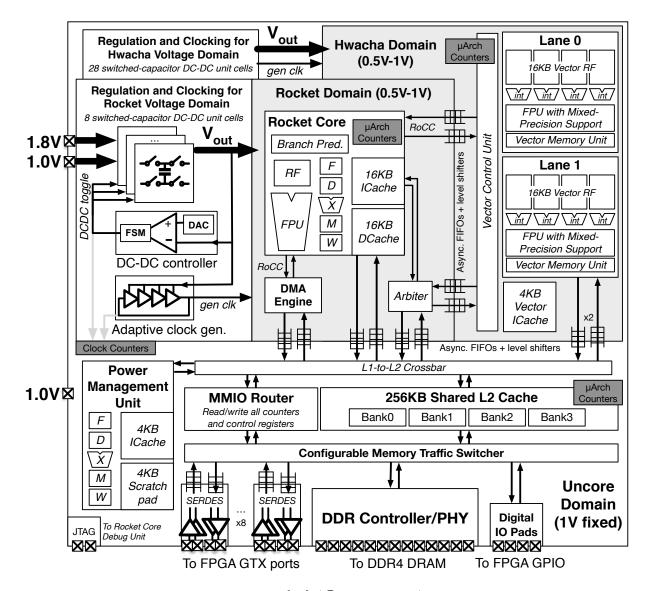

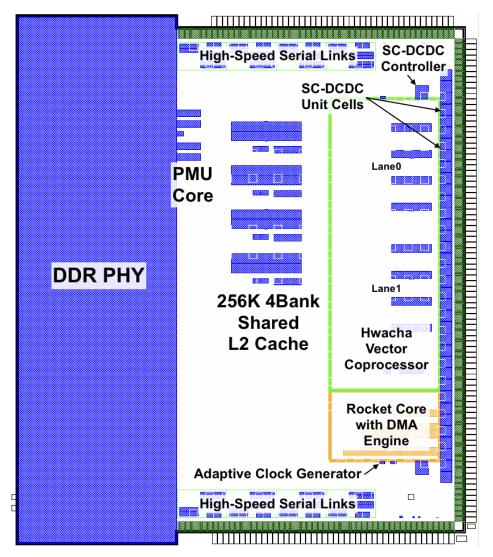

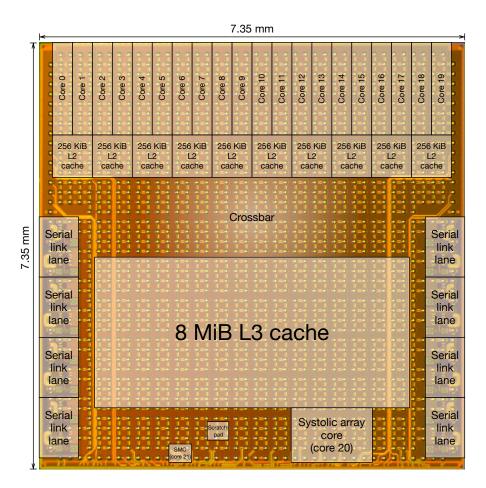

| 3.1  | Annotated Eagle die micrograph                                               |   |

| 3.2  | Eagle chip generation flow                                                   | 9 |

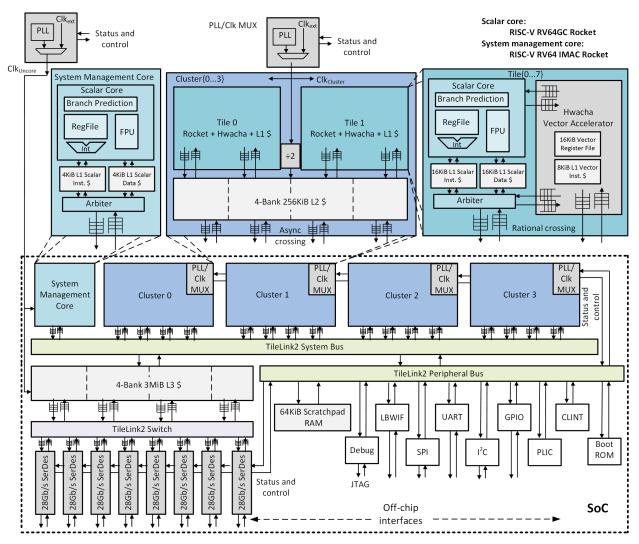

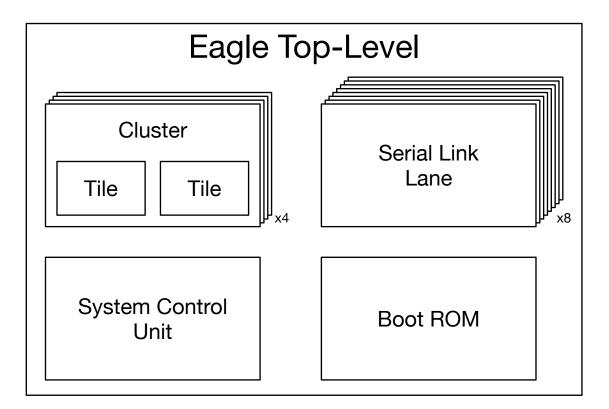

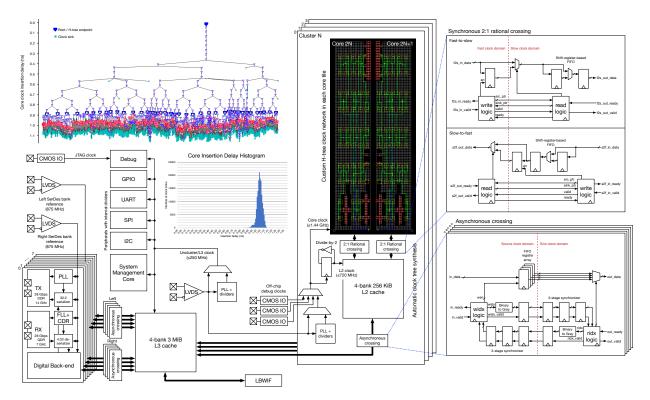

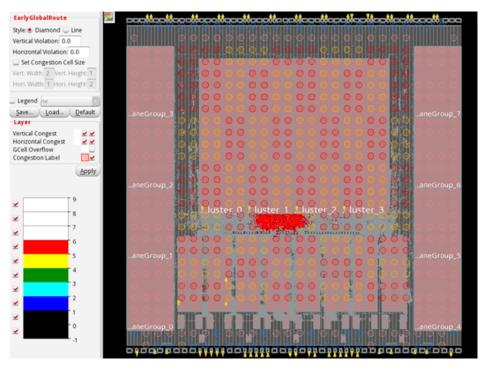

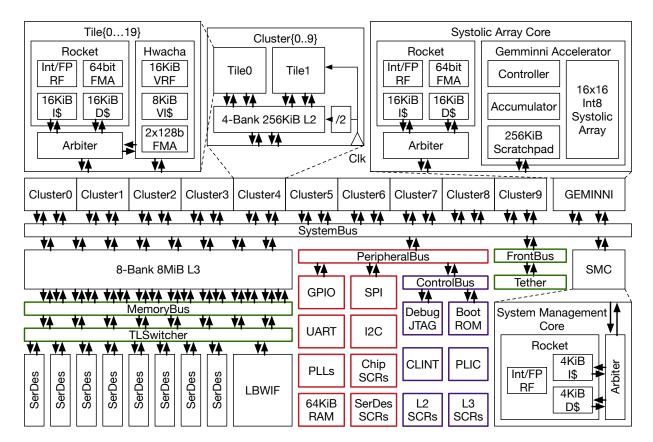

| 3.3  | Eagle block diagram                                                              | 50  |

|------|----------------------------------------------------------------------------------|-----|

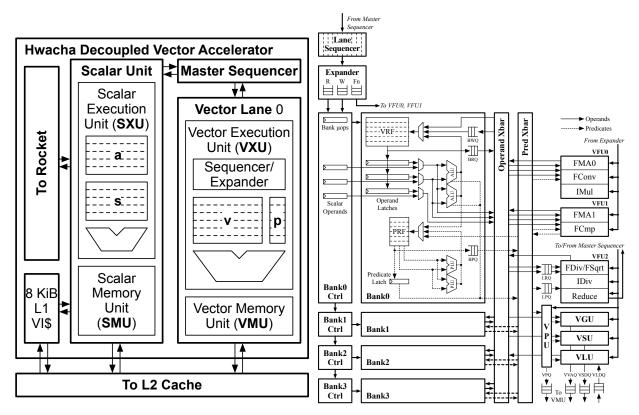

| 3.4  | Block diagram of the Hwacha vector unit on Eagle                                 | 51  |

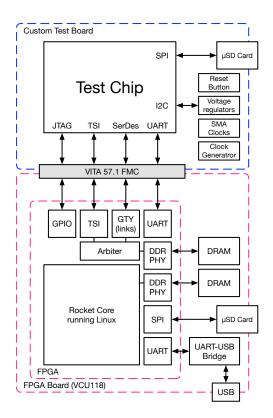

| 3.5  | Eagle test setup and block diagram                                               | 52  |

| 3.6  | Eagle test board on lab bench with labeled components                            | 52  |

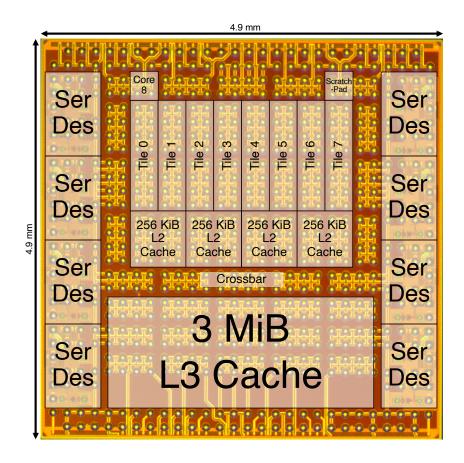

| 3.7  | Eagle maximum frequency and GEMM energy efficiency                               | 53  |

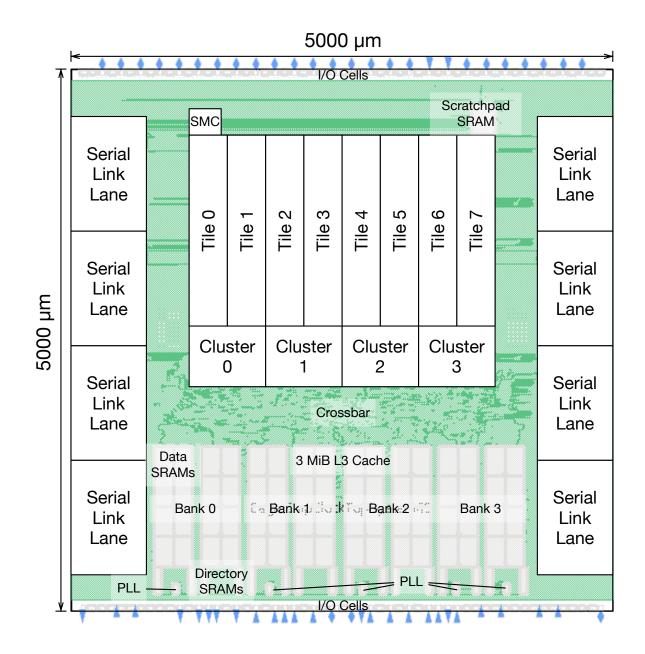

| 3.8  | Annotated Eagle chip floorplan                                                   | 56  |

| 3.9  | Physical design hierarchy of Eagle                                               | 57  |

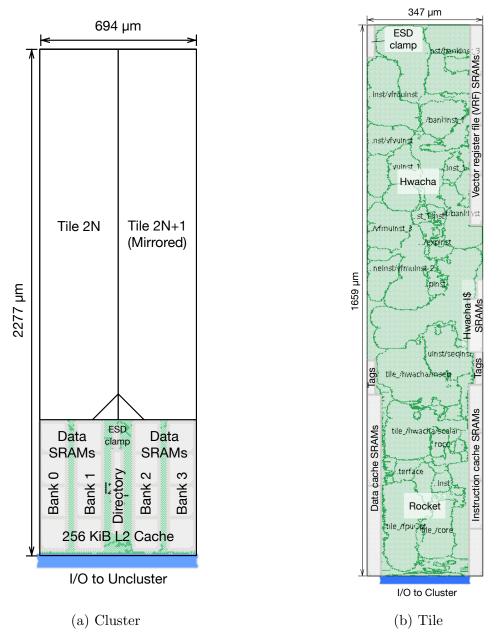

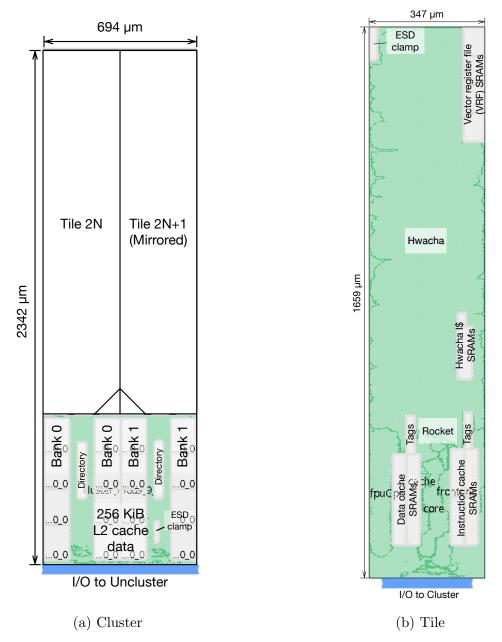

| 3.10 | Eagle cluster and tile floorplans                                                | 58  |

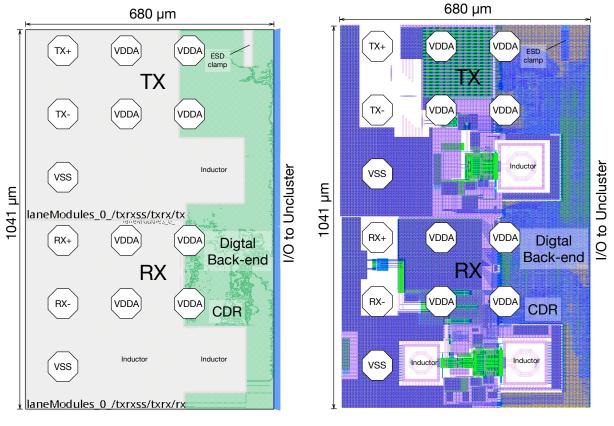

| 3.11 | Eagle serial link lane floorplan and layout                                      | 59  |

| 3.12 | Eagle PCB footprint                                                              | 60  |

|      | Eagle clocking diagram                                                           | 61  |

|      | An example of multi-voltage power straps on EagleX using a 1:3 supply ratio      | 63  |

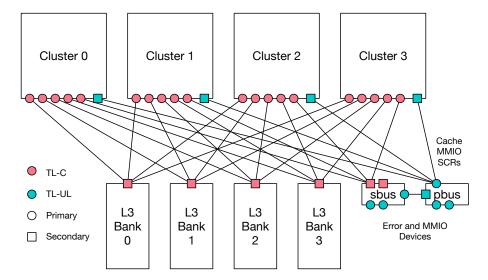

|      | Eagle crossbar topology                                                          | 64  |

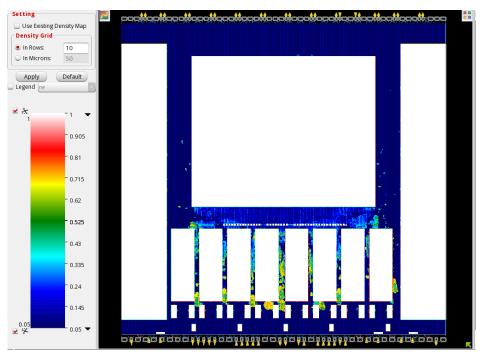

|      | Low placement density in area with high routing density on Eagle                 | 65  |

|      | Example of routing congestion in a large crossbar on Eagle                       | 65  |

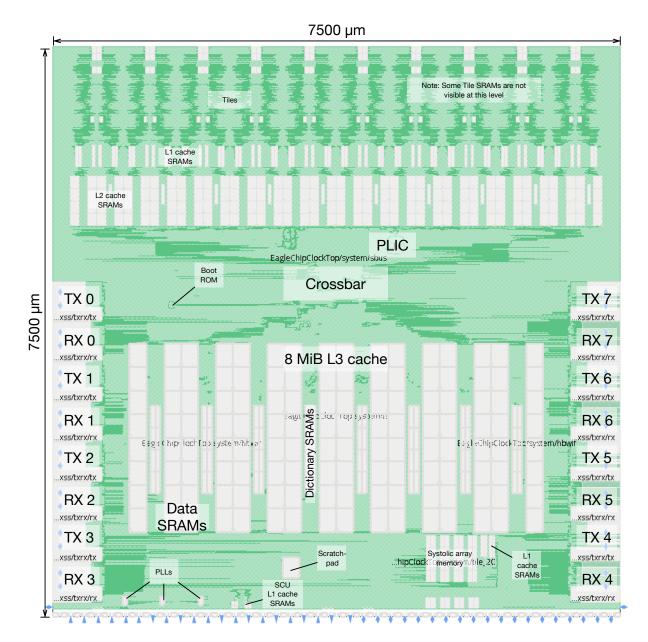

|      | Annotated EagleX die micrograph                                                  | 66  |

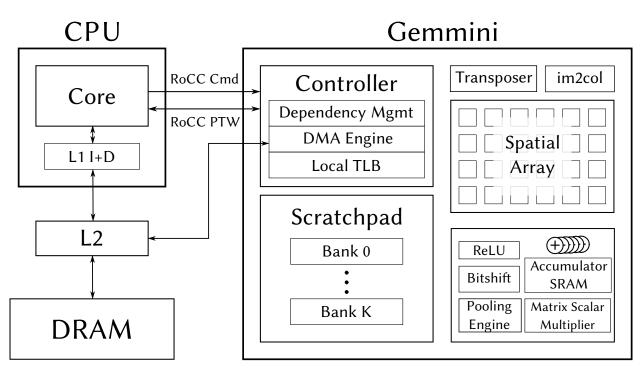

|      | EagleX block diagram                                                             | 67  |

|      | EagleX systolic array accelerator architecture                                   | 68  |

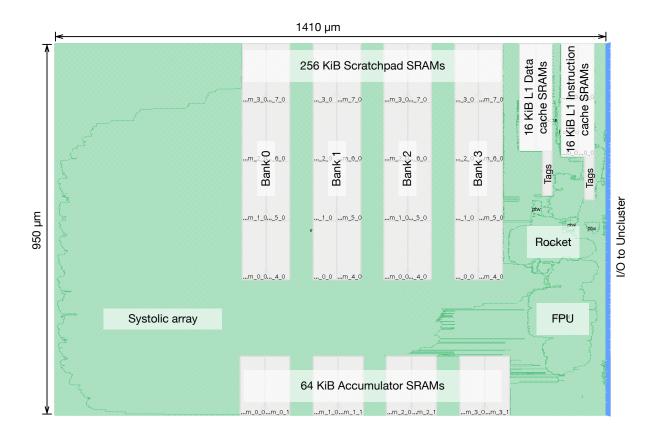

|      | EagleX chip floorplan (hierarchical)                                             | 69  |

|      | EagleX chip floorplan (flat)                                                     | 70  |

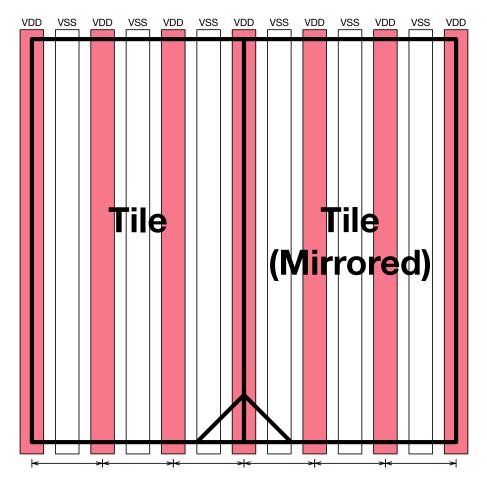

|      | Power strap alignment on mirrored tiles                                          | 71  |

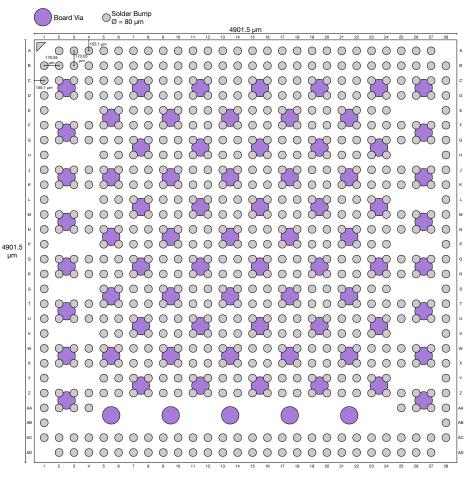

|      | EagleX bump designations                                                         | 72  |

|      | EagleX BGA package pinout                                                        | 73  |

|      | EagleX cluster and tile floorplans                                               | 74  |

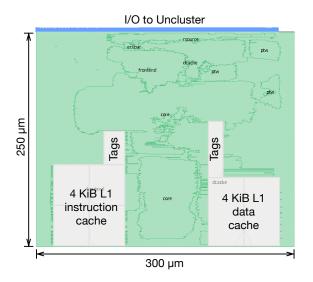

|      | EagleX system management core floorplan                                          | 75  |

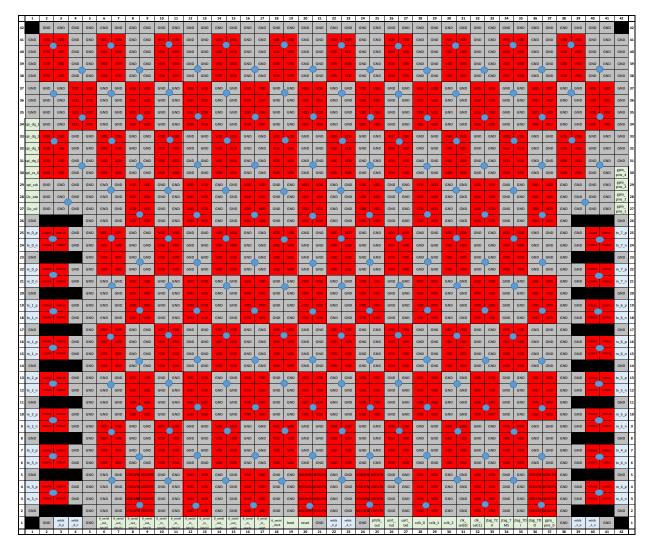

|      | Floorplan of the EagleX systolic array accelerator with its CPU core             | 78  |

|      |                                                                                  |     |

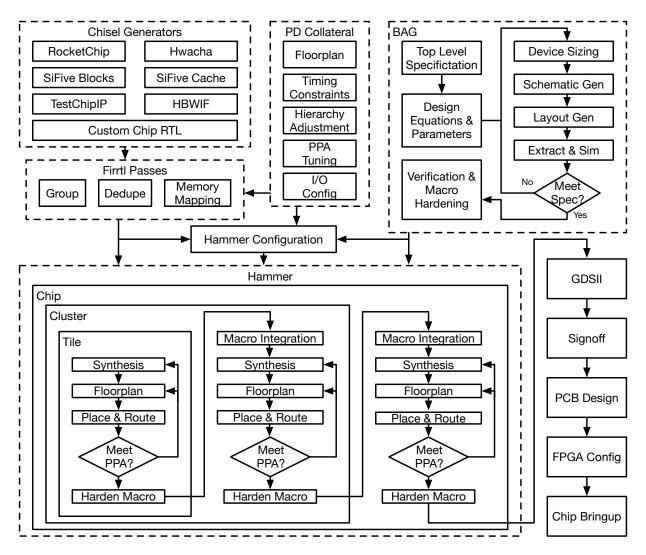

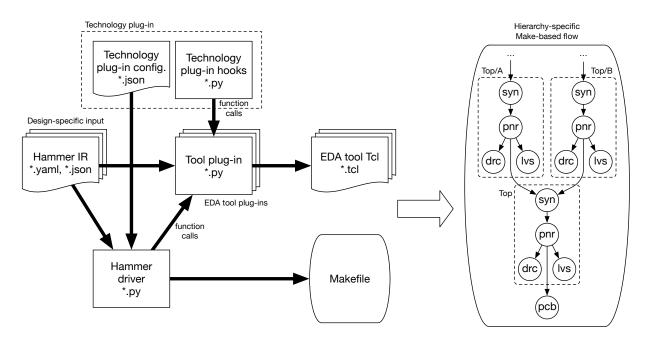

| 4.1  | Hammer design flow                                                               | 81  |

| 4.2  | Simple power strap generation using the Hammer power strap generation $API$ .    | 93  |

| 4.3  | An example of sparse and dense power straps using ASAP7                          | 95  |

| 5.1  | Chisel SRAM floorplanning flow without automation                                | 97  |

| 5.2  | Chisel SRAM floorplanning flow with automation                                   | 97  |

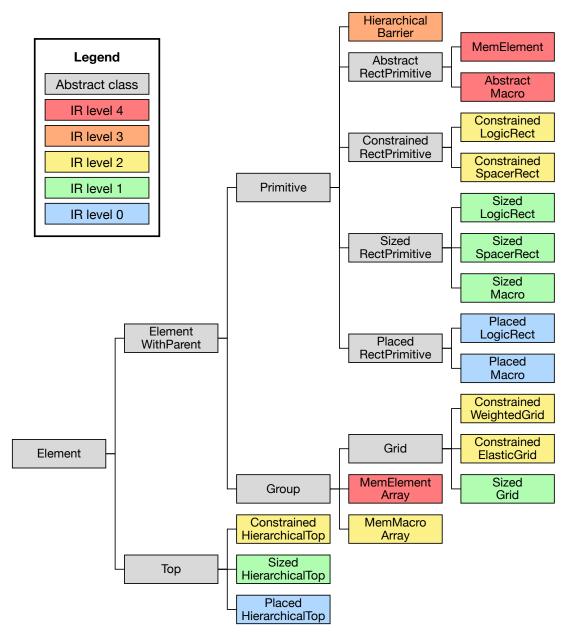

| 5.3  | Floorplan IR class hierarchy and levels                                          | 102 |

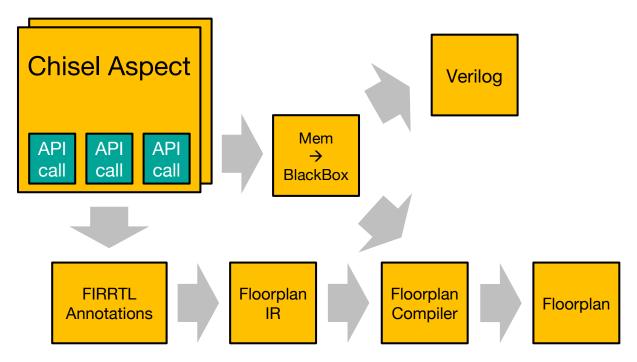

| 5.4  | Chisel floorplan compiler flow                                                   | 109 |

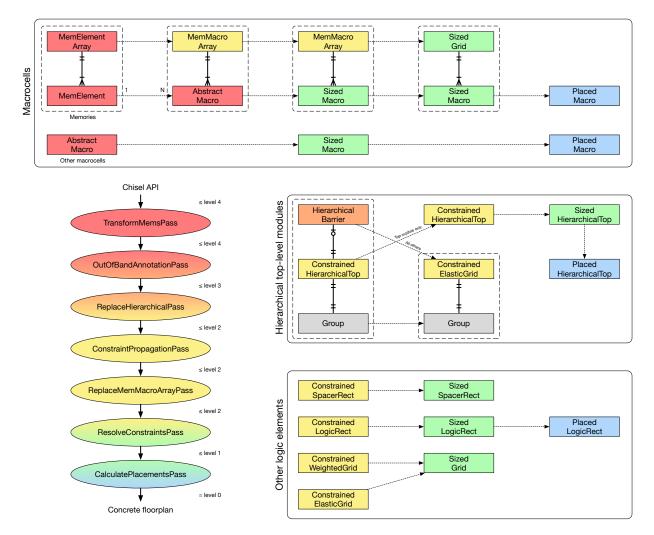

| 5.5  | Floorplan compiler passes and FPIR lowering flows                                | 110 |

| 5.6  | SRAM mapping using the floorplan compiler                                        | 111 |

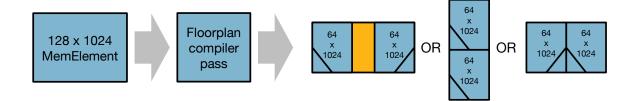

| 5.7  | SRAM legalization flow using the floorplan compiler                              | 112 |

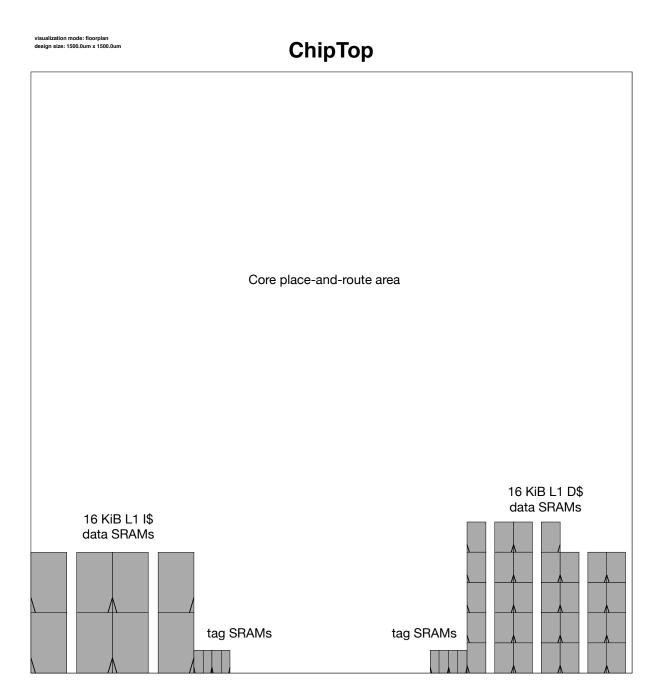

| 5.8  | Annotated floorplan of a single-core ChipTop using the generators shown in List- | ±±4 |

| 0.0  | ing 5.6 and Listing 5.5 and visualized using Hammer                              | 119 |

| 6.1  | Die micrographs of the chips presented in this dissertation to scale             | 121 |

| 0.1  | Die interographie of the emps presented in this dissertation to scale            | 141 |

# List of Tables

| 1.1 | Examples of CAD tool applications                                                                                             | 4  |

|-----|-------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Splash2 compared with state-of-the-art ASIC spectrometersHurricane1 compared with prior artHurricane2 compared with prior art | 35 |

| 3.1 | Eagle compared with prior art                                                                                                 | 54 |

# List of Listings

| 3.1 | EagleX running Linux on the twenty main applications cores                 | 77  |

|-----|----------------------------------------------------------------------------|-----|

| 4.1 | Example Hammer IR (YAML format) excerpt from EagleX                        | 85  |

| 4.2 | An example defaults.yml for Vivado synthesis                               | 86  |

| 4.3 | An excerpt from the plug-in file for Vivado synthesis                      | 87  |

| 4.4 | An excerpt from the ASAP7 technology JSON file                             | 88  |

| 4.5 | An abridged Makefile for a hierarchical Hammer flow                        | 90  |

| 4.6 | Hammer IR to specify power straps in ASAP7 using the by_tracks power strap |     |

|     | generation API                                                             | 94  |

| 5.1 | Serialized floorplan IR example                                            | 103 |

| 5.2 | Example of a floorplan compiler memory instance map file                   | 107 |

| 5.3 | Example of an out-of-band annotation file setting memory dimensions        | 108 |

| 5.4 | A simple example floorplan generator                                       | 114 |

| 5.5 | Floorplan generator code for RocketTile modules                            | 117 |

| 5.6 | Floorplan generator code for a ChipTop modules                             | 118 |

### Acknowledgments

I am tremendously grateful for the help and support I received throughout my doctoral studies. Berkeley is uniquely collaborative, and I am fortunate to have worked with numerous brilliant minds during my time here. While I am appreciative of everyone I met throughout this adventure, the following colleagues, mentors, faculty, staff, and friends deserve special recognition. I apologize in advance to any deserving individuals that I may have missed.

First and foremost, I am grateful to have had Bora Nikolić as an advisor. Bora, you are uniquely skilled in identifying problems that are simultaneously interesting to industry and academia. I continue to be impressed by your breadth and depth of knowledge, your ability to keep up with the state of the art, and your ability to drive projects of massive scope to success. There is simply no way I could have had the opportunity to tape out so many times, in such advanced process nodes, or such large chips without your leadership. I believe your continuing push for agile hardware development is producing a generation of ASIC designers who think so differently that we will feel the impact industry-wide. I will miss your ComIC group meeting stories and will have to find some new way of keeping up with the latest industry gossip.

I am thankful to have had additional guidance from Elad Alon and Krste Asanović. Elad, your support throughout the Eagle project was incredibly helpful, especially when the hours grew long and deadlines started passing. I appreciate your willingness to jump on Slack calls at 4 A.M. to hack on RTL alongside the grad students to keep the tapeout moving. I also enjoyed working with and learning from you and your students on the serial link generator project. Krste, thank you for your support throughout all the tapeouts and project meetings and for making me feel welcome to participate in projects with the Berkeley Architecture Research group. I eagerly look forward to seeing what's next for RISC-V. I would also like to thank Vladimir Stojanović for serving on my qualifying exam committee, reading my M.S., and otherwise being available for discussion. Likewise, I thank Rob Leachman for serving on my qualifying exam and dissertation committees and Jonathan Bachrach and Sophia Shao for their help along the way.

I am indebted to a number of people in the broader engineering community for their guidance as well. Todd Hastings and Bruce Walcott (University of Kentucky), thank you for getting me started in research and sending me down this path. Scott Savage and Joseph Elias (Infineon), thank you for providing recommendations and encouragement. It was a tough decision to leave a full-time job to return to school, and I appreciate your candid advice and assistance to do what you believed to be in my best interest. Mohamed Abu-Rahma and Jared Zerbe (Apple), thank you for your mentorship and the thought-provoking technical discussions. The opportunity to work on cutting-edge projects at Apple provided meaningful insight and context to the work I did at Berkeley. Mark Rowland and Steve Burns (Intel), your feedback at the many ASPIRE and ADEPT retreats was useful and entertaining. It's not always clear that we are moving in the right direction, and confirmation (bonus points) from our industrial sponsors is always welcome. Rajeev Jain (Qualcomm), your affirmation of the usefulness of many components of this dissertation was rewarding as well. I appreciate the deep technical discussions I had with you and others at Qualcomm in the denouement of my graduate career. Masood Qazi (Qualcomm), thank you for the advice you gave along the way. I'm happy to have overlapped with you at Cypress and Apple and hope we'll one day overlap again.

Much of the work presented in this dissertation required custom fabrication and assembly of chips, packages, circuit boards, et cetera. There are many who helped with this, but I owe a few individuals special mentions; thank you. Mo Ohady (Digicom Electronics) was available off-hours for special assembly requests to meet paper deadlines and always enthusiastic to work with Berkeley. Gary Thorne (MOSIS) helped with our GDS submissions, and I would especially like to thank him for enduring so many slips and being available for the final EagleX submission on the 4th of July holiday. Linton Salmon (DARPA) led the CRAFT program, which made a large portion of this work possible. Andreia Cathelin (STMicroelectronics) championed many of the earlier tapeouts in my graduate career (Splash2, Hurricane1, Hurricane2). Hien Ly, Quyen Chu, and Sundar Sethuraman (Jabil Blue Sky) helped by experimenting with aggressive die attach techniques and gave us a lab tour. Didier Campos and Vince Mangion (STMicroelectronics) designed the Hurricane2 package. Pierre Brunet (EuroCan) designed the EagleX package when many others would not. Darin Heckendorn (Cadence) provided invaluable support of the tool flow for Eagle and EagleX.

Within Berkeley, we are lucky to have talented research staff to help ensure the success of these projects. Brian Richards is a vault of tapeout knowledge and spent many hours helping with every project I worked on. Thank you for all you do to keep the BWRC tapeout machine running. Anita Flynn is a PCB wizard, human confusion detector, and bug catcher. Thank you for all your hard work on the Hurricane<sup>2</sup>, Eagle, and Eagle<sup>X</sup> boards; they are works of art. James Dunn, your curiosity and excitement is enviable, and I hope you continue to have such passion. Thank you for helping with sysadmin, lab, and PCB tasks over the years. Shirley Salanio does so much behind-the-scenes work to help every EECS grad student stay on track with program requirements. Thank you for all your help over the years, and especially for helping with the flurry of questions about Summer filing procedures. Candy Corpus and Yessica Bravo, thanks for organizing social events and generally making BWRC a happy place. Greg Pearson and Jeff Anderson-Lee, thanks for keeping the compute servers up and running despite my best efforts to fill up the file system. Chick Markley, thanks for all the interesting discussions and scala whispering. I also thank Kostadin Ilov, Ria Briggs, Tami Chouteau, Fred Burghardt, Mikaela Cavizo-Briggs, Ken Lutz, Melissa Trevizo, Olivia Nolan, Amber Sanchez, and Erin Hancock.

A large portion of this work was done in collaboration with Colin Schmidt, who has become a great friend and a colleague I hope to continue working with in the future. Somehow after all of the all-night Slack calls, frustrating bring-up puzzles, and tapeout delays, you still kept a positive attitude. I'm indebted to you for all the help you provided, all your code reviews, and support throughout the whole process.

I also thank the following individuals for their technical contributions. Dan Werthimer and Robert Jarnot contributed significantly to the Splash2 architecture and guided the project. Zhongkai Wang drove the SerDes generator development for the Eagle tapeout with the help of Eric Chang, Paul Kwon, and Woorham Bae. Howie Mao wrote a large number of RTL widgets we used for every tapeout. Adam Izraelevitz built Chisel Aspects, which is an integral component of the floorplan generator. Albert Ou wrote RTL and software and helped with bring-up for the Hurricane and Eagle tapeouts and was also willing to answer many of my silly RISC-V and Linux questions. Edward Wang led the Hammer project and designed and built much of its infrastructure, which made the Eagle, EagleX, and floorplanning work in this dissertation possible. Vighnesh Iyer helped with many different FPGA designs and automated the build flow. Jingyi Xu, Ryan Lund, Anson Tsai, and Gary Choi were wonderful undergraduate and master's researchers who helped with various aspects of these projects.

I'm happy to have had the support of many other friends and colleagues at BWRC throughout this journey as well. Antonio Puglielli, thank you for being a dependable backpacking adventure-buddy and jib-trimmer. Krishna Settaluri, thank you for being a good motivator and for all the lighthearted jokes. Luke Calderin, you are a fantastic co-skipper of The Floating Node, even though we never did sail to a retreat, and for that I salute you. Nathan Narevsky, thanks for always showing up early to help set up the party and for enduring Zoom thesis-writing sessions with me. Ozzy LaCaille, thank you for the coffee walks, the complaining sessions, and the Tide Pod. Sameet Ramakrishnan, thanks for all the brainstorming sessions, entertaining sports bets, and, of course, getting me a job. Pavan Bhargava, thanks for always bringing a delicious dish and for joining in our adventures. Stevo Bailey, thanks for dragging me to Core Blast, for showing me the ropes in the early days, and for your upbeat attitude. Ben Keller, thanks for your leadership on the Hurricane projects, for your activism, and for taking all my extra tomato plants. Alon Amid, in addition to all your help with paper writing and Chipyard, thanks for introducing us to Bamba and always bringing an interesting story to Thanksgiving. Paul Rigge, thanks for always having an interesting perspective and for explaining scala nuances in great detail. Keertana Settaluri, thanks for being my over-the-divider buddy. Daniel Grubb and Harrison Liew, I appreciate your senses of humor; thank you for joining us in the trenches of the 2019 tapeouts and for carrying the baton to keep many of these projects alive. Rachel Hochman, thank you for throwing fancy parties and always being supportive and positive. Nandish Mehta, thank you for providing many laughs and, of course, your dal makhani. Mira Videnović-Mišić, thank you for your genuine kindness and always bringing delicious treats to share. Ajith Amerasekera, thank you for always being available for a quick chat at Triple Rock.

There are many other BWRC students and visitors who impacted my time here, and I'd like to thank a few of them as well: Brian Zimmer, Jaehwa Kwak, Amy Whitcombe, Milos Jorgovanović, Pi-Feng Chiu, Martin Cochet, Jarno Salomaa, Guillaume Bonnechère, Angie Wang, Matthew Anderson, Lorenzo Iotti, Nick Sutardja, Katerina Papadopoulou, Marko Kosunen, Sean Huang, Sam Steffl, Zhenghan Lin, Yue Dai, Zhaokai Liu, Vladimir Milovanović, Emily Naviasky, Christos Adamopoulos, Sidney Buchbinder, Andy Zhou, and Chris Yarp. Thanks for your help, and thanks for keeping BWRC lively. I'd also like to acknowledge some additional members of the ASPIRE/ADEPT labs: Abe Gonzalez, Jerry Zhao, Sagar Karandikar, Albert Magyar, David Biancolin, Nathan Pemberton, Hasan Genc, Ameer Haj-Ali, Eric Love, Kevin Laeufer, Yunsup Lee, Andrew Waterman, Palmer Dabbelt, and Jack Koenig. Thanks for making my up-the-hill time enjoyable.

Outside of the Berkeley community, I have been fortunate to have the support of many loving friends and family, most of whom are not explicitly named here but are appreciated nonetheless. I would like to thank Alex Heilman specifically for his encouragement to pursue a Ph.D. and his support throughout. My parents, Bonnie and Randy, instilled a respect and admiration of higher education in me from a young age. I appreciate their unrelenting encouragement throughout this long endeavor. I also think my brother, Clay, for coming to visit and keeping me upbeat.

Finally, I owe all of this to my loving wife and life co-captain, Xuân. She not only endured all of the all-nighters, the months-long tapeout pushes, retreats, quals, etc., but she also provided much-needed graduate school advice, helped me edit papers, and critiqued my figures along the way. I appreciate your sacrifices and understanding that helped get me through this, and look forward to our next big step coming very soon. I love you and thank you.

# Funding

I thank the sponsors of this work for their financial support and for providing multiple opportunities to tape out on expensive process nodes. The Splash2 project was supported by NASA's Earth Science Technology Office Instrument Incubator Program as part of the Compact, Adaptable Microwave Limb Sounder project, grant number NNX12AK39G. The Hurricane1 and Hurricane2 projects were supported in part by Defense Advanced Research Projects Agency (DARPA) Power Efficiency for Embedded Computing Technologies (PER-FECT) award HR0011-12-2-0016 and in part by the Intel Science and Technology Centers (ISTC) on Agile Design. Fabrication of Splash2, Hurricane1, and Hurricane2 was donated by STMicroelectronics. The Eagle, EagleX, and Hammer projects were supported by DARPA Circuit Realization at Faster Timescales (CRAFT) grant HR0011-16-C0052 and the Intel ISTC on Agile Design. The Chipyard project was funded by NSF grant number 2016662. I also thank the sponsors of the Berkeley Wireless Research Center, ASPIRE, and ADEPT labs for additional funding that supported this work.

# Contributions to this work

RocketChip is an open-source IP initially developed at UC Berkeley and now maintained by SiFive. Chisel and FIRRTL are open-source projects developed and maintained by numerous people at Berkeley and elsewhere. The Splash2 ASIC development was led by Stevo Bailey. Vladimir Milovanović contributed the PLL design. Nandish Mehta contributed the serial link receiver design for Splash2, Hurricane1, and Hurricane2. The Hurricane1 and Hurricane2 ASIC development was led by Ben Keller. Cadence Design Systems donated the DDR PHY for Hurricane2, and the DC-DC converters were reused from prior projects. The Eagle and EagleX projects were co-led with Colin Schmidt. Sean Huang built the PLL based on previous work by Vladimir Milovanović. Zhongkai Wang, Eric Chang, and Woorham Bae built the serial links for Eagle and EagleX. Colin Schmidt and Albert Ou developed the Hwacha accelerator for Hurricane1, Hurricane2, Eagle, and EagleX. SiFive donated the L2 and L3 cache generator RTL for Eagle and EagleX. Hasan Genc, Ameer Haj-Ali, Vighnesh Iyer, and Alon Amid developed the Gemmini accelerator for EagleX. The Hammer project was led by Edward Wang.

# Chapter 1

# Introduction

# 1.1 Motivation

Throughout the second half of the twentieth century, integrated circuit (IC) designers enjoyed a consistent improvement in process technology as famously predicted by Gordon Moore [1]. This period saw everything from the first integrated circuits with only a handful of transistors visible by the naked eye to quarter-micron microprocessors running at sub-nanosecond clock periods [2]. While Moore's law continued into the early twenty-first century, another oncedependable law authored by Robert Dennard began to break down. In his paper [3], Dennard noted that the increases to power caused by increasing transistor density and frequency were offset by decreasing supply voltage. In the mid-2000s, Dennard scaling began to slow due to the increasing effect of leakage power at short channel lengths, a phenomenon also known as the "Power wall" [4].

Reaching the power wall forced IC designers to improve performance in new and creative ways—primarily via the introduction of multicore processor chips [5]. As state-of-the-art transistor feature sizes approach fundamental limits, it is reasonable to assume the end of Moore's Law is also imminent and that similar creativity will be required to continue advancing processing capability. This, along with the surge in compute-intensive workloads like deep neural networks, has led to increased use of specialized compute accelerators on modern systems-on-chip (SoCs) [6–9]. With the changes to these workloads outpacing typical IC design cycles, it is becoming increasingly necessary to make improvements to IC design methodology to shorten these design cycles [10–12].

Generators, software programs capable of producing instances from a larger class of possible configurations, have been shown repeatedly to improve IC design productivity [13–15]. When building digital components, the primary focus of generators thus far has been to produce logical circuit descriptions (register-transfer level, or RTL) and any necessary verification and integration collateral. When generating only a small component of a larger system, this is often sufficient, as the generated component is not likely to require a custom floorplan. However, when generating more complex components, components with large

numbers of memory macrocells, or full SoC designs, the overall cycle time improvement offered by the RTL generator is limited by the manual back-end implementation cycle, which is frequently dominated by the creation of an instance-specific floorplan. It is therefore desirable that generators should not only produce logical descriptions of configured instances but also produce a floorplan for each generated instance in order to maximize the productivity gains afforded by generator-based design.

This dissertation presents multiple systems-on-chip manufactured in advanced process nodes build using generator-based design flows. The lessons learned from these tapeouts are motivate a physical design methodology, which is also presented. This physical design methodology has been incorporated into the open-source Chipyard [16] framework and includes both a physical design generator framework, Hammer [17], and a novel floorplanning framework for Chisel designs.

# 1.2 Background

## 1.2.1 Fundamentals of VLSI design

Very-large-scale integration (VLSI) is the process of manufacturing integrated circuits (ICs) with large numbers of transistors and has existed in different forms since the 1970s. In a traditional design flow, the VLSI design process begins with the creation a high-level architectural description of the entire system, including both on-chip and off-chip elements. The architectural description includes every aspect of the design required for software programmers to use the system without specific implementation details. Next, one or more microarchitectures are created to implement the specified architecture. These microarchitectures include the circuit-level implementation details, down to the signal level, needed to create a functioning design. An implementation team uses this information to build a logical schematic, a detailed description of devices<sup>1</sup> and their connections, and a layout, a representation of physical geometries that implements them.

The semiconductor integrated circuit manufacturing process consists of a series of steps which manufacture the devices themselves, called front-end processing, and the metal wires that connect them, called back-end processing. Each process step may use one or more photomasks to restrict the affected area to the unique geometries for a specific design. The set of geometries for a single photomask and processing step combination is often termed a layer, or, less commonly, level. Thus, the layout for an integrated circuit design will consist of geometries on multiple layers.

The layers in a layout are specific to a process technology, often shortened to process or technology, meaning that the geometries on them are generally are not portable to other process technologies<sup>2</sup>. A process technology is a series of repeatable recipes used to manufac-

<sup>&</sup>lt;sup>1</sup>In digital designs, a device often refers to a transistor, but integrated circuits usually include other classes of devices, including resistors, inductors, capacitors, fuses, and diodes.

<sup>&</sup>lt;sup>2</sup>This has a number of implications on the reusability of design work, which are discussed in Chapter 4.

ture integrated circuits in a semiconductor fabrication plant ("Fab"). Many different circuit designs will use the same process technology with different, unique photomasks to achieve different functionality.

In the early years of semiconductor manufacturing, the integrated circuit design firm would also own the fab. While this afforded circuit design groups the luxury of highly customizable manufacturing processes, the economy of scale eventually drove a majority of the industry to use what is known as the "Fabless" model, where integrated circuits are designed and manufactured by separate entities through contract manufacturing. The contract manufacturing companies offer a menu of process technologies, amortizing the cost of research, development, and capital expenditure over a large volume of products from multiple customers.

Modern VLSI design utilizes a wide range of computer-aided design (CAD) tools to automate labor-intensive tasks that were previously performed manually. A modern tool flow for digital design primarily focuses on three tasks: synthesis, placement, and routing. A synthesis tool consumes a logical description of a circuit, typically Verilog, SystemVerilog, or VHDL, and produces a gate-level netlist, which is a textual representation of logic gate instances and their connections, called nets. These logic gates come from a processspecific library provided by the fab, developed internally, or acquired from a third party. These libraries contain combinational and sequential logic elements, standard cells, built from transistors and are designed so that the cells fit into a grid and can be tiled easily by an automated tool. The placement tool, or placer, will consume this netlist along with cell layout information and use heuristics to determine the placement of each logic cell within the specified die area. The placer will also replace cells with larger<sup>3</sup>, logically equivalent cells to meet circuit timing goals specified by the user at the cost of additional power and area. The router is then responsible for creating wires to connect the placed cells using the available metal routing layers in the process technology. Placement and routing are often implemented as steps within a single CAD tool, a place-and-route tool, which gives it the ability to perform multiple iterations of incremental placement and routing to achieve area and timing goals, the latter of which is colloquially termed "Closing timing." Table 1.1 lists common CAD tool types in a typical flow.

Floorplanning also includes creation of routing blockages and routing guides, which help the tool avoid areas that create problematic routing congestion or design rule violations. Floorplans can similarly include placement blockages to prevent the tool from placing standard cells in unwanted regions, often to prevent spacing-related design rule violations.

The synthesis and place-and-route tools require additional information for macrocells included in the design. Macrocells, or macros, are circuit components that do not conform to the standard cell tiling scheme and are usually much larger than any single standard cell. Until recently, placement tools have required the user to manually determine placements for macrocells, creating what is known as a floorplan. There is a research trend moving towards

<sup>&</sup>lt;sup>3</sup>Larger in this context can either mean physically larger transistors in the drive stage or transistors with a lower threshold voltage, or both.

| Tool                             | Purpose                                  | Input                                | Output                           |

|----------------------------------|------------------------------------------|--------------------------------------|----------------------------------|

| Synthesis                        | Convert RTL to gates                     | RTL                                  | Gate-level<br>netlist            |

| Place-and-route<br>(P&R)         | Create a physical layout of gates        | Gate-level<br>netlist                | Layout,<br>Gate-level<br>netlist |

| Design rule checker<br>(DRC)     | Check manufacturability of layout        | Layout                               | Report                           |

| Layout versus<br>schematic (LVS) | Check that layout matches schematic      | Layout,<br>Gate-level<br>netlist     | Report                           |

| RTL Verilog<br>simulation        | Simulate a design                        | RTL,<br>stimulus                     | Waveforms                        |

| Gate-level Verilog<br>simulation | Simulate a design                        | GL netlist,<br>stimulus              | Waveforms                        |

| Power analysis                   | Analyze dynamic and leakage power        | GL netlist,<br>waveforms             | Report                           |

| SPICE simulation                 | Analyze analog and mixed signal circuits | SPICE<br>netlist,<br>stimulus        | Waveforms                        |

| Characterization                 | Create timing models for library cells   | Waveforms                            | .lib files                       |

| Static timing<br>analysis (STA)  | Analyze digital circuit timing           | Gate-level<br>netlist, .lib<br>files | Reports                          |

Table 1.1: Examples of CAD tool applications.

applying machine-learning techniques to automate this process, with reinforcement-learning techniques able to beat humans in some situations [18], but human experts are currently still competitive. A system-on-chip will include many different types of macrocells, some of which perform logical functions in the circuit and others that are necessary for electrical functionality or manufacturability. The most common macrocell with logical functionality in a digital design is a synchronous random-access memory (SRAM), which is an area- and energy-efficient circuit for storing state within a design.

After a place-and-route tool has created a layout, designers begin what is known as "Signoff," the process of confirming that the layout is manufacturable and meets specifications.

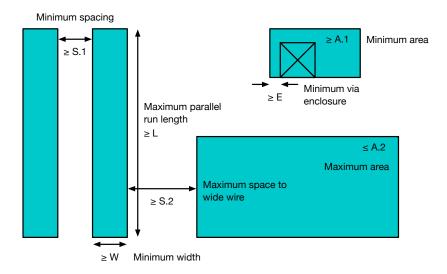

Figure 1.1: An example of metal layer design rules.

Design rule checking (DRC) checks every shape in the layout against a set of procedural rules, sometimes called a deck, to verify that the design is manufacturable. Simpler rules, like checking minimum spacing between two polygons on the same layer or checking that a single polygon meets a minimum area constraint, tend to be derived from the capabilities of the lithography process. More complex rules check for hard-to-simulate electrical issues like latch-up, an effect where parasitic bipolar transistors can cause positive feedback that destroys the chip. An example of common DRC rules for metal layers is shown in Figure 1.1, although modern process nodes have many more complex conditions than can be easily shown in a single figure. DRC is very parallelizable, but even so can take from hours to days for a full chip due to the vast number of polygons in a full chip layout. For digital flows, DRC rules tend to be related to routing, but sometimes also involve standard cell or macro placement. Placement issues are always solved with tool script changes, but routing issues are sometimes fixed by hand by correcting the tool-generated paths with custom shapes. However, most tool-generated routes for properly configured designs will have no violations.

Layout versus schematic (LVS) checks that the final layout matches the schematic, which captures the intended functionality for a chip. This tool extracts a comparison schematic from the layout and uses an algorithm to correlate the devices and nets between the two schematics. Analog components on the chip will use a SPICE netlist for the schematic, while digital components generally use Verilog to specify the gate-level netlist along with the SPICE netlists for the standard cells instantiated within. Any unintended changes, shorts, or other problems will be flagged in the tool report. When given a good floorplan and proper constraints, the place-and-route tool will produce a layout that matches the schematic, however routing congestion will lead to opens or shorts on nets that the tool cannot route properly. Custom routing, power nets, or nets inside of black boxes can also create LVS problems that the place-and-route tool is unable to fix. For these reasons, it is imperative to audit the place-and-route tool output with LVS to ensure the design will function as intended.

Static timing analysis (STA) calculates the timing paths in the design by summing the incremental cell and wire delays using pre-characterized delay models. These timing paths start from clocks or constrained inputs and end at sequential data pins or constrained outputs. Any paths that violate setup or hold constraints<sup>4</sup> are reported so that the designer can fix them with RTL or physical design changes. For production designs, STA is run at multiple process, voltage, and temperature (PVT) corners to ensure the design has sufficient margin to tolerate variations in manufacturing and a range of environmental conditions.

STA is also used to generate timing annotations, which are applied to gate-level Verilog simulations to simulate the implemented design while modeling real delays. This is useful for verifying that the gate level design still functions as the RTL intended and for generating accurate waveforms for power simulation. Improper RTL structures or custom changes to the netlist within the CAD tools can result in gate-level netlists which do not function identically to the RTL. Logical equivalency checking (LEC) is another tool that uses formal methods<sup>5</sup> to prove equivalence between gate-level netlists and RTL. There are many other signoff flows not discussed here; the specific concerns of the designers and goals for the design will determine what additional signoff is required.

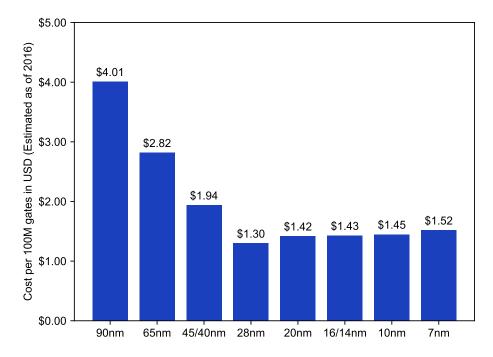

### **1.2.2** Impact of technology scaling on system architecture

Once the 28nm process node saw widespread adoption and volume production, per-transistor costs in new nodes no longer continued to steadily and reliably decline [19, 20], shown in Figure 1.2. This has the effect of decreasing margins for comparable designs, increasing the volume required to amortize the non-recurring engineering (NRE) and capital expense required to fabricate (tape out) a new design, exacerbated by the increasing number of masks required for multiple patterning<sup>6</sup> [21]. Designers of new low-volume, special-purpose systems-on-chip must decide between staying at a cost-efficient process node like 28nm or by increasing price to recoup margins, which may lose customers to cost-competitive, higher-volume, general-purpose chips.

To bridge the gap between fixed-function ASICs and general-purpose processors, a growing trend is the use of highly specialized accelerators [22–24], which are compute engines tuned to a specific workload or family of workloads that can be added to a conventional system-on-chip platform to complement the general-purpose central processing units (CPUs). These accelerators vary in programmability, with highly programmable accelerators offering

$<sup>^{4}\</sup>mathrm{There}$  are other constraint types, including recovery, removal, and minimum pulse width, which are not discussed here.

<sup>&</sup>lt;sup>5</sup>Not to be confused with formal verification.

<sup>&</sup>lt;sup>6</sup>Multiple patterning may be obviated by extreme ultraviolet (EUV) lithography, but this comes with its own challenges and costs.

Figure 1.2: Cost per 100 million gates across process technologies as of 2016 [20].

more flexibility but lower cost and power savings than their less-flexible counterparts. While accelerators have uses in all process nodes, they are increasingly being used to improve performance in older nodes while avoiding the increased tapeout costs associated with cuttingedge nodes. This is especially useful for medium- and low-volume parts, which have trouble recouping these costs.

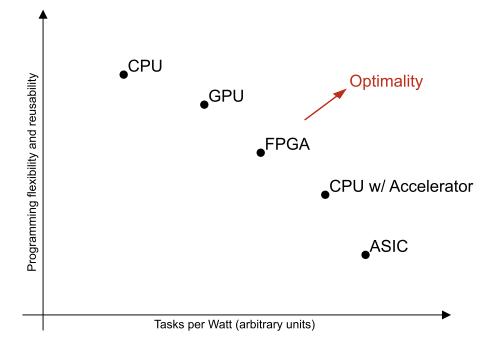

The CPU-with-accelerator approach is an important data point on a spectrum of solutions that provide chip designers options for trading flexibility for cost, energy-efficiency, or both for a given application. Figure 1.3 illustrates a set of design paradigms that span the range of flexibility options. General-purpose CPUs are the least energy-efficient as they rely on pure software implementations of workloads and are unable to exploit temporal locality as efficiently as specialized accelerators, requiring many data to be transferred to and from DRAM multiple times. Systems targeting aggressive workloads will also require multiple or large CPUs to meet the equivalent performance of more specialized solutions, increasing their cost. Graphics processing units (GPUs) can be more energy-efficient than CPUs on tasks with high levels of data parallelism, but this caveat inherently renders them less flexible than CPUs. Popular modern workloads like deep neural networks and blockchain technology are examples of these tasks with high levels of data parallelism.

Like GPUs, field-programmable gate arrays (FPGAs) can provide advantages over CPUs for specific workloads. Unlike GPUs and CPUs, FPGAs are not programmed with software, rather relying on the user to provide a hardware description to create custom connections on a pre-fabricated logic array. The maximum clock frequency of an FPGA is usually lower

Figure 1.3: Pareto-optimal frontier of compute acceleration.

than that of a CPU or GPU—hundreds of Megahertz versus Gigahertz—but FPGAs can be configured with custom data paths that perform computation in a single cycle equivalent to many CPU instructions. These FPGA designs can be used in products, but for a given number of logic gates, FPGAs are much larger and more expensive than application-specific integrated circuits (ASICs) due to the configuration overhead, so products which use FPGAs tend to be very low volume. While FPGAs are technically very flexible by virtue of being highly configurable, the difficulty of programming them and the relatively low number of people with the required skill set makes them a more specialized approach than either CPU or GPU software programming. Purpose-built ASICs offer the highest level of customization, performance, and energy-efficiency by offering the same custom data paths available to FPGAs but with much higher clock frequencies and lower power. ASICs, however, cannot be reconfigured in the field like FPGAs, making them the least flexible of all design paradigms. The CPU-with-accelerators scheme combines aspects of ASICs with general-purpose CPUs, resulting in a design that is slightly more flexible than a pure ASIC, but with additional software programmability. By effectively utilizing this gamut of design styles, chip designers can design in process nodes behind the leading edge to produce high-performance parts that meet specific needs while maintaining cost efficiency.

### 1.2.3 Generator-based design

Generator-based design has become increasingly popular as specialized ASIC designs have become more prevalent. Generators have been shown to improve the productivity of ASIC designers [13–15] and will be an important design component for specialized ASIC designs as they become commonplace. Generator-based design differs from a traditional design methodology by focusing on the development of large classes of designs rather than a single design instance. The productivity gains by this may seem counter-intuitive at first, but the ability to change significant design parameters rapidly allows designers to defer critical decision-making until more information is available.

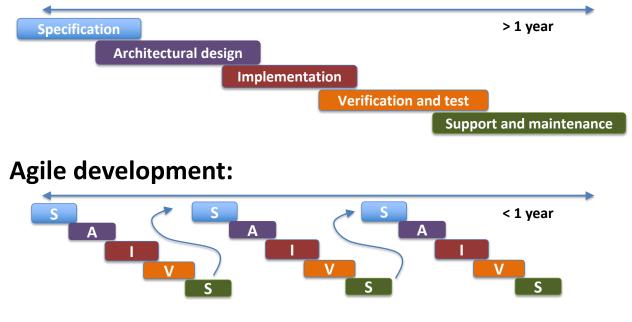

This acceptance of late-binding changes is one of the principles in the Agile Manifesto [25], a collection of principles for improving the efficiency of software developers written in 2001. In the time since the Agile Manifesto has been written, Agile software development has become commonplace in the software development community, and its success has inspired hardware developers to follow suit. Several Agile hardware development methodologies have been developed in recent years [10, 12], which focus on improving ASIC design productivity through the use of generators and repeated full design iterations, called by the tongue-incheek term "Tape-in." The goal of a tape-in is to go through the full VLSI design process up to and including generation of layout data without manufacturing any masks. This process encourages the designer to automate many design flow elements and pipe cleans the generators and physical design automation used to build the chip. Tape-ins align with the Agile principle to deliver a working product frequently. Unlike software products, which are inexpensive to patch and deliver frequently, ASIC designs are very costly to manufacture, so rather than delivering the tape-in results to end customers, this process allows the designers to have a working minimum viable product (MVP) ready at all times to manufacture if needed.

Agile stands in stark contrast to waterfall development, which has traditionally been the model for the semiconductor industry. Waterfall development requires developers to freeze specifications early and pass design information to other groups, like water moving down a waterfall. This works well if the architecture and microarchitecture specifications can be frozen easily and the team is large enough, with a large enough volume of designs, to keep the pipeline of work full. However, with modern workloads like deep neural networks changing so quickly that software can become obsolete within a typical ASIC design cycle, the long latency of waterfall methodologies becomes less attractive than Agile flows. Figure 1.4 illustrates the differences in Agile and waterfall development methodologies.

# 1.2.4 Chipyard: An Agile generator-based SoC flow

Chipyard<sup>7</sup> [16] is a platform developed specifically for developing RISC-V [26] systems-onchip using an Agile methodology. Chipyard combines many tools and intellectual property

<sup>&</sup>lt;sup>7</sup>https://github.com/ucb-bar/chipyard

# Waterfall development:

Figure 1.4: A comparison of Agile vs. waterfall development methodologies [11] (© 2018 Steven Bailey).

blocks (IP) developed at The University of California: Berkeley, along with external contributions, to provide a base SoC platform using the Rocket Chip generator [27], which includes a highly configurable in-order RISC-V CPU core, interconnect fabric, and SoC subsystem IP. Users can start with a base configuration and add custom generator IP, modify the existing generator configurations, or swap in new CPU cores. An example out-of-order core, The Berkeley Out-of-Order Machine (BOOM), is included. Chipyard supports custom IP written in Verilog, SystemVerilog, or Chisel.

Chisel [28] is a domain-specific language for constructing digital hardware embedded within the Scala programming language. Hardware construction languages differ from more traditional hardware description languages in that they are programs that call functions to generate hardware rather than being descriptions of the hardware itself. Some features of hardware construction languages are available in hardware descriptions languages. In Verilog or SystemVerilog, generate statements provide the user with simple construction functionality, but this is limited to basic program building blocks like numeric **for** loops or conditional blocks. Because Chisel is embedded within a modern high-level language with rich object-oriented programming support, strong typing, and powerful built-in functional programming support, users are able to build construction programs that leverage these features to build generators that are succinct and provide complex configuration options. For example, by passing functions as arguments to modules, users can inject custom hardware in a type-safe manner without messy module interface manipulation.

The current version of Chisel, chisel3, produces an intermediate representation of the generated hardware known as FIRRTL [29]. No commercial CAD tools can currently consume FIRRTL, but it is nevertheless a powerful tool that improves the usability of chisel3 over prior versions of Chisel. There are multiple levels of FIRRTL; these range from high to low and progressively become more restrictive, reducing the number of supported abstractions at lower levels. This allows advanced users and compiler writers to interact with FIRRTL at different levels of elaboration, providing the opportunity to transform or analyze the design during its compilation. The lowest level of FIRRTL is directly translatable to Verilog and avoids complex statements like **generate** to ensure support across the widest range of commercial and open-source CAD tools. The FIRRTL compiler utilizes a series of transformations or passes to elaborate the design. By default, FIRRTL preserves the cycle-level behavior of the Chisel design in the elaborated Verilog using a bare-minimum set of passes. However, there are many uses for custom transformations that modify the logical behavior of the circuit, such as introducing redundancy for resiliency or modifying the hierarchy of the design. One such transformation is the conversion of FIRRTL's memory primitive into SRAMs for use in a VLSI flow. Designing generators for an Agile flow using SRAMs can be challenging because the SRAMs usually have process- and dimension-specific module names and ports. There are also often different SRAM configurations within a process technology to support a range energy and performance criteria. By decoupling the SRAM instance information from the logical source, written in Chisel, designers can describe how to map a set of sizes to process-specific SRAM modules, converting what is effectively an  $O(n \times m)$ problem into an O(n+m) problem. This is further explored in Chapter 4 and Chapter 5.

In addition to RTL generation, Chipyard includes a number of additional built-in flows for other design activities, such as simulation, emulation, and physical design. A standard simulation flow exists for standard all-digital Verilog simulations with the simulator of the user's choice. More interestingly, Chipyard incorporates FireSim [30], a cloud-FPGAbased, cycle-accurate simulation engine, which cost-effectively accelerates large simulations to Megahertz-speed, a large improvement over pure software simulators. This simulation speed is crucial for the fast decision-making that is required of Agile flows.

Chipyard's physical design flow incorporates Hammer [17], a framework for creating reusable physical design components for generator-based systems-on-chip. Hammer is discussed in greater detail in Chapter 4. The Hammer framework provides tool, technology, and design abstractions to facilitate reuse of physical design collateral for generator-based flows. This reduces the effort associated with transitioning a design to a new CAD tool vendor or process technology and encourages re-use of physical design inputs for multiple designs that

#### share common generators.

Physical design is the process of scripting and constraining the place-and-route tool<sup>8</sup> to implement the synthesized design. Physical design includes floorplanning, which is the placement of macros, including SRAMs, as described above, along with other physical constraints like routing and placement blockages and guides. Nearly all designs will have some amount of macro placement. Hammer provides an application programming interface (API) for creating a floorplan in a tool-agnostic format using JSON<sup>9</sup>- or YAML<sup>10</sup>-based intermediate representation, or HammerIR. Hammer floorplans are predominantly written by hand or via rudimentary scripts, but the automation of floorplans is an area of active research [18, 31]. Chapter 5 of this dissertation describes a method for generating floorplan data alongside RTL in generator-based design flows.

The tools in Chipyard adequately handle most facets of digital chip design; however, many aspects of analog or mixed-signal design are not addressed. All systems-on-chip include analog or mixed-signal IP to function, such as a phased-locked loop (PLL) for clock generation, a voltage regulator for power supply regulation, a double-data rate (DDR) memory interface, or other type of off-chip interface. The Berkeley Analog Generator (BAG) [32] is a Python framework for building process-portable analog IP generators. BAG is not integrated into Chipyard, but is used to build many of the analog and mixed signal IP used on Chipyard-based designs, such as BEAGLE [33], and the non-Chipyard designs described in Chapter 3.

To use BAG, the designer creates a schematic that connects platform-agnostic design primitives in a manner similar to traditional analog design. These design primitives are typically devices like transistors, resistors, capacitors, inductors, or diodes, but can also be more complicated groupings of devices. A set of primitive generators is then built once per process technology and re-used by all designers who generate designs on it. The layout of BAG designs is generated using a python script which utilizes BAG API calls to place the device primitives and route analog wires between them. BAG currently does not implement automatic routing like digital tools; instead, it relies on the user to provide a specific algorithm to plan the routes. The analog wires need to be larger than minimum width to reduce parasitic resistance, and designs will often have varied wire widths to optimize layout effects and parasitics. These design scripts are written so that layouts can be generated iteratively in order to converge to a design that meets given specs or to pass DRC. Nascent efforts exist to automate this process further using machine learning techniques, specifically reinforcement learning [34], and it is likely this will become more commonplace as this technology matures.

<sup>&</sup>lt;sup>8</sup>In some flows, synthesis is also topologically aware and may need some physical design input.

<sup>&</sup>lt;sup>9</sup>https://www.json.org

<sup>&</sup>lt;sup>10</sup>https://yaml.org

## 1.2.5 Challenges with generator-based design

While generator-based design flows improve many aspects of the design process, there remain many unsolved challenges that are unique to such flows. Verification and floorplanning are two significant challenges among these and are of particular relevance to the integrated circuit design component of system design.

### 1.2.5.1 Verification

Digital chips are often verified using the Universal Verification Methodology (UVM) [35] or similar method, which relies on a scoreboard to compare transaction-level data from directed or constrained random input vectors to the output generated by the device under test (DUT). A scoreboard is effectively a module that incorporates a known-good reference model, or "Golden" model, to produce the desired output from an input stimulus. Designers rely on RTL coverage statistics, measurements of the percent of possible states wires and registers enter throughout the simulation, to gauge confidence in a design, often requiring minimum coverage metrics before allowing a design to be manufactured. This process is time consuming and only builds confidence in the specific instance being verified.

Formal verification [36] is a technique that complements constrained random verification by formally proving that user-specified properties hold for an RTL design. When used successfully, this allows verification engineers to cover cases that would take a large number of random or directed tests to verify, if even possible at all. Formal verification is more difficult to use, however, and is only successful with high quality properties and assertions. Formal verification is also only appropriate for smaller designs, as run time scales exponentially with design size.

Verification for generators currently uses these traditional verification methodologies on generated instances, which becomes a productivity bottleneck when designers are required to intervene to create new test cases or modify test benches or models for the instance under test. Generator concepts have been shown to benefit verification [37], but using verification generators still fundamentally requires re-running verification on each generated instance. Ideally the generator itself would be able to be verified, which would certify that all generated instances are correct, allowing designers to bypass the verification step for generated designs, thus increasing productivity. However, such flows have yet to be implemented and are outside the scope of this dissertation.

#### 1.2.5.2 Floorplanning

Historically, integrated circuit floorplans have been developed manually by skilled physical designers, who work with the RTL designers to understand the data movement between components in the design. With this knowledge, physical designers choose locations for SRAM macros to optimize timing and power, often seeking to minimize the physical distance from sequential elements (SRAMs, flip flops, or latches). Physical designers must also account for

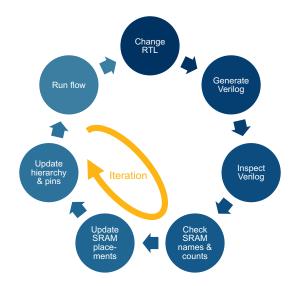

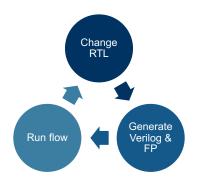

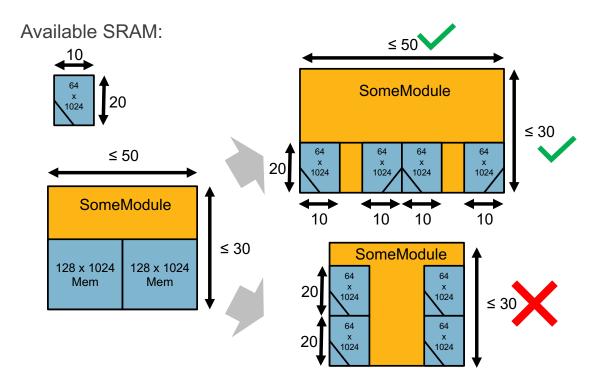

electrical issues like power distribution, placement of power gating and tap cells, and placement of input-output (IO) devices that impact the die-to-package interface. More so than with verification, small changes to generator parameters can have profound effects on the floorplan of a design, especially if the change modifies the number of macros in the design. For example, even in a conventional Verilog flow, it is possible to parameterize a cache size so that a **generate** statement instantiates the required number of SRAM macros. In this flow, every parameterization of cache would require a unique floorplan. Generated instances which add or remove large amounts of placed-and-routed logic will also require floorplans which increase or decrease the available area accordingly. This issue is exacerbated by the productivity improvement afforded by generators written in high-level languages like Chisel, which allow for much more dramatic design changes with relative ease.

To add to this, floorplans are process-specific by nature, meaning a floorplan in a given process technology is not usable in another, although they may share some topology. This poses a challenge not just to generator-based designs, but to any design that a designer wants to port to a new process technology. One of the most significant impediments to process portability is the use of SRAM macros. For the same dimensions and port types, SRAM macros will have different aspect ratios and physical dimensions in different process technologies due to changing bit cell and periphery cell dimensions. While this is not always significant enough to change floorplan topology, it can be important enough to require a different macro arrangement. Furthermore, the timing characteristics of SRAMs change with feature size, shifting the optimal banking of large memory arrays and changing the number and dimensions of the SRAM macros.

## **1.2.6** Floorplanning concepts

In a VLSI flow, the floorplan refers to the set of physical design constraints that determine the physical arrangement of components on the die. The floorplan is typically conveyed through a series of EDA tool commands, most often using the Tcl language. Figure 1.5 shows a visualization of a simple floorplan. While most logic circuit components are placed by using an automated place-and-route algorithm, larger macrocells are manually placed by the designer in the floorplan file. These macrocells can include custom digital logic, analog or mixed-signal circuits, memories (e.g. SRAMs), or manufacturing structures like fiducial markers. Macrocell placement is the primary focus of the floorplanning effort, as it has the largest impact on quality-of-results. Placing two macrocells that interact logically too far apart creates long synchronous paths with long delays, making timing closure difficult. However, placing macrocells too densely restricts the placement of synthesized logic or signal routing between them. This is most commonly observed with SRAM cell placement, as there are typically many SRAM instances in a single digital circuit design which form logical memory banks that need to be clustered together.

Placement of top-level pins also contribute significantly to the quality-of-results produced by the place-and-route tool. For a logic block that is not a top-level chip, these pins are just metal wires to be connected at another level of hierarchy, but for full-chip designs, these pins

Figure 1.5: An example of a simple floorplan.

are either wire bond pads or solder bumps. Pin placement affects the coarse clustering of cells by the place-and-route tool, which must organize the design into logically connected groups based on the graph connectivity of the synthesized design. Similar to macrocell placement, pins must be grouped logically to avoid long routing delays to the relevant logic elements. For example, bits from a large bus should usually be grouped together, and if the bus has its own clock, it should be close as well. Placing pins too closely, however, regardless of connectivity, can lead to routing congestion, which manifests as a result of the routing pitch being significantly smaller than either dimension of a minimum-sized driver cell.

Beyond macrocell and pin placement, floorplans contain a number of additional physical constraints necessary to produce high-quality designs. These tend to be even more processand design-specific than either macrocell or pin placement. They include, among others, power strap placement, routing and placement blockages, routing guides, and placement

Feedthroughs are shown from TopModule through ModuleB to ModuleC as an example. These would be timing critical signals for ModuleC.

TopModule/ModuleB/ModuleA demonstrates multiple levels of hierarchy. ModuleC and ModuleD demonstrate a single level of hierarchy with abutment. Hierarchical flows can use one or both of these techniques.

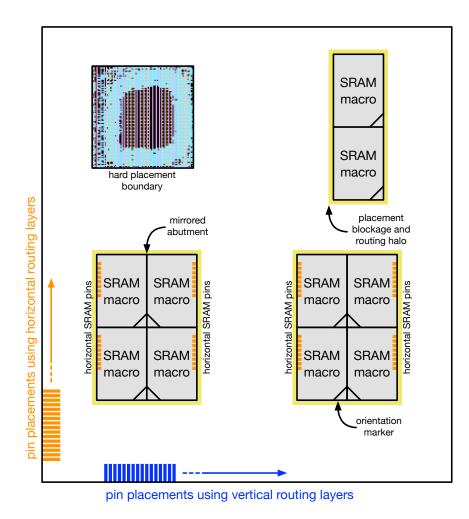

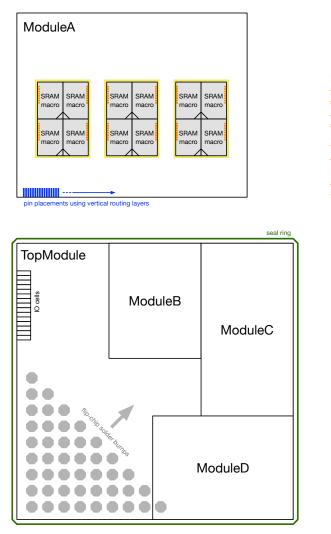

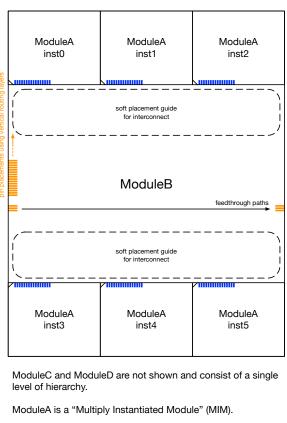

Figure 1.6: An example of a hierarchical floorplan.

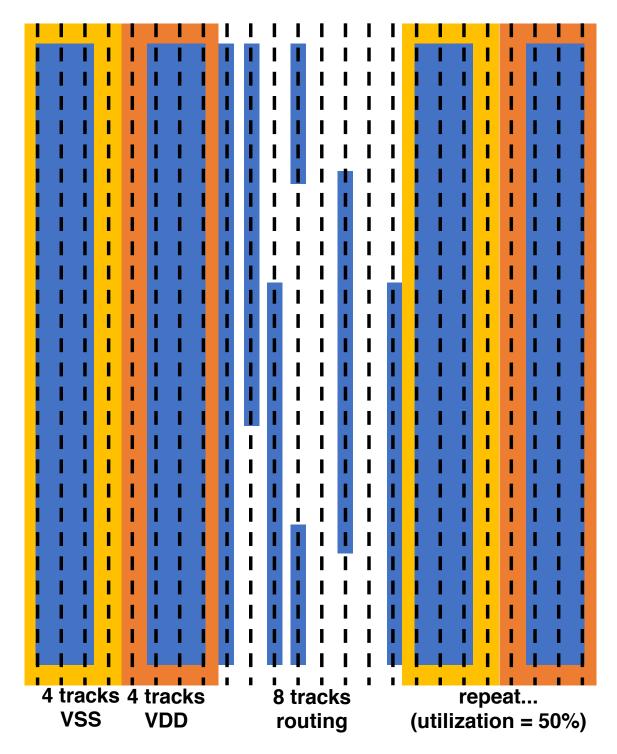

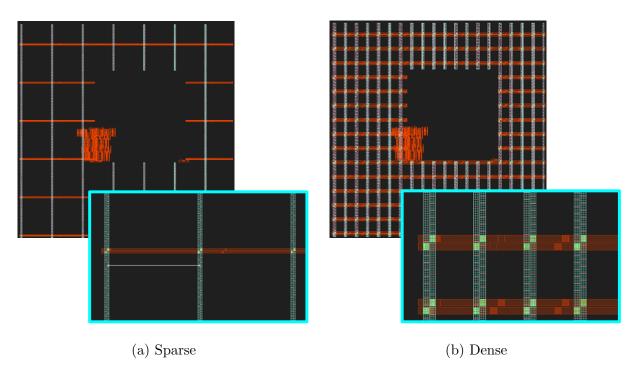

boundaries. Power strap placement is discussed in Chapter 4 and is important for optimizing available routing tracks with voltage drop. Routing and placement blockages prevent the automatic place-and-route tool from using regions of the die for routing or automatic standard cell placement. This may be done to meet certain design rules, to prevent a pathological congestion issue, or for signal integrity reasons. Routing guides provide the converse effect; they encourage the tool to utilize specific routing tracks for specific routes to improve quality-of-results. Placement boundaries may be hard or soft, meaning that they are requirements or suggestions, respectively, and are guides to the tool to place logic of a specific placed-and-routed module in a given boundary. These are used in lieu of a hierarchical boundary for smaller modules that need to be isolated from other modules to meet timing, routing, or power requirements. VLSI flows, and floorplans, are either flat or hierarchical. A flat flow means that the entire design is placed and routed entirely in a single tool run. A hierarchical flow splits the design into sub-designs which are individually synthesized, placed, and routed and subsequently incorporated into higher levels of the design. A sub-design at or above one million gates is generally considered to be a candidate for hierarchical place-and-route [38]. For a sufficiently large design, a hierarchical flow improves tool runtime and quality-of-results at the expense of flow complexity. Floorplans for hierarchical designs require knowledge of the hierarchical boundaries and require additional constraints, like pin placement for sub-blocks. Hierarchical floorplans also may include feed-through paths, which are paths that are logically unrelated to the hierarchical sub-block itself but connect neighboring elements together. An example of a hierarchical floorplan is shown in Figure 1.6.

### 1.2.7 State-of-the-art placement and floorplanning

Placement has been an active area of research since the earliest digital integrated circuits and continues to be an important, unsolved area of research [39]. Until recently, placement research has focused on methods of improving placement of standard cells on flat designs [40, 41] or by using hierarchical approaches [42], but automated placement of macrocells has traditionally resulted in inferior quality-of-results when compared to human-created floor-plans. State-of-the-art automated mixed-size placement results as recent as 2019 [43] have been shown to be inferior to human experts [18]. Many research groups are actively investigating the applications of machine learning for physical design and floorplanning [18, 31, 44]. Of these, reinforcement learning approaches appear to have merit, with recent work showing reinforcement learning has also been shown to assist physical design in other areas such as IR drop estimation [45], layout parasitics and device parameter prediction [46], timing prediction [47], and clock tree prediction and optimization [48].

However, machine learning approaches have yet to become widespread, as many face steep compute costs, require large training datasets, or require rare engineers with deep technical expertise in machine learning and physical design. Many high-quality production designs continue to use human-generated floorplans, but some commercial products use generated floorplans [49]. Floorplan generators bridge the gap between fully automated placers and hand-written floorplans.