## Practical Solutions to Accelerating ASIC Design Development Using Machine Learning

Keertana Settaluri

#### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2022-27 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-27.html

May 1, 2022

Copyright © 2022, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Practical Solutions to Accelerating ASIC Design Development Using Machine Learning

by

Keertana Settaluri

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Co-chair Professor Krste Asanović, Co-chair Professor Michael Ranney

Summer 2021

Practical Solutions to Accelerating ASIC Design Development Using Machine Learning

Copyright 2021 by Keertana Settaluri

#### Abstract

#### Practical Solutions to Accelerating ASIC Design Development Using Machine Learning

by

Keertana Settaluri

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor Borivoje Nikolić, Co-chair

Professor Krste Asanović, Co-chair

Application specific integrated circuits (ASICs) are ubiquitous in modern society, with their high performance, low power, low area characteristics aptly utilized in state-of-the-art electronics and devices. As technology nodes scale, however, it becomes increasingly difficult to bring innovation to circuit systems, as the complexity of design rules and the substantial impact of layout parasitics not only delays time-to-market, but is also more expensive. Emphasis is therefore placed on improving the ASIC design flow, with the primary focus of addressing inefficiencies in this manual and iterative process. The implications of faster ASIC development are far-reaching, allowing for rapid prototyping and better scaling in complex and large System-on-Chip designs, reducing overall cost. Improving the chip design process, however, is challenging, as the iterative circuit, layout, and verification stages heavily involve circuit designers, who often use circuit intuition to dictate crucial decisions. Tools that accelerate the chip design process must therefore consider the unique constraints posed by the ASIC domain in order to be practically utilized by circuit designers.

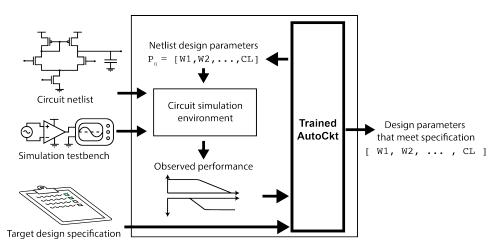

This thesis presents a method for analyzing the efficacy of automated ASIC design tools, specifically by assessing the accuracy, practicability, automation, interpretability, generalizability and run-time efficiency of the algorithm. This is established by presenting one in-depth case study and two projects where machine learning can be used to address inefficiencies in ASIC design, and include: 1) an analog circuit design framework that uses reinforcement learning (RL) to size parameters for a given circuit topology to meet a target specification, 2) an analog sub-clustering tool that uses graphical convolutional neural networks (GCNNs), and 3) using convolutional neural networks (CNNs) to detect defects in circuit yield. The goal is demonstrate that machine learning techniques can not only be successfully used for these three applications, but can be comprehensively analyzed to obtain practical and feasible solutions in circuit design. Specifically, the results of the RL analog circuit framework show that this solution achieves state-of-the-art run-time efficiency across six unique circuit topologies of varying complexity while considering layout parasitics. Additional analyses is also conducted to explain the decision-making of the algorithm, establishing that the obtained performances are explainable and analyzable in the context of circuit design. Furthermore, for several non-linear circuits, the algorithm obtains initial designs that are better than that of an expert, providing potential for better intuition into the boundaries of performance for these circuits.

The GCNN framework for analog sub-clustering project demonstrates that high run-time efficiency with over 91% accuracy can be achieved while being fully automated, requiring no input from the designer for classification. In addition, the algorithm successfully scales to a variety of analog circuits, which is crucial in establishing practicality. The yield defect detection framework using CNNs shows that ML can be applied to a post-silicon application, successfully resulting in identification of yield defects in real and noisy scan diagnosis tests while reducing the layout search space significantly.

To Mom and Dad

# Contents

| $\mathbf{C}$ | onter | ts                                                                                                         | ii            |

|--------------|-------|------------------------------------------------------------------------------------------------------------|---------------|

| Li           | st of | Figures                                                                                                    | v             |

| Li           | st of | Tables v                                                                                                   | iii           |

| 1            | Intr  | oduction                                                                                                   | 1             |

|              | 1.1   | Motivation                                                                                                 | $\frac{1}{2}$ |

|              | 1.2   | Prior work                                                                                                 | 4             |

|              | 1.3   | Thesis scope and outline                                                                                   | 5             |

| <b>2</b>     | Rei   | forcement Learning for Well-Defined Circuit Topologies                                                     | 7             |

|              | 2.1   | Introduction to analog design and sizing                                                                   | 7             |

|              | 2.2   | Prior analog sizing tools                                                                                  | 8             |

|              | 2.3   | Introduction to machine learning                                                                           | 10            |

|              | 2.4   | Reinforcement learning framework                                                                           | 10            |

|              |       | 2.4.1 RL analog sizing setup                                                                               | 11            |

|              |       | 2.4.2 Trajectory generation                                                                                | 11            |

|              |       | 2.4.3 RL agent                                                                                             | 12            |

|              |       | 2.4.4 Training with schematic simulations                                                                  | 12            |

|              |       | 2.4.5 Deployment $\ldots$ | 14            |

|              | 2.5   | Transimpedance amplifier results                                                                           | 16            |

|              | 2.6   | Two-stage amplifier                                                                                        | 18            |

|              |       |                                                                                                            | 18            |

|              |       | 2.6.2 Operational amplifier reinforcement learning setup                                                   | 20            |

|              | 2.7   | Low-dropout voltage regulator                                                                              | 22            |

|              |       | 2.7.1 Manual design procedure                                                                              | 22            |

|              |       | 2.7.2 LDO target metrics and action space                                                                  | 24            |

|              |       |                                                                                                            | 25            |

|              |       |                                                                                                            | 26            |

|              | 2.8   | Two-stage operational transimpedance amplifier with negative $g_m$ load $\ldots$                           | 32            |

|          |     | 2.8.1   | Schematic results                                                                                                                    |

|----------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------|

|          |     | 2.8.2   | Layout simulation results                                                                                                            |

|          | 2.9 | Analys  | sis and conclusion $\ldots \ldots 36$                                 |

| 3        | Rei | nforcer | nent Learning for Parasitic-Sensitive Circuit Topologies 38                                                                          |

|          | 3.1 |         | ed deployment algorithm                                                                                                              |

|          | 3.2 | Two-s   | tage transimpedance amplifier with negative $g_m$ load $\ldots \ldots \ldots \ldots \ldots 40$                                       |

|          |     | 3.2.1   | Design equations and expert methodology                                                                                              |

|          |     | 3.2.2   | RL setup                                                                                                                             |

|          |     | 3.2.3   | Training results                                                                                                                     |

|          | 3.3 | Folded  | $-$ cascode amplifier $\ldots$ $\ldots$ $\ldots$ $\ldots$ $46$                                                                       |

|          |     | 3.3.1   | Schematic training setup                                                                                                             |

|          |     | 3.3.2   | Design equations and expert methodology                                                                                              |

|          |     | 3.3.3   | Schematic training and deployment results for folded-cascode 53                                                                      |

|          |     | 3.3.4   | Reachability analyses in schematic trained agent for folded-cascode . 58                                                             |

|          |     | 3.3.5   | Generalization to layout parasitics                                                                                                  |

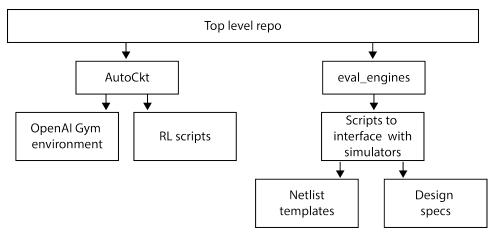

|          | 3.4 | Open-   | source code and framework                                                                                                            |

|          |     | 3.4.1   | Setup                                                                                                                                |

|          |     | 3.4.2   | Code flow                                                                                                                            |

|          |     | 3.4.3   | Training                                                                                                                             |

|          | 3.5 | AutoC   | kt analyses and conclusion                                                                                                           |

| 4        | Boi | nforcor | nent Learning for Nonlinear Circuit Topologies 77                                                                                    |

| 4        | 4.1 |         | uction                                                                                                                               |

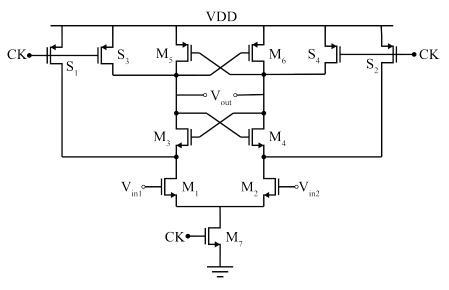

|          | 4.2 |         | -arm comparator                                                                                                                      |

|          | 4.4 | 4.2.1   | Comparator basics                                                                                                                    |

|          |     | 4.2.2   | Manual comparator design                                                                                                             |

|          |     | 4.2.3   | Comparator RL setup                                                                                                                  |

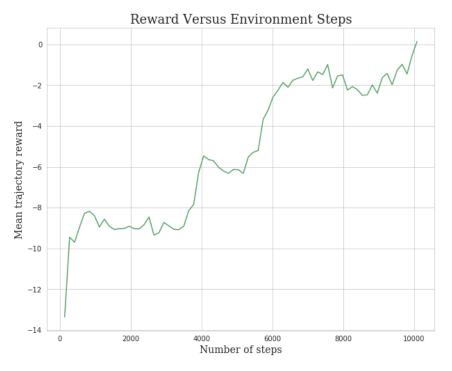

|          |     | 4.2.4   | Results on training and deploying with schematic simulations 80                                                                      |

|          | 4.3 |         | mplifier                                                                                                                             |

|          | 1.0 | 4.3.1   | -                                                                                                                                    |

|          |     | 4.3.2   | RAMP Autockt setup                                                                                                                   |

|          |     | 4.3.3   | Results on training and deploying with schematic simulations 86                                                                      |

|          |     | 4.3.4   | Results on deploying with layout simulations                                                                                         |

|          | 4.4 |         | $1 \text{ sion}$ $\dots \dots \dots$ |

|          |     |         |                                                                                                                                      |

| <b>5</b> |     | -       | b-Circuit Clustering with Graph Convolutional Neural Networks 96                                                                     |

|          | 5.1 |         | g synthesis and sub-circuit extraction background                                                                                    |

|          | 5.2 |         | I framework         97                                                                                                               |

|          |     | 5.2.1   | Feature extraction                                                                                                                   |

|          |     | 5.2.2   | Cluster count and label extraction                                                                                                   |

|          |     | 5.2.3   | Graph creation                                                                                                                       |

|                  |                                                                  | 5.2.4 Graph labelling                                      | 98  |  |  |

|------------------|------------------------------------------------------------------|------------------------------------------------------------|-----|--|--|

|                  | 5.3                                                              | Experimental setup and results                             | 99  |  |  |

|                  | 5.4                                                              | Analysis and conclusion                                    | 101 |  |  |

| 6                | Yiel                                                             | d Defect Detection using Convolutional Neural Networks     | 102 |  |  |

|                  | 6.1                                                              | Defect-prone layout pattern detection                      | 102 |  |  |

|                  |                                                                  | 6.1.1 Contribution                                         | 103 |  |  |

|                  | 6.2                                                              | Layout feature learning with convolutional neural networks | 104 |  |  |

|                  | 6.3                                                              |                                                            |     |  |  |

|                  | 6.3.1 Saliency extraction from learned CNN                       |                                                            |     |  |  |

|                  |                                                                  | 6.3.2 Common defect pattern extraction from saliency map   | 107 |  |  |

|                  | 6.4 Experimental results with synthetic and real diagnostic data |                                                            |     |  |  |

|                  |                                                                  | 6.4.1 Synthetic diagnostic data results                    | 109 |  |  |

|                  |                                                                  | 6.4.2 Real diagnostic data results                         | 111 |  |  |

|                  | 6.5                                                              | Analysis and conclusion                                    | 112 |  |  |

| 7                | Con                                                              | clusion                                                    | 115 |  |  |

|                  | 7.1                                                              | Thesis contributions                                       | 115 |  |  |

|                  | 7.2                                                              | Future directions                                          | 116 |  |  |

| Bibliography 117 |                                                                  |                                                            |     |  |  |

# List of Figures

| 1.1  | Productivity and quality gap during ASIC development [3]                                                                                                                                                                                            |    |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| 1.2  | Requirements for automation in ASIC design                                                                                                                                                                                                          |    |  |  |  |

| 2.1  | Reinforcement learning algorithm showing that the input to the network are the current performance, target specification, and current parameters, and the output is a probabilistic distribution that is sampled to determine whether to increment, |    |  |  |  |

| 2.2  | decrement, or retain each circuit parameter                                                                                                                                                                                                         | 11 |  |  |  |

|      | the circuit such that it meets the specification                                                                                                                                                                                                    | 12 |  |  |  |

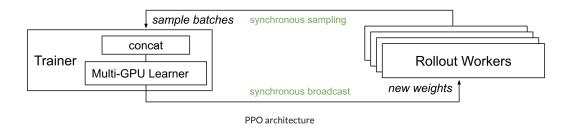

| 2.3  | Proximal policy optimization framework setup using Ray [52]                                                                                                                                                                                         | 14 |  |  |  |

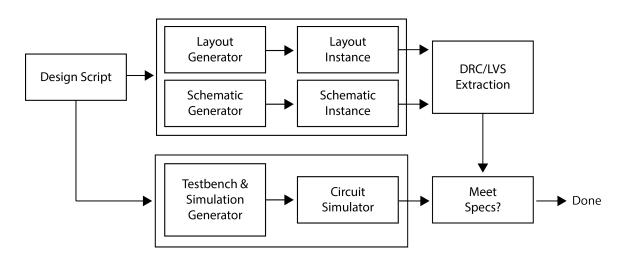

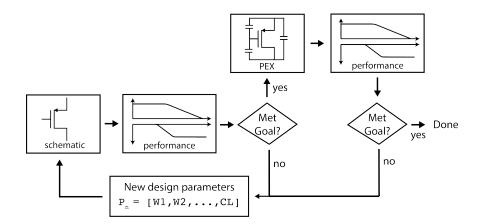

| 2.4  | Diagram of generator-based design using BAG [55]                                                                                                                                                                                                    | 15 |  |  |  |

| 2.5  | Simple transimpedance amplifier schematic.                                                                                                                                                                                                          | 17 |  |  |  |

| 2.6  | Mean episode reward for transimpedance amplifier                                                                                                                                                                                                    | 17 |  |  |  |

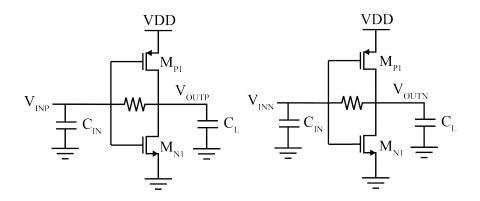

| 2.7  | Two-stage operational amplifier schematic.                                                                                                                                                                                                          | 18 |  |  |  |

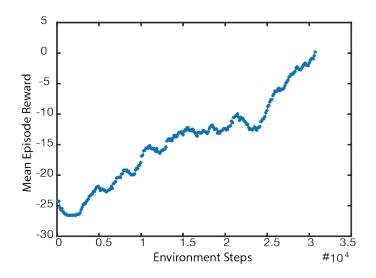

| 2.8  | Mean episode reward for two-stage amplifier                                                                                                                                                                                                         | 20 |  |  |  |

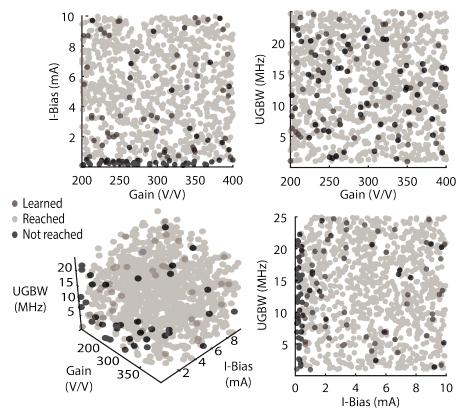

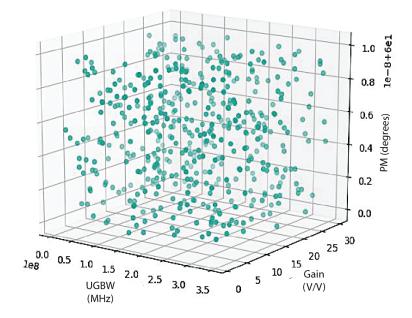

| 2.9  | Distribution of obtained or learned, reached, and unreached target design spec-                                                                                                                                                                     |    |  |  |  |

|      | ifications. Bottom left shows the 3D plot with three of the four design metrics.                                                                                                                                                                    |    |  |  |  |

|      | The rest of the plots show differing metric combinations to visually demonstrate                                                                                                                                                                    |    |  |  |  |

|      | which design points are not met.                                                                                                                                                                                                                    | 21 |  |  |  |

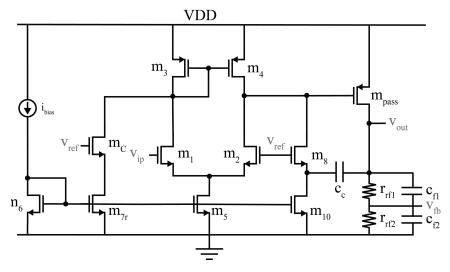

|      | LDO schematic.                                                                                                                                                                                                                                      | 25 |  |  |  |

|      | Mean episode reward for LDO                                                                                                                                                                                                                         | 25 |  |  |  |

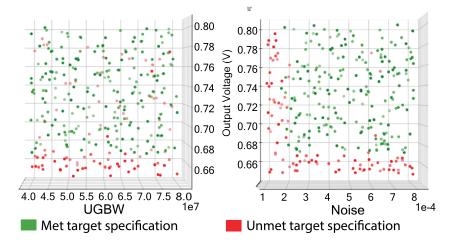

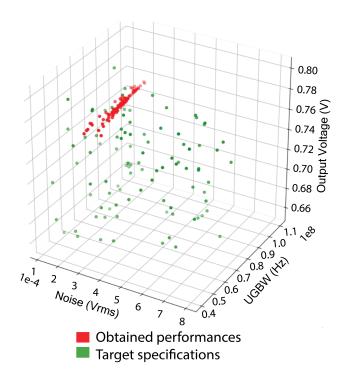

| 2.12 | Met and unmet target specifications for LDO                                                                                                                                                                                                         | 27 |  |  |  |

| 2.13 | Obtained performances by agent versus target specifications                                                                                                                                                                                         | 28 |  |  |  |

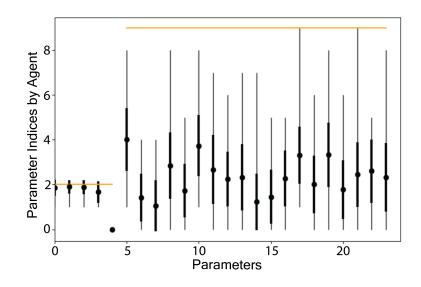

| 2.14 | Obtained parameters by agent for reached performances                                                                                                                                                                                               | 28 |  |  |  |

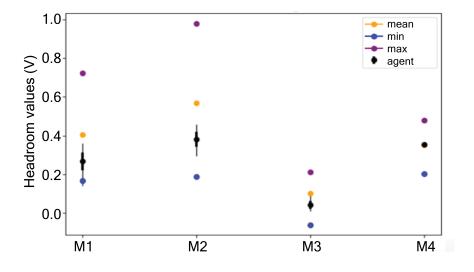

| 2.15 | Agent-obtained headroom values for several devices                                                                                                                                                                                                  | 29 |  |  |  |

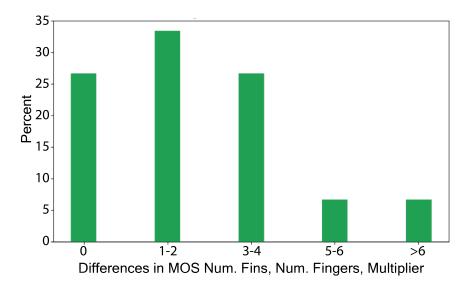

| 2.16 | Comparing agent versus expert parameter values                                                                                                                                                                                                      | 30 |  |  |  |

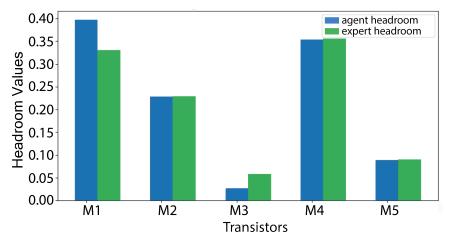

| 2.17 | Headroom values for expert and agent designs                                                                                                                                                                                                        | 31 |  |  |  |

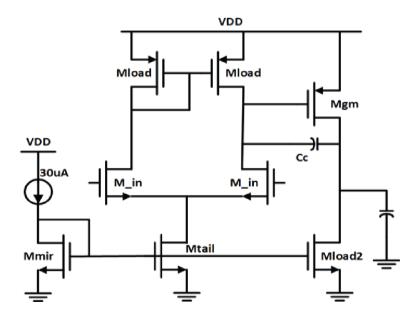

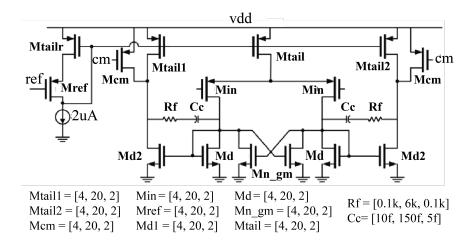

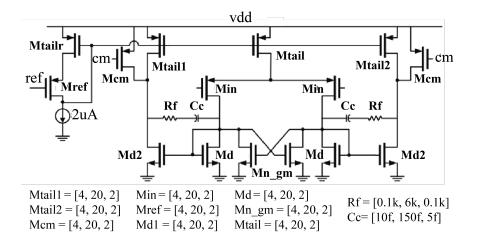

| 2.18 | Schematic and action space for two-stage op amp with negative $g_m$ load                                                                                                                                                                            | 32 |  |  |  |

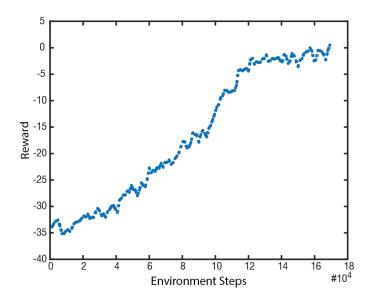

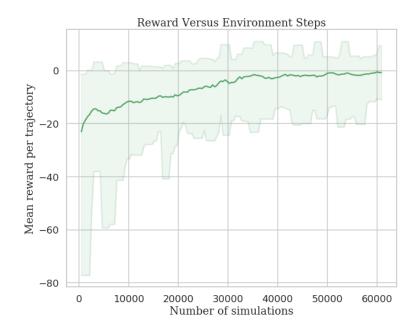

| 2.19 | Mean episode reward over environment step for negative $g_m$ operational amplifier.                                                                                                                                                                 | 33 |  |  |  |

| 2.20 | Distribution of reached target design specifications for the operational amplifier                                                                                                                                                                  |    |  |  |  |

|      | with negative $g_m$ load. Note that this example does not contain any unreached                                                                                                                                                                     |    |  |  |  |

|      | objectives                                                                                                                                                                                                                                          | 34 |  |  |  |

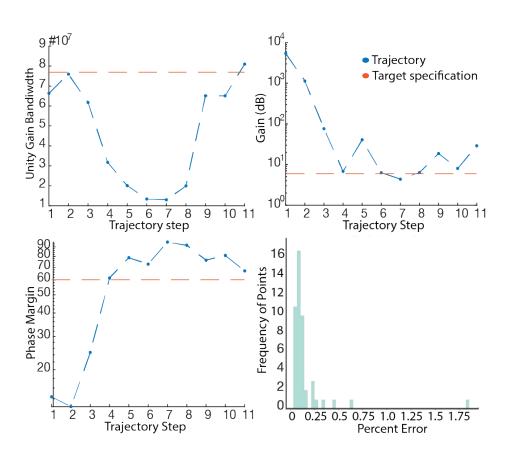

| 2.21         | Top left, top right, and bottom left figures show a sample trajectory for the trans-<br>ferred agent attempting to reach one target design specification. Bottom right<br>shows a histogram plotting difference between schematic and layout simulation. | 35         |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.1          | Parasitic deployment algorithm that shows how schematic and layout simulation                                                                                                                                                                            | 20         |

| 0.0          | distributions are combined to obtain a target specification.                                                                                                                                                                                             | 39         |

| 3.2          | Two-stage transimpedance amplifier schematic.                                                                                                                                                                                                            | 41         |

| 3.3          | Mean episode reward for full two-stage transimpedance amplifier                                                                                                                                                                                          | 44         |

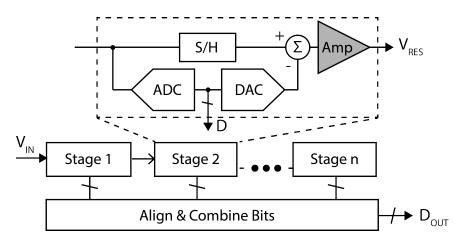

| 3.4<br>2 5   | Pipeline ADC block diagram with amplifier circuit in gray                                                                                                                                                                                                | $46 \\ 47$ |

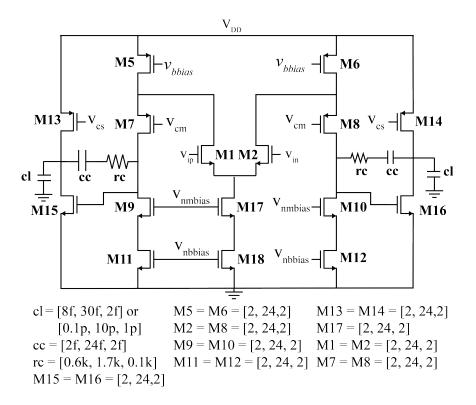

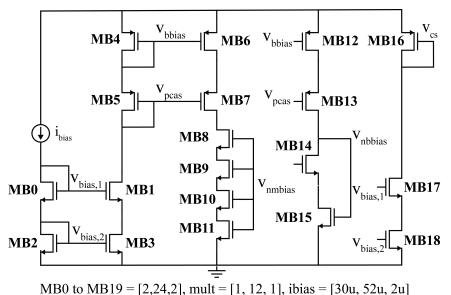

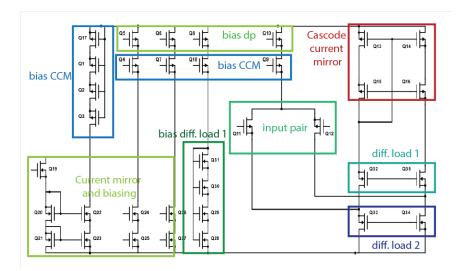

| $3.5 \\ 3.6$ | Folded-cascode core topology: 22 parameters total                                                                                                                                                                                                        | 47<br>48   |

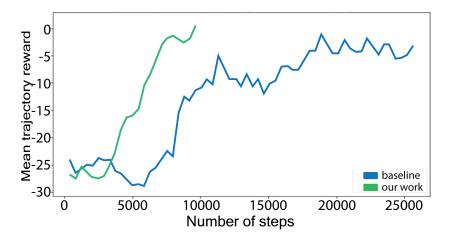

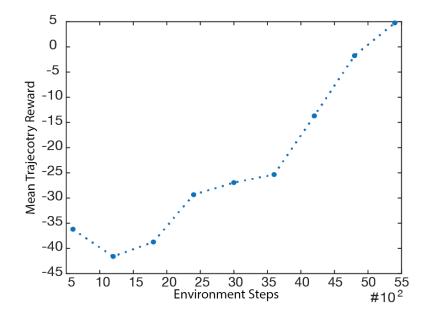

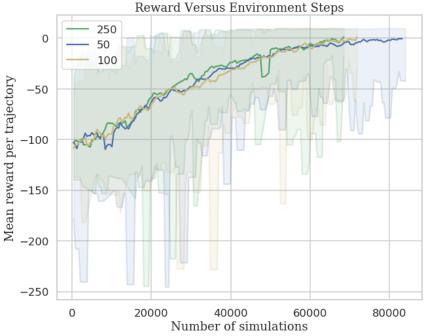

| 3.0<br>3.7   | Mean reward per trajectory for 50, 100, and 250 training target specifications.                                                                                                                                                                          | 40<br>55   |

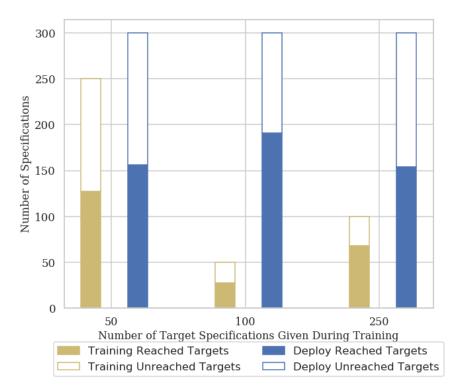

| 3.8          | Deploying trained agent on target specifications not seen before: folded-cascode.                                                                                                                                                                        | 55 - 56    |

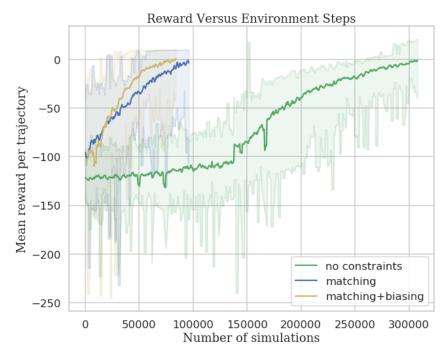

| 3.9          | Mean reward per trajectory for varying number of constraints: folded-cascode.                                                                                                                                                                            | 57         |

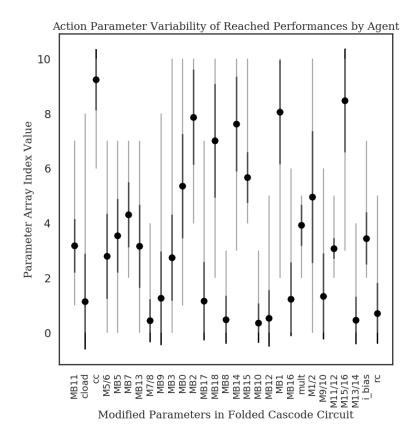

| 3.10         | Parameter variation for reached performances: folded-cascode                                                                                                                                                                                             | 59         |

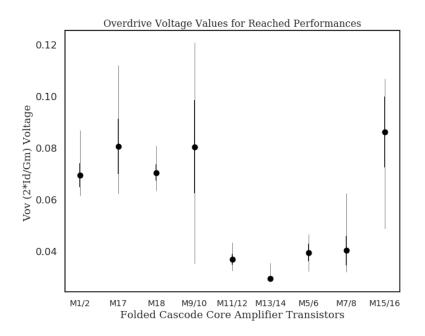

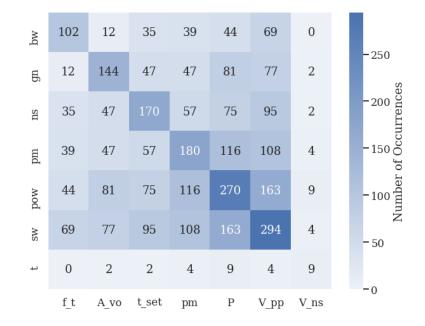

| 3.11         |                                                                                                                                                                                                                                                          | 60         |

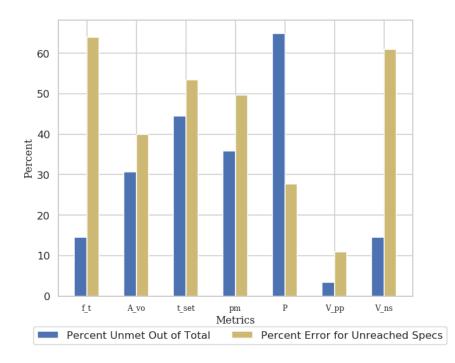

|              | Metric failure percentage and percent difference to target for those failed metrics,                                                                                                                                                                     |            |

|              | where $f_{-t}$ is unity-gain frequency, $A_{-vo}$ is gain, $t_{-set}$ is settling time, $pm$ is phase                                                                                                                                                    |            |

|              | margin, $P$ is power, $V\_pp$ is voltage swing, and $V\_ns$ is noise.                                                                                                                                                                                    | 61         |

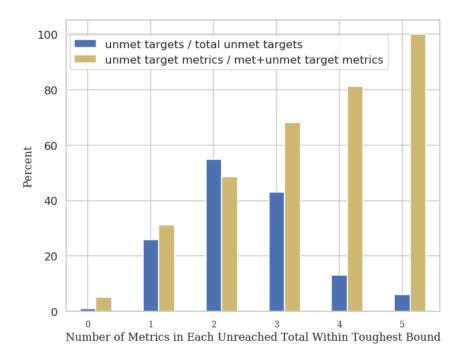

| 3.13         | Distribution of unreached targets binned by number of metrics that are within                                                                                                                                                                            |            |

|              | their toughest bound                                                                                                                                                                                                                                     | 62         |

| 3.14         | Heatmap of number of occurrences of different metric tradeoffs in unreached tar-<br>get specifications, where $f_{-}t$ is unity-gain frequency, $A_{-}vo$ is gain, $t_{-}set$ is settling                                                                |            |

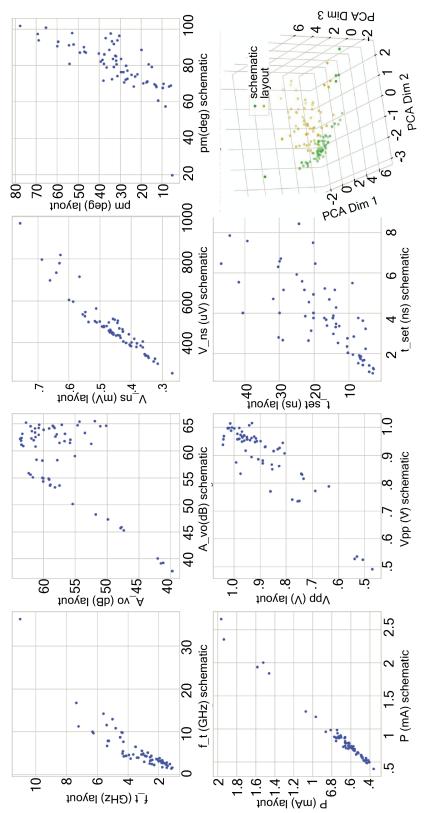

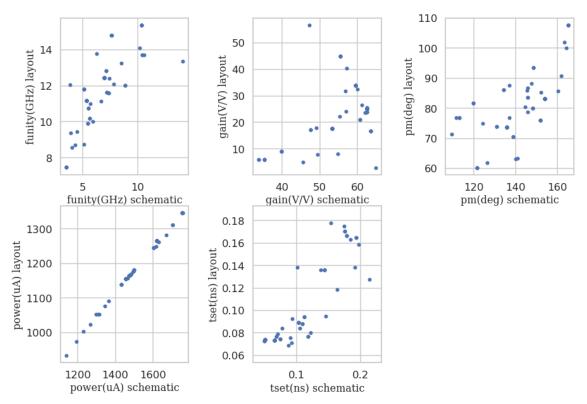

| 3 15         | time, $pm$ is phase margin, $P$ is power, $V\_pp$ is voltage swing, and $V\_ns$ is noise.<br>Scatterplot showing the difference between schematic and layout simulation re-                                                                              | 63         |

| 0.10         | sults: folded-cascode circuit.                                                                                                                                                                                                                           | 65         |

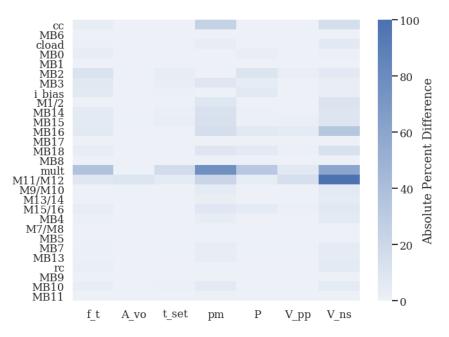

| 3.16         |                                                                                                                                                                                                                                                          | 00         |

|              | design: folded-cascode                                                                                                                                                                                                                                   | 66         |

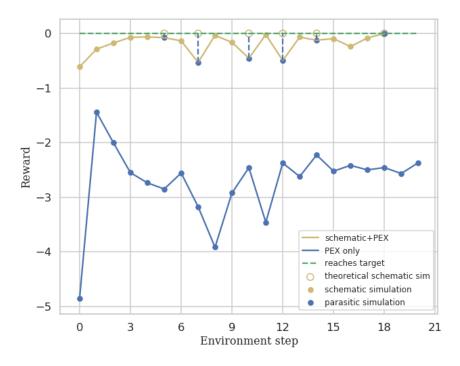

| 3.17         |                                                                                                                                                                                                                                                          |            |

|              | simulations, versus only layout simulations.                                                                                                                                                                                                             | 67         |

| 3.18         | BAG-generated LVS-passed layout for the core and biasing folded-cascode circuit                                                                                                                                                                          |            |

|              | for an obtained performance.                                                                                                                                                                                                                             | 68         |

| 3.19         | Flow-chart for AutoCkt framework on Github                                                                                                                                                                                                               | 74         |

| 4.1          | Strong-arm comparator schematic.                                                                                                                                                                                                                         | 79         |

| 4.2          | Mean episode reward for strong-arm comparator.                                                                                                                                                                                                           | 81         |

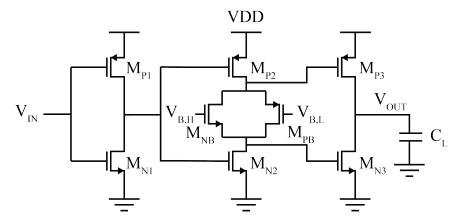

| 4.3          | Ring amplifier topology proposed in [71]                                                                                                                                                                                                                 | 83         |

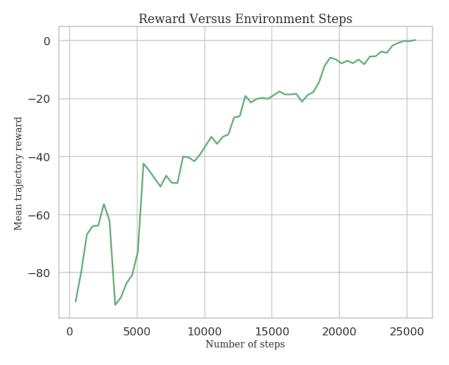

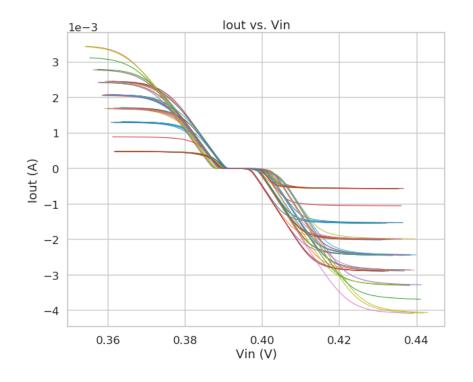

| 4.4          | Mean reward per trajectory for the ring amplifier.                                                                                                                                                                                                       | 86         |

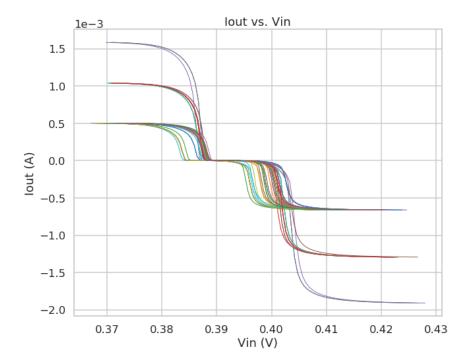

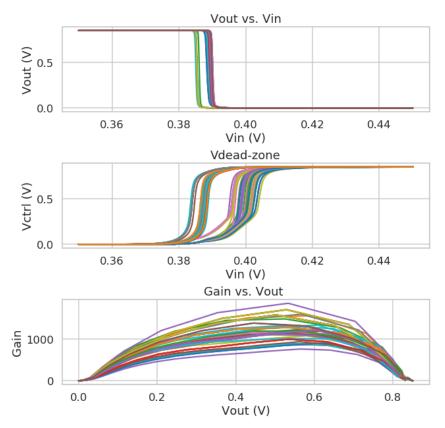

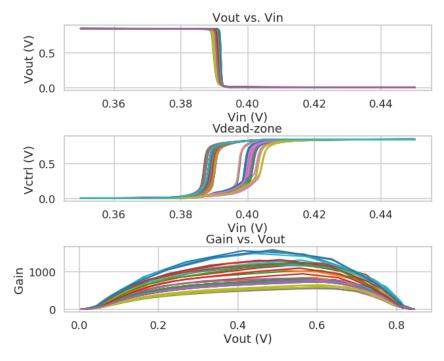

| 4.5          | Output current versus input voltage schematic simulation plot for the ring am-<br>plifier for different designs.                                                                                                                                         | 87         |

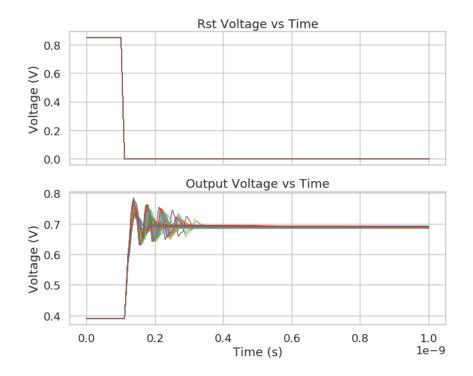

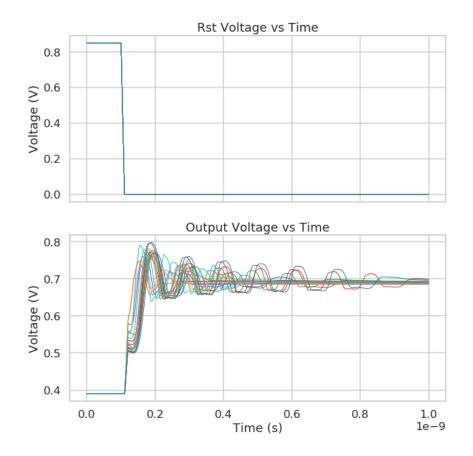

| 4.6   | Schematic simulation results for reset and output voltage versus time for the ring amplifier for different designs.  | 88       |

|-------|----------------------------------------------------------------------------------------------------------------------|----------|

| 4.7   | Obtained schematic performance plots of output versus input voltage (top), dead-                                     |          |

|       | zone versus input voltage (middle), and gain versus output voltage (bottom) for                                      |          |

|       | the ring amplifier for different designs.                                                                            | 89       |

| 4.8   | Scatterplot showing the difference between schematic and PEX simulations for                                         |          |

|       | each target metric for the ring amplifier                                                                            | 90       |

| 4.9   | Output current versus input voltage layout simulation plot for the ring amplifier                                    |          |

|       | for different designs.                                                                                               | 91       |

| 4.10  |                                                                                                                      | 0.0      |

| 4 1 1 | for different designs.                                                                                               | 92       |

| 4.11  |                                                                                                                      |          |

|       | versus input voltage (middle), and gain versus output voltage (bottom) for the ring amplifier for different designs. | 93       |

| 1 19  | ring amplifier for different designs                                                                                 | 93<br>94 |

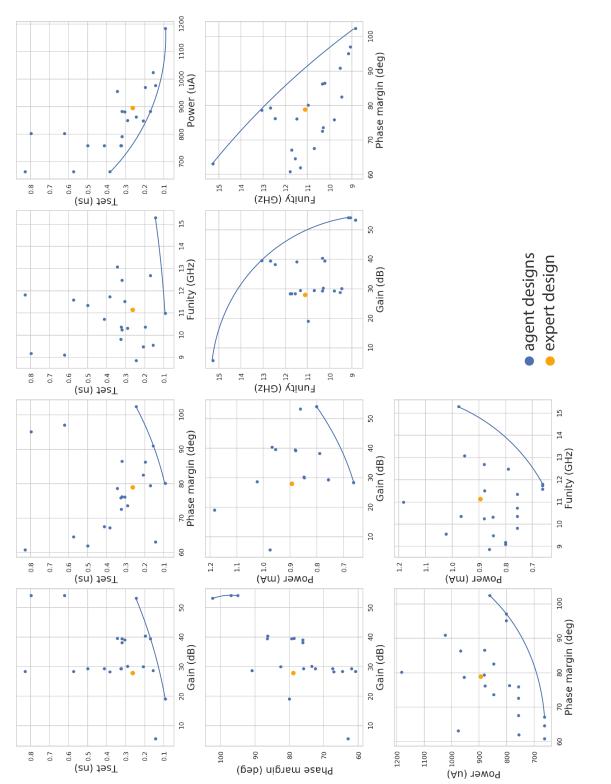

| 4.12  | i areto curves for reached performances by agent, along with the expert design.                                      | 54       |

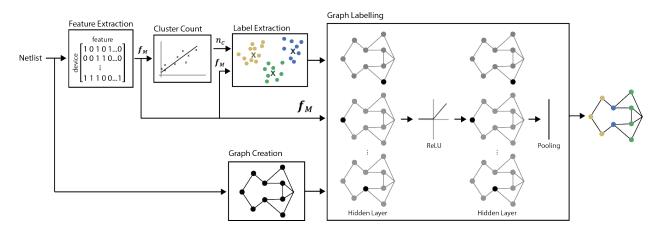

| 5.1   | Total system overview of the analog clustering algorithm                                                             | 97       |

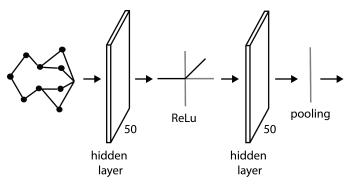

| 5.2   | GCNN architecture showing two 50 neuron hidden layers, one ReLu non-linearity,                                       |          |

|       | and one pooling layer                                                                                                | 99       |

| 5.3   | Folded cascode with biasing circuit, with hand-labelled clusters                                                     | 100      |

| 5.4   | Output of GCNN algorithm visualized, the black boxes show incorrectly labelled                                       | 100      |

|       | devices, and the similarly-colored circles correspond to the same cluster                                            | 100      |

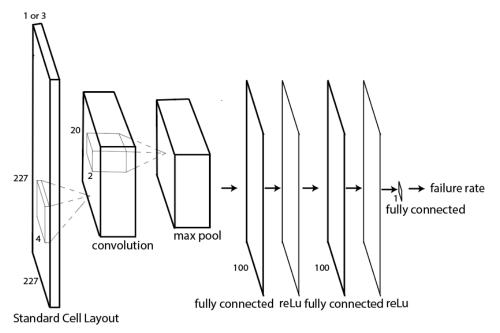

| 6.1   | CNN architecture to learn defect-prone layout feature.                                                               | 105      |

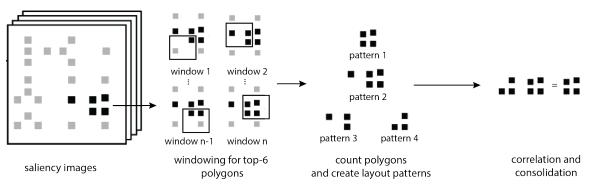

| 6.2   | Extracting defect patterns (shown in black) with windowing pattern extraction.                                       | 107      |

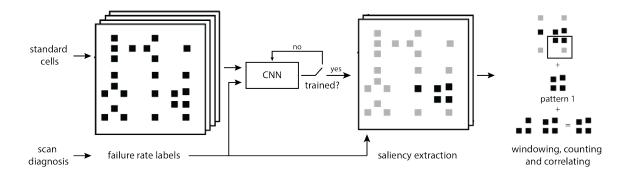

| 6.3   | System level overview of defect-prone layout pattern-detection algorithm                                             | 107      |

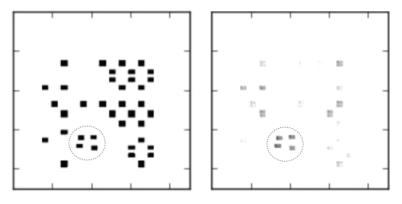

| 6.4   | Cell layout (left) and its saliency image (right), with synthetic defect circled                                     | 110      |

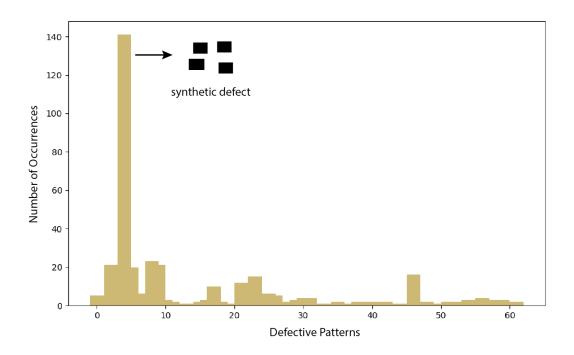

| 6.5   | Results of applying windowing technique to saliency results                                                          | 110      |

vii

# List of Tables

| 2.1          | Comparison of prior analog sizing methods with required simulation count to converge and number of specifications reached versus tested: transimpedance amplifier. | 17 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2          | Agent-obtained performances and an expert design for the two-stage amplifier with load capacitance of $10pF$ .                                                     | 23 |

| 2.3          | RSC and number of specifications reached versus tested: two-stage op amp                                                                                           | 24 |

| 2.4          | Training and deployment number of specifications reached versus tested: LDO                                                                                        | 26 |

| 2.5          | Obtained performances by agent for LDO                                                                                                                             | 27 |

| 2.6          | Agent versus expert: LDO.                                                                                                                                          | 30 |

| $2.7 \\ 2.8$ | LDO comparison table                                                                                                                                               | 32 |

| 2.9          | plifier with negative $g_m$ load                                                                                                                                   | 33 |

|              | plifier with negative $g_m$ load with layout parasitics                                                                                                            | 35 |

| 2.10         | Summary of circuit topology results presented in this chapter                                                                                                      | 37 |

| 3.1          | Performance range sampled during training for full operational transimpedance amplifier.                                                                           | 43 |

| 3.2          | Obtained schematic performances of trained agent for full operational tran-<br>simpedance amplifier.                                                               | 44 |

| 3.3          | Layout performance obtained by agent compared to expert for one design                                                                                             | 45 |

| 3.4          | Rounded average required simulation count (RSC) for transimpedance two-stage                                                                                       | 10 |

|              | amplifier in schematic and layout for 60 performances                                                                                                              | 45 |

| 3.5          | Derived target specifications for folded-cascode in pipeline ADC application                                                                                       | 50 |

| 3.6          | Parameter constraint selection.                                                                                                                                    | 51 |

| 3.7          | Comparison of efficiency between agent-obtained and expert-designed performances.                                                                                  | 54 |

| 3.8          | Comparison of prior analog sizing methods with required simulation count (RSC)                                                                                     |    |

|              | to converge and number of specifications reached versus tested.                                                                                                    | 58 |

| 3.9          | Reached performance ranges by agent $(100o^*)$                                                                                                                     | 59 |

| 3.10         | Reached performance metric distribution for unreached targets.                                                                                                     | 60 |

| 3.11         | Reached performance ranges with layout parasitics.                                                                                                                 | 67 |

| 3.12         | Prior work and AutoCkt layout performances for 8-bit and 10-bit pipeline ADC                                                                                       | CO |

|              | specifications with load capacitance varying from $8 - 30 fF$ .                                                                                                    | 68 |

| 3.13 | Required Simulation Count (RSC) for AutoCkt with varying seeds (average min/mean/max) and two prior works | 68  |

|------|-----------------------------------------------------------------------------------------------------------|-----|

| 3.14 | FF, SS, SF, SS corner simulation results showing minimum, mean, and maximum                               | 00  |

| 0.11 | obtained metric performances across 60 agent-obtained designs                                             | 70  |

| 3.15 | 8-bit corner simulation results                                                                           | 71  |

|      | 10-bit corner simulation results.                                                                         | 71  |

|      | Comparison table for prior analog automation works.                                                       | 72  |

|      | Comparison table for folded-cascode topologies.                                                           | 73  |

| 4.1  | Performance range sampled during training for strong-arm comparator                                       | 80  |

| 4.2  | Performance range obtained by agent during training                                                       | 82  |

| 4.3  | Comparison for expert-designed and agent-obtained performances for the same                               |     |

|      | target specification.                                                                                     | 82  |

| 4.4  | Performance range sampled during training for ring amplifier                                              | 85  |

| 4.5  | Required simulation count (RSC) to converge and number of specifications                                  |     |

|      | reached versus tested: ring amplifier                                                                     | 86  |

| 4.6  | Obtained schematic simulation performance ranges by agent                                                 | 87  |

| 4.7  | Obtained layout simulation performance ranges by agent                                                    | 91  |

| 4.8  | Expert versus agent-obtained design for same target specification                                         | 92  |

| 4.9  | Comparison of agent-obtained ring amplifier performance to an expert for the                              |     |

|      | same target specification                                                                                 | 93  |

| 5.1  | Comparison table showing maximum number of devices in a tested topology,                                  |     |

|      | accuracy of algorithm, and automation                                                                     | 99  |

| 5.2  | Maximum accuracy of algorithm for multiple circuits                                                       | 99  |

| 6.1  | Accuracy, loss and divergence for the trained CNN                                                         | 109 |

| 6.2  | Test results on simulated diagnosis for different parameters                                              | 111 |

| 6.3  | Test results on real diagnosis data.                                                                      | 112 |

| 6.4  | Comparison table for prior yield defect detection works                                                   | 114 |

ix

#### Acknowledgments

This dissertation, and my PhD, would not have been possible without the help of so many people. First and foremost, I want to thank my advisors Bora Nikolić and Krste Asanović. Bora, you not only provided me with practical guidance and freedom in pursuing ASIC design automation, but also helped me sell a research vision that was not readily accepted in the circuits community. Despite our differences, you came on board and worked your magic - and my dissertation is better because of it. Krste, you were always available when I needed, and understood my research in the short amount of time I used to describe it to you. You gave valuable input during my qualifying exam, that helped me describe my algorithm better in this dissertation.

I also want to thank my outside committee member, Michael Ranney. The field of education has always fascinated me, and I remember becoming semi-obsessed with education history in your class. Even though I was an outsider with no prior knowledge about the area, you were welcoming and friendly, and seemed to truly care about your students. I appreciate the time you spent (voluntarily) reading my dissertation and meeting with me, the curiosity you had about it and my research, and the questions you asked about my job and general well-being, which was very new to me.

To my mentors Rajeev Jain and Elias Fallon. You both came into my graduate career at really critical points, and your enthusiastic support, positive reinforcement, and selflessness in mentoring a graduate student even before and after I finished my internships at Qualcomm and Cadence, with absolutely no personal gain, really speaks to your characters. My research would not have been the same without your help and support.

I would also like to thank my research collaborators, especially Zhaokai Liu, for providing the necessary (and very well-designed) BAG generators that were crucial to my research. Thanks as well to Ameer Haj-Ali, Jenny Huang, Kourosh Hakhamaneshi, Rishubh Khurana, Arash Mirhaj, and Onur Atan, for coding, mentoring, advising, or all three. Thanks to the other students in Bora's group for providing feedback and friendship.

When I first joined graduate school, I happened upon a tight-knit group of friends in BWRC that have been instrumental during my PhD. Specifically, Antonio, you were a seniorish student when Emily and I joined, and somehow (maybe it was your constant, very loud and prominent cursing?), we became very good friends. You gave me late-night, post-rager advice on graduate school, while making BWRC feel like home. Ozzy, you were there for those ragers, but I also enjoyed the wonderfully weird conversations we've shared, along with watching basketball games that I didn't really understand.

Emily, we've always joked about where we would be if we didn't meet each other. We've been teammates, desk buddies, roommates, bakers, sometimes bad bakers (though that was mostly me), and shared a lot of incredible memories together. You have a way of perceiving and understanding material and making it intuitive that I've never seen before. They make you so unique, and I'm glad I got to have some of that perspective on my research.

Sidney, Matt, George, Alvaro, Candy, Yessica, Eisha and Anusha: thank you for your friendship and general existence. To my friends from home, who've known me for far too

many years: Ben, Misha, and Sasha, thanks for sticking around and providing endless laughs and entertainment.

One of the biggest surprises for me in graduate school was happening upon you, Andy. It's crazy to think, six years ago, we met at visit days not knowing what we would be. Since then, we've shared so many experiences, yet it's still so weird to me that I can enjoy and love even the most mundane things we do together, like going to a store. You've helped me become the strong, independent woman I am today by believing in my abilities, advocating for me when I needed it, and helping me laugh at some of the more unfortunate and awkward events that have happened. I am really excited for the future, but even more so because I know you'll be there with me.

Finally, to my family. Dad, thank you for always pushing me to be ambitious and promoting equality even when circumstances wouldn't allow for it. You introduced me to Electrical Engineering, and gave me so much valuable advice from your time as a PhD student. I truly couldn't have done this without you. Mom, you always care for other people so selflessly. Every day I think about how strong and brave you are, for doing things I couldn't have done myself - from dealing with the loss of loved ones, to risking your life to serve as a nurse, all during the pandemic with a huge smile and positive attitude. I still have a lot to learn from you. And finally, my brother. We somehow ended up in the same lab, doing very similar things - and it's half coincidence and half me being a copycat. I've always looked up to you, not only for your intellect, but having the unique ability to cohesively and correctly express your thoughts, be it technical or anything else. I think you are an amazing leader, and I'm definitely trying to copycat that too.

## Chapter 1

## Introduction

### 1.1 Motivation

Application-specific integrated circuits (ASICs) are ubiquitous in modern society, with their high performance, low power, low area characteristics aptly utilized in state-of-art electronics and devices. As a result, the ASIC market is growing by an estimated 8.6% every year, and predicted to be valued at over \$28 billion by 2026 [1]. This higher demand is not only fueling technological innovation, but also reliance on ASICs to provide newer process technologies at smaller form factors, faster speeds and better energy efficiency than their predecessors.

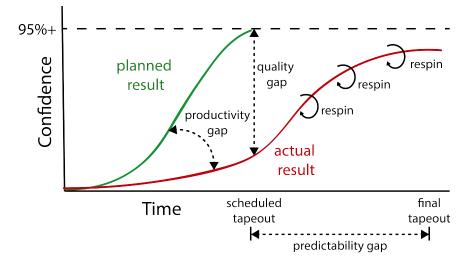

As technology nodes scale, however, it becomes increasingly difficult to bring innovation to circuits, as the complexity of design rules and prominence of layout parasitics not only delays time-to-market, but is also more expensive. In fact, the typical non-recurring engineering (NRE) cost ranges in the tens of millions of dollars, with the development process, consisting of creating goals and constraints, design space exploration, modelling and simulation of the resulting design, creating the physical layout that passes various manufacturing checks, verifying that the circuit functions with this physical design, manufacturing the design, and finally, verifying the design in physical silicon, taking many months to years to complete [2]. In addition, productivity and quality standards are often difficult to meet within a certain time-frame because the development process is iterative, with designers cycling through the different stages many times in order to obtain a feasible design that meets performance specifications. This is illustrated in part in Figure 1.1, where costly chip re-spins alone, which require manufacturing the chip multiple times, significantly delay the development process.

Significant emphasis is therefore placed on improving the ASIC design flow, with the primary focus of addressing inefficiencies in this iterative and manual process. The implications of faster ASIC development are far-reaching, allowing for rapid prototyping and better scaling in complex and large System-on-Chip (SoC) designs, reducing overall cost immensely. Improving the chip design process, however, is challenging, as the iterative circuit, layout, and verification stages heavily involve circuit designers, who often use circuit intuition, or

#### CHAPTER 1. INTRODUCTION

their prior experience to dictate crucial decisions made to the current design. Tools that accelerate the chip design process must consider the unique constraints posed by the ASIC domain in order to be practically utilized by circuit designers.

Figure 1.1: Productivity and quality gap during ASIC development [3].

#### 1.1.1 Automation of ASIC design

The goal is to automate areas of ASIC development that are innately inefficient or manual, allowing designers to focus on other crucial aspects of the design flow, improving overall development time and cost. Before determining specific algorithms that can be used to address these inefficiencies, it is important to qualify the requirements for an automated tool, that are unique to the ASIC design domain. Figure 1.2 summarizes the six key features, explained below:

• Accurate: the proposed tool must be accurate, meaning that it achieves its objective correctly. The specific ASIC subproblem generally dictates the tolerance for this constraint. For example, automated place and route algorithms often provide initially infeasible designs, even with established CAD tools, versus DRC (design rule check) or LVS (or layout versus schematic) checks must be fully accurate with no errors. The accuracy metric can be represented in many ways, but should be specific to the ASIC problem being solved as opposed to the proposed solution. For example, for a machine learning (ML) algorithm, training or deployment accuracy is traditionally used to assess efficacy [4]. If, however, the proposed ASIC problem is optimization-related, it is also important to also assess the ML solution under this context as well, perhaps via an accuracy metric that compares the ML solution to an expert, or the percent difference between the ML-obtained answer versus a CAD tool.

Figure 1.2: Requirements for automation in ASIC design.

- Practicable: the proposed solution must be useful, meaning that within the confines of the ASIC design sub-problem, it should consider all relevant requirements. This includes quantifying any failures and understanding the design space or region where the tool is successful. This analyses not only reveals the limitations of the tool, but can be used to understand its behavior.

- Automated: the tool accelerates the design process compared to traditional methods. The degree of automation can vary considerably, from requiring designers to be heavily involved in the creation and maintenance of the tool's functionality to being fully autonomous with no intervention or hand-holding from the designer.

- Interpretable: the tool should make, to some degree, reasonable assumptions and decisions on the ASIC sub-problem so that it reaches the objective in an interpretable way. This is important, not only as a method to verify the efficacy of the tool, but also to validate and obtain confidence that the tool can achieve objectives reliably. This metric can be derived by comparing designer or CAD tool decision-making and performance to that of the algorithm.

- Generalizable: the tool should function across process technologies, topologies, and SoC designs in a well-defined and scalable manner, ideally with little to no modification of the algorithm. This ensures that the algorithm remains applicable in the changing landscape of ASIC chip design.

- Run-time efficient: the tool should reach the objective in a reasonable amount of time, with nominal compute resources. The constraints vary widely based on the specific ASIC development problem, but in general should require less resources and time than the traditional designer/CAD tool approach. This metric is generally represented in time and required compute machines or operations.

Knowing these six baseline features, and to some degree understanding the trade-offs between them, can not only help in selecting algorithms to address inefficiencies in ASIC design, but also comprehensively assess their efficacy and practicality. The projects covered in this thesis, and their design decisions, are qualified under these metrics.

### 1.2 Prior work

Electronic design automation (EDA) tools are a class of specialized programs solely developed and primarily used to aid in the design of ASICs. Traditional EDA tool-chains [5] encompass multiple facets of the design process, from design methodology and data modeling to physical hardware implementation, manufacturing checks, and logical synthesis. Though these commercially licensed tools are used to partially automate the ASIC flow, they require designers to be heavily involved in process-technology dependent processes, and face long end-to-end run-times due to complex optimization algorithms [6]. Thus, recent research efforts have focused on automating aspects of this existing flow, by either replacing the EDA framework in its entirety, or appending additional algorithms that rely and interface with existing EDA tools. In this section, seminal papers are presented based on frequently occurring themes in the ASIC development process: decision-making, optimization, performance prediction and automation of the end-to-end design flow [7]. These papers are discussed in the context of the six ASIC automation requirements.

Traditionally, decision-making in the ASIC flow is left to the designer, who is responsible for selecting specific tool-chains, hyperparameters and higher-level system design requirements that interface with the EDA framework. Several works address aspects of this decision process, for example using a heterogeneous or deep neural network framework to automate logic synthesis [8, 9], applying Bayesian optimization to select hyperparameters for neural network accelerators [10], or selecting between differing circuit topologies with integer programming [11] or simulation-based approaches [12]. These works enhance automation for their specific sub-problems while demonstrating high fidelity and practicality, and could be explored further to ensure interpretability and generalizability to different technology nodes and unique designs.

Optimization problems in the ASIC design process include applications like deep neural network compression [13], multi-objective tasks such as creating designs to minimize power or other specifications, selecting or generating topologies, or determining parameters for a circuit topology that meet a given target performance. Often, solutions for these design issues are either formulated as numerical or black-box optimization problems. Geometric programming [14] and constraint-based methods have been used in numerical formulations for parameters in a circuit topology and multi-objective design tasks [15], but have not yet been robustly tested for scalability or generalizability, as they are generally applicable in certain specific, and well-defined cases. Evolutionary methods like genetic algorithms and machine learning techniques have been used extensively in designing circuits [16, 17, 18, 19], and are automated, accurate solutions that require more analysis to prove accuracy, reliability, and interpretability.

Performance prediction algorithms accelerate the design flow by providing alternative approximate modeling that provides quicker end-to-end run-time in iterative processes. Examples include power prediction modeling based on a library of pre-modeled components [20], routing congestion prediction with deep graph neural networks [21], clock-tree prognostication using generative adversarial networks [22], or layout-parasitic prediction using machine learning techniques [23]. In general, prediction algorithms range in automation, with the least automated, most manual methods requiring designers to hand-encode accurate models, and the most automated methods demonstrating feasible results but are not extensively tested for interpretability and generalizability.

Full end-to-end design flow automation encompasses the entire EDA flow, and can range from full custom design of digital or analog circuit blocks to larger heterogeneous system-level designs. Generator-based methodologies provide a feasible semi-automated and accurate solution by encouraging designers to manually codify designer intent for a given circuit topology, which can then be reused or regenerated for varying specifications, becoming a more agile process [24, 25]. More ambitious, and still-in-progress initiatives are looking into fully automated end-to-end design using machine learning or other automation techniques [3, 26], but still require accuracy and practicality verification.

In summary, prior automation works provide promising and successful approaches to different aspects of the ASIC design process, and vary vastly in methodology depending on the particular sub-problem they solve. These approaches range in degree of automation, generalizability, accuracy, and interpretability.

### 1.3 Thesis scope and outline

This thesis will focus on how applying various machine learning (ML) techniques can successfully automate different areas of ASIC development, while showing analysis to support that ML can address the six main baseline requirements, which are accuracy, practicability, automation, interpretability, generalizability and run-time efficiency. The goal is to demonstrate that ML techniques have the potential to practically accelerate inefficiencies in the ASIC flow, by presenting one in-depth case study and two initial projects which include: 1) an analog circuit design framework that uses reinforcement learning (RL) to size parameters for a given circuit topology to meet a target specification, 2) using convolutional neural networks (CNNs) to detect defects in physical silicon that affect circuit yield, and 3) an analog sub-clustering tool that uses graph CNNs to group analog circuits. These projects are discussed in the context of the six requirements, and new analyses, metrics, and comparisons are used to validate their efficacy and feasibility.

• Chapter 2 introduces and discusses using RL to size a two-stage amplifier and two-stage amplifier with negative  $g_m$  load, and demonstrates that this automated framework has high accuracy, is interpretable and run-time efficient.

#### CHAPTER 1. INTRODUCTION

- Chapter 3 expands these results by testing on a complex parasitic-sensitive two-stage folded-cascode circuit to show that the algorithm is scalable, practicable, and general-izable.

- Chapter 4 discusses results on difficult-to-design ring amplifier and comparator topologies, and further analyzes and validates that the framework is generalizable and accurate.

- Chapter 5 discusses initial results on applying GCNNs to cluster analog sub-circuits to identify critical structures to automate the generation of analog layouts.

- Chapter 6 presents initial results and analyses on applying CNNs to detect systematic layout defects in standard cells for circuit yield.

- Chapter 7 concludes the thesis with overall discussion on the three projects, in addition to providing directions to future work in this area.

## Chapter 2

# Reinforcement Learning for Well-Defined Circuit Topologies

This chapter presents a machine-learning optimization framework trained by using deep reinforcement learning to find post-layout circuit parameters to meet a given target specification, while also gaining knowledge about the entire design space through a sparse sub-sampling training technique. We show that this approach:

- generalizes across four well-defined circuit topologies of varying complexity,

- is accurate, as it obtains performances that meet at least 96.3% of tested target design specifications, while also considering post-layout simulations, which is an important part of the design process,

- is up to  $40 \times$  more run-time efficient compared to prior work, and

- is practical, as the failures in the tool reflect design constraints as opposed to anomalies in the framework.

### 2.1 Introduction to analog design and sizing

Analog design is an important part of the ASIC development process, as analog circuits are responsible for filtering, amplifying and retaining fidelity in continuous time-domain signals. Even though analog blocks in analog and mixed-signal (AMS) chips do not take as much area as their digital counterparts, the design effort that goes into creating these blocks is still dominated by analog circuits, primarily because they require significant manual design effort. Today's designers are confronted with higher simulation workloads that result from more corners and parasitic elements, tougher design challenges due to difficult-to-predict parasitic effects, and more layout effort because of generally higher device count and restrictive design rules [27]. In order to reduce time-to-market, it therefore becomes crucial to identify and automate time-consuming analog procedures in an efficient and accurate manner.

Analog sizing is one aspect of analog design, where a designer selects parameters for a given circuit topology such that it meets a known target specification. This process can be

summarized as a guided multi-objective optimization problem, where designers are heavily involved in the iteration process and are responsible for understanding the tradeoffs between specification and parameters in order to find a feasible solution. Analog sizing is a difficult problem, however, primarily because it involves multiple schematic and layout simulations at different stages of the design process, and these often rely on designers to manually create the required circuit layout, which, when simulated, can take a long time. In addition, the traditional analog design process relies on designer intuition to drastically reduce the range of possible parameters in the search space. Even though this methodology can be manually scripted into a program, simulation results in newer technology nodes are difficult to predict due to enhanced parasitic effects. The relationship between parameters and specification can also vastly vary depending on the circuit topology, which ranges in complexity and variety, greatly increasing the number of tunable parameters in the design space, while also making any fixed circuit-specific methodology infeasible for a scalable analog sizing tool.

### 2.2 Prior analog sizing tools

Developing a practical and accurate analog sizing algorithm requires understanding the unique constraints imposed by considering layout parasitics, which are a result of the physical elements of the circuit, such as wires, adding previously unmodeled resistances, capacitances, and inductances to the design. In particular, post-layout simulation is not only a manual process that takes significantly more time than its schematic counterpart, but also leads to large, often unpredictable variability in the simulation results. This then dictates that a sizing approach requires minimal simulations to converge to the target specification, while also being robust and accurate in situations where large variations in performance exist due to parasitics. We discuss prior work in both of these contexts.

Traditionally, expert circuit designers employ a knowledge-based analog circuit synthesis methodology [28, 29, 30, 31], where design considerations and parameter selection algorithms are manually codified or formulated as templates in an effort to encapsulate the designer's knowledge. This strategy, however, still requires circuit designers to be heavily involved in the sizing process, and though efficient in converging to a specification, it is not automated, and often does not consider parasitics explicitly as its effects are difficult to model. In addition it requires a large overhead in defining any new specification.

Equation-based methods [32] manually or automatically obtain constraint equations that are then optimized or solved. These solvers require very few, if any, simulation iterations, but involve manual equation formulations, do not consider parasitics, and only allow circuits with known dependencies to be characterized.

Bayesian optimization, genetic algorithms and their optimization-based variants have also been utilized extensively, primarily via stochastic sampling to simulate a certain population of design points which are either mutated based on a fixed cost function to produce new, potentially more fit points that are simulated again in the next iteration [17], or used to generate surrogate models [33]. Genetic algorithms, traditionally, require many simulations to

converge and are not reliable, as the converged result heavily depends on how well the initial stochastic sampling reflects the true design space. In addition, they require the algorithm to be re-started whenever a change is made to the goal. Though Bayesian optimization solutions [33] are more sample efficient, formulating a Gaussian Process model is more expensive as the dimensionality of the data increases, meaning that this solution is potentially prone to issues in scalability. Several works exist that attempt to reduce the inefficiency of these algorithms, primarily via learning [34, 35, 16, 36]. [34], [35], and [36] do not, however, demonstrate results with layout parasitics, making it difficult to claim the reliability and practicality of these results. Authors in [16] demonstrate that their combined neural-network-boosted genetic algorithm can function on complex circuits with post-layout simulation following parasitic extraction (PEX), but the algorithm requires many PEX simulations to converge, making it difficult to scale to more complex circuits. Bayesian optimization methods [33], despite being more sample efficient, have not yet been proven with parasitic simulations.

Reinforcement learning (RL) has been applied to analog sizing as well, where an agent traverses the design space while trying to maximize a reward function. [37] explores initial results using this method, but only tests with NGSpice as the simulator, which is not reflective of the true complexity of state-of-the-art processes. [38] and [25] and use enhanced RL methods with recurrent or graph convolutional neural networks, respectively, that are trained using policy gradients. These algorithms do not consider layout effects and train the agent to meet only one target specification, requiring many circuit simulations to converge to other targets. [25] does however, show initial promise in using generalization to transfer information across topologies. [39] accelerates RL convergence by incorporating local constraint satisfaction while considering process corners, but fails to consider layout parasitics.

Despite the existence of automated layout-synthesis tools [40], prior sizing algorithms opt to use parasitics models [41, 42, 43, 44, 45, 46] to approximate layout effects without impacting simulation time. Approximate models show initial promise in predicting parasitic effects, but need to be further analyzed for accuracy and scalability on more complex circuits in newer and more parasitic-dominant technology nodes. Methodologies also exist that use lookup tables a-priori to simulate all relevant designs, but are time consuming and not scalable, as they require collecting a large number of layout simulations [47]. Authors in [44] propose a neural network metamodel that performs optimization in a sample efficient manner, requiring just two layout simulations to converge to a solution. Their methodology, however, requires a designer to manually create layout, and only tests on smaller-order circuits.

In summary, there is need for an accurate and reliable method for solving analog circuit sizing, that not only considers the many stages of the design process that experts use to validate an analog design, from schematic, layout and process-corner simulations, but must also do so with reasonable run-times. This, in addition to understanding how and why the tool works, is crucial in the adoption of any sizing framework in the analog design community.

## 2.3 Introduction to machine learning

Machine learning (ML) is a growing field that studies the computational processes used by humans and machines [48], and is often used to solve complex tasks such as natural language processing, medical diagnosis, or speech recognition. ML encompasses a broad range of algorithms for classification, regression, optimization, recognition, clustering, and more, with new algorithms being developed as active research areas. Most ML methods take advantage of data by attempting to extract patterns within the data, or relationships between sets of data. The amount of data required, however, varies depending on the specific algorithm.

Determining whether ML is the right solution for a given task greatly depends on the type of problem, and is generally applied in cases where:

- deterministic rules cannot be codified easily for the task by using a simple algorithm, making it too difficult for a human to accurately code rules, and the

- existing solutions cannot scale in complexity to larger or more complicated data [49].

Traditional ML techniques are often seen as a black box; to the user the objective is reached but the process the algorithm uses to obtain it is unknown. Recently, researchers have looked into increasing the transparency and controllability of automated ML systems [50], allowing the efficacy, accuracy, interpretability and practicability of the algorithm to be analyzed. This analysis is especially important in tasks where reliability is crucial. It is the intent of this thesis to demonstrate application-specific study for a traditionally black-box ML algorithm, in the hopes of convincing the reader that ML methods can be understood effectively.

## 2.4 Reinforcement learning framework

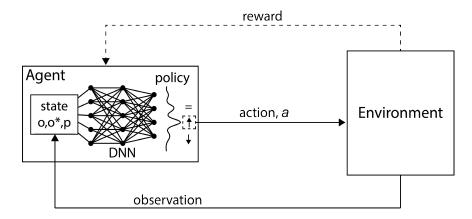

Reinforcement learning (RL) is a class of techniques under machine learning that consists of an agent that interacts with its environment through a trial-and-error process that mimics learning in humans. It is a simulation-in-the-loop method, and relies on the ability to verify outputs from a true simulation source.

At each environment step, the RL agent, which contains a neural network, observes the state of the environment and takes an action sampled from the output of this probabilistic distribution. The environment then returns a new state which is used to calculate the reward for taking that action. The agent iterates through a trajectory of multiple environment steps, accumulating the rewards at each step, until the target is met or a predetermined maximum number of steps is reached. After running multiple trajectories, the neural network is updated to maximize the expected accumulated reward using policy gradients.