# PCB-less Integration of a Robust Wireless MEMS Tactile Package

Dillon Acker-James

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2023-1 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2023/EECS-2023-1.html

January 9, 2023

Copyright © 2023, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### PCB-less Integration of a Robust Wireless MEMS Tactile Package

by

#### Dillon Acker-James

A thesis submitted in partial satisfaction of the requirements for the degree of

Masters

in

Electrical Engineering

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Kris Pister, Chair Professor Eric Paulos

Fall 2022

## PCB-less Integration of a Robust Wireless MEMS Tactile Package $\,$

Copyright 2022 by Dillon Acker-James

#### Abstract

PCB-less Integration of a Robust Wireless MEMS Tactile Package

by

Dillon Acker-James

Masters in Electrical Engineering

University of California, Berkeley

Professor Kris Pister, Chair

Creating a wireless tactile actuator the size of an aspirin will allow for more precise physical stimulation. This will lead to a more immersive virtual reality (VR) experience and better convey information via touch. Making this wireless tactile actuator can be accomplished by further utilizing the existing Si on Insulator (SOI) structure. Currently, a printed circuit board (PCB) is used for the sole purpose of assembly, however, further utilization of the Micro Electromechanical Systems (MEMS) SOI structure can allow the chip to operate as both the actuator and housing package. In addition, the MEMS Si could replace circuitry previously incorporated in eternal components: lateral relays replacing high voltage buffers. The assembly of electronics into a MEMS housing was found to require finer assembly tools, lateral SOI relays to control the MEMS devices showed a need for a more durable contact material, and fabrication methods to enhance MEMS robustness are presented. These are meant to enable a durable aspirin-sized package to controllably stimulate the human skin.

Find what you enjoy doing and go do it.

## Contents

| Conten                          | ts                                                                                                                                                                                                                                             | ii                                   |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| List of                         | Figures                                                                                                                                                                                                                                        | iv                                   |

| List of                         | Tables                                                                                                                                                                                                                                         | vii                                  |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | gration to Create a Wireless Tactile Stimulator Vibration: The Most Common Tactile Stimulation Method A More Precise Method of Tactile Stimulation Overview Power: Zappy Control: SCuM MEMS Device Fabrication Integration of the 3 Components | 1<br>1<br>2<br>2<br>3<br>4<br>4<br>5 |

| 2.1<br>2.2                      | Powering Integration by Eliminating the Need for SCuM and Zappy Powering Inchworm Motors with Structural Si Hot Switching Mechanical Finite State Machine (MFSM) to Run an Inchworm Motor Conclusions for Eliminating SCuM and Zappy           | 14<br>15<br>17<br>18<br>21           |

|                                 | Cion Devices Preventing Contamination                                                                                                                                                                                                          | 25<br>26<br>33                       |

| 4.1<br>4.2<br>4.3<br>4.4        | Integration                                                                                                                                                                                                                                    | 35<br>35<br>36<br>36<br>44           |

| Bibliog                         | raphy                                                                                                                                                                                                                                          | 45                                   |

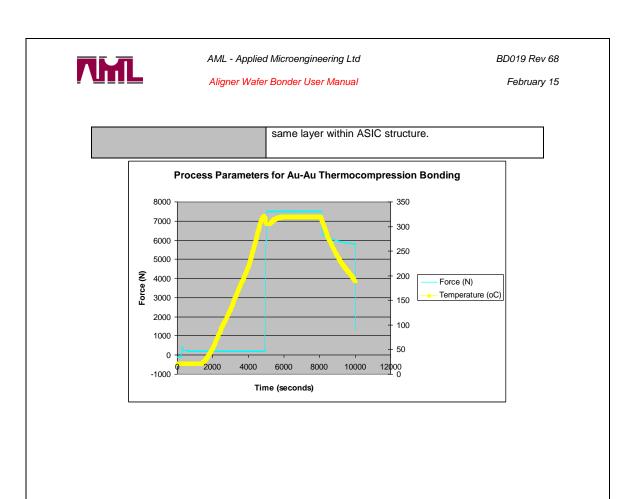

A AML AWB-08-30 Wafer Bonder Manual Chapter on Thermocompression Bonding

**47**

## List of Figures

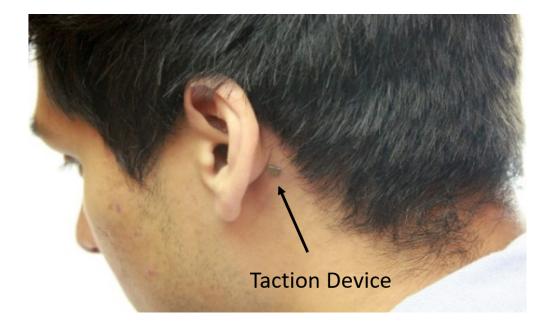

| 1.1  | An image taken by the Paulos group showing a taction device placed by the ear        |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | of a user. Note, this is only the MEMS component and not the entire wearable         |     |

|      | system                                                                               | Ç   |

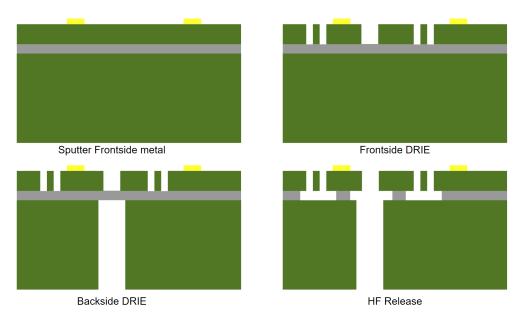

| 1.2  | Top left: pattern sputtered metal stack - 50nm of Ti or Cr and 0.5um of Au. Top      |     |

|      | Right: DRIE frontside features, 2um minimum. Bottom Left: Backside DRIE              |     |

|      | 40um wide trenches. Bottom Right: HF release with 6um undercut                       | 4   |

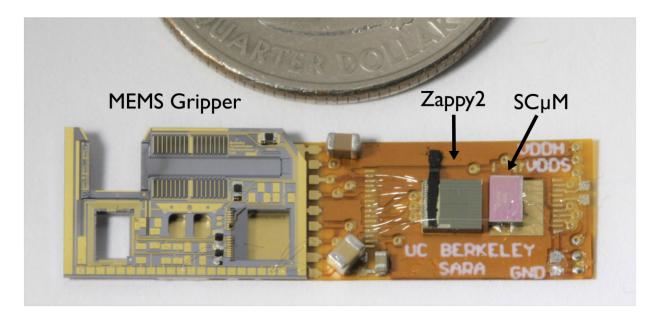

| 1.3  | The proof of concept setup where the three chips are fixed to a PCB and then         |     |

|      | wirebonded together along with external capacitors soldered to the flexible PCB.     |     |

|      | Left to right, Gripper, Zappy, and SCµM [10]                                         | Ę   |

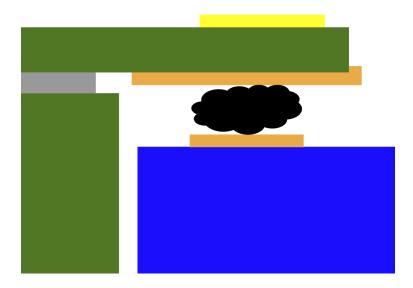

| 1.4  | A cross section cartoon of an IC (blue) with its Al pad (orange) epoxied (black)     |     |

|      | to the Al (orange) that has been sputtered on the backside of the device Si (green). | 7   |

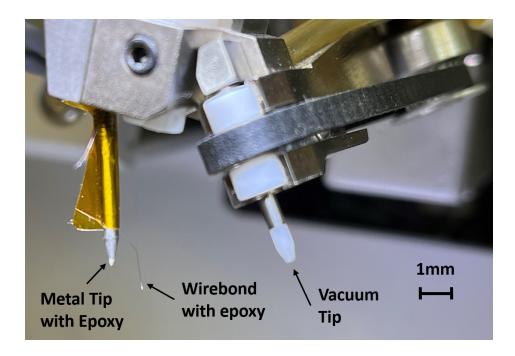

| 1.5  | The three tips attached to the micromanipulator. The metal and vacuum tips           |     |

|      | came with the tool, but a wirebond wire was taped to the metal tip for epoxy         |     |

|      | application.                                                                         | 8   |

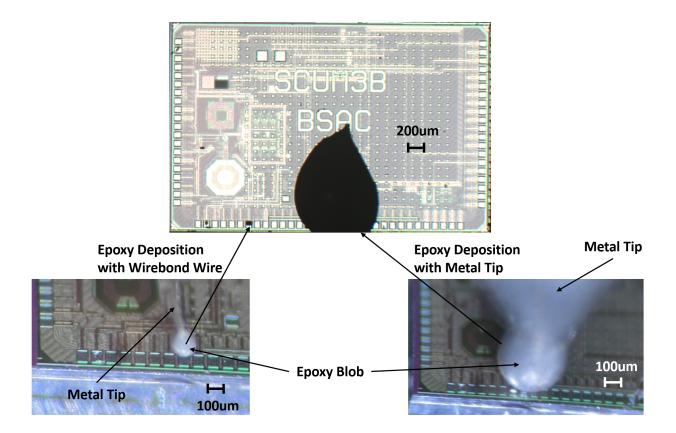

| 1.6  | Three images of SCuM where the bottom left shows the application of epoxy with       |     |

|      | the wirebond, the right shows the application of epoxy with the metal tip and        |     |

|      | the top image shows the resulting epoxy droplets from each method                    | Ć   |

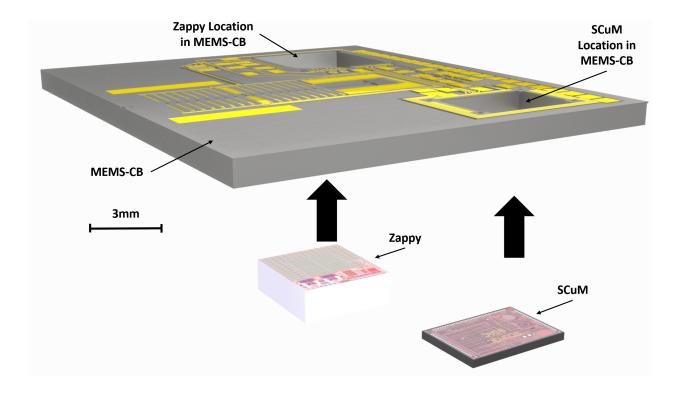

| 1.7  | A 3D rendering of the integration step where the MEMS-CB is lowered onto the         |     |

|      | two ICs with conductivity epoxy on their pads                                        | 10  |

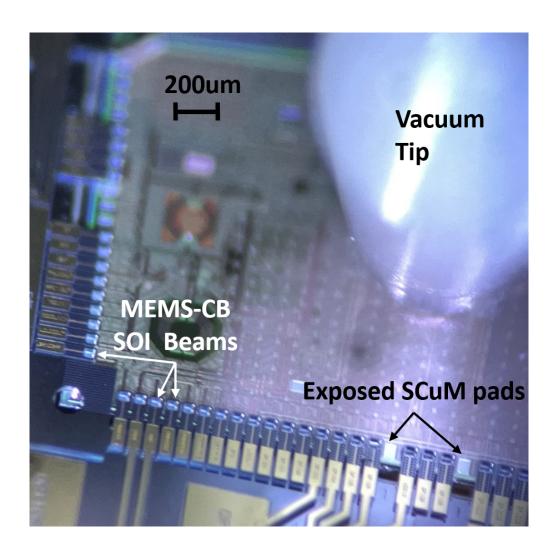

| 1.8  | SCuM was raised and aligned to the SOI Beams of the MEMS-CB with the                 |     |

|      | vacuum tip of the micromanipulator. Two SOI beams were purposely removed so          |     |

|      | that the Al IC pads could be seen                                                    | 11  |

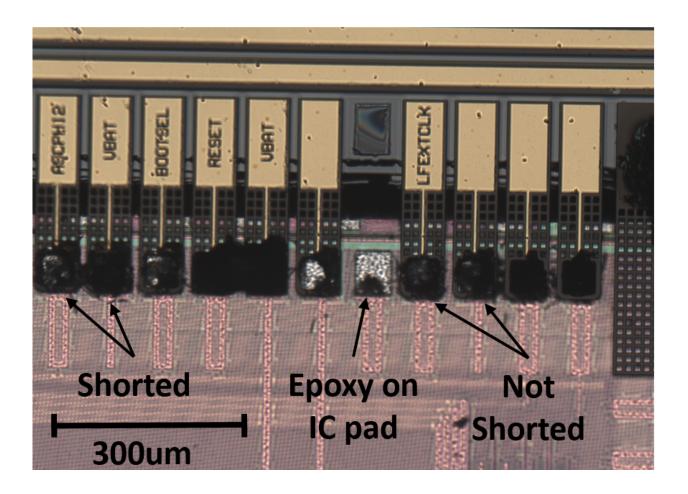

| 1.9  | An image of an attempt to integrate SCuM into the MEMS-CB. Most adjacent             |     |

|      | SOI beams were shorted together, not all are labeled. One beam was intentionally     |     |

|      | removed to show the size of the epoxy blob on the IC pad that caused this shorting.  | 12  |

| 1.10 | A 3D rendering of the full wearable where SCuM and Zappy are fixed to the            |     |

|      | MEMS-CB with glass only covering the MEMS components. The ten shown                  |     |

|      | circuit components are needed for integration: jumpers in black and capacitors       |     |

|      | in blue. The remaining Au pads are for debugging during the assembly process         |     |

|      | and                                                                                  | 13  |

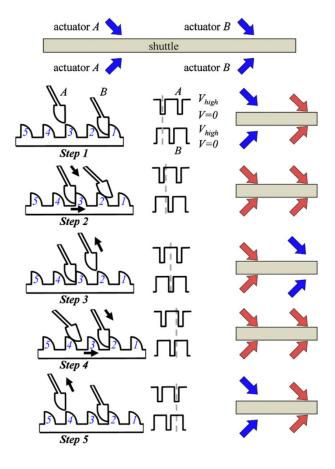

| 2.1  | Overview of inchworm motor control and operation [12]                                | 1.5 |

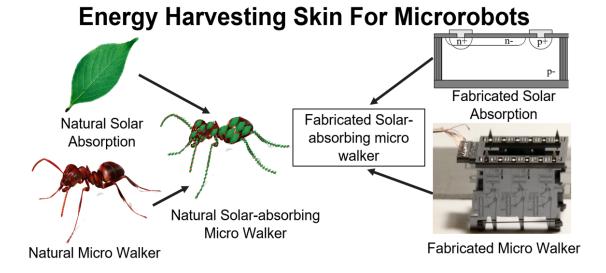

| 2.2        | Cartoon illustrating the idea of solar skin on a MEMS device, which for this example, is a microwalker [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.3        | Process flow for solar skin MEMS structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16         |

| 2.4        | Plot of experimental and theoretical force [15]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17         |

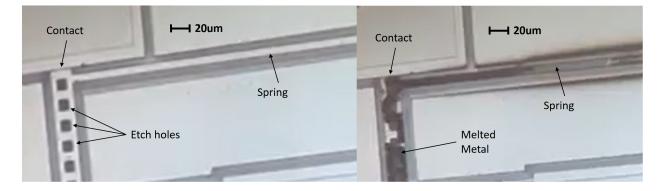

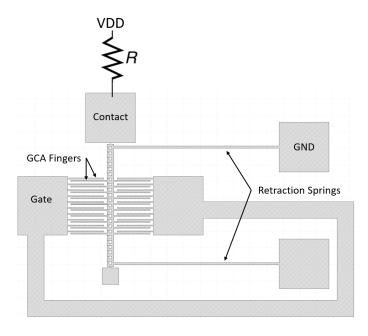

| 2.5        | Layout and a schematics of the pull up network for a pull in and pull out sensor where R is $1M\Omega$ . Left: layout of a relay with a pull in sensor Contact and a pull out sensor PO. Top Right: the schematic for the pull in sensor. Bottom Right: A zoomed in image of what the device looks like once its been setup - not its layout. The PO node must make contact to the GND node, but cannot be fabricated connected since they also must be separate physical parts. The large Si rectangle is dragged into contact with a probe - note the difference between the left and |            |

| 2.6        | bottom right images                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19         |

| o =        | of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20         |

| 2.7        | 100nm of sputtered Ru film underwent a visual change when the Contact node was left floating upon pull in. Left: the relay just before pull. Right: Just after                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.1        |

| 0.0        | pull in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21         |

| 2.8        | The circuit schematic of the hot switch test setup. VDD was 30V for Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 00         |

| 2.9        | 2.10 and 2.11 and but R was constant at $1M\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22         |

| 2.10       | left probe was GND, and the right was Contact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22         |

| 2.11       | The top probe was Contact, left probe was Gate, and the right was GND A relay sputtered with 30nm of Ru that underwent a violent change when hot switched at 30V, even with a $1M\Omega$ resistor                                                                                                                                                                                                                                                                                                                                                                                       | 23<br>23   |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _          |

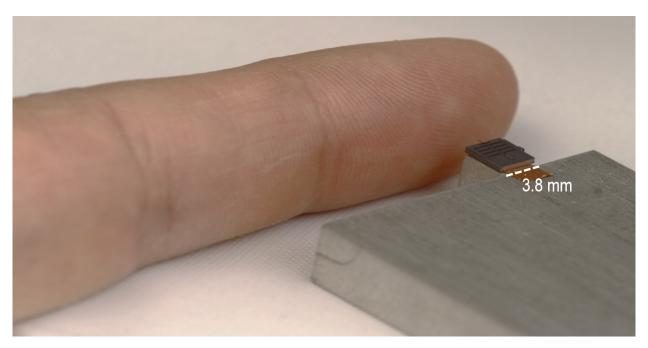

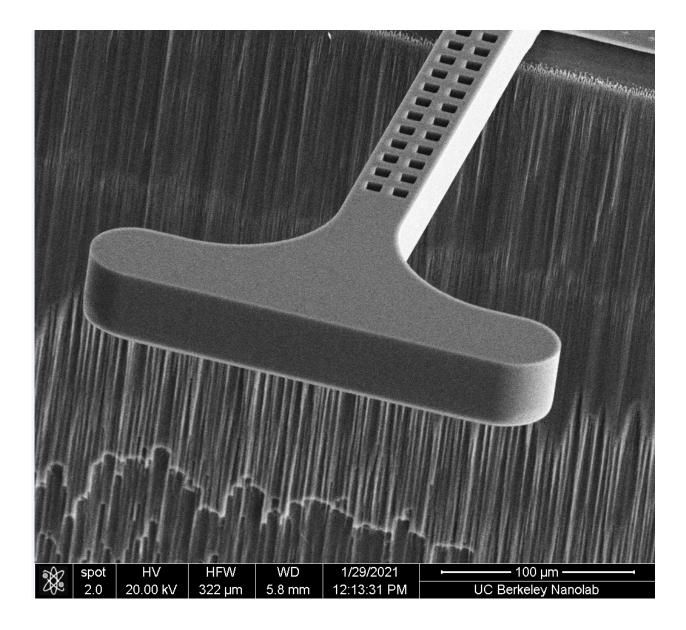

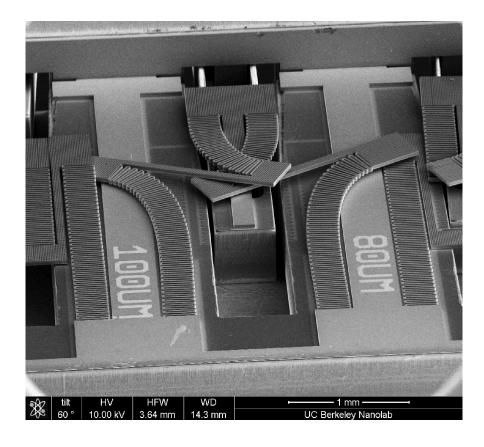

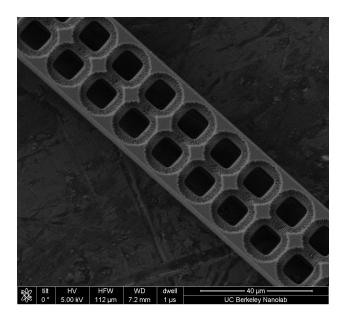

| 3.1<br>3.2 | An image of the V1 taction device next to a finger provided by the Paulos group. A SEM image of the V1 taction device's end effector. This is the Si that makes                                                                                                                                                                                                                                                                                                                                                                                                                         | 25         |

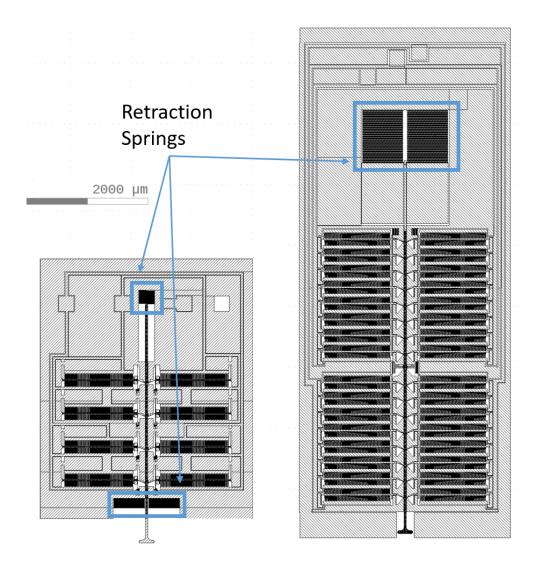

| 3.3        | contact with human skin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26         |

|            | device from the end effector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25         |

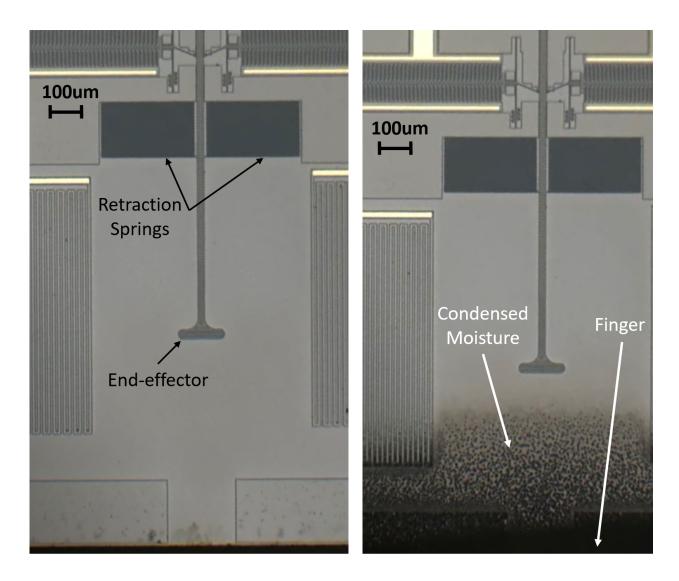

| 3.4        | Left: a tactile device with no contamination (human skin) nearby. Right: a finger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27         |

|            | is placed at the bottom edge of the chip which causes particles to condense on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28         |

| 3.5        | A zoomed in image of the bonded stack cracking and misalignment. On the image to the left, the gray is the Titanium (the bottom of the Au stack) shown though                                                                                                                                                                                                                                                                                                                                                                                                                           | <i>4</i> 0 |

|            | the quartz wafer and the yellow is the gold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29         |

| 3.6  | Au stack peeling after liftoff. The black strips are peeled back folds of the metal                                                                                                                                                            |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | stack and the green is the glass wafer                                                                                                                                                                                                         | 30 |

| 3.7  | The quartz wafer cracking after the bonded stack cools                                                                                                                                                                                         | 31 |

| 3.8  | The SOI substrate cracking as the bonded stack cools                                                                                                                                                                                           | 32 |

| 3.9  | Process flow showing how to create 2 chips and expose pads through a full and partial dice where grey is glass wafer and SiO2, yellow is Au, and green is Si                                                                                   | 33 |

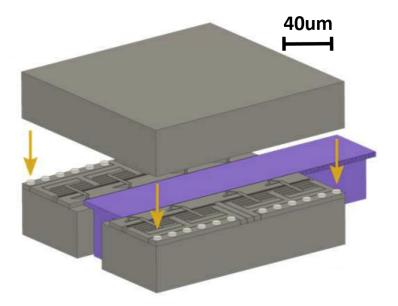

| 3.10 | An 3D rendering from [16] showing simplified illustrations of the inchworm motor running after an SOI cap was bonded. The cover is bonded on top with dots of silver epoxy and the (purple) inchworm motor shuttle is still able to move after |    |

|      | the bond                                                                                                                                                                                                                                       | 34 |

| 4.1  | An image of Dr. Hani Gomez's locking springs that became twisted due to an unaccounted moment [5]                                                                                                                                              | 37 |

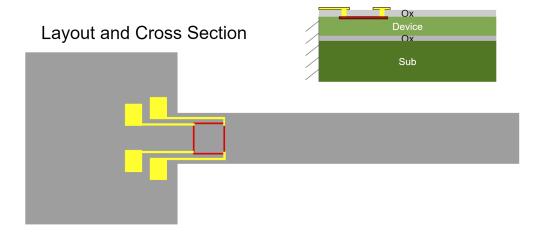

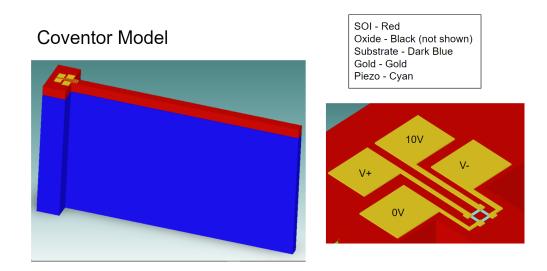

| 4.2  | The layout and cross section of the device to be simulated                                                                                                                                                                                     | 37 |

| 4.3  | An overview of the cantilever's design.                                                                                                                                                                                                        | 38 |

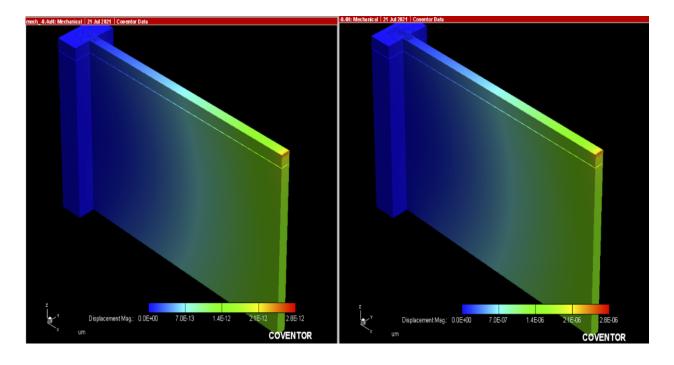

| 4.4  | Two simulated displacements in CoventorWare. Left: designed minimum sensible                                                                                                                                                                   | 00 |

| 1.1  | force of 0.4uN. Right: designed maximum force of 0.4N                                                                                                                                                                                          | 38 |

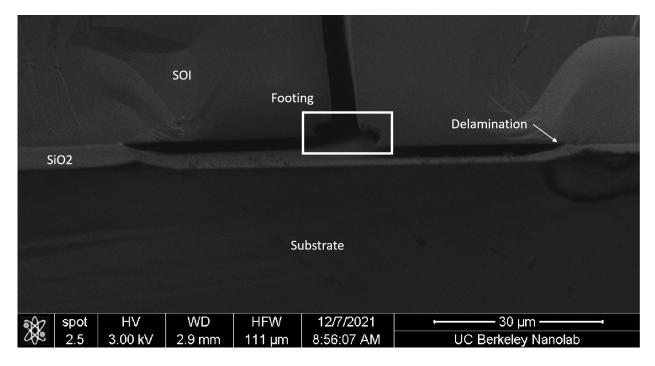

| 4.5  | Cross section of an SOI wafer that shows footing of a DRIE trench and the delamination of Si from SiO2. The SiO2 layer is 2um and though some remains,                                                                                         | 90 |

|      | it has been laterally etched 30um.                                                                                                                                                                                                             | 39 |

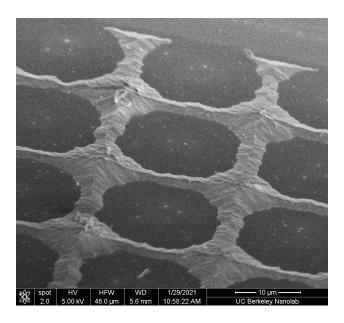

| 4.6  | Unetched SiO2 on the Si substrate that caused device Si, that was supposed to                                                                                                                                                                  |    |

| 4 7  | be released, to catch as it moved                                                                                                                                                                                                              | 40 |

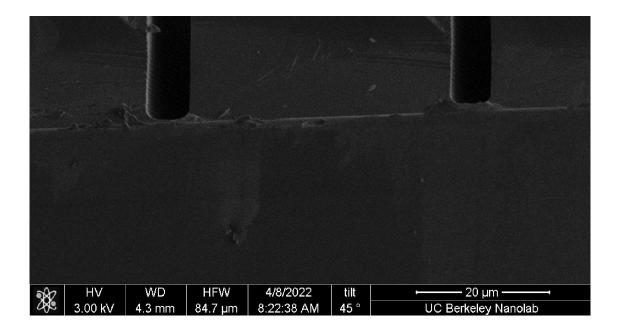

| 4.7  | Two DRIE trenches that did not etch down to the SiO2 layer, resulting in all devices on the wafer not functioning                                                                                                                              | 41 |

| 4.8  | The serpentine springs after the overetch in the DRIE caused them to overheat and burn off the photoresist defining the structure                                                                                                              | 41 |

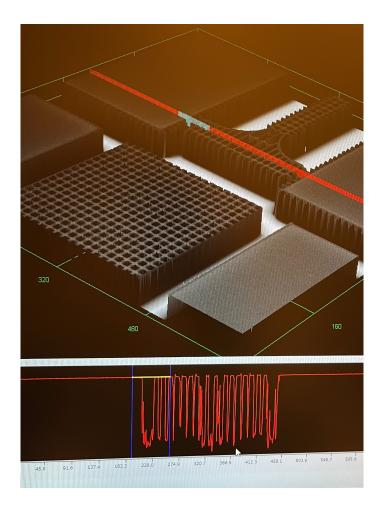

| 4.9  | Screenshot of Olympus measuring SOI features that have not completed their                                                                                                                                                                     |    |

|      | etch. The top image is a 3D optical scan of the SOI features, where the red line                                                                                                                                                               |    |

|      | shows the cross section plane of the etch holes shown below. It does not appear                                                                                                                                                                |    |

|      | that etch holes completed their etch, but further etching does not change the                                                                                                                                                                  |    |

|      | clarity on this tool                                                                                                                                                                                                                           | 42 |

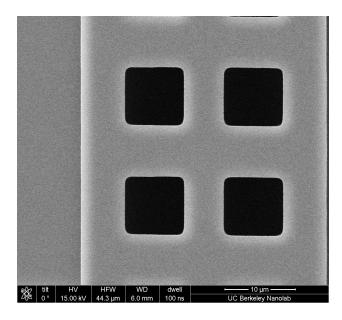

| 4.10 | The topside of a feature, which looks as drawn                                                                                                                                                                                                 | 43 |

| 4.11 | The bottom of the same feature, showing extreme footing. The circular shapes around the squares are where Si was etched due to ions bounding off of the SiO2                                                                                   |    |

|      | and removing the Teflon passivation                                                                                                                                                                                                            | 43 |

|      |                                                                                                                                                                                                                                                |    |

## List of Tables

| 2.1 | Table of the 100x change in contact resistance with changing applied voltage. |    |

|-----|-------------------------------------------------------------------------------|----|

|     | The 100nm Ru-sputtered relay was designed to pull in at 30V, but pulled in at |    |

|     | 27V                                                                           | 19 |

| 3.1 | Table of Si, Quartz and Borofloat TCE [1] [13] [11]                           | 31 |

| 3.2 | Manual Recommended Values Compared to Those of a Successfully Bonded Stack    | 31 |

### Acknowledgments

My mentors, friends, and family, thank you.

I would like to additionally acknowledge all of the people involved in the development of

- SCUM: Filip Maksimovic, Brad Wheeler, David C. Burnett, Osama Khan, Sahar Mesri, Alex Moreno, Austin patel, Ioana Suciu (Universitat Oberta de Catalunya), Lydia Lee, Arvind Sundararajan, Bob Zhou, Rachel Zoll, Andrew Ng, Tengfei Chang (Inria, EVA Team), Xavier Villajosana (Universitat Oberta de Catalunya), Thomas Watteyne (Inria, EVA Team), Ali Niknejad, and Kristofer S.J. Pister

- Zappy2: Jan Rentmeister (Dartmouth), Professor Jason Stauth (Dartmouth)

- The 3D rendering software: Daniel Teal

- Devices were fabricated in the UC Berkeley Marvell Nanofabrication Laboratory and the staff were extremely helpful.

## Chapter 1

## Integration to Create a Wireless Tactile Stimulator

## 1.1 Vibration: The Most Common Tactile Stimulation Method

Our world is constantly vibrating. This is not a reference to the constant movement of atoms due to thermal energy, but rather the smartphones that are never too far away. Vibration motors are standard in all smartphones, in fact it would even be strange if one did not come with that feature. The first time tactile stimulation was widely used in electronic notification was in the 1950's with Motorola pagers to alert the wearer without disturbing others; the devices were everywhere, even used by emergency response, and the technology was borrowed by emerging electric toothbrushes [6]. Two decades later, Thomas Shannon was granted the first US patent for tactile telephones in 1973, and now they are not just standard in phones, but each smartphone has multiple vibration motors. But in 1995, Geir Jensen illustrated the idea of a haptic wristwatch, Tap-in, where the device had a unique poking pattern for defined callers. It could even facilitate the user to reply with a set of selected short messages. However, the project was not pursued or published until 2015 - the same year Apple started selling a wristwatch that included skin tap alerts to the user [17].

Though commonly used for notification, haptic devices are also used to immerse the user in other worlds. For decades, Disney has been using a combination of haptic actuators to create more immersive rides and shows. In conjunction with visual and audio stimulation, there are tactile simulators incorporated into the system to create more immersive experiences [7]. However, these actuators are still vibration-based, thus limiting the amount of sensations that are able to mimic due to the large location a vibration motor stimulates. With the prevalence of tactile stimulators based solely on vibration actuation, new methods, more precise methods, of touch actuators are needed.

#### 1.2 A More Precise Method of Tactile Stimulation

Rather than a spinning weight causing vibrations, a more precise method of stimulation can add a different gadget to the to the toolbox of haptics engineers: creating a poking wireless tactile stimulator the size of an aspirin. Humans have five senses, of which only three are widely used for stimulation from electronics: sight, sound and touch. A variety of sights and sounds can be generated and programmed, not just by engineers who make them, but by the users themselves: phones, electronic watches, cars, etc. can all have customizable notifications. However, the only physical sensation electronics really use is vibration. Imagine all of the different physical surfaces touched in a single day. Mimicking those to create a more realistic virtual reality, for example, will require more precise stimulation than just vibration. Investigating other ways to electronically control tactile stimulation is critical to better communicate information via touch.

When operational, a wireless aspirin-sized poking device could be utilized in a myriad of ways, especially with arrays of them are linked to create more complex sensations. In virtual reality (VR) applications, the added functionality of a suit of wireless tactile stimulators has impactful possibilities. Used in conjunction with the widely-popular vibration motors, arrays of pokers could further add to linking the physical with virtual worlds. This potential, though extremely useful for, goes beyond the entertainment industry. With an overwhelming amount of sights and sounds sometimes overstimulating the daily senses, incorporating more precise tactile feedback can aid in the completion of more complex tasks. For example, remote operation of a surgical robot. With the development of robotics along with remote control, video game-like consoles can be used for more than just entertainment. In this situation, a vibrational notification, like getting too close to an artery, may increase the difficulty of the user to accomplish the task due to the large area vibration stimulated. Whereas a single poke, or multiple pokes, in defined patterns may relay the information in a more subtle and useful way.

One method to expand this haptic toolbox by stimulating the skin in a different way, is to use a Silicon on Insulator (SOI) Micro Electromechanical Systems (MEMS) device that physically pokes the user. Fig. 1.1 shows a goal of this work fixed to a user: to make a wireless tactile MEMS actuator the size of an aspirin. The inchworm motors in this work provide enough force to be detectable by the human skin when run with at least 30V. The small, 2um minimum, feature size of microfabrication and large force, multi-mN, capability of inchworm motors allows for the potential creation of many more electronically controlled physical sensations. However, to wirelessly run an inchworm motor to accomplish this haptic goal, it currently needs to be integrated with two other chips that provide power and control.

### 1.3 Overview

To make a wireless MEMS device, three components are needed: Power, Control and the MEMS component. Previous work has shown three chips (Zappy for power, SCuM for

Figure 1.1: An image taken by the Paulos group showing a taction device placed by the ear of a user. Note, this is only the MEMS component and not the entire wearable system.

control and a Gripper as the MEMS component) working together [9]. Though this shows proof of concept, it is not practical for a wearable package. Zappy and SCuM are made in foundry processes with limited flexibility to aid in post-process assembly. However, the MEMS component is made by a graduate student in a SOI process in the UC Berkeley nanolab, which offers more design flexibility. Thus, instead of using a printed circuit board (PCB) as a housing to mechanically and electrically connect the three components shown in Fig. 1.3, the MEMS device can be designed based on the integrated circuits (ICs) layouts: integrate the two foundry ICs with the SOI chip as the hub rather than using a printed circuit board solely for integration like in Fig. 1.10. In addition, other MEMS components could replace the inchworm motor and other components could be added to increase the functionality further.

### 1.4 Power: Zappy

One of the limiting factors to microrobotics is a power source. The Stauth group developed an optically powered high-voltage drive circuit for microrobot applications [8]. This device is made in a 650V SOI CMOS process with 100umx100um pads with a 140um pitch. There is further work on improving the efficiency, flexibility and functionality of this chip, but this thesis will mainly consider the physical dimensions for integration purposes.

#### 1.5 Control: SCuM

Another limiting factor to microrobots is communication and control. The Single Chip micro Mote (SCuM) allows optical and Bluetooth communication and its GPIOs can interface with Zappy's high-voltage buffers to control multiple inchworms motors simultaneously. The pads are 40umx70um with an 80um pitch. Like with Zappy, there is further work on improving the efficiency, flexibility and functionality of this chip, but this thesis will mainly consider the physical dimensions for integration purposes.

#### 1.6 MEMS Device Fabrication

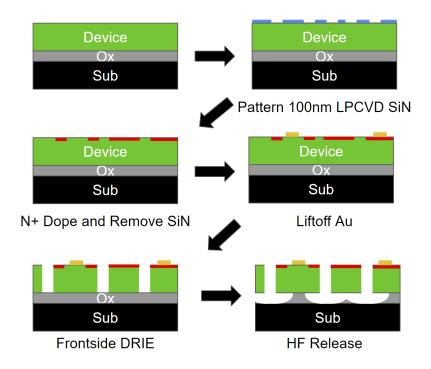

A 3 mask SOI process shown in Fig. 1.2 has the capability to fabricate devices with wide ranging functions. Though, not an overly complex process, it is useful for quickly trying different designs for a faster design loop. This fabrication is done in the UCB nanolab. Furthermore, making process and design changes can be accomplished quickly; once a design need is determined, for example sidewall conductivity needs to increase, a researcher can simply sputter a conductive material onto devices. This flexibility in design and process allows for the MEMS component to be utilized as hub chip for IC assembly.

Figure 1.2: Top left: pattern sputtered metal stack - 50nm of Ti or Cr and 0.5um of Au. Top Right: DRIE frontside features, 2um minimum. Bottom Left: Backside DRIE 40um wide trenches. Bottom Right: HF release with 6um undercut.

### 1.7 Integration of the 3 Components

#### Connections

How the chips are electrically and mechanically connected to each other is crucial. High resistance traces are lossy, which is detrimental to microrobots, and can even prevent the ICs from working properly. In addition, a weak physical connection is likely to lead to package failure. Ideally, the two ICs are bonded to the MEMS circuit board (MEMS-CB) with strong, low resistance connections.

#### Wirebonding Connections and PCB Housing

In the previous integration work, the chips were mechanically fixed with silver epoxy and the electrical connections were made with wirebonds as shown in Fig 1.3, along with the three external capacitors 22 uF 0402 Capacitor, 100 uF 0805 Capacitor, and 100 nF 0805 Capacitor required to respectively to maintain voltages VDDIO, VBAT, and VDDH.

Figure 1.3: The proof of concept setup where the three chips are fixed to a PCB and then wirebonded together along with external capacitors soldered to the flexible PCB. Left to right, Gripper, Zappy, and SCμM [10].

This proved that these three components could act as an independent system under 2 suns [10]. However, the size increased caused by the flexible PCB is not ideal, and the free-floating wirebonds are not robust enough for wearable applications. A smaller and more durable package was needed.

#### MEMS Circuit Board (MEMS-CB)

The MEMS chip itself could be used as the circuit board to connect all of the electrical components of the system. The MEMS chip has the potential of very small features, such as 2 um wide Si beams. Even the wider beams required to support a Au trace are only 12um wide, including a 2 micron wide Au trace down the middle. While these dimensions are quite large by integrated circuit standards, they are quite small compared to most PCB designs, which are typically at least 100um wide. However, the MEMS chip provides only one layer of wiring, which is quite restrictive, but is mitigated by a lid chip described in chapter 3, or by  $0\Omega$  resistors used as jumpers to connect planar traces, both of which are seen in Fig. 1.10.

Using beams on the SOI layer like probes on a probe card, SCuM, Zappy or another IC can be inserted from the back side of the MEMS chip into an appropriately sized hole etched in the substrate, with all of the pads lined up under the SOI beams shown in Fig. 1.7.

Thus, small drops of epoxy deposited on Zappy and SCuM can serve as the mechanical and electrical connections. Currently, the resistivity of the SOI beams is  $15\text{-}25\Omega^*$ cm, and so traces of sputtered Au on the frontside, and Al sputtered to the bottom side of the device Si aid in decreasing the connection resistance. This resistance, defined from Al pad of IC to Au pad on the MEMS device, will be dominated by the resistance of the Si beam: roughly 40um thick x 40um wide x 70um long with a resistivity of  $15\text{-}25\Omega^*$ cm. The resistivity and thickness are set by the wafer spec, but width and length are set by the IC pad dimensions. This is theoretically  $3k\Omega$ , which matches experimental data. A large drop (5 pads worth) of epoxy was deposited on a gold surface, which was then brought into contact with SOI beams of a MEMS-CB; adjacent SOI beams were purposely shorted. Then the resistance was measured between adjacent pads that were shorted together through the epoxied Au; the resistance path is then roughly 2x of the  $3k\Omega$  resistive path illustrated in Fig. 1.4.

After release (Fig. 1.2) the underside of the device Si was sputtered with Al to decrease the connection resistance, but when that was compared to a MEMS-CB that did not have backside material sputtered, the resistance was within 10%, which is within experimental variation. Thus, the resistance between IC pads and the SOI beams of the MEMS-CB is dominated by the resistance of the device Si. Since the pad dimensions are defined by the IC pad pitch, they cannot be greatly changed. Therefore, lowering the connection resistance has to be accomplished by lowering the resistivity of the Si. Wafers with a highly doped device Si have not yet been explored in this application.

### Alignment and Assembly

We use the same micromanipulator for assembly alignment and epoxy application, using the appropriate tip for each. The tool came with 2 different tips, but we taped on a third for epoxy application shown in Fig. 1.5. With the current tool, alignment at this scale is difficult. The best solution that we've found is to use the wirebond tip on the micromanipulator to

Figure 1.4: A cross section cartoon of an IC (blue) with its Al pad (orange) epoxied (black) to the Al (orange) that has been sputtered on the backside of the device Si (green).

apply epoxy to the pads of the IC chips, and then raise the aligned IC chips with the vacuum tip until the epoxied pads contact the SOI beams of the MEMS-CB as shown in Fig. 1.7.

#### **Epoxy Application**

First, epoxy deposition was attempted by dipping the metal tip into epoxy and then controllably placing a blob onto a desired pad. However Fig. 1.6 shows that the epoxy deposited by the metal tip is nearly a millimeter and obviously far too large for the attempted microassembly. To apply a smaller amount of epoxy, a wirebond wire was taped to the tip of the micromanipulator. The wirebond's small gauge acts as a fine-tip to apply the epoxy; the micromanipulator is moved such that the wire is dipped into the epoxy and then onto the desired pad, leaving a droplet behind. Note, the epoxy deposited by the wirebond in Fig. 1.6 was left by touching down 3 times, despite the blob in the bottom left image of 1.6 looking larger than the IC pad. The amount of epoxy needed for each pad is significantly smaller than the blob picked up by the wirebond, but it is still recommenced that the wirebond is redipped into the epoxy between each pad application to keep the epoxy blob uniform. If this is not done the amount of epoxy deposited with the same force changes and can lead to unintended mechanical and electrical connections.

#### Alignment

The vacuum nozzle can be controlled in XYZ by moving the joystick of the micromanipulator; separately, the  $\theta$  of the vacuum nozzle is controlled with a dial on the joystick. The alignment

Figure 1.5: The three tips attached to the micromanipulator. The metal and vacuum tips came with the tool, but a wirebond wire was taped to the metal tip for epoxy application.

is then done by eye with the vacuum tip of the micromanipulator through a 1-5x microscope. After epoxy has been applied to the pads of the IC, it is placed below the raised MEMS-CB as shown in Fig. 1.7: the MEMS-CB remains fixed during alignment. Aligning and moving the IC pads into contact with the underside of the MEMS-CB SOI beam is accomplished by only moving the IC. The vacuum nozzle of the micromanipulator is used to pickup the IC and align it to the MEMS-CB shown in Fig. 1.8. Once aligned, the epoxy on the IC's Al pads comes into contact with the underside of their respective SOI beams to create mechanical and electrical connections between the two chips without the need for wirebonds nor a separate structural PCB.

### Full System Conclusions

With SCuM, Zappy and a MEMS-CB mechanically and electrically connected, an autonomous wearable tactile stimulator can be assembled as rendered in Fig. 1.10. Closer inspection shows ten circuit components mounted to MEMS-CB; the black  $0\Omega$  jumpers bridge planar traces due to the complex wiring needed on a single routing layer, and three voltage-maintaining capacitors shown in blue. In addition, adding a glass slide further discussed in chapter 3, increases the robustness of the MEMS device as well as potentially eliminating the need for the jumpers. The glass wafer is shown in conjunction with the jumpers to show

Figure 1.6: Three images of SCuM where the bottom left shows the application of epoxy with the wirebond, the right shows the application of epoxy with the metal tip and the top image shows the resulting epoxy droplets from each method.

different assembly options: the glass slide is not needed to integrate the wearable, but is a benefit to robustness and could also be used to simplify the MEMS-CB assembly. Whereas the jumpers are needed for the wearable assembly if the glass cover is not utilized due to the complexity of the necessary connections and limitations of a single routing layer. Regardless, the three capacitors are necessary components of the system.

The full integration was attempted multiple times but misalignment in conjunction with epoxy spreading was not solved. Aligning to the fine pad pitch of the SCuM chip is challenging and less than 100um misalignment is difficult with the current micromanipulator and 5x microscope. However, proper alignment was achieved, but even with adequate alignment, epoxy spreading is difficult to control. Dispensing a blob of epoxy smaller than the pads is achievable utilizing the wirebond wire explained above. However, the proper amount of epoxy is challenging. Too much epoxy and nearby traces were shorted, and too little did not result in a measurable connection. These assembly issues are likely solved with a finer micromanipulator, high magnification microscope and a more viscous epoxy.

Figure 1.7: A 3D rendering of the integration step where the MEMS-CB is lowered onto the two ICs with conductivity epoxy on their pads.

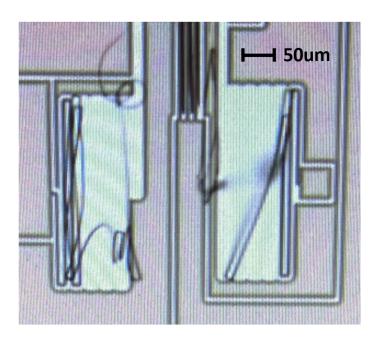

Figure 1.8: SCuM was raised and aligned to the SOI Beams of the MEMS-CB with the vacuum tip of the micromanipulator. Two SOI beams were purposely removed so that the Al IC pads could be seen.

Figure 1.9: An image of an attempt to integrate SCuM into the MEMS-CB. Most adjacent SOI beams were shorted together, not all are labeled. One beam was intentionally removed to show the size of the epoxy blob on the IC pad that caused this shorting.

Figure 1.10: A 3D rendering of the full wearable where SCuM and Zappy are fixed to the MEMS-CB with glass only covering the MEMS components. The ten shown circuit components are needed for integration: jumpers in black and capacitors in blue. The remaining Au pads are for debugging during the assembly process and

## Chapter 2

## Simplifying Integration by Eliminating the Need for SCuM and Zappy

As explained in chapter 1, power and control are needed in conjunction with a MEMS component to make a wireless MEMS package. This chapter explores ways to eliminate the need for Zappy, and in some applications, SCuM. The first objective of this chapter is to ease integration by eliminating the need for IC assembly by including essential functions of the ICs within components that can constructed in the MEMS fabrication process. The second is for microrobots to explore high temperature environments, for example the surface of Venus, where CMOS chips like SCuM cannot survive without extensive thermal protection.

To eliminate SCuM, the two square wave signals shown in Fig. 2.1 must be generated. However, if SCuM were to not be included, there could be no communication with the device. It could only be turned on and off by supplying enough power to run the inchworm motor, thus limiting its applications. However, the inchworm motors can be controllably run by illuminating the package: with Zappy's solar cells or others. To replace Zappy, not only does the power source need to be replaced, but high voltage buffers as well.

In the current operation with SCuM and Zappy running an inchworm motor, SCuM generates the square waves at a low voltage, which control Zappy's high voltage buffers that connect the solar cell high voltage output to the inchworm motor. To replace Zappy, high voltage hot-switchable relays and on-chip solar cells must be constructed; to replace SCuM, a method of generating the offset square waves must be constructed. This is proposed to be accomplished with a multifunctional solar skin, and an oscillator comprised of resistors and relays.

Figure 2.1: Overview of inchworm motor control and operation [12].

## 2.1 Powering Inchworm Motors with Structural Si

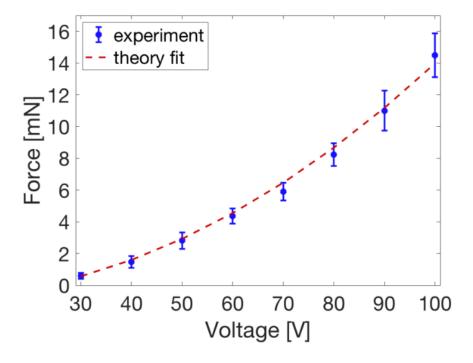

In the package outlined in chapter 1, the power comes from solar cells in the Zappy IC, and Fig. 1.10 shows a vast area of underutilized Si. It is there for structural purposes, but if doped, and wired, could potentially provided the needed energy to power an inchworm motor. Creating a solar skin from the device Si to power itself, like in Fig. 2.2 could be accomplished with the proposed flow shown in Fig. 2.3. In this flow, the N+ doping step along with the p- device Si makes the solar cell, and the Au pattern is used instead of a p+ region to conduct holes. This Au can also be used for wiring; as discussed in chapter 3, a glass or SOI chip with patterned Au can be bonded to the Au on the SOI wafer. This can simplify routing an array of solar cells, as well as increasing robustness. This MEMS device is a useful structures to achieve mN forces and cm displacements in a mm scale-package, however, to power it, with appreciable force, at least 30V is needed with an estimated few nanoamps of current Fig. 2.4.

Figure 2.2: Cartoon illustrating the idea of solar skin on a MEMS device, which for this example, is a microwalker [3].

Figure 2.3: Process flow for solar skin MEMS structures.

Figure 2.4: Plot of experimental and theoretical force [15].

## 2.2 Hot Switching

Hot switching is defined as two separate structures of different potential, physically coming into contact with one another. This is a major limitation with current micro-relays because hot switching, even at a few volts, leads to the contacts welding shut, thus destroying the device. Different theories exist on the exact physics that occur, but arcing and material transfer leading to contacts getting stuck closed with a higher potential differential is clear [2].

Making a high voltage hot-switchable relay is trivial for high resistance contacts: our Si-Si contacts range from  $1-10M\Omega$ s have survived over 100M hot switch cycles [3]. Stuck closure events are not currently seen in our SOI inchworm motors because the contact material is Si. Lower resistance contacts are achieved through metals, but suffer from hot switching failure; the contacts weld shut when the adhesion force is larger than the spring force, thus the relay remains closed. Our group has successfully hot switched lateral SOI relays with 60nm of sputtered TiN, but this was only done for a few cycles at 4V [14]. The purpose was to measure the time delay of a GCA opening and closing, not to have the device cycle more than a few times at a low voltage.

#### 18

## 2.3 Mechanical Finite State Machine (MFSM) to Run an Inchworm Motor

For mechanical relays to drive an inchworm motor with appreciable force, they must be hot-switched at least at 30V, which is very limiting to the force/usefulness of the inchworm motor, yet still difficult for a relay to survive even a few cycles. Fig. 2.1 shows the phase-shifted square waves required to run an inchworm motor. Currently, these signals are made with CMOS circuits but can also be generated only with relays - thus, eliminating the need for CMOS to run an inchworm motor.

There was significant effort to create a system where the opening and closing of the inchworm's two gap-closing arrays (GCAs), Actuator A and Actuator B shown in Fig. 2.1, would cause the next step in the state diagram. Meaning, applying one DC voltage would allow the inchworm motor to operate as though the same 2 phase-shifted square waves were applied. Since, the state where both GCAs are closed has two possible subsequent states, Actuator A opening or Actuator B opening, the control system requires memory. However, its not that simple because the mechanical and electrical time constants for a relay and GCA all need to be taken into account. Actuator A cannot open until Actuator B closes, and vice versa, in addition both actuators must open enough to fully release the shuttle.

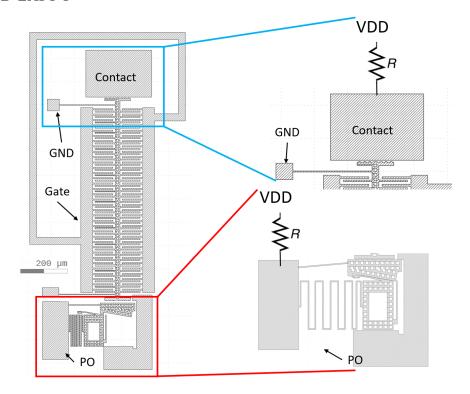

Thus, the test structures to measure the pull in and release times were repurposed to measure when the two actuators of the inchworm motors were open, closed or traveling between the two states [14]. When the relay is pulled out, Contact is VDD and PO is ground, and Contact is ground while PO is VDD when the relay is pulled out shown in Fig. 2.5. To avoid vertical pull in between movable SOI components and the substrate, they are both grounded. Thus pull up resistors to VDD were used to determine what state the Actuators were in, shown by the circuit in Fig. 2.5. However, this complex system of relays was never successfully fabricated; problems with relays intermittently sticking closed and syncing time delays of the physical structures with so many relays were not able to be overcome.

The easiest solution was found to simply create the two waveforms with oscillators constructed by relays. This is similar to the idea from Professor King Liu's group where simulated square waves were generated only from resistors and a mechanical relay [4]. The goal of this work was to run inchworm motors without the need for CMOS control, but never worked experimentally. Both the more complex MFSM and oscillator systems both use a relay as their basic unit, which is difficult to make hot-switchable at high voltages.

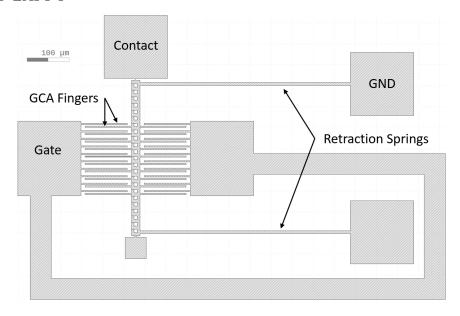

### Single Relay

Whether a more complicated MFSM, or oscillators, the building block of the control system is the same: a relay. With the current fabrication method, lateral SOI relays can be constructed with 3 terminals with the basic structure shown in Fig. 2.6. Once the Gate node is above

Figure 2.5: Layout and a schematics of the pull up network for a pull in and pull out sensor where R is  $1M\Omega$ . Left: layout of a relay with a pull in sensor Contact and a pull out sensor PO. Top Right: the schematic for the pull in sensor. Bottom Right: A zoomed in image of what the device looks like once its been setup - not its layout. The PO node must make contact to the GND node, but cannot be fabricated connected since they also must be separate physical parts. The large Si rectangle is dragged into contact with a probe - note the difference between the left and bottom right images.

the pull in voltage of the device, the relay will pull in and connect the GND node to the Contact node.

Table 2.1: Table of the 100x change in contact resistance with changing applied voltage. The 100nm Ru-sputtered relay was designed to pull in at 30V, but pulled in at 27V.

| Applied Voltage | Contact Resistance |

|-----------------|--------------------|

| 27V (VPI)       | $33k\Omega$        |

| 100V            | $241\Omega$        |

Making a low resistance lateral SOI relay in an SOI process is straightforward, and accomplished by sputtering a conductive material after the normal SOI process. The most

Figure 2.6: Layout of a single relay. Three nodes of this device are the Gate, GND, and Contact where the voltage between the Gate and GND node determine actuation of the device.

difficult aspect is what conductive material to use. Bare Si-Si contacts have a large resistance,  $1\text{-}10\mathrm{M}\Omega$ , thus a more conductive contact material is needed. Sputtered Ruthenium, Chrome, and Titanium-nitride were used as contact materials, each with thicknesses of 30nm, 50nm, 100nm and 200nm: totaling 12 contact material variations. No appreciable change in resistance nor ability to survive hot switching was seen between these materials. The driving factor of change in contact resistance is applied voltage. Table 2.1 shows a 100x decrease in resistance by increasing the applied voltage across a relay.

The pull in voltage of this device was designed to be 30V, but was measured to be 27V. The Contact and GND nodes were grounded, while the voltage of the Gate node was increased until pull in occurred. Then, the resistance was measured between the Contact and GND nodes. This resistance was noted as the gate voltage was further increased. The purpose for shorting the Contact and GND node before opening or closing the relay, rather than measuring the contact resistance between the same nodes as the relay pulls in, is to avoid hot switching. Even minimal hot switching caused by measuring a resistance across soon-to-be contacting materials, or involving a floating node, can result in a stuck closure. Fig. 2.7 shows a relay that was closed but the Contact node was left floating. However, this was an extreme example and often relays get stuck closed without any visual change to the film.

Figure 2.7: 100nm of sputtered Ru film underwent a visual change when the Contact node was left floating upon pull in. Left: the relay just before pull. Right: Just after pull in.

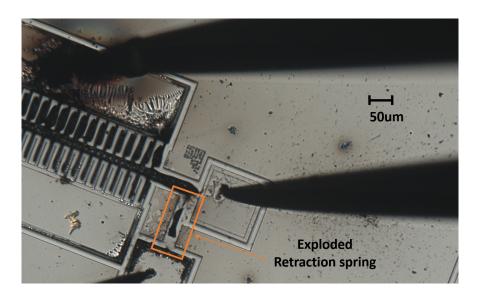

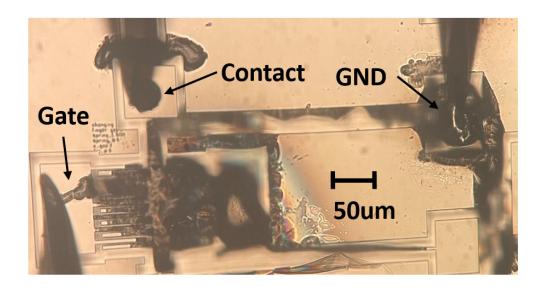

#### High Voltage Experiments: 30V-100V

To show that these relays can be used to run inchworm motors, they were hot switched from 30-100V. The first test setup was identical to the one described above, except the contact Node was instead fixed at 100V instead of shorting to ground with the GND node. Thus, the Contact node was 100V, GND was grounded and Gate was increased from 0V to 100V with a step function. Fig. 2.9 shows the result where the retraction spring was blown away. This relay had the same Gate voltage vs. resistance that was shown in Table 2.1 When the relay pulled in, 100V was across the  $241\Omega$  contact resistance: over 400mA of current caused a loud popping noise and the retraction spring to vaporize. Thus, a current limiting resistor was included for the subsequent tests.

High current upon closure was thought to be the cause so a  $1M\Omega$  current limiting resistor was included as shown in Fig. 2.8. While open, the Contact node was VDD, GND was grounded and Gate stepped up from 0V to 30v. Again there was a popping sound and obvious destruction shown in Figures 2.10 and 2.11 with 100nm and 30nm of sputtered Ru respectively. These relays also had a similar 27V VPI and Gate voltage vs. resistance, so the current causing this was 30uA. No appreciable change was seen in material thickness nor element. For these explosive experiments, the three probes were even difficult to remove from the pads due to the redeposition of the contact material, which splattering over a hundred microns away.

## 2.4 Conclusions for Eliminating SCuM and Zappy

This work was unable to experimentally show the ability to eliminate SCuM nor Zappy. To replace Zappy, on-chip solar cells and low resistance 30V hot-switchable relays must be constructed, in addition to a power source. The solar cells process was never able to be properly run: fabrication errors prevented the testing of initial test structures.

Figure 2.8: The circuit schematic of the hot switch test setup. VDD was 30V for Figures 2.10 and 2.11 and but R was constant at  $1M\Omega$ .

Figure 2.9: A relay sputtered with 30nm of Ru that underwent a violent change when hot switched at 100V with no current limiting resistor. The top probe was the Gate, left probe was GND, and the right was Contact.

Figure 2.10: Relay sputtered with 100nm of Ru when hot switched at 30V with a  $1M\Omega$  resistor. The top probe was Contact, left probe was Gate, and the right was GND.

Figure 2.11: A relay sputtered with 30nm of Ru that underwent a violent change when hot switched at 30V, even with a  $1M\Omega$  resistor.

24

Zappy's high voltage buffers could also not be replaced with SOI relays due to lack of hot-switching capability. Si-Si relays can be hot switched over 100V, but their resistance is  $1\text{-}10\text{M}\Omega$ ; relays with resistances less than  $30k\Omega$  were unable to be hot switched above 5V. Low voltage (under 5V) lateral SOI relays can be fabricated and hot switched, however, inchworm motors force is proportional to the square of the applied voltage such that 30V is the minimum voltage to achieve a useful force for tactile applications. Twelve contact material variations were tried (three different materials each with different 4 thicknesses) but no change in hot switching capability was observed. In addition the the contact resistance depended on the force between contacts more than the thickness or material of the sputtered contact. This contact resistance did decrease from  $1\text{M}\Omega\text{-}10\text{M}\Omega$  for the Si-Si contacts to  $241\Omega\text{-}33k\Omega$  for sputtered contacts, depending on the applied voltage. Further investigation into a conductive, hard and non-sticky contact material is required for these relays to be implemented in an system controlling inchworm motors.

To replace SCuM, a method of generating the offset square waves must be constructed. A complex design where the opening/closing of actuator A causes the opening/closing of actuator B that mimics the state diagram of 2.1 was attempted but never shown to work, even at low voltages where the relays could survive hot switching for limited cycles. Instead, a simpler solution is to create the square waves from relay oscillators. However, this was not shown experimentally. The best method found to create a wireless tactile wearable is to incorporate SCuM and Zappy into a MEMS-CB outlined in chapter 1.

# Chapter 3

## **Taction Devices**

The proof of concept design, V1, suffered from failure due to contamination, but proved that a 40um thick, 250um wide piece of Si could be felt by a human when pushed into contact with skin with 1mN of force. This V1 device is shown in Fig. 3.1 next to a finger, and it's layout is compared with an updated High Force version in Fig. 3.3. The High Force version addresses the contamination issue with post processing and layout changes, in addition it can provide 15x the force.

Figure 3.1: An image of the V1 taction device next to a finger provided by the Paulos group.

Figure 3.2: A SEM image of the V1 taction device's end effector. This is the Si that makes contact with human skin.

## 3.1 Preventing Contamination

The main failure mode of V1 was condensation from human skin which caused the retraction springs of the device to stick: making the device inoperable. Partial encapsulation and layout redesign were explored to mitigate that failure.

Fig. 3.4 shows moisture and oils from human skin condensing onto the Si surface. These particles can cause failure of movable structures that they come into contact with. The

Figure 3.3: Left: V1 with 2 sets of retractions springs - one near the probe pads and the other close to the end effector highlighted in blue boxes. Right: The High Force redesign has only one set of retraction spring that are on the opposite end of the device from the end effector.

end-effector is the exception. Though it is 40um thick Si with a 2um gap to the substrate below, it did not get stuck due to repeated exposure to moisture by contact a finger. The failure mode was when the moisture reached the retraction springs or GCA of the inchworm motor. Those are the two types of features that need protection.

Figure 3.4: Left: a tactile device with no contamination (human skin) nearby. Right: a finger is placed at the bottom edge of the chip which causes particles to condense on the Si.

## Partial Encapsulation

The MEMS tactile device is designed to physically contact the human skin and is thus exposed to the moisture and oils of the human skin. Thus, it cannot be hermetically sealed as many MEMS devices are. It can however be partially encapsulated. Either on a wafer scale by wafer bonding, or on a chip-scale by adding a cover by hand post process.

Both methods are an effective way to protect the devices from moisture, and physical destruction. Additional process steps were explored where Au-Au thermocompression bonding a glass wafer with Au traces to the MEMS wafer was completed. In addition to providing

protection, this approach provides a second routing layer: simplifying traces and decreasing the need for costly post-process wirebonding.

#### Wafer Bonding Glass to the SOI Wafer

Three challenges were overcome to successful produce partially encapsulated chips from a wafer-bonded stack. The Au delaminated which decreased bond integrity, the wafer stack cracked after bond, and individual devices were difficult to remove from the wafer. These challenges were solved by adding a lift off resist, using a different glass wafer, and changing the dicing procedure respectively.

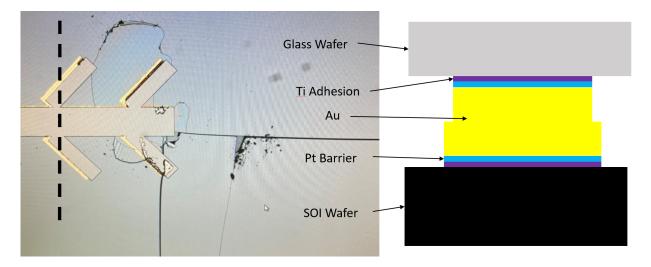

The first issue was the Au stack itself. The stack is 50nm Ti, 50nm of Pt, and 1um of Au; the Titanium acts as an adhesion layer, while the Platinum acts as a barrier layer, and the Gold layer allows the bond. The tool manual, shown in Appendix A, recommends a Au layer 0.5-1um thick and notes that thinner films drastically decrease in bond strength. All three films in the metal stack are critical for a successful thermocompression bond. The Ti layer is visible in Fig 3.5 because the bottom is the metal stack is seen through the quartz wafer. Also in this image, the Au on the SOI wafer is seen. This is due to misalignment. Bonding was done on an AML AWB-08-30 wafer bonder; 8um of misalignment was achieved, but less than 2um has been achieved by other tool users.

Figure 3.5: A zoomed in image of the bonded stack cracking and misalignment. On the image to the left, the gray is the Titanium (the bottom of the Au stack) shown though the quartz wafer and the yellow is the gold.

Thermocompression bonding is much less sensitive to defects as other types of bonds: the bonding surfaces do not need to be as clean and flat as fusion bonding. However, folds of

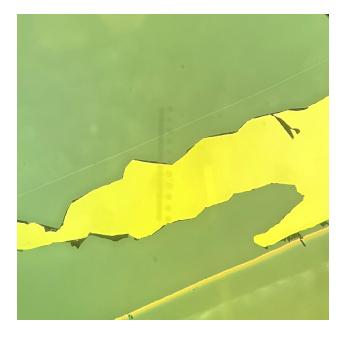

Figure 3.6: Au stack peeling after liftoff. The black strips are peeled back folds of the metal stack and the green is the glass wafer.

delaminated Au shown in Fig 3.6 are large enough to cause the thermocompression bond to fail. In this figure, the gold is supposed to be a solid strip, but much of the gold peeled back in the liftoff process and the black are folds of metal left behind when it ripped off. This delamination was caused by the Au on the Si being ripped up during the liftoff process. A thinner Au layer (which limits bond strength and success) or utilizing liftoff resist eliminates the issue. This is because less Au is deposited on the sidewalls of the photoresist (PR), so when the PR is removed, it does not peel back the Au designed to be left behind on the Si.

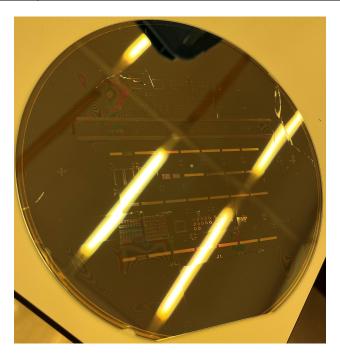

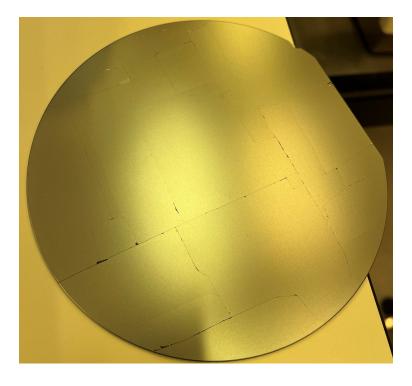

The next issue with thermocompression bonding was caused by thermal mismatch. The SOI wafer was bonded to a quartz wafer, but as the bonded pair cooled, the stack cracked and ripped itself apart shown in 3.5, Fig. 3.7, and 3.8. The bond took place at 300°C, thus as the stack cooled to room temperature, the stressed caused by the TCE differential between Si and Quartz caused the wafers to crack. This issue was fixed by using a borofloat wafer instead of quartz. This solved the issue because the borofloat's temperature coefficient of thermal expansion is matched to Si, while quartz's is roughly 6x highlighted in Table 3.1. Once this change was made, a SOI and Borofloat wafer, each with 1um thick Au traces, were successfully bonded with the given parameters in Table 3.2.

The final challenge to wafer bonding was how to get chips out of the wafer stack. Traditionally, the backside DRIE etch singulates the wafer, however, plasma dicing was not possible because of the bonded borofloat wafer; the SOI wafer was extremely fragile after the substrate DRIE and the glass wafer was not able to be controllably etched without

Table 3.1: Table of Si, Quartz and Borofloat TCE [1] [13] [11]

| Material  | Temperature Coefficient of Thermal Expansion |

|-----------|----------------------------------------------|

| Si        | $2.6 - 3.3uK^{-1}$                           |

| Quartz    | $0.5 \ uK^{-1}$                              |

| Borofloat | $3.25uK^{-1}$                                |

Figure 3.7: The quartz wafer cracking after the bonded stack cools.

Table 3.2: Manual Recommended Values Compared to Those of a Successfully Bonded Stack

| Parameter     | Manual Recommendation | Experimental Value Used |  |

|---------------|-----------------------|-------------------------|--|

| Temperature   | $300 - 320^{\circ}C$  | 300 °C                  |  |

| Bond Pressure | 1-7MPa                | 6.5MPa                  |  |

| Bond Time     | 2-15 minutes          | 15 minutes              |  |

breaking the SOI wafer. Therefore, the stack was diced. The whole stack could be diced into chips, but the pads were still inaccessible. A break in the SOI and Au trace is purposefully left such that the end effector can protrude from the stack, note the end effector in 3.4. However, a second opening is needed to contact the pads to control the device. Through glass vias (TGVs) could eliminate the need for the second opening, such that the entire structure is hermetically sealed except for the opening smaller that 300umx2um that the end-effector

Figure 3.8: The SOI substrate cracking as the bonded stack cools.

protrudes from. However, a much simpler solution is to partially dice the glass wafer after fully dicing the bonded stack into chips shown in Fig. 3.9. The partial dice, 200um deep, creates a stress concentration that is controllably broken with tweezers: providing a simple post-processing method to access the pads.

Initially, stress concentrations were made in the glass wafer and then the full-stack dices were made to singulate chips. However, the force of the full-stack dices caused the partially diced glass to break apart prematurely and the water jet of the dicing saw ruined all devices. Thus, the full-stack dicing must be done prior to the partial dices.

#### Post Process Bonding Glass to an SOI Chip

The easiest solution to protect the MEMS device from physical and moisture failures is to attach a cover to each chip individually, rather than singulated a bonded wafer stack into chips. For example, run a typical SOI process with one added post processing step; frontside DRIE, backside DRIE, and HF release with an optional metallization step 1.2. Then, manually apply epoxy to a chip-sized piece of glass slide, and fix it to the SOI chip covering the fine features, while leaving the probe pads exposed. In addition, instead of using a glass slide, a micromachined SOI chip made in the same process could be bonded [16]. This is simpler than wafer bonding, because it is one extra step, and require no changes

Figure 3.9: Process flow showing how to create 2 chips and expose pads through a full and partial dice where grey is glass wafer and SiO2, yellow is Au, and green is Si.

to the fabrication process. However, it is not a wafer-scale solution. This can also provide an extra routing layer but requires larger bond pads because this alignment is dependent on the skill of the user: less than 100um is achievable with the current micromanipulator.

## Changing Layout To Solve Contamination Failures

The simplest and most effective method to decrease failure due to contamination, without post processing nor changing the fabrication process, is to simply design for sufficient space between the fine movable components (springs and GCAs) and human skin.

Repeated exposure to human skin increases the distance that they moisture condenses, but after repeated trials they were never seen condensing more than 1mm from the skin that they originated from. The V1 design failed because 2 of the 4 retractions springs were placed less than 1mm from the edge of the chip. Redesigning such that there was more than 1mm was the easiest solution to solving the failure mode caused by moisture shown in the layout comparison of Fig. 3.3.

### 3.2 Conclusion for a Robust Tactile Stimulator

Ensuring a 1mm space is between the fine features of the device (retraction springs and GCAs) is the easiest way to prevent condensation failure. This was first fixed by removing

Figure 3.10: An 3D rendering from [16] showing simplified illustrations of the inchworm motor running after an SOI cap was bonded. The cover is bonded on top with dots of silver epoxy and the (purple) inchworm motor shuttle is still able to move after the bond.

the second pair of retraction springs from the V1 design that were closest to the end effector. However, fixing a cover to act as a physical and moisture barrier also protects against condensation. For small batches, this is best done by post processing single chips, but can be also accomplished by wafer bonding for higher volume manufacturing. Post process fixing a lid can be any material because the epoxy bonding is done at room temperature, but due to the elevated temperature in thermocompression bonding, a Si-matched TCE cover material must used for the wafer-scale solution. In addition, either chip or wafer scale bonding can provide an additional routing layer. This simplifies the wearable assembly by removing the need for jumpers between planar traces.

The main failure mode of the V1 device was contamination, which is mitigated by increasing the spacing around the edge of the chip in conjunction with a lid covering the MEMS components. This change in layout and process allowed for the tactile devices to be repeatedly used without failing due to condensation.

# Chapter 4

## Lessons Learned and Future Work

## 4.1 Integration

The keys to improving integration are connection and alignment. The current method is very labor intensive and difficult. It is possible to properly align an IC to the MEMS-CB, but is very difficult. In order to make it easier, and increase the yield, epoxy type and deposition method should be investigated along with a finer alignment tool and higher magnification microscope.

### Connection Resistance and Reliability

#### Change the SOI Wafer

The easiest way to decrease resistance of connections is to use a lower resistivity SOI wafer. Experiments showed that with sufficient epoxy, the resistance from MEMS-CB SOI beam to IC pad was dominated by the resistance of the SOI beam. For example, if using an SOI wafer with a device layer doping of 1e18 instead of 1e15, the connection resistance would be lowered to tens of Ohms, compared to thousands of Ohms, which would be suitable for this application.

#### Using Different Epoxies

In addition, different epoxies can be tested. Only 3 were tried and all had particle sizes in the same order of magnitude as the droplets: even highly conductive epoxies may not have many conductive particles in the applied droplet, due to the small amount of epoxy used. For example, if an epoxy particle size is 30um, but the epoxy droplet is 40um in diameter, it may still be a highly resistive connection. Therefore, nanoparticle epoxies should be explored. Other epoxies should also be considered on their viscosity. The alignment will become easier if the epoxies spread less when the IC and MEMS-CB come into contact, making sure that connections are only made where the alignment step dictates. This was a

major difficult in assembly as even when properly aligned, adjacent traces were shorting due to epoxy spreading.

#### Alignment

The alignment can also be aided by including a fixture to the assembly setup. Making a structure where the alignment is not done by hand, but rather guided by a fixture would increase accuracy, speed and ease of assembly. Though it can be done by hand with the current micromanipulator, a finer micromanipulator, especially with a fixture to hold the two IC chips in place, would greatly increase the success of alignment. In addition a high magnification microscope would also increase the likely hood of successful assembly.

#### 4.2 Simulation

The MEMS designs are based off of theoretical equations and working devices were found by making arrays of prototypes with varying parameters. Though this leads to a faster design cycle, it often takes more time due to dealing with unforeseen problems that could have been avoided through simulation, like the unaccounted moments shown in Fig. 4.1.

### Wafer Weighing Simulation