# Analog Generators for SerDes Clock Generation and Distribution

Zhongkai Wang Elad Alon

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2023-36 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2023/EECS-2023-36.html

May 1, 2023

Copyright © 2023, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Analog Generators for SerDes Clock Generation and Distribution

by

#### Zhongkai Wang

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Elad Alon, Chair Professor Vladimir Stojanovic Professor Liwei Lin

Fall 2021

### Analog Generators for SerDes Clock Generation and Distribution

Copyright 2021 by Zhongkai Wang

#### Abstract

Analog Generators for SerDes Clock Generation and Distribution

by

#### Zhongkai Wang

Doctor of Philosophy in Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Elad Alon, Chair

The ever-increasing demand for ultra-high-speed interconnects has driven the development of wireline transceivers operating at > 100Gbps per lane. As a major contribution of data random jitter, clock-dependent distortion of transmitters and receivers, the clock generation and distribution circuits in SerDes becomes increasingly complex and time-consuming with stringent specifications, especially considering the fast development of technology nodes of the FinFET processes. This thesis focuses on the design of energy-efficient clock generation and distribution network with generator-based design methodology using Berkeley Analog Generator, which speeds up the design procedure, while satisfying the performance requirements.

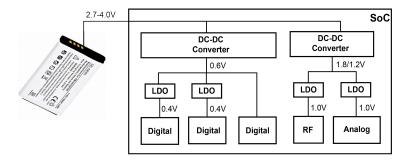

A bang-bang phase-locked loop generator for 28/32Gbps SerDes that encapsulates this design methodologies for its circuit blocks and the complete PLL system is first reported. The generator is fully automated and parameterized, producing the layout and schematic based on process characterization and top-level specifications. Three 14GHz PLLs are instantiated in TSMC 16nm, GF 14nm and Intel 22nm technologies, demonstrating the process portability. The rapid generation time of less than four days enables fast PLL design and technology porting. The PLL design fabricated in TSMC 16nm shows RMS jitter of 565.4fs and power of 6.64mW from a 0.9V supply.

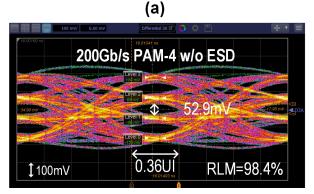

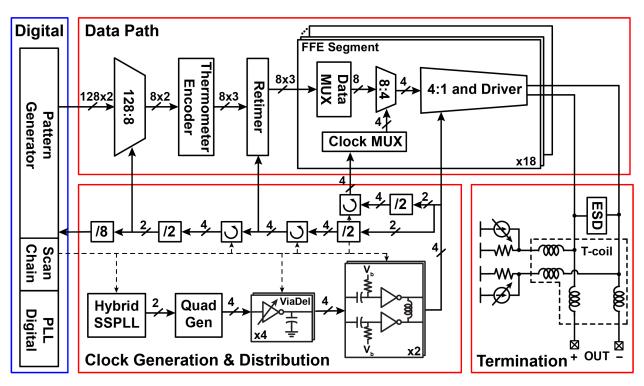

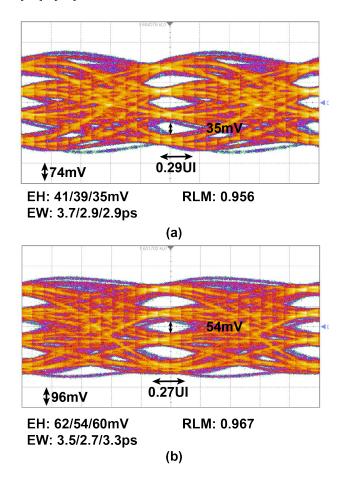

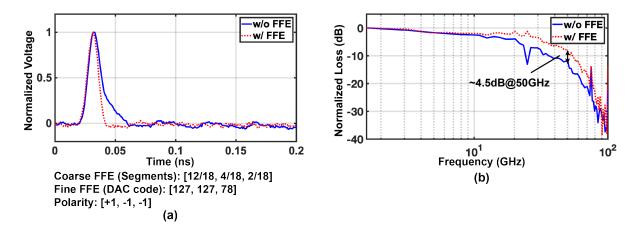

Furthermore, a flexible clock distribution network for a 200Gbps pulse amplitude modulation four-level transmitter is designed using the layout generators in 28nm CMOS technology. The proposed TX achieves an eye opening with > 52.9mV eye height, 0.36UI eye width, 98% RLM and 4.63pJ/b at 200Gbps PAM-4 signaling under > 6dB channel loss at 50GHz, demonstrating the highest data rate achieved using a planar process.

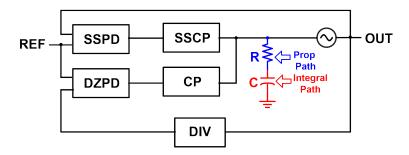

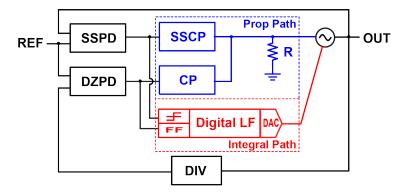

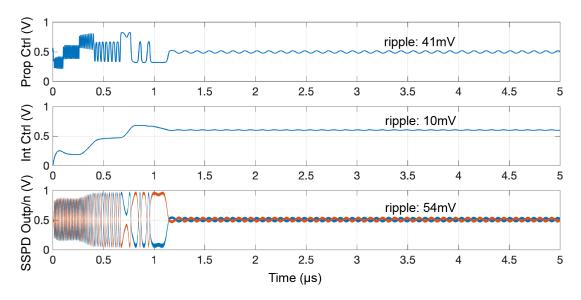

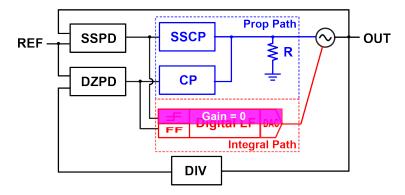

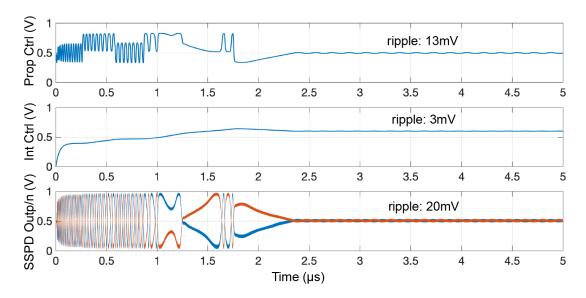

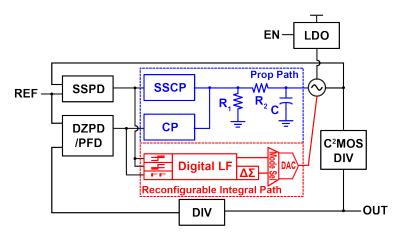

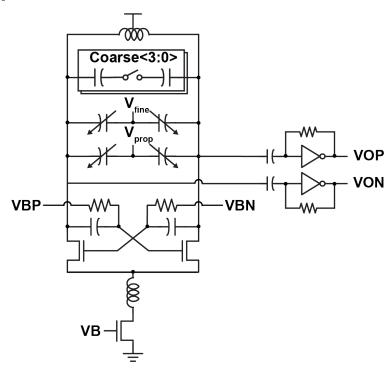

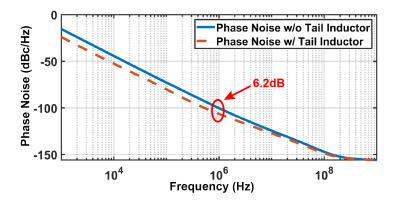

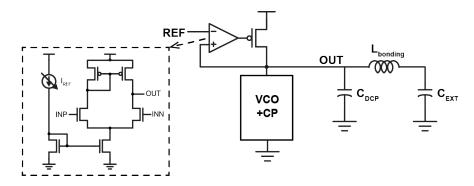

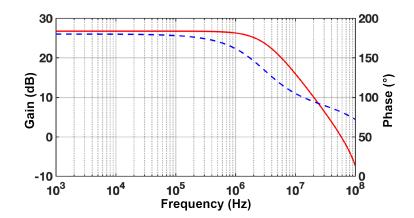

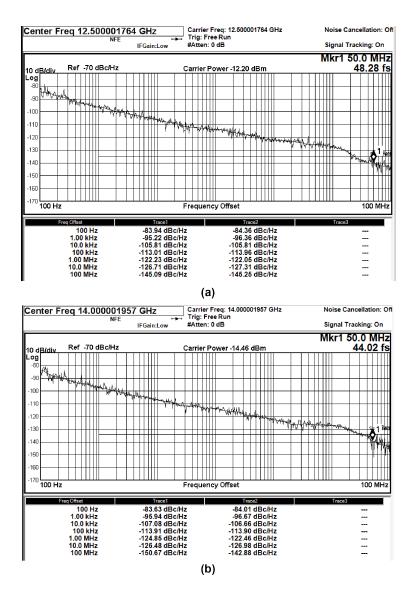

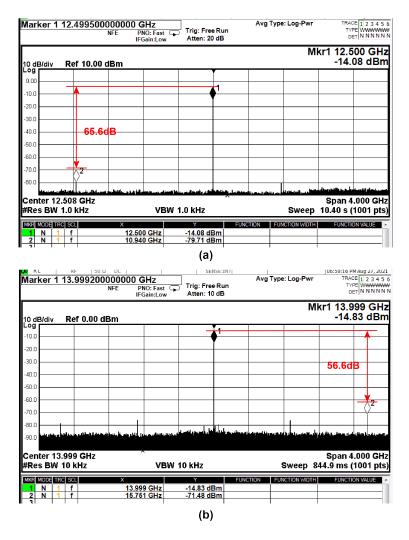

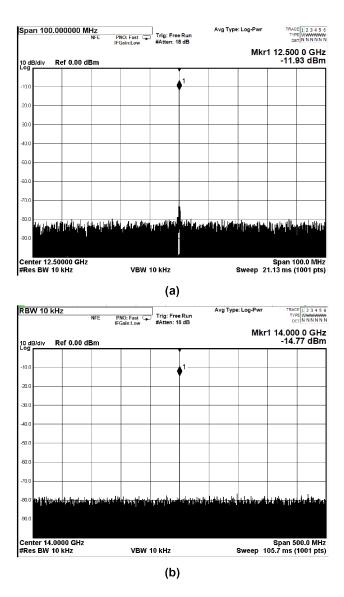

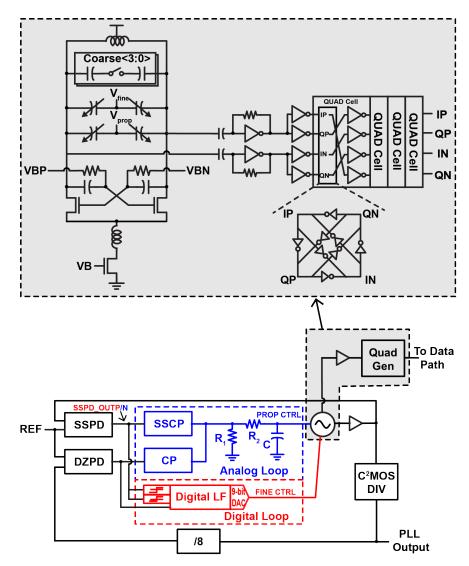

To complete the whole TX design, a layout generator for sub-100fs sub-sampling PLL is proposed. With a type-I loop and tri-state integral path, the voltage ripples of the hybrid

loop is eliminated and the PLL reaches a RMS jitter of 44fs at 28GHz output, a spur of -56.6dB, which results in the FOM value -254.8dB. Finally, the PLL is merged with the transmitter data path, achieving 4.69 pJ/bit efficiency, 54mV eye height, 0.27UI eye width, and 97% RLM under 6dB channel loss at 50GHz, showing the capability of the generator-based design methodology.

To Yajuan and my family

## Contents

| $\mathbf{C}_{\mathbf{c}}$ | ontei                                                | nts                                                                                                                                                                                                      | ii                                     |

|---------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Li                        | st of                                                | Figures                                                                                                                                                                                                  | iv                                     |

| Li                        | st of                                                | Tables                                                                                                                                                                                                   | viii                                   |

| 1                         | Inti<br>1.1<br>1.2                                   | Motivation                                                                                                                                                                                               | 1<br>1<br>4                            |

| 2                         | An<br>2.1<br>2.2<br>2.3<br>2.4                       | Automated and Process-Portable Generator for Phase-Locked Loops Background                                                                                                                               | 6<br>8<br>25<br>28                     |

| 3                         | Clo<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5               | ck Distribution for 200Gb/s PAM-4 SerDes TX  200Gb/s TX architecture and Clock Distribution Requirements  Implementation of Clock Distribution Network  Circuit Generation  Measurement Results  Summary | 30<br>32<br>35<br>38<br>40             |

| 4                         | Sub<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | PLL Design for 200Gb/s PAM-4 SerDes Transmitter PLL Specification for High-Speed SerDes TX                                                                                                               | 44<br>45<br>48<br>51<br>54<br>67<br>70 |

| 5                         | Sub                                                  | o-100fs Sub-Sampling PLL Measurement Results                                                                                                                                                             | 71                                     |

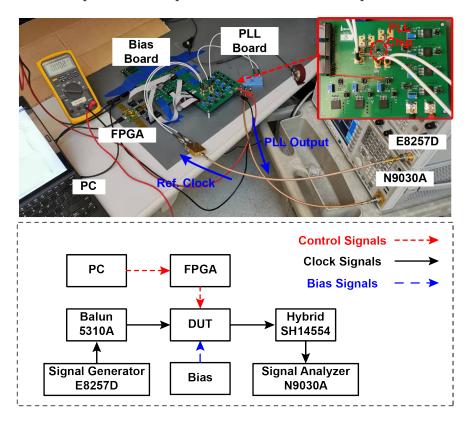

|              | 5.1   | Testbench Setup                                                            | 71  |

|--------------|-------|----------------------------------------------------------------------------|-----|

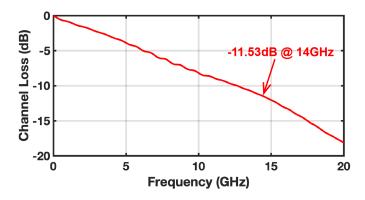

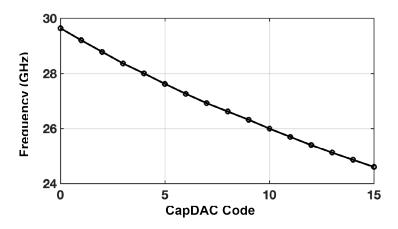

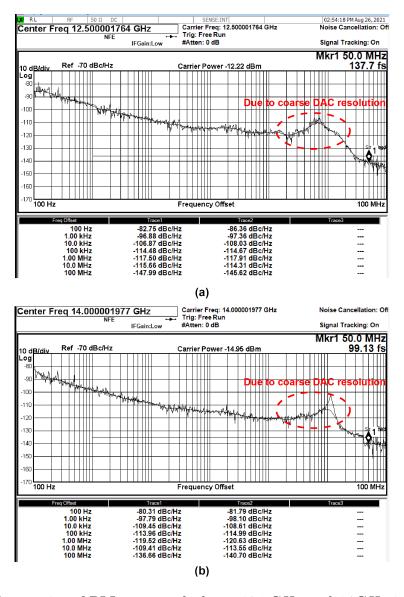

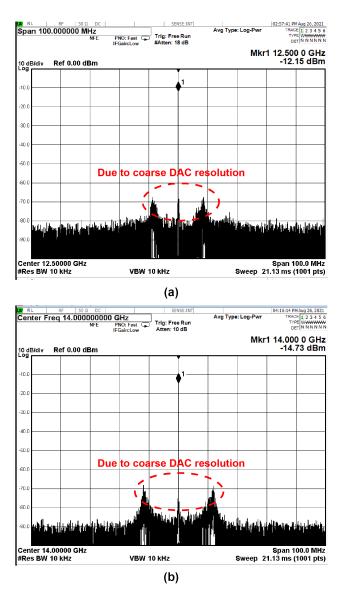

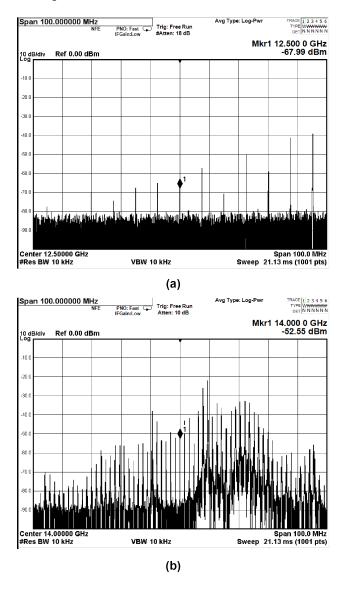

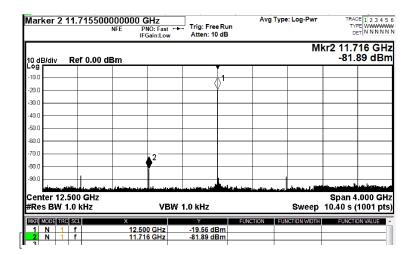

|              | 5.2   | VCO Measurement Results                                                    | 72  |

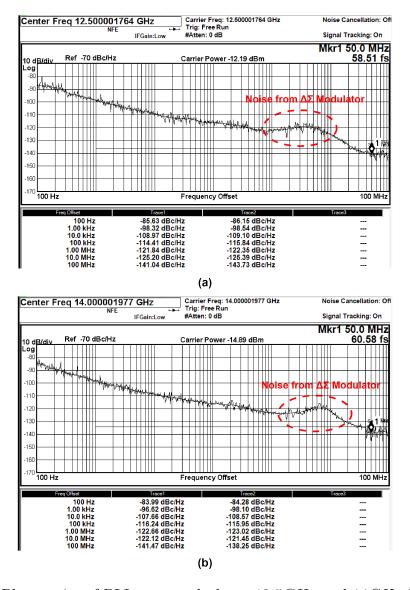

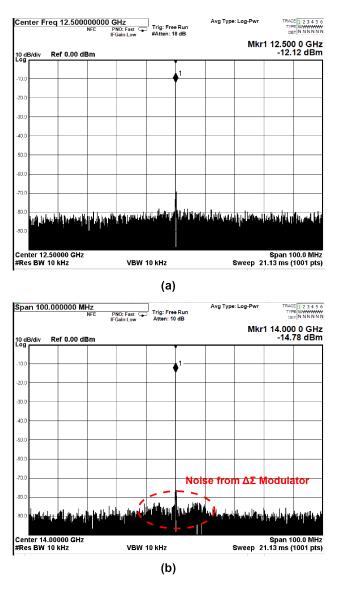

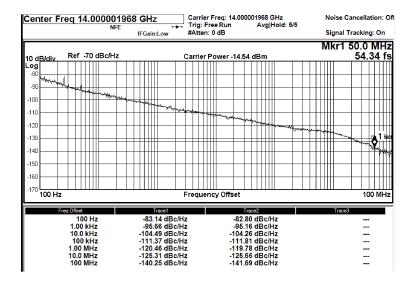

|              | 5.3   | PLL Measurement Results                                                    | 74  |

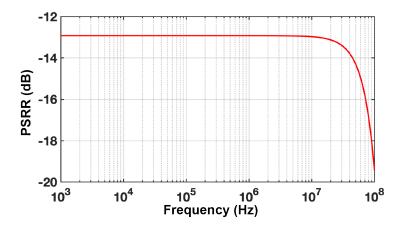

|              | 5.4   | LDO effects on Phase Noise                                                 | 83  |

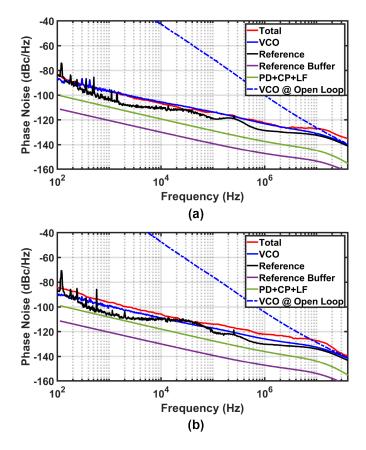

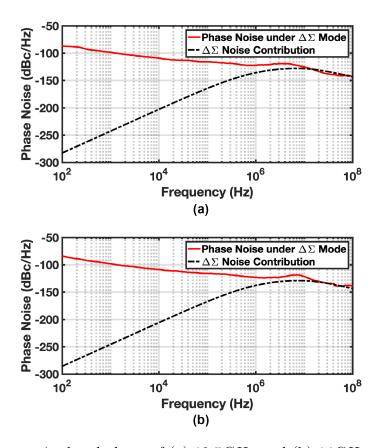

|              | 5.5   | Phase Noise Breakdown                                                      | 84  |

|              | 5.6   | Summary and Comparison Table                                               | 84  |

| 6            | 200   | Gbps PAM-4 Transmitter with Hybrid Sub-Sampling PLL                        | 88  |

|              | 6.1   | Structure and Clock Design Considerations of the 200Gb/s PAM-4 Transmitter | 88  |

|              | 6.2   | Layout and Testbench Setup                                                 | 91  |

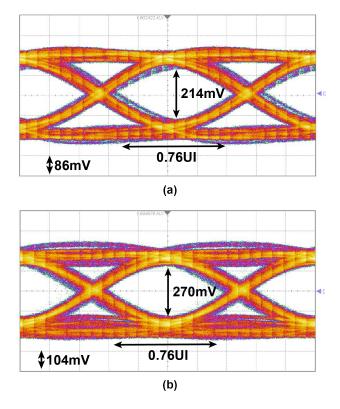

|              | 6.3   | Measurement Results                                                        | 92  |

|              | 6.4   | Summary and Comparison Table                                               | 98  |

| 7            | Cor   | nclusions                                                                  | 100 |

|              | 7.1   | Thesis Summary                                                             | 100 |

|              | 7.2   | Future Directions                                                          | 101 |

| Bi           | bliog | graphy                                                                     | 102 |

| $\mathbf{A}$ | VC    | O Frequency Optimization                                                   | 108 |

## List of Figures

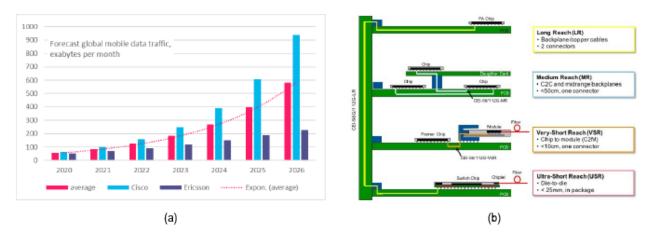

| 1.1  | (a) Comparison of global mobile data traffic forecasts [1] and (b) different forms                                                                                   | 1        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2  | of serial interfaces in data centers [2]                                                                                                                             | 1        |

| 1.2  | (a) I/O bandwidth (data rate per lane) and actual bandwidth (data rate of link) of<br>the PCIe standard versus year [3] and (b) a summary forecast from the Ethernet |          |

|      | Bandwidth Assessment [4]                                                                                                                                             | 2        |

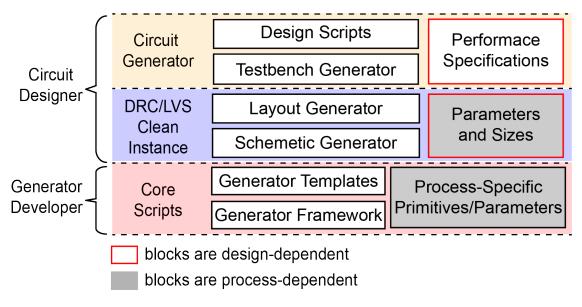

| 1.3  | The hierarchy of Berkeley Analog Generator                                                                                                                           | 4        |

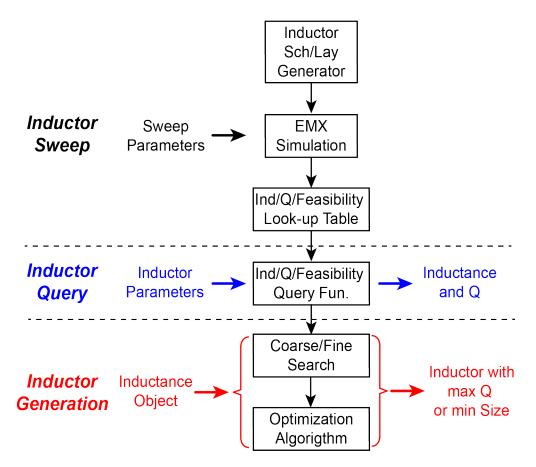

| 2.1  | Analog circuit generation flow using BAG                                                                                                                             | 7        |

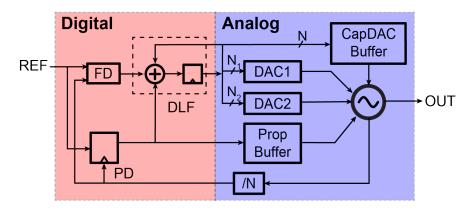

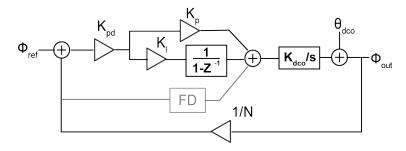

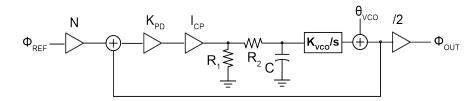

| 2.2  | Bang-bang PLL architecture                                                                                                                                           | 8        |

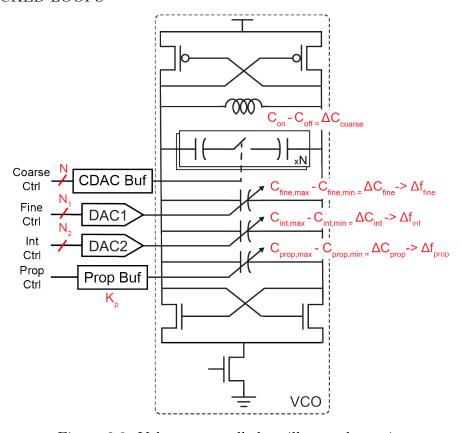

| 2.3  | Voltage-controlled oscillator schematic                                                                                                                              | 9        |

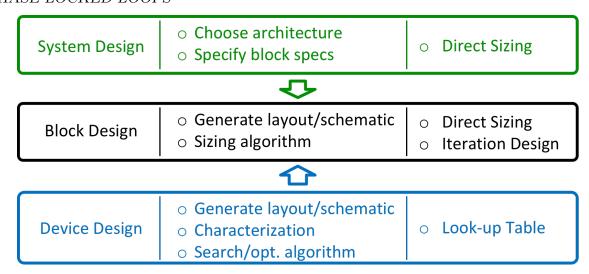

| 2.4  | Three types of design methodologies for different levels of the PLL                                                                                                  | 9        |

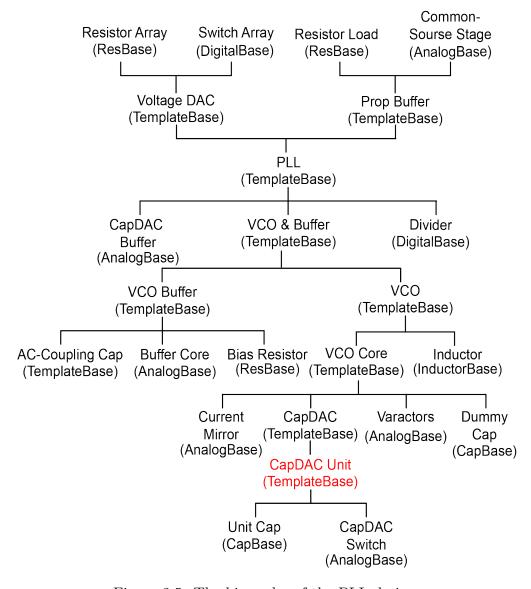

| 2.5  | The hierarchy of the PLL design                                                                                                                                      | 10       |

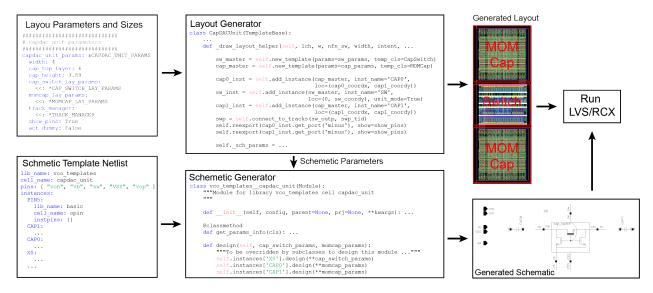

| 2.6  | Schematic and layout generation flow example with the analog generator                                                                                               | 11       |

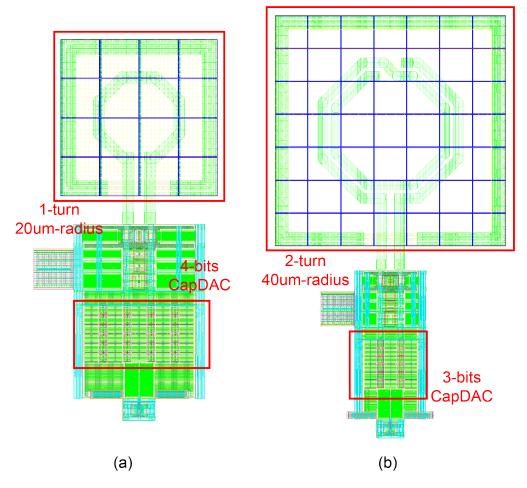

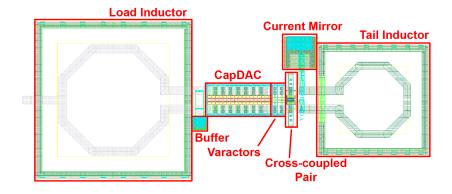

| 2.7  | VCO layout with (a) 4-bit CapDAC, 1-turn inductor with radius of $20\mu m$ and                                                                                       |          |

|      | (b) 3-bit CapDAC, 2-turn inductor with radius of $40\mu m$                                                                                                           | 12       |

| 2.8  | PLL model                                                                                                                                                            | 12       |

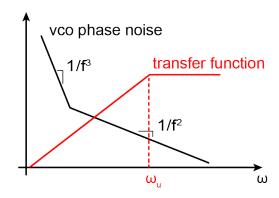

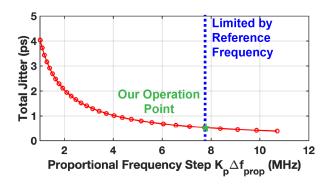

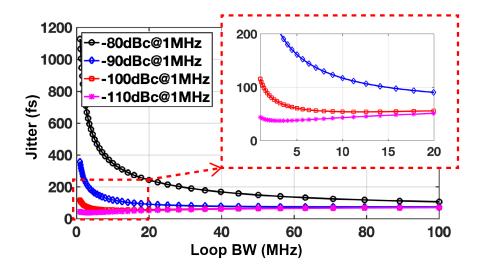

| 2.9  | VCO phase noise and its transfer function of the BBPLL                                                                                                               | 14       |

| 2.10 | Phase noise optimization of the BBPLL in this design                                                                                                                 | 14       |

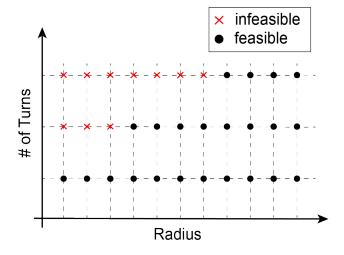

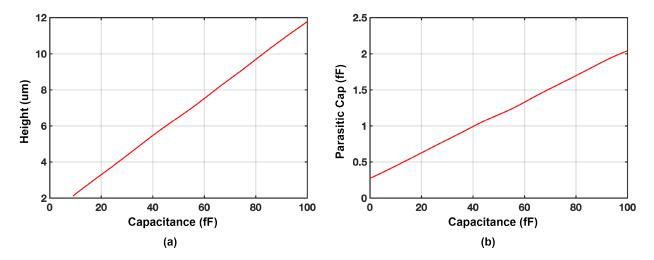

|      | Inductor feasibility check example (for given width and space)                                                                                                       | 16       |

| 2.12 | 9                                                                                                                                                                    | 16       |

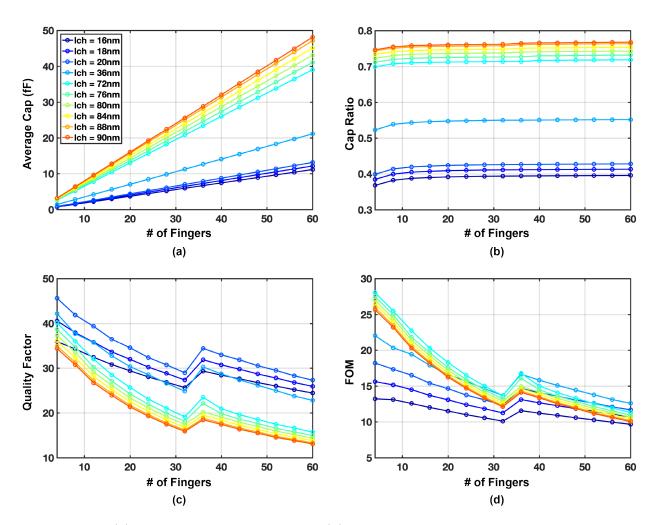

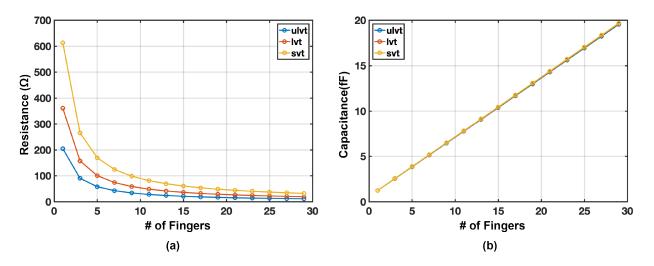

| 2.13 | 0 0 / ( ) 1                                                                                                                                                          |          |

|      | average capacitance, (c) Q and (d) FOM versus different number of fingers and                                                                                        | 1.0      |

| 0.14 | channel lengths for ulvt varactors                                                                                                                                   | 18       |

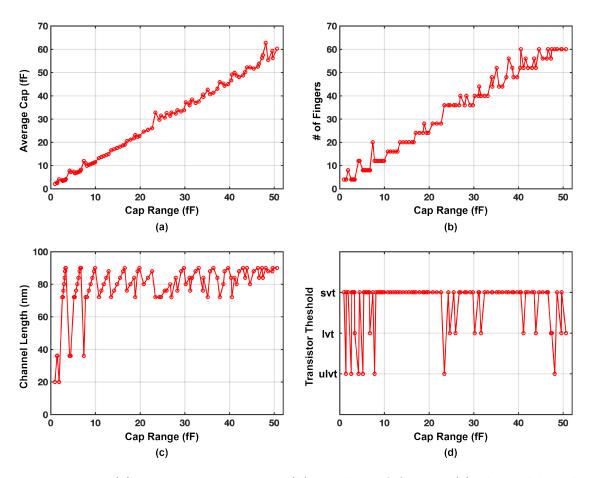

| 2.14 |                                                                                                                                                                      | 10       |

| 0.15 | sistor threshold versus capacitance tuning range of optimal varactors                                                                                                | 19       |

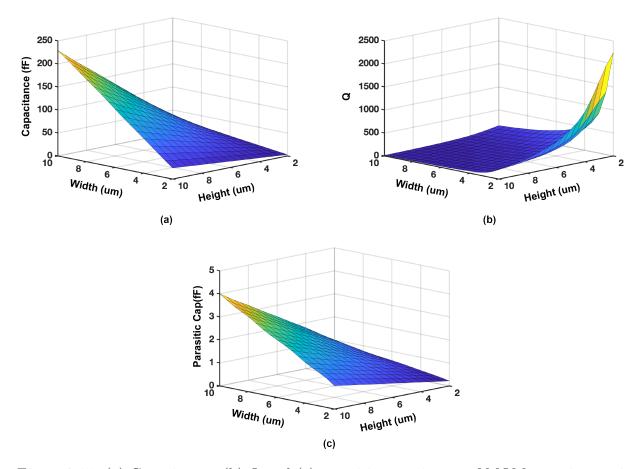

| 2.15 |                                                                                                                                                                      | 00       |

| 2 16 | M5 and M6 with different width and height                                                                                                                            | 20       |

| 2.16 | ( ) ( ) [                                                                                                                                                            | า1       |

| 2 17 | capacitors using M5 and M6 with different capacitances                                                                                                               | 21       |

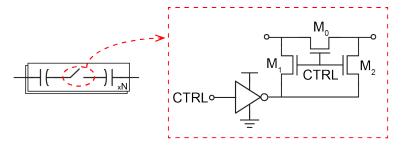

|      | Capacitance switch circuit diagram                                                                                                                                   | 22<br>22 |

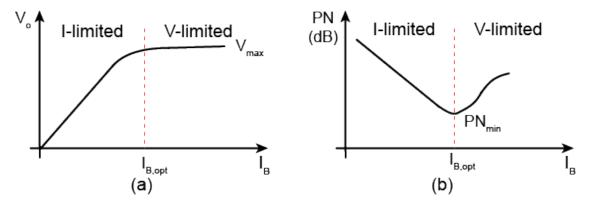

|      | VCO (a) output amplitude and (b) phase noise versus bias current                                                                                                     | 23       |

| 4.10 |                                                                                                                                                                      | 40       |

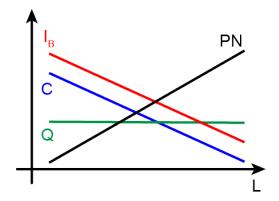

| 2.20 | VCO Bias current, tank capacitance, Q and phase noise versus tank inductance,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | for the same frequency range and resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.21 | VCO tank model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

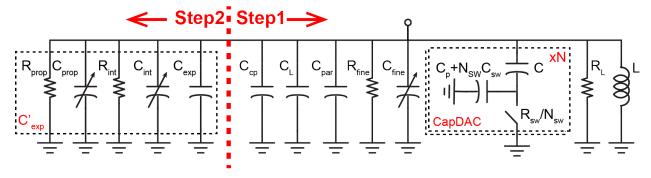

|      | Automatic VCO design flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

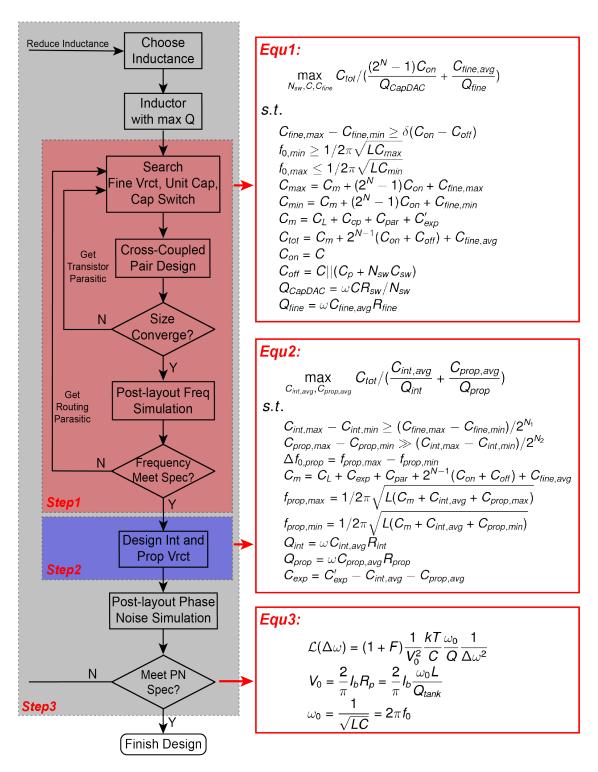

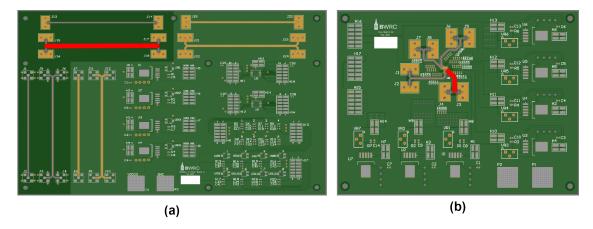

|      | Generated PLL layouts at (a) GF 14nm and (b) Intel 22nm technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

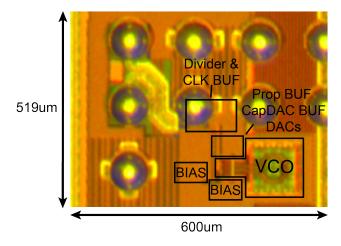

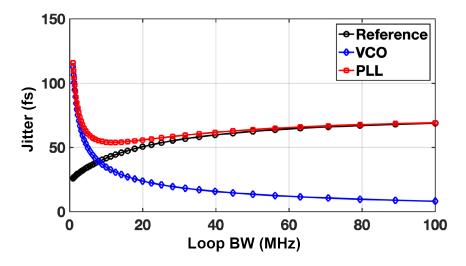

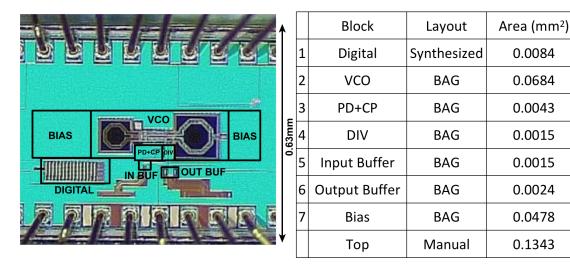

|      | Chip micrograph of the PLL in TSMC 16nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

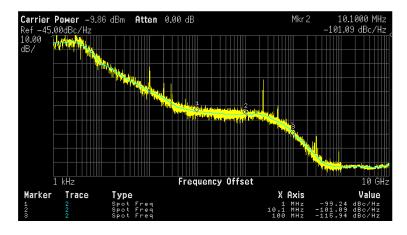

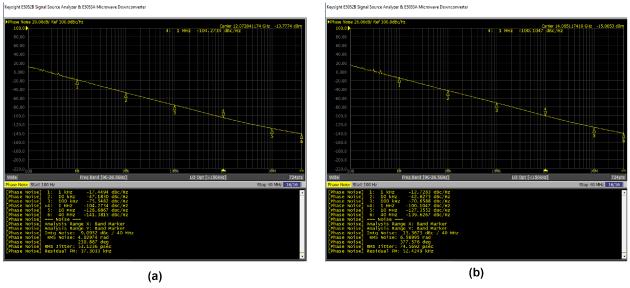

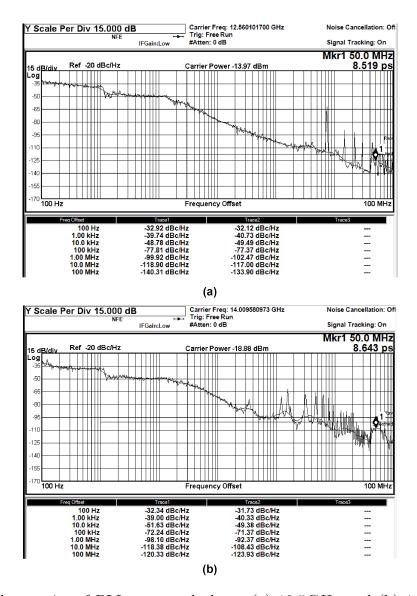

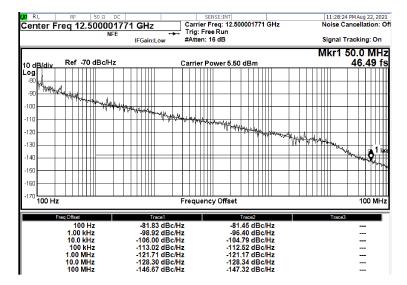

|      | Measured PLL phase noise at 14GHz in TSMC 16nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

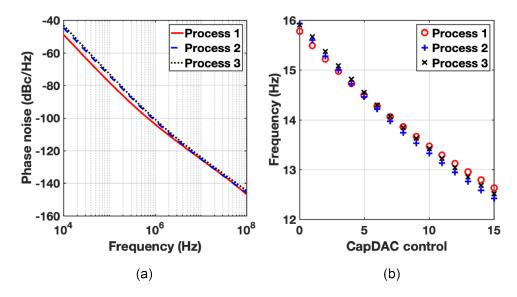

|      | Simulated VCO performance in three different technologies: (a) Phase noise and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | (b) frequency range with CapDAC control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | (a) requested range with eaptive contract to the terms of the contract to the |

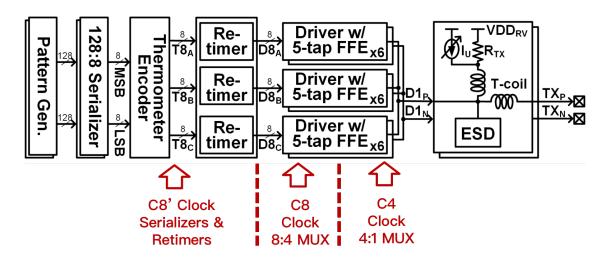

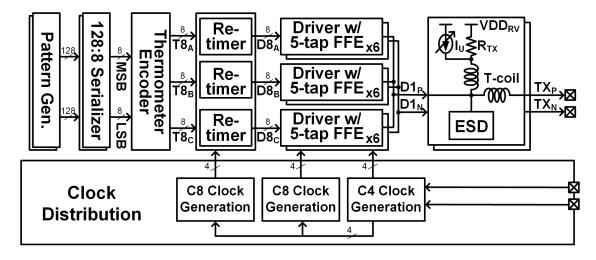

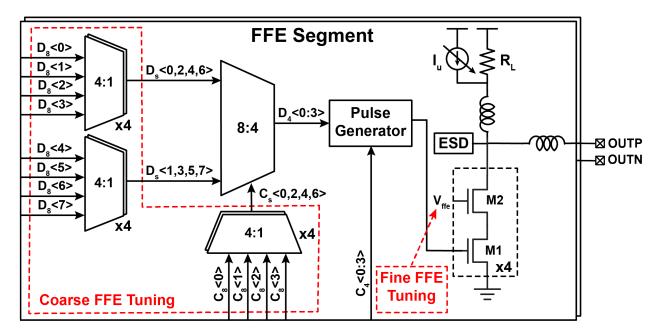

| 3.1  | TX data path diagram and its requirements for clock distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

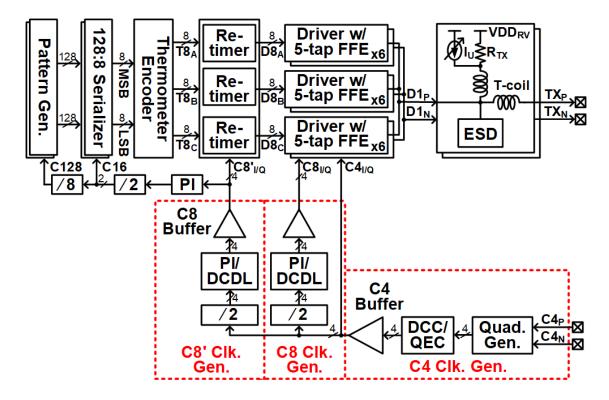

| 3.2  | TX data path diagram and its requirements for clock distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

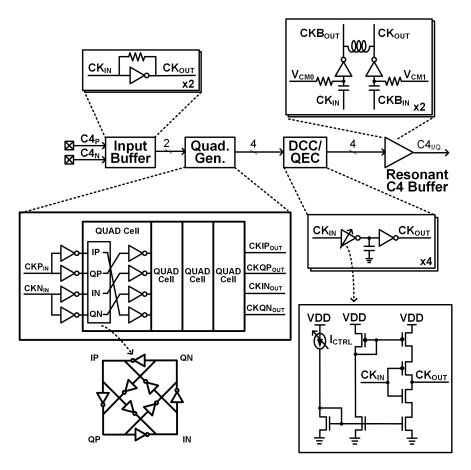

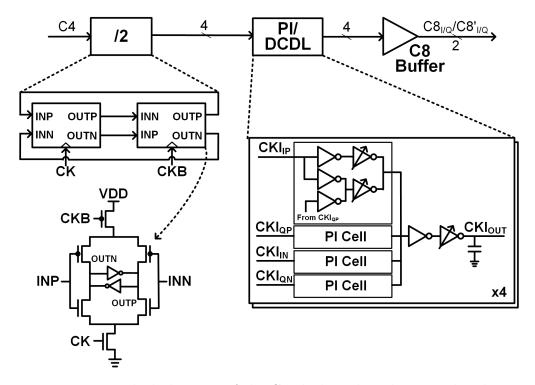

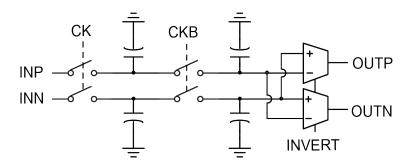

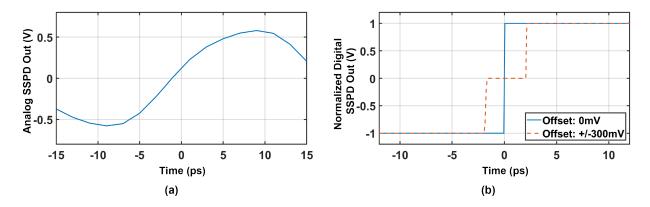

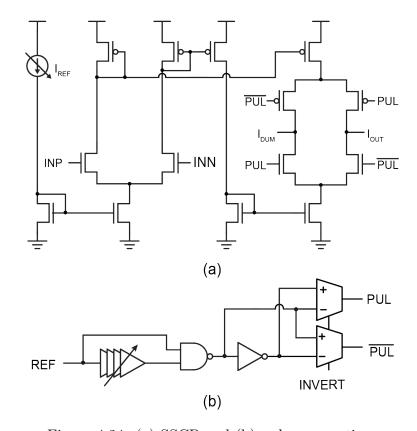

| 3.3  | Block diagram of the C4 clock path and circuit details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.4  | Block diagram of the C4 clock path and circuit details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

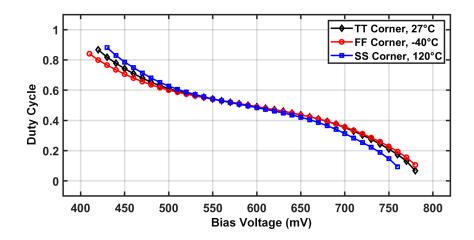

| 3.5  | Simulated C4 clock duty cycle versus input bias voltage under different corners                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | and temperatures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.6  | Block diagram of the C8 clock path and circuit details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

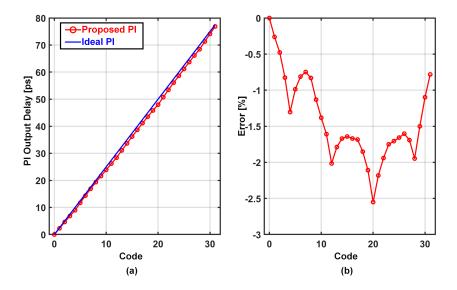

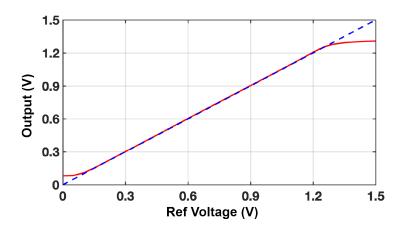

| 3.7  | (a) PI output delay versus ideal and (b) their percentage errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

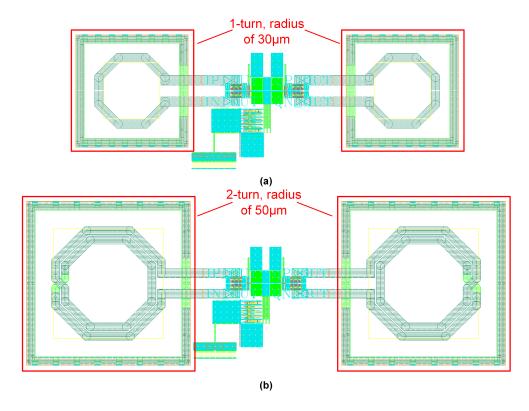

| 3.8  | C4 clock distribution layouts using (a) 1-turn inductor of radius $30-\mu m$ and (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 2-turn inductor of radius $50$ - $\mu m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

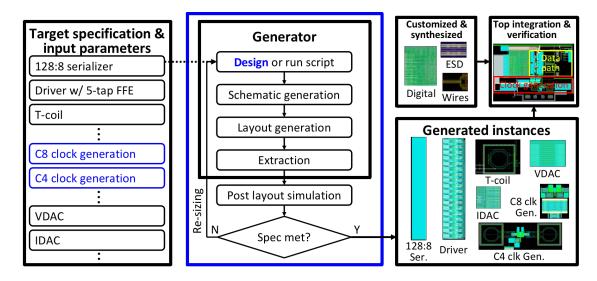

| 3.9  | Design flow of the proposed TX with BAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

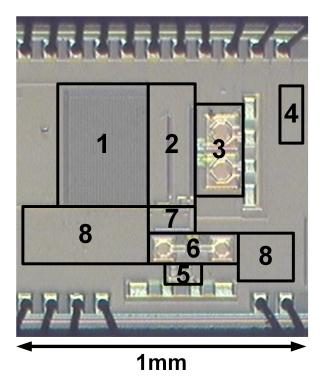

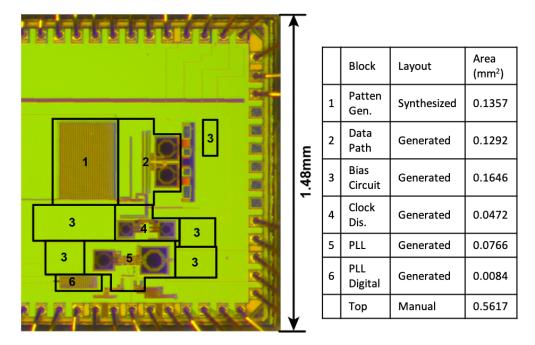

| 3.10 | Die photo and layout details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

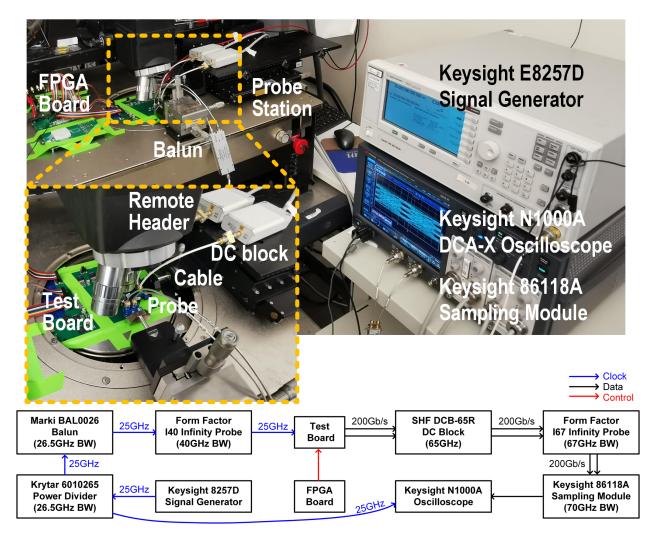

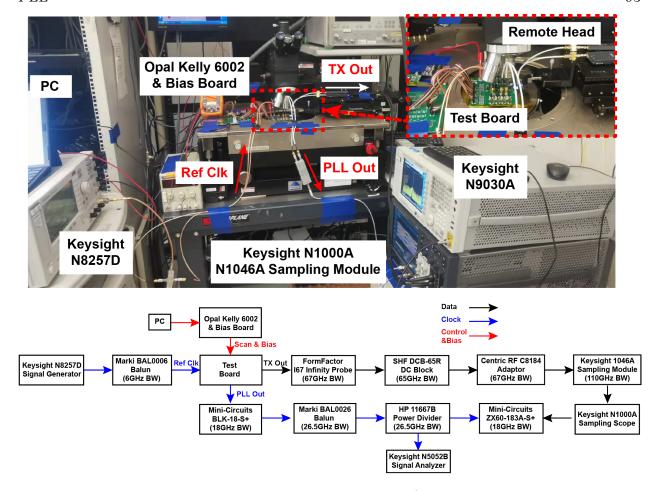

| 3.11 | Measurement setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

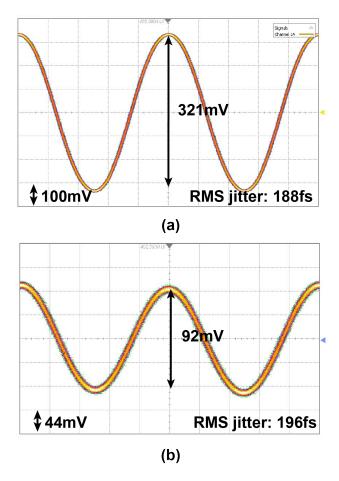

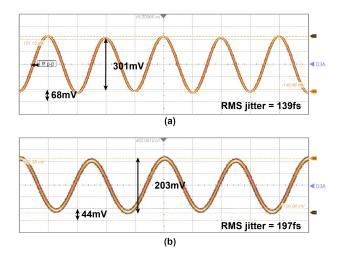

|      | Comparison of (a) the $25GHz$ clock from signal generator and (b) $50GHz$ clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | pattern from TX output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

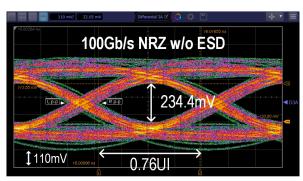

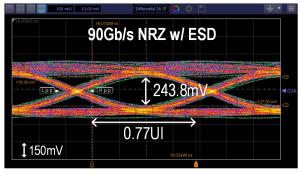

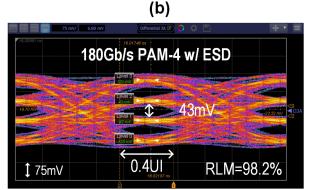

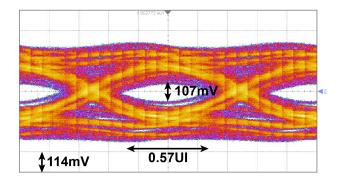

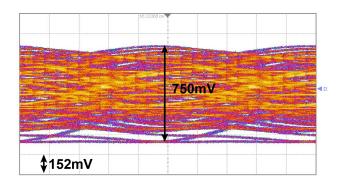

| 3.13 | Measured NRZ and PAM-4 eye diagrams w/o and w/ ESD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

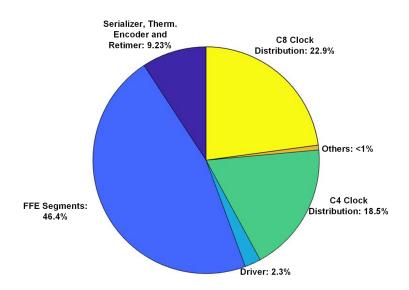

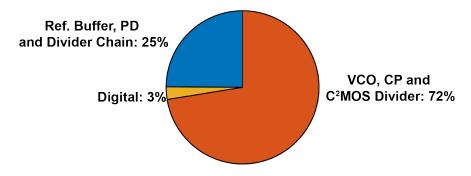

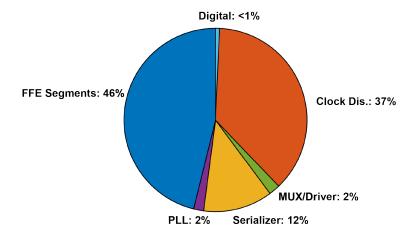

|      | Power breakdown based on post-layout extracted simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

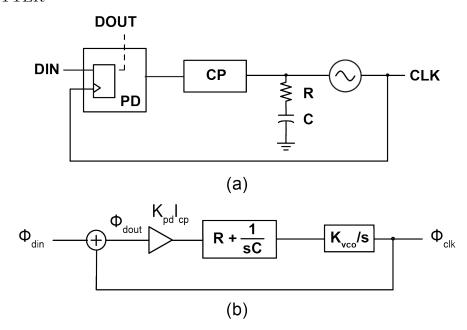

| 4.1  | (a) CDR example and (b) model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

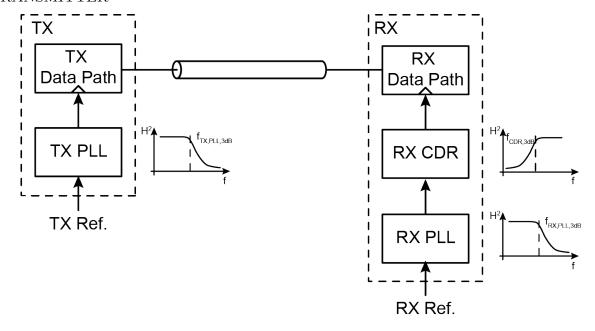

| 4.2  | Transceiver system with TX PLL, RX PLL and RX CDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

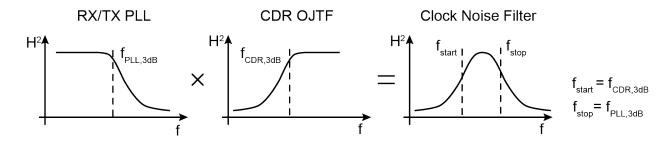

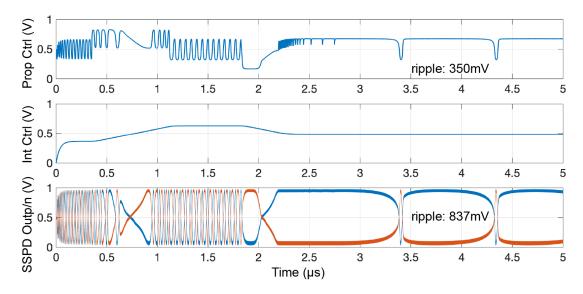

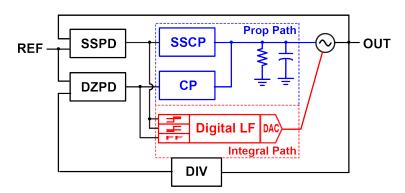

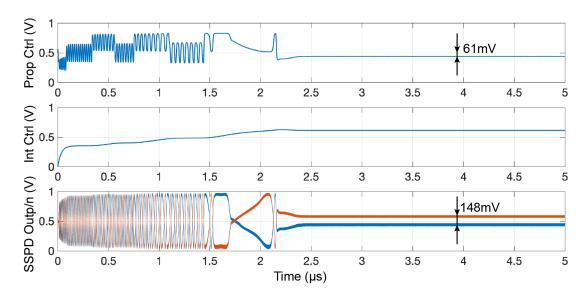

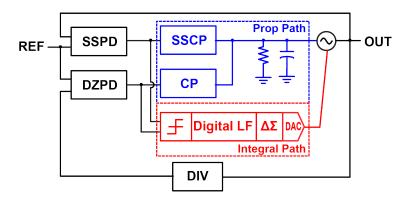

| 4.3  | Clock phase noise filter with PLL and CDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |