# Generic architectures for efficient Hyper-Dimensional Computing

Sohum Datta

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2023-54 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2023/EECS-2023-54.html

May 1, 2023

Copyright © 2023, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Generic architectures for efficient Hyper-Dimensional Computing

by

#### Sohum Datta

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Jan Rabaey, Chair Professor John Wawrzynek Professor Bruno Olshausen Professor Sayeef Salahuddin

Summer 2022

#### Abstract

#### Generic architectures for efficient Hyper-Dimensional Computing

by

#### Sohum Datta

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Jan Rabaey, Chair

The last decade has witnessed a slowdown in technology scaling. At the same time, the emergence of machine learning has substantially increased computational demand. While these trends have seriously challenged traditional paradigms for digital design, novel computing methods based on randomness can be leveraged for continued increase in performance and energy efficiency. Hyper-dimensional Computing (HDC), a brain-inspired paradigm using high-dimensional random vectors as its fundamental data-type, shows promise. It is known to provide competitive accuracy on sequential prediction tasks with far smaller model size and training time compared to conventional machine learning, and is robust to representation errors.

This dissertation considers efficient architectures for real-time Hyper-dimensional Computing on edge devices. After a study of implementations on classical compute platforms, a highly-pipelined, data-flow architecture is developed from the first principles of HDC. A detailed construction for a reasonably large HDC processor, capable of supporting a wide variety of prominent body-sensing applications, forms the foundation of this work.

The basic architecture is extended to HDC processors requiring more than a single bit of representation for vector elements. Using results from high-dimensional probability theory, a numerical normalization is proposed and its effectiveness is proven for applications obeying reasonable assumptions on vector elements' distribution. Verification experiments indicate that empirical performance of the proposed normalization is far better than the theoretical guarantee.

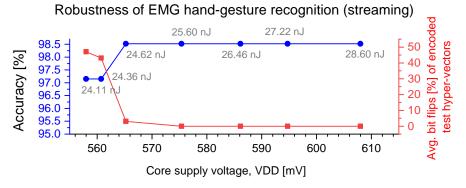

A 2048-bit wide HDC processor, designed using the architectural principles developed here, was manufactured in a leading technology node. The chip reliably achieves an energy cost of approximately 30 nanojoules per classification on a state-of-the-art body-sensing application – the best when compared to all known previous hardware in the existing literature. Measurements establish energy efficiency and robustness of the designed processor.

The architecture, arguments, experiments and measurements presented in this dissertation confirm the great potential of Hyper-Dimensional Computing as a computing paradigm capable of competitive performance in extremely energy-constrained environments.

## Acknowledgements

This project would not be possible without the continuous support and encouragement from my adviser, Prof. Jan M. Rabaey. While working with him, I have learned the value of principled thinking, originality and perseverance. Although there have been great highs and tremendous lows throughout this journey of about seven years, Jan's support was instrumental in eventually effecting progress every time. Indeed, it has been a privilege to watch an *excellent* researcher think, brain-storm and make decisions so closely in over two dozen presentations, more than eighty group meetings and many more conversations – for which I am eternally grateful.

I have been very fortunate to have known Professors Bruno Olshausen, John Wawrzynek and Sayeef Salahuddin. Their careful examination of this work's arguments, in-depth discussions and specific feedback has been essential for me to successfully correct logical faults, improve my hypotheses and presentation of the material. Pentti Kanerva and Bruno have been foundational in forming and maintaining the Berkeley community interested in HDC, located at the Redwood institute. I'm very grateful for Prof. Subhasish Mitra's pithy comments and feedback on the subject and allied fields. I'm also pleasantly reminded of the five continuous hours on a bright afternoon at Stanford, where an extempore, free-for-all discussion had broken out in Subhasish's group – barely hinged to my presentation.

I am grateful for the outstanding teachers who have taught me during my stay at Berkeley. Memorable experiences include Krste Asanovic's and John Wawrzynek's expositions on classical architectural monuments and recent creativity, Jan's renowned sandbox for students to try their skills in imagining tiny processors (or its lack thereof); Bin Yu's brilliant and unbelievably informal course on statistics, augmented with mathematical treatments by Martin Wainwright, William Fithian and Michael Jordan (in the order of booming complexity), and the entirely new experience at Tom Griffith's seminars on cognition. I am especially grateful to Jonathan Shewchuk for the memorable and unconventional introduction to machine learning in Spring 2016, and for the wonderful opportunity to teach and influence that flagship undergraduate and early-graduate course in Computer Science (with more than 650 completing students). Jonathan also gave me the *rare* opportunity to write all questions for an entire homework set and an essay-type written question for the final exam during both semesters that I assisted in teaching. Teaching and interacting with such a large and diverse group of students has been an incredible learning experience.

I have been fortunate to work with brilliant colleagues during this period. Abbas Rahimi (IBM Zurich) and Mohsen Imani (UC Irvine) have been very helpful in guiding me through the proverbial research thicket by sharing data sets, tips and producing a stream of related research – guiding me to my destination. Andy Zhou, Ali Moin and George Alexandrov's splendid data set and paper on EMG hand-gesture recognition provided a great final benchmark for comparison. Paxon Frady, Friedrich Sommer and Denis Kleyko's papers were the first theoretical works on the subject that I came across after reading Pentti's decades-old book. Finally, I especially appreciate Alisha Menon, Youbin Kim, Laura Galindez, Denis Kleyko, Spencer Kent, Matthew Andersen and Mohamed Ibrahim for their thoughtful comments on my work during the dozens of group presentations over the years. During my research at Berkeley, I was fortunate to work with visitors from University of the Philippines Diliman. Ryan A. G. Antonio and Aldrin R. S. Ison were very helpful in modifying and deploying my source code on an embedded GPU and CPU core. They were quick learners, and our collaboration produced the first publication of this project. Denise Soriano, Alexis Czezar Cruz Torreno and Bentz Del Mundo visited Berkeley in early 2020 – while the pandemic was rapidly spreading in North America. Despite that, they collected a great amount of useful data that helped me scope-out a successful idea later.

The chip taped-out during this project would not have been possible without Brian Richards. Apart from his deep expertise, excellent design suggestions and incisive questions during technical reviews, I will miss his usual cool-headed demeanor in the presence of tape-out deadlines and him always cheering me up when I'm falling behind or getting demotivated. Brian is a tremendous resource for all graduate students at BWRC, and the generations of chip designers taping out and graduating from my lab are privileged to have such excellent research staff to support them. The graduate students who created the Hammer tape-out tool, especially Harrison Liew, were essential for making physical design manageable. Harrison was available and super helpful during the entire eight-months long physical design phase, slowly teaching me how to use Hammer and providing guidance when I got stuck.

I'm thankful to Youbin Kim, Daniel Sun and Mohamed Ibrahim for lending me a helping hand at times when the effort seemed unbearable. Youbin assisted me in completing the chip's Input/Output pad-frame, Daniel was instrumental in getting a Hammer setup started for my chip, and Mohamed was very helpful in fixing a few last-moment DRC errors in my design.

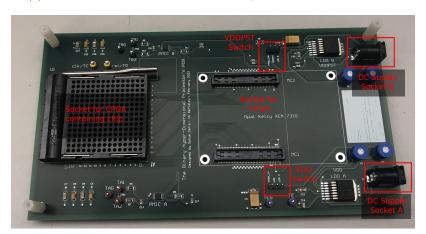

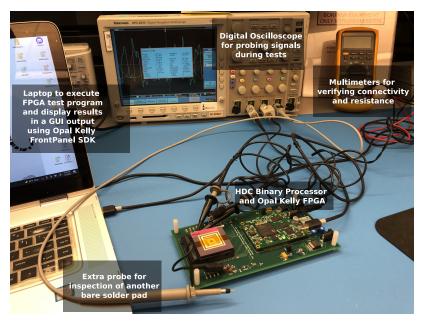

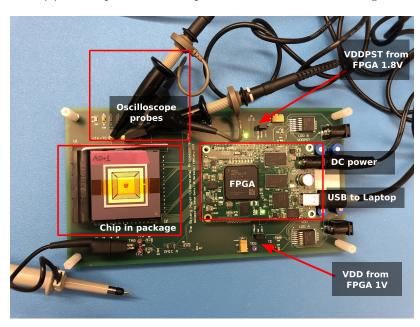

The enormous effort spent in designing and fabricating the chip would have been in vain without a successful testing setup. Crucial to that is to design a Printed-Circuit Board (PCB) that can properly support tests and measurements. My first PCB design experience wouldn't have been successful without the continuous advise of Brian and James Dunn. They are experts in PCB design, and their periodic reviews were essential for debugging within deadlines. James was generous with his time in helping me with soldering certain components to the board. Anita Flynn and Robert Kondner selflessly devoted their time to my project outside of normal working hours – helping my board by designing PCB foot-prints for some non-standard package components. Anita's attention to detail and careful documentation stood out as great skills that I should cultivate to become an excellent engineer.

The Berkeley Wireless Research Center (BWRC) is lucky to have superb administrative staff such as Columba Candy Corpus-Steudeman, Mikaela Cavizo-Briggs and Yessica Bravo. Candy, assisted by Yessica and Mikaela, has been extremely kind and supportive throughout this journey – handling all research, financial and travel-related paperwork with great organization. Jeffrey Anderson-Lee helped me stay connected to the lab machines even while the pandemic was spreading and lock-downs were being announced. Most importantly, I want thank Candy for greeting me with a *smile everyday* at the reception area near the entrance all these years.

I'm indebted to the Taiwan Semiconductor Manufacturing Company, Limited (TSMC) for funding my research, providing us with the physical design kit and manufacturing my chip in an industry-leading technology node. I am thankful to the Semiconductor Research Corporation (SRC), the Defense Advanced Research Project Agency (DARPA), the National Science Foundation (NSF), TSMC and all sponsors of the Berkeley Wireless Research Center (BWRC) at UC Berkeley for funding and supporting my project.

Finally, I thank the wider community for expressing an interest in my research, providing counter-arguments and sharing relevant information from their fields related to my project. They include Jared Zerbe (Apple), Bryan Raines (Apple), Dana Massie (Apple), William Athas (Apple), Julia Ng (NVIDIA), Jonathan Yedidia (Analog Garage), Nicolas Le Dortz (Analog Garage), Phillip Nadeau (Analog Garage), Mehul Tikekar (Waymo), Chiraag Juvekar (Apple), Tony Wu (Meta), Haitong Li (Purdue), Geoffrey Burr (IBM), Matthew Ziegler (IBM), Krishnan Kailas (IBM), Mondira Pant (Intel), Mike Davies (Intel), Christopher Hughes (Intel), Jinjun Xiong (IBM), Todd Younkin (SRC), Ramesh Chauhan (Qualcomm), Cliff Young (Google) and Derrick Aguren (AMD). Discussions with the larger community expanded my horizons and allowed to gain a longer-term perspective on my work.

Berkeley, CA Sohum Datta

This dissertation is dedicated to my father.

## Contents

| 1 | Intr | oduct   | ion                                                    | 1  |

|---|------|---------|--------------------------------------------------------|----|

| 2 | Hyl  | er-Di   | mensional Computing (HDC): preliminaries and a survey  | 5  |

|   | 2.1  |         | gonality in high dimensions                            | 6  |

|   | 2.2  | The N   | Multiply-Add-Permute (MAP) paradigm                    | 8  |

|   | 2.3  |         | ples of computing with hyper-vectors                   | 9  |

|   |      | 2.3.1   | Encoding semantics with random hyper-vectors           | 10 |

|   |      | 2.3.2   | Language recognition                                   | 11 |

|   | 2.4  | A sun   | nmary of HDC hardware literature                       | 13 |

| 3 | Pri  | nciples | of constructing an efficient architecture for HDC      | 15 |

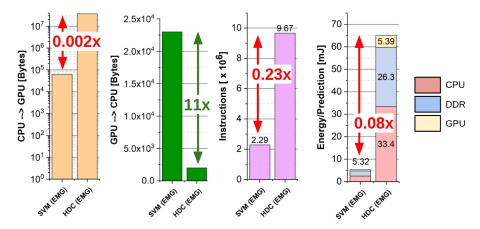

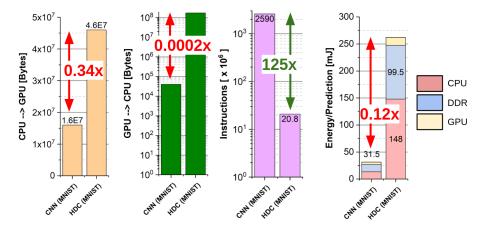

|   | 3.1  | _       | ng HDC on embedded CPU and GPU                         | 15 |

|   |      | 3.1.1   | Benchmark applications for instrumentation             | 16 |

|   |      | 3.1.2   | Hardware setup for instrumentation                     | 17 |

|   |      | 3.1.3   | Instrumentation results on eCPU                        | 17 |

|   |      | 3.1.4   | Instrumentation results on eGPU                        | 20 |

|   |      | 3.1.5   | Lessons learned                                        | 22 |

|   | 3.2  | Struct  | sure of HDC algorithms                                 | 24 |

|   |      | 3.2.1   | Value representation in HDC                            | 24 |

|   |      | 3.2.2   | Encoding stages                                        | 24 |

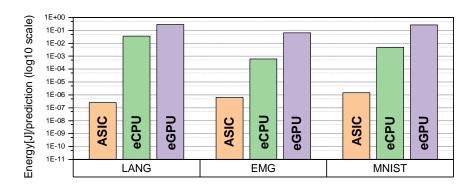

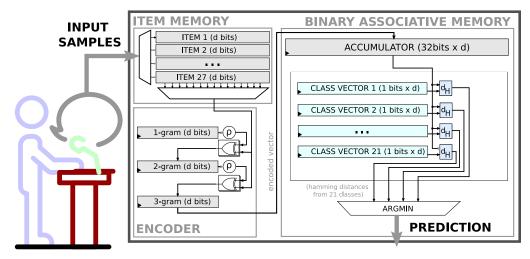

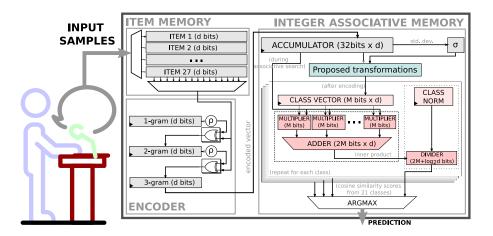

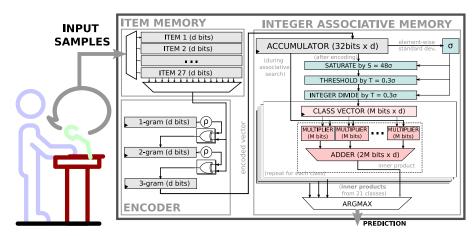

|   | 3.3  | The C   | Generic architectural model for HDC                    | 26 |

|   |      | 3.3.1   | Common algorithmic kernels                             | 26 |

|   |      | 3.3.2   | The Generic abstraction                                | 27 |

|   |      | 3.3.3   | Major components of the Generic architecture           | 28 |

|   |      | 3.3.4   | Arguments for a data-flow architecture                 | 29 |

| 4 | Pro  | gramn   | nability, scalability and a hardware evaluation of the |    |

|   |      | _       | IDC architecture                                       | 30 |

|   | 4.1  | Organ   | ization of the Encoder                                 | 30 |

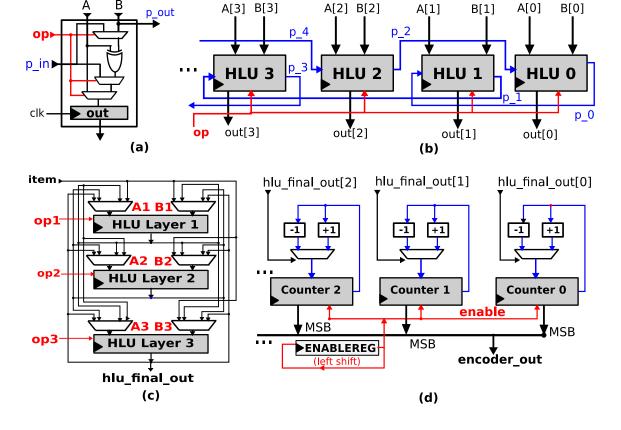

|   |      | 4.1.1   | Hyper-dimensional Logic Unit (HLU)                     | 31 |

|   |      | 4.1.2   | Programming the Encoder                                | 34 |

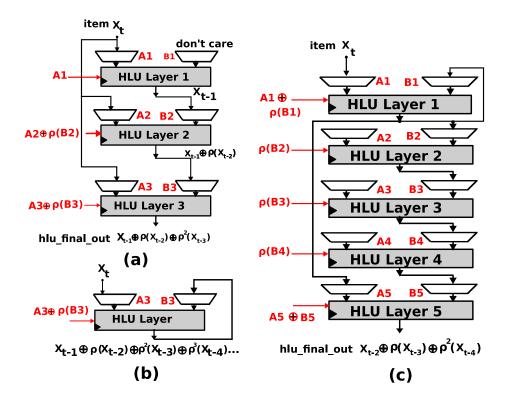

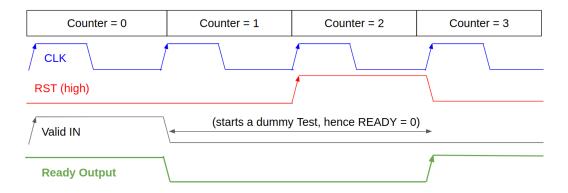

|   |      | 4.1.3   | The Valid Chain: a flow-based pipeline control         | 36 |

|   |      | 4.1.4   | Considerations of sparsity and security                | 43 |

|   | 4.2  | Exten   | sions of the Generic architecture                      | 45 |

|   |      | 4.2.1   | Item Memory and its extensions                         | 48 |

|   |      | 422     | Associative Memory and its extensions                  | 50 |

|   |             | 4.2.3            | Multi-component extensions                                             | 52         |

|---|-------------|------------------|------------------------------------------------------------------------|------------|

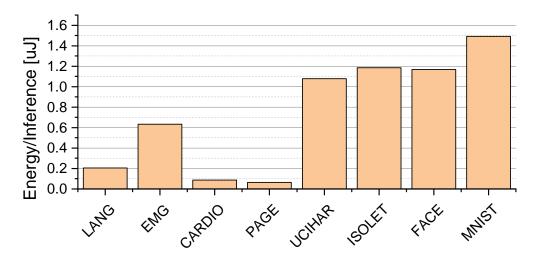

|   | 4.3         | Hardw            | vare evaluation of the Generic HDC architecture                        | 54         |

|   |             | 4.3.1            | Benchmark of supervised classification tasks                           | 54         |

|   |             | 4.3.2            | Energy efficiency on a synthesized 28nm processor                      | 55         |

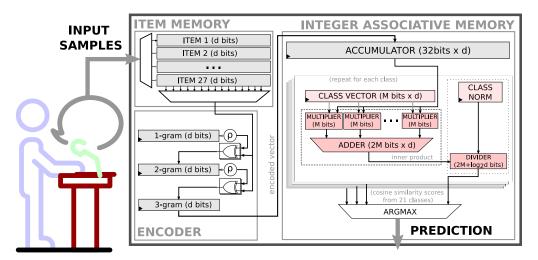

| 5 | Arc         | hitectı          | ral techniques for multi-bit HDC                                       | <b>58</b>  |

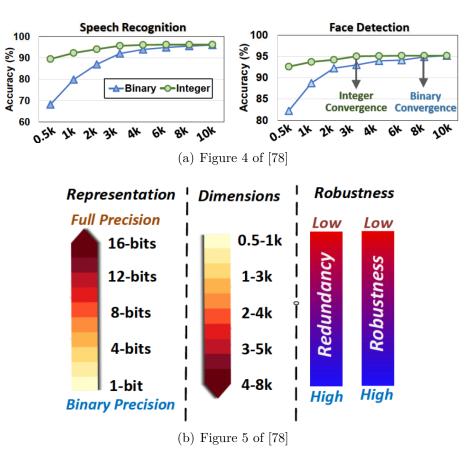

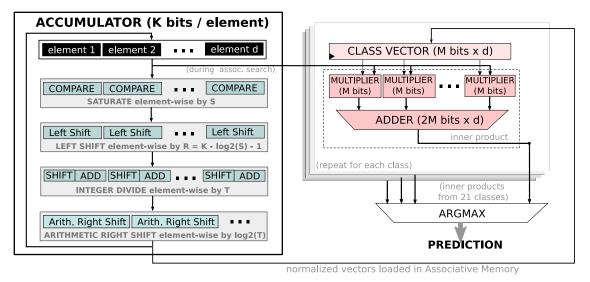

|   | 5.1         | Challe           | nges in multi-bit HDC architectures                                    | 59         |

|   |             | 5.1.1            | The need for multi-bit HDC                                             | 59         |

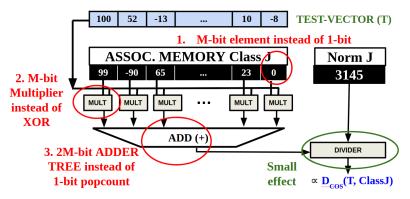

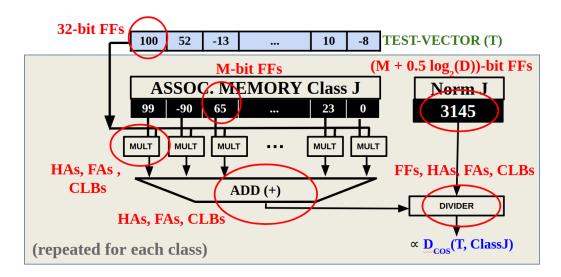

|   |             | 5.1.2            | Logic complexity of integer Associative Memory                         | 61         |

|   |             | 5.1.3            | A literature review of multi-bit HDC                                   | 64         |

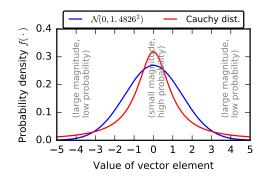

|   | 5.2         | Releva           | nt properties of the probability distribution of hyper-vector elements | 65         |

|   |             | 5.2.1            | Tails of probability density functions                                 | 66         |

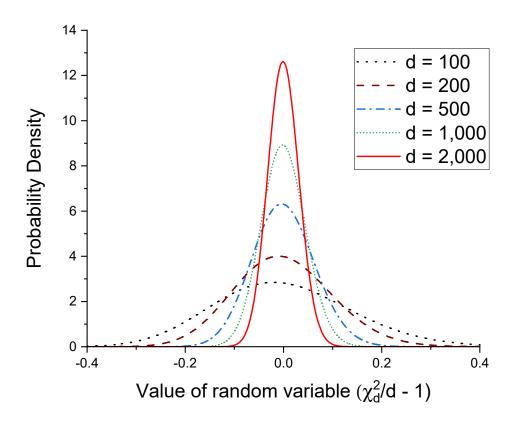

|   |             | 5.2.2            | Chi-squared concentration                                              | 69         |

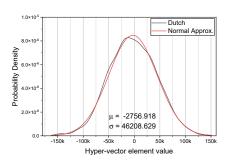

|   |             | 5.2.3            | Normality assumption and the EUROPARL dataset                          | 71         |

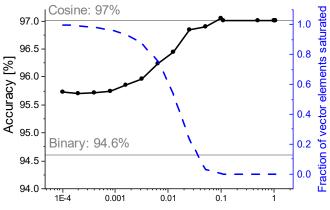

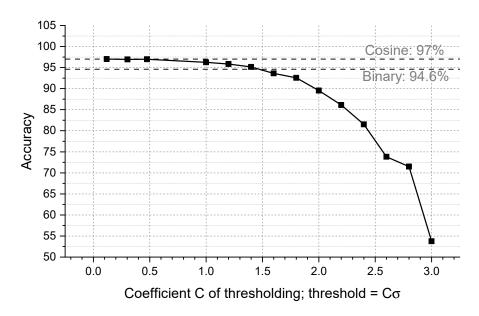

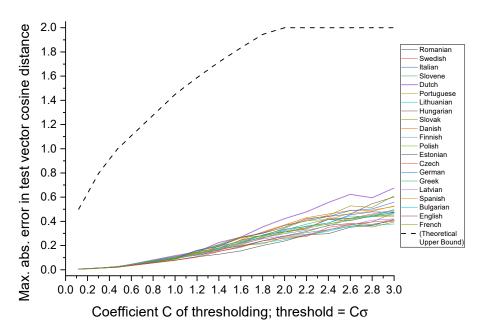

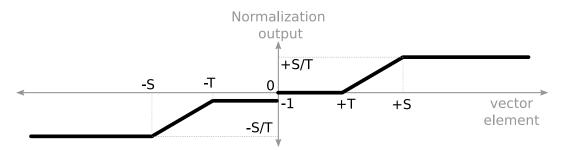

|   | 5.3         | Transf           | formations for precision reduction                                     | 74         |

|   |             | 5.3.1            | Saturation                                                             | 75         |

|   |             | 5.3.2            | Thresholding                                                           | 76         |

|   |             | 5.3.3            | Putting it all together: Modified Thresholding                         | 81         |

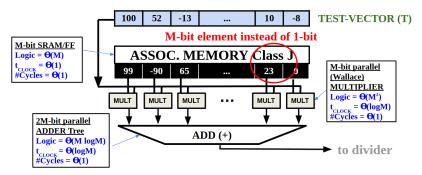

|   | 5.4         | Prelim           | inary estimates for hardware savings due to Modified Thresholding      | 84         |

|   |             | 5.4.1            | Estimating number of sequential gates                                  | 86         |

|   |             | 5.4.2            | Estimating logic complexity for the adder-tree                         | 87         |

|   |             | 5.4.3            | Estimating logic complexity for multipliers                            | 89         |

|   |             | 5.4.4            | Estimating logic complexity for the divider                            | 93         |

|   |             | 5.4.5            | Comparison of logic complexity estimates with and without              |            |

|   |             |                  | transformations for Integer HDC associative search                     | 94         |

| 6 | <b>A</b> 20 | 048 <b>-di</b> n | n generic Hyper-Dimensional Binary core                                | 95         |

|   | 6.1         | Physic           | eal characteristics and specifications                                 | 96         |

|   |             | 6.1.1            | Physical design and implementation                                     | 98         |

|   |             | 6.1.2            | Timing constraints and design convergence                              | 99         |

|   | 6.2         | Testin           | g infrastructure and experiments                                       | 102        |

|   |             | 6.2.1            | Printed Circuit Board and components for testing                       | 102        |

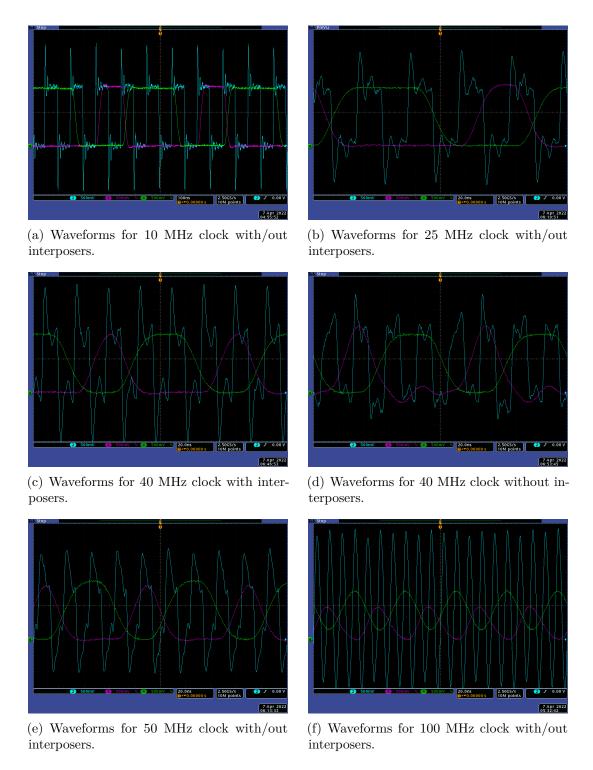

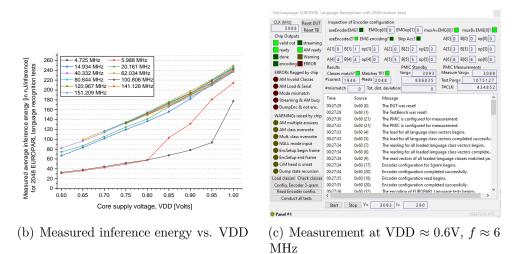

|   |             | 6.2.2            | Testing basic I/O and chip response                                    | 106        |

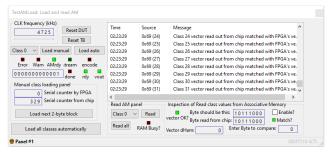

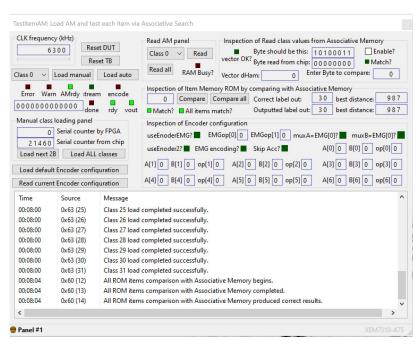

|   |             | 6.2.3            | Testing Associative Memory functionality                               | 108        |

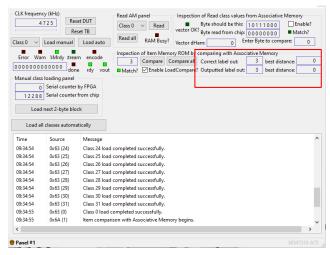

|   |             | 6.2.4            | Testing ROM and Item Memory functionality                              | 110        |

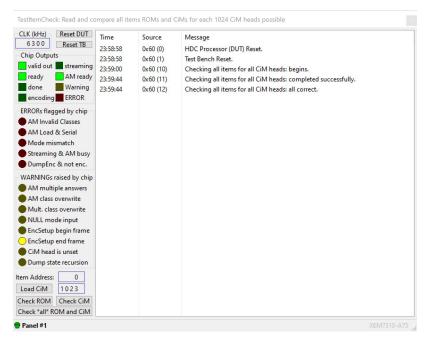

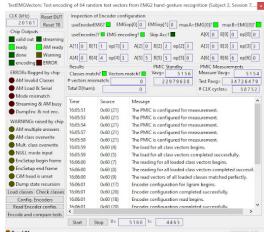

|   |             | 6.2.5            | Testing Encoder for on-chip benchmark applications                     | 110        |

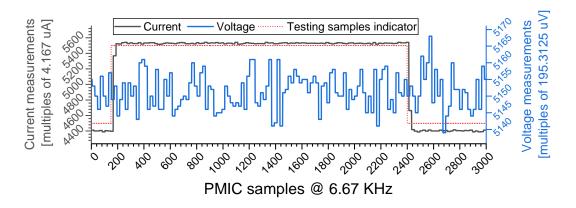

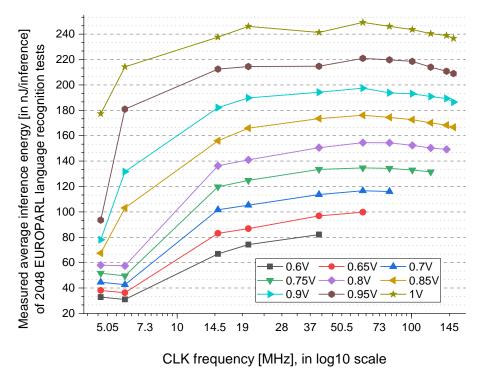

|   | 6.3         | Inferer          | nce energy measurements on chip                                        | 113        |

|   |             | 6.3.1            |                                                                        | 116        |

|   |             | 6.3.2            | Measured inference energy for EMG hand-gesture recognition             | 119        |

|   |             | 6.3.3            |                                                                        | 125        |

| 7 | Con         | clusio           | ns                                                                     | <b>128</b> |

## List of Figures

| 1-1<br>1-2<br>1-3               | Figure 1 of [3]: eras of transistor scaling                                                   | ]<br>3                     |

|---------------------------------|-----------------------------------------------------------------------------------------------|----------------------------|

| 1-4                             | HDC is robust to representation errors and well-suited for in-memory hardware implementations | 4                          |

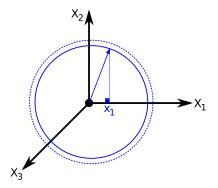

| 2-1                             | Orthogonality in High Dimensions                                                              | 6                          |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5 | Examples of measured power trace on eCPU and eGPU                                             | 18<br>19<br>21<br>23<br>28 |

|                                 | Encoder organization                                                                          | 32                         |

| 4-1<br>4-2                      | Permutation leads to across-word dependency in the Encoder                                    | $\frac{32}{33}$            |

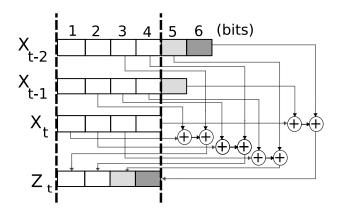

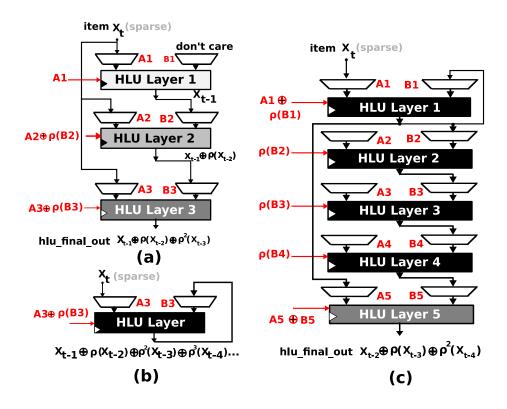

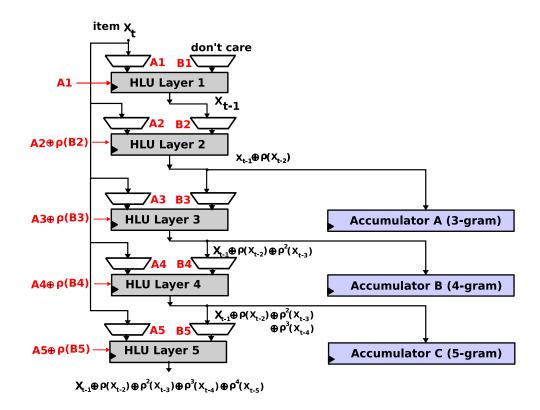

| 4-2<br>4-3                      | Examples of programming 3-gram in a HLU Network                                               | 35                         |

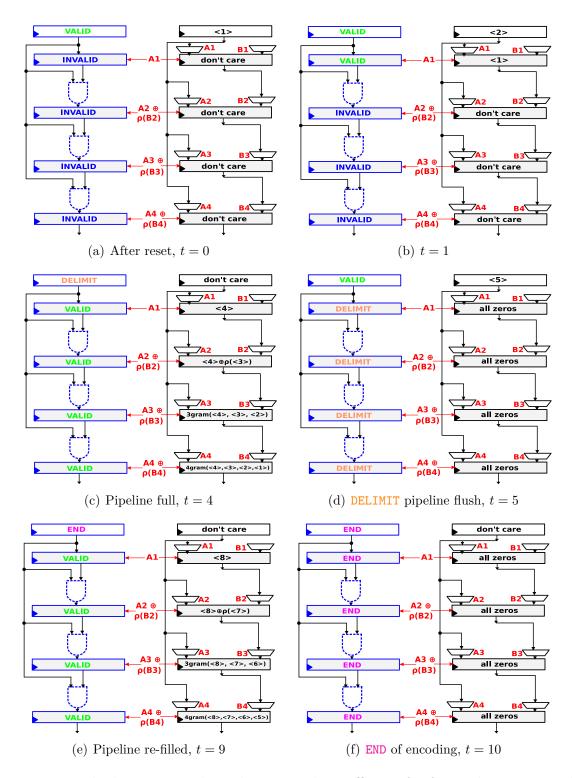

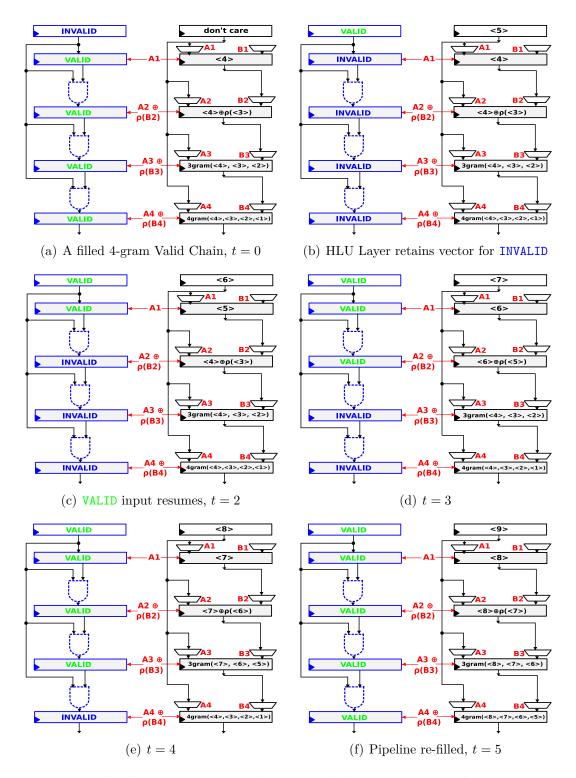

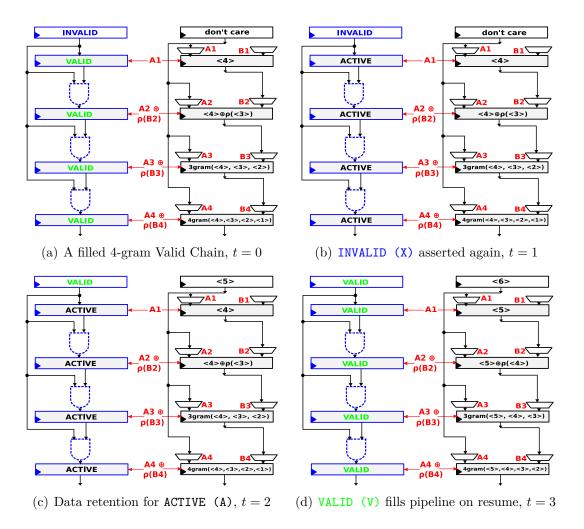

| 4-3<br>4-4                      | Flow-based pipeline control in HLU Layer Network                                              | 37                         |

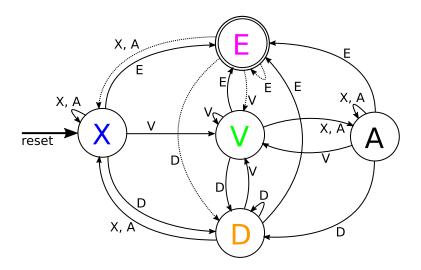

| 4-5                             | State transition diagram for valid[out] using the 5-signal pipeline control.                  | 39                         |

| 4-6                             | The basic 4-signal pipeline control is sufficient for forward progress and                    | 0.                         |

| 10                              | pipeline flush in feed-forward networks                                                       | 40                         |

| 4-7                             | The basic 4-signal pipeline control does not support data retention                           | 41                         |

| 4-8                             | 5-signal pipeline control supports data retention for feed-forward networks.                  | 42                         |

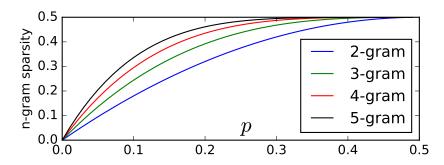

| 4-9                             | Sparsity of <i>n</i> -gram with item sparsity                                                 | 43                         |

| 4-10                            | Trade-off between sparsity and side-channel security for 3-gram                               | 44                         |

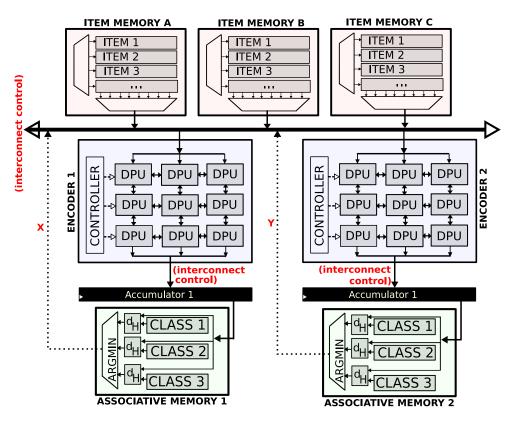

| 4-11                            | Two-stage encoder in a Generic HDC processor                                                  | 46                         |

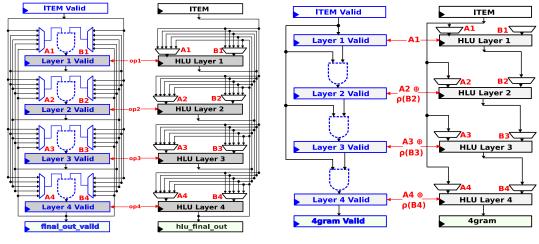

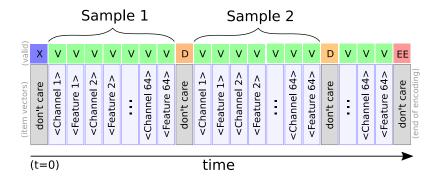

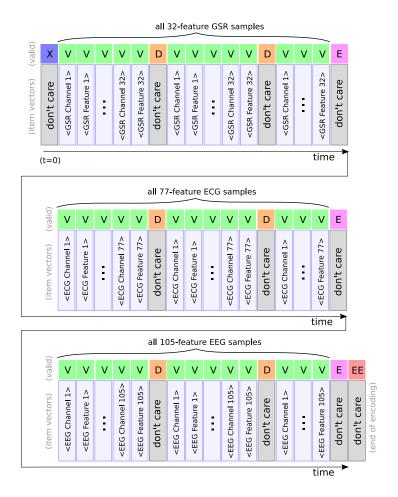

| 4-12                            | Valid signals and input scheme for two-stage encoding of EMG hand-                            |                            |

|                                 | gesture data in a Generic HDC processor                                                       | 47                         |

| 4-13                            | Valid signals and input scheme for two-stage encoding of physiological                        |                            |

|                                 | data for Emotion recognition in a Generic HDC processor                                       | 47                         |

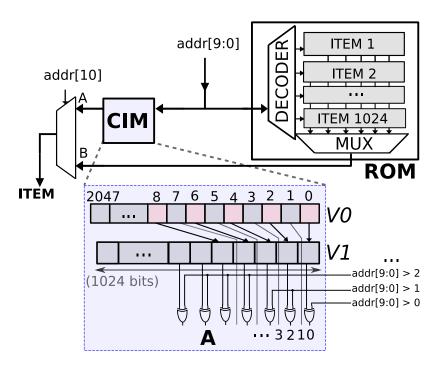

|                                 | Item Memory with continuous-item generation logic for scalar values.                          | 48                         |

| 4-15                            | Figure 6 of [136]: Variation in cell delay is used to produce 27 items.                       | 50                         |

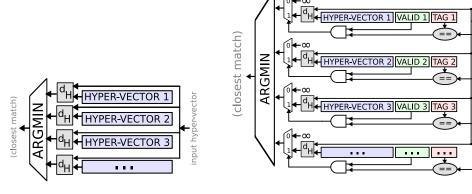

|                                 | Associative Memory and its extensions                                                         | 51                         |

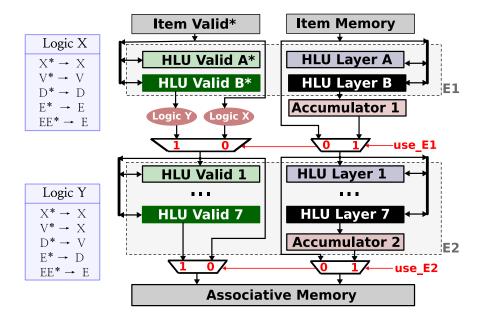

|                                 | A scaled up HDC processor with multiple components                                            | 52                         |

| 4-18                            | A common HLU Layer Network can be configured to simultaneously                                |                            |

|                                 | encode multiple expression from a common input stream                                         | 53                         |

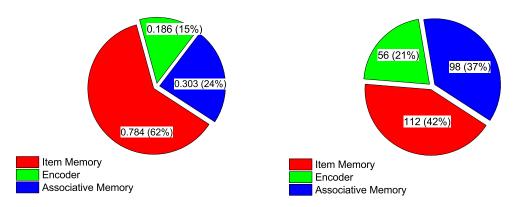

| 4-19                            | Post-synthesis energy per inference for benchmark applications                                | 56                         |

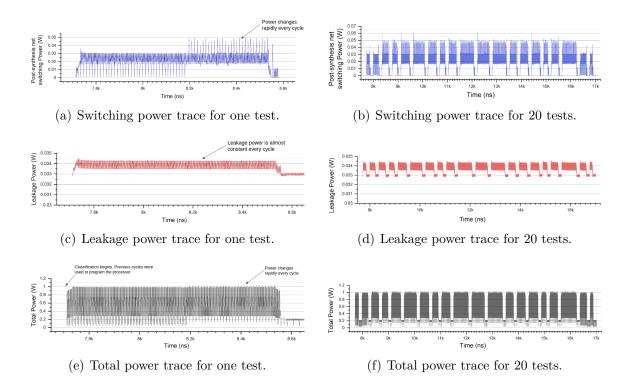

| 4-20       | Post-synthesis simulation traces for EUROPARL Language Recognition.                                                                        | 57  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

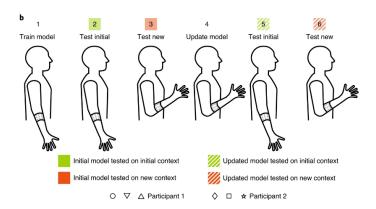

| 5-1<br>5-2 | Integer models are <i>uniformly more accurate</i> than binary models Figure 6b of [39]: training, updating hand-gestures and transitioning | 60  |

|            | to other gestures require intermediate storage of learned hyper-vectors.                                                                   | 61  |

| 5-3        | Only the associative memories differ among HDC data-paths for the                                                                          | c c |

| 5-4        | binary and the integer model                                                                                                               | 62  |

| 0-4        | increasing bits/element $M$                                                                                                                | 63  |

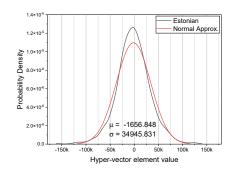

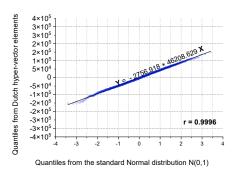

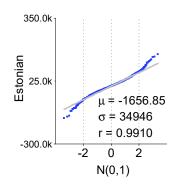

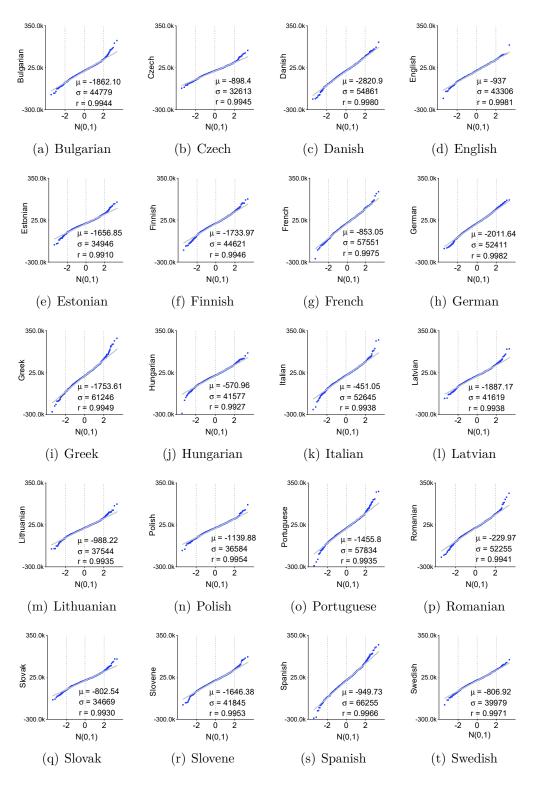

| 5-5        | Properties of hyper-vector probability distribution.                                                                                       | 67  |

| 5-6        | Concentration of probability density around $d$ for $\chi_d^2$                                                                             | 70  |

| 5-7        | Normality assumption for best fitting (Dutch) and least fitting (Esto-                                                                     |     |

|            | nian) language hyper-vectors in the EUROPARL corpus                                                                                        | 72  |

| 5-8        | Normality assumption for all except Dutch in the EUROPARL corpus.                                                                          | 73  |

| 5-9        | The proposed transformations require elements' standard deviation $\sigma$ .                                                               | 74  |

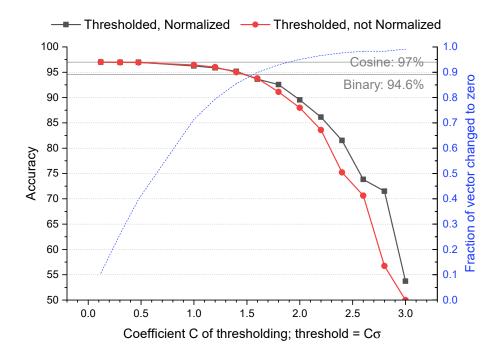

| 5-10       | ,                                                                                                                                          | 76  |

| 5-11       | Thresholding leads to conservative upper bounds of error introduced in                                                                     | 70  |

| 5 19       | cosine similarity                                                                                                                          | 79  |

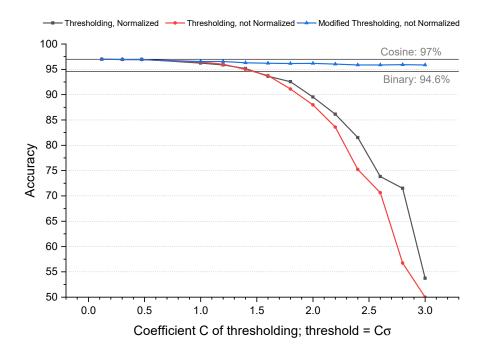

| J-12       | compared for associative search                                                                                                            | 80  |

| 5-13       | Modified thresholding for the integer HDC Associative Memory                                                                               | 82  |

|            | Accuracy of EUROPARL language recognition using modified thresh-                                                                           |     |

|            | olding with increasing threshold $T = C\sigma$                                                                                             | 83  |

| 5-15       | Logic components of integer Associative Memory considered for a                                                                            |     |

|            | preliminary estimate of hardware cost                                                                                                      | 85  |

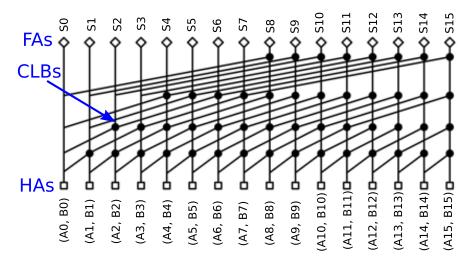

| 5-16       | The 16-bit Kogge-Stone adder containing Half Adders (HAs), Carry Lookahead Blocks (CLBs) and Full Adders (FAs)                             | 87  |

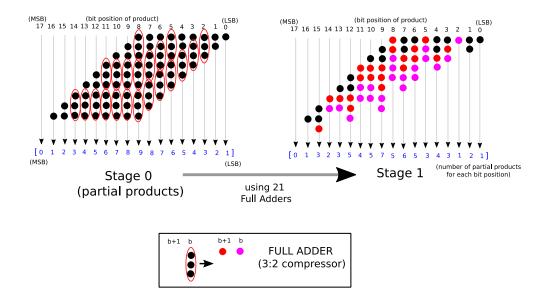

| 5-17       | A stage of reducing partial products for $N = 9$ -bit Wallace tree multi-                                                                  |     |

|            | plier using Full Adders                                                                                                                    | 90  |

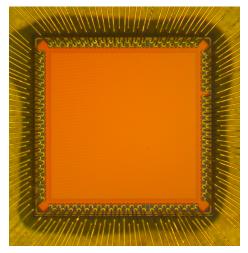

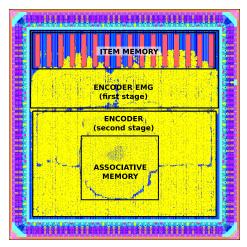

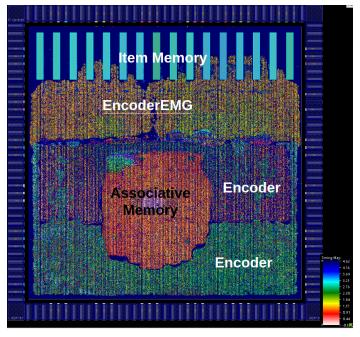

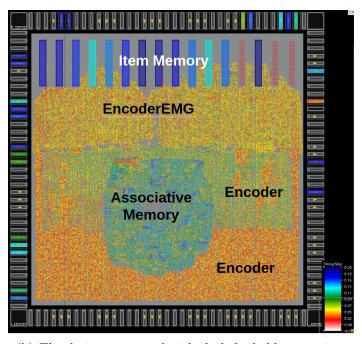

| 6-1        | Chip micrograph of the 2048-dim binary HDC processor                                                                                       | 97  |

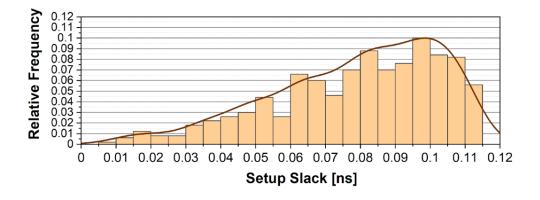

| 6-2        | Heavy-tailed distribution of positive setup slack                                                                                          | 96  |

| 6-3        | 1                                                                                                                                          | 101 |

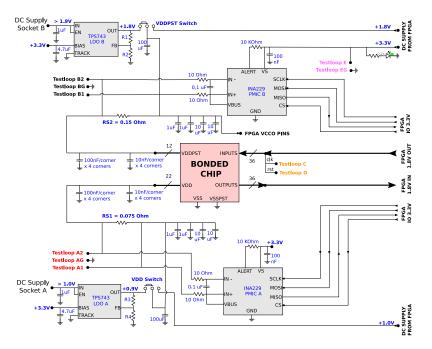

| 6-4        | <u> </u>                                                                                                                                   | 103 |

| 6-5        | <u> </u>                                                                                                                                   | 104 |

| 6-6        |                                                                                                                                            | 105 |

| 6-7        | O V I                                                                                                                                      | 106 |

| 6-8<br>6-9 | Captured waveforms for testing ready output                                                                                                | 107 |

| 0-9        | , , , , , , , , , , , , , , , , , , ,                                                                                                      | 109 |

| 6-10       | Item Memory tests: ROM and continuous vectors are read and associa-                                                                        | 100 |

| 3          |                                                                                                                                            | 111 |

| 6-11       | v                                                                                                                                          | 112 |

| 6-12       | A measurement trace from PMIC                                                                                                              | 113 |

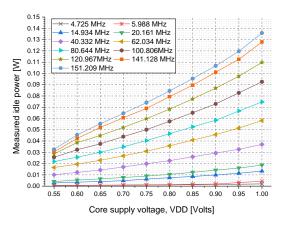

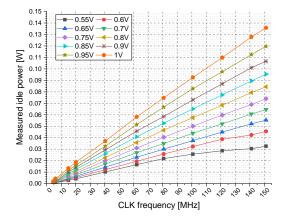

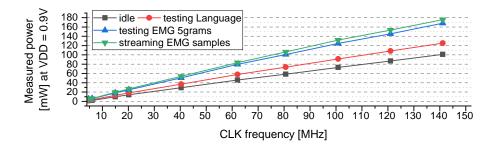

| 6-13       | Idle power measurements                                                                                                                    | 114 |

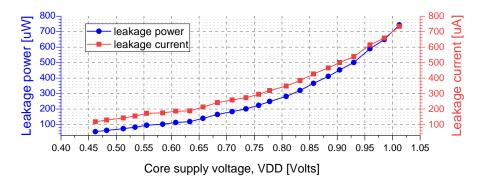

| 6-14   | Measurements of leakage power at various VDD voltages                     | 114 |

|--------|---------------------------------------------------------------------------|-----|

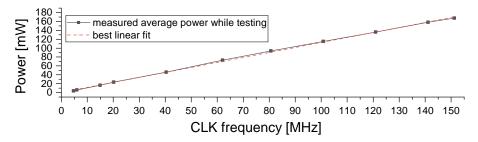

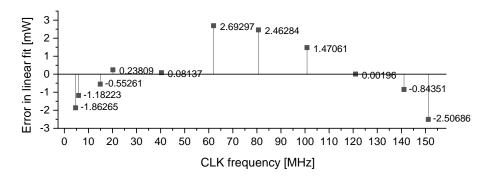

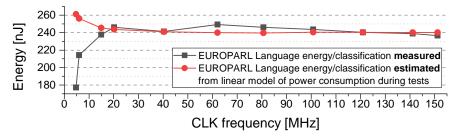

| 6 - 15 | Using the linear model for power consumption leads to inaccurate          |     |

|        | energy/predioction estimates at low frequencies                           | 115 |

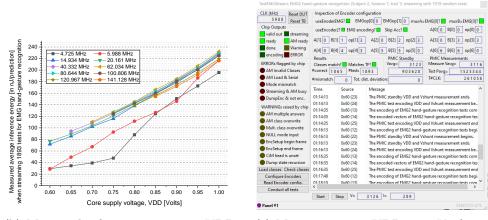

| 6-16   | Measured energy/prediction for 2048 random tests of EUROPARL              |     |

|        | language recognition                                                      | 117 |

| 6-17   | Measured test power for Language recognition and EMG hand-gesture         |     |

|        | recognition at VDD $\approx 1$ V                                          | 122 |

| 6-18   | Measured energy/prediction for 512 random tests of EMG hand-gesture       |     |

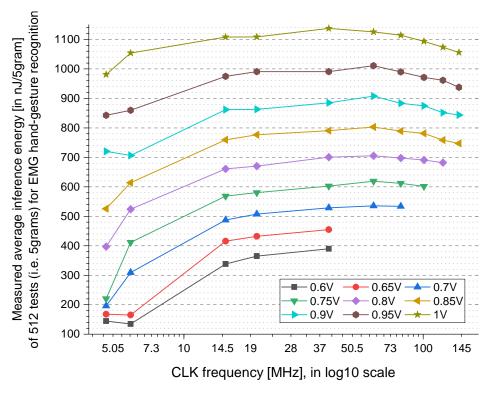

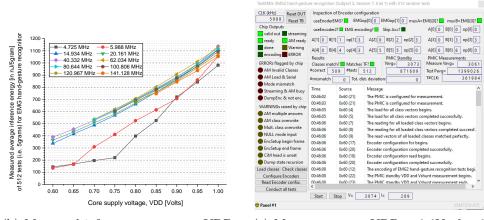

|        | recognition classified each 5-gram at a time                              | 123 |

| 6-19   | Measured energy/prediction for 1893 random tests of EMG hand-gesture      |     |

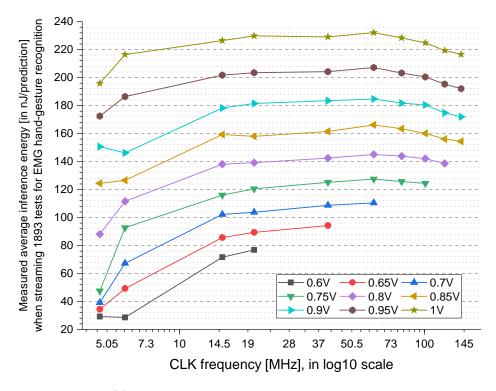

|        | recognition with samples streamed in continuously                         | 124 |

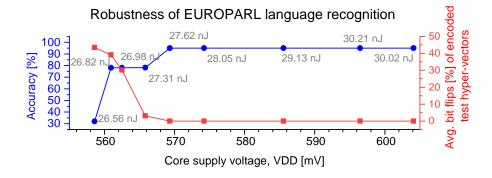

| 6-20   | Measured robustness of classification accuracy with voltage over-scaling. | 127 |

| - 1    |                                                                           | 100 |

| 7-1    | HDC is suitable paradigm for human-centric computing                      | 130 |

## List of Tables

| 3.1 | Inference accuracy of the instrumented algorithms                      | 16  |

|-----|------------------------------------------------------------------------|-----|

| 3.2 | Levels of parallelism present in instrumented algorithms               | 22  |

| 3.3 | Comparison of ASIC implementation of HDC with hand-optimized           |     |

|     | FPGA implementation [103] for dimension $d \approx 10000$              | 23  |

| 4.1 | Benchmark for energy evaluation of the Generic HDC architecture        | 54  |

| 4.2 | Quality of Results (QoR) report for the synthesized Generic processor. | 55  |

| 5.1 | Preliminary estimates for logic cost of associative search in Integer  |     |

|     | Associative Memory with and without transformations                    | 94  |

| 6.1 | Benchmark applications for on-chip measurements                        | 95  |

| 6.2 | Summary of technical specifications of the 2048-dim binary HDC pro-    |     |

|     | cessor                                                                 | 96  |

| 6.3 | Comparison of measured energy per inference for Language Recognition.  | 118 |

| 6.4 | Comparison of measured energy per inference for EMG hand-gesture       |     |

|     | recognition.                                                           | 126 |

## Chapter 1

#### Introduction

Two crucial events in the last decade determine the pace of technical innovation today. The first is the gradual slowdown in relentless miniaturization of semiconductor devices, known as Moore's law [1]. Beginning in the late 1960s, the self-aligned, planar-gate silicon metal-oxide transistor created the foundation for a three-decade period of relentless and exponential progress in transistor miniaturization. Gordon Moore's prediction of transistor counts doubling every two years was remarkably prescient for this era, aided by Robert Dennard's scaling prescriptions for reliably manufacturing faster and smaller transistors [2].

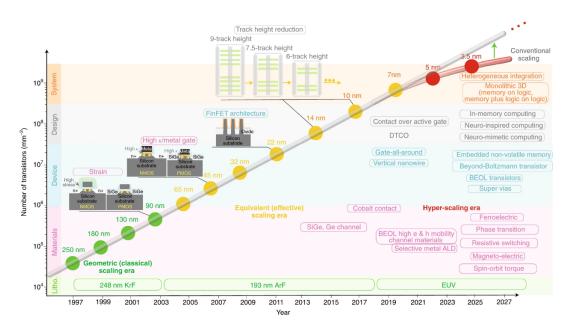

Figure 1-1: Figure 1 of [3]: eras of transistor scaling.

At turn of the millennium, this classical period of geometric scaling of transistors gave way to various manufacturing innovations which *equivalently* produced the same effect as the (slowing) rate of physical dimension scaling (see figure 1-1). It is believed that the current period of equivalent scaling of transistors using novel gate materials

and geometries is likely to give way to hyper-scaling i.e. functionality-aware beyond-Boltzmann transistors after 2025 [3]. And as transistor dimensions approach 10nm, variability and reliability effects begin to dominate its deterministic behavior [4]. For continued miniaturization, new avenues of research into materials, semiconductor physics and organic chemistry for emerging devices have materialized [5].

Secondly, the rise of data-driven learning algorithms have completely changed the way businesses function [6]. Due to the widespread proliferation of sensory devices and improvements in connectivity, the huge amounts of data gathered must be processed for ensuring quality of services. Furthermore, mobile devices (e.g. smartphones, tablets, sensor-nodes in sensor networks) function under limited bandwidth, battery and storage capacity, thereby requiring high energy efficiency in their computations [7].

Clearly, one way to harness the two trends going forward is to perform machine learning on emerging post-Moore devices with much lower energy footprints. This is especially useful for edge-based Internet-of-Things (IoT), where data is partially processed immediately after collection to reduce bandwidth usage and server workload. Emerging devices allow such computations to meet the strict energy constraints required. However, adapting emerging devices to the exact-computing paradigm is difficult due to their inherent variability [8]. As energy efficiency no longer scales with integration capacity, voltage reduction and near-threshold operation reduces power consumption at the expense of favorable signal-to-noise ratio (SNR) [9]. Finally, for conventional architectures such as CPUs and General-Purpose GPUs (GPGPUs), few applications today (including data mining and classification) have enough parallelism to completely utilize available hardware [10].

While challenges of using unreliable components have long been known [11], biology offers the most concrete inspiration. For example, our brain processes massive data  $(3.6 \times 10^{15} \text{ synaptic ops./s})$  with very slow and diverse neurons (typical firing rates are 10 - 100 Hz) while exhibiting tremendous energy efficiency (total power is about 12 W) [12]. Consequently, **brain-inspired computing** could provide the required robustness and scalability for continued improvements.

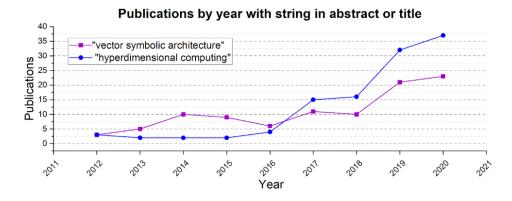

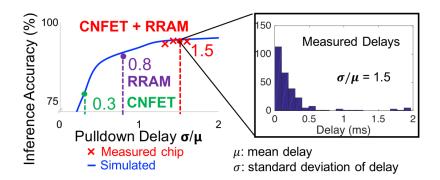

Hyper-Dimensional Computing (HDC) is one such nano-scalable paradigm [14], and is known to excel in body-based sensing/IoT applications [15]. Also known as Vector Symbolic Architectures (VSAs), it originated from a theoretical model of cognitive reasoning [16, 17]. It is motivated by the model that brains compute by transforming activation patterns of a large population of neurons (see figure 1-2 and the adjoining explanation). Hence, tolerance to variability is inherent: changes in activation of a few neurons do not affect the overall functionality. Its energy efficiency and robustness to noise (introduced by reduced supply voltage VDD) in the data path was demonstrated for language recognition [18, 19] and tested on fabricated systems based on emerging devices: a hybrid of carbon nanotube field-effect transistors (CNFETs) and resistive RAM (RRAM) memory in [20], and a CMOS/vertical-RRAM (VRRAM) implementation in [21]. [21] also demonstrated the robustness of HDC to inherent RRAM variability in endurance cycles and wafer-level device-to-device characteristics. Buoyed by the potential benefits offered by HDC, research has grown dramatically over the past few years (as shown in figure 1-3).

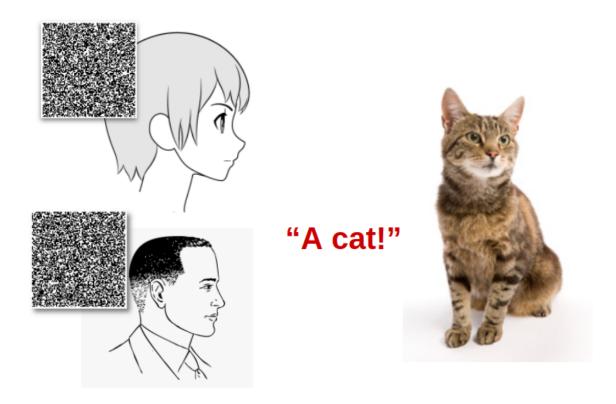

Figure 1-2: Neural-sampling hypothesis and Hyper-Dimensional Computing.

The neural sampling hypothesis [13] is a commonly-used model for neural computation and human cognition. The brain is thought to perform computations using probability distributions by transmitting neural activity samples between neurons, whereby the activity of a large population of neurons directly represent samples from the said distributions.

Consequently, even though two individuals may have *completely different and* random neural activations (illustrated here as a display of random noise) to a common stimulus (illustrated here as an image of a cat) due to the distinct ways in which their nerves and sensory tissues are interconnected in the sensory organs, the subsequent computations in their brains conducted by sampling, transforming and transmitting these sensory activations still results in identical and predictable behaviour (i.e. both identify the image as "a cat").

Hyper-Dimensional Computing represents the sensory activations in individuals as binary random vectors with *large number of bits* and abstracts the subsequent transformations as a sequence of operations from a collection of operators defined on large binary vectors.

Figure 1-3: Research literature related to HDC is increasing rapidly with time. Plot produced using data retrieved from dimensions.ai.

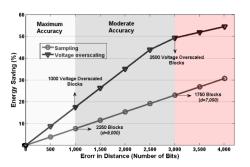

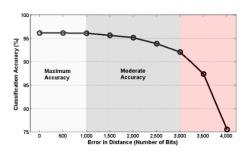

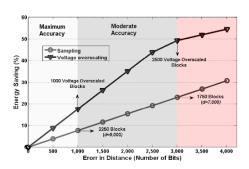

- (a) Figure 5 of [18]: Energy savings in Associative Memory by sampling and distributed VDD overscaling

- (b) Figure 3(b) of [18]: resistive Content Addressable Memory(CAM) arrays used in HDC associative search

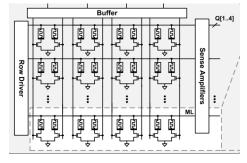

Figure 1-4: HDC is robust to representation errors and well-suited for in-memory hardware implementations.

(a) As shown in [18], robustness can be utilized by trading off tolerable representation errors for lower energy consumption. (b) Furthermore, the distributed and simple nature of HDC computations (especially associative search) makes it ideal for computing directly in or near memory cells.

However, as mentioned in section 2.4 in the next chapter, most research on HDC hardware are limited to specific datasets or applications and often have low data-width (eg. 32 bits on-chip to compute hyper-vectors containing thousands of bits in [20]), requiring large amount of time-multiplexing to simulate the complete machine of full width. Data-paths specific to applications other than language recognition have also been proposed [22], but a general HDC system is yet to be developed.

A general and widely programmable HDC architecture, which can be easily programmed to perform a variety of applications on different datasets, is crucial for evaluating HDC as a viable IoT and in-sensor computing paradigm [15]. This requires developing the fundamental architectural blocks that are configured and interconnected to produce a complete system. A comprehensive exploration of the above is the main goal of this work.

## Chapter 2

# Hyper-Dimensional Computing: preliminaries and a survey

Hyper-Dimensional Computing (HDC) emerged from a theoretical model of memory and cognition [17]. It is based on the fact that human brains compute by transforming activation patterns of a large mass of neurons. The set of activations are modeled as points in very high dimensional spaces ( $d \geq 1000$ ), and neural processing as transformations in this space. The central idea is that the mathematical properties of high-dimensional metric spaces – which pose a challenge to common machine learning algorithms [23] such as nearest-neighbor search [24], clustering [25] and regression [26] – can be used to explain cognitive functions like association of concepts, learning and recalling by analogy. Simple operations such as superposition, binding, permutation and their inverses form an algebraic field, giving (in principle) the same universality as algebra with numbers [27].

The HDC formalism can also be regarded as a mathematical abstraction of the memory functions exhibited by the human brain, similar to McCullouch and Pitts' artificial neurons formulated in 1943 [28]. There are numerous paradigms of similar or directly related origin, such as Holographic Reduced Representation [27], Binary Spatter Code [29] and Semantic Pointer Architecture [30]. Collectively, these models of human cognition are referred to as **Vector Symbolic Architectures (VSAs)** in the wider literature related to Psychology and Cognitive Neuro-science [31].

While there are several variants of HDC suited for different applications [14], this chapter provides the necessary preliminaries for the **Multiply-Add-Permute** (MAP) architecture most commonly used in the HDC hardware community [32]. The MAP architecture is the only HDC variant studied in this dissertation. After a brief introduction to the basic concepts and a demonstration of its use for two exemplar applications, a survey of published literature related to hardware designs capable of supporting multiple HDC algorithms concludes this chapter.

#### 2.1 Orthogonality in high dimensions

Hyper-dimensional Computing defines random high-dimensional vectors (d > 1000) as its fundamental data type [16, 14]. It is a **holographic** computing framework: unlike arithmetic over numbers, no vector component contains more information than any other. Although vectors with elements from any algebraic field can be used (see Table I of [14]), we will consider only binary vectors as it results in the simplest hardware.

To compare vectors, a distance metric is required. Hamming distance (denoted by  $d_H(a,b)$ ) is the number of dissimilar elements between vectors a and b. Two binary vectors x and y of dimension d are said to be orthogonal if  $d_H(x,y) = d/2$ . This definition is more familiar in bipolar code (0-valued elements replaced by integer -1): orthogonal x and y have zero inner product,  $\langle x, y \rangle = 0$ .

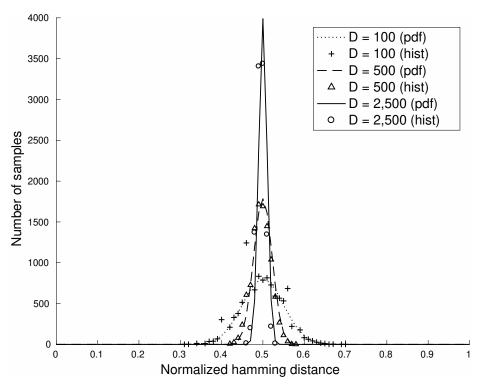

Figure 2-1: Orthogonality in High Dimensions.

Shown histogram (hist) and scaled probability density function (pdf) of normalized hamming distances for 10,000 pairs of random binary vectors with varying dimension d. For ease of plotting, the normal approximation of the binomial probability distribution is used. All vectors are generated uniformly and distance is normalized by d. Note the sharper concentration around 0.5 as vector dimension d increases.

The underlying principle of HDC is almost certain orthogonality in high-dimensional spaces. This is also called "almost-sure orthogonality", "pseudo-orthogonality", "near-orthogonality" and "orthogonality in high dimensions" in the literature. For a rigorous demonstration, see that if vectors x and y are chosen independently and uniformly from  $\{0,1\}^d$  (i.e. probability of any bit being 1 is p=1/2), their hamming distance is binomially distributed:  $d_H(x,y) \sim Bin(d,p=1/2)$ . Fig. 2-1 plots a histogram (hist) of

$d_H(x,y)$  normalized by dimension d for 10,000 randomly-generated pairs (x,y). It also plots the density function (pdf) for Normal Approximation  $\mathcal{N}(dp,dp(1-p))$  of Bin(d,p) scaled to have an area equalling sample size 10,000. The Normal Approximation helps in plotting and is very accurate for high dimensions: using the Berry-Essen bound (Theorem 10.4 in [33]) for  $X \sim Bin(d,p)$ ,  $Y \sim \mathcal{N}(dp,dp(1-p))$ , p = 1/2 we have that  $\forall t \in \mathbb{R}$ :

$$|\Pr(X \le t) - \Pr(Y \le t)| \le \frac{4 - 8p(1 - p)}{5\sqrt{dp(1 - p)}}$$

Using p = 1/2 and for dimension  $d \ge 1024$ , the maximum error in cumulative distribution  $(\max_{0 < t < 1} |\Pr(X \le t) - \Pr(Y \le t)|)$  is as most 0.025.

Given that the hamming distance between random vectors is binomially distributed, it can be shown that (Theorem 1 of [34]):

$$\Pr\left[\left|\frac{d_H(x,y)}{d} - \frac{1}{2}\right| \ge \epsilon\right] < 2e^{-2d\epsilon^2}$$

(2.1)

Only high dimensions (d > 1000) result in a meaningful right-hand side in equation 2.1 [35]. Then random vectors x and y have normalized distance very close to 0.5. The exponential drop in probability beyond  $\epsilon$ -deviation from the mean is the crucial property exploited in HDC algorithms. This phenomenon is a consequence of concentration of functions in high-dimensional geometry. For the interested reader, [36] provides an excellent treatment from a non-asymptotic viewpoint. Chapter 5 uses related phenomena to develop efficient architectures for HDC.

All high-dimensional vectors used in a given computation will be called **hyper-vectors**. When the context is obvious, hyper-vectors and vectors will be used interchangeably.

## 2.2 The Multiply-Add-Permute (MAP) paradigm of Hyper-Dimensional Computing

To simplify the formulation of HDC operations, the following conventions will be adopted throughout the dissertation:

- The starting hyper-vectors are binary and generated uniformly at random.

- Unless stated otherwise, bipolar hyper-vectors are adopted instead of binary hyper-vectors, where -1 replaces 0 as the hyper-vector element. The main advantage of this adoption is that superimposed bipolar hyper-vectors (defined below) preserves the elements' mean value of 0.

In addition to high dimensionality, a set of operations are required that preserve near orthogonality. Although there are many sets of operations with equivalent performance (see Table I of [14]), the **Multiply-Add-Permute (MAP)** framework is most suitable as it uses *binary* hyper-vectors – the easiest to implement in digital logic. The following operations are fundamental to the MAP paradigm:

- Multiplication/Binding is useful for forming associations among related hyper-vectors. X and Y are bound together to form  $C = X \oplus Y$  that is nearly orthogonal to both its constituents. It is implemented as element-wise XOR  $x_i^{\wedge}y_i$  of two binary hyper-vectors, and as the negative of the product  $-x_iy_i$  of two bipolar hyper-vectors.

- Addition/Superposition is the primary conjunctive operation. Based on Hebbian learning [27], the goal is to find a hyper-vector z representing the set of operand hyper-vectors  $\{x_1, x_2, ... x_n\}$ . It is denoted by  $z = x_1 + x_2 + ... + x_n$  and implemented by performing element-wise integer sum of operand hyper-vectors.

- Thresholding each element of a hyper-vector X at the element-wise mean (0 for bipolar) is denoted by z = [X]. An element of the thresholded hyper-vector is +1 if the corresponding element of X is non-negative; it is -1 otherwise. Note that thresholding is idempotent i.e. [X] = X for all bipolar vectors X. Thresholding is almost always performed after superposition of multiple bipolar hyper-vectors  $[x_1 + x_2 + \dots x_n]$  so that the output hyper-vector is bipolar, formed by element-wise majority of the superimposed hyper-vectors  $x_1, x_2 \dots x_n$ .

- **Permutation** is a unary operation such that the permuted hyper-vector denoted by  $\rho(x)$  is nearly orthogonal to its operand x. The choice of permutation does not matter as long is it has no fixed points so that the period is the largest value possible: the HDC dimension d. Circular shift (in either direction) is a widely adopted permutation. Hyper-vector x permuted n times is written  $\rho^n(x)$ .

Associative search. As Fig. 2-1 shows, it is very rare for random hyper-vectors to deviate much from orthogonality. The addition operation generates non-orthogonal hyper-vectors from random operand hyper-vectors. This allows one to capture semantics between hyper-vectors as any significant deviation from orthogonality among two hyper-vectors implies some dependency. In the final stage of all HDC algorithms, an associative search is performed among all possible solution hyper-vectors to find the closest match to the query hyper-vector calculated from input bipolar hyper-vectors using MAP operations.

Following from their definitions [16], the four fundamental MAP operations in HDC have the following laws governing the relationships among them:

- 1. Superposition and binding are commutative: for all vectors A, B we have A+B=B+A and  $A\oplus B=B\oplus A$ .

- 2. Superposition and binding are associative: for all vectors A, B, C we have (A+B)+C=A+(B+C) and  $(A\oplus B)\oplus C=A\oplus (B\oplus C)$ .

- 3. Binding can be inverted: for all vectors A and B we have  $A \oplus A \oplus B = B$

- 4. Permutation distributes over binding: for all integers  $n \ge 1$ , the following holds true for all vectors  $A, B: \rho^n(A \oplus B) = \rho^n(A) \oplus \rho^n(B)$ .

- 5. Permutation distributes over superposition and thresholding: for all integers  $n \geq 1$ , the following holds true for all vectors  $A, B: \rho^n(A+B) = \rho^n(A) + \rho^n(B)$ , and for all vectors C we have that  $\rho^n([C]) = [\rho^n(C)]$ .

- 6. Binding distributes over superposition and thresholding: For all vectors A, B, C the following hold:  $A \oplus [B + C] = [(A \oplus B) + (A \oplus C)]$  and  $A \oplus [C] = [A \oplus C]$ .

#### 2.3 Examples of computing with hyper-vectors

HDC has been employed in a range of applications in supervised classification [37]. Prominent examples include human-sensing and biomedical signal processing [38, 39], classification using multimodal sensor fusion [40] and DNA pattern matching [41, 42]. Other notable works in the wider application space include using hypervectors to ensure trustable service discovery in highly decentralized and dynamic networks [43], predicting onset of short-term [44] and long-term [45] seizures in patients, performing factorization of integers using resonator networks [46], activity recognition of subjects by classifying their radar images [47], characterization of circuit reliability in state-of-the-art technology node [48], constructing a "proof-of-use" blockchain [49], electrocardiogram-based emotion recognition when subjects are in motion [50], guaranteeing privacy in distributed learning systems [51], using HDC and feed-forward neural network to recognize driving style for Advanced Driver Assistance Systems (ADAS) [52], building recommender systems [53], efficient communication via noisy channels and near-channel classification [54], classification of massive DNA methylation data for predicting cancer [55] and for dynamic vision sensing [56].

Several papers have proposed using principles of HDC such as orthogonality in high dimensions in other fields of study. Most prominently, proposals of hybrid HDC-neural network systems and machine learning algorithms with VSA-inspired learning cost functions have received attention. For example, in [57], a hybrid HDC-neural network system for storage and inference on knowledge graphs was proposed based on concentration of measures in high dimensions. HDC was used to implement the back-end processing pipeline in the vision engine for active perception in robots [58] and training multiple neural networks simultaneously in a single model [59]. In [60], a neuro-symbolic system constructed as a hybrid of neural networks and VSA was used to solve Raven's progressive matrices (a common exercise present in Intelligence Quotient tests). Most recently, [61] used the orthogonality in high dimensions as

a training objective to train Convolutional Neural Networks (CNN) that can learn hyper-vector representations of images and store it in a associative memory. The memory-augment CNN supported by orthogonality can dynamically expand to learn new image categories; experiments on large data sets of natural images show it performs better than state-of-the-art CNN models. Use of reinforcement learning to automatically search for the HDC algorithm that results in the best accuracy on a given classification task has also been proposed [62].

All applications of HDC use the symbolic nature of its computations. The idea is to use the  $e^{-\Theta(t^2)}$  drop in probability beyond a t-deviation from the mean normalized distance between high-dimensional random vectors (as demonstrated in section 2.1) to encode semantic relationships. The following sub-section illustrates this with a few examples.

#### 2.3.1 Encoding semantics with random hyper-vectors

Perhaps the foremost feature of HDC that distinguishes it from other algorithms is its symbolic nature of processing. HDC is related to symbolic models of computation – like connectionist models proposed and studied in late 1980s (the interested reader is referred to chapters 1-3 of [27] for a detailed survey). Symbolic computation begins by defining **symbols** that represent entities from the universe where the reasoning is to be conducted. For HDC, a randomly generated hyper-vector is assigned to each such entity, and the collection of all entity-vector pairs is *stored for the entire duration of the computation*.

**Set membership**. The most fundamental semantic relationship is membership of entities in a collection. Using random hyper-vectors to represent entities and using superposition to represent a collection of entities, HDC provides an easy algorithm to test set membership. For example, suppose there are 26 entities which are represented by random (bipolar) hyper-vectors  $A, B, \ldots Z$ . Then, to represent the set  $\mathbb{S} = \{A, B, C\}$  one can simply superimpose the hyper-vectors of its members:  $\mathcal{S} = [A + B + C]$ .

To test membership of  $A, B, \ldots Z$  in  $\mathbb{S}$ , check whether the hamming distance between their representation hyper-vectors  $d_H$  is smaller than d/2 by a significant margin. Thus for non-members such as X, we have that  $d_H(X, \mathcal{S}) \approx d/2$  with very high probability because of orthogonality of random hyper-vectors in high dimensions. For members like A, we have  $d_H(A, \mathcal{S}) = d_H(A, [A+B+C])$  which is close to  $d_H(A, A) = 0$  (see [16] for a demonstration).

Analogical reasoning. Using hyper-vectors as symbols also allows representing analogical structures and reasoning about them. For example, consider a system capable of answering "What is the Dollar of Mexico?". In order to get a reply to this question, it is necessary to infer the entity that bears the same relation to "Mexico" as "Dollar" does to "United States". If "United States" and "Mexico" are represented by random hyper-vectors US and MEXICO and their respective currencies by hyper-vectors DOLLAR and PESO, then the hyper-vector CURRENCY  $\triangleq$  [US  $\oplus$  DOLLAR + MEXICO  $\oplus$  PESO] represents the collection of country-currency analogies for "United States" and "Mexico" [63]. In other words, the hyper-vector CURRENCY encodes the set of (unordered) pairs

formed from the four entities "United States", "Dollar", "Mexico" and "Peso":

"Currency"

$$\triangleq \{ \text{("United States", "Dollar"), ("Mexico", "Peso")} \}$$

(2.2)

One may now compute the "Dollar" of "Mexico" by seeking entity X such that ("Mexico", X)  $\in$  "Currency" in equation 2.2. This can be solved as follows:

$$\begin{split} & d_{\mathrm{H}}(X \oplus \mathtt{MEXICO}, \mathtt{CURRENCY}) \approx 0 \\ \Longrightarrow & d_{\mathrm{H}}(X \oplus \mathtt{MEXICO} \oplus \mathtt{MEXICO}, \mathtt{CURRENCY} \oplus \mathtt{MEXICO}) = d_{\mathrm{H}}(X, \mathtt{CURRENCY} \oplus \mathtt{MEXICO}) \approx 0 \\ \Longrightarrow & X = \underset{x \in \{\mathtt{US},\mathtt{MEXICO},\mathtt{DOLLAR},\mathtt{PESO}\}}{\arg\min} d_{\mathrm{H}}(x, \mathtt{MEXICO} \oplus \mathtt{CURRENCY}) \end{split}$$

Of the four entities defined so far, following from the properties of HDC operations in section 2.2 one can conclude that X = PESO. This deduction is shown below:

$$\begin{split} & d_{H}(X, \texttt{MEXICO} \oplus \texttt{CURRENCY}) \approx 0 \\ \Longrightarrow & d_{H}(X, \texttt{MEXICO} \oplus [\texttt{US} \oplus \texttt{DOLLAR} + \texttt{MEXICO} \oplus \texttt{PESO}]) \approx 0 \\ \Longrightarrow & d_{H}(X, [\texttt{PESO} + \texttt{MEXICO} \oplus \texttt{US} \oplus \texttt{DOLLAR}]) \approx 0 \\ \Longrightarrow & d_{H}(X, [\texttt{PESO} + (random \ hyper-vector)]) \approx 0 \\ \Longrightarrow & X = \texttt{PESO} \end{split}$$

The final step in equation 2.4 above determines which of the four defined entities that are assigned random hyper-vectors in this problem (i.e. "United States", "Dollar", "Mexico" and "Peso") is a member of the transformed set

Since triples are not a part of the four defined entities, "Peso" is the final solution.

Hyper-Dimensional Computing has been used to represent a variety of data structures such as lists, sequences, trees and Turing machines [27, 64]. The method of solving for the solution X consists of systematically transforming the set "Currency" to a new set of symbols by applying MAP operations from section 2.2 so that only the correct solution among all the recognized entities is its member. Maintaining the collection of assigned hyper-vectors representing all the defined entities, and associatively searching the transformed vector (like MEXICO  $\oplus$  CURRENCY) for the closest entity hyper-vector are common features of all HDC algorithms.

The next sub-section introduces language recognition using HDC operations and orthogonality among random hyper-vectors.

#### 2.3.2 Language Recognition using HDC

Language recognition using HDC was a seminal work [65] that inspired a subsequent wave of research on using HDC for supervised classification tasks. This application also illustrates how the symbolic nature of HDC and orthogonality in high dimensions may be employed for a supervised classification task.

HDC language recognition was first performed on the EUROPARL corpus of 21 European languages transliterated in the Latin alphabet [19, 65]. The EUROPARL corpus was extracted from the proceedings of the European parliament. Due to its diplomatic nature, the sentences are longer and use larger vocabulary than in everyday use. Therefore, the EUROPARL corpus is considered to be a difficult dataset for language recognition and translation.

The n-gram baseline model. The goal is to recognize the language from a short sentence of text transliterated in the Latin alphabet. Written languages can be modeled as a probability distribution on character sequences or word sequences of finite length n, called n-grams [66]. While more sophisticated models such as dictionary of words, phrases, etc. can be used, studies indicate they increase model complexity with negligible gains [67, 68]. Since the language recognition algorithm is likely to be a front-end of a complex language-processing pipeline, having a complicated and large recognition model effectively nullifies the advantages of a simple and lightweight front-end. While training a language, raw n-gram frequency counts are generated from a large corpus from that language and iteratively smoothened [69] to remove outlier artifacts. The resulting n-gram distribution is the trained language model. The steps are repeated for a test query, and the trained model with the closest distribution is the language prediction.

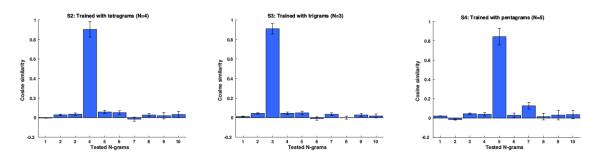

HDC algorithm for n-grams. The first step is to assign random hyper-vectors to all meaningful entities in this task. Assigning hyper-vectors for each character of the Latin alphabet and a few punctuation marks should suffice. In [19] and [65], HDC dimension d = 10000 was used. Using smaller hyper-vectors with d = 2048 produces reasonable accuracy [32]. The HDC algorithm uses the assigned character hyper-vectors to encode the training text of a language and generate a *single hyper-vector* for each language.

A direct equivalent of frequency counting is the superposition of hyper-vectors representing each occurring n-gram in the text. Permutation and binding are used to generate an n-gram vector from constituent character hyper-vectors. For example, the 3-gram "abc" is encoded as  $V_{abc} \triangleq \rho^2(V_a) \oplus \rho(V_b) \oplus V_c$ , where  $V_z$  is hyper-vector representing character or character sequence z. From properties of binding and permutation in section 2.2, deduce that all distinct n-gram and character hyper-vectors are nearly orthogonal to each other.

Hence, the language hyper-vector is the thresholded superposition of all n-gram hyper-vectors from the training text. The test hyper-vector is computed similarly, and the language with closest hyper-vector (i.e. the smallest hamming distance) is returned as the prediction. Since the superimposed language vector is in the linear space spanned by the set of all n-gram vectors, the class with the closest n-gram distribution from baseline equivalently has the smallest distance in HDC.

HDC has an accuracy of 96.7% against a baseline of 97.1% [19] for n=4 and HDC dimension d=10000. However, it is an online algorithm requiring a *single iteration* though the entire training text. The deviations from orthogonality in high dimensions (in fig. 2-1) automatically smoothen the superimposed multi-set of n-grams, obviating the need for iterations over a possibly large training corpus. Finally, the HDC model

size (1 vector/class) is fixed with n-gram size but grows exponentially in the baseline. Indeed, for n = 4, the HDC model is **20X smaller** than the baseline model.

#### 2.4 A summary of hardware designs for Hyper-Dimensional Computing

Several hardware designs have been proposed in the Hyper-Dimensional Computing community. Following the demonstration of associative memory's robustness to noise (introduced by reduced VDD) in the HDC data path for language recognition [18, 19], a hybrid design of Carbon Nanotube Field-Effect Transistors (CNFETs) and Resistive RAM (RRAM) memory in [20] was fabricated and tested for EUROPARL language recognition. A CMOS/vertical-RRAM (VRRAM) implementation in [21] demonstrated the robustness of HDC to inherent RRAM variability in endurance cycles and wafer-level device-to-device characteristics. In [70], a Phase-Change Memory (PCM) based Associative Memory and Encoding module with digital CMOS peripherals was simulated for EUROPARL language recognition.

However, all HDC hardware designs fabricated and measured so far are tailor-made for a specific application or data set. Both [21] and [20] are hard-wired to perform only language recognition on a specific dataset; these chips cannot be used for other datasets and applications. The data path simulated in [70] and the chip illustrated in [71] can only perform a 2-min-term approximation of the complete n-gram in language recognition, and can only compute n-grams from a single data stream such as characters in a single text. Furthermore, its encoder contains CMOS digital logic which was simulated in software – only the PCM memory blocks were measured in hardware. Designs [21, 20] also have low data-width (32 bits), requiring large amount of time-multiplexing to simulate the complete hyper-vector in full width (> 1000 bits). Data paths specific to applications other than language recognition have also been proposed for future fabrication [22].

A great majority of HDC hardware literature do not perform the *complete HDC algorithm* on manufactured Application-Specific Integrated Circuits (ASICs) designed specifically for HDC. For example, [72] implements a neural network in software augmented by a key-value Associative Memory in PCM Content-Addressable Memory (CAM) on chip. Ferro-Electric Field Effect Transistors' (FEFET) measured performance characteristics were used to simulate the efficiency of a FEFET-based CAM cell to implement an Associative Memory for HDC in [73]. While [74] has wide applicability due to its instruction-based architecture, its results are simulation-only: it performs simulations on a placed and routed design for 3 applications. However, it is unclear that the routed design is ready for manufacturing as the reported core-area utilization of 70% is extremely high for most technology nodes. The paper [74] does not provide results of manufacturing Design Rule and Electrical Rule checks that can ascertain its manufacturability.

In some papers such as [39, 75], direct measurements on a Field-Programmable Gate Array (FPGA) programmed with the HDC algorithm, instead of a manufactured

ASIC implementing it, are reported. While FPGAs are a great resource for prototyping an application-specific hardware design before manufacturing, its measured energy and performance characteristics often differ from that of ASICs by a factor of  $10-50\times$  (for example, see table 3.1.5 discussed in the next chapter).

Most hardware papers study specialized designs *synthesized* into a circuit of logic gates from a standard library. Performance and energy estimates are reported after profiling an application on a compiled program that simulates the synthesized circuit. For example, in [32] a complete and widely-programmable HDC data path was synthesized and profiled by performing simulations of several supervised classification tasks. Similarly, [76, 42, 77] used simulations on synthesized circuits for specialized HDC hardware designs performing supervised classifications on public data sets.

A few papers report measurements of HDC algorithms programmed and run on classical architectures such as CPUs [78, 79] (including on ultra-low-power CPU cores [80, 81, 82]) and general-purpose GPUs [83, 45, 84, 85]. However, as described in section 3.1.5 later on, classical architectures have orders of magnitude higher delay and energy costs than ASICs implementing the same circuit.

A general HDC system capable of supporting multiple applications and HDC algorithms is yet to be architected, designed, fabricated and measured. Such a general HDC architecture, which can be easily programmed to perform a variety of applications on different datasets, is crucial for evaluating HDC's potential as a viable paradigm for energy-constrained environments [15]. This requires developing the fundamental architectural blocks that are configured and interconnected to produce a complete system. Furthermore, actual measurements from a digital CMOS chip in a leading technology node is necessary to establish the anticipated benefits and provide a foundational hardware benchmark for comparing performance benefits of future chips using emerging non-volatile memory such as RRAMs, PCMs, etc.

A comprehensive exploration of such generally-programmable and efficient architectures for HDC is the object of study in this dissertation. The next chapter compares efficiency of HDC on conventional architectures to deduce the likely macroscopic properties of the most suitable architectural family for HDC.

## Chapter 3

# Principles of constructing an efficient architecture for Hyper-Dimensional Computing

This chapter develops of an *efficient and programmable* architecture for implementing Hyper-Dimensional Computing in custom silicon. The objective is to make the architecture as energy-efficient as possible without sacrificing reasonable programmability. An instrumentation study of HDC and conventional algorithms on embedded CPU and GPU reveals sources of inefficiency when deploying HDC on conventional hardware. Guided by these results and a careful analysis of the structure of HDC algorithms, the prominent macro-properties and most appropriate architectural style are deduced.

The core motif of this chapter is the definition of the *Generic class* of HDC algorithms, and the consequential properties of an efficient architecture supporting it. The idea is that although this class is smaller than the class of all possible HDC algorithms, it contains all known HDC algorithms and is rich enough to likely contain future expert-designed algorithms (discussed further in section 3.3.2). Furthermore, the architecture developed for the Generic class can be easily extended to support more complicated HDC algorithms. After an exposition on the Generic architecture, these extensions are discussed in section 4.2.3 of the next chapter.

#### 3.1 Profiling HDC on embedded CPU and GPU

As noted in section 2.4, a few papers measure the energy and performance of HDC algorithms on CPUs, GPUs and FPGAs. However, no detailed instrumentation on classical architectures, particularly embedded CPU cores (eCPUs) and embedded general-purpose GPUs (eGPUs), has been conducted to date. Instrumenting the execution of a competitive HDC model and comparing with conventional algorithms for the same task will reveal inadequacies of classical architectures for performing efficient HDC. For this comparison, the first step was to decide a set of benchmarks.

#### 3.1.1 Benchmark applications for instrumentation

Since HDC has been widely used for supervised classification [37], 3 popular datasets for supervised classification were chosen for the instrumentation study. Listed in table 3.1.1, these algorithms differ in the amount of available parallelism and belong to different tiers of success by best-known HDC algorithms.

| Application                            | ML algorithm | HDC $(d = 2048)$ |

|----------------------------------------|--------------|------------------|

| EMG Hand-gesture Recognition (EMG)     | 95.32% (SVM) | 95.13 %          |

| Language Recognition (LANG)            | 97.40% (kNN) | 90.82 %          |

| Hand-written digit recognition (MNIST) | 99.13% (CNN) | 80.28 %          |

Table 3.1: Inference accuracy of the instrumented algorithms.

1. **EMG hand-gesture recognition (EMG)** classifies electromyography signals sampled from an electrode array attached to the skin of a subject into a set of hand-gestures. The variations in electric and magnetic fields caused due to flexion and relaxation of muscle to produce a gesture changes the electric potential of the electrodes, which are used to recognize hand gestures.

Support Vector Machines (SVM) are typically used for the EMG by the machine learning (ML) community: more capable algorithms such as Multi-Layer Perceptrons and Convolutional Neural Networks are expensive to train with negligible accuracy gains [86]. A multi-class SVM was profiled for EMG hand-gesture recognition using the dataset of [38].

EMG has been the most successful application of HDC till date [87, 38]: HDC has higher accuracy and energy efficient than ML algorithms [86] and allows online learning and adaptability to different subjects [88, 39]:

2. Language recognition (LANG) was performed on the EUROPARL corpus <sup>1</sup> of 21 Indo-European languages transliterated in the Latin alphabet [19] (as explained in section 2.3.2).

LANG was one of the first applications of HDC to supervised classification and has been widely used as a benchmark in a majority of subsequent work [65].

3. Hand-written digit recognition (MNIST). The MNIST dataset of hand-drawn digits is a popular dataset used for evaluating ML algorithms, where  $28 \times 28$  greyscale pixel-array are used to recognise the drawn digit.

<sup>&</sup>lt;sup>1</sup> The EUROPARL corpus was extracted from the proceedings of the European Parliament. Due to its diplomatic nature, the sentences are longer and use larger vocabulary than normally used. Thus, EUROPARL is believed to be a difficult dataset for language recognition and translation.

This instrumentation study used a beta release [89], containing 23 languages for training but 21 languages for testing. The 2 additional trained languages Afrikaans and Norwegian are absent from the most recent version [90]. Since Afrikaans is derived from Dutch and Norwegian is similar to Danish and Swedish, their presence as 2 additional trained classes reduces testing accuracy from 93.6% to 90.8% of table 3.1.1. However, since only inference was instrumented, updating the training EUROPARL dataset to the most recent version would negligibly affect results presented here.

MNIST is an elementary dataset in computer vision. It was chosen to represent the fact that known HDC algorithms do not perform well on computer vision applications, especially when using raw pixel values. To evaluate HDC on MNIST, a feature-value superposition (see section 3.3.1) was used on the gray-scale frames [91]. Since the pixel values are bimodal, its values are thresholded first to a 0 or 1 before mapping to 2 random hyper-vectors.

A large number of ML models exist with testing accuracy > 99.5% on MNIST. Usually a committee of a few dozen deep Convolutional Neural Networks (CNNs) are required to achieve such low error rates. However, in this experiment, a single and shallow CNN was profiled for MNIST since instrumenting dozens of state-of-the-art deep CNNs requires access to supercomputing facilities or prohibitively high compute time on commodity processors. The profiled CNN has 2 convolutional layers with 32 kernels of dimensions  $3 \times 3$  and ReLU activation, followed by  $2 \times 2$  max-pooling layer and finally a 128-node dense layer (about half a million learned parameters). This CNN is much smaller than the best MNIST classifier but has comparable accuracy (99.13% vs 99.77% for [92]).

Unlike HDC algorithms which need a single pass for training; SVM, kNN and CNNs require multiple iterations – the total number of which depends on initial values of parameters and hyper-parameters. Therefore, only inference accuracy on the test dataset after loading a pre-trained model was profiled.

#### 3.1.2 Hardware setup for instrumentation

The NVIDIA Jetson TX2 embedded platform [93] was used to instrument the compiled codes for HDC and its ML counterparts. The Jetson TX2 platform contains a 256-core NVIDIA Pascal eGPU, an ARM Cortex A57 eCPU with 4 cores and 2 megabyte (L2) cache, and 8 gigabytes of 128-bit DRAM (DDR).

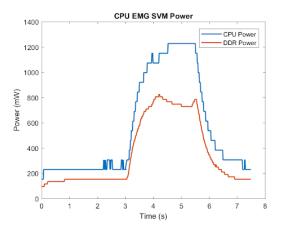

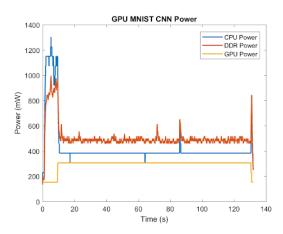

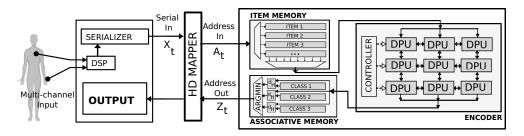

Jetson TX2 has an on-board power monitor INA226 [94] used for energy and power measurements. The INA226 power monitor measures power drawn from the separate voltage supplies of CPU, GPU and DDR. This makes it possible to quantify the contribution of each component to the total measured energy/prediction of the profiled algorithm. Power traces are collected from a few seconds before the actual execution of test code begins, so that the start and end time on the traces are clearly visible. Estimates of energy/prediction do not include the initial standby energy. Fig. 3-1 shows an example of power measurement trace for eCPU and eGPU. The eCPU trace (fig. 3-1(a)) illustrates that the power consumption profile is similar to charging and discharging a large capacitor. For the eGPU trace (fig. 3-1(b)), the initial burst of CPU-only activity is followed by a long duration where all 3 components are active – this was observed in all measured traces for eGPU experiments.

#### 3.1.3 Instrumentation results on eCPU

The main goal here to gain a *preliminary understanding* of bottlenecks in classical architectures for doing HDC, by comparing HDC codebase's instrumentation results

- (a) The power trace for running SVM for EMG on (b) The power trace for running CNN for MNIST ARM Cortex A57.

- on ARM Cortex A57 & Pascal GPU system.

Figure 3-1: Examples of measured power trace on eCPU and eGPU.

with that of conventional ML algorithms.

**Target code:** For LANG, HDC and kNN algorithms were written in C [19]. The text-histograms for kNN was generated using a standard C hash function [95]. For EMG, the HDC algorithm [87] was written in C. SVM was implemented in Python using the LIBSVM library [96]. For MNIST, both HDC and CNN algorithms were written in C. CNN's C code and the pre-trained model were obtained from [97].

The following quantities were estimated at runtime:

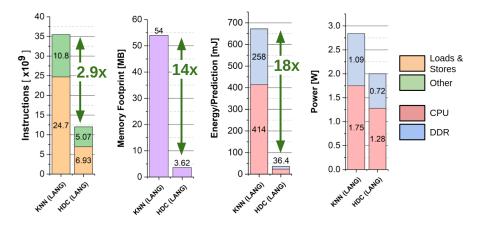

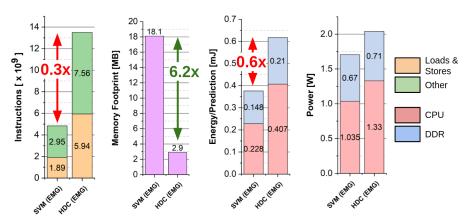

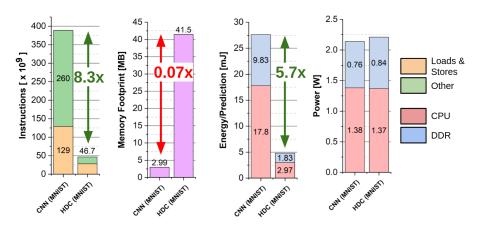

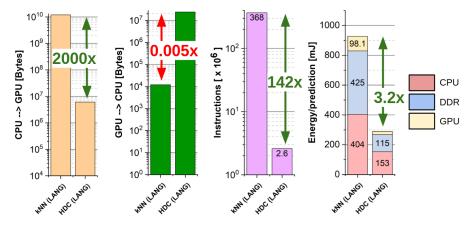

- CPU instruction count: the total number of instructions retired by the program during execution. Hardware performance counters were sampled using the perf-stat program [98] at about 1000 samples/s. Estimates from 10 independent runs were averaged to reduce empirical variance and the impact of interference by other processes and the operating system.