# **Novel Non-Volatile Memory Devices and Applications**

Tsegereda Esatu

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2023-97 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2023/EECS-2023-97.html

May 11, 2023

Copyright © 2023, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Novel Non-Volatile Memory Devices and Applications

By

#### Tsegereda Esatu

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Ming C. Wu Professor Junqiao Wu

Spring 2023

# Novel Non-Volatile Memory Devices and Applications

Copyright ©2023

by

Tsegereda Esatu

#### Abstract

#### Novel Non-Volatile Memory Devices and Applications

By

#### Tsegereda K. Esatu

Doctor of Philosophy in Engineering Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

The performance of semiconductor logic and memory devices has improved significantly with advancements in complementary metal-oxide-semiconductor (CMOS) manufacturing technology to miniaturize transistors, resulting in increased integrated circuit ("chip") processing speed, energy efficiency, and cost per function. The proliferation of the Internet of Things (IoT) and the generation and processing of large data sets, commonly known as "big data," have increased demand for non-volatile (NV) information storage that can be embedded with energy-efficient logic switches so that certain computational tasks can be performed in the memory itself. To achieve ultra-low-power electronics, alternative switching devices that can be operated with much smaller voltages than CMOS transistors are required. Micro-electro-mechanical (MEM) switches have been shown to be promising for ultra-low-power digital computing applications due to their negligible  $I_{OFF}$  and abrupt switching behavior across a wide range of operating temperatures. Therefore, they have attracted growing interest for embedded energy-efficient logic and NVM applications. In addition to energy efficiency, it is also crucial to maintain the security and confidentiality of information collected and shared by IoT devices. To address this issue, memory devices that can store data and function as hardware security key generator are desirable. Emerging Resistive Random Access Memory (ReRAM) is a promising technology for hardware security applications due to its inherent variability.

This dissertation focuses on novel non-volatile memory devices and their applications. First, logic MEM switches are demonstrated to be operable as NV memory devices using controlled welding and unwelding of the contacting electrodes. Reprogrammability with consistently low programmed state resistance, and excellent (essentially infinite) retention time at elevated temperature, are experimentally demonstrated. These results indicate that MEM switches are promising for low-cost implementation of ultra-low-power integrated systems.

Next, this dissertation presents a prototype MEM switch design incorporating a floating gate (FG) for non-volatile charge storage. The FG-MEM NV switch potentially can achieve much longer data retention time than a conventional floating-gate MOS transistor, since there exists an air gap between conductive electrodes when the switch is in the OFF-state. Initial experimental results and FG-MEM NV switch design improvements are discussed.

Finally, this dissertation proposes a new method of generating Physically Unclonable Function (PUF) encryption keys that leverage the inherent random variability of ReRAM device

programming time, for hardware security applications. The design and operation of a ReRAM device is presented, followed by a detailed discussion of the PUF key generation scheme. The randomness and reliability of the generated keys are then evaluated. The randomness of the ReRAM-based PUF is found to be of high quality compared to previous PUF implementations. Therefore, ReRAM technology enables the incorporation of both NVM and PUF functions within the same chip.

To my family,

for their endless love and support

# **Contents**

| Co    | ntents                                                                | ii |

|-------|-----------------------------------------------------------------------|----|

| Lis   | t of Figures                                                          | iv |

| Lis   | t of Tables                                                           | ix |

| 1 Int | roduction                                                             | 1  |

| 1.1   | Brief History and Evolution of Integrated Circuits                    |    |

| 1.2   |                                                                       |    |

| 1.3   |                                                                       |    |

| 1.4   |                                                                       |    |

| 1.5   | · ·                                                                   |    |

| 1.6   | References                                                            | 10 |

| 2 A F | Reprogrammable MEM Switch Utilizing Controlled Contact Welding        | 13 |

| 2.1   | Introduction                                                          |    |

| 2.2   |                                                                       |    |

| 2.3   | •                                                                     |    |

| 2.4   | E .                                                                   |    |

| 2.5   | ±                                                                     |    |

| 2.6   | 1 6                                                                   |    |

| 2.7   | · · · · · · · · · · · · · · · · · · ·                                 |    |

| 2.8   | Summary                                                               | 34 |

| 2.9   | References                                                            | 34 |

| 3 Inv | restigation of Floating-Gate MEM Switch for Non-Volatile Memory       |    |

| Ap    | plication                                                             | 36 |

| 3.1   | Introduction                                                          | 36 |

| 3.2   | Proposed FG-MEM NV Switch Design                                      | 37 |

| 3.3   | Experimental Investigation of FG-MEM NV Switches                      | 40 |

| 3.4   | FG-MEM NV Switch Design Improvements                                  | 45 |

| 3.5   | Summary                                                               | 45 |

| 3.6   | References                                                            | 45 |

| 4 Hig | ghly Reliable and Secure PUF Using Resistive Memory Integrated into a |    |

| 28n   | im CMOS Process                                                       | 48 |

| 4.1   | Introduction                                                          | 48 |

| 4.2    | ReRAM Structure and Operation                        | 50 |

|--------|------------------------------------------------------|----|

| 4.3    | Inherent Stochastic Behavior of ReRAM for PUF        | 55 |

| 4.4    | PUF Generation Scheme Using Switching Time Variation | 58 |

| 4.5    | PUF Randomness Evaluation                            | 63 |

| 4.6    | PUF Performance Benchmarking                         | 66 |

| 4.7    | Conclusion                                           |    |

| 4.8    | References                                           | 68 |

| 5 Cone | clusion                                              | 72 |

| 5.1    | Contributions of This Work                           | 72 |

| 5.2    | Suggestions for Future Work                          |    |

| 5.3    | References                                           | 74 |

|        |                                                      |    |

# **List of Figures**

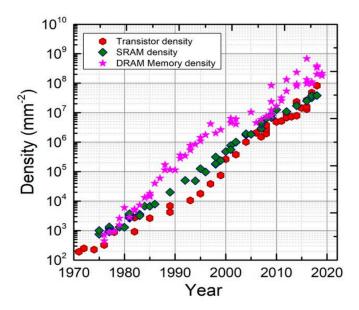

| 1.1 | Evolution of chip component density scaling trends. Transistor density is defined as the number of transistors on a chip divided by the chip area. SRAM bit density and DRAM bit density have advanced at the same pace as the transistor density (reproduced from [8])                                                                                                          |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

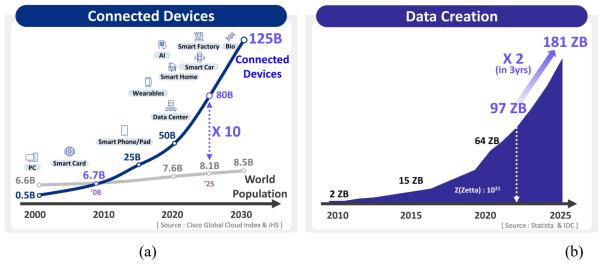

| 1.2 | Exponential growth of (a) connected devices and (b) data creation (adapted from [11] 3                                                                                                                                                                                                                                                                                           |

| 1.3 | Memory hierarchy diagram [19]                                                                                                                                                                                                                                                                                                                                                    |

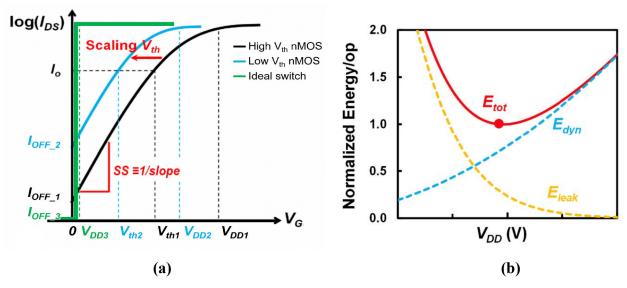

| 1.4 | Conceptual illustrations of (a) the switching <i>I-V</i> characteristics of a high- <i>Vth</i> n-channel MOSFET, a low- <i>Vth</i> n-channel MOSFET, and an ideal switch; (b) dynamic, static, and total energy consumed per operation of a CMOS digital logic circuit. The lower limit for CMOS energy efficiency exists due to MOSFET OFF-state leakage (reproduced from [26]) |

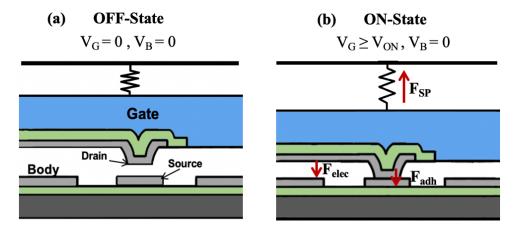

| 1.5 | Cross-section illustrations of a 4-terminal MEM switch in a) OFF-state, and b) ON-state                                                                                                                                                                                                                                                                                          |

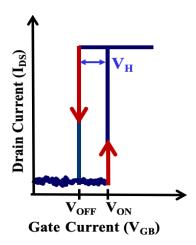

| 1.6 | A typical $I_{DS}$ - $vs$ $V_G$ characteristic of a MEM switch for bidirectional voltage sweep, showing abrupt switching behavior.                                                                                                                                                                                                                                               |

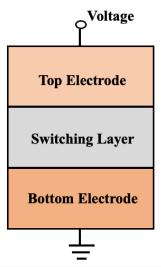

| 1.7 | Simple cross-section schematic illustrating the metal-insulator-metal structure of a ReRAM device                                                                                                                                                                                                                                                                                |

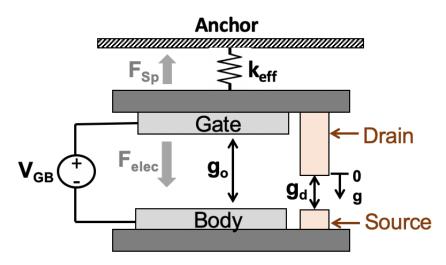

| 2.1 | Schematic diagram and mechanical spring model of a four-terminal MEM switch designed for digital logic applications. Electrostatic actuation and spring restoring forces are illustrated.                                                                                                                                                                                        |

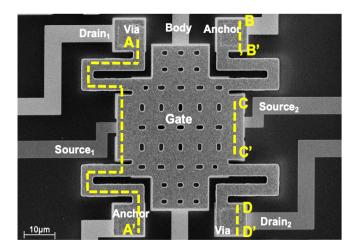

| 2.2 | Plan-view scanning electron micrograph (SEM) image of a fabricated MEM switch 17                                                                                                                                                                                                                                                                                                 |

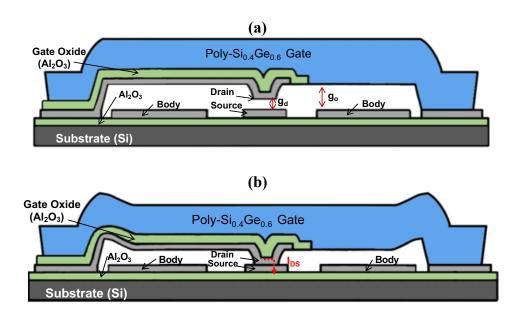

| 2.3 | Schematic cross-sectional views along A-A' cutline in Fig. 2.2: (a) OFF–state (b) ON–state                                                                                                                                                                                                                                                                                       |

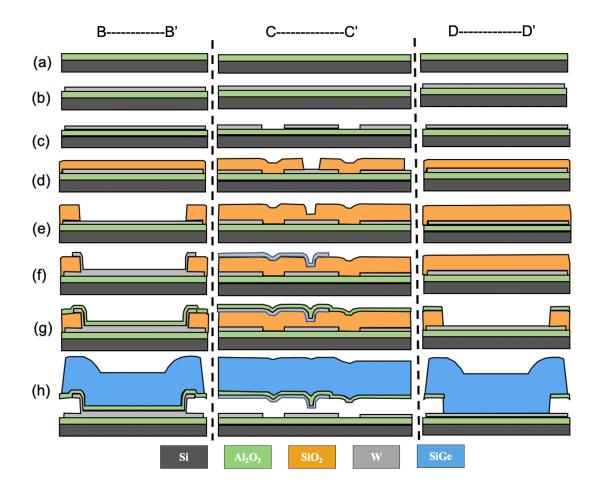

| 2.4 | Schematic device cross-sections along B-B', C-C', and D-D' (cf. Figure 2.2) illustrating key MEM switch fabrication steps                                                                                                                                                                                                                                                        |

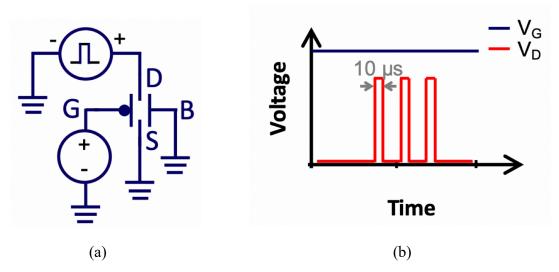

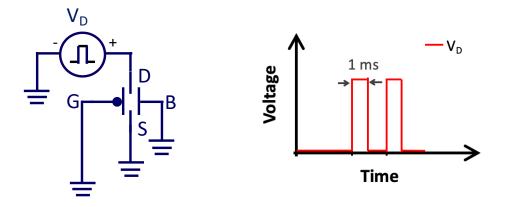

| 2.5 | Pulsed cold switching oxide breakdown procedure: (a) circuit schematic and (b) voltage timing waveforms (not to scale). Adapted from [13]                                                                                                                                                                                                                                        |

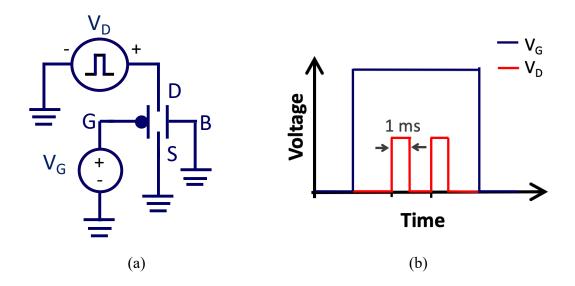

| 2.6  | MEM switch program operation: (a) circuit schematic and (b) voltage timing waveforms (not to scale)                                                                                                                                                                                                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

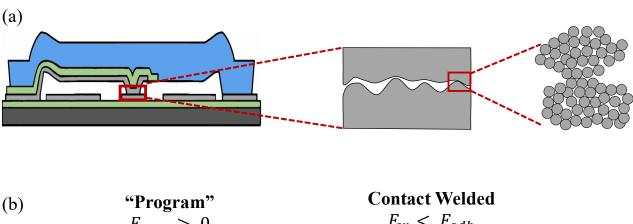

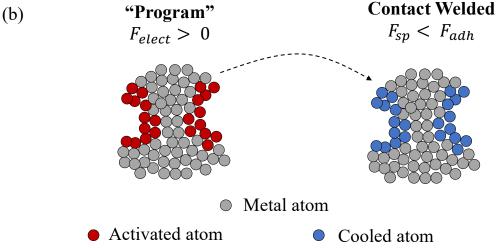

| 2.7  | Contact welding in a MEM switch, induced by Joule heating: (a) Due to surface roughness, physical contact and current flow occur only at one or more asperities. (b) During "Program" operation, Joule heating softens the contact, resulting in contacting asperity growth and increased area of physical contact, effectively welding the electrodes together.                        |

| 2.8  | Illustration of erase operation (a) circuit schematic and (b) voltage timing waveform 24                                                                                                                                                                                                                                                                                                |

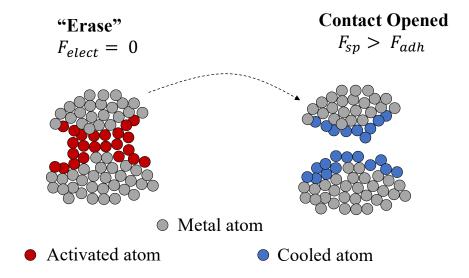

| 2.9  | Contact un-welding in a programmed MEM switch: During "Erase" operation, Joule heating weakens the bonding strength so that the spring restoring force causes the contact to be broken.                                                                                                                                                                                                 |

| 2.10 | Circuit schematic diagram of read operation                                                                                                                                                                                                                                                                                                                                             |

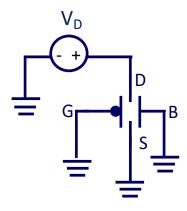

| 2.11 | Measured $I_{\rm DS}$ - $V_{\rm GB}$ curves for a MEM switch before programming (blue) and after one P/E cycle (red).                                                                                                                                                                                                                                                                   |

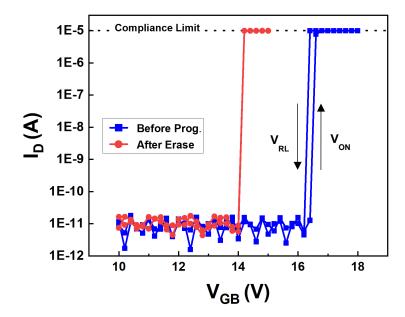

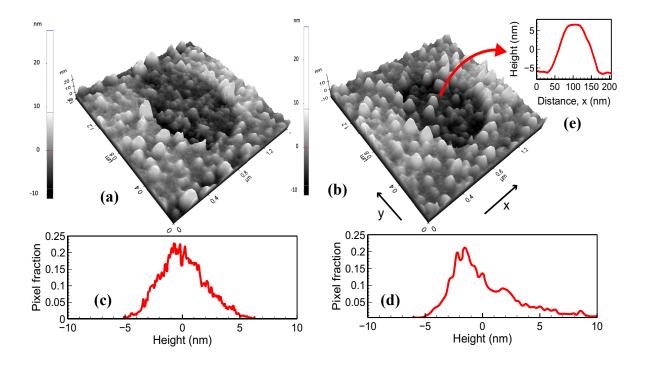

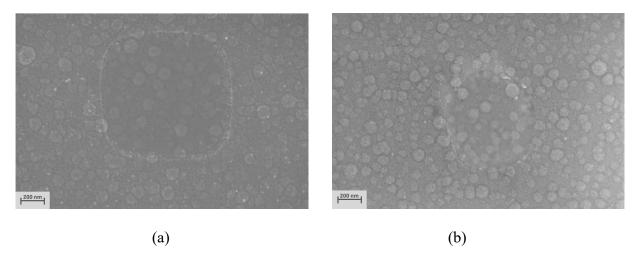

| 2.12 | AFM analyses of MEM switch source electrode topography: Scans (1.6 $\mu$ m x 1.6 $\mu$ m) of electrode surfaces for (a) an unprogrammed contact, and (b) a P/E-cycled contact; height distributions within the contact dimple region for (c) the unprogrammed contact and (d) the P/E-cycled contact. (e) Height $vs$ . distance for an asperity, showing that it is $\sim$ 13 nm tall. |

| 2.13 | SEM images of MEM switch source electrodes: (a) for a fresh switch and (b) for a P/E-cycled switch. More prominent features (asperities) can be seen in the contact dimple for the cycled switch                                                                                                                                                                                        |

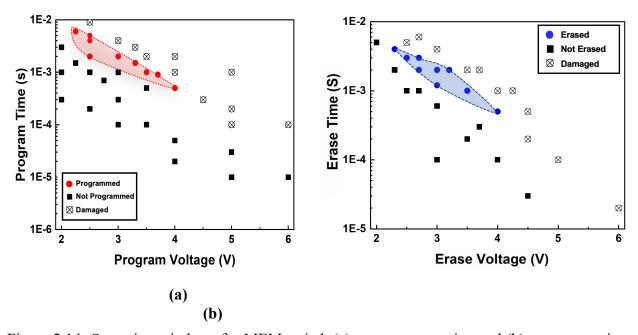

| 2.14 | Operating windows for MEM switch (a) program operation and (b) erase operation. The shaded regions indicate the combinations of $V_{\rm DS}$ pulse duration and voltage for successful re-program/erase operation. Damaged switches are not functional afterwards, <i>i.e.</i> , they cease to conduct any current                                                                      |

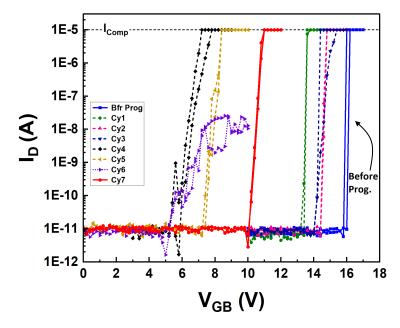

| 2.15 | Evolution of MEM switch $I_{\rm DS}$ - $V_{\rm GB}$ characteristic through multiple program/erase cycles. The change in $VON$ from cycle to cycle is non-deterministic because it depends on the shape and height of the contacting asperities                                                                                                                                          |

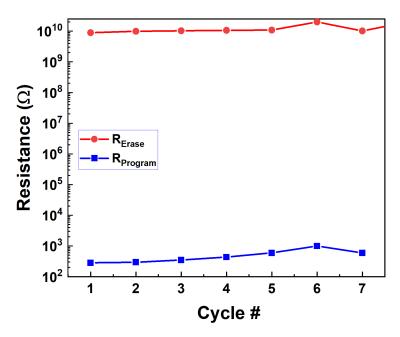

| 2.16 | Evolution of the measured resistance of a MEM switch in the programmed state $(R_{\text{program}})$ and in the erased state $(R_{\text{erase}})$ , over multiple P/E cycles. $R_{\text{program}}$ is consistently below $1 \text{k}\Omega$ . $R_{\text{erase}}$ essentially indicates an open circuit, as the measurement limit due to noise is $\sim 10^9  \Omega$ .                   |

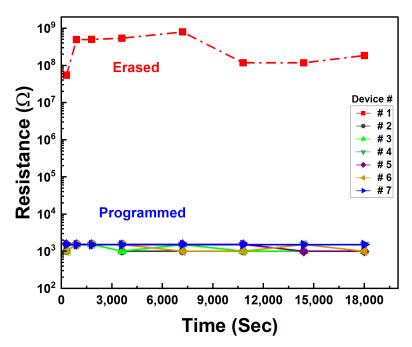

| 2.17 | Data retention testing of multiple MEM switches (1 erased, 6 programmed) at high temperature (200°C) in vacuum ( $\sim$ 1 $\mu$ Torr). The current noise floor is higher at elevated temperature, resulting in smaller apparent $R_{\rm erase}$                                                                                                                                         |

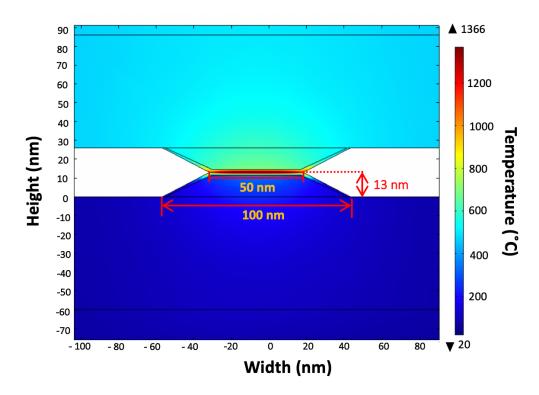

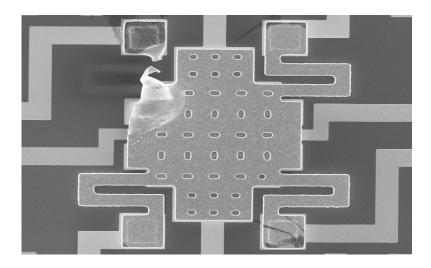

| 2.18 | COMSOL simulation of Joule heating in a MEM switch during erase operation (cf. Table 2.1)                                                                                                                                                                                                                                                                                               |

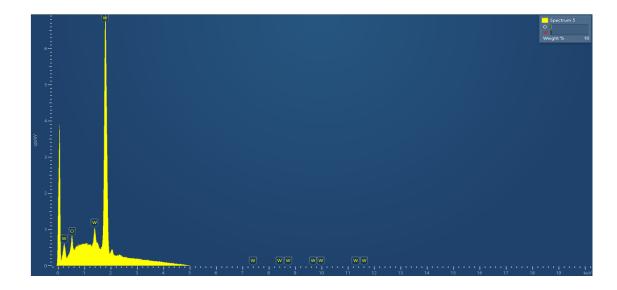

| 2.19 | Measured EDX spectrum of source electrode showing the presence of W and O at the surface                                                                                                                                                                                                                                                                                                |

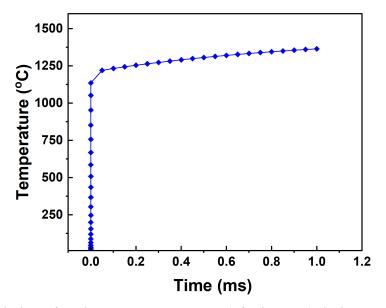

| 2.20 | Evolution of peak contact temperature (cf. Fig. 2.18) during erase operation                                                                                                                                                                                          |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.21 | Top view SEM image of a MEM switch that failed after 6 program/erase cycles                                                                                                                                                                                           |

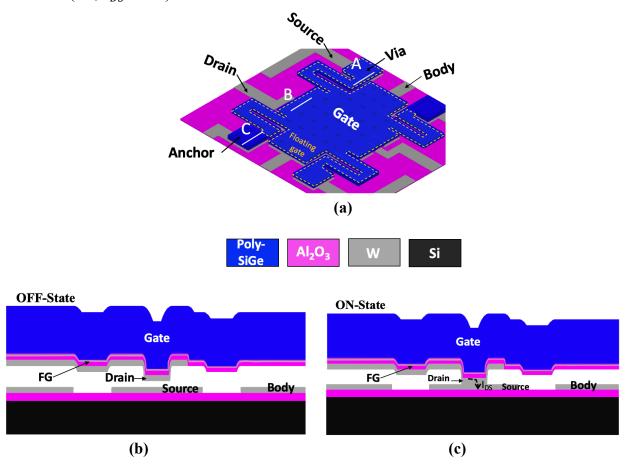

| 3.1  | (a) Schematic isometric view of the floating-gate MEM switch studied in this work and cross-sectional views along the 'B' cutline in (b) OFF-state (c) ON-state                                                                                                       |

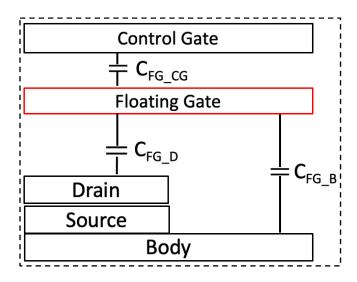

| 3.2  | Schematic illustrating capacitances within a FG-MEM switch in the ON-state39                                                                                                                                                                                          |

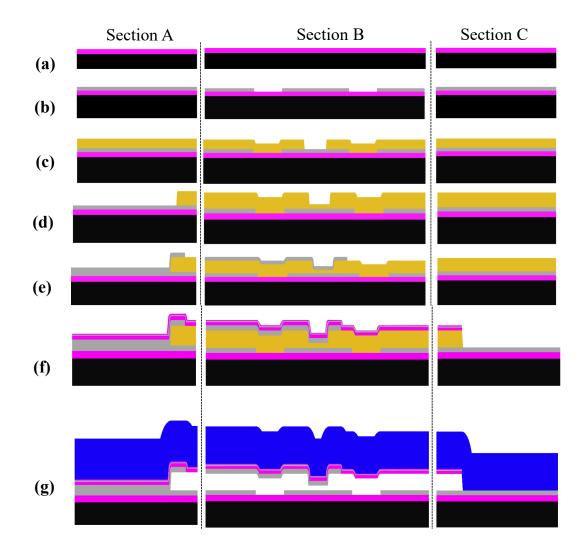

| 3.3  | Schematic cross-sectional views along A, B and C cut-lines in Figure 3.1(a) illustrating the fabrication process steps for the FG-MEM switches studied in this work                                                                                                   |

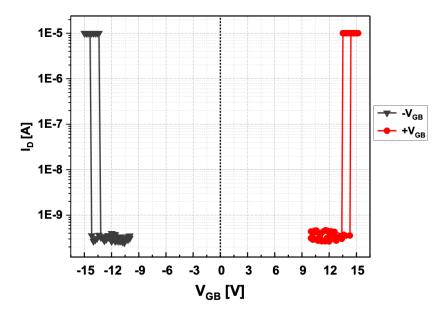

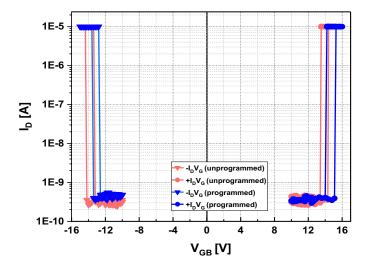

| 3.4  | Measured <i>I-V</i> characteristics of a FG-MEM switch showing symmetric values of VON. (Negative VGB sweep is shown in Black while positive VGB sweep is shown in Red.) 42                                                                                           |

| 3.5  | Measured $I$ - $V$ characteristics of a FG-MEM switch before (red) and after (blue) programming for negative and positive $VGB$ sweeps. $VON$ is no longer symmetrical due to injected charges and is shifted by $+0.79$ V to the right, after programming            |

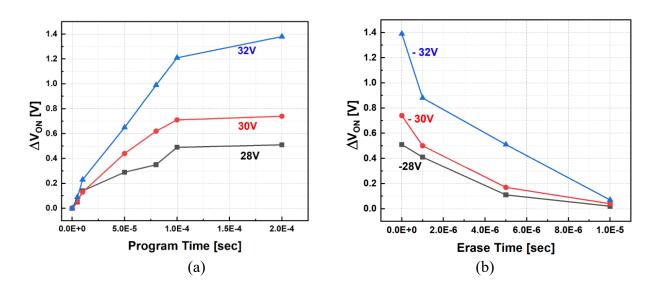

| 3.6  | Change in FG-MEM switch turn-ON voltage with (a) program and (b) erase time, for different program/erase voltages. 43                                                                                                                                                 |

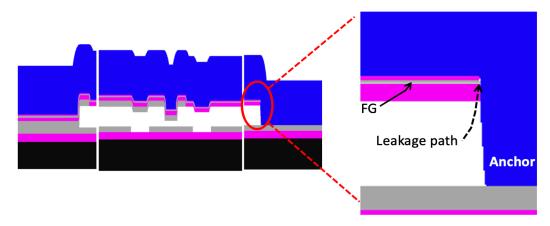

| 3.7  | Zoomed-in cross-sectional schematic of the initial FG-MEM NV-switch design (cf. Figure 3.3(g)) showing that the floating gate (FG) contacts the gate electrode in the anchor region, allowing charge on the FG to leak away                                           |

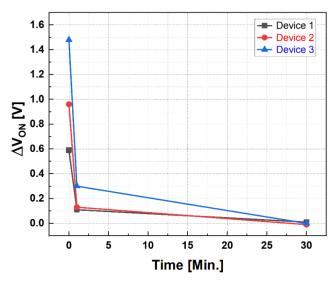

| 3.8  | Data retention characteristics of three FG-MEM devices at 200°C. Most of the charge stored on the FG in each of the three devices leaked away within ~1 minute                                                                                                        |

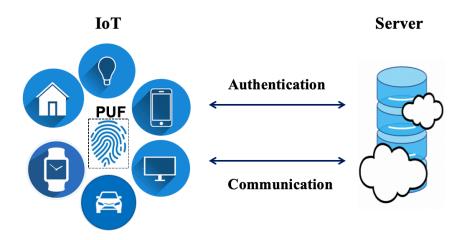

| 4.1  | Typical PUF based authentication scheme for IoTs                                                                                                                                                                                                                      |

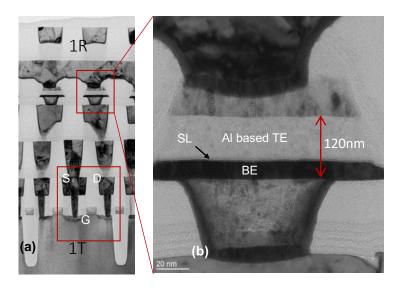

| 4.2  | (a) Cross-sectional transmission electron micrograph of a fabricated 1 transistor (1T) 1 ReRAM (1R) cell (b) higher-magnification view showing ReRAM layer stack: inert bottom electrode (W), switching layer (AlOx), and Al-based top electrode (AlNx)               |

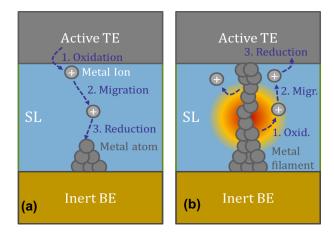

| 4.3  | Schematic illustration of the switching mechanisms of a Conductive Bridge ReRAM device: (a) program operation and (b) erase operation                                                                                                                                 |

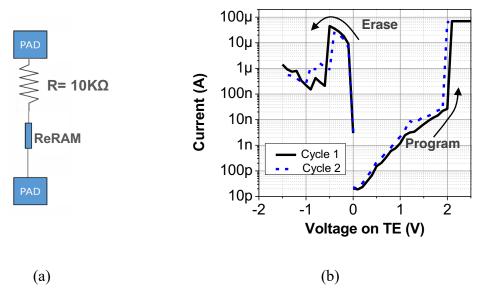

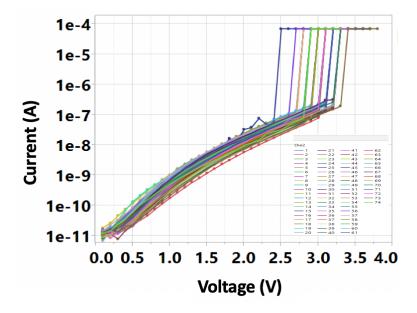

| 4.4  | (a) I-V measurement circuit schematic. (b) Typical measured I-V curves of a ReRAM device. 'Cycle 1' is the 1st cycle from pristine device ('form' and 'erase') and 'Cycle 2' shows 'program' and 'erase' operation. Voltage sweep directions are indicated by arrows. |

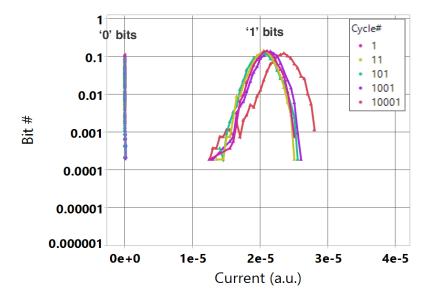

| 4.5  | Distributions of measured ReRAM cell current after verified program/erase cycles. Excellent endurance (more than 10,000 cycles) is seen for the two distinct states (ON and OFF).                                                                                     |

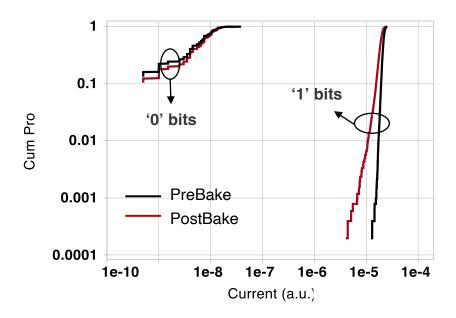

| 4.6  | ReRAM retention performance. Clearly differentiated 'ON' ('1') and 'OFF' ('0') states are retained after baking at 225°C for 1 hour. The projected retention time at 85°C is greater than 98 years                                                                    |

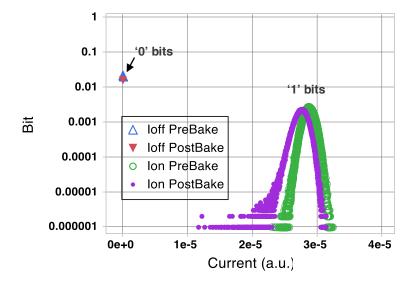

| 4.7  | ReRAM forming current distributions before and after baking at 265°C for 1 hour, confirming solder reflow process compatibility                                                                                                                                       |

| 4.8  | Characterization of DC forming voltage randomness of 74 ReRAM cells                                                                                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

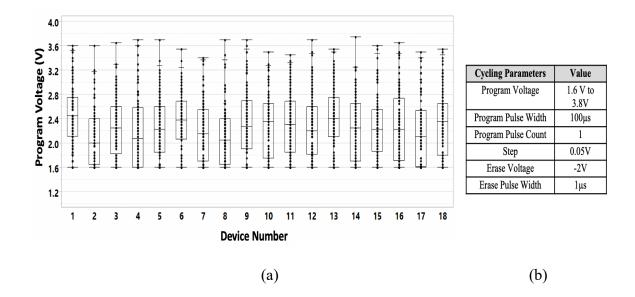

| 4.9  | (a) Cycle-to-cycle program voltage distribution for 18 ReRAM devices. Each device is cycled 100 times. The edges of the box indicate the 25 <sup>th</sup> and 75 <sup>th</sup> percentiles and the median value is indicated inside the box. (b) Program/erase parameters used. More than 1 erase pulse was used if needed.     |

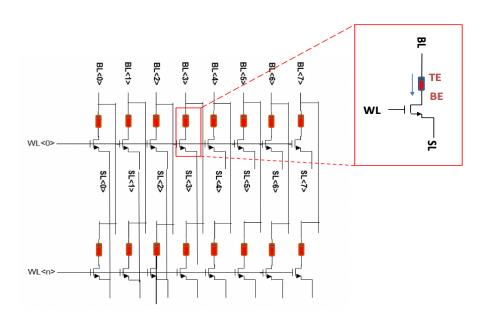

| 4.10 | Cell array architecture used for measuring ReRAM program/erase times. 'BL', 'WL' and 'SL' denote bit line, word line, and source line, respectively                                                                                                                                                                             |

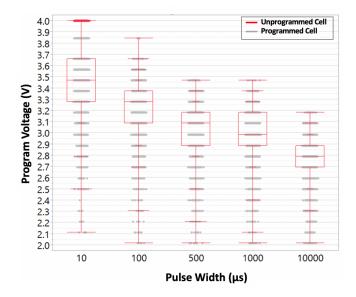

| 4.11 | Measured distributions of ReRAM program voltage for various program pulse widths. The edges of the red box indicate the 25 <sup>th</sup> and 75 <sup>th</sup> percentiles and the median program voltage is indicated inside the box                                                                                            |

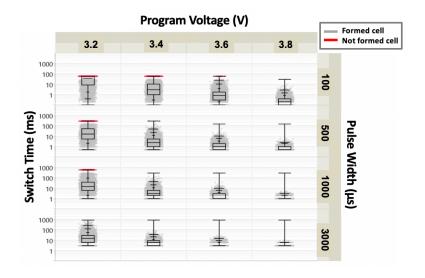

| 4.12 | Measured distributions of ReRAM switching time for various values of program voltage. (The switching time is the product of program pulse width and pulse count.) The edges of the black box indicate the 25 <sup>th</sup> and 75 <sup>th</sup> percentiles and the median value of switching time is indicated inside the box. |

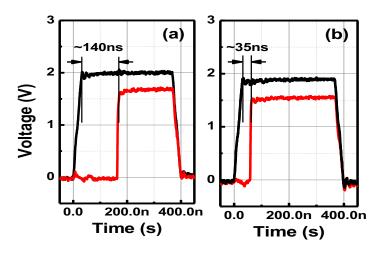

| 4.13 | Programming voltage pulse (black) and measured voltage (red) across 5 k $\Omega$ series resistor. (Once the ReRAM cell is programmed, the voltage across the resistor increases.) A large difference in switching time is seen for the two different ReRAM cells in (a) and (b)                                                 |

| 4.14 | Circuit diagram illustrating voltage-differential based PUF generation. A pair of 1T-1R cells ('Cell 1' and 'Cell 2') forms one PUF bit-cell. 'BL', 'WL' and 'SL' denote bit line, word line, and source line, respectively                                                                                                     |

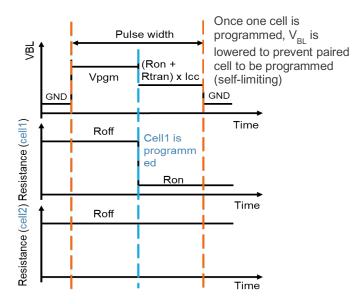

| 4.15 | Timing diagram for PUF bit generation during Gentle Program step. Once one cell is programmed, the voltage on the bit line (VBL) drops, preventing the programming of the other cell in the pair. Rtran is the ON-state resistance of the programmed cell transistor                                                            |

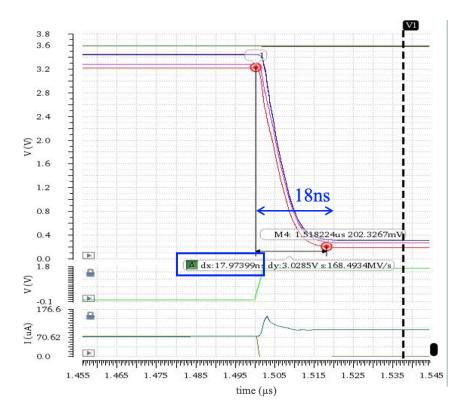

| 4.16 | Simulation of bit-line voltages (for program voltages of 3.2V, 3.3V and 3.4V) when 100uA current compliance is set. It takes ~18ns for the bit-line voltage to drop after a cell is programmed                                                                                                                                  |

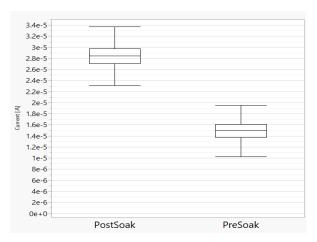

| 4.17 | Measured ReRAM current before and after soaking step. ON-state current is higher after soaking due to enhanced filament strength                                                                                                                                                                                                |

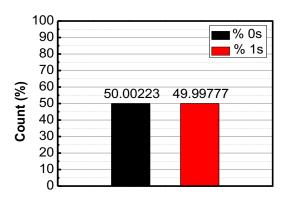

| 4.18 | Percentages (%) of '0's (OFF-state cells) and '1's (ON-state cells) in 102,400,000 generated PUF bits. The percentages are very close to 50%, the ideal value for randomness                                                                                                                                                    |

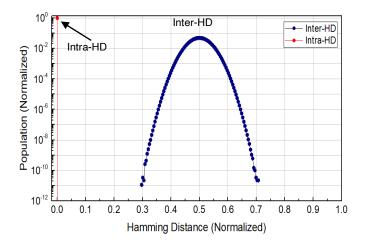

| 4.19 | Inter- and Intra- hamming distance (HD) of generated PUF bits (102,400,000 bits). PUF key length is 256 bits and total PUF count is 400,000. Inter-HD follows an ideal Gaussian distribution. There is no overlap between inter- and intra- HD distributions 64                                                                 |

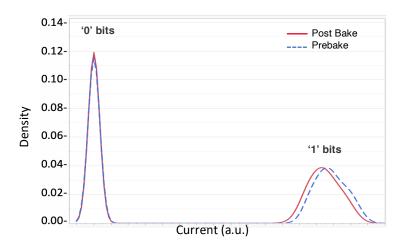

| 4.20 | Stability of '1' and '0' bits after 150°C, 50 hours (PostBake) compared to before bake (PreBake). 100% retention is achieved for both '0' and '1' states                                                                                                                                                                        |

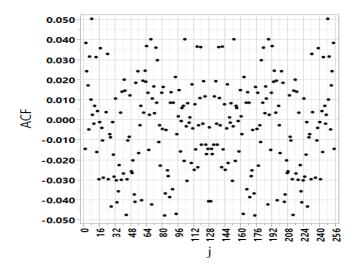

| 4.21 | Auto correlation test results of 400,000 PUF keys of length 256 bits each, showing no correlation between PUF key bits                                                                                                                                                                                                          |

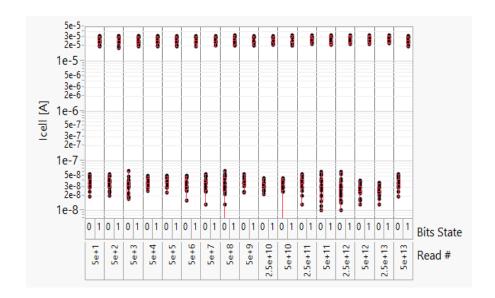

| 4.22 | ReRAM read endurance (measured $I_{Cell}$ vs. Read #) showing that distinction between ON and OFF devices is well maintained after 5E13 read operations.                                                                                                                                                                                                                         | 65 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

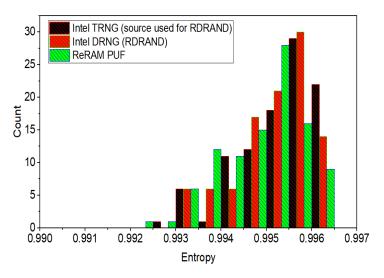

| 4.23 | Randomness comparison of Intel TRNG (which uses non-deterministic hardware sources for RDRAND), Intel RDRAND (Digital RNG), and the ReRAM-based PUF demonstrated using 28nm-generation CMOS technology in this work. Entropy of 0.990 indicates 2 <sup>-0.990</sup> = 50.3% chance for 0 or 1 in any sequence/circumstance. (1.0 corresponds to perfect entropy of binary bits.) | 67 |

# **List of Tables**

| 2.1 | Default parameters for MEM switch program, erase and read operations               | 25 |

|-----|------------------------------------------------------------------------------------|----|

| 2.2 | Key material properties and values used for simulation                             | 31 |

| 2.3 | Mechanical and electrical properties of alternative contacting electrode materials | 33 |

| 3.1 | FG-MEM design parameter values used in this study                                  | 41 |

| 4.1 | Parameters for ReRAM program and erase cycling                                     | 53 |

| 4.2 | PUF bit generation conditions used in gentle program and soaking steps             | 60 |

| 4.3 | Detailed results for the standard NIST SP800-22 randomness check test suite        | 66 |

| 4.4 | Comparison of advanced PUF implementations                                         | 67 |

#### Acknowledgments

As I reflect upon this momentous occasion, I cannot help but feel overwhelmed with a deep sense of gratitude and accomplishment. It has been a long and arduous journey to reach this point, filled with moments of doubt and uncertainty. However, as Philippians 4:13 states, "I can do all things through Christ who strengthens me." With the help of God Almighty, who has blessed me with countless opportunities and guidance, I have finally reached this day. This has indeed been an incredible journey and the accomplishment cannot be attributed solely to my efforts, but rather to all those who have played a role in this journey.

First and foremost, I would like to express my sincere gratitude to my advisor, Professor Tsu-Jae King Liu, for her exceptional mentorship, leadership, thoughtfulness, support, and encouragement. Her technical innovation, research expertise, and visionary leadership have been a tremendous inspiration to me as a scholar. In addition, her guidance and mentorship have helped me to grow and develop significantly in my field. I am deeply grateful for her unwavering support even in times when I doubted myself. As I embark on the next phase of my life, I aspire to follow in her footsteps, both in achieving technical excellence and in shaping the next generation. Thank you, Prof. King Liu!

I would also like to thank Prof. Ming Wu and Prof. Junqiao Wu for serving on my qualifying examination committee and dissertation committee. I am very grateful for their invaluable feedback and guidance on my research projects. Additionally, I'm grateful to Prof. Ana Claudia Arias, who not only served on my preliminary examination and qualifying exam committee but also shared invaluable life advice from her own academic journey. I would like to thank Prof. Jeffrey Bokor for dedicating his time to helping me understand advanced engineering concepts beyond what was taught in class. I also want to express my appreciation to Dr. Hei Kam, alumnae of King Liu group, for generously providing me with insightful suggestions and constructive feedback throughout the course of our reprogrammable MEM switches project. The constructive feedback and guidance were integral to the success of this project, and I am truly thankful for the collaboration.

Thank you to Prof. Gireeja Ranade and Dr. Jaeseok Jeon for allowing me to serve as a Graduate Student Instructor for EECS16A and EE130/230A. I have found the experience thoroughly enjoyable and rewarding as well. I thank Profs. Ali Javey, Vivek Subramanian, Clark Nguyen, Ali Niknejad, and Eli Yablonovitch for their expert guidance and outstanding courses in the field of electrical engineering.

Throughout my research journey, I have received steadfast support from various organizations, especially from the CrossBar Inc. team. I want to express my sincere gratitude to Dr. Sung Hyun Jo, Dr. Zhi Li, Dr. Amit Prakash, and Dr. Derek Lau, for their valuable contributions to the ReRAM project. Their insightful suggestions, brainstorming discussions, and constructive feedback have been immensely helpful. I am truly grateful for their guidance and support.

My sincere thanks also goes to the King Liu research group who made my experience at Berkeley as smooth and stress-free as possible. I truly cherished the meaningful interactions we had as both colleagues and friends. I am especially thankful to Dr. Sergio Almeida, Dr. Benjamin Osoba, Dr. Zhixin Alice Ye, Dr. Urmita Sikder, Dr. Xaioer Hu, Lars P. Tatum, Dasom Lee, Dr. Xi (Robin) Zhang, Dr. Fei Ding, Dr. Thomas Rembert, Dr. Rebecca Mih, and Dr. Min-Wu Kim. I am deeply grateful for the expertise and the frequent discussions we have had, which have played a

crucial role in my academic growth and development. I also would like to thank my friends and colleagues from the Black Graduate Engineering and Science Students (BGESS) for being by my side encouraging me and allowing me to serve as a board member. Thank you Dr. Liya Weldegebriel, Dr. Carlos Biaou, and Dr. Juan Pablo Llinas for providing a support system within and outside of academics.

I am fortunate to have had the opportunity to interact with the staff at UC Berkeley's Marvell Nanofabrication Laboratory, and I am deeply grateful to Bill Flounders, Dave Taosaka, Ryan Rivers, Allison Dove, Joanna Bettinger, Richelieu Hemphill, Sam Tsitrin, Jay Morford, and Jason Chukes for their invaluable assistance. They not only taught me how to use the fabrication equipment but also helped me address process issues and ensured that the equipment remained operational. Their support has been immensely valuable.

I would also like to thank all the faculty and staff members of the EECS department and College of Engineering including Audrey Sillers, Susanne Kauer, Tiffany Reardon, Meltem Erol, Lea Marlor, Dr. Michael Bartl, Charlotte Jones, Dr. Kedrick Perry, and many others for their support and guidance in administrative matters. In particular, I am sincerely grateful to Shirley Salanio for her continuous support, prompt replies, and encouragement during challenging times. Additionally, I would also like to thank Dr. Sheila Humphrey for her kindness and willingness to share her knowledge.

I also would like to express my gratitude to Dr. Satish Naidu, Dr. Jose Romero, and Dr. Atul Shah from Intel Inc., for the valuable knowledge they imparted to me during my internship.

Thank you to the University of California Office of the President and the National GEM Consortium for their generous fellowship support and funding, which made my graduate studies possible. Additionally, I would like to thank the UC-HBCU initiative for the opportunity to conduct research at Berkeley during my undergraduate studies, which played a pivotal role in my decision to pursue a Ph.D. at UC Berkeley.

I am also deeply grateful to all the young adult fellowship, choir, and my entire church family at Abenezer Evangelical Church. Their love, encouragement, spiritual guidance, and hospitality have meant the world to me, and I truly feel like I am home. Thank you all!

Finally, I am tremendously grateful to my family for their unconditional love and support. I am deeply indebted to them for their sacrifices, which have helped shape me into the person I am today. Their constant guidance, support, and endless caring have helped me navigate through life's many challenges. Special thanks to my husband, Bekalu Aneme, for taking care of me and sharing all my laughs and tears. I can never get through my Ph.D. journey without his love and patience.

# Chapter 1

## Introduction

## 1.1 Brief History and Evolution of Integrated Circuits

Integrated circuits (ICs), also known as microchips, are tiny electronic devices that integrate a large number of electronic components such as transistors, resistors, and capacitors on a single chip of silicon. The advent of the IC chip was a revolutionary innovation that transformed the electronics industry and paved the way for advanced information processing and communication systems [1]. This breakthrough has led to the development of personal computers, smartphones, and other portable electronic devices that have become vital in daily life. Furthermore, the proliferation of computing has profoundly advanced many areas of technology, including the Internet of Things (IoT), cloud computing, artificial intelligence, and other domains. By enabling the integration of numerous components onto a single chip, microchips have made it possible to design smaller, more powerful, and more energy-efficient devices that have enhanced people's productivity and convenience.

The history of ICs can be traced back to the invention of the transistor in 1947 by John Bardeen, Walter Brattain, and William Shockley at Bell Labs. The transistor was a replacement for the bulky and inefficient vacuum tubes that were used in electronics at the time. It was smaller, used less power, and was more reliable than vacuum tubes, making it ideal for use in electronic devices. In 1958, Jack Kilby of Texas Instruments invented the first integrated circuit. Kilby's circuit comprised a tiny piece of germanium with a few transistors and other components etched onto its surface [2]. In 1965, Gordon Moore, the co-founder of Intel Corporation, made an observation that the number of Complementary Metal Oxide Semiconductor (CMOS) transistors on a single chip doubled about every year and later in 1967 adjusted to every two years [3][4]. This prediction, which became known as Moore's Law, has been remarkably accurate over the past several decades and has driven the rapid advancement of computer technology. Nowadays, modern microprocessor chips contain many billions of transistors enabled by the steady miniaturization of the transistor, which allows exponential pace of improvement in computational speed while lowering the cost and energy consumed per function [5].

Along with transistor (switches used to implement digital logic and for signal amplification), the advancement of memory devices has also been a key factor in the development of modern information technology. In the early days of computing, data was stored on magnetic tape, punch cards, and other physical media which were large, heavy, and expensive. However, the invention of ICs led to the creation of the first solid-state memory device, the metal-oxide-semiconductor (MOS) memory [6][7]. Today, solid-state memory devices are ubiquitous and used in a wide range of applications, including personal computers, smartphones, wearable devices, servers, and data centers.

Figure 1.1: Evolution of chip component density scaling trends. Transistor density is defined as the number of transistors on a chip divided by the chip area. SRAM bit density and DRAM bit density have advanced at the same pace as the transistor density (reproduced from [8]).

Despite rumors of the end of Moore's law in recent years [9], the semiconductor industry has continued to steadily advance IC manufacturing. This progress is driven by growing demand for easy access to information and mobile connectivity, resulting in the widespread acceptance and rapid advancement of internet and wireless communication technologies. Today we live in a globally connected society with universal access to information, which is increasingly collected by machines with the emergence of the IoT.

The Internet of Things (IoT) refers to objects with embedded electronic devices that are used to collect, process and communicate information via a wired or wireless network. Over the past decade, there has been an exponential growth in the number of connected devices and data generated worldwide. This trend is primarily driven by the proliferation of IoT devices [10]. As shown in Figure 1.2, the number of connected devices is expected to reach 125 billion by 2030. The exponential growth in the number of connected devices has also led to an exponential growth in the amount of digital data generated. It is estimated that the total amount of digital data generated worldwide will reach 181 zettabytes by 2025, up from just 2 zettabytes in 2010 [11][12]. This

growth trend is expected to continue in the years ahead. However, this growth also brings challenges, such as data privacy and security concerns, as well as the need for more energy-efficient and more reliable data storage and processing solutions.

Figure 1.2: Exponential growth of (a) connected devices and (b) data creation (adapted from [11]).

## 1.2 Memory Requirements for IoT

The widespread availability of electronic devices and the generation and processing of large data sets ("big data") necessitate the need for a storage medium that is both non-volatile and energy-efficient, with high endurance and retention, low manufacturing cost, and most importantly, embedded with logic circuitry so that certain computational tasks can be performed in the memory itself for faster processing speed [13]. Meanwhile, it is also crucial to maintain the security and confidentiality of information collected and shared by IoT devices. A recommended solution to achieve this is to utilize memory devices that can store data and function as hardware security keys as well.

#### 1.1.1 Traditional Memory Devices

Modern computer architectures have a hierarchical memory system, as illustrated in Figure 1.3, comprising different types of conventional memory devices ranging from high-speed, small-capacity storage devices to slower, large-capacity devices [14–16].

Conventionally the memory pyramid from top to bottom (small capacity to large capacity) comprises central processor unit (CPU) registers and cache memory on the same chip as the CPU, and main working memory and long-term storage memory on separate chips. CPU registers at the top of the pyramid are the fastest type of memory used in a computer. Registers are built into the processor and are used to store the instructions and data that are frequently accessed or currently

being executed by the processor. However, registers are the most expensive type of memory and have very limited capacity, typically only a few bytes [17].

Next in the hierarchy is cache memory. Caches are designed to reduce the time it takes to access data from the main memory by temporarily storing copies of data frequently used. Typically, caches are slower than the CPU registers and mostly comprise Static Random Access Memory (SRAM) cell arrays due to their higher access speed compared to other types of memory [14][18]. A typical SRAM cell consists of six transistors (two cross-coupled CMOS inverters, forming a latch, plus two pass-gate transistors for accessing the two storage nodes of the latch) to store one bit of information while power is supplied. Yet, it has a limitation in terms of storage density (meaning that it stores less data per unit area on a chip compared to other types of memory). This makes it more expensive and impractical for large capacity and long-term storage.

Main memory comprises Dynamic Random Access Memory (DRAM) chips. A DRAM cell stores one bit of information using a capacitor and an access transistor. One of the main benefits of DRAM is its high storage density, *i.e.*, it can store more data per unit area compared to SRAM. This makes it more cost-effective for applications where large amounts of data need to be temporarily stored. However, the simpler cell design results in slower data access speeds [15]. A DRAM cell requires regular refreshing to restore charge on its capacitor (because the access transistor has non-zero leakage current). For this reason it consumes more power than non-volatile memory.

Although both SRAM and DRAM are useful for temporary data storage, they are volatile, meaning data will be lost when power to the chip is turned off. For long-term data storage, hard-disk drives (HDDs) have been used for over 50 years. HDDs have several benefits, including nonvolatility, large storage capacity, and low cost per bit. Their main downside is their slow data transfer rate for both reading and writing operations.

Figure 1.3: Memory hierarchy diagram [19].

In recent years, due to the performance (latency) gap between DRAM and HDD, flash memory devices have emerged as a solution. Flash memory stores information by injecting (erasing) electrons to (from) a charge-storage layer through an electrically insulating dielectric material. These devices have become widely used in solid-state drives (SSD), displacing traditional HDD for some applications because of their faster speed and lower power consumption. Flash memories have also found extensive usage in portable electronic devices, such as mobile phones, and USB flash drives [20]. Vertical (three-dimensional, or 3-D) stacking of flash memory cells has been adopted to increase storage density and increase storage capacity [21].

Among the well-established types of memory devices there exists a sizable gap in performance (latency) between volatile memory (DRAM) and non-volatile storage (Flash) devices. Emerging Non-Volatile Memory (eNVM) device technologies aim to bridge this gap.

#### 1.1.2 Emerging Non-Volatile Memory Technologies

Increasing requirements for reduced IoT power consumption have driven efforts to develop new devices for storage-class memory (SCM), filling the gap in performance and storage density that currently exists between volatile memory and non-volatile storage devices [22]. Among several emerging memory device technologies, phase change memory (PCM), spin-transfer torque random access memory (STT-RAM), ferroelectric RAM (FeRAM), and resistive random-access memory (RRAM) are the most promising.

These emerging technologies employ novel materials (metal oxides, ferroelectric oxides, ferromagnetic metals, chalcogenides, carbon materials, *etc.* [23]) and mechanisms such as quantum mechanical phenomena, redox reaction, phase transition, spin-state, molecular reconfiguration, *etc.* to change the state of the memory device and thereby store information. Some have a simple two-terminal cell structure that is most amenable for high-density storage.

Although the dream of a "universal memory" (that offers high speed, large capacity and low cost) has not yet been achieved, SCM devices have the potential to bridge the performance gap between storage and memory, to enable new computer architectures such as brain-inspired computing systems and new applications such as hardware security systems. Practical manufacturing challenges exist, such as device-to-device variability and reliability. Therefore, there are still room for innovation in SCM devices to meet future computing needs.

#### 1.3 Energy-Efficient Computing for IoT

## 1.1.3 Energy-Efficiency Limit for CMOS Technology

Continual improvements in digital IC performance and reductions in cost per function have been enabled by the steady miniaturization of CMOS transistors. Ideally, as the dimensions of a transistor shrink, the operating voltage  $(V_{DD})$  should decrease to avoid increasing the peak electric field [24]. However, since the 90 nm technology node, voltage scaling slowed down because the threshold voltage  $(V_{th})$  of a MOS field-effect transistor (MOSFET) cannot be too close to 0 V; otherwise, the off-state leakage current  $(I_{OFF})$ , which increases exponentially with a linear reduction in  $V_{th}$ , will result in unacceptably high static power dissipation.

To explain this, Figure 1.4(a) shows a standard drain current vs. gate voltage semi-log plot, for two n-channel MOSFETs with different values of  $V_{th}$  as well as for an ideal switch.  $I_{OFF}$  is defined as the drain current when  $V_{GS} = 0V$  and  $V_{DS} = V_{DD}$ , where  $V_{DD}$  is the power supply voltage.

$$I_{OFF} \propto \exp(-\frac{V_{th}}{SS})$$

(1.1)

where the subthreshold swing (SS) is defined as the inverse slope of the  $log(I_D)$ - $V_G$  curve. The lower limit of SS is 60 mV/dec at room temperature due to the Boltzmann energy distribution of electrons in the source region of a MOSFET [25].

Figure 1.4: Conceptual illustrations of (a) the switching I-V characteristics of a high- $V_{th}$  n-channel MOSFET, and an ideal switch; (b) dynamic, static, and total energy consumed per operation of a CMOS digital logic circuit. The lower limit for CMOS energy efficiency exists due to MOSFET OFF-state leakage (reproduced from [26]).

The total energy dissipated  $(E_{tot})$  per digital operation is composed of a dynamic energy dissipation component  $(E_{dyn})$  and a static energy dissipation component  $(E_{leak})$ :

$$E_{tot} = E_{dyn} + E_{leak} (1.2)$$

If  $V_{DD}$  is lowered to decrease  $E_{dyn}$  then the transistor on-state current  $(I_{ON})$  will be lowered, resulting in slower digital circuit operation. The more time  $(t_{delay})$  it takes for a digital circuit to complete its function, the more energy is wasted due to transistor off-state leakage since  $E_{leak} \propto I_{off}V_{DD}t_{delay}$ . If  $V_{th}$  is lowered together with  $V_{DD}$  to maintain  $I_{ON}$  for fast circuit operation,  $I_{OFF}$  is exponentially higher, again resulting in higher  $E_{leak}$ . Therefore as  $V_{DD}$  is lowered,  $E_{leak}$  increases while  $E_{dyn}$  decreases, so that a minimum value of  $E_{tot}$  exists (at  $V_{DD} = V_{th}$ ).

As illustrated by the green curve in Figure 1.4 (a), an ideal switch would have an abrupt switching characteristic with  $I_{off} \approx 0$  and  $V_{th} \approx 0$  to enable ultra-low energy per operation. Thus, in order to achieve dramatically improved energy efficiency, an alternative switching device is needed.

#### 1.1.4 MEM Switches for Energy-Efficient Computing

Microelectromechanical (MEM) switches operate by making and breaking physical contact between two conductive electrodes (drain and source electrodes) so they have essentially zero  $I_{OFF}$ , enabling zero static power consumption, and abrupt switching characteristics across a wide range of temperatures [27], enabling lower supply voltage  $V_{DD}$ . Therefore, MEM switches have been investigated for energy-efficient logic switches and NVM device applications [28-30].

Figure 1.5 shows the schematic cross-section of body-biased MEM switch consisting of four terminals: gate, body, drain, and source electrodes. The movable structure is referred to as the gate and has an attached conductive metal strip underneath, called the drain, that is electrically insulated from the gate by a thin dielectric layer. A fixed actuation electrode underneath the gate is referred to as the body; the source electrode is coplanar with the body and runs underneath the drain in the dimpled contact region. In the OFF state, an air gap separates the conducting source and drain electrodes, hence no current flows between them as shown in Figure 1.5(a). When a sufficiently large voltage is applied across the gate and body such that  $V_{GB} > V_{ON}$ , the attractive electrostatic force  $(F_{elec})$  actuates the movable gate electrode downwards towards the fixed body electrode, bringing the drain electrode into physical contact with the source electrode so that the device turns ON abruptly, allowing current to flow (Figure 1.5(b)). To turn OFF the switch, the voltage across gate and body is reduced below  $V_{OFF}$ , so that the spring restoring force  $(F_{sp})$  of the deformed movable electrode actuates is upward to break contact between the drain and source. As shown in Figure 1.6,  $V_{OFF}$  is smaller than  $V_{ON}$  due to contact adhesive force  $F_{adh}$  between the drain and source electrodes in the ON state. The hysteresis voltage  $(V_H)$  is the difference between  $V_{ON}$  and  $V_{OFF}$ , and can be engineered to be very small (on the order of 10 mV) [30].

Figure 1.5: Cross-section illustrations of a 4-terminal MEM switch in a) OFF-state, and b) ON-state.

Figure 1.6: A typical  $I_{DS}$ -vs.- $V_G$  characteristic of a MEM switch for bidirectional voltage sweep, showing abrupt switching behavior.

Due to their negligible OFF-state leakage and abrupt switching characteristics, MEM switches are attractive for energy-efficient logic and NVM applications.

## 1.4 Ensuring IoT Security

IoT devices collect, process, and exchange a significant amount of potentially security-risking and/or private information. They are vulnerable to various malicious attacks, particularly because they communicate wirelessly and operate in an energy-constrained environment with very limited hardware resources [32][33], e.g., their memory capacity may be insufficient for storing encryption keys.

Physically unclonable functions (PUFs) are promising for authentication and secure encryption key generation/storage without expensive hardware [34]. Rather than storing keys in digital memory, PUFs leverage inherent variability in the integrated circuit manufacturing process that results in random variations in physical properties and hence electrical characteristics from device to device. Although device variability is not desirable for circuit performance, it is crucial for PUF implementation.

Resistive Random Access Memory (ReRAM) is an eNVM technology of keen interest for PUF key generation due to its low-power switching characteristics and relatively large device-to-device variability. As illustrated in Figure 1.7, a ReRAM device comprises two terminals with an oxide "switching layer" sandwiched between the two metallic electrodes. The ReRAM switching mechanism is based on the movement of ions under the influence of an electric field, to form or to remove an electrically conductive filament within the switching layer [35]. To program the ReRAM device, a positive voltage pulse is applied to the top electrode to cause a conductive filament to form, resulting in a low resistance state. To erase the ReRAM device, a negative voltage pulse is applied to the top electrode to break the filament, resulting in a high resistance state.

Depending on the composition of the conductive filament, a ReRAM device can be classified as one of two types: metal ion based, also referred to as conductive-bridge random access memory (CBRAM); or oxygen vacancy based random access memory (OxRAM). In a CBRAM device,

filament formation/breakage occurs via migration of metal ions and subsequent reduction/oxidation (redox) reactions. In an OxRAM device, filament formation occurs via migration of oxygen ions or vacancies [36].

Figure 1.7: Simple cross-section schematic illustrating the metal-insulator-metal structure of a ReRAM device.

Random device-to-device resistance variability can be leveraged to generate a unique PUF key based on the resistance of each cell within an ReRAM cell array. ReRAM-based PUFs can be implemented within a standard ReRAM cell array, enabling information storage together with PUF storage. Moreover, ReRAM-based PUFs have relatively low power consumption and a small footprint, making them ideal for use in resource-limited settings like embedded systems [37][38].

## 1.5 Dissertation Objectives and Overview

The main objective of this dissertation is to investigate novel/emerging NVM devices for ultralow-power electronics applications. A significant portion of this work focuses on adapting microelectro-mechanical (MEM) switches for eNVM applications. Another area of focus is the application of Resistive Random Access Memory (ReRAM) devices for efficient implementation of physical unclonable functions (PUFs).

In chapter 2, the concept of a reprogrammable NV-MEM switch is presented. After an introductory overview of the MEM switch design and fabrication process, program and erase operations are discussed. It is experimentally demonstrated that MEM switches can be programmed and erased with relatively small voltage (< 3V) and that they have excellent retention characteristics at elevated temperature (200°C). This allows non-volatile information storage at zero incremental fabrication cost.

In chapter 3, a floating-gate MEM switch design is investigated. The device fabrication process and initial experimental results are presented. Challenges their possible solutions are discussed.

In chapter 4, a novel PUF key architecture and generation scheme that utilizes the inherent program-time variation of resistive random access memory (ReRAM) cells as an entropy source is presented. ReRAM design and robust nonvolatile memory operation is first discussed, followed by the PUF generation scheme and randomness evaluation using a standard NIST test suite. Further verifications to confirm the high reliability of the generated PUF keys are described.

Chapter 5 summarizes the key findings and contributions of this dissertation. Suggestions for future research are also offered.

#### 1.6 References

- [1] 60 Years of Integrated Circuits. *Nat Electron*, vol. 1, no. 483, September 2018, doi: 10.1038/s41928-018-0145-6.

- [2] W. Brinkman, D. Haggan, and W. Troutman, "A History of the Invention of the Transistor and Where It Will Lead Us," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 12, pp. 1858-1865, Dec. 1997, doi: 10.1109/4.643644.

- [3] Gordon E. Moore, "Cramming more components onto integrated circuits," *Electronics Magazine*, vol. 38, no. 8, April 1965, doi:10.1109/N-SSC.2006.4785860.

- [4] G.E. Moore, "Progress in Digital Integrated Electronics," *Proc. Technical Digest Int'l Electron Devices Meeting*, vol. 21, pp. 11–13, 1975, doi: 10.1109/N-SSC.2006.4804410.

- [5] F. Faggin, "The Birth of the Microprocessor," *IEEE Micro*, vol. 41, no. 6, pp. 16-19, 2021, doi: 10.1109/MM.2021.3112302.

- [6] D. Klein, "The History of Semiconductor Memory: From Magnetic Tape to NAND Flash Memory," *IEEE Solid-State Circuits Magazine*, vol. 8, no. 2, pp. 16-22, Spring 2016, doi: 10.1109/MSSC.2016.2548422.

- [7] S. Asai, "Semiconductor Memory Trends," in Proceedings of the IEEE, vol. 74, no. 12, pp. 1623-1635, Dec. 1986, doi: 10.1109/PROC.1986.13681.

- [8] H. -S. P. Wong et al., "A Density Metric for Semiconductor Technology [Point of View]," *Proceedings of the IEEE*, vol. 108, no. 4, pp. 478-482, April 2020, doi: 10.1109/JPROC.2020.2981715.

- [9] T. N. Theis and H.-S. P. Wong, "The End of Moore's Law: A New Beginning for Information Technology," *Computing in Science & Engineering*, vol. 19, no. 2, pp. 41-50, Mar.-Apr. 2017, doi: 10.1109/MCSE.2017.29.

- [10] M. Bali, K.Gupta, D. Koundal, A. Zaguia, S. MahajanA. Pandit, "Smart Architectural Framework for Symmetrical Data Offloading in IOT," *Symmetry* 13, 1889, October 2021, doi:10.3390/sym13101889.

- [11] D. Ha, "Energy Efficient CMOS Scaling for 1nm and Beyond," 2022 IEDM Short Course 1-2, 2022.

- [12] A. Weissberger. Cisco's Annual Internet Report (2018–2023) forecasts huge growth for IoT and M2M; tepid growth for Mobile. *IEEE Com. Soc.* February 20, 2020

- [13] J. Lipman, S. Corp, "NVM Memory: A Critical Design Consideration for IoT Applications," *Design and Reuse*, 2017.

- [14] S. Manegold, "Memory Hierarchy" *Encyclopedia of Database Systems*, Springer, pp 2222–2229: 2018, doi:10.1007/978-1-4614-8265-9 657.

- [15] J.L. Hennessy and D.A. Patterson, "Computer Architecture A Quantitative Approach," 3rd ed. San Mateo: Morgan Kaufmann; 2003.

- [16] D.R. Parthasarathi, "Computer Architecture, Memory Hierarchy Design Basics Computer Architecture" *INFLIBNET Centre*.

- [17] S. Kumar and P. K. Singh, "An overview of modern cache memory and performance analysis of replacement policies," *IEEE International Conference on Engineering and Technology (ICETECH)*, pp. 210-214, 2016 doi: 10.1109/ICETECH.2016.7569243.

- [18] K. Osada, "Fundamentals of SRAM Memory Cell," Low Power and Reliable SRAM Memory Cell and Array Design. Springer Series in Advanced Microelectronics, vol 31. 2011, doi:10.1007/978-3-642-19568-6\_2.

- [19] Chuang Qian. Electro-Mechanical Devices for Ultra-Low-Power Electronics. PhD thesis, EECS Department, University of California, Berkeley, May 2017. URL: <a href="http://www2.eecs.berkeley.edu/Pubs/TechRpts/2017/EECS-2017-21.html">http://www2.eecs.berkeley.edu/Pubs/TechRpts/2017/EECS-2017-21.html</a>.

- [20] V. . -Y. Aaron and J. . -P. Leburton, "Flash memory: towards single-electronics," *IEEE Potentials*, vol. 21, no. 4, pp. 35-41, Oct.-Nov. 2002, doi: 10.1109/MP.2002.1044216.

- [21] Y. Li, "3D NAND Memory and Its Application in Solid-State Drives: Architecture, Reliability, Flash Management Techniques, and Current Trends," *IEEE Solid-State Circuits Magazine*, vol. 12, no. 4, pp. 56-65, 2020, doi: 10.1109/MSSC.2020.3021841.

- [22] C. H. Lam, "Storage Class Memory," *IEEE International Conference on Solid-State and Integrated Circuit Technology*, pp. 1080-1083, 2010, doi: 10.1109/ICSICT.2010.5667551.

- [23] A. Chen, "Emerging nonvolatile memory (NVM) technologies," *45th European Solid State Device Research Conference (ESSDERC)*, pp. 109-113, 2015, doi: 10.1109/ESSDERC.2015.7324725.

- [24] R.H. Dennard, F.H. Gaensslen, H.-N. Yu, V.L. Rideout, E. Bassous, A.R. Leblanc, "Design of ion-implanted MOSFETs with very small physical dimensions," IEEE Journal of Solid-State Circuits, Vol. 9, 1974.

- [25] K. K. Ng and S. Sze, "Physics and properties of semiconductors A review," *Physics of Semiconductor Devices. John Wiley Sons*, pp. 5–75, 2006, doi: 10.1002/9780470068328.ch1.

- [26] Xiaoer Hu. Micro-Electro-Mechanical Relay Technology for Beyond-Von-Neumann Computer. PhD thesis, EECS Department, University of California, Berkeley, May 2017. URL: <a href="https://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-251.html">https://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-251.html</a>

- [27] X. Hu, S. F. Almeida, Z. Alice Ye, and T. -J. K. Liu, "Ultra-Low-Voltage Operation of MEM Relays for Cryogenic Logic Applications," *IEEE International Electron Devices Meeting (IEDM)*, pp. 34.2.1-34.2.4, 2019, doi: 10.1109/IEDM19573.2019.8993629.

- [28] O. Y. Loh and H. D. Espinosa, "Nanoelectromechanical Contact Switches," *Nature Nanotechnology*, vol. 7, no. 5, p. 283, 2012, doi: 10.1038/nnano.2012.40.

- [29] J. E. Jang, S. N. Cha, Y. J. Choi, D. J. Kang, T. P. Butler, D. G. Hasko, J. E. Jung, J. M. Kim, and G. A. Amaratunga, "Nanoscale Memory Cell Based on a Nanoelectromechanical Switched Capacitor," *Nature Nanotechnology*, vol. 3, no. 1, p. 26, 2008, doi: 10.1038/nnano.2007.417.

- [30] B. Osoba et al., "Sub-50 mV NEM Relay Operation Enabled by Self-Assembled Molecular Coating," *IEEE International Electron Devices Meeting*, pp. 26.8.1-26.8.4, 2016, doi: 10.1109/IEDM.2016.7838489.

- [31] S. W. Lee, S. J. Park, E. E. Campbell, and Y. W. Park, "A Fast and Low-Power Microelectromechanical System-Based Non-Volatile Memory Device," *Nature Communications*, vol. 2, p. 220, 2011, doi: 10.1038/ncomms1227.

- [32] B. Halak, M. Zwolinski, and M. S. Mispan, "Overview of PUF-Based Hardware Security Solutions for the Internet of Things," *IEEE 59th International Midwest Symposium on Circuits and Systems (MWSCAS)*, pp. 1-4, 2016, doi: 10.1109/MWSCAS.2016.7870046.

- [33] W. Trappe, R. Howard, and R. S. Moore, "Low-Energy Security: Limits and Opportunities in the Internet of Things," *IEEE Security & Privacy*, vol. 13, no. 1, pp. 14-21, Jan.-Feb. 2015, doi: 10.1109/MSP.2015.7.

- [34] R. Maes, "Physically Unclonable Functions: Properties. In: Physically Unclonable Functions," Berlin, Heidelberg: Springer, pp. 49-80, 2013, doi: 10.1007/978-3-642-41395-7\_3.

- [35] F. Zahoor, T.Z. Azni Zulkifli, and F.A. Khanday, "Resistive Random Access Memory (RRAM): an Overview of Materials, Switching Mechanism, Performance, Multilevel Cell (mlc) Storage, Modeling, and Applications," *Nanoscale Res Lett*, vol. 15, no. 90, 2020, doi: 10.1186/s11671-020-03299-9.

- [36] A. Calderoni, S. Sills, and N. Ramaswamy, "Performance comparison of O-based and Cu-based ReRAM for high-density applications," *IEEE 6th International Memory Workshop (IMW)*, pp. 1-4, 2014, doi: 10.1109/IMW.2014.6849351.

- [37] F. Pan, C. Chen, Z. Wang, Y. Yang, J. Yang, F. Zeng, "Nonvolatile Resistive Switching Memories-Characteristics, Mechanisms and Challenges," *Progress in Natural Science: Materials International*, vol 20, pp. 1-15, 2010, doi:10.1016/S1002-0071(12)60001-X.

- [38] ReRAM Memory Overview: Crossbar Inc. URL: <a href="https://www.crossbar-inc.com/technology/reram-overview/">https://www.crossbar-inc.com/technology/reram-overview/</a>.

# Chapter 2

# A Reprogrammable MEM Switch Utilizing Controlled Contact Welding

#### 2.1 Introduction

With the emergence of the Internet of Things (IoT), the number of electronic devices has rapidly increased, and the volume of generated data has grown exponentially. The IoT refers to a network of objects that are wirelessly connected together. This is made possible by embedding into the objects ("things") electronic information processing devices, sensors, actuators, *etc.* for the purpose of communicating data and information with other objects. The number of IoT devices worldwide is forecast to almost triple from 9.7 billion in 2020 to more than 29 billion IoT devices in 2030 [1], when the total amount of data generated would be approximately 10 times more than exists today [2].

With the proliferation of IoT devices, as well as "edge" and cloud computing, electricity consumption of electronics is growing at an exponential pace. Therefore, new computing and memory device technologies are needed to enable much more energy-efficient digital computing and non-volatile (NV) data storage [3]. For IoT applications, low manufacturing cost is also an important requirement.

Micrometer-scale electro-mechanical (MEM) switches are considered an attractive option for IoT applications and wearable/disposable electronics due to their negligible OFF-state power consumption and abrupt switching characteristics enabling zero standby power consumption and milli-Volt operation across a wide range of operating temperatures [4–6]. MEM switches can be fabricated using standard CMOS integrated circuit manufacturing processes and can be designed to be non-volatile, *e.g.*, serving as reconfigurable interconnects [7], [8].

In this chapter, MEM switches designed for digital logic applications are demonstrated to be multi-time programmable via controlled contact welding and un-welding. This newfound capability provides for greater versatility of device operation, enabling non-volatile information storage to be embedded with digital logic circuitry with no incremental fabrication cost.

## 2.2 MEM Switch Operation

MEM switches operate by making and breaking physical contact between two conductive electrodes, separated physically by an air gap in the OFF-state. As shown in Figure 2.1, the movable top structure is referred to as the gate, which is mechanically suspended by a spring with effective spring constant  $k_{eff}$  while the underlying fixed electrode is referred as the body.  $g_d$  and  $g_o$  are the as-fabricated contact gap size and the actuation gap size, respectively.

Figure 2.1: Schematic diagram and mechanical spring model of a four-terminal MEM switch designed for digital logic applications. Electrostatic actuation and spring restoring forces are illustrated.

In the OFF-state, an air gap exists between the drain and source conductive electrodes, preventing any current flow. When a voltage is applied across the gate and body  $(V_{GB})$ , an attractive electrostatic force  $F_{elec}$  is exerted on the top movable gate electrode toward the fixed body electrode. Displacement of the gate electrode from its equilibrium position produces a spring restoring force  $(F_{sp})$  opposing the electrostatic force  $(F_{elec})$ :

$$F_{sp} = -k_{eff} \times g \tag{2.1}$$

where g is the displacement of the top electrode from its original position towards the bottom fixed electrode. (The negative sign of the spring restoring force indicates that the force is in the upward direction.)

$$F_{elec} = \frac{1}{2} \frac{\varepsilon_0 A_{ACT} V_{GB}^2}{(g_0 - g)^2} \tag{2.2}$$

where  $\varepsilon_o$  is the vacuum permittivity,  $A_{ACT}$  is the effective actuation (overlap) area, and  $V_{GB}$  is the potential difference between the gate and body electrodes. The net force  $F_{net}$  on the gate electrode is given by:

$$F_{net} = F_{sp} + F_{elec}$$

$$= -k_{eff} \times g + \frac{1}{2} \frac{\varepsilon_0 A_{ACT} V_{GB}^2}{(g_0 - g)^2}$$

(2.3)

Taking a derivative with respect to g, one obtains the following equation:

$$\frac{dF_{net}}{dg} = -k_{eff} + \frac{\varepsilon_0 A_{ACT} V_{GB}^2}{(g_0 - g)^3}$$

(2.4)

As the applied voltage  $V_{GB}$  is increased, the movable structure is physically displaced (g > 0) to maintain force balance  $(F_{net} = 0)$ . However, since the electrostatic force  $(F_{elec})$  increases superlinearly while  $|F_{sp}|$  increases linearly with decreasing actuation gap size  $(g - g_o)$ , eventually g reaches a critical value beyond which force balance is no longer possible and the movable structure is "pulled-in" to contact. The value of  $V_{GB}$  at which this phenomenon occurs is referred to as the pull-in voltage  $V_{PI}$ . Both  $V_{PI}$  and the critical displacement g can be calculated by setting  $F_{net}$  and  $\frac{dF_{net}}{dg}$  equal to 0 in Equations 2.3 and 2.4:

$$V_{PI} = \sqrt{\frac{8k_{eff}g_o^3}{27\varepsilon_o A_{ACT}}} \tag{2.5}$$

$$g = \frac{g_o}{3} \tag{2.6}$$

For the MEM switch to operate in pull-in (PI) mode, the as-fabricated contact gap size  $g_d$  should be greater than 1/3 of the as-fabricated actuation gap size  $g_o$  [3][4][6]. If the as-fabricated contact gap size  $g_d$  is less than  $g_o/3$ , (i.e.,  $g_o>3g_d$ ), however, then the switch turns ON before it enters into the PI region of operation, i.e., it operates in non-pull-in (NPI) mode. The applied voltage required to turn on a NPI MEM switch is

$$V_{ON} = \sqrt{\frac{2k_{eff}(g_o - g_d)^2}{\varepsilon_o A_{ACT}}}$$

(2.5)

In the ON-state there exists an attractive contact adhesive force  $F_{adh}$  between the contacting source and drain electrode surfaces, so the net force equation becomes

$$F_{net} = F_{sp} + F_{elec} + F_{adh} (2.6)$$

If the contacting surfaces comprise the same material, then the adhesive force is due primarily to Van der Waals force which is proportional to the apparent contact surface area [9,10].

Note that  $F_{adh}$  is additive to  $F_{elec}$ , *i.e.*, it helps to keep the MEMS switch in the ON–state. For this reason, the minimum value of applied voltage required to keep the MEMS switch ON is less than  $V_{ON}$ . That is, a MEM switch exhibits hysteretic switching behavior. The spring restoring force of the movable plate must overcome both the electrostatic force and the contact adhesive force in order to turn off the MEMS switch:

$$k_{eff}g = \frac{1}{2} \frac{\varepsilon_o A_{ACT} V_{OFF}^2}{(g_o - g)^2} + F_{adh}$$

(2.7)

$$V_{OFF} = \sqrt{\frac{2(k_{eff}g_d - F_{adh})(g_o - g_d)^2}{\varepsilon_o A_{ACT}}}$$

(2.8)

The hysteresis voltage is defined as

$$V_H = V_{ON} - V_{OFF} \tag{2.9}$$

and is the minimum actuation voltage-swing required to operate the MEMS switch.

Solving for  $V_H$  for a NPI-mode switch with  $g_d \leq \frac{g_o}{3}$ :

$$V_{H} \approx F_{adh} \sqrt{\frac{2g_{d}}{\varepsilon_{o} A_{ACT} k_{eff}}}$$

(2.10)

Previous studies indicate that PI-mode switch designs can provide for the lowest switching energy due to a relatively compliant (lower  $k_{eff}$ ) structure. However, this makes them prone to stuck-ON failure (i.e.,  $F_{SP} < F_{adh}$ ) [11]. Therefore, to avoid stuck-ON failures, body-biased ( $V_{\rm B} > 0$ ) NPI-mode MEM switch designs with stiffer structures are more practical for reliable operation. Therefore NPI-mode switches are used for the work of this dissertation.

#### 2.3 MEM Switch Design and Fabrication Process

Figure 2.2 is a plan-view scanning electron micrograph (SEM) image of a fabricated MEM switch; it is designed for digital logic applications and comprises two electrical switches and hence has two pairs of source/drain contact electrodes [6].

Figure 2.2: Plan-view scanning electron micrograph (SEM) image of a fabricated MEM switch.

As shown in the schematic cross-sectional views in Figure 2.3, the 2-contact (2C) device comprises a movable gate electrode suspended by four folded-flexure beams over a fixed body electrode. The drain electrodes are attached to and routed underneath the gate electrode and electrically insulated from it by an Al<sub>2</sub>O<sub>3</sub> gate-dielectric layer.

Figure 2.3: Schematic cross-sectional views along A-A' cutline in Fig. 2.2: (a) OFF–state (b) ON–state.

In the OFF-state (Fig. 2.3 (a)), the as-fabricated air gap separates the conductive drain and source electrodes, so that no current can flow between them. The movable gate is electrostatically actuated downward toward the body electrode when a voltage is applied between the gate and body  $(V_{GB})$ . When  $V_{GB}$  is larger than the turn-on voltage  $(V_{ON})$ , the electrostatic force overcomes the opposing spring restoring force of the folded flexure beams. This causes each of the drain

electrodes comes into physical contact with its underlying source electrode, allowing current  $(I_{DS})$  to flow under the influence of an applied voltage between the drain and source electrodes  $(V_{DS})$ . This state is referred to as the ON–state (Fig. 2.3 (b)).

To turn off the switch,  $V_{\rm GB}$  is reduced toward 0V so that the spring restoring force  $(F_{sp})$  of the folded flexure beams actuates the movable structure upward, causing the drain and source electrodes to break contact. The voltage at which  $I_{DS}$  drops back to zero is referred to as the turn-off voltage  $(V_{OFF})$ . Due to contact adhesive force between the contacting surfaces,  $V_{OFF}$  is always smaller than  $V_{ON}$ . The hysteresis voltage  $(V_H)$  is defined as  $V_{ON} - V_{OFF}$ .

Figure 2.4 illustrates key steps of the MEM switch fabrication process along cutlines B-B', C-C', and D-D' of Figure 2.2. The MEM switches are fabricated using conventional planar processing techniques with a maximum substrate temperature below 450 °C for compatibility with post-CMOS integration [4]. Initially, an 80 nm-thick  $Al_2O_3$  layer is deposited on a silicon substrate using an atomic layer deposition (ALD) system (Fig. 2.4 (a)). Next, a 60 nm-thick tungsten (W) layer is deposited by sputtering (Figure 2.4 (b)) and patterned to form the fixed body electrodes, drain electrodes, and source electrodes as shown in Figure 2.4 (c). Then, a 160 nm-thick sacrificial low-temperature deposited  $SiO_2$  layer (LTO<sub>1</sub>) is deposited using low pressure chemical vapor deposition (LPCVD), followed by contact "dimple" region definition (Fig. 2.4 (d)). A second sacrificial layer of 60 nm-thick  $SiO_2$  layer (LTO<sub>2</sub>) is then deposited and routing via regions are defined (Fig. 2.4 (e)). Note that the thickness of the second layer determines the as-fabricated air gap thickness between the drain electrode and the source electrode in the contact regions ( $g_d$ ) while the combined thickness of LTO<sub>1</sub> and LTO<sub>2</sub> layers determines the as-fabricated actuation airgap thickness ( $g_0$ ) between the movable structure and the body electrode.

Afterwards, a second 60 nm-thick tungsten is deposited and patterned to form drain electrodes (Fig. 2.4 (f)). Next, a 55 nm-thick gate-insulating  $Al_2O_3$  is deposited and patterned to define anchor regions (Fig. 2.4 (g)). A 1.9  $\mu$ m-thick p-type heavily *in-situ* doped polycrystalline- Si<sub>0.4</sub>Ge<sub>0.6</sub> (poly-SiGe) structural layer is then deposited using LPCVD and patterned to form the movable gate electrode (Fig. 2.4 (h)). Finally, the structural layer is released by selectively removing the sacrificial LTO layers using vapor hydrofluoric acid (HF). In this work,  $g_d$  is designed to be less than one third of  $g_o$  so that the MEM switch operates in non-pull-in mode, which is beneficial for minimizing  $V_H$  [12].