## PLL Design for FMCW Radar Systems

Benyuanyi Liu Ali Niknejad, Ed. Sophia Shao, Ed. Liwei Lin, Ed.

## Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2024-106 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2024/EECS-2024-106.html

May 15, 2024

Copyright © 2024, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Acknowledgement

First of all, I would like to thank my advisor, Prof. Ali M. Niknejad, for his patience, guidance, and support over the years. There are ups and downs in the PhD journey, but he always encourages me to move forward. Discussions with him are always enlightening, from which I gain insights into circuits and the key problems that need solving. The same goes for his classes. Explanations, examples, and analogies help me understand the physics and circuitry intuitively. I feel very lucky to have spent my time in his group.

I wish to thank Prof. Sophia Shao, Prof. Liwei Lin, and Dr. Osama Shana'a, for being on my qualifying exam committee and dissertation committee. Their feedback is very valuable for my research.

PLL Design for FMCW Radar Systems

By

Benyuanyi Liu

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Liwei Lin Professor Sophia Shao

Spring 2024

PLL Design for FMCW Radar Systems

Copyright 2024 by Benyuanyi Liu

#### Abstract

#### PLL Design for FMCW Radar Systems

By

#### Benyuanyi Liu

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor Ali M. Niknejad, Chair

In this thesis, the PLL design for FMCW radar systems is illustrated. The FMCW radar imposes requirements on the PLL-based chirp generator in several aspects. Both the phase noise and the bandwidth of the PLL influence the measurement accuracy and resolution of the radar. The phase noise should be minimized, given a certain power consumption, and the bandwidth needs to be matched with the FMCW chirp slope to achieve better linearity.

For system-level design, unlike PLLs for other applications, the output of the chirp generator PLL is always changing. In many applications, such as precision measurement, the output never truly settles at each step. This necessitates careful modeling of the loop dynamics. In this thesis, conventional PLL phase noise and settling time models are presented and adapted for the chirp generator. However, these models are insufficient for optimizing the design. Therefore, a more accurate time-domain model for calculating the chirp is proposed. This model aids in designing the PLL bandwidth, calculating the acceptable chirp slope for a given PLL, and computing the dynamic phase noise. To the best of our knowledge, this is the first relatively accurate model for the entire chirp generation process.

For the design of circuit blocks, the frequency division modules, which include a dualmodulus divider and a Delta-Sigma Modulator, are presented. For the high-frequency circuit, an analytical model and a corresponding design methodology are proposed. The PLL has been taped-out, and measurements will be conducted to confirm the performance and design methodology. To my family

# Contents

| Co       | ontents                                                                                                                                                                                                       | ii                                     |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Li       | st of Figures                                                                                                                                                                                                 | iv                                     |

| Li       | st of Tables                                                                                                                                                                                                  | vii                                    |

| 1        | Introduction         1.1       Introduction to FMCW Radar                                                                                                                                                     | 3<br>11<br>11                          |

| 2        | PLL Architecture and System-level Modeling         2.1       Architecture of Proposed PLL         2.2       System-level Modeling         2.3       PLL Specifications         2.4       Conclusion           | $\begin{array}{c} 17\\ 33 \end{array}$ |

| 3        | Linearity and Settling Model         3.1       Practical Chirp         3.2       Modeling         3.3       Calculation Results and Chirp Linearity         3.4       Discussion         3.5       Conclusion | 37<br>42<br>47                         |

| 4        | Frequency Division         4.1       Dual-Modulus Divider       .         4.2       Delta-Sigma Modulator       .         4.3       Simulation Results       .         4.4       Conclusion       .           | $52 \\ 57$                             |

| <b>5</b> | High-Frequency Circuit Design and Modeling                                                                                                                                                                    | <b>62</b>                              |

|         | 5.1              | Introduction                                               | 62       |  |  |  |  |  |  |

|---------|------------------|------------------------------------------------------------|----------|--|--|--|--|--|--|

|         | 5.2              | Analytical Delay Model Derivation                          | 63       |  |  |  |  |  |  |

|         | 5.3              | Transistor Stacking                                        | 67       |  |  |  |  |  |  |

|         | 5.4              | Modeling the Effective Mobility                            | 68       |  |  |  |  |  |  |

|         | 5.5              | Delay Model Validation                                     | 70       |  |  |  |  |  |  |

|         | 5.6              | Conclusion                                                 | 74       |  |  |  |  |  |  |

| 6       | Pro              | totype and Measurement Plan                                | 76       |  |  |  |  |  |  |

|         | 6.1              | Prototype                                                  | 76       |  |  |  |  |  |  |

|         | 6.2              | Measurement Plan                                           | 77       |  |  |  |  |  |  |

| 7       | 7 Conclusions    |                                                            |          |  |  |  |  |  |  |

|         |                  |                                                            |          |  |  |  |  |  |  |

| Bi      | bliog            | graphy                                                     | 79       |  |  |  |  |  |  |

|         |                  | graphy<br>dices                                            | 79<br>87 |  |  |  |  |  |  |

| Al      | ppen             |                                                            |          |  |  |  |  |  |  |

| Al      | open<br>Ma       | dices                                                      | 87       |  |  |  |  |  |  |

| Al<br>A | ppen<br>Ma<br>Ma | dices<br>tlab Code for Noise and Settling Time Calculation | 87<br>88 |  |  |  |  |  |  |

# List of Figures

| 1.1  | Single chip integration enabled by CMOS                                           | 3 |

|------|-----------------------------------------------------------------------------------|---|

| 1.2  | Block diagram of a general FMCW radar system.                                     | 3 |

| 1.3  | Frequency chirp for FMCW radar.                                                   | 4 |

| 1.4  | Range measurement of a single object.                                             | 5 |

| 1.5  |                                                                                   | 6 |

| 1.6  | Two objects with equal distance to the radar, but different radial velocities     | 7 |

| 1.7  | Range-Doppler signal processing in FMCW radar system.                             | 8 |

| 1.8  | Angle measurement based on two RX antennas.                                       | 8 |

| 1.9  | Angle measurement of a single object.                                             | 9 |

| 1.10 | Two objects have equal distance from the data and equal velocity towards the      |   |

|      | radar                                                                             | 0 |

| 1.11 | Angle FFT based on rangle-Doppler map.    10                                      | 0 |

| 2.1  | LiDAR module on a car with advanced driving assistance function                   | 6 |

| 2.2  | Block diagram of charge-pump PLL                                                  | 7 |

| 2.3  | Reference-modulated PLL-based chirp generator                                     | 8 |

| 2.4  | Division-ratio-modulated PLL-based chirp generator                                | 8 |

| 2.5  | Generated chirp with different bandwidth. (a) PLL bandwidth is too narrow (b)     |   |

|      | PLL bandwidth is suitable (c) PLL bandwidth is too wide                           | 9 |

| 2.6  | Phase-domain model of charge-pump PLL with main noise sources                     | 0 |

| 2.7  | Phase noise spectrum of reference signal                                          | 1 |

| 2.8  | Simplified schematic of charge pump                                               | 3 |

| 2.9  | Waveform of control signals, UP and DN                                            | 4 |

| 2.10 | Noise simulation setup for PFD and charge pump                                    | 5 |

| 2.11 | Schematic of NAND-gate PFD with dead-zone elimination buffer                      | 6 |

| 2.12 | Waveform of $UP$ and $DN$ signals when phase error (between reference and divided |   |

|      | signal) is $0$ . $\ldots$ $20$                                                    | 6 |

| 2.13 | Waveform of $UP$ and $DN$ signals when phase error (between reference and divided |   |

|      | signal) is $\frac{\pi}{2}$ or $\pi$                                               | 7 |

| 2.14 | Phase noise of PFD and charge pump at different phase error values                | 7 |

| 2.15 | Comparison between proposed model and simulation results                          | 8 |

| 2.16 | Comparison between proposed model and simulation results                          | 9 |

| 2.17 | Time-domain model of charge-pump PLL                                              | 9 |

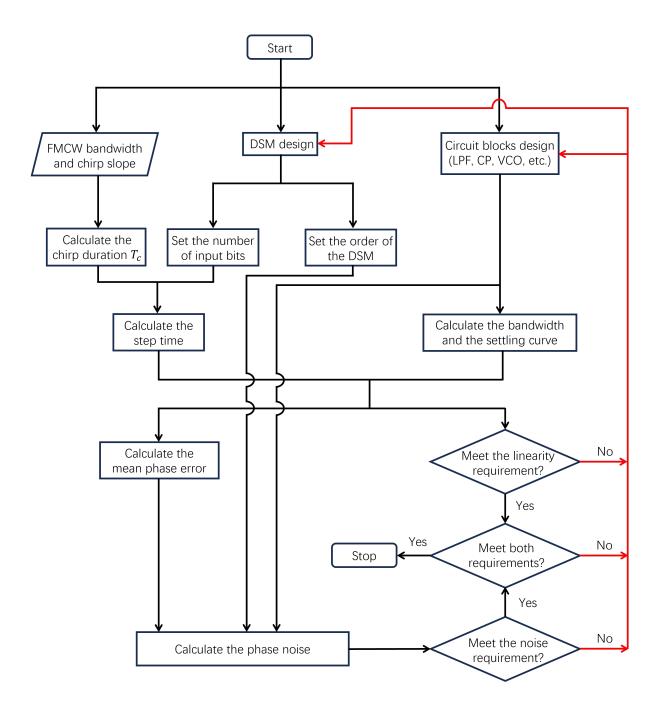

|              | Topology for (a) 2nd-order filter (b) 3rd-order filter (c) 4th-order filter Design flowchart of the system-level specifications. The red lines represent the                                      | 31              |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|              | process of design iteration.                                                                                                                                                                      | 34              |

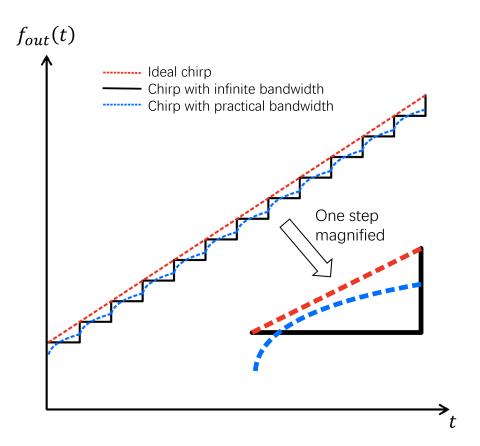

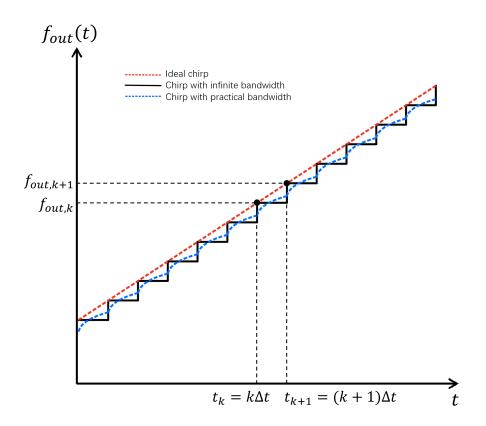

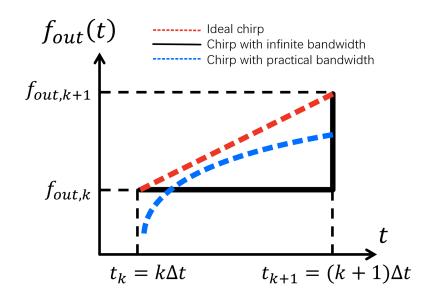

| $3.1 \\ 3.2$ | Ideal chirp and practical chirp. $\ldots$ The step to be analyzed is $k\Delta t \sim (k+1)\Delta t$ , where $t_k = k\Delta t$ and $t_{k+1} = (k+1)\Delta t$ .                                     | $\frac{37}{38}$ |

| 3.3          | The step $k\Delta t \sim (k+1)\Delta t$                                                                                                                                                           | 39              |

| 3.4          | The time-domain model of the PLL                                                                                                                                                                  | 39              |

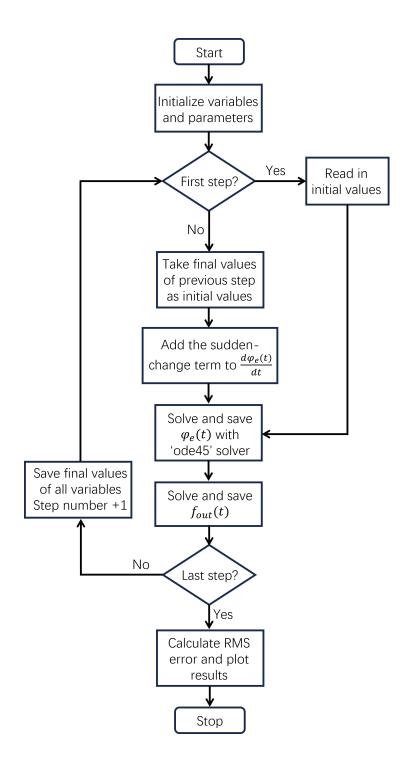

| 3.5          | The flow chart of calculating $f_{out}(t)$                                                                                                                                                        | 43              |

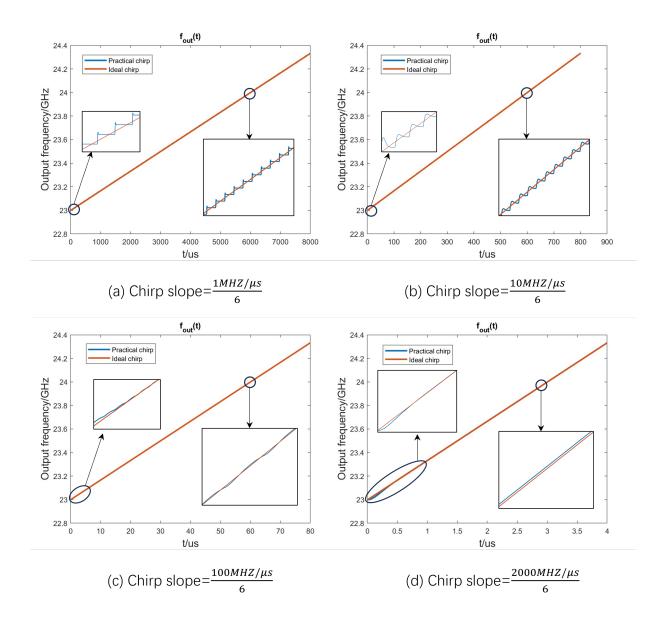

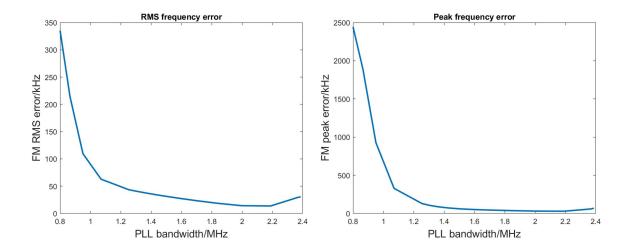

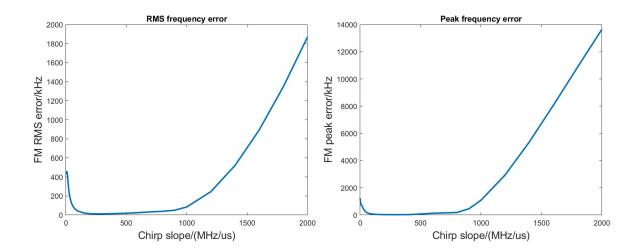

| $3.6 \\ 3.7$ | A PLL with 2.19MHz bandwidth at different chirp slopes. $\ldots$ Calculation results for 200MHz/ $\mu$ s FMCW chirp slope. Both RMS error and                                                     | 45              |

| 3.8          | peak error are plotted                                                                                                                                                                            | 46              |

|              | error are plotted.                                                                                                                                                                                | 47              |

| 4.1          | Chirp frequency and division ratio.                                                                                                                                                               | 51              |

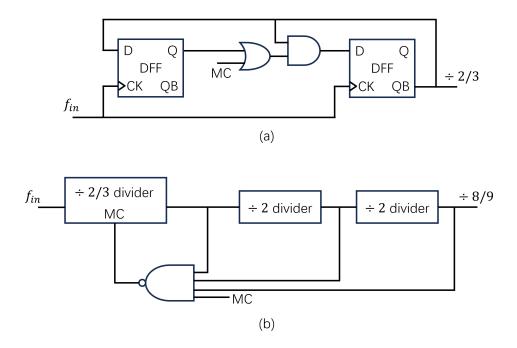

| 4.2          | (a) A divide-by- $2/3$ prescaler. (b) A $8/9$ dual-modulus frequency divider                                                                                                                      | 51              |

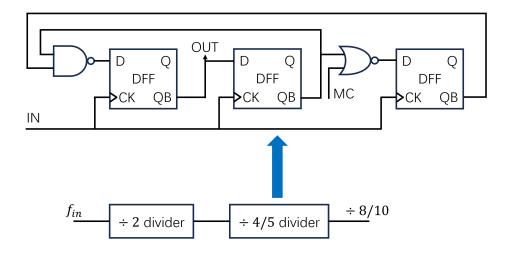

| 4.3          | The block diagram of divide-by- $8/10$ divider and schematic of the $4/5$ divider.                                                                                                                | 52              |

| 4.4          | Layout of the divide-by-8/10 divider.                                                                                                                                                             | 53              |

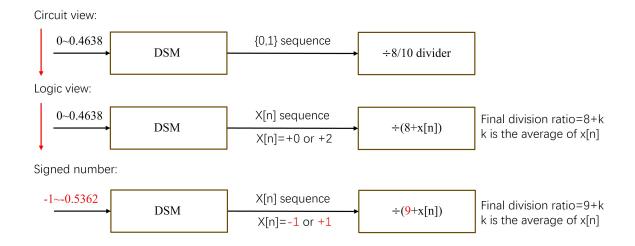

| 4.5          | Implementations of fractional-N division ratio.                                                                                                                                                   | 53              |

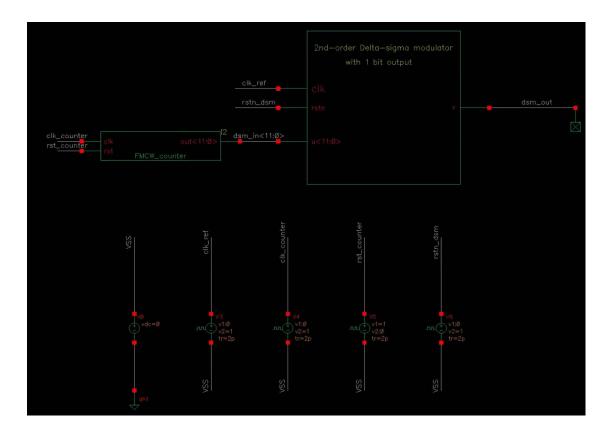

| 4.6          | Chirp generator with a Delta-Sigma Modulator.                                                                                                                                                     | 54<br>54        |

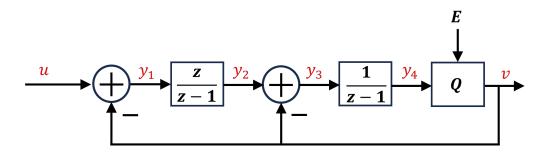

| 4.7<br>4.8   | 1-bit DSM controls the division ratio of the divide-by-8/10 divider Block diagram of the 2nd-order 1-bit output DSM                                                                               | $\frac{54}{55}$ |

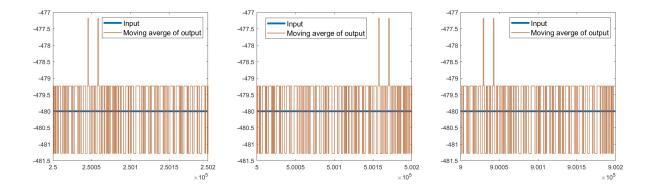

| 4.8<br>4.9   | Simulation results for DC input.                                                                                                                                                                  | $55 \\ 58$      |

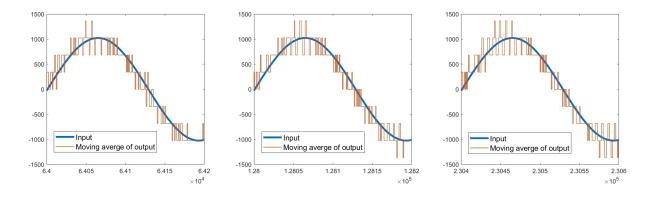

| 4.10         | Simulation results for sine-wave input.                                                                                                                                                           | 58              |

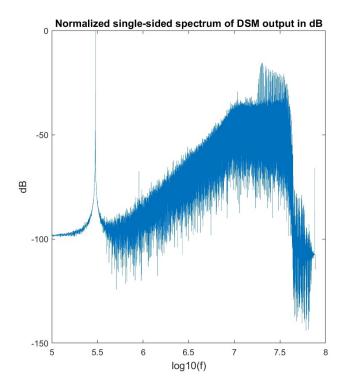

| 4.11         | Output spectrum with a sine-wave input.                                                                                                                                                           | 59              |

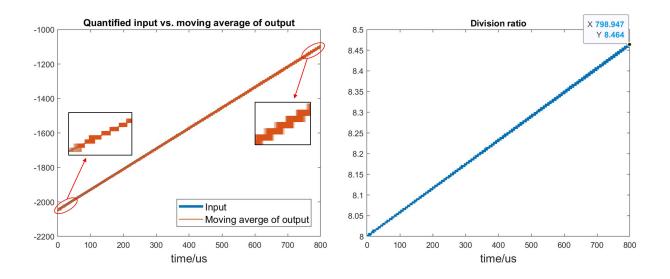

| 4.12         |                                                                                                                                                                                                   | 60              |

|              | Simulation setup for the sine-wave test                                                                                                                                                           | 60              |

|              | Simulation setup for the ramp test                                                                                                                                                                | 61              |

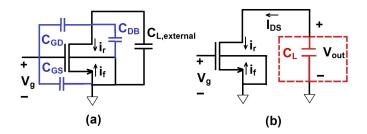

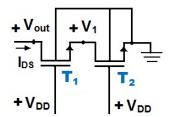

| 5.1          | Normalized forward and reverse terminal currents in NMOS transistor with (a) intrinsic capacitance network and external capacitance load, (b) lumped equivalent output load capacitance $(C_L)$ . | 64              |

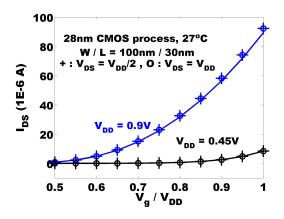

| 5.2          | Comparison of approximated drain current model Eq. $5.2$ (symbols) with exact                                                                                                                     | 04              |

|              | drain current model Eq. 5.1 (lines).                                                                                                                                                              | 65              |

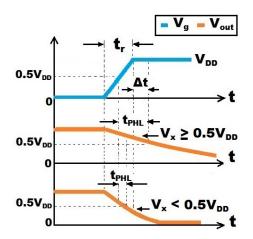

| 5.3          | Input and output waveform schematic.                                                                                                                                                              | 65              |

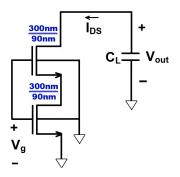

| 5.4          | NMOS transistor stacking.                                                                                                                                                                         | 67              |

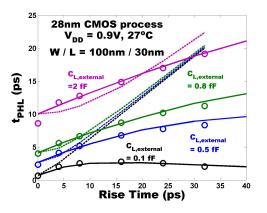

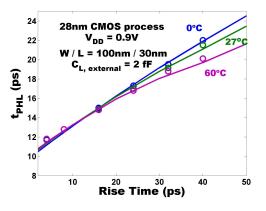

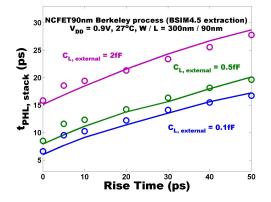

| 5.5          | Variation of delay with rise-time $(t_r)$ (Line: proposed model, symbol: simulation, dotted line: delay model in [1]).                                                                            | 70              |

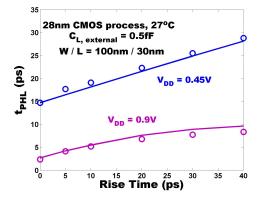

| 5.6          | Variation of delay with rise-time $(t_r)$ and bias voltage $(V_{DD})$ (Line: proposed model, symbol: simulation).                                                                                 | 70              |

|              |                                                                                                                                                                                                   |                 |

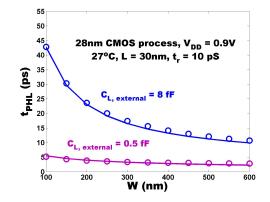

| 5.7  | Variation of delay with NMOS channel width $(W)$ and capacitive load $(C_{L,external})$                                                                           |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | (Line: proposed model, symbol: simulation).                                                                                                                       | 71 |

| 5.8  | Variation of delay with rise time $(t_r)$ and temperature (Line: proposed model, symbol: simulation).                                                             | 72 |

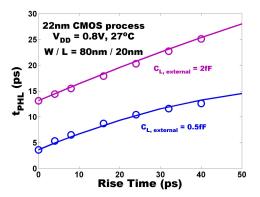

| 5.9  | Variation of delay with rise time $(t_r)$ using 22nm CMOS process (Line: proposed model, symbol: simulation).                                                     | 72 |

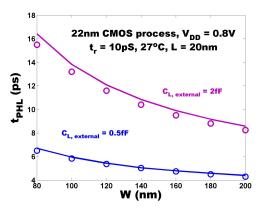

| 5.10 | Variation of delay with channel width $(W)$ using 22nm CMOS process (Line:                                                                                        |    |

| 5.11 | proposed model, symbol: simulation)                                                                                                                               | 73 |

|      | cess (BSIM4.5 extraction) (Line: proposed model, symbol: simulation)                                                                                              | 73 |

| 5.12 | Schematic of the two transistor stack connected to an effective capacitive load $(C_L)$                                                                           | 74 |

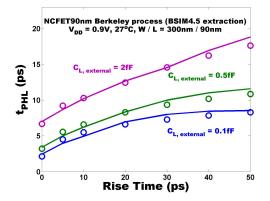

| 5.13 | Variation of delay with rise time $(t_r)$ for a 2 transistor stack (Fig. 5.12) using<br>in-house Berkeley 90nm NCFET process (BSIM4.5 extraction) (Line: proposed |    |

|      | model, symbol: simulation)                                                                                                                                        | 74 |

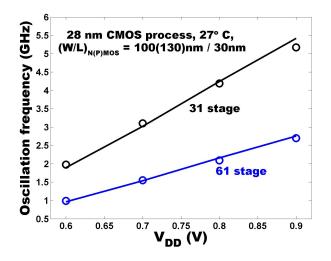

| 5.14 | Variation of Ring Oscillator oscillation frequency with supply voltage $V_{DD}$ (Line: proposed model, symbol: simulation).                                       | 75 |

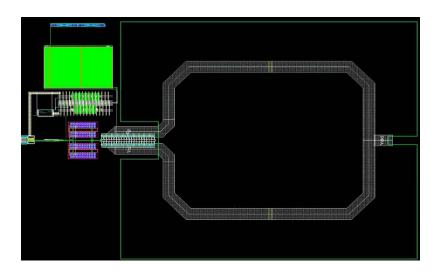

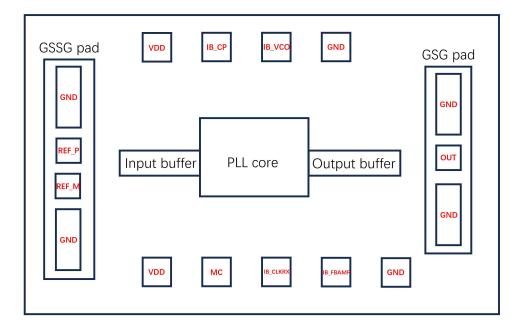

| 6.1  | Layout of the proposed PLL core                                                                                                                                   | 76 |

| 6.2  | Pads of the taped-out chip.                                                                                                                                       | 77 |

vi

# List of Tables

| 1.1 | State-of-the-art FMCW radar systems in F-band (90-140GHz), D-band (110-                                |    |

|-----|--------------------------------------------------------------------------------------------------------|----|

|     | 170GHz), and G-band (110-300GHz)                                                                       | 2  |

| 1.2 | State-of-the-art PLLs for FMCW radar systems                                                           | 13 |

| 0.1 | $\mathbf{D}$ , $\mathbf{D}$ , $\mathbf{D}$ , $\mathbf{D}$ , $\mathbf{D}$ , $\mathbf{D}$ , $\mathbf{D}$ | 00 |

| 2.1 | Phase noise chart of Keysight E8267D in dBc/Hz                                                         | 20 |

| 2.2 | Coefficients for 2nd-, 3rd, and 4th-order low-pass filter transfer function                            | 31 |

| 2.3 | FMCW chirp specifications.                                                                             | 33 |

| 2.4 | PLL specifications.                                                                                    | 33 |

| 5.1 | Variables involved in $\mu_{eff}^{(t_r)}$ modeling                                                     | 69 |

#### Acknowledgments

During my time at UC Berkeley as a graduate student, I have received guidance, help, and support from many people. In my PhD journey, I have been working in several fields, and it would have been impossible to learn quickly without their help. I'd like to express my thanks to them at the beginning of my thesis.

First of all, I would like to thank my advisor, Prof. Ali M. Niknejad, for his patience, guidance, and support over the years. There are ups and downs in the PhD journey, but he always encourages me to move forward. Discussions with him are always enlightening, from which I gain insights into circuits and the key problems that need solving. The same goes for his classes. Explanations, examples, and analogies help me understand the physics and circuitry intuitively. I feel very lucky to have spent my time in his group.

I wish to thank Prof. Sophia Shao, Prof. Liwei Lin, and Dr. Osama Shana'a, for being on my qualifying exam committee and dissertation committee. Their feedback is very valuable for my research.

I would also like to thank all BWRC staff, Ajith Amerasekera, Anita Flynn, Brian Richards, Jeff Anderson, James Dunn, Candy Corpus, and Mikaela Cavizo, for their help with my research and for making my life at BWRC much easier. In particular, I want to thank Candy Corpus and Mikaela Cavizo for ensuring all kinds of events run smoothly. Brian Richards and James Dunn have helped me a lot with CAD tool settings. Anita Flynn has made a tremendous contribution by keeping the lab clean and well-organized.

BWRC is a place where everyone can learn from everyone. I wish to thank BWRC students for their help, discussion, cooperation, and feedback. I thank Bo Zhao, Lorenzo Iotti, and Ananda Sankar Chakraborty for their help on my research. They were postdocs when I worked with them in different research projects and each of them taught me a lot on CAD tool usage, circuit and device modeling, design methodologies, and measurements. In particular, I would like to thank Ananda. He is both a research partner and a true friend of mine. The Zoom chats with him really relieve the stress and anxiety at the beginning of the COVID-19 pandemic. I also thank Nai-Chung Kuo, Greg Lacaille, Nima Baniasadi, Emily Navisky, Yi-an Li, Luya Zhang, Ali Ameri, Yikuan Chen, Rohit Braganza, Pengpeng Lu, Ali Moin, Zhongkai Wang, John Wright, Matthew Anderson, Jongbeom Baek, Hesham Beshary, Ethan Chou, Rami Hijab, Meng Wei, and Kunmo Kim, for their help on my research.

Last but not least, I would like to thank my parents and my wife for their love and support. They are completely behind me in my endeavors, and I couldn't have completed my PhD journey without them. I also want to thank my best friend, Yun Zhong, for the understanding, listening, help, support, funny chats, and brainstorming he provides. We have known each other for almost 20 years, and I couldn't feel luckier to have such a friend.

## Chapter 1

## Introduction

## 1.1 Introduction to FMCW Radar

In 1924, the first bistatic FMCW radar experiment was conducted by Appleton and Barnett to measure the height of the ionosphere [2], followed by the Daventry experiment in 1935 to detect aircraft [3]. During World War II, transmit-receive switch was invented and monostatic FMCW radars were built for bomb aiming and surveillance [4]. In mid 1970's, a major step forward was made as digital signal processing became available to perform the signal processing to extract information from the received signals [5]. Nowadays, FMCW radars have been widely used for civil applications (such as automotive applications [6] and gesture recognition [7]), industry measurements (such as altimeter [8], coating characterization [9], and level gaging [10]), and military applications (such as small drone detection [11]).

Today, state-of-the-art FMCW radar systems are implemented with CMOS and SiGe technologies, and both have their pros and cons.  $f_T$  and  $f_{max}$  of advanced SiGe process are higher than those of CMOS process that has comparable cost [12]. And higher  $f_T/f_{max}$  makes it more feasible to achieve both lower power and higher performance simultaneously. Because to achieve the same performance, high- $f_T/f_{max}$  devices consume less current. And with the same current consumption, high- $f_T/f_{max}$  devices could achieve better performance [13]. Another difference between CMOS devices and SiGe devices is maximum allowable bias voltage. The collector-base breakdown voltage of SiGe devices keeps above 4V with increasing RF performance while maximum supply voltage of CMOS devices rapidly decreases with more advanced nodes [14]. Low supply voltage of CMOS devices is excellent for reducing power consumption for digital circuits, but it also makes it more and more difficult to transmit RF power out at the cost of higher current level. However, from the perspective of radar system, CMOS process still has advantage of higher integration level. Shown in Fig. 1.1 is an example for automotive radar [15]. Today's high-end vehicles feature a multichip SiGe radar system. But as the number of sensors increases to at least ten, the big and bulky multichip SiGe

| Technology                    | MIT,<br>JSSC<br>2021<br>[17]<br>65nm<br>CMOS<br>1TX, | Toronto,<br>TMTT<br>2021<br>[18]<br>22nm<br>FDSOI<br>2TX, | Ulm,<br>TMTT<br>2019<br>[19]<br>SiGe<br>1TX, | Ulm<br>JSSC<br>2021<br>[20]<br>SiGe<br>1TX, | IMEC,           ISSCC           2019           [21]           28nm           CMOS           1TX, | Wuppertal,<br>Trans.<br>THz 2016<br>[22]<br>SiGe<br>1TX, | MIT,<br>ISSCC<br>2022<br>[23]<br>65nm<br>CMOS<br>1TX,<br>1RX |

|-------------------------------|------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------|

| Architecture                  | 1RX<br>Fre-<br>quency<br>comb                        | 2RX<br>Stepped-<br>frequency<br>chirp                     | 1RX<br>MMIC-<br>based                        | 1RX<br>Leakage<br>sup-<br>pression          | 1RX<br>Leakage<br>sup-<br>pression                                                               | 1RX<br>Circular<br>polariza-<br>tion                     | Low-<br>loss<br>duplex-<br>ing                               |

| Center frequency (GHz)        | 220                                                  | 151                                                       | 160                                          | 169                                         | 145                                                                                              | 240                                                      | 140                                                          |

| Chirp bandwidth (GHz)         | 100                                                  | 9                                                         | 16                                           | 20                                          | 13                                                                                               | 60                                                       | 14                                                           |

| Resolution (mm)               | 1.5                                                  | 17                                                        | 10                                           | 21                                          | 11                                                                                               | 2.57                                                     | 11                                                           |

| RX min. NF (dB)               | 22.2                                                 | 7.5-10                                                    | 25                                           | 15.5                                        | 8                                                                                                | 22.5                                                     | 12.9                                                         |

| Phase noise @1MHz<br>(dBc/Hz) | N/A                                                  | -107                                                      | -87                                          | -80                                         | -80                                                                                              | N/A                                                      | N/A                                                          |

| Chip size $(mm^2)$            | 5                                                    | 2.75                                                      | N/A                                          | 5.4                                         | 6.5                                                                                              | 3.2                                                      | 3.1                                                          |

| Power (mW)                    | 840                                                  | 1130<br>(chirp<br>synthe-<br>sizer<br>not in-<br>cluded)  | N/A                                          | 860                                         | 500                                                                                              | 1800                                                     | 405<br>(chirp<br>synthe-<br>sizer<br>not in-<br>cluded)      |

Table 1.1: State-of-the-art FMCW radar systems in F-band (90-140GHz), D-band (110-170GHz), and G-band (110-300GHz).

radar system solution becomes too space-consuming [16], making CMOS technology more appealing, which can integrate into one chip radar front ends, microcontrollers (MCUs), and digital signal processing (DSP) circuits. As some wireless sensing applications are putting an increasing demand on bandwidth. The industry is addressing this challenge in many ways, one of which is by moving to higher frequencies. SiGe is applied to build the transceivers to address these applications first, due to its performance advantages. Over time, bulk CMOS would catch up and address the applications with circuits that are more integratable with other parts of the radar system. Some state-of-the-art FMCW radars systems are summrized in Table. 1.1.

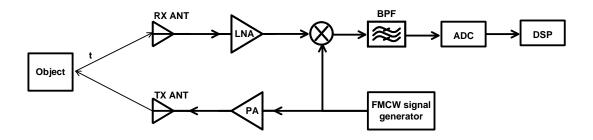

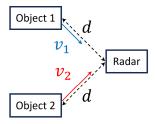

The traditional architecture of FMCW radar is very simple, as shown in Fig. 1.2. The FMCW signal is sent to both transmitter antenna and receiver mixer to get beat frequencies of objects. The frequency of the FMCW signal linearly ramps, so the distance is translated into frequency. Such an architecture leads to strong noise correlation, thus noise cancellation, for short-distance objects [24]. As distance increases, the correlation becomes weaker and noise cancellation is less.

Figure 1.1: Single chip integration enabled by CMOS.

Figure 1.2: Block diagram of a general FMCW radar system.

Based on the basic architecture, researchers proposed many variants to address issues for specific applications. [25] and [26] adopt adaptive algorithm to cancel the leakage and interference. Synthetic bandwidth technique is applied in [17] to achieve ultra-wide chirp bandwidth of 100GHz. [27] and [28] implement on-chip calibration to reduce gain mismatch and phase mismatch of complex baseband.

## 1.2 Operating Principle of FMCW Radar

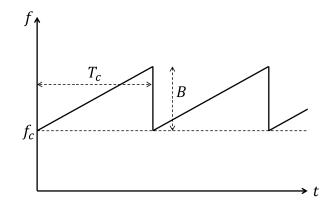

A complete FMCW radar system can measure range, velocity, and angle of multiple objects. For each measurement, the maximum measurement range and resolution are determined by system parameters. The FMCW radar measurements are based on transmitting frequency chirp, characterized by start frequency  $f_c$ , bandwidth B, and chirp duration  $T_c$  as shown in Fig. 1.3. And corresponding chirp slope is

$$S = \frac{B}{T_c} \tag{1.1}$$

Figure 1.3: Frequency chirp for FMCW radar.

### **Range Measurement**

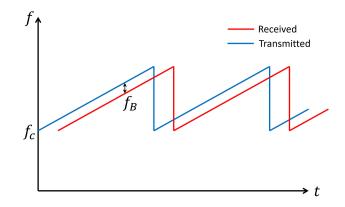

When a chirp is transmitted and then the electromagnetic wave (EM wave) is reflected back to the radar, the system would mix the transmitted signal and the received one, as shown in Fig. 1.4, getting a beat frequency  $f_B$  for each object. The one-way travelling time for EM wave from radar to the object is

$$t_0 = \frac{d}{c} \tag{1.2}$$

where d is the distance between the radar and the object, c the speed of light. And the round-trip travelling is  $2t_0$ , so the beat frequency  $f_B$  should be

$$f_B = 2t_0 \cdot S = S \cdot \frac{2d}{c} \tag{1.3}$$

In this way, the distance d can be calculated by measuring beat frequency  $f_B$ .

The maximum range is determined by FMCW chirp bandwidth B and IF sampling frequency  $F_s$ .

$$f_{B,max} = S \cdot \frac{2d_{max}}{c} < B \tag{1.4}$$

$$f_{B,max} = S \cdot \frac{2d_{max}}{c} < \frac{F_s}{2} \tag{1.5}$$

For multiple objects, according to Discrete Fourier Transform (DFT) theory, an observation window of  $T_c$  can separate frequency components that are separated by more than

Figure 1.4: Range measurement of a single object.

$\frac{1}{T_c}$ Hz, which means the frequency resolution is  $\frac{1}{T_c}$ . As a result, the range resolution is

$$\Delta d = \frac{c}{2B} \tag{1.6}$$

### Velocity Measurement

In terms of radial velocity measurement of moving objects, the beat frequency consists additionally of Doppler frequency  $f_D$

$$f_B = S \cdot \frac{2d}{c} + f_D = S \cdot \frac{2d}{c} + \frac{2v_r}{\lambda_c}$$

(1.7)

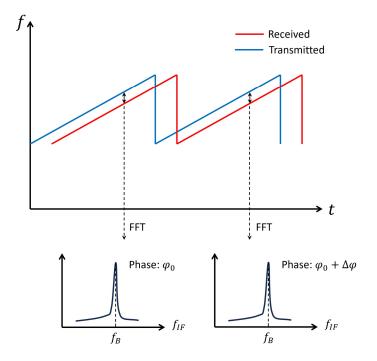

where  $\lambda_c$  is the corresponding wavelength of start frequency  $f_c$ . The beat frequency  $f_B$  from a single chirp contains unknowns of d and  $v_r$  in an unsolvable way. The principle of velocity measurement is that phase of the IF signal is very sensitive to small changes in object range, and that Doppler frequency's impact on beat frequency is negligible. As shown in Fig. 1.5, two chirps separated by  $T_c$  are transmitted, and received signal corresponding to each chirp will have the same beat frequency but different phases. The phase difference is  $\Delta \varphi$ :

$$\Delta \varphi = 2\pi f_D T_c = 2\pi \cdot \frac{\frac{2v_r T_c}{c}}{\frac{1}{f_c}} = \frac{4\pi v_r T_c}{\lambda_c}$$

(1.8)

$$v_r = \frac{\lambda_c \Delta \varphi}{4\pi T_c} \tag{1.9}$$

And the phase difference  $\Delta \varphi$  is positive when the object moves towards radar, and negative when moving away. As a result, to assure unambiguous velocity measurement,

Figure 1.5: Radial velocity measurement of a single object.

$$\Delta \varphi | < \pi \tag{1.10}$$

should be fulfilled, from which the maximum measurable velocity could be expressed as

$$|v_r|_{max} = \frac{\lambda_c}{4T_c} \tag{1.11}$$

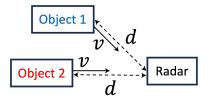

For multiple objects, in extreme cases where two objects have equal distance from the radar but different velocities as shown in Fig. 1.6, they need to be distinguished by velocity, which can be done with Doppler FFT.

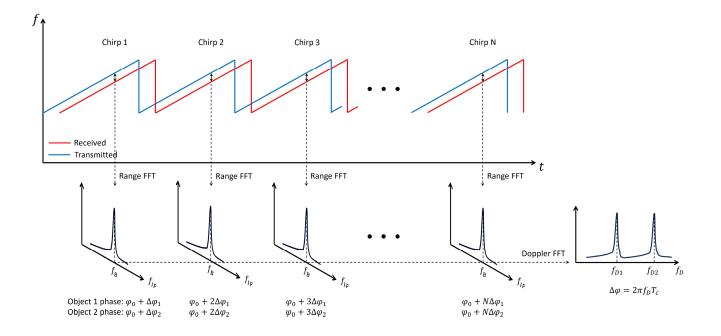

Shown in Fig. 1.7, is range-Doppler processing in FMCW radar system. N chirps are transmitted, and after mixing the transmitted signal with received one, range FFT are conducted to get the spectrum of IF signal. Object 1 and object 2 are not distinguishable on this spectrum because their beat frequencies are equal (equal distance). Phase of IF signal contains velocity information. And for each IF frequency, there are N data points with different phases. Doppler FFT is conducted to such set of phase data of each IF frequency, giving us a 2-dimensional range-Doppler map. In the case described in above, Fig. 1.7 shows the Doppler FFT result of frequency  $f_B$ , on which object 1 and object 2 could be

Figure 1.6: Two objects with equal distance to the radar, but different radial velocities.

distinguished for their different radial velocities. Fig. 1.7 only shows the Doppler FFT result at the IF frequency of  $f_B$ . To get a complete range-Doppler map, Doppler FFT is conducted for each IF frequency point.

As for resolution of velocity measurement, as known, a sequency of length N can separate frequencies that are separated by more than  $\frac{2\pi}{N} rad/s$  after FFT, which is

$$2\pi\Delta f_D T_c = \frac{2\pi}{N} \tag{1.12}$$

and that gives the velocity resolution

$$\Delta v_r = \frac{\lambda_c}{2NT_c} = \frac{\lambda_c}{2T_f} \tag{1.13}$$

where  $T_f$  is the frame time and one frame consists of N chirps.

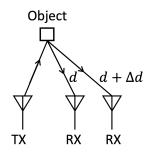

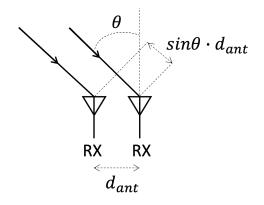

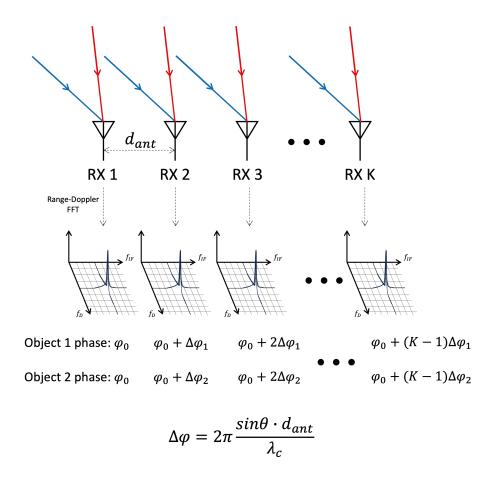

### Angle Measurement

Angle measurement requires at least two antennas. Similar to velocity measurement, the angle measurement is based on the fact that the phase of received signal is sensitive to difference of EM wave travelling time caused by non-zero incident angle, as shown in Fig. 1.8.

For a single object, Fig. 1.9 shows the measurement principle with two antennas. A frame of chirp is transmitted via a TX antenna, and when the EM wave bounces back, a range-Doppler map could be drawn for each RX antenna. The peaks on these maps would be at the same location because these two antennas are observing the same object with same distance and same velocity. But the phase of the received signal would be different due to different travelling time caused by  $sin\theta \cdot d_{ant}$  shown in Fig. 1.9. And corresponding phase difference is

$$\Delta \varphi = 2\pi \frac{\sin\theta \cdot d_{ant}}{\lambda_c} \tag{1.14}$$

Figure 1.7: Range-Doppler signal processing in FMCW radar system.

Figure 1.8: Angle measurement based on two RX antennas.

Figure 1.9: Angle measurement of a single object.

So the incident angle is

$$\theta = \sin^{-1}(\frac{\Delta \varphi \cdot \lambda_c}{2\pi d_{ant}}) \tag{1.15}$$

And to assure unambiguous angle measurement,

$$|\Delta\varphi| < \pi \tag{1.16}$$

which gives

$$|\theta|_{max} = \sin^{-1}(\frac{\lambda_c}{2d_{ant}}) \tag{1.17}$$

For multiple objects, K receiving antennas are needed to achieve certain angle resolution. Again, consider a extreme case shown in Fig. 1.10 where two objects have equal distance from the radar and equal radial velocity towards the radar. Thus, for each RX antenna, there will be only one peak on the range-Doppler map, as shown in Fig. 1.11. They can be distinguished from angle. In this case, angle FFT is applied to the phase sequence of the peak. And there would be two peaks in the resulting plot, one for object 1 and the other for 2.

For angle resolution, similarly to velocity resolution, the minimum distinguishable frequency separation is  $\frac{2\pi}{K}$ . And the "frequency" in angle FFT is the phase difference  $\Delta \varphi$  of the received signals

$$\Delta \varphi = \frac{2\pi d_{ant}}{\lambda_c} \cdot \left[ \sin(\theta + \Delta \theta) - \sin(\theta) \right]$$

(1.18)

$$\Delta \varphi \approx \frac{2\pi d_{ant}}{\lambda_c} \cos(\theta) \Delta \theta \tag{1.19}$$

Figure 1.10: Two objects have equal distance from the data and equal velocity towards the radar.

Figure 1.11: Angle FFT based on rangle-Doppler map.

Thus, the angle resolution is

$$\Delta \theta = \frac{\lambda_c}{K \cdot d_{ant} \cdot \cos(\theta)} \tag{1.20}$$

Conventionally, the angle resolution is quoted assuming  $\theta = 0$

$$\Delta \theta = \frac{\lambda_c}{K \cdot d_{ant}} \tag{1.21}$$

## **1.3** Frequency Synthesizers for FMCW Radar

Shown in the previous section are theoretical resolutions for range, velocity, and angle, assuming a perfect FMCW chirp. However, in real life, FMCW chirp has imperfections, among which nonlinearity and phase noise are the main factors that degrade resolution and contribute to measurement error.

Several types of frequency synthesizers (chirp generator) are applied to generate the chirp, and each of them has its pros and cons. Direct digital synthesizer (DDS) is the most straightforward way to generate a chirp [29]. It's a quick and easy solution for prototype testing, but it comes with high spur level and limited bandwidth.

For analog methods, the chirp generator could be implemented mainly in three ways, which are VCO-based frequency synthesizers [30], multiplier-based frequency synthesizers [31], and PLL-based frequency synthesizers. VCO-based frequency synthesizers suffer from nonlinearity issue, which requires compensation circuitry to correct the nonlinearity. Multiplier-based frequency synthesizers have low phase noise, but they suffer from nonlinearity and harmonic spurs issue, resulting in lower dynamic range. PLL-based frequency synthesizers have good linearity and low phase noise, which leads to good radar resolution with comparable hardware cost.

## 1.4 Design Needs of PLL-based Chirp Generator

There are several main design needs for PLLs in FMCW radar system, namely low phase noise, good linearity, fast chirp generation, and wide chirp bandwidth.

Phase noise of PLL has a great impact on FMCW radar performance [24]. In multi-target scenario, when objects are close to each other, larger in-band phase noise of PLL would lead to wider peak on IF spectrum for each object, making it harder to clearly distinguish objects, and thus lowering spatial resolution and the image quality. When objects are far from each other, larger out-of-band noise of PLL leads to higher noise tail from closer objects, which raises the noise floor for farther objects. That would make it more difficult to detect the farther objects, limiting the maximum detection range of FMCW radar.

In terms of frequency deviation and chirp linearity, phase noise contributes to the random frequency deviation, and other sources (such as digital circuit switching, PLL transient response, and nonlinear circuit blocks) contribute to the deterministic or even periodic frequency deviation. The resultant nonlinear chirp could be modeled as a sinusoidal nonlinearity term [32] or a square-law nonlinearity term [33] in instantaneous output frequency expression, both of which contribute to lower range resolution and larger range estimation error.

The basic waveform to measure range and velocity consists of a up-ramp and a downramp, duration of each of which is larger than 1ms [34]. That makes ranging frequency  $f_r$ and Doppler frequency  $f_d$  fall in kHz range, which is flicker noise range. As a result, the ranging resolution of FMCW radar is affected by flicker noise of the circuit. To solve the issue, designers adopt fast chirp to move  $f_r$  and  $f_d$  above flicker noise corner frequency. Duration of such chirp is around 100 $\mu$ s. That leads to some requirements of the PLL bandwidth [35], which would be discussed in detail in later chapters.

Another need is wide chirp bandwidth. As known, for FMCW radar, the ranging resolution is inversely proportional to chirp bandwidth [36]. To get range resolution of 10mm, chirp bandwidth needs to be as wide as 16GHz [19]. The high-resolution measurement is needed for industry quality inspection and measurement, such as accurate positioning of machines, measuring thickness of layer coating, and separating closely adjacent targets [37]. And wide bandwidth systems also offers possibility to operate in many different frequency bands [38].

As for the architecture, generally, PLL-based chirp generators can be categorized into two types. One is one-point-modulation (OPM) architecture, and the other is two-pointmodulation (TPM) architecture [39].

For OPM architecture, the modulation signal is injected at only one point of the PLL. In [40], the modulation signal is imposed as part of VCO's control signal. Such PLL is simple and doesn't have additional noise source. Modulation can also be implemented by modulating reference frequency of a PLL. For instance, a chirp is generated with a direct digital frequency synthesizer (DDFS) and fed into the PLL as reference in [41]. DDFS can avoid the issue of limited bandwidth of LC-VCO, and a high-resolution DDFS can minimize the chirp nonlinearity, but power consumption of DDFS is high and it needs a large amount of memory for the lookup table and a high-resolution DAC. Similarly in [42], a fast and linear chirp as reference signal can facilitate the design of other components of PLL, but an external instrument is needed in the design. So such designs are only for prototyping or testing purposes, not for practical applications. Alternatively, the frequency modulation can be achieved by varying the feedback division ratio in fractional-N PLL [43], [44]. The generated chirp has good linearity if loop bandwidth is designed properly, and its power is significantly lower than DDFS architecture, but additional noise from Delta-Sigma Modulator should be

|                                  | Xidian,<br>VLSI  | ECNU,<br>TCAS     | NTU, IS-<br>CAS 2022 | ADI,<br>ISSCC | IMEC,<br>ISSCC | Toronto,<br>TMTT | IBM,<br>JSSC  | DENSO,<br>RFIC   |

|----------------------------------|------------------|-------------------|----------------------|---------------|----------------|------------------|---------------|------------------|

|                                  | 2022 [47]        | 2022 [48]         | [49]                 | 2022 [50]     | 2020 [51]      | 2021 [18]        | 2018 [52]     | 2020 [53]        |

| Technology                       | 65nm<br>CMOS     | 55nm<br>CMOS      | 40nm<br>CMOS         | 28nm<br>CMOS  | 28nm<br>CMOS   | 22nm<br>FDSOI    | 130nm<br>SiGe | 40nm<br>CMOS     |

| Architecture                     | DS-PLL           | Fractional-<br>N  | Fractional-<br>N     | ADPLL         | SSPLL          | Integer-N        | Dual-<br>loop | Fractional-<br>N |

| Reference<br>(MHz)               | 277 to<br>562.5  | 40                | 50                   | 80 to 200     | 80             | 8400 to<br>1100  | 125           | 50               |

| Center<br>frequency<br>(GHz)     | 8.55 to<br>17.11 | 21.24 to<br>24.64 | 4.8 to 5.5           | 8.8 to 12     | 8.3 to<br>11.7 | 160              | 79            | 76 to 77         |

| Chirp band-<br>width (GHz)       | 0.5              | 1.25              | 0.7                  | 0.65          | 1.21           | 8.5              | 8             | 0.3              |

| Chirp rate<br>(MHz/µs)           | 33.33            | 1.818             | 1.22                 | 65            | 94.5           | 5300             | 100           | N/A              |

| Phase noise<br>@1MHz<br>(dBc/Hz) | -120             | -98.54            | -110                 | -121          | -109.1         | -113             | -97           | -91              |

| PLL power<br>(mW)                | 22.1             | 92.1              | 3.3                  | 187           | 11.7           | 300              | 590           | N/A              |

Table 1.2: State-of-the-art PLLs for FMCW radar systems.

considered in the design. For all the OPM architectures, PLL loop bandwidth should be designed considering some trade-offs. The loop bandwidth of PLL should be much less than modulation frequency to allow VCO frequency variations and to suppress the quantization noise. However, the cut-off frequency of the PLL transfer function should be much higher than the modulation frequency to allow enough harmonics to pass for a linear chirp. This trade-off doesn't pose a problem if fast chirp generation is not required. Otherwise, it makes the design challenging.

TPM architecture can decouple modulation frequency from PLL loop bandwidth. It injects the modulation signal to both tuning port of VCO (DCO) and feedback path [45], [46]. With two-point injection, the transfer function of the PLL could be expressed as Eq. 1.22, which is a all-pass function if  $g_0$  is equal to  $f_{ref}/K_{DCO}$ . The TPM architecture allows fast chirp generation and provides more design freedom. But the circuitry is more complicated and there are more noise sources. Also, TPM is very sensitive to gain mismatch, as all-pass characterization disappears if  $g_0$  is not equal to  $f_{ref}/K_{DCO}$ . As a result, calibration circuitry is needed to eliminate gain mismatch across PVT [46]. State-of-the-art PLLs for FMCW radar system are shown in Table. 1.2.

$$H_{TPM}(s) = f_{ref} \cdot \left[ \frac{G_{loop}(s)}{1 + G_{loop}(s)} + \frac{g_0 K_{VCO} \cdot (1/f_{ref})}{1 + G_{loop}(s)} \right]$$

(1.22)

## 1.5 Conclusion

In this chapter, the background and design needs of the research are introduced. The proposed design is a PLL used as a chirp generator in FMCW radar systems.

The thesis is organized as follows: In Chapter 2, the architecture of the proposed PLL is explained and system-level modeling is presented. With the phase noise model and bandwidth model, some PLL specifications can be determined. In Chapter 3, a more accurate model for linearity and settling calculation is explored. This model provides comprehensive insight into PLL bandwidth design and the calculation provides more accurate data for dynamic phase noise calculation. Chapter 4 shows the dual-modulus divider and its controller, a Delta-Sigma Modulator. Chapter 5 illustrates an analytical modeling method for high-frequency circuit, which is used to design and optimize the prescaler and divider in the proposed PLL. In Chapter 6, a prototype CMOS design is illustrated. Chapter 7 draws the conclusion.

## Chapter 2

# PLL Architecture and System-level Modeling

## 2.1 Architecture of Proposed PLL

## Background

In recent years, mm-wave FMCW radar at 140GHz is gaining more and more attention. Sitting between microwave frequencies and visible light frequencies, mm-wave has its own advantages.

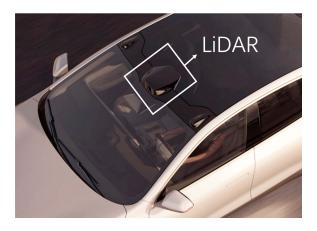

Microwave radars, of which frequency is lower than that of mm-wave radars, suffer from large physical size [54] and limited bandwidth [55]. Compared with microwave radar, mmwave radar has larger bandwidth, better angular resolution, better spacial resolution, and smaller physical size.

For visible light radars (LiDAR), such systems can be categorized into two types, namely flash type and scanning type [56]. Flash type LiDAR could achieve high resolution easily at the cost of the limited measurement distance (typically < 20m), for laser power needs to be diffused to all pixels. The scanning type could focus laser power on one column or one row and conduct horizontal or vertical scanning respectively, resulting in much larger measurement distance. However, its frame rate is lower due to its mechanical scanning mechanism. And to get good optical properties and thus good SNR, rotating mirror is commonly applied in the system, resulting in a bulky radar module, as shown in Fig. 2.1. Compared with LiDAR, mm-wave radar has lower resolution, but it's more compact and less sensitive to bad weather, strong light interference, and EM interference [57].

In summary, mm-wave radar systems have good angular resolution, good spacial resolution, and small physical size. Based on its compact size and precise motion sensing, 140GHz

Figure 2.1: LiDAR module on a car with advanced driving assistance function.

radar could be applied to many applications, such as driving assistance, driver monitoring, patient monitoring, smart building, robotics, and gesture recognition [58].

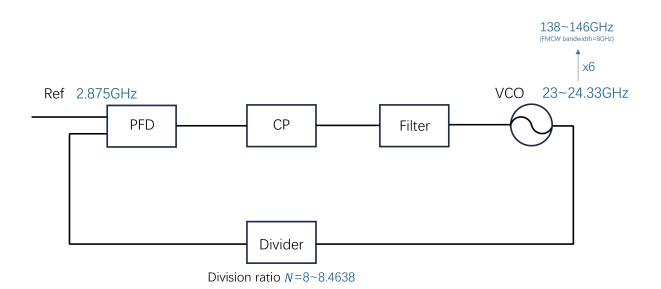

The proposed PLL is used as the chirp generator in a 140GHz FMCW radar system. And some circuit blocks of the proposed PLL are re-used from an integer-N PLL from previous research [59], which is a transceiver operating at 140GHz.

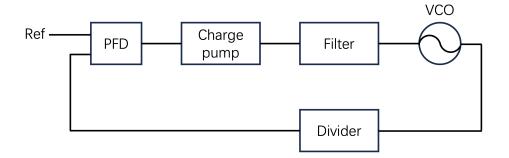

## Integer-N PLL and Fractional-N PLL

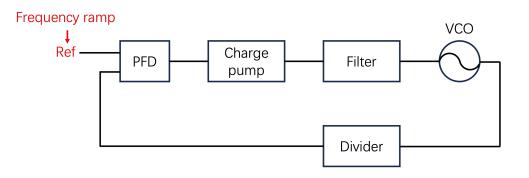

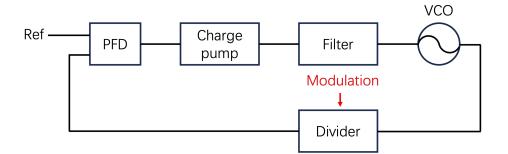

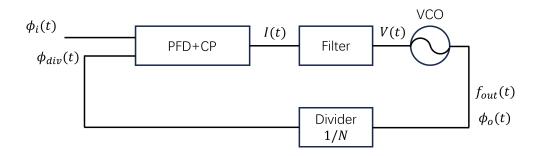

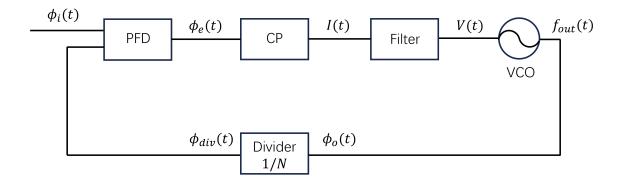

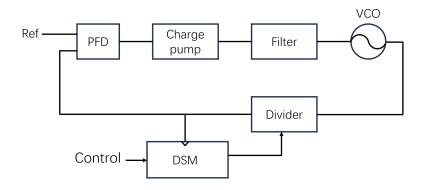

Fig. 2.2 shows the block diagram of conventional charge-pump PLL (CPPLL), consisting of phase-frequency detector (PFD), charge pump (CP), low-pass filter (LPF), voltage-controlled oscillator (VCO), and divider.

Depending on the division ratio of the divider, the PLL could be categorized into integer-N PLL and fractional-N PLL. For FMCW chirp generation, fractional-N PLL is commonly applied. Because for integer-N PLL, the bandwidth should be smaller than tenth of reference frequency, in order to avoid the stability issue due to the discrete sampling action of PFD (bandwidth should be twentieth of reference frequency considering PVT). Thus, faster settling requires higher reference frequency. However, the frequency step of the chirp is equal to the reference frequency, meaning that finer frequency step requires smaller reference frequency. As a result, there is a fundamental trade-off between fast settling and small frequency step, making it hard to generate a fast and linear chirp.

Fractional-N PLL is widely used as chirp generator because its frequency step is de-coupled from PLL bandwidth. Its frequency step could be smaller than reference frequency so in

Figure 2.2: Block diagram of charge-pump PLL.

order to generate a chirp with fine step, low frequency reference is not required and much higher reference frequency is applicable.

### Architecture

Different from conventional fractional-N PLL, the frequency of chirp generator's output ramps up with time linearly. And to generate the frequency ramp, modulation needs be injected at some point of the loop. Generally, there are two modulation schemes for onepoint modulation, namely reference modulation and division-ratio modulation, as shown in Fig. 2.3 and Fig. 2.4 respectively.

In the case of reference-modulated architecture, the reference signal, typically a chirp, is usually supplied by an external instrument. The PLL serves as a frequency multiplier in this architecture, which is usually utilized for testing and prototyping FMCW radar systems. For division-ratio-modulated architecture, the division ratio increases linearly over time. This architecture is suitable for a fully-integrated FMCW radar system. Therefore, the divisionratio-modulated architecture is applied to the proposed PLL.

## 2.2 System-level Modeling

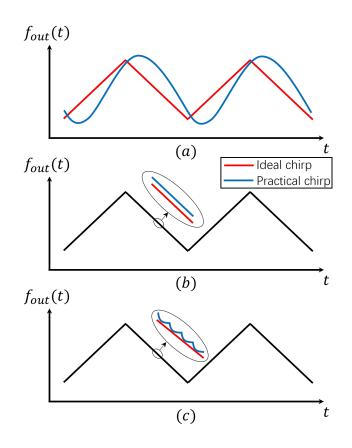

In this section, models of phase noise and PLL bandwidth are discussed. The corresponding code is in Appendix A. For phase noise, the phase noise contribution of each circuit block of the PLL will be discussed. Based on the zero-dead-zone PFD, a new model is proposed to calculate the charge pump phase noise. For PLL bandwidth, Fig. 2.5 shows the comparison of generated chirp with different PLL bandwidths. If the PLL is too slow, in other words, if the bandwidth of the PLL is too narrow, then the generated chirp cannot follow the ideal chirp. This leads to a nonlinear chirp and an unpredictable FMCW slope. On the contrary, if the PLL is too fast, or if the PLL bandwidth is very wide, every time the division ratio

Figure 2.3: Reference-modulated PLL-based chirp generator.

Figure 2.4: Division-ratio-modulated PLL-based chirp generator.

changes, the PLL would settle quickly. The resultant chirp would have a step shape, which results in poor linearity. Such bandwidth is denoted by  $BW_{settle}$  where the PLL can settle on each step. As a result, when designing a PLL, its bandwidth should fulfill the following relation:

$$\frac{1}{T_c} \ll BW_{PLL} \ll BW_{settle} \tag{2.1}$$

In this section, the method for calculating  $BW_{settle}$  will be shown. A more accurate method for designing PLL bandwidth will be discussed in the next chapter, which can not only provide a rough range of PLL bandwidth but also tune and optimize the chirp linearity without time-consuming circuit simulation.

## Phase Noise Modeling

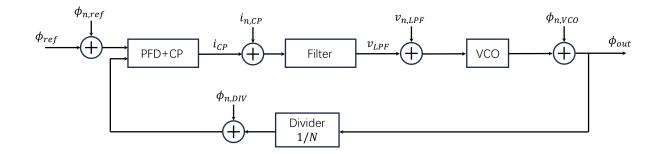

A general phase-domain model of a charge-pump PLL, which includes the main noise sources, is shown in Fig. 2.6. The corresponding forward gain, G(s), and feedback gain,

Figure 2.5: Generated chirp with different bandwidth. (a) PLL bandwidth is too narrow (b) PLL bandwidth is suitable (c) PLL bandwidth is too wide.

H(s), are given by

$$G(s) = \frac{I_{CP}K_{VCO}Z(s)}{s}$$

(2.2)

and

$$H(s) = \frac{1}{N} \tag{2.3}$$

respectively, where Z(s) is the transfer function of the low-pass filter. The loop gain is then given by

$$T(s) = G(s)H(s) = \frac{I_{CP}K_{VCO}Z(s)}{sN}$$

(2.4)

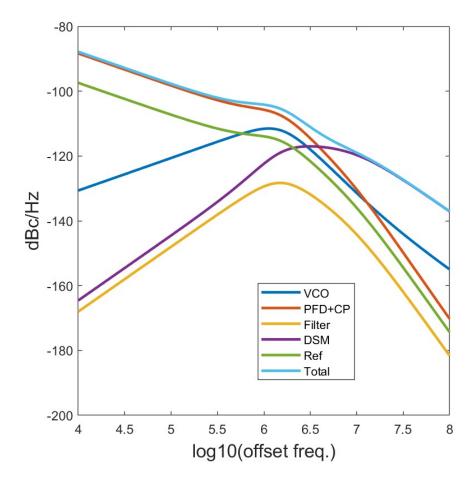

To calculate the total output noise and plot the noise contribution from each noise source, each circuit block must be simulated using a circuit simulator. The resultant phase noise spectrum can then be used to calculate the total output phase noise in MATLAB.

Figure 2.6: Phase-domain model of charge-pump PLL with main noise sources.

Table 2.1: Phase noise chart of Keysight E8267D in dBc/Hz.

|                 |     | Offset from carrier (Hz) |      |      |      |      |               |      |  |  |

|-----------------|-----|--------------------------|------|------|------|------|---------------|------|--|--|

| Frequency       | 1   | 10                       | 100  | 1k   | 10k  | 100k | $1\mathrm{M}$ | 10M  |  |  |

| >2 to $3.2$ GHz | -58 | -84                      | -102 | -117 | -134 | -134 | -150          | -150 |  |  |

#### **Reference Noise**

Generally, the reference noise spectrum is not obtained from circuit simulation because the reference signal is typically generated from a crystal or testing equipment, depending on the application scenario or testing setup. The datasheet of the crystal or testing equipment would describe the phase noise spectrum of the source signal it generates. For example, the Keysight E8267D PSG vector signal generator is used as the reference source. Its datasheet [60] provides its phase noise parameters, as shown in Table. 2.1.

Based on the phase noise data, the phase noise spectrum of the reference signal,  $S_{ref}$ , can be plotted in MATLAB with interpolation and extrapolation as shown in Fig. 2.7. The noise gain from reference signal phase to output phase is

$$G_{n,ref} = \frac{\phi_{out}}{\phi_{n,ref}} = \frac{NG(s)}{N + G(s)} \tag{2.5}$$

And the corresponding power spectral density of phase noise at the output is

$$S_{ref,out} = S_{ref} \cdot |G_{n,ref}|^2 \tag{2.6}$$

#### Filter Noise

In the proposed design, the low-pass filter is a passive network. The noise of such a network can be modeled as a voltage noise source in series with the network's impedance  $Z_{passive}(s)$ ,

Figure 2.7: Phase noise spectrum of reference signal.

or as a current noise source in parallel with the network's admittance  $Y_{passive}(s)$ . For the low-pass filter, the voltage noise power is given by

$$S_{V_{n,LPF}} = 4k_B T \mathcal{R}\{Z(s)\}$$

$$(2.7)$$

where  $k_B$  is Boltzmann's constant, T is the temperature, and Z(s) is the transfer function of the filter. The gain from the filter noise voltage to the output phase is

$$G_{n,LPF} = \frac{\phi_{out}}{v_{n,LPF}} = \frac{2\pi}{I_{CP}Z(s)} \cdot \frac{NG(s)}{N+G(s)}$$

(2.8)

where  $I_{CP}$  is the charging current of the charge pump. The filter noise spectrum at the output is then given by

$$S_{LPF,out} = S_{V_{n,LPF}} \cdot |G_{n,LPF}|^2 \tag{2.9}$$

### VCO Noise

For the phase noise of LC oscillators, Leeson's model is most commonly used [61]. This model accounts for flicker noise and thermal noise, and the phase noise power spectral density can be expressed as

$$S_{VCO}(\Delta f) = n \left( \frac{1}{\Delta f^2} + \frac{f_c}{\Delta f^3} \right)$$

(2.10)

where n is the noise parameter,  $f_c$  is the corner frequency, and  $\Delta f$  is the offset frequency from the carrier. The values of  $f_c$  and n can be extracted or calculated from the VCO phase noise simulation results. In the proposed design, the corner frequency  $f_c = 10$  MHz and  $n = 2.87 \text{ rad}^2/\text{Hz}$ . The phase noise at the output is then given by

$$S_{VCO,out} = S_{VCO} \cdot |G_{n,VCO}|^2 \tag{2.11}$$

where the gain  $G_{n,VCO}$  is given by

$$G_{n,VCO} = \frac{\phi_{out}}{\phi_{n,VCO}} = \frac{N}{N+G(s)}$$

(2.12)

#### **Divider** Noise

Divider noise in fractional-N PLL is primarily generated by the modulation signal that controls the divider. To achieve fractional division ratio, the divider must continually switch between two integer division ratios, ensuring that the average division ratio equals the desired non-integer value. In the proposed design, a Delta-Sigma Modulator is applied to control the dual-modulus divider and more details of the scheme will be covered in a later chapter. This section focuses solely on the noise contribution, which can be modeled as [62] [63]

$$S_{DSM}(\Delta f) = \frac{(2\pi)^2}{12f_{ref}} \left[ 2\sin\left(\frac{\pi\Delta f}{f_{ref}}\right) \right]^{2(m-1)}$$

(2.13)

where  $f_{ref}$  is the reference frequency and m is the order of Delta-Sigma Modulator. The gain from divider to the output is

$$G_{n,DSM} = -\frac{NG(s)}{N+G(s)} \tag{2.14}$$

And the noise contribution at the output is

$$S_{DSM,out} = S_{DSM} \cdot |G_{n,DSM}|^2 \tag{2.15}$$

#### PFD and CP Noise

The noise from the charge pump in steady-state is influenced by the conducting time of the charging and discharging currents,  $I_{up}$  and  $I_{dn}$ . A higher duty cycle increases the noise due to the injection of more noise current.

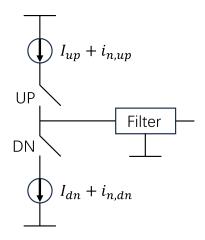

Mathematically, [64] derives the expression for the phase noise of the charge pump. Fig. 2.8 depicts a simplified charge pump, where the UP and DN signals control the charging and discharging currents, respectively, and  $I_{up} = I_{dn} = I_{CP}$ . When the charging current is active, its noise component  $i_{n,up}$  also flows into the filter, thereby increasing the output noise. The same principle applies to the discharging current and  $i_{n,dn}$ . The total output noise power is the sum of the power of the charging noise and discharging noise, as they are incoherent noise sources.

Figure 2.8: Simplified schematic of charge pump.

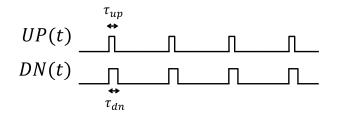

To compute the output noise, the waveform of the switched current can be represented as the product of the input noise current and the control signal (see Fig. 2.9).

$$i_{n,sw,up}(t) = i_{n,up} \cdot UP(t) \tag{2.16}$$

$$i_{n,sw,dn}(t) = i_{n,dn} \cdot DN(t) \tag{2.17}$$

As a result, the output noise spectrum is the convolution of input noise spectrum and squared magnitude of the Fourier transform of the control signal.

$$S_{sw,up} = S_{n,up} * |\mathcal{F}\{UP(t)\}|^2$$

(2.18)

$$S_{sw,dn} = S_{n,dn} * \left| \mathcal{F} \{ DN(t) \} \right|^2$$

(2.19)

where the Fourier transform of the control is

$$\left|\mathcal{F}\{DN(t)\}\right|^{2}(f) = \frac{\tau^{2}}{T_{ref}^{2}} \sum_{k=-\infty}^{\infty} \left[sinc^{2}\left(\frac{k\tau}{T_{ref}}\right) \cdot \delta\left(f - \frac{k}{T_{ref}}\right)\right]$$

(2.20)

The current noise comprises two components: white noise and flicker noise. To determine the output noise spectrum, we need to calculate the output white noise power and the flicker corner frequency. The white noise power can be computed by summing the series in Eq. 2.20.

$$S_{sw,white} = S_{n,white} \cdot \frac{\tau}{T_{ref}}$$

(2.21)

where  $\tau$  is the pulse width of UP(t) or DN(t) as shown in Fig. 2.9. The switched-noise power is the continuous-time noise scaled by duty cycle  $\alpha_{CP} = \frac{\tau}{T_{ref}}$ .

Figure 2.9: Waveform of control signals, UP and DN.

For flicker corner frequency, it's usually lower than  $\frac{f_{ref}}{2}$  in fractional-N PLL, so it's not affected by noise folding due to Eq. 2.20. And the output flicker noise spectrum is

$$S_{sw,flicker} = S_{n,flicker} \cdot \left(\frac{\tau}{T_{ref}}\right)^2 \tag{2.22}$$

The switched flicker noise power is the continuous-time noise scaled by square of duty cycle. Due to different scaling factors of the white noise and the flicker noise, the corner frequency of output noise spectrum is scaled by  $\alpha_{CP}$ .

$$f_{c,out} = f_{c,CP} \cdot \frac{\tau}{T_{ref}} \tag{2.23}$$

where  $f_{c,CP}$  is the noise corner frequency of the charge pump, and  $f_{c,out}$  is the corner frequency of switched noise. Thus, the output noise spectrum of charge pump is [65][66]

$$S_{i_n,CP}(f) = S_n^{white} \cdot \alpha_{CP} \left( 1 + \frac{\alpha_{CP} \cdot f_{c,CP}}{f} \right)$$

(2.24)

The noise gain from charge pump output current to output phase is

$$G_{n,CP} = \frac{\phi_{out}}{i_{n,CP}} = \frac{2\pi}{I_{CP}} \cdot \frac{N \cdot G(s)}{N + G(s)}$$

(2.25)

and the noise spectrum at the output is

$$S_{CP,out} = S_{i_n,CP} \cdot |G_{n,CP}|^2 \tag{2.26}$$

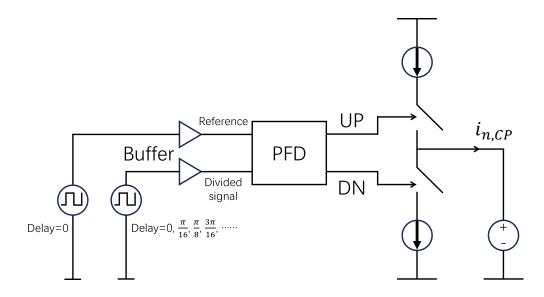

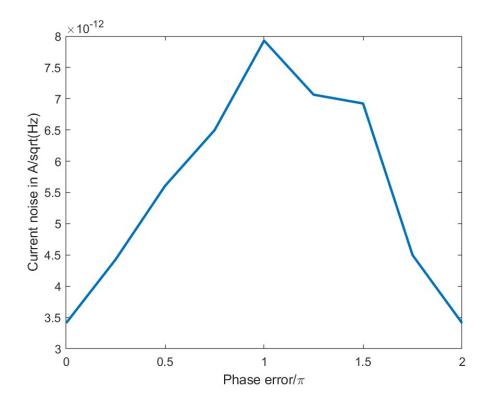

In this model, the white noise  $S_n^{white}$  and corner frequency  $f_{c,CP}$  are obtained from simulation of PFD and CP, the setup of which is shown in Fig. 2.10. The reference signal and divided signal are generated by two signal sources, between which a delay is applied to simulate phase noise under different steady-state phase error values. For each phase error value, the noise spectrum can be obtained from PSS simulation, from which  $S_n^{white}$  and  $f_{c,CP}$  can be extracted from this spectrum.

Figure 2.10: Noise simulation setup for PFD and charge pump.

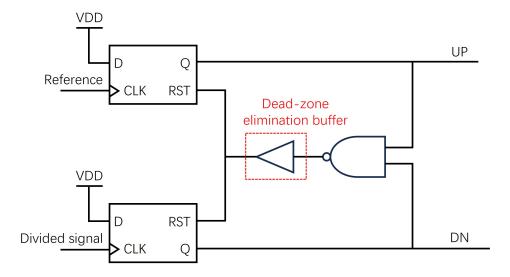

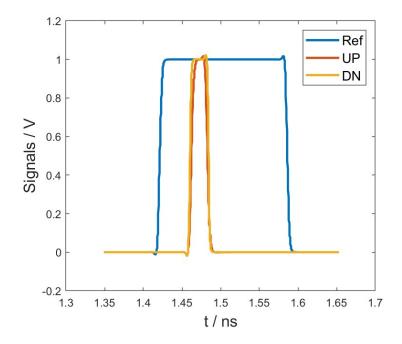

However, in many PLL designs, the phase frequency detector (PFD) is implemented with dead-zone elimination structure for better linearity. For instance, in the proposed design, a conventional NAND-gate-based PFD is used as shown in Fig. 2.11 and a dead-zone elimination buffer is inserted between the NAND gate output and the reset terminal. This converts a very small phase error from a very narrow pulse into two wider pulses with a difference in width. In such architecture, the duty cycle of charging current and discharging current cannot be zero, even if the phase error is 0, which contradicts the previous model Eq. 2.24. Simulation results (Fig. 2.12) shows that after the reference signal and divided signal (overlapped with reference and not shown) rise from 0 to 1V, both UP and DN signals go high after a certain delay and then fall down to 0 together. In this simulation, reference frequency is 2.875GHz, and pulse width of UP and DN are 0.021ns and 0.025ns respectively. Thus, the average duty cycle of the charge pump is  $\alpha_0 = 6.6125\%$ . The overlapping behavior of UP and DN comes from the delay of the dead-zone elimination buffer, and it persists when phase error is nonzero as shown in Fig. 2.13.

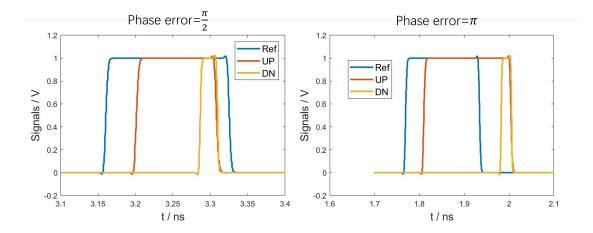

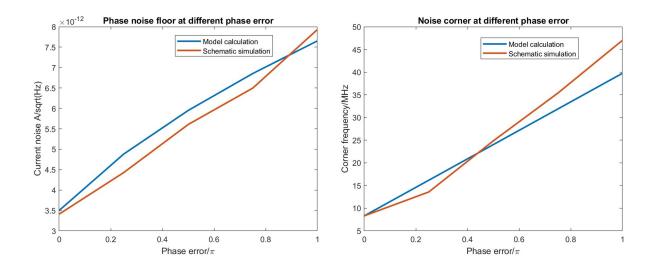

As a result, Eq. 2.24 needs modification. Fig. 2.14 illustrates the phase noise of the PFD and charge pump at various phase error values. The new model incorporates two factors: the new noise floor and the new noise corner. Specifically, the previous noise floor is  $S_n^{white} \cdot \alpha_{CP}$ , while the new noise floor results from the power addition of incoherent noise, given by  $S_n^{white} \cdot (2\alpha_0 + \alpha_{CP})$ . In this case,  $\alpha_0 = 6.6125\%$  as mentioned. And  $S_n^{white}$  can be determined from the data presented in Fig. 2.14 using the expression

$$S_n^{white} = \left(\frac{3.5 \times 10^{-12} A / \sqrt{Hz}}{2\alpha_0}\right)^2$$

(2.27)

Figure 2.11: Schematic of NAND-gate PFD with dead-zone elimination buffer.

Figure 2.12: Waveform of UP and DN signals when phase error (between reference and divided signal) is 0.

Figure 2.13: Waveform of UP and DN signals when phase error (between reference and divided signal) is  $\frac{\pi}{2}$  or  $\pi$ .

Figure 2.14: Phase noise of PFD and charge pump at different phase error values.

Figure 2.15: Comparison between proposed model and simulation results.

The same principle applies to the new corner frequency. The previous corner frequency,  $\alpha_{CP} \cdot f_{c,CP}$ , is replaced with  $(2\alpha_0 + \alpha_{CP}) \cdot f_{c,CP}$ . The new noise floor and new corner frequency match the simulation well as depicted in Fig. 2.15. Consequently, the proposed new phase noise model is

$$S_{i_n,CP}(f) = S_n^{white} \cdot \left(2\alpha_0 + \alpha_{CP}\right) \left(1 + \frac{\left(2\alpha_0 + \alpha_{CP}\right) \cdot f_{c,CP}}{f}\right)$$

(2.28)

#### **Total Noise**

By adding up the noise from all noise sources, the total phase noise at the output can be calculated as

$$S_{out,total} = S_{ref,out} + S_{LPF,out} + S_{VCO,out} + S_{DSM,out} + S_{CP,out}$$

(2.29)

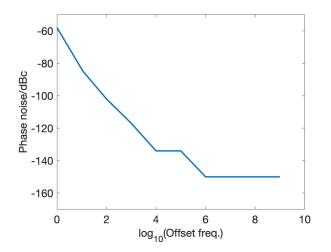

And noise contribution can be illustrated as shown in Fig. 2.16.

## PLL Bandwidth Modeling

As previously mentioned, this section encompasses the modeling and calculation of the bandwidth where PLL can settle on such frequency step, specifically  $BW_{settle}$ .

The time-domain model of CPPLL is shown as Fig. 2.17. The phase error  $\phi_e$  is

$$\phi_e(t) = \phi_i(t) - \phi_{div}(t) \tag{2.30}$$

Figure 2.16: Comparison between proposed model and simulation results.

Figure 2.17: Time-domain model of charge-pump PLL.

The output current of charge pump is

$$I(t) = \phi_e(t) \cdot K_{PD} \tag{2.31}$$

where  $K_{PD} = \frac{I_{CP}}{2\pi}$  is the gain of charge pump. For VCO, the frequency of its output is

$$\omega_{out}(t) = 2\pi f_{out}(t) = 2\pi \cdot K_{VCO} \cdot V(t) = \frac{d \left[ N \cdot \phi_{div}(t) \right]}{dt}$$

(2.32)

where  $K_{VCO}$  is the VCO gain. Based on division ratio modulation for chirp generation, the output frequency

$$\omega_{out}(t) = \omega_{ref} \cdot (N_0 + \alpha \cdot t) \tag{2.33}$$

where  $\omega_{ref}$  is the reference frequency,  $N_0$  the division ratio at the beginning of the chirp,  $\alpha$  the slope of division ratio. And the  $N(t) = N_0 + \alpha t$ . It's important to note that the expression for N(t) assumes the division ratio of the divider changes continuously and linearly over time, which is a simplification and approximation. More accurate modeling will be discussed in Chapter 3. From Eq. 2.32 and Eq. 2.33, the output voltage of the filter can be expressed as

$$V(t) = \frac{1}{2\pi K_{VCO}} \cdot \left[ \alpha \phi_{div}(t) + (N_0 + \alpha t) \frac{d\phi_{div}(t)}{dt} \right]$$

(2.34)

For the filter, in S-domain, its transfer function is

$$\frac{V}{I} = \frac{b_n s^n + b_{n-1} s^{n-1} + \dots + b_1 s + b_0}{a_n s^n + a_{n-1} s^{n-1} + \dots + a_1 s}$$

(2.35)

which can be written in time-domain as

$$a_n \cdot \frac{d^n V(t)}{dt^n} + \dots + a_1 \cdot \frac{dV(t)}{dt} = b_n \cdot \frac{d^n I(t)}{dt^n} + \dots + b_1 \cdot \frac{dI(t)}{dt} + b_0 \cdot I(t)$$

(2.36)

Here V(t) can be substituted with  $\phi_{div}(t)$  (Eq. 2.34), which is equal to  $\phi_i(t) - \phi_e(t)$ , and I(t) can be substituted with  $\phi_e(t)$  (Eq. 2.31). As a result, Eq. 2.36 can be written as a derivative equation of  $\phi_e(t)$ . By solving this equation, the settling process can be plotted and settling time can be calculated.

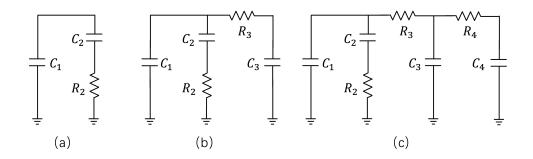

For low-pass filter, traditional topologies for 2nd-, 3rd-, and 4th-order filter is shown in Fig. 2.18 and their transfer function can be written as the general form

$$Z(s) = \frac{R_2 C_2 \cdot s + 1}{a_4 s^4 + a_3 s^3 + a_2 s^2 + a_1 s}$$

(2.37)

where the coefficients  $a_1$ ,  $a_2$ ,  $a_3$ , and  $a_4$  are summarized in Table. 2.2.

Figure 2.18: Topology for (a) 2nd-order filter (b) 3rd-order filter (c) 4th-order filter

| 2nd-order | $a_1$ | $C_1 + C_2$                                                                                           |

|-----------|-------|-------------------------------------------------------------------------------------------------------|

|           | $a_2$ | $C_1 \cdot C_2 \cdot R_2$                                                                             |

|           | $a_3$ | 0                                                                                                     |

|           | $a_4$ | 0                                                                                                     |

| 3rd-order | $a_1$ | $C_1 + C_2 + C_3$                                                                                     |

|           | $a_2$ | $C_2 \cdot R_2 \cdot (C_1 + C_3) + C_3 \cdot R_3 \cdot (C_1 + C_2)$                                   |

|           | $a_3$ | $C_1 \cdot C_2 \cdot C_3 \cdot R_2 \cdot R_3$                                                         |

|           | $a_4$ | 0                                                                                                     |

| 4th-order | $a_1$ | $C_1 + C_2 + C_3 + C_4$                                                                               |

|           | $a_2$ | $C_2 \cdot R_2 \cdot (C_1 + C_3 + C_4) + C_4 \cdot R_4 \cdot (C_1 + C_2 + C_3)$                       |

|           |       | $+R_3 \cdot (C_1 + C_2) \cdot (C_3 + C_4)$                                                            |

|           | $a_3$ | $C_1 \cdot C_2 \cdot R_2 \cdot R_3 \cdot (C_3 + C_4) + C_4 \cdot R_4 \cdot (C_2 \cdot C_3 \cdot R_3)$ |

|           |       | $+ C_1 \cdot C_3 \cdot R_3 + C_1 \cdot C_2 \cdot R_2 + C_2 \cdot C_3 \cdot R_2)$                      |

|           | $a_4$ | $C_1 \cdot C_2 \cdot C_3 \cdot C_4 \cdot R_2 \cdot R_3 \cdot R_4$                                     |

Table 2.2: Coefficients for 2nd-, 3rd, and 4th-order low-pass filter transfer function.

2nd-order filter is taken as an example. When n = 2, Eq. 2.36 becomes

$$a_2 \cdot \frac{d^2 V(t)}{dt^2} + a_1 \cdot \frac{dV(t)}{dt} = b_2 \cdot \frac{d^2 I(t)}{dt^2} + b_1 \cdot \frac{dI(t)}{dt} + b_0 \cdot I(t)$$

(2.38)

From Eq. 2.34,  $\frac{dV(t)}{dt}$  and  $\frac{d^2V(t)}{dt^2}$  can be derived as

$$\frac{dV(t)}{dt} = \frac{1}{2\pi K_{VCO}} \left[ 2\alpha \frac{d\phi_{div}(t)}{dt} + (N_0 + \alpha t) \frac{d^2 \phi_{div}(t)}{dt^2} \right]$$

(2.39)

$$\frac{d^2 V(t)}{dt^2} = \frac{1}{2\pi K_{VCO}} \left[ 3\alpha \frac{d^2 \phi(t)}{dt^2} + (N_0 + \alpha t) \frac{d^3 \phi(t)}{dt^3} \right]$$

(2.40)

And based on Eq. 2.30, following relationships can be derived

$$\frac{d\phi_e(t)}{dt} = \omega_{ref} - \frac{d\phi_{div}(t)}{dt}$$

(2.41)

$$\frac{d^2\phi_e(t)}{dt^2} = -\frac{d^2\phi_{div}(t)}{dt^2}$$

(2.42)

$$\frac{d^3\phi_e(t)}{dt^3} = -\frac{d^3\phi_{div}(t)}{dt^3}$$

(2.43)

Substituting I(t) with  $\phi_e(t)$  (Eq. 2.31) in Eq. 2.38, an ordinary differential equation of  $\phi_e(t)$  can be derived

$$a_{2} \cdot \frac{-1}{2\pi K_{VCO}} \left[ 3\alpha \frac{d^{2}\phi_{e}(t)}{dt^{2}} + (N_{0} + \alpha t) \frac{d^{3}\phi_{e}(t)}{dt^{3}} \right] + a_{1} \cdot \frac{1}{2\pi K_{VCO}} \left[ 2\alpha \omega_{ref} - 2\alpha \frac{d\phi_{e}(t)}{dt} - (N_{0} + \alpha t) \frac{d^{2}\phi_{e}(t)}{dt^{2}} \right] \\ = b_{2} \cdot K_{PD} \frac{d^{2}\phi_{e}(t)}{dt^{2}} + b_{1} \cdot K_{PD} \frac{d\phi_{e}(t)}{dt} + b_{0} \cdot K_{PD} \cdot \phi_{e}(t)$$

(2.44)

The settling time can be calculated by solving Eq. 2.44 with initial conditions. For ease of solving it in tools like MATLAB, Eq. 2.44 can be re-written as following first-order system

$$y_1' = y_2$$

(2.45)

$$y'_2 = y_3$$

(2.46)

$$y_{3}^{\prime} = \frac{-\frac{2\pi K_{VCO}}{a_{2}}(b_{2}K_{PD}\cdot y_{3} + b_{1}K_{PD}\cdot y_{2} + b_{0}K_{PD}\cdot y_{1}) + \frac{a_{1}}{a_{2}}\left[2\alpha\omega_{ref} - 2\alpha\cdot y_{2} - (N_{0} + \alpha t)\cdot y_{3}\right] - 3\alpha\cdot y_{3}}{N_{0} + \alpha t} \quad (2.47)$$

Based on this model, a PLL with a bandwidth  $BW_{settle}$  can be designed if settling time is much smaller than step time (less than tenth or twentieth of step time). Furthermore, the bandwidth of the practical design should be much smaller than  $BW_{settle}$ , as indicated by Eq. 2.1. Regarding the initial conditions, the initial value of  $\phi_e(t)$  is set as  $\pi$  to calculate the worst-case settling time. And the settling threshold is within  $\pm 0.01$  degree of the steady-state value.