# Towards Scalable Sub-THz Massive MIMO: Beamforming ASICs and 3D Die-to-Die Interconnects

Harrison Liew

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2024-178 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2024/EECS-2024-178.html

August 10, 2024

Copyright © 2024, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Towards Scalable Sub-THz Massive MIMO: Beamforming ASICs and 3D Die-to-Die Interconnects

by

#### Harrison Liew

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Ali Niknejad Assistant Professor Jessica Boles External Member Farhana Sheikh

Summer 2024

## Towards Scalable Sub-THz Massive MIMO: Beamforming ASICs and 3D Die-to-Die Interconnects

Copyright 2024 by Harrison Liew

#### Abstract

Towards Scalable Sub-THz Massive MIMO: Beamforming ASICs and 3D Die-to-Die Interconnects

by

#### Harrison Liew

Doctor of Philosophy in Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

The incessant growth of wireless communication demand is driving the desire for massive antenna arrays operating at mm-Wave to sub-THz carrier frequencies, where many GHz of bandwidth are readily available. However, this opportunity comes with an integration dilemma as antenna pitch falls below 1mm and digitized baseband data rates surpass a terabit per second. To address these and other design challenges, heterogeneous integration (HI) of radio, mixed-signal, baseband, and power delivery chiplets is a solution. Towards this goal, this dissertation presents a multi-part exploration into the technologies and design methodologies required for future sub-THz massive MIMO systems.

First, a pair of baseband ASICs for scalable linear massive MIMO arrays with digital beamforming is presented. The learnings from the design process of these chips is directly applied to the improvement of Hammer, a physical design flow generator, that has since accelerated the implementation of over ten research chips and is now used in multiple courses. Extrapolating from the integration limitations of the presented and other state-of-the-art chips, the scaling challenges and HI opportunities of sub-THz two-dimensional massive MIMO arrays is subsequently reviewed. The findings culminate in a case for 3D chiplet integration into "radio cubes", which are consequently tiled horizontally into a scalable array. To enable 3D integration, a comprehensive study of technology constraints for standardizing 3D die-to-die interconnects is performed, demonstrating how scaling roadmaps for process and packaging technologies converge towards a very different circuit architecture compared to existing die-to-die interconnects. Given the opportunities afforded by this architecture, a Chisel generator framework is presented that performs rapid design space exploration for a novel defect repair mechanism and validates a new standard (UCIe- $3D^{TM}$ ) in the Intel 16 process technology. Most importantly, this generator demonstrates a significant design effort reduction for exploring and implementing die-to-die interconnects-a key enabler for a future chiplet ecosystem. Finally, with solutions proposed for key technologies needed for the envisioned heterogeneously-integrated system, a set of integration concepts is presented, detailing remaining technological feasibility tradeoffs.

To my partner, Helen Zhou; my parents, Shelley Mau and Seng Liew; and all my friends, family, and mentors who have supported me in my career.

## Contents

| C        | onter            | nts                                                         | ii           |

|----------|------------------|-------------------------------------------------------------|--------------|

| Li       | st of            | Figures                                                     | $\mathbf{v}$ |

| Li       | st of            | Tables                                                      | vii          |

| Li       | $\mathbf{st}$ of | Listings                                                    | viii         |

| 1        | Intr             | roduction                                                   | 1            |

|          | 1.1              | Motivation                                                  | 1            |

|          | 1.2              | Background                                                  | 2            |

|          |                  | 1.2.1 Massive MIMO, in Hardware                             | 2            |

|          |                  | 1.2.2 Generator-based and Agile Design                      | 4            |

|          |                  | 1.2.3 Heterogeneous Integration                             | 5            |

|          | 1.3              | Dissertation Scope and Outline                              | 5            |

| <b>2</b> | ΑТ               | Cale of Two Chips                                           | 7            |

| _        | 2.1              | Introduction                                                | 7            |

|          | 2.2              | Hydra Spine I                                               | 8            |

|          | 2.2              | 2.2.1 Design of DSP Blocks in Chisel                        | 9            |

|          |                  | 2.2.2 Agile Physical Design                                 | 11           |

|          |                  | 2.2.2 Agne Thysical Design Challenges                       | 12           |

|          | 2.3              | Hydra Spine II                                              | 13           |

|          | 2.3              |                                                             | 16           |

|          | 0.4              |                                                             |              |

|          | 2.4              | Discussion: Reformulating the Integration Problem           | 17           |

|          |                  | 2.4.1 The $\lambda/2$ Dilemma                               | 18           |

|          |                  | 2.4.2 A Solution: Tiled Radio Cubes                         | 19           |

| 3        | Har              | nmer: Enhancements to a Modular and Reusable VLSI Flow Tool | 22           |

|          | 3.1              | Introduction                                                | 22           |

|          | 3.2              | Overview                                                    | 23           |

|          | 3.3              | Architectural Improvements                                  | 25           |

|          |                  | 3.3.1 Flow Construction and Control                         | 25           |

|   |              | 3.3.2 Multi-Library Support                                                   |

|---|--------------|-------------------------------------------------------------------------------|

|   | 3.4          | Community Contributions                                                       |

|   |              | 3.4.1 Floorplan Visualization                                                 |

|   |              | 3.4.2 Technology Plugins                                                      |

|   |              | 3.4.3 Tool Plugins                                                            |

|   | 3.5          | Evaluation: Flow Reuse Across Diverse Chips                                   |

|   | 3.6          | Related Work                                                                  |

|   | 5.0          | 3.6.1 Vendor/Foundry Reference Flows                                          |

|   |              | 3.6.2 SiliconCompiler and mflowgen                                            |

|   | 3.7          | 1 0                                                                           |

|   |              |                                                                               |

|   | 3.8          | Conclusion                                                                    |

| 4 | Silio        | con Process Technology Constraints for 3D Die-to-Die Interconnects 38         |

|   | 4.1          | Introduction                                                                  |

|   |              | 4.1.1 3D-IC Scaling Trends                                                    |

|   |              | 4.1.2 Foundations of Vertical D2D Interconnect                                |

|   | 4.2          | Scaling Constraint Analysis                                                   |

|   | 1.2          | 4.2.1 On-Die Interconnect: Routing Resources                                  |

|   |              | 4.2.2 I/O Circuit Architecture                                                |

|   |              | 4.2.3 Clocking and De-skew                                                    |

|   | 4.3          | Discussion                                                                    |

|   | 4.4          | Conclusion                                                                    |

|   | 4.4          | Conclusion                                                                    |

| 5 | $\mathbf{A}$ | Chisel Generator for Standardized 3D Die-to-Die Interconnects 60              |

|   | 5.1          | Introduction                                                                  |

|   | 5.2          | Background                                                                    |

|   |              | 5.2.1 Methodology                                                             |

|   |              | 5.2.2 Circuit Architecture                                                    |

|   |              | 5.2.3 Choosing Chisel                                                         |

|   | 5.3          | Defect Repair and Redundancy                                                  |

|   |              | 5.3.1 Previously Proposed Redundancy Schemes                                  |

|   |              | 5.3.2 Spatial Coding Redundancy                                               |

|   | 5.4          | Implementation                                                                |

|   | 0.1          | 5.4.1 Parameters                                                              |

|   |              | 5.4.2 Bump Mapping                                                            |

|   |              | 5.4.3 Logic Generation                                                        |

|   |              | 5.4.4 Collateral Generation                                                   |

|   | 5.5          | Evaluation                                                                    |

|   | 5.5          |                                                                               |

|   |              | 5.5.1 Physical Design                                                         |

|   |              | 5.5.9. Analysis                                                               |

|   | r c          | 5.5.2 Analysis                                                                |

|   | 5.6<br>5.7   | 5.5.2 Analysis       86         Results       86         Future Work       88 |

| • |   |

|---|---|

| 1 | V |

|              | 5.8               | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 91                          |

|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 6            | Disc              | cussion and Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 92                          |

|              | 6.1               | System Integration Concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 92                          |

|              | 6.2               | Summary of Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93                          |

|              | 6.3               | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 95                          |

|              |                   | 6.3.1 System Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95                          |

|              |                   | 6.3.2 Design Methodologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 96                          |

| Bi           | bliog             | graphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 98                          |

| Aı           | ppen              | dices 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 09                          |

| $\mathbf{A}$ | Har               | 7. Table 1. |                             |

|              |                   | nmer 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                          |

|              | A.1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>10</b><br>10             |

|              |                   | Path Resolution in TechJSON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |

|              | A.1<br>A.2        | Path Resolution in TechJSON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10                          |

| В            | A.1<br>A.2<br>A.3 | Path Resolution in TechJSON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10<br>11                    |

|              | A.1<br>A.2<br>A.3 | Path Resolution in TechJSON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10<br>11<br>12              |

|              | A.1<br>A.2<br>A.3 | Path Resolution in TechJSON 17 Sky130 Multi-Library Conversion 17 Tutorials and Labs 17 sel Generator 17 Parameter Tables 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10<br>11<br>12<br><b>14</b> |

## List of Figures

| 1.1  | Hydra module architecture, reproduced from [13]                                       | 4  |

|------|---------------------------------------------------------------------------------------|----|

| 2.1  | Head/Spine integration concept                                                        | 7  |

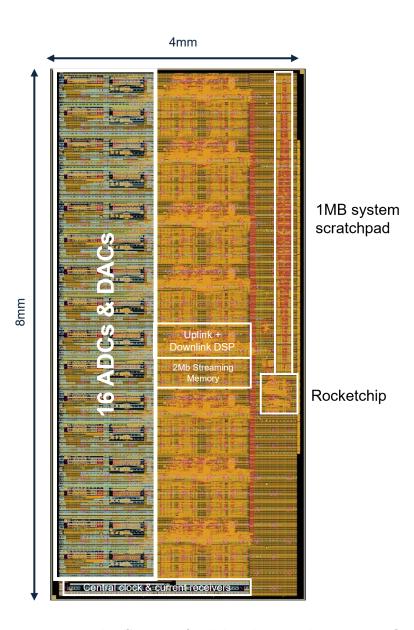

| 2.2  | Hydra Spine I final annotated floorplan                                               | 8  |

| 2.3  | Hydra Spine I DSP architectural block diagram                                         | 10 |

| 2.4  |                                                                                       | 10 |

| 2.5  | Visualized floorplan generator, scaling from $2\times2$ to $16\times16$ configuration | 11 |

| 2.6  | Congestion (red) and uplink dataflow (yellow)                                         | 13 |

| 2.7  | Hydra Spine II DSP architectural block diagram                                        | 14 |

| 2.8  | Hydra Spine II final die photo and annotated floorplan                                | 15 |

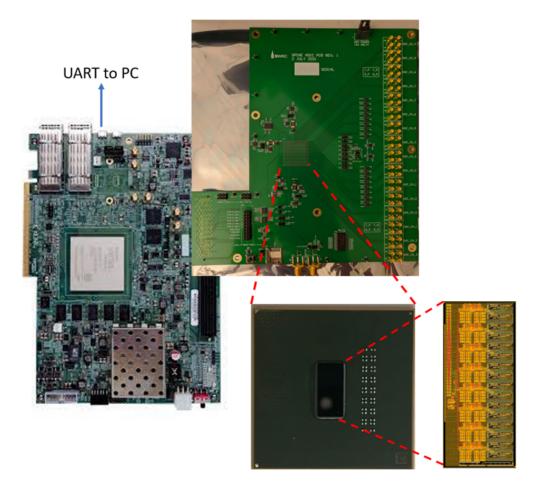

| 2.9  | Hydra Spine II board-level test setup                                                 | 16 |

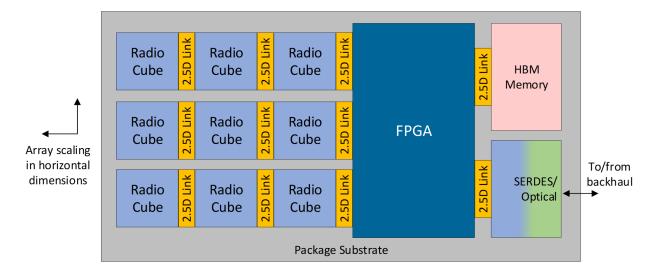

| 2.10 | Concept of tiling the radio cubes from [36] into a scalable 2D array                  | 21 |

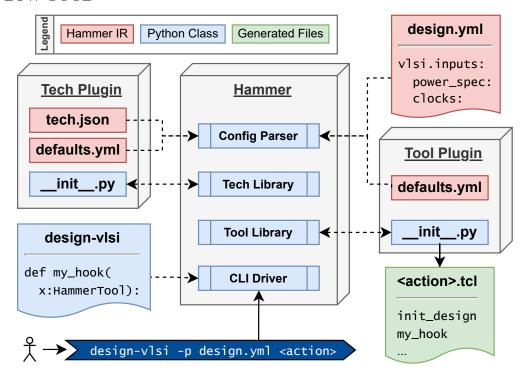

| 3.1  | Hammer software architecture.                                                         | 24 |

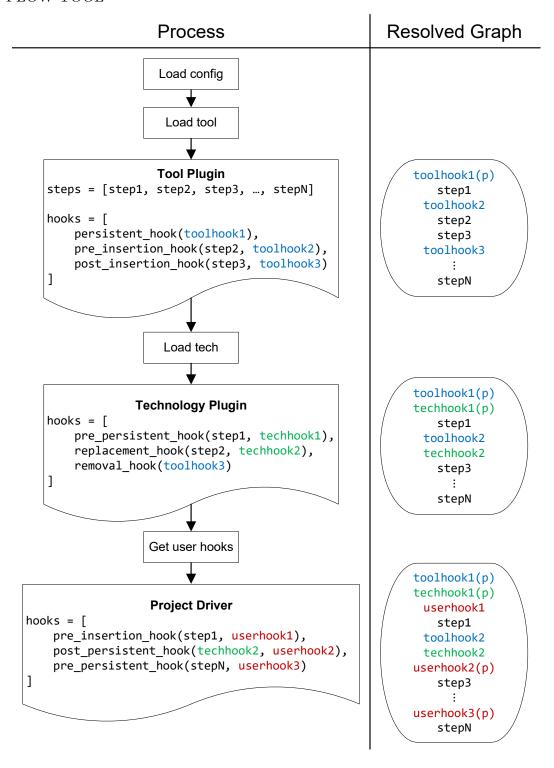

| 3.2  | Resolution of tool, tech, and user hooks                                              | 27 |

| 3.3  | Graph execution with flow control                                                     | 28 |

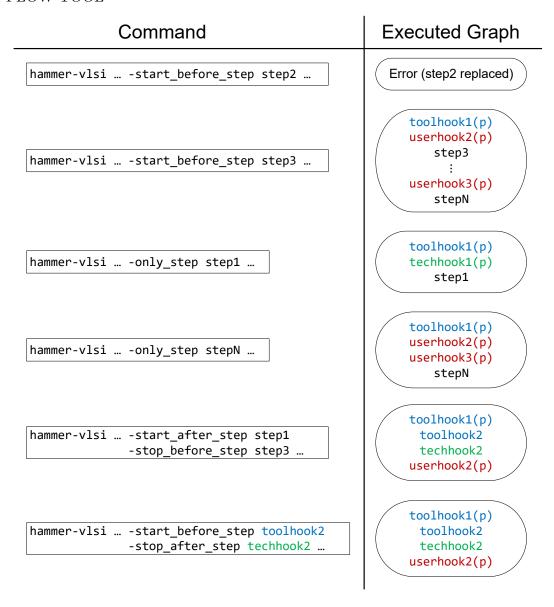

| 3.4  |                                                                                       | 31 |

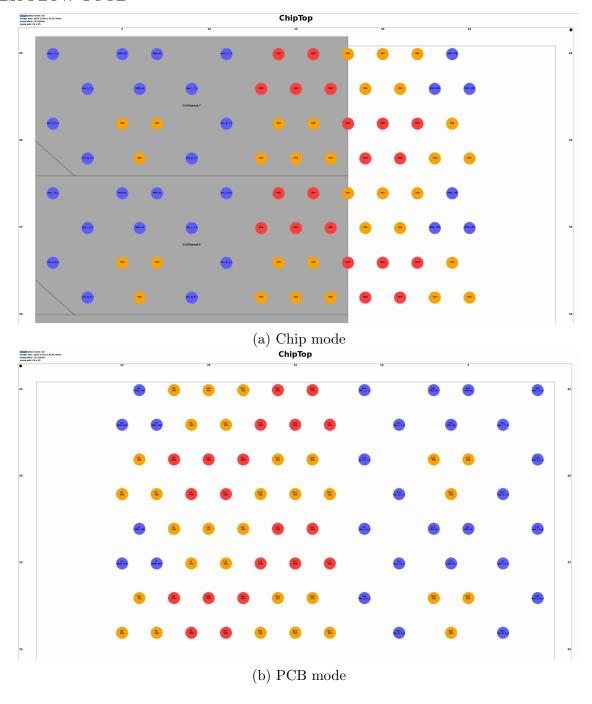

| 3.5  | LoC and PD effort trends                                                              | 34 |

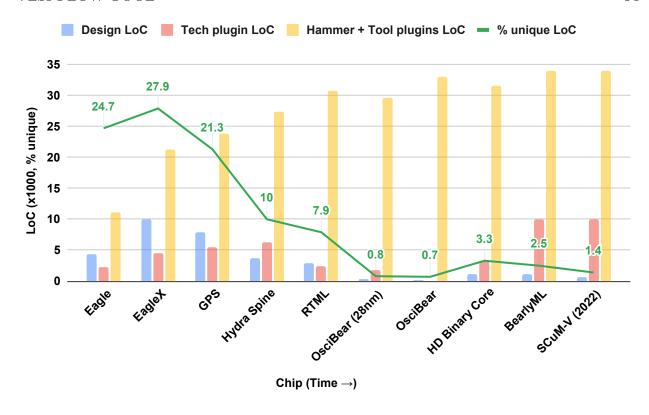

| 3.6  | Diversity of Hammer-generated chips                                                   | 36 |

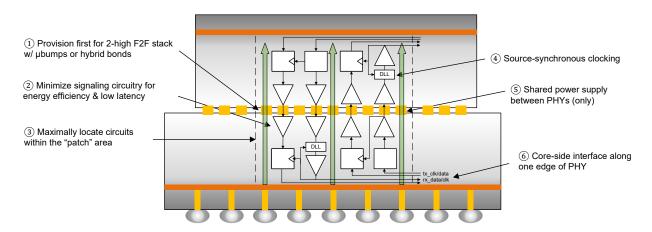

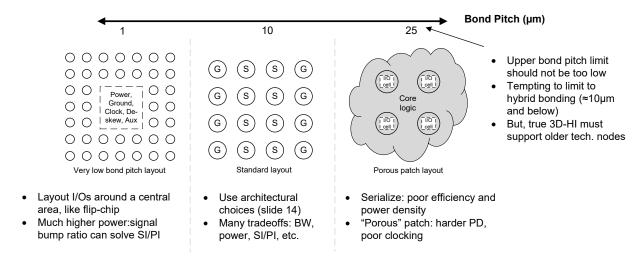

| 4.1  | Architectural concerns in 3D-IC design                                                | 39 |

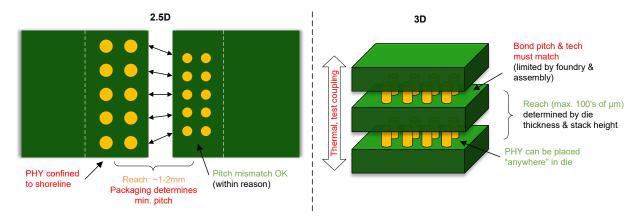

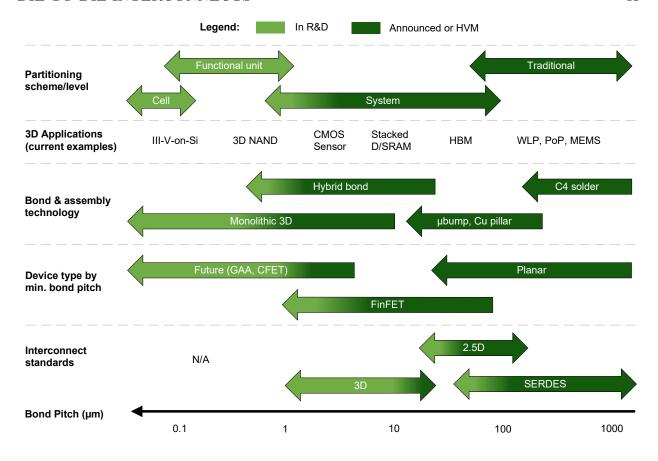

| 4.2  | $2.5D \neq 3D$ interconnect: different limiting factors                               | 42 |

| 4.3  | $2.5D \neq 3D$ interconnect: scaling and applications. Adapted from [84]              | 43 |

| 4.4  | High-level architectural choices for standardized vertical D2D interconnect           | 44 |

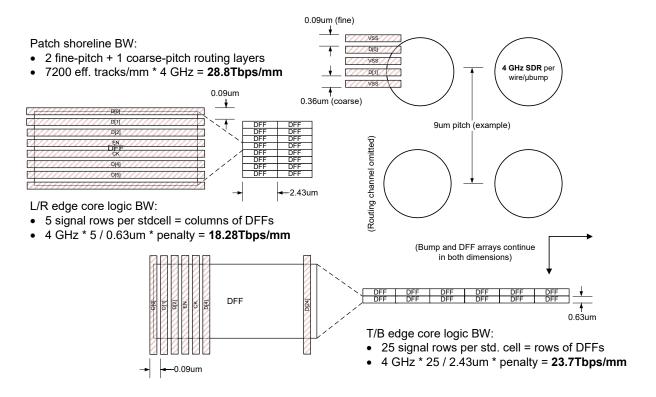

| 4.5  | Shoreline bandwidth, visualized                                                       | 46 |

| 4.6  | 00                                                                                    | 47 |

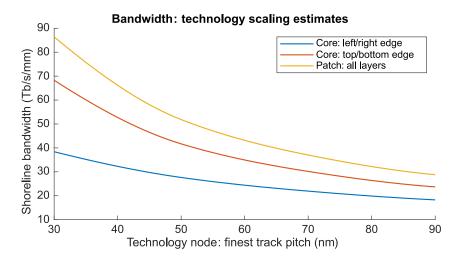

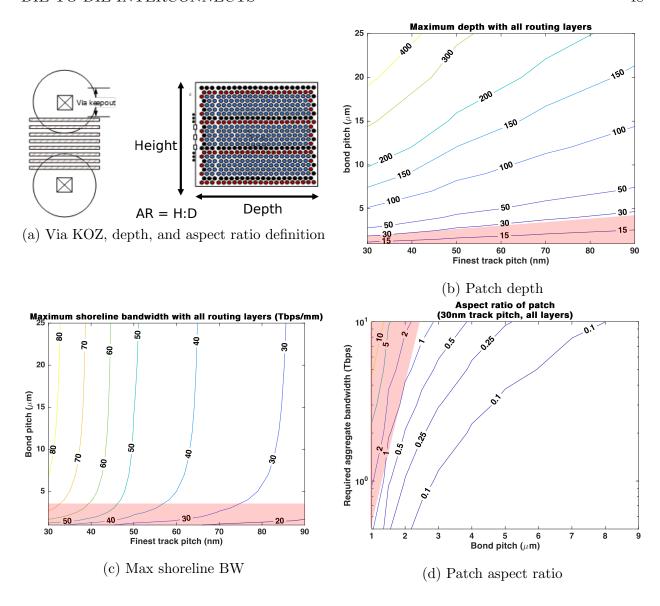

| 4.7  | Via keep-out zone and its effect on patch depth and shoreline bandwidth vs. bond      |    |

|      | pitch and technology node                                                             | 48 |

| 4.8  | V                                                                                     | 49 |

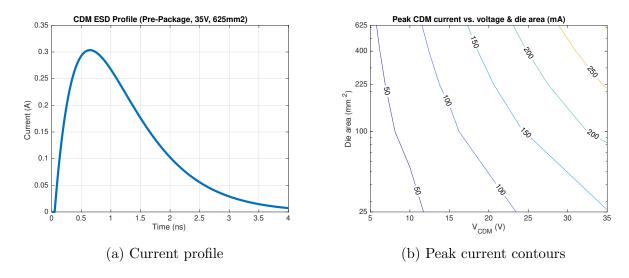

| 4.9  |                                                                                       | 50 |

| 4.10 |                                                                                       | 51 |

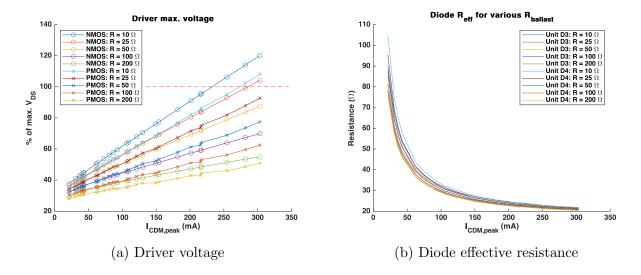

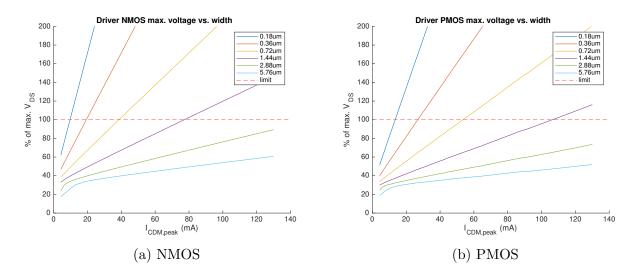

| 4.11 | Driver voltage and diode effective resistance as a function of the peak CDM ESD       |    |

|      | current.                                                                              | 51 |

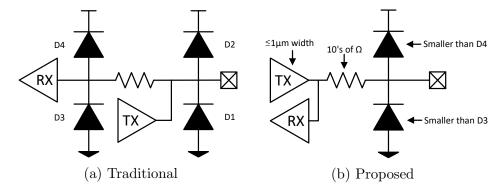

| 4.12         | Minimum NMOS and PMOS transistor widths for self-protection                                                                                                      | 52  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

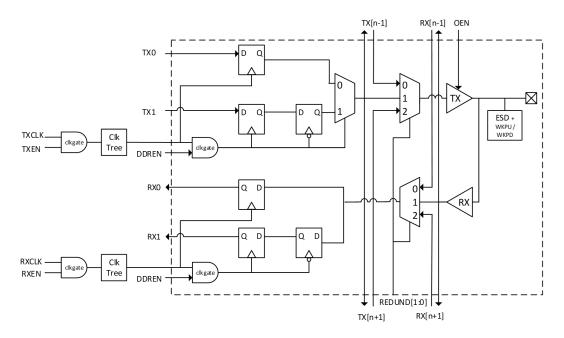

|              | Basic DDR I/O cell                                                                                                                                               | 53  |

|              | Reduced area DDR I/O cell                                                                                                                                        | 54  |

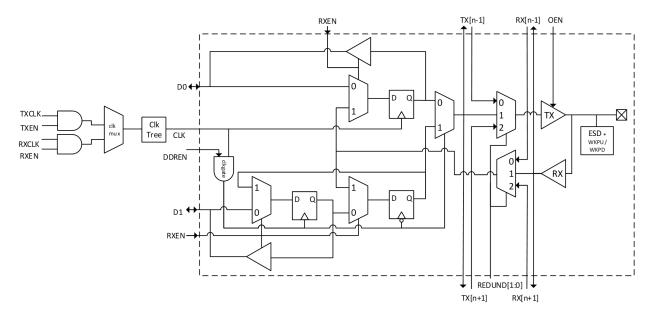

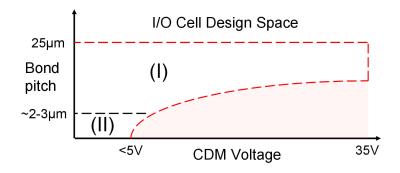

|              | Proposed I/O cell specification vs. ESD & pitch                                                                                                                  | 54  |

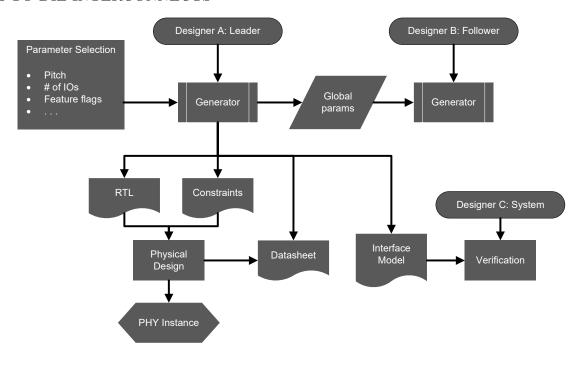

|              | Generator-based soft macro methodology                                                                                                                           | 58  |

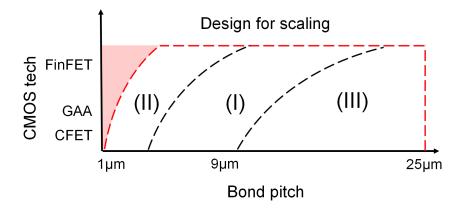

| 4.17         | Vertical interconnect specification vs. scaling                                                                                                                  | 59  |

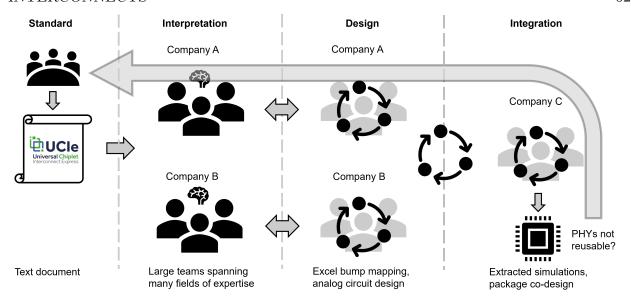

| 5.1          | Typical 2.5D D2D interconnect design and integration process                                                                                                     | 62  |

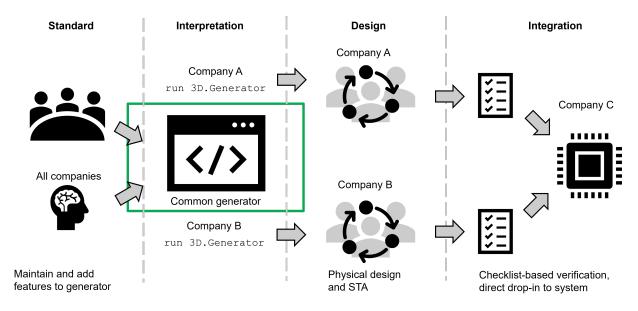

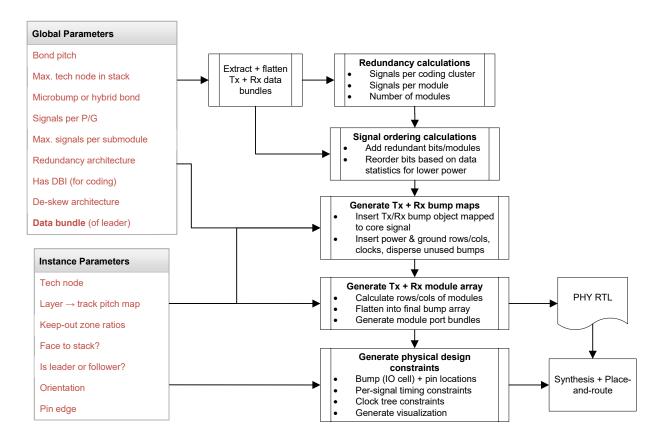

| 5.2          | Proposed 3D D2D interconnect design and integration process                                                                                                      | 64  |

| 5.3          | $UCIe-3D^{TM}$ circuit architecture                                                                                                                              | 66  |

| 5.4          | Module-shift redundancy scheme, repairing a defect spanning 1, 2, and 4 modules.                                                                                 | 67  |

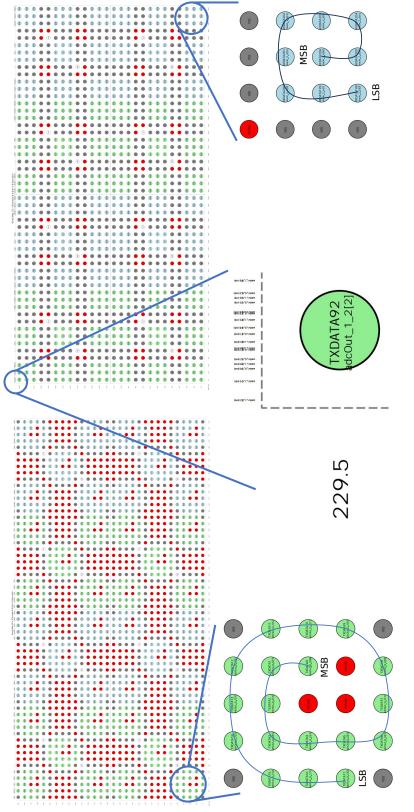

| 5.5          | Spatial coding redundancy packing concept                                                                                                                        | 70  |

| 5.6          | Logic/flop location in the spatial coding redundancy scheme. Bump-facing side                                                                                    |     |

|              | (top) versus core-facing side (bottom)                                                                                                                           | 71  |

| 5.7          | Generator architecture: parameters, compilation, and outputs                                                                                                     | 72  |

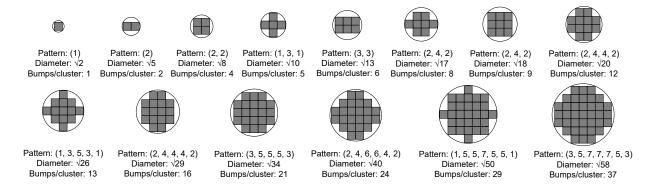

| 5.8          | Square in circle packing arrangements                                                                                                                            | 74  |

| 5.9          | Circle in square packing arrangements                                                                                                                            | 74  |

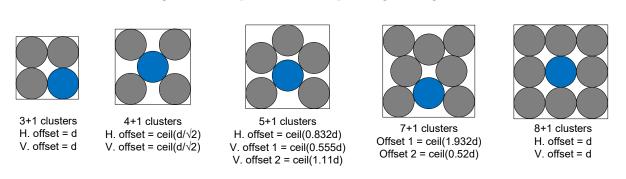

| 5.10         | Programmatic bundle generation and connection                                                                                                                    | 76  |

| 5.11<br>5.12 | Doodle-generated visualizations for coding (left) and shifting (right) redundancy. HPWL calculation for clock tree insertion and core-facing input/output delays | 78  |

|              | (pins on North edge)                                                                                                                                             | 81  |

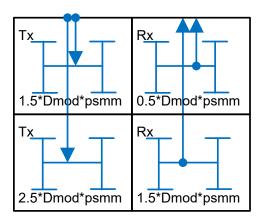

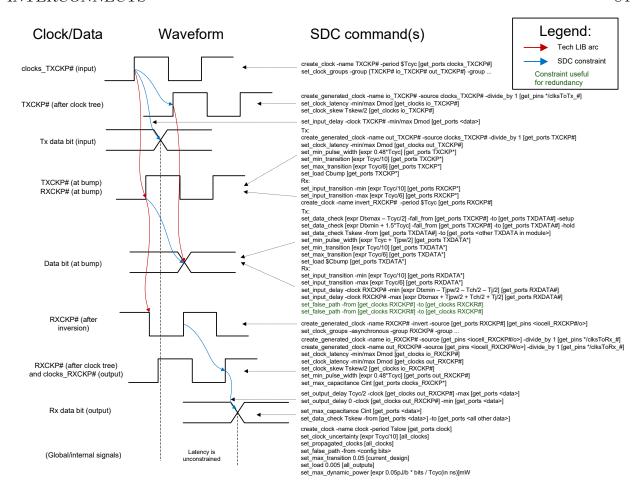

|              | Visualized SDC constraints                                                                                                                                       | 84  |

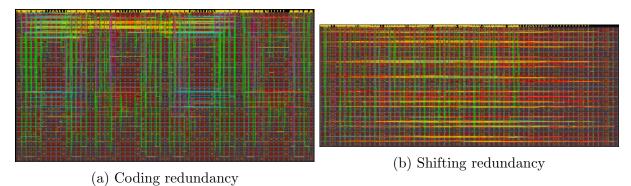

|              | Innovus generated layouts                                                                                                                                        | 87  |

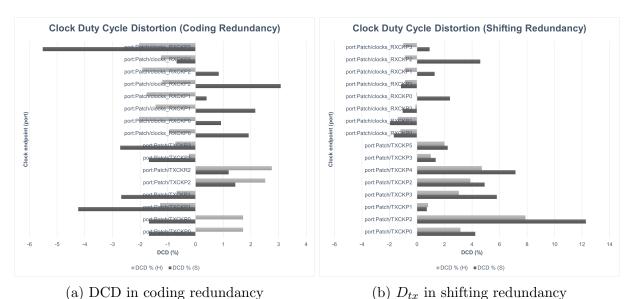

|              | Forwarded clock duty cycle distortion                                                                                                                            | 88  |

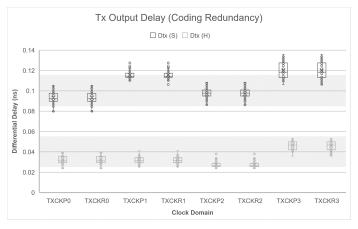

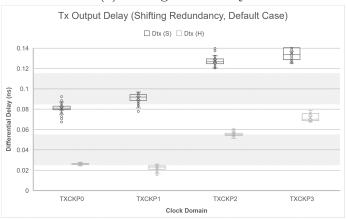

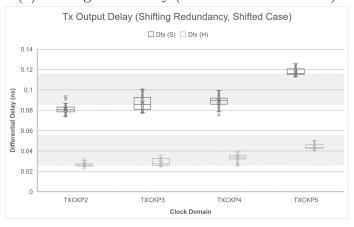

| 5.16         | $D_{tx}$ measurements. $D_{tx,min} + t_{skew}$ indicated by lower shaded region, $D_{tx,max} + t_{skew}$ indicated by upper shaded region                        | 89  |

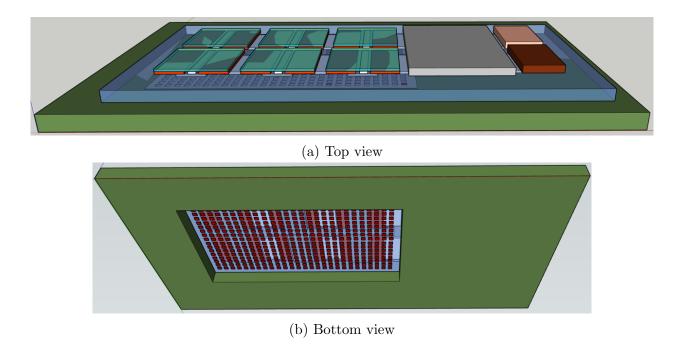

| 6.1<br>6.2   | 3D mockup of 2-high chiplet stack and on-package antennas                                                                                                        | 93  |

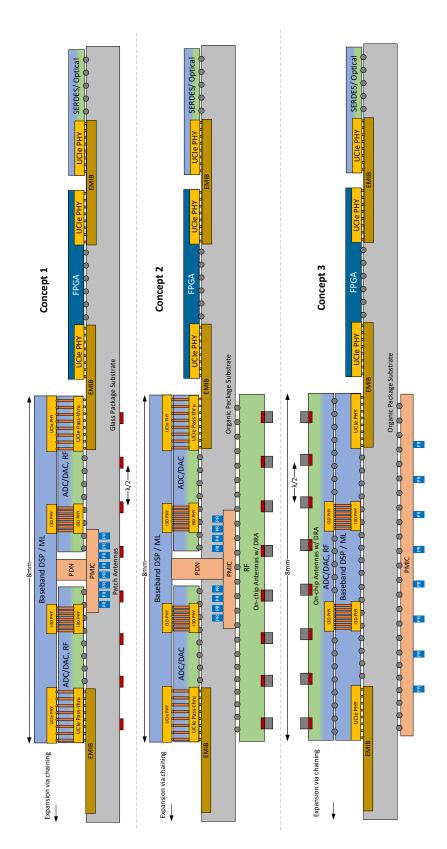

|              | agement, and more                                                                                                                                                | 94  |

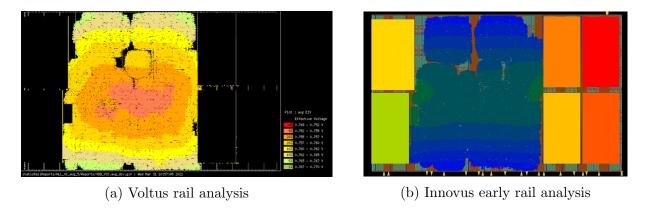

| A.1          | Rail analysis results on the ASAP7 tutorial configuration.                                                                                                       | 113 |

## List of Tables

| 2.1 | State-of-the-art interconnect comparison                                 |

|-----|--------------------------------------------------------------------------|

| 2.2 | Roadmaps: Can Everything Fit Inside $(\lambda/2)^2$ ?                    |

| 3.1 | Supported tool (left) and tech (right) plugins                           |

| 3.2 | Dummy SRAM timing equation parameters                                    |

| 3.3 | Comparison of chips using Hammer                                         |

| 4.1 | Hypothetical technology scaling roadmap                                  |

| 4.2 | Source-Synchronous clocking topology tradeoffs                           |

| 5.1 | Qualitative comparison of D2D interconnect construction methodologies 65 |

| 5.2 | Metrics for coding and shifting redundancy                               |

| В.1 | Global Technology Parameters                                             |

| B.2 | Global Design Parameters                                                 |

| В.3 | Instance Technology Parameters                                           |

| B.4 | Instance Design Parameters                                               |

| B.5 | I3DBump Container Members   117                                          |

| B.6 | I3DCore Container Members                                                |

## List of Listings

| 5.1 | Transmit clock SDC example                                                                                                                  | 79  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2 | Transmit clock with shift redundancy SDC example                                                                                            | 80  |

| 5.3 | Receive clock SDC example                                                                                                                   | 80  |

| 5.4 | Constraining lane-to-lane skew                                                                                                              | 83  |

|     | Snippet of hard-coded selection of technology LEF in sky130.tech.json Snippet of code-based selection of technology LEF in Sky130Tech class |     |

| B.1 | ModuleBundle Generation                                                                                                                     | 118 |

| B.2 | CoreBundle to dataBundle Connection                                                                                                         | 119 |

| В.3 | Subset of Encoder Generator                                                                                                                 | 120 |

### Acknowledgments

I feel tremendously lucky to have been able to learn from so many talented people here at Berkeley and at my various internships, co-ops, and full-time positions before and during my Doctoral studies.

Most importantly, Bora Nikolić, my advisor, who has been instrumental in supporting me with a wealth of resources and helping me think critically about my own and others' research. Bora, you are particularly skilled in connecting academia with industry, which has been invaluable in allowing me to tape out such complex chips and work on 3D interconnect research. Though the way you set your expectations is simultaneously sky-high and frustratingly vague, I hope I was able to meet a sufficient number of them throughout my meandering journey. I will certainly miss your group meeting stories and industry gossip—I will have to find new sources of entertainment!

Secondly, I would like to thank Farhana Sheikh, my internship mentor turned committee member and now full-time manager. Your mentorship style is perfect, as you have stimulated my curiosity to dig ever deeper into problems; helped me think big picture and long-term; improved my communication and writing skills; and helped show me the ropes of the academic, industry, and government research landscape and politics. I am particularly grateful for your continuous support over the last two years and for the opportunity to continue working with you going forward.

I particularly enjoyed my internship experiences as they provided project diversity and new mentorship experiences, and am somewhat sad that I will not have the luxury of having these experiences going forward. Beyond Farhana, David Kehlet and others at Intel, including those in the Altera CTO Advanced Chiplet Technologies Group and the UCIe Standards Group: Jong-ru Guo, Zuoguo Wu, Gerald Pasdast, Zhiguo Qian, Sathya Tiagaraj, Stephen Wong, and Tanay Karnik, provided great feedback during the process of 3D interconnect design. Marcos Tavares at Nokia Bell Labs gave me a challenging project far outside my comfort zone on an analog implementation of for RNN-based eigenvalue decomposition that incredibly won the 2<sup>nd</sup> best internship project prize.

The other faculty members of my committee, Ali Niknejad and Jessica Boles were also instrumental in providing feedback and guidance. From my Hydra Spine tapeouts to my qualifying exam to a fascinating collaboration on piezoelectric resonator-based power conversion, you were patient and wonderful teachers. Multiple faculty at Columbia University, like Mingoo Seok, Peter Kinget, and David Vallancourt, put me on the path towards integrated circuits research. Finally, the team at Analog Bits taught me clocking and SerDes design, which proved to be surprisingly valuable throughout my time here despite my research being nominally unrelated.

Many senior graduate students helped me along the way, to whom I remain tremendously indebted. John Wright, Colin Schmidt, and Greg LaCaille showed me the ropes for how to tape out, spending countless hours teaching me physical design and analog integration. There is a long list of collaborators on the Hydra Spine tapeouts. Yue Dai was an amazing partner on the Hydra DSP project; James Dunn was the lead designer on the Hydra Spine

II package and PCB; Zhaokai Liu was a genius at using BAG to generate high-performance ADCs; Zhenghan Lin helped design clock receivers and distribution; Kwanseo Park helped with simulation; Paul Rigge helped with making a streaming memory block; Marko Kosunen helped with translating the Hydra system model to RTL; Ethan Chou helped design a VGA; Amin Torabi helped design a DAC; Zhongkai Wang, Woorham Bae, Minsoo Choi, and Kevin Zheng all helped design the SerDes. I cannot thank you all enough for your generous contributions to project and would like to apologize for not being able to see them through to completion and publication.

Daniel Grubb was my best friend throughout my journey, with me all the way from all-nighters during our first year tapeouts to class project partners, fun deskmate, and roommate. Alisha Menon was a great project partner, and I am proud of how our work contributed to your thesis. Vighnesh Iyer and Mustapha Touhami were also wonderful partners on projects ranging from classes to research. Ken Ho, Felicia Guo, Kunmo Kim, Hesham Beshary, Rohit Braganza, Daniel Kramnik, Bob Zhou, Emily Naviasky, and Lorenzo Iotti, all graced me with infinite wisdom and wonderful camaraderie. Everyone else at the ADEPT/SLICE and BWRC labs, including staff like Candy and Brian Richards, were also instrumental in making my time here very enjoyable.

I have mentored many undergraduate students for chip bringup and Hammer projects: Bryan Ngo, Edison Wang, Daniel Chang, Mike Xiao, Josh Davis, Rohit Kanagal, Reuben Thomas, Evan Li, Cade Richard, Jason Chiou, Adam Ashkenazi, Arda Akman, Derrick Qi, and Maithili Bapat. Though your project quality was certainly very hit or miss, I thank you all for making my mentoring experience surprisingly rewarding as I learned how to communicate complex ideas to a new generation of engineers and work with very different learning and working styles.

I would also like to thank my friends, old and new, near and far, for going on amazing trips and gatherings to experience all of what this world has to offer. My partner, Helen Zhou, has been a constant source of support and love, despite us being across the country from each other for the last 7 and a half years! I cannot express how much I enjoy spending time with you (and Sage!), sharing so many interests and values as we take in new experiences. I am constantly humbled by your ability to take up new hobbies, delighted by your music and food tastes, and spoiled by your care and compassion. It has truly been a wild ride as we have both been so busy, me with my PhD and you with your medical school and residency. I very much look forward to the day when we don't have to video chat and fly across the country every month! Lastly, my parents, Shelley Mau and Seng Liew, have been the most supportive parents I could ask for, always encouraging me to do better and be better. Thank you so much for letting me explore my interests throughout my childhood, attempting to satisfy my unending curiosity, and trusting my big life decisions. I hope to have made you proud, and will strive to continue doing so!

## **Funding**

I would like to thank a myriad of sponsors for their financial support and providing opportunities to tape out on advanced process nodes.

- The Hydra Spine I chip was funded via DARPA CRAFT under Grant HR0011-16-C0052 and DARPA under JUMP Task 2778.026 Grand Challenge Demonstration: Massive and Point-Point MIMO.

- The Hydra Spine II chip was funded by Intel Corporation via a free Intel 22FFL shuttle and DARPA under JUMP Task 2778.026 Grand Challenge Demonstration: Massive and Point-Point MIMO.

- Hammer development was funded via DARPA CRAFT under Grant HR0011-16-C0052 and NSF CCRI Award 2016662.

- 3D interconnect development and base station concept exploration was funded via the Intel PSG (now Altera) intern fund and DARPA under JUMP DSSP Task 2278.054 Architectures for RADAR and Wireless Systems with 3D Heterogeneous Integration.

Finally, I would like to thank the sponsors of the Berkeley Wireless Research Center, ADEPT Lab, and SLICE Lab for general funding that made all this work possible.

## Chapter 1

## Introduction

### 1.1 Motivation

The last few decades have witnessed the incessant growth of wireless communication traffic, driven by the rapid proliferation of internet-connected devices for applications ranging from mobile video to autonomous vehicles to augmented/virtual reality. An examination of the evolution of cellular (3GPP) and Wi-Fi (IEEE 802.11) standards reveals a steady march towards a target of 1Tbps data rate per-user equipment (UE) by the middle of the next decade to satisfy an annualized growth rate in mobile traffic of about  $1.4 \times [1]$ . Compounding the problem, the peak density of these UEs is also increasing, such as in urban environments or venues like stadiums. To satisfy this need, standards like 6G are targeting a  $10 \times$  connection density boost over 5G to a target of 10 million devices per square kilometer [2].

Unfortunately, the capabilities of wireless communication technologies are currently unable to reach those targets. Since Claude Shannon introduced the concept of channel capacity in 1948 [3], which states that a channel's capacity is a function of its bandwidth and signalto-noise ratio (Eq. 1.1), numerous innovations such as LDPC [4] and OFDM [5] have already brought modern communications very close to the Shannon limit. Increasing capacity can be achieved by increasing bandwidth, which is available only in the higher-frequency mm-Wave and sub-THz bands [6], leading to significant opportunities and challenges in circuit design and system integration. Increasing spectral efficiency (capacity divided by bandwidth) by a single bit/s/Hz requires a doubling of signal power, clearly not a scalable solution as wireless networks already consume about 200TWh of electricity annually-about 1% of global electricity consumption [7]. This is worsened by the fact that noise power also includes interference from other UEs, which is a function of network density. On the topic of density, networks serve multiple UEs within a given budget of frequency, time, and power using multiple access technology to divide up those axes. These techniques are known as FDMA, TDMA, CDMA, and OFDMA (and variants), which form the basis of wireless communications standards. Fundamentally, however, the combination of capacity-boosting and multiple access techniques are merely knobs to trade off per-UE capacity versus network density, but do not fundamentally increase the entire network's capacity within its frequency and power budgets.

$$C = B\log_2(1 + \frac{S}{N})\tag{1.1}$$

where

C = Channel capacity (bits/s)

B = Bandwidth (Hz)

S = Signal power (W)

N = Noise power (W)

In reality, wireless communications, by virtue of it occurring in three-dimensional space, has another dimension (i.e., budget) to divvy up: space. To achieve practical spatial multiplexing, massive MU-MIMO (multiple user, multiple-input, multiple-output) is the technique that utilizes a large number of antennas at a base station to communicate with cheap, MU-MIMO UEs [8]. This antenna array generates multiple, simultaneous, and non-overlapping beams of electromagnetic energy steered precisely to the direction of each UE (called beamforming), thereby forming distinct, nearly interference-free channels, upon which traditional capacity-boosting techniques can be applied. In this regime, increasing the number of antennas to infinity theoretically resolves to the asymptotes of:

- Infinitesimally thin beams, meaning infinite antenna array gain and minimal power per bit (only limited by intrinsic system noise)

- No more uncorrelated noise and interference, and no fading effects (e.g., multipath, reflections)

- Perfect channel reciprocity, meaning equal uplink and downlink channel characteristics, simplifying channel estimation

- Only contamination between cells, which can be mitigated by coordination and cell shrinkage

Ever since this concept was introduced, significant research and development has led to some small-scale deployments, but no demonstrations so far approach this asymptotic limit [9].

## 1.2 Background

## 1.2.1 Massive MIMO, in Hardware

Currently, practical beamforming requires applying coordinated phase shifts to an array of radio frequency (RF) front-ends to form constructive wavefront interference in the direction

of the desired beam. Phased array antennas must be spaced at half-wavelength  $(\lambda/2)$  to avoid grating lobes, which is spurious energy directed in undesired directions. These antennas are typically made as square metallic patches on a substrate, which are highly-manufacturable, have inherent directivity, and have a reasonably large steering angle [10]. Achieving higher fractional bandwidth (bandwidth divided by center frequency) is in active research, needed to take advantage of the 10's of GHz of bandwidth available at mm-Wave and sub-THz frequencies. Phase shifting can occur in multiple places in the signal chain, such as at the RF front-end, in the data converters, or in the digital baseband. The location and connectivity of the phase shifting block determines the number of signal chains after beamforming, which translates to the number of possible simultaneous beams that can be formed. There are additional considerations such as the supported dynamic range of received signals, beamforming performance, and power consumption when choosing between analog, hybrid, and digital beamforming architectures. To fully realize the massive MIMO paradigm, fully-digital beamforming with extremely large arrays allows for the most powerful and flexible method of implementing algorithms for channel estimation, detection, and nonlinearity correction. In this architecture, an entire signal chain (RF-to-bits) is dedicated to each antenna with all processing and phase shifting occurring in the digital domain. However, this requires an inordinate amount of data to be moved and processed within the system, leading it to be traditionally dismissed as too area- and power-hungry.

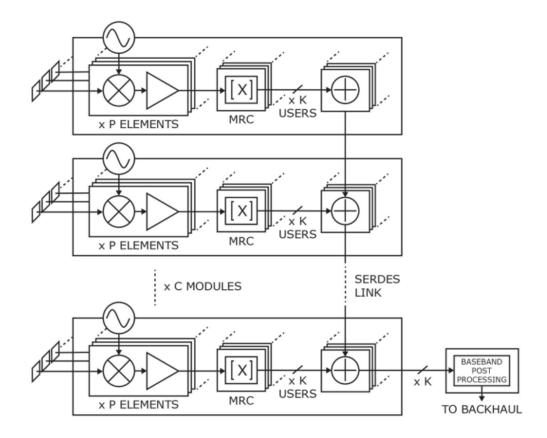

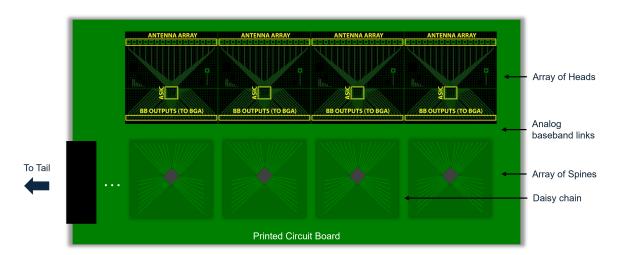

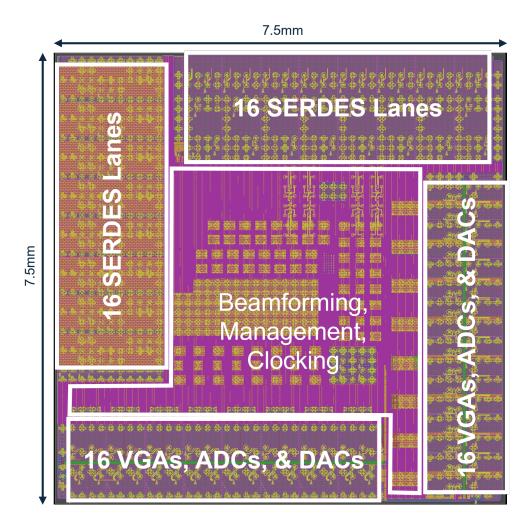

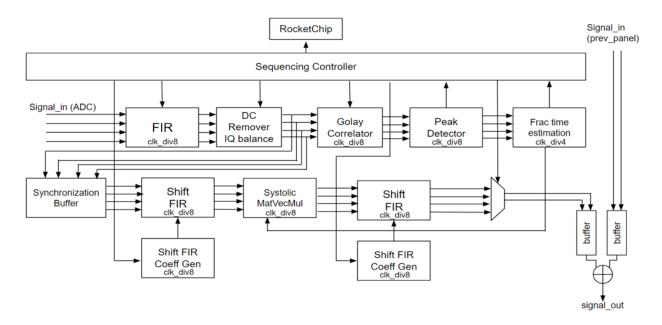

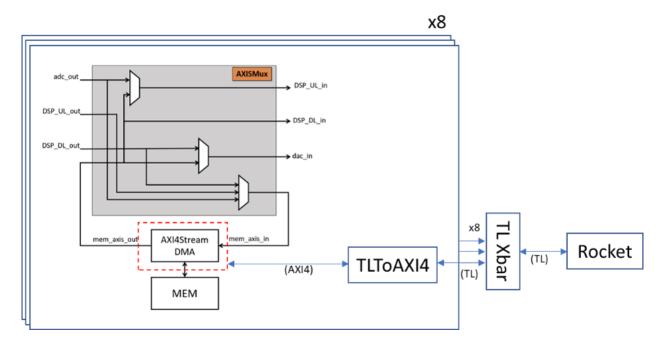

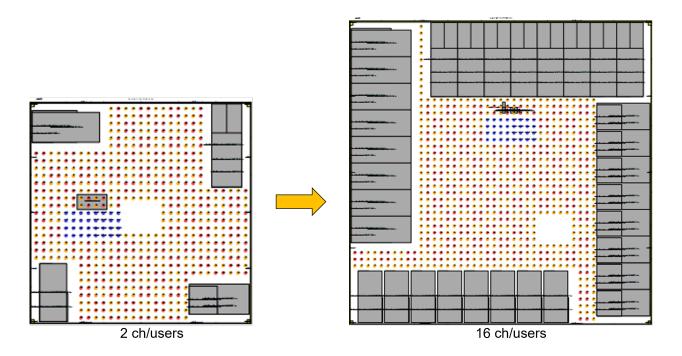

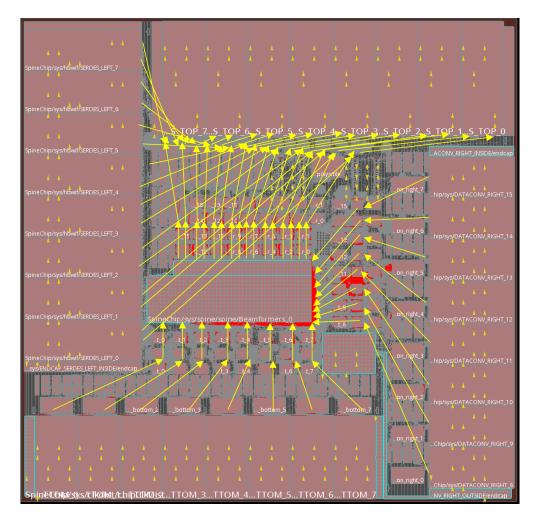

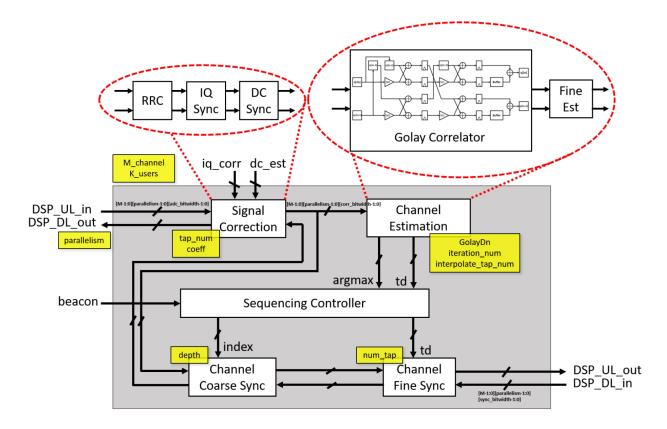

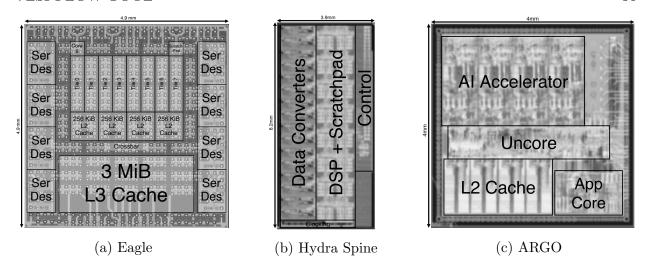

To begin to tackle the bandwidth limits of fully-digital beamforming, an architecture targeting scalable linear antenna arrays is presented in [11] and elaborated in [12]. This architecture, called Hydra, implements a two-stage beamforming algorithm, using interchangeable Head modules with radio frequency front-ends, Spine modules with digital maximum ratio combining (MRC) beamforming, and a Tail module with frequency-dependent zero-forcing (ZF) beamforming. Heads and Spines are paired together, and then Spines are daisy-chained together, solving the scalability problem. Bandwidth reduction is achieved in this algorithm by making the links between Spines and Tail proportional only to the number of users served in the system (K in Fig. 1.1), rather than the number of antennas (P in Fig. 1.1), which must be a multiple of the number of users for good per-user performance.

An E-band hardware implementation of this architecture is presented in [13]. Commercial off-the-shelf (COTS) components are used for the Head modules, and VCU118 field-programmable gate arrays (FPGAs) implement the logic for the Spine modules. Per-module beamformed data are aggregated on a PC that emulates the Tail logic. While this demonstrates the scalability of the architecture, it is still not practical for a real-world system, due to its high power consumption and latency compared to the low throughput (equivalent to only 10's of MHz of bandwidth). For comparison, numerous other testbeds are also limited in bandwidth and consume upwards of 1kW (if disclosed at all) [14]–[17].

Significant effort has been made in shrinking these testbeds with custom application-specific integrated circuits (ASICs). To-date, many published papers have claimed to support massive MIMO at a wide variety of frequencies, some well above 100GHz. However, they have generally come with significant caveats, such as only containing the RF-to-analog baseband chain (RF beamforming), only the analog baseband-to-bits chain, only generating a small

Figure 1.1: Hydra module architecture, reproduced from [13].

number of beams (e.g., only two afforded by H/V polarization), or supporting low bandwidth. Only [18] has demonstrated a fully-integrated (RF-to-bits) digital beamforming array for 16 antennas (in a  $4 \times 4$  array) and 4 simultaneous beams at 28GHz for 1GHz bandwidth—albeit only as a receiver (i.e., uplink only). Clearly, there remains a significant gap between the state-of-the-art and the theoretical limits of massive MIMO.

### 1.2.2 Generator-based and Agile Design

With the complexity of the chips needed to support massive MIMO and the relatively small amount of design resources allocated to wireless circuits, it is critical to employ development methodologies that dramatically improve design productivity. To this end, generator-based design contrasts with traditional methodologies by developing a large class of highly-parameterized designs from which one can generate many distinct instances. This allows for rapid design iteration without locking-in final parameters until more information is available—a key principle in the agile software design methodology as described in the Agile Manifesto [19].

UC Berkeley has since developed a menu of generators and implementation tools that en-

able agile hardware development. Chisel [20] is a Scala-based hardware description language, upon which generators such as the RocketChip [21] RISC-V [22] processor core are written. Hardware generators like this are integrated into the Chipyard [23] platform, a one-stop shop for SoC designers to write generators, simulate them, and implement them on FPGAs (with FireSim [24]) or ASICs (with Hammer [25], described in detail in Chapter 3). Beyond digital design, Berkeley has also developed the Berkeley Analog Generator (BAG) [26], an analog circuit generator framework that dramatically reduces the time it takes to create analog IP and port them to new process technologies. The work described in Chapters 2, 4, and 5 all extensively employ combinations of these tools for significant design productivity gains.

### 1.2.3 Heterogeneous Integration

In Chapter 2, the case is made for heterogeneous integration (HI) to make massive MIMO a reality. HI, as a concept, especially applied to phased arrays, is nothing new. In fact, Gordon Moore, in a follow-up to his seminal Moore's Law paper [27], described:

"It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected."

and:

"The successful realization of such items as phased-array antennas, for example, using a multiplicy of integrated microwave power sources, could completely revolutionize radar."

Currently, industry is investing heavily into enabling HI for a wide variety of applications. Led by advancements in wafer-level processing and packaging, chiplets are now able to be placed and connected very closely together, unlocking significant performance boosts.

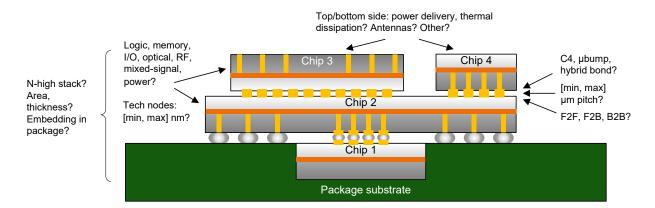

HI architectures can be categorized by the following paradigms [28]: scale-up, split, disaggregate, and aggregate. In the scale-up paradigm, capabilities can be expanded by tiling identical compute units into an array, as exemplified by [29] and [30]. In the split paradigm, an existing design is chopped up into separate chiplets, usually driven by the need to exceed the reticle limit or improve chip yield, as exemplified by [31] and [32]. In the disaggregate paradigm, different components of a design, such as cache memory or I/O, are split into their own chiplets, thereby optimizing for process technology and/or data movement, as exemplified by [33] and [34]. In the aggregate paradigm, a system is built-up from modular functional units to achieve maximum performance and to enable entirely new applications, as exemplified by [35]. If done correctly, the possibilities for IP reuse (in the form of chiplets in an ecosystem) and new capabilities are unbounded in the aggregate paradigm, limited only by resources and industry's will to coalesce around chiplet standards. This is explored in [36], whose radio cube concept forms a significant basis for this dissertation.

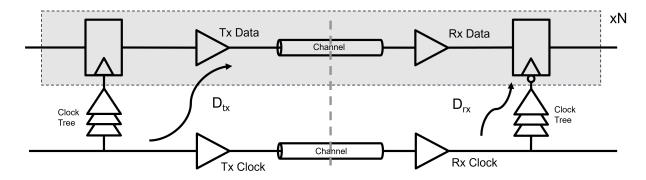

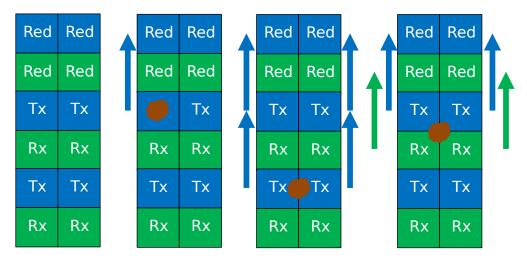

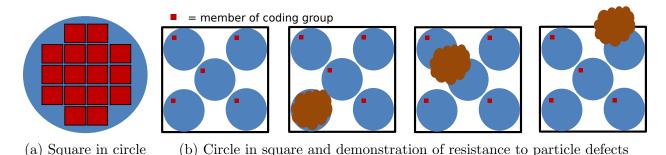

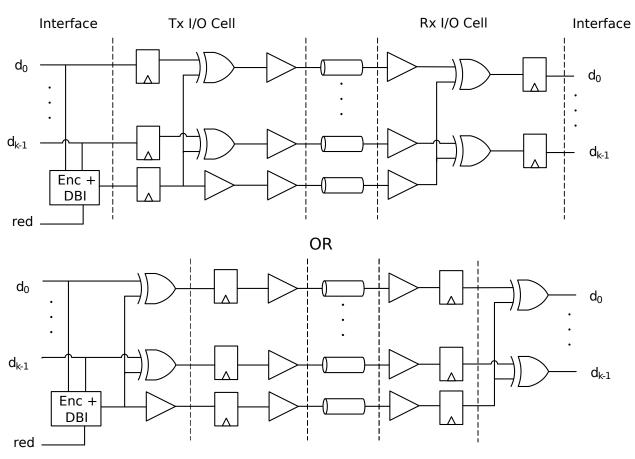

## 1.3 Dissertation Scope and Outline