## Split-Phase and Multi-Resonant Operation of Hybrid Switched-Capacitor Converters

Rose Abramson Robert Pilawa-Podgurski

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2024-189 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2024/EECS-2024-189.html

September 23, 2024

Copyright © 2024, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Split-Phase and Multi-Resonant Operation of Hybrid Switched-Capacitor Converters

By

Rose Antoinette Abramson

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Robert C.N. Pilawa-Podgurski, Chair Assistant Professor Jessica Boles Professor Kristofer Pister Associate Professor Hanh-Phuc Le

Spring 2024

### Split-Phase and Multi-Resonant Operation of Hybrid Switched-Capacitor Converters

$\begin{array}{c} \text{Copyright 2024} \\ \text{by} \\ \text{Rose Antoinette Abramson} \end{array}$

#### Abstract

Split-Phase and Multi-Resonant Operation of Hybrid Switched-Capacitor Converters

by

#### Rose Antoinette Abramson

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Robert C.N. Pilawa-Podgurski, Chair

Hybrid switched-capacitor (SC) converters have seen increased use in applications that demand both high efficiency and high power density. These converters exhibit the traditional benefits of pure SC converters, such as efficient utilization of switches and the use of energy-dense capacitors, along with lossless capacitor charge transfer due to the use of one or more augmenting inductors. Increased performance can also be obtained by using more complex control schemes than the traditional two-phase control common with pure switched-capacitor converters.

Split-phase control, one such modified control scheme, is used to ensure full soft-charging of all flying capacitors in several hybrid switched-capacitor topologies belonging to the Dickson-derived class of converters. Here, capacitors are inserted into the switch-capacitor network in a staggered manner to ensure that they do not over- or under-charge in each phase, which would result in lossy hard-charging transitions. However, the time at which to insert these capacitors can change based on operating condition, component tolerance, and phase-ordering. This work will present an analysis of these effects, as well as describe specific control schemes and active-tuning methods that can ensure full soft-charging operation.

In addition, other control schemes such as multi-resonant operation, can be utilized to achieve high-performance designs. Multi-resonant hybrid switched-capacitor converters operate with multiple operating phases per switching period, and can achieve the same conversion ratio as standard two-phase hybrid switched-capacitor converters with a fewer number of switches and capacitors, allowing for higher efficiency and power density design. One such topology, the cascaded series-parallel (CaSP) converter, will be analyzed, and several high-performance hardware prototypes designed for 48 V data center dc-dc power delivery will be presented.

$To \ Kai \\ for all \ the \ loving \ years \ gone \ by \ and \ all \ those \ yet \ to \ come \\$

## Contents

| $\mathbf{C}$ | onter | nts                                                                       | ii |

|--------------|-------|---------------------------------------------------------------------------|----|

| Li           | st of | Figures                                                                   | iv |

| Li           | st of | Tables                                                                    | xi |

| 1            | Intr  | roduction                                                                 | 1  |

|              | 1.1   | Introduction                                                              | 1  |

|              | 1.2   | Organization of Thesis                                                    | 3  |

| 2            | Soft  | -Charging of Hybrid Switched-Capacitor Converters                         | 6  |

|              | 2.1   | Introduction                                                              | 6  |

|              | 2.2   | Analyzing Arbitrary Switched-Capacitor Topologies for Soft-Charging Capa- |    |

|              |       | bility                                                                    | 8  |

|              | 2.3   | General Overview of the Nullspace Method                                  | 9  |

|              | 2.4   | Extension 1: Multiple Inductors at the Low-Side Port                      | 13 |

|              | 2.5   | Extension 2: Multiple Inductors with Tank Configuration                   | 20 |

|              | 2.6   | Extension 3: Multiple Operating Phases $(> 2)$                            | 24 |

|              | 2.7   | Chapter Summary                                                           | 25 |

| 3            | Spli  | t-Phase Switching Overview                                                | 26 |

|              | 3.1   | Hard-Charged Two-Phase Resonant Dickson Converter Operation               | 26 |

|              | 3.2   | Soft-Charged Split-Phase Resonant Dickson Converter Operation             | 30 |

|              | 3.3   | Split-Phase Timing Calculation                                            | 34 |

| 4            | Effe  | ects of Split-Phase Sub-Phase Ordering                                    | 35 |

|              | 4.1   | Introduction                                                              | 35 |

|              | 4.2   | Resonant Dickson Converter                                                | 39 |

|              | 4.3   | Dual Inductor Hybrid Converter                                            | 46 |

|              | 4.4   | Effect of Sub-Phase Ordering on Split-Phase Time Durations for the DIH    |    |

|              |       | Converter                                                                 | 69 |

| 5  | $\mathbf{Act}$ | ive Splitphase Control Using Capacitor Voltage Discontinuity Detec-       |           |

|----|----------------|---------------------------------------------------------------------------|-----------|

|    | tion           |                                                                           | <b>76</b> |

|    | 5.1            | Introduction                                                              | 76        |

|    | 5.2            | Theory of Operation                                                       | 77        |

|    | 5.3            | 8-to-1 Single-Ended Dickson Hardware Prototype                            | 81        |

|    | 5.4            | 8-to-1 Hybrid Interleaved-Input Single-Inductor Dickson (HISID) Converter |           |

|    |                | Hardware Prototype                                                        | 90        |

|    | 5.5            | Possible Extensions and summary                                           | 96        |

| 6  | Pas            | sive Volume Analysis Using Peak Energy Storage Requirements               | 97        |

|    | 6.1            | Introduction of Methodology                                               | 97        |

|    | 6.2            | Topological Vectors                                                       | 98        |

|    | 6.3            | Phase Timings                                                             | 104       |

|    | 6.4            | Passive Volume Calculation                                                | 107       |

|    | 6.5            | Comparison of ReSC Converter Passive Volume                               | 115       |

|    | 6.6            | Chapter Summary                                                           | 116       |

| 7  | The            | Cascaded Series-Parallel (CaSP) Converter                                 | 117       |

|    | 7.1            | Introduction                                                              | 117       |

|    | 7.2            | Theory of Operation                                                       | 118       |

|    | 7.3            | Hardware Prototypes                                                       | 135       |

|    | 7.4            | CaSP Split-Phase Switching                                                | 148       |

|    | 7.5            | Chapter Summary                                                           | 154       |

| 8  | Con            | nclusion                                                                  | 155       |

|    | 8.1            | Future Work                                                               | 155       |

|    | 8.2            | Conclusion                                                                | 157       |

| Bi | bliog          | graphy                                                                    | 158       |

# List of Figures

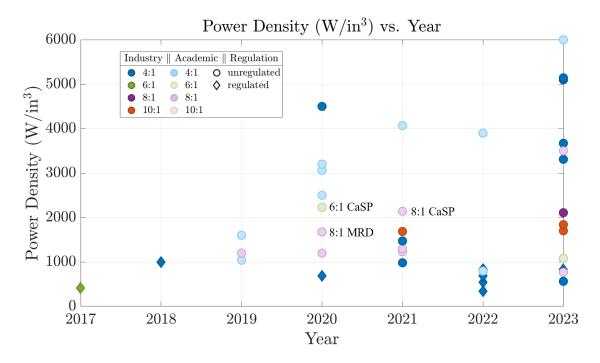

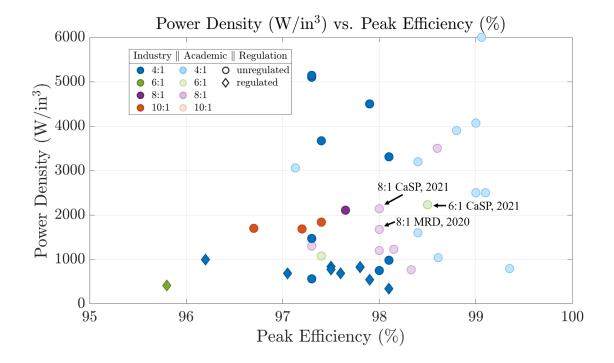

| 1.1                               | Power density versus year-of-release, for a survey of 48 V / 54 V intermediate bus converters for data center applications. Converters are categorized by conversion ratio, regulation capability, and whether the work is academic or commercial Power density versus peak efficiency, for a survey of 48 V / 54 V intermediate bus converters for data center applications. Converters are categorized by conversion ratio, regulation capability, and whether the work is academic or commercial | 2        |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

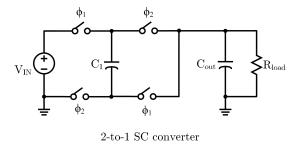

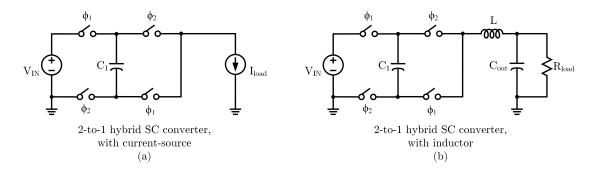

| 2.1<br>2.2                        | Example pure SC converter, showing a 2-to-1 conversion ratio Example hybridized SC converter, showing a 2-to-1 conversion ratio. (a) shows hybridization with a controlled-current source load, and (b) shows hybridization                                                                                                                                                                                                                                                                         | 7        |

| 2.3                               | with an inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7<br>8   |

| <ul><li>2.4</li><li>2.5</li></ul> | Output impedance, $R_{\text{out}}$ , versus frequency for a pure SC converter and a hybrid SC converter                                                                                                                                                                                                                                                                                                                                                                                             | 8        |

| 2.6                               | and $\phi_2$ are annotated on the schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14<br>14 |

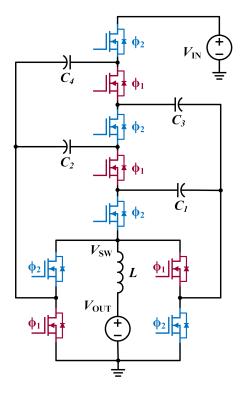

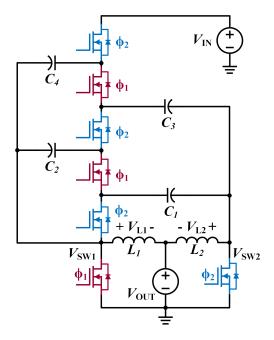

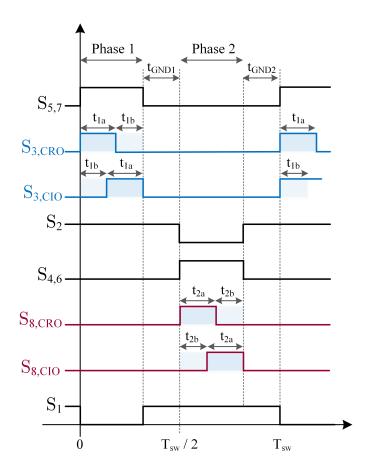

| 2.7                               | Schematic drawing of a 5-to-1 DIH converter. The two-phase gate signals $\phi_1$ and $\phi_2$ are annotated on the schematic. Regulating phases can be ignored for this analysis.                                                                                                                                                                                                                                                                                                                   | 15       |

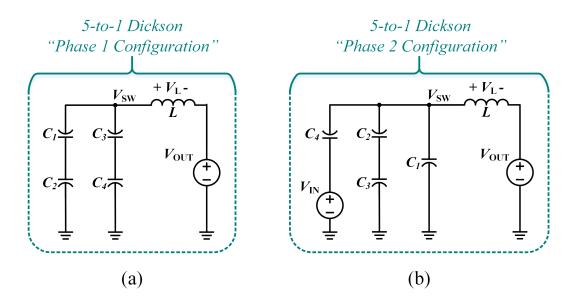

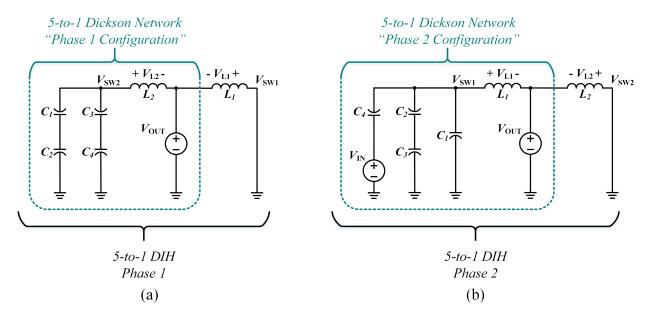

| 2.8                               | Phase equivalent circuits for the 5-to-1 DIH Converter. The switch-capacitor network configuration is the same as that in the 5-to-1 Dickson converter, as labeled by the teal bracket.                                                                                                                                                                                                                                                                                                             | 16       |

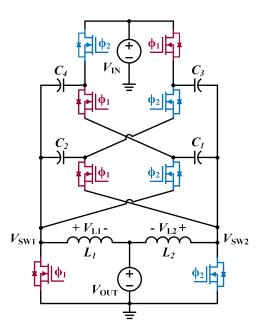

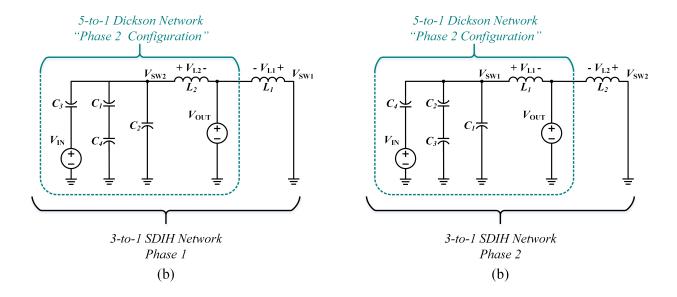

| 2.9                               | Schematic drawing of a 3-to-1 SDIH converter. The two-phase gate signals $\phi_1$                                                                                                                                                                                                                                                                                                                                                                                                                   | 10       |

| 2.10                              | and $\phi_2$ are annotated on the schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19       |

|                                   | ration" of the 5-to-1 Dickson converter for both of its own phases                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19       |

| 2.11 | Schematic drawing of a 5-to-1 dual LC tank converter. The two-phase gate signals $\phi_1$ and $\phi_2$ are annotated on the schematic                                                                                                                               | 21 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

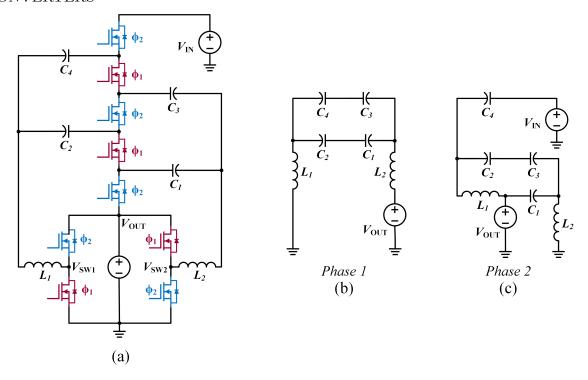

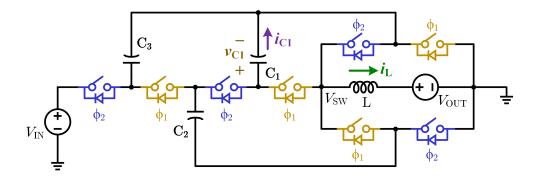

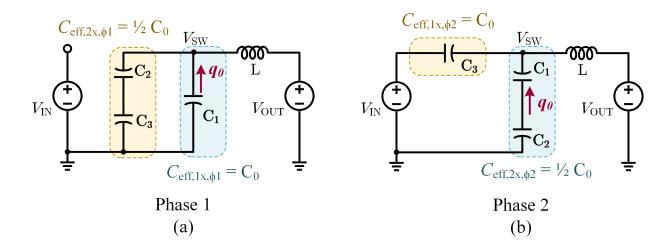

| 3.1  | Schematic drawing of the 4-to-1 resonant Dickson converter, operated with two-<br>phase gate signals, $\phi_1$ and $\phi_2$                                                                                                                                         | 27 |

| 3.2  | Simplified Phase 1 and Phase 2 equivalent circuits for the 4-to-1 resonant Dickson converter. The effective branch capacitances are labeled, as is the charge into and out of $C_1$                                                                                 | 27 |

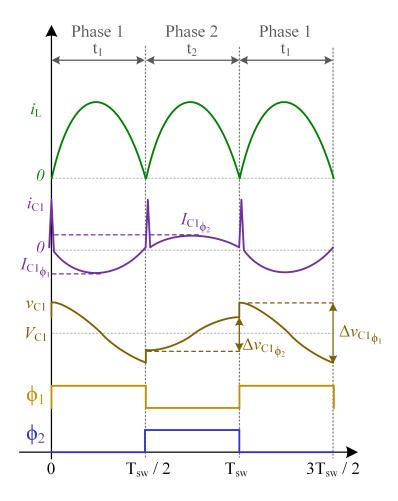

| 3.3  | Operating waveforms for the 4-to-1 resonant Dickson converter, under two-phase control. The inductor current, $i_L$ ; $C_1$ capacitor current, $i_{C_1}$ , and voltage, $v_{C_1}$ ; and phase control signals, $\phi_1$ and $\phi_2$ are illustrated                | 30 |

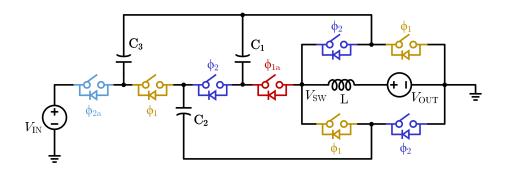

| 3.4  | Schematic drawing of the 4-to-1 resonant Dickson converter, operated with split-                                                                                                                                                                                    |    |

| 3.5  | phase gate signals, $\phi_{1a}$ , $\phi_{1b}$ , $\phi_{2a}$ , and $\phi_{2b}$                                                                                                                                                                                       | 31 |

| 3.6  | 4-to-1 resonant Dickson converter                                                                                                                                                                                                                                   | 31 |

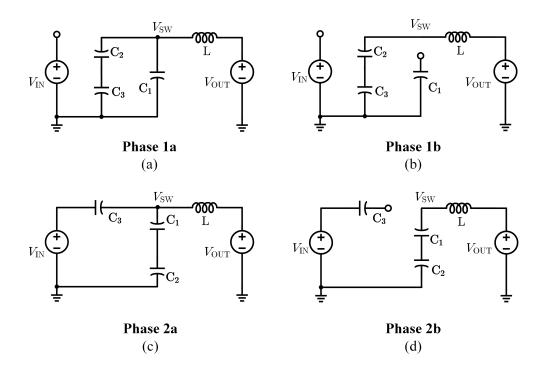

|      | phase control signals, $\phi_{1a}$ , $\phi_{1b}$ , $\phi_{2a}$ , and $\phi_{2b}$ are illustrated                                                                                                                                                                    | 33 |

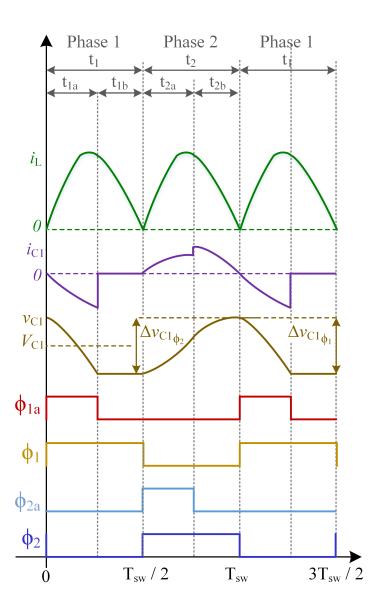

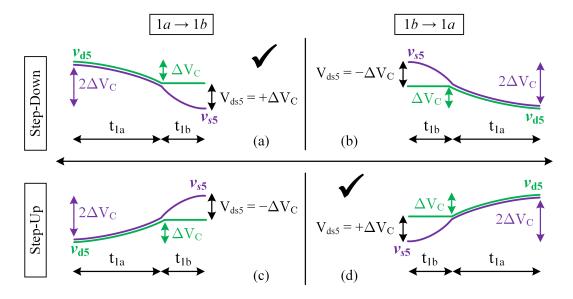

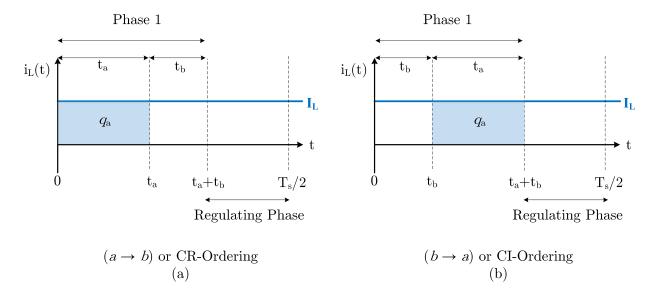

| 4.1  | General illustration of sub-phase $a$ and $b$ capacitor network configurations for split-phase operation. Capacitor removal ordering (i.e. $a \to b$ , top), and capacitor insertion ordering (i.e. $b \to a$ , bottom) are illustrated. Optional regulation phases |    |

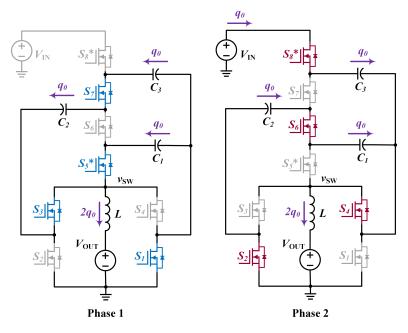

| 4.2  | in which all capacitors are disconnected are shown in between Phase 1 and Phase 2. Annotated charge flow diagram for the step-down and step-up configurations of an $N=4$ resonant Dickson converter, with circuit states shown for Phase 1 and                     | 37 |

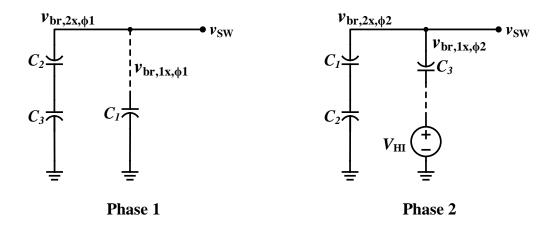

| 4.3  | Phase 2. Switches $S_5$ and $S_8$ are only ON for a portion of their respective phases.<br>Phase 1 and Phase 2 equivalent circuits for the Dickson converter in Fig. 4.2a                                                                                           | 40 |

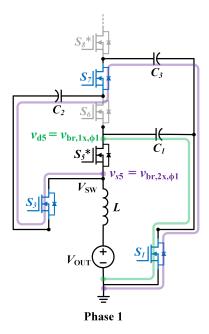

| 4.4  | and Fig. 4.2b                                                                                                                                                                                                                                                       | 42 |

| 4.4  | of $S_5$ , $v_{d5}$ , equals the branch voltage $v_{\text{br},1x,\phi_1}$ . The source voltage of $S_5$ , $v_{s5}$ , equals the branch voltage $v_{\text{br},2x,\phi_1} = v_{\text{SW}}$ . $S_5$ is OFF during Phase 1b                                             | 44 |

| 4.5  | Phase 1 source and drain voltages for device $S_5$ , as labeled in Fig. 4.4. Device $S_5$ is turned OFF for all $b$ phases. The branch voltage behavior is shown for both $1a \to 1b$ and $1b \to 1a$ phase orderings for step-down and step-up operation. Note     |    |

| 4.6  | that $v_{s5} = v_{SW}$ for the entirety of Phase 1                                                                                                                                                                                                                  | 44 |

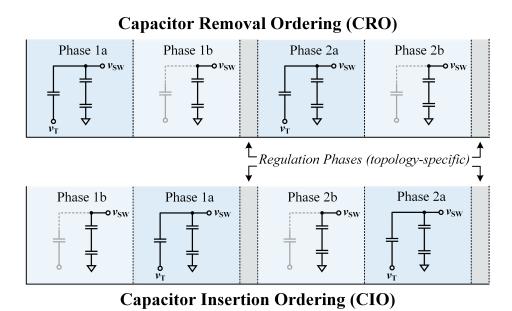

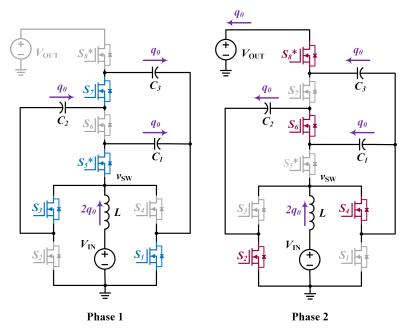

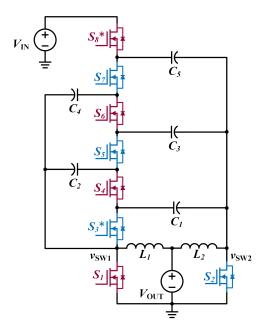

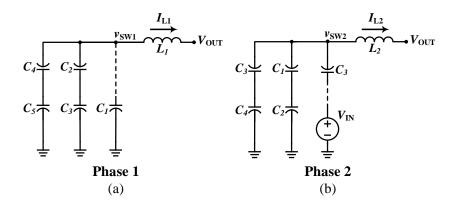

| 4.7  | require split-phase switching and are marked with an asterisk (*) Gate signals for CRO and CIO control schemes applied to the DIH converter. The split-phase switches are controlled with $S_{3,\text{CRO}}$ and $S_{5,\text{CRO}}$ for CRO control                 | 46 |

|      | and with $S_{3,CIO}$ and $S_{5,CIO}$ for CIO control. All other switches have identical gate signals for both control schemes                                                                                                                                       | 47 |

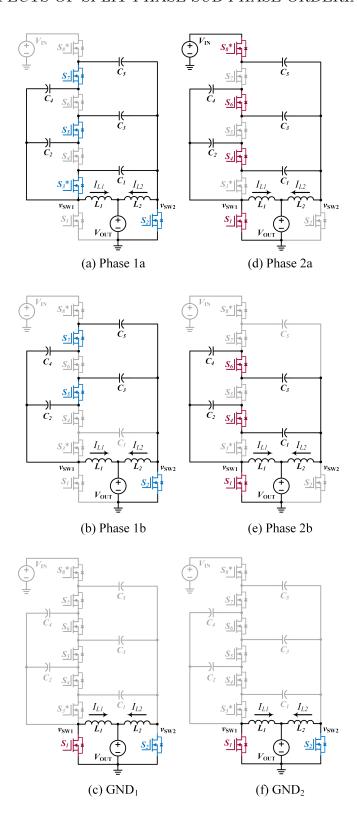

| 4.8  | Phase equivalent circuit states for the step-down $N=6$ DIH converter                                                                      | 49         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.9  | Charge flow for the step-down $N=6$ DIH converter, for the entirety of (a)                                                                 |            |

|      | Phase 1 and (b) Phase 2. Soft-charging operation is assumed                                                                                | 50         |

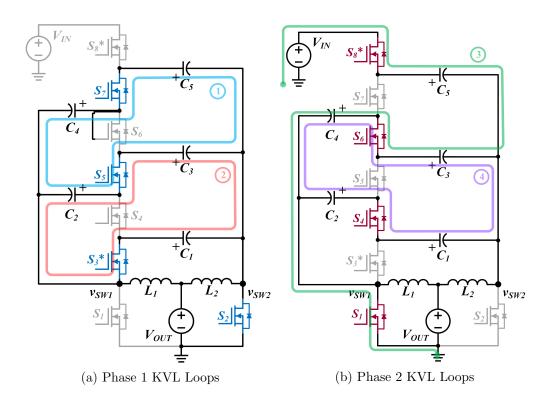

| 4.10 | KVL loops for determining mid-range DC voltages, in (a) Phase 1 and (b) Phase                                                              |            |

|      | 2. For CRO control, the loops should be evaluated at the start of Phase 1a (i.e.                                                           |            |

|      | the overall start of Phase 1). For CIO control, the loops should be evaluated at                                                           |            |

|      | the end of Phase 1a (i.e. the overall end of Phase 1)                                                                                      | 53         |

| 4.11 | Equivalent circuits for the DIH converter in (a) Phase 1 and (b) Phase 2                                                                   | 56         |

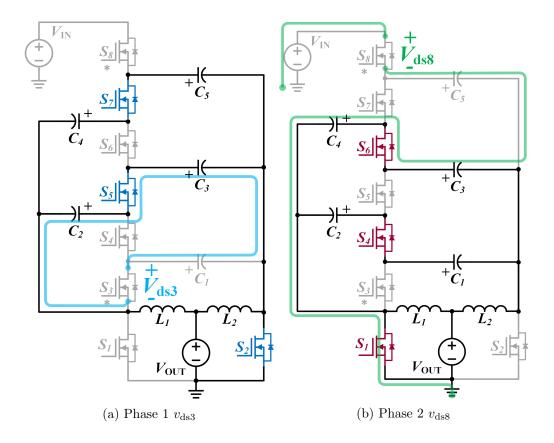

| 4.12 | Voltage loops to calculate split-phase switch blocking voltage for (a) Phase 1b                                                            |            |

|      | and (b) Phase 2b. For CRO control, (a) should be evaluated at the end of Phase                                                             |            |

|      | 1b (i.e. the overall end of Phase 1). For CIO control, (b) should be evaluated at                                                          |            |

|      | the <i>start</i> of Phase 1b (i.e. the overall start of Phase 1)                                                                           | 60         |

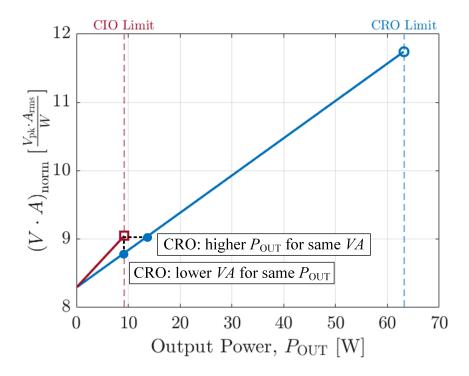

| 4.13 | Maximum normalized switch stress $(V \cdot A)_{\text{norm}}$ voltage as a function of output                                               |            |

|      | power, $P_{\text{OUT}}$ , for CRO and CIO timing schemes for step-down operation. The                                                      |            |

|      | limit $\Delta_{\text{CRO,max}}$ is found assuming a maximum reverse blocking voltage of 1 V. The                                           |            |

|      | output power corresponding to the maximum capacitor voltage ripple conditions                                                              |            |

|      | are illustrated by the CRO and CIO limit lines                                                                                             | 64         |

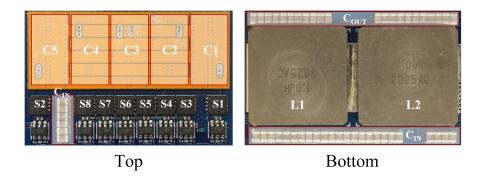

| 4.14 | Annotated photograph of the 48 V input, $N=6$ DIH converter hardware proto-                                                                |            |

|      | type. Dimensions: $23.2 \text{mm} \times 35.5 \text{mm} \times 5.7 \text{mm}$                                                              | 65         |

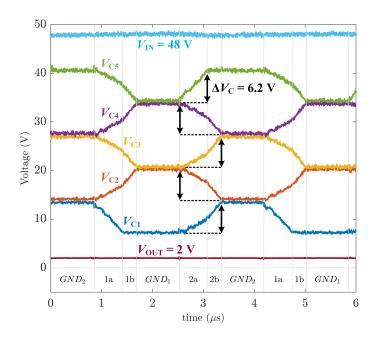

| 4.15 | Measured flying capacitor waveforms at $V_{\text{IN}} = 48 \text{ V}$ , $V_{\text{OUT}} = 2 \text{ V}$ , $I_{\text{OUT}} = 26 \text{ A}$ , |            |

|      | and $f_{\rm sw} = 300$ kHz. The capacitors are operating near their theoretical maximum                                                    |            |

|      | ripple, with a peak-to-peak voltage swing of 6.2 V across all flying capacitors                                                            | 67         |

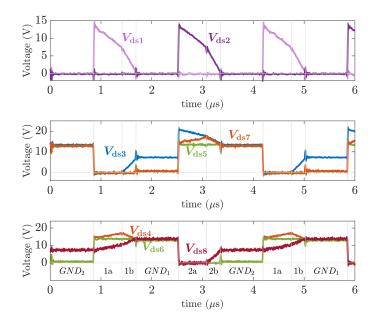

| 4.16 | Measured switch $V_{\rm ds}$ waveforms at $V_{\rm IN}=48$ V, $V_{\rm OUT}=2$ V, $I_{\rm OUT}=26$ A, and                                    |            |

|      | $f_{\rm sw} = 300$ kHz. All switches exhibit positive blocking voltages over the entire                                                    | <b>0</b> • |

|      | switch period, due to the use of CRO control                                                                                               | 67         |

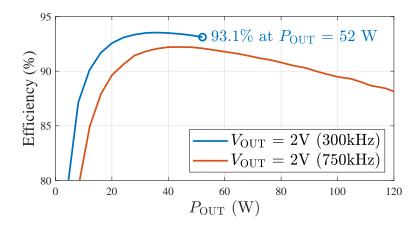

| 4.17 | Measured efficiency curve for $V_{\rm IN} = 48 \text{ V}$ , $V_{\rm OUT} = 2 \text{ V}$ , at a switching frequency                         |            |

|      | of $f_{\rm SW}=300$ kHz and 750 kHz. The output power is limited by the maximum                                                            |            |

|      | allowable fly capacitor voltage at 300 kHz, while the output power is thermally                                                            | 0.0        |

| 4.10 | limited at 750 kHz                                                                                                                         | 69         |

| 4.18 | Calculation of Phase $a$ charge assuming a constant current, $I_{\rm L}$ . Under this as-                                                  |            |

|      | sumption, the ordering of the $a$ and $b$ sub-phases does not have an impacted on                                                          | 71         |

| 1.10 | the calculated sub-phase timings                                                                                                           | 71         |

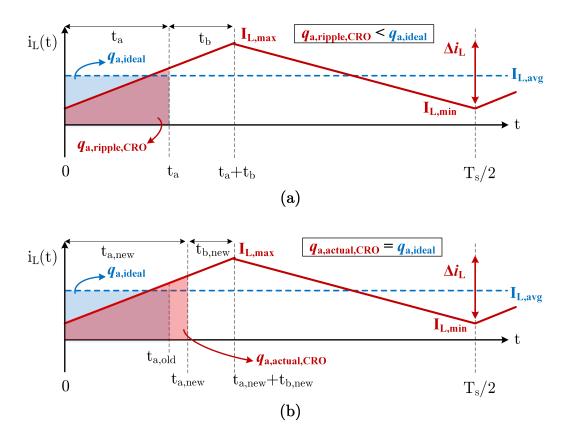

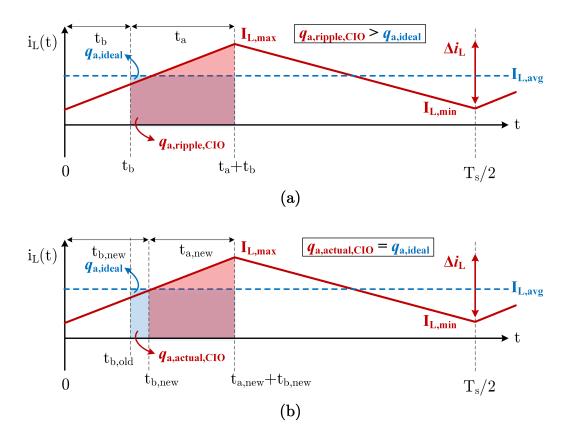

| 4.19 | Required adjustments to $t_a$ and $t_b$ sub-phase timings for CRO $(a \to b)$ ordering.                                                    |            |

|      | If Phase 1 starts with an a sub-phase, the constant-current derived timings are                                                            | 76         |

| 4.20 | an under-estimate of the required Phase 1a timing                                                                                          | 72         |

| 4.20 | Required adjustments to $t_a$ and $t_b$ sub-phase timings for CIO $(b \to a)$ ordering.                                                    |            |

|      | If Phase 1 starts with the b sub-phase, the constant-current derived timings are                                                           | 79         |

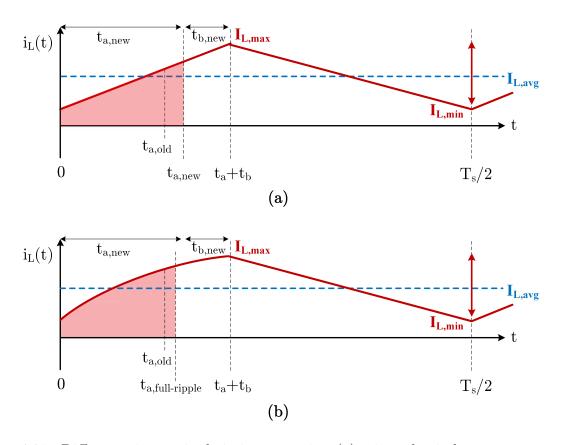

| 4 91 | an over-estimate of the required Phase 1a timing                                                                                           | 73         |

| 4.41 | small capacitor voltage ripple, and (b) both large inductor current ripple and                                                             |            |

|      | large capacitor voltage ripple, including the 2nd-order $LC$ tank effects                                                                  | 75         |

|      | range capaciton voltage rippie, including the zhu-order DC talix effects                                                                   | 10         |

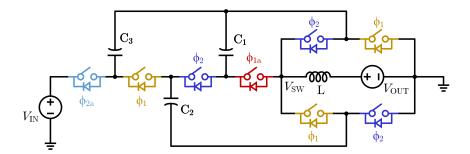

| 5.1        | Schematic drawing of a 4-to-1 single-inductor resonant Dickson converter, with operating phases labeled. The control signals $\phi_1$ and $\phi_2$ are the main phase                       |            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | signals, while $\phi_{1a}$ and $\phi_{2a}$ are the split-phase control signals                                                                                                              | 77         |

| 5.2        | Gating signals for the converter in Fig. 5.1. The capacitor voltage across $C_1$ is also                                                                                                    |            |

|            | shown for soft-charging operation (correct timing) and hard-charging operation                                                                                                              |            |

|            | (too long or too short timing)                                                                                                                                                              | 78         |

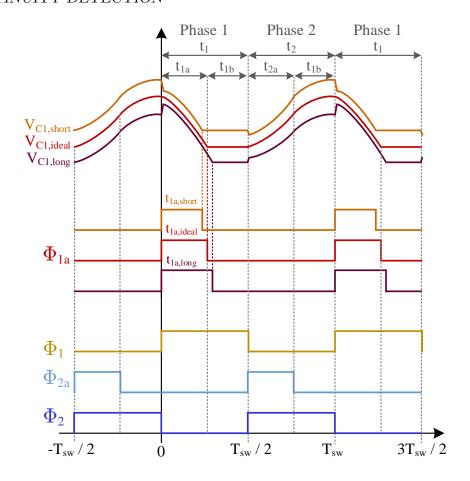

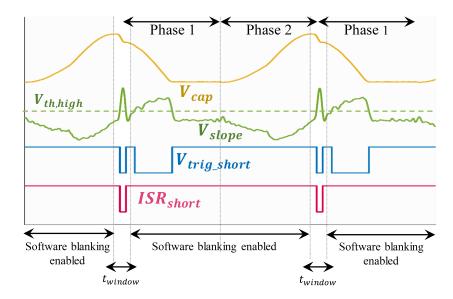

| 5.3        | Schematic of the active split-phase control circuitry, including the analog slope detect circuitry and the controller logic. The "short" timing path is color-coded                         |            |

|            | to match the experimental waveforms shown in Fig. 5.10                                                                                                                                      | 79         |

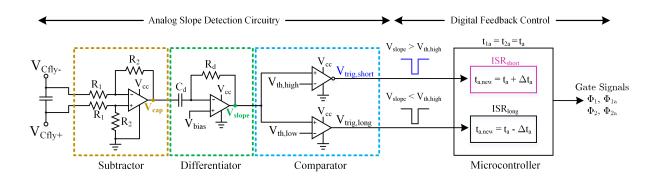

| 5.4        | Simplified control circuit waveforms, corresponding to the case where $t_a$ is too short. The output of each control stage is plotted. A blanking window is im-                             |            |

|            | plemented in code to isolate only the $V_{\text{slope}}$ pulses at the Phase 2-to-Phase 1                                                                                                   | 0.1        |

|            | transition                                                                                                                                                                                  | 81         |

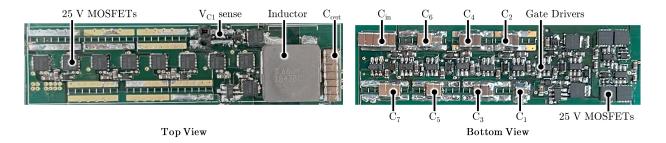

| 5.5        | Annotated photograph of the 8-to-1 Dickson power stage, with main components                                                                                                                | 0.0        |

| <b>-</b> . | labeled. Dimensions: 2.8 in (7.0 cm) x 0.7 in (1.8 cm)                                                                                                                                      | 82         |

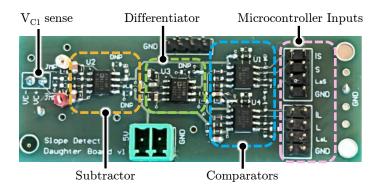

| 5.6        | Annotated photograph of the single-sided control daughterboard. Dimensions: 2.8 in (7.0 cm) x 1.1 in (2.8 cm)                                                                               | 82         |

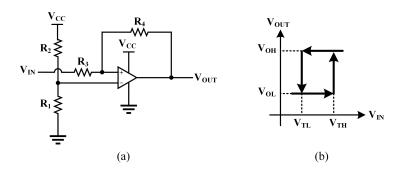

| 5.7        | Theory of operation for a single-supply comparator: (a) Schematic drawing of                                                                                                                | Ŭ <b>_</b> |

|            | a single-supply comparator configured with hysteresis. The signal, $V_{\rm IN}$ , is fed                                                                                                    |            |

|            | into the noninverting input. (b) Comparator input-output transfer characteristics                                                                                                           |            |

|            | (note that the reference voltage on the inverting input biases the circuit operation                                                                                                        |            |

|            | entirely within the first quadrant.)                                                                                                                                                        | 85         |

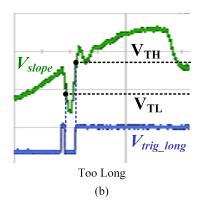

| 5.8        | Operating waveforms showing the output of the differentiator, $V_{\text{slope}}$ , and the output of the corresponding comparator, $V_{\text{trig}}$ for (a) too short of $t_a$ and (b) too |            |

|            | long of $t_{\rm b}$ . The low threshold, $V_{\rm TL}$ , and the high threshold, $V_{\rm TH}$ are annotated.                                                                                 | 86         |

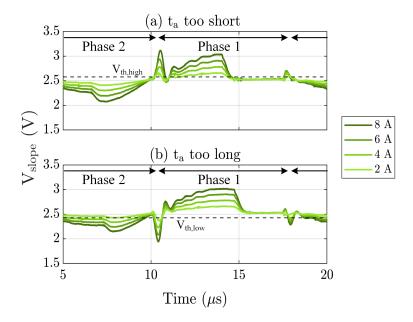

| 5.9        | Experimental $V_{\text{slope}}$ waveforms across several values of $I_{\text{load}}$ , for (a) "too short"                                                                                  |            |

|            | $t_a$ and (b) "too long" $t_a$ . At the Phase 2-to-Phase 1 transition, a short $t_a$ results                                                                                                |            |

|            | in an upwards pulse on $V_{\text{slope}}$ , while a long $t_a$ results in a downwards pulse. The                                                                                            |            |

|            | comparator trigger thresholds $V_{\rm th,high}$ and $V_{\rm th,low}$ are also plotted                                                                                                       | 87         |

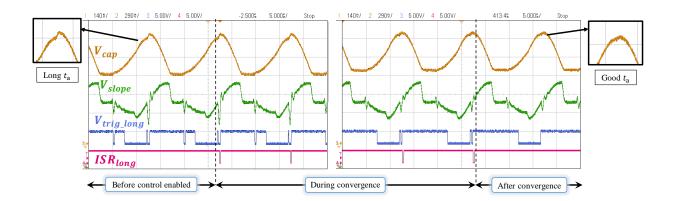

| 5.10       | Experimental waveforms for the converter operating at 48 V input, 6 V output,                                                                                                               |            |

|            | and 5 A load current. The converter is initialized with a split-phase time $t_a$ ,                                                                                                          |            |

|            | which is shorter than that required for soft-charging. After control is enabled,                                                                                                            |            |

|            | the converter converges on smooth capacitor voltage waveforms                                                                                                                               | 88         |

| 5.11       | Experimental waveforms for the converter operating at 48 V input, 6 V output,                                                                                                               |            |

|            | and 5 A load current. The converter is initialized with a split-phase time $t_a$ ,                                                                                                          |            |

|            | which is longer than that required for soft-charging. After control is enabled, the                                                                                                         |            |

|            | converter converges on smooth capacitor voltage waveforms                                                                                                                                   | 88         |

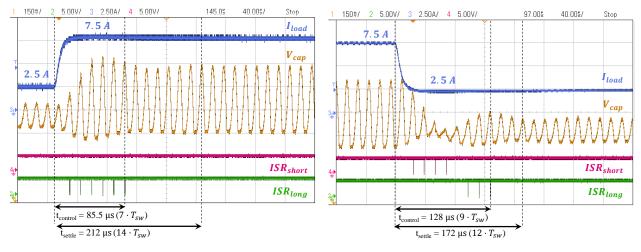

| 5.12       | System waveforms for both step-up and step-down load transients. For a load step of (a) 2.5 A to 7.5 A, the control takes 85.5 $\mu$ s to converge on soft-charged                                                                                                                         |     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | split-phase timing, and an overall total of 212 $\mu$ s (approximately 14 switching periods, $T_{\rm sw}$ ) to settle to its new steady state condition. For a load step of (b)                                                                                                            |     |

|            | 7.5 A to 2.5 A, the control takes 128 $\mu s$ to converge on soft-charged split-phase                                                                                                                                                                                                      |     |

|            | timing, and an overall total of 172 $\mu$ s (approximately 12 switching periods, $T_{\rm sw}$ )                                                                                                                                                                                            | 00  |

| 5 13       | to settle to its new steady state condition                                                                                                                                                                                                                                                | 89  |

| 0.10       | their control signals, where $\phi_1$ and $\phi_2$ are 50% duty cycle control signals, and $\phi_{1a}$                                                                                                                                                                                     |     |

|            | and $\phi_{2a}$ are the split-phase control signals                                                                                                                                                                                                                                        | 90  |

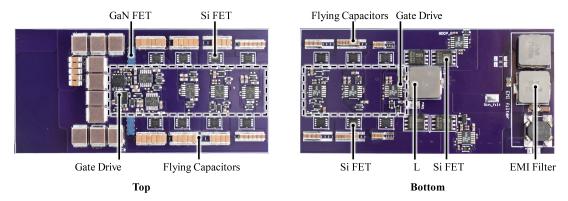

| 5.14       | Annotated photograph of the hardware prototype, showing the main power com-                                                                                                                                                                                                                |     |

| F 1F       | ponents as noted in [52]                                                                                                                                                                                                                                                                   | 91  |

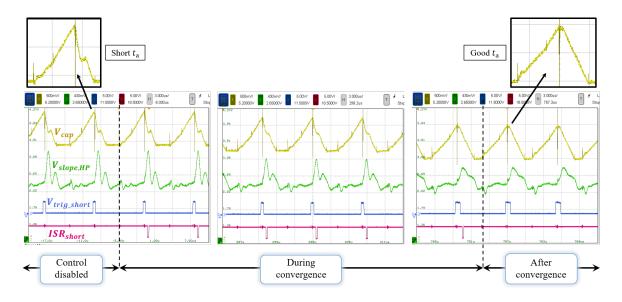

| 5.15       | Experimental waveforms for the HISID converter operating at 48 V input, 6 V output, and 10 A load current. The converter is initialized with a split-phase                                                                                                                                 |     |

|            | time $t_a$ which is too short. After control is enabled, the converter converges on                                                                                                                                                                                                        |     |

|            | smooth capacitor voltage waveforms. As the operating frequency is high above                                                                                                                                                                                                               |     |

|            | resonance, the capacitor waveforms are more triangular than sinusoidal                                                                                                                                                                                                                     | 92  |

| 5.16       | Capacitor voltage, $V_{\text{cap}}$ , and differentiator output, $V_{\text{slope}} = -dV_{\text{cap}}/dt$ , waveforms                                                                                                                                                                      |     |

|            | for the converter (a-b) operating near the resonant frequency (i.e. $f_{\text{sw}} = f_{\text{res}}$ ); and (c-d) operating high above resonance (i.e. $f_{\text{sw}} > f_{\text{res}}$ ). The effect on the $V_{\text{cap}}$                                                              |     |

|            | waveform is shown on the ability of the circuit to detect peaks on $V_{\text{slope}}$                                                                                                                                                                                                      | 93  |

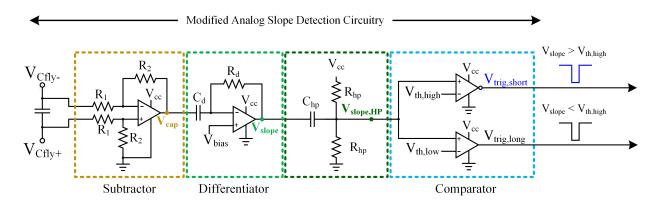

| 5.17       | Modified analog slope detect circuit, showing the high-pass filter placed between                                                                                                                                                                                                          |     |

|            | the differentiator and comparator stages                                                                                                                                                                                                                                                   | 95  |

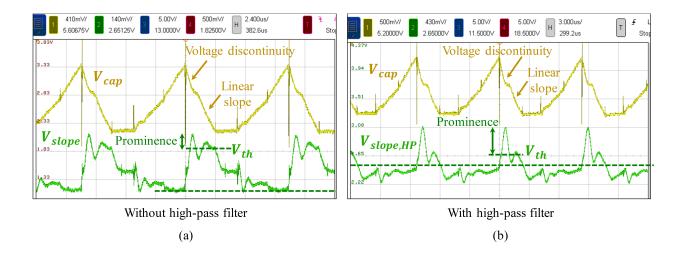

| 5.18       | $V_{\text{cap}}$ , $V_{\text{slope}}$ , and $V_{\text{slope,HP}}$ waveforms for the converter operating at $V_{\text{in}} = 48 \text{ V}$ , $V_{\text{out}} = 6 \text{ V}$ , $I_{\text{out}} = 10 \text{ A}$ , with too short of $t_{\text{a}}$ timing. The input signal to the comparator |     |

|            | is shown (a) without an additional high-pass filter (i.e. $V_{\text{slope}}$ directly), and (b)                                                                                                                                                                                            |     |

|            | with an additional high-pass filter (i.e. $V_{\text{slope,HP}}$ )                                                                                                                                                                                                                          | 95  |

| 6.1        | Charge flow in an $N:1$ Series-Parallel converter                                                                                                                                                                                                                                          | 100 |

| 6.2        | Two adjacent phases of the inductor current waveform, $i_L(t)$ , operating above                                                                                                                                                                                                           | 100 |

|            | resonance. Each phase constitutes a symmetrically centered sinusoidal segment                                                                                                                                                                                                              |     |

| <i>a</i> a | with angular frequency governed by (6.22)                                                                                                                                                                                                                                                  | 106 |

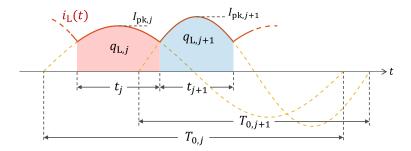

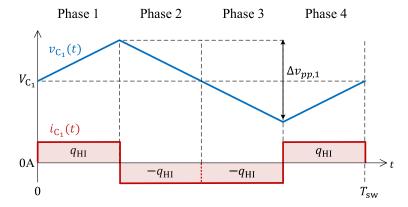

| 6.3        | Exemplar capacitor voltage and current waveforms for the given normalized charge flow vector $a_{C,1}$ in (6.37). The capacitor is charged by quantity $q_{HI}$ in                                                                                                                         |     |

|            | phases 1 and 4, and discharged by quantity $-q_{\rm HI}$ in Phases 2 and 3. For simplic-                                                                                                                                                                                                   |     |

|            | ity, constant capacitor current and linear capacitor voltage are shown                                                                                                                                                                                                                     | 109 |

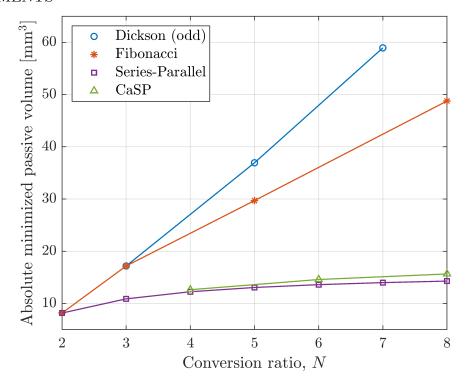

| 6.4        | Minimized passive volume for the Dickson (odd), Fibonacci, Cascaded Series-                                                                                                                                                                                                                |     |

|            | Parallel (CaSP), and Series-Parallel converters, at the operating conditions sum-                                                                                                                                                                                                          | 110 |

|            | marized in Table 6.2. The converters are assumed to be operated at resonance                                                                                                                                                                                                               | 116 |

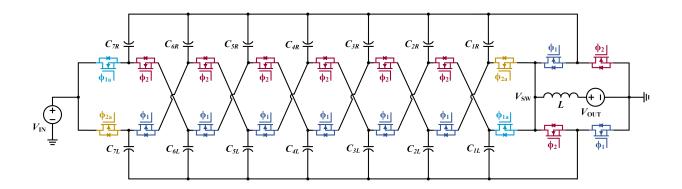

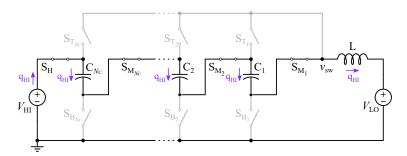

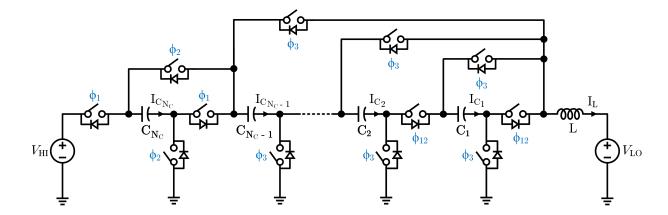

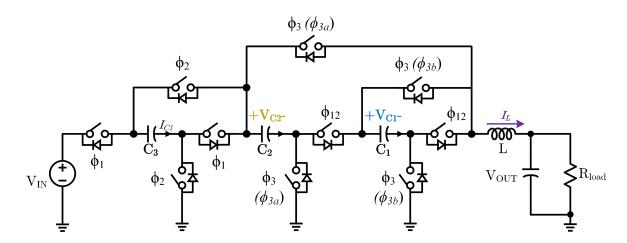

| 7.1  | Schematic drawing of a general $N$ -level Cascaded Series-Parallel (CaSP) converter, with switch control signals labeled. Here, $N_{\rm C}$ refers to the total number |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | of flying capacitors                                                                                                                                                   | 118 |

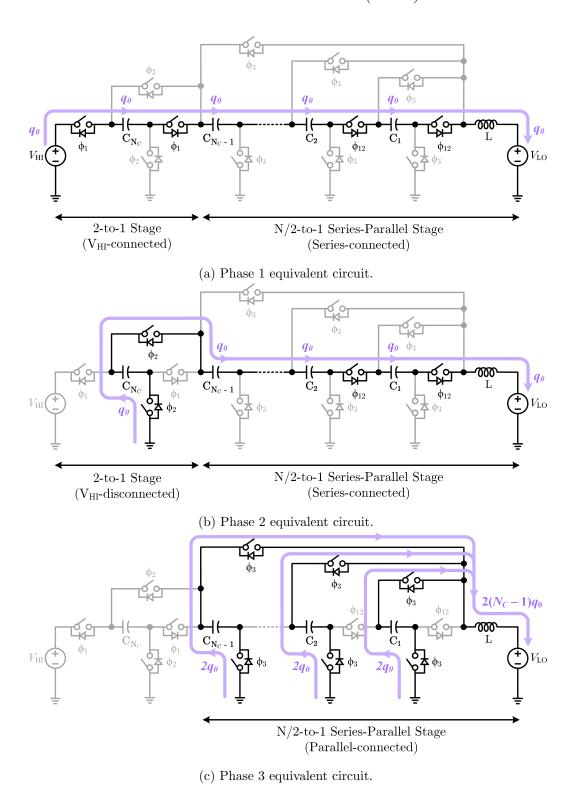

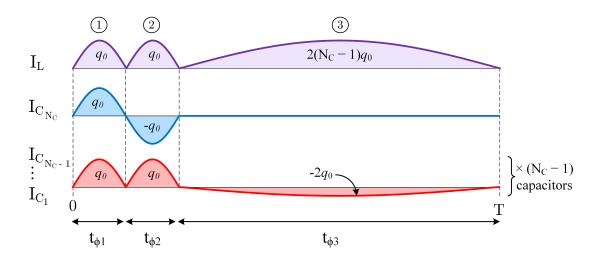

| 7.2  | Charge flow shown for the $N$ -level CaSP converter for each operating phase                                                                                           | 120 |

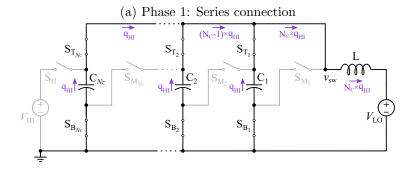

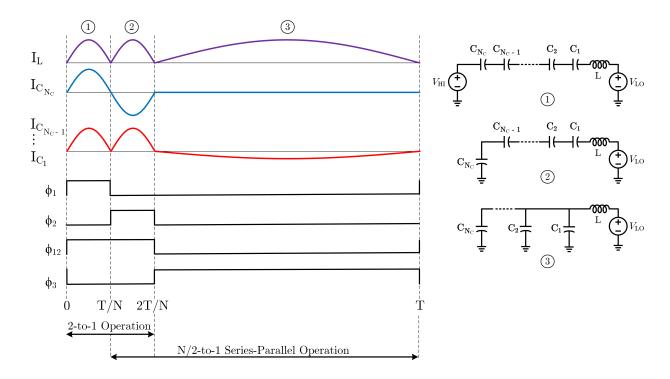

| 7.3  | Inductor and capacitor current waveforms for an N-level Cascaded Series-Parallel                                                                                       |     |

|      | (CaSP) converter                                                                                                                                                       | 124 |

| 7.4  | Inductor and capacitor current waveforms, along with corresponding charge de-                                                                                          |     |

|      | livered in each phase                                                                                                                                                  | 125 |

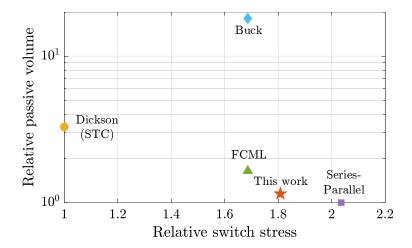

| 7.5  | Relative passive volume vs. normalized switch stress for several 6-to-1 converters,                                                                                    |     |

|      | using the method proposed in [42]                                                                                                                                      | 133 |

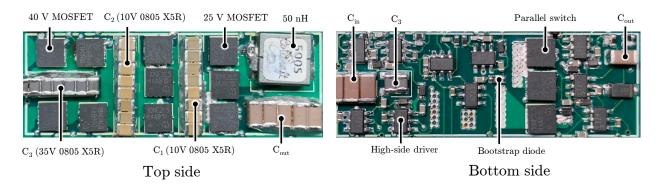

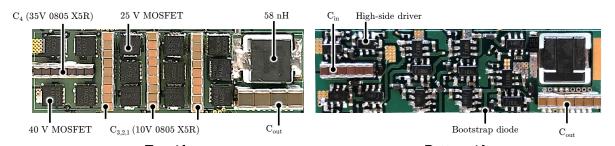

| 7.6  | Photograph of the 6-to-1 prototype converter. Dimensions: $1.38 \times 0.46 \times 0.22$                                                                               |     |

|      | inch $(3.5 \times 1.17 \times 0.56 \text{ cm})$                                                                                                                        | 136 |

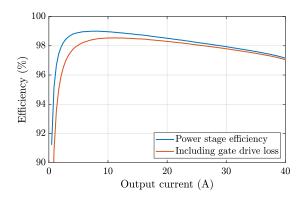

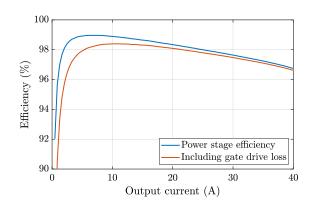

| 7.7  | Measured efficiency                                                                                                                                                    | 138 |

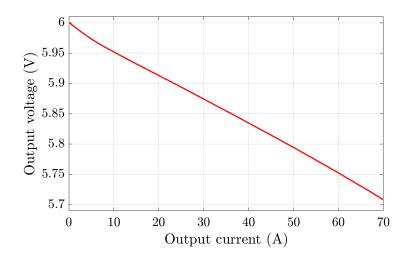

| 7.8  | Load regulation curve                                                                                                                                                  | 138 |

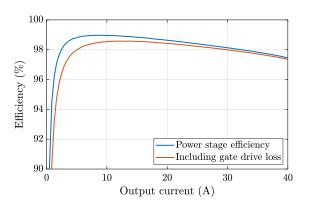

| 7.9  | Measured efficiency                                                                                                                                                    | 138 |

| 7.10 | Measured efficiency                                                                                                                                                    | 138 |

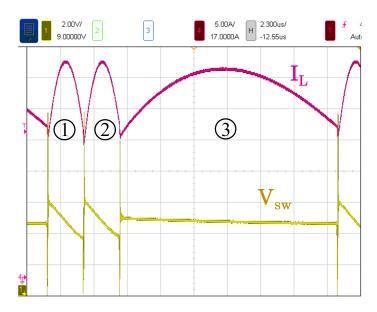

| 7.11 | Inductor current, switch node voltage, and Phase 1 $(\phi_1)$ gate signal waveforms                                                                                    |     |

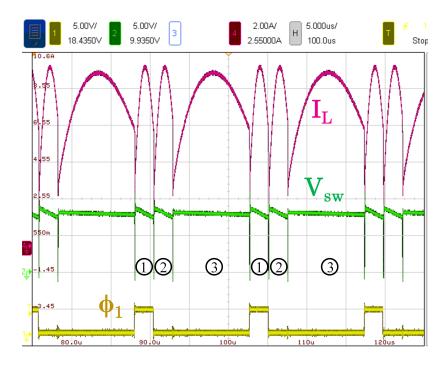

|      | for 48-to-8 V                                                                                                                                                          | 139 |

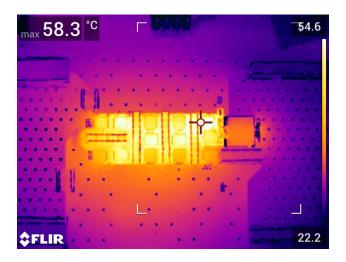

| 7.12 | Thermal image at full-load (40 A) for 48-to-8 V operation with fan cooling                                                                                             | 140 |

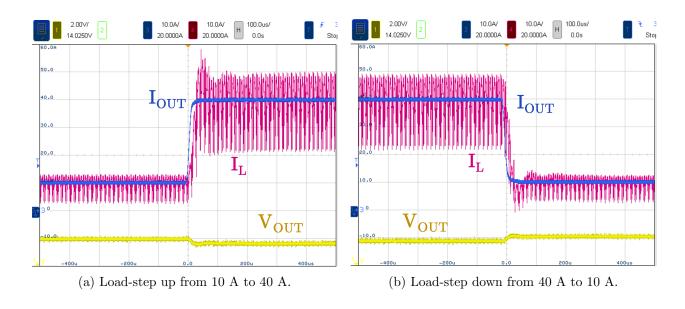

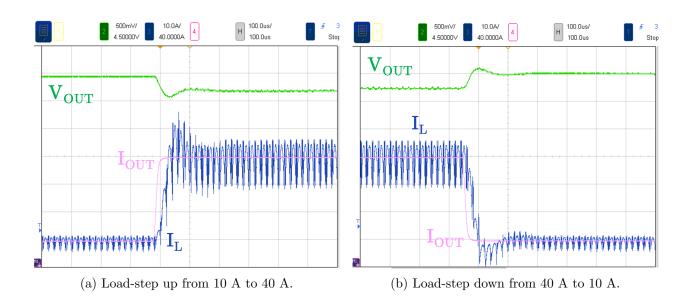

| 7.13 | Load transient response of the converter for a (a) step-up and (b) step-down                                                                                           |     |

|      | transition at 48 V to 8 V operation                                                                                                                                    | 140 |

| 7.14 | Photograph of the converter. Dimensions: $1.76 \times 0.51 \times 0.21$ inch $(4.47 \times 1.30)$                                                                      |     |

|      | $\times$ 0.53 cm)                                                                                                                                                      | 142 |

| 7.15 | Inductor current and switch node voltage for 48-to-6 V operation at 30 A                                                                                               | 144 |

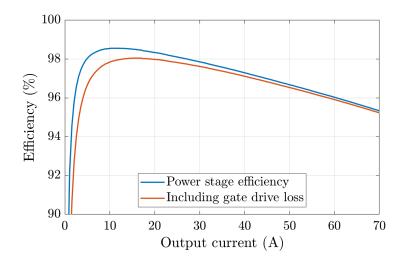

|      | Measured efficiency at 48 to 6 V, $f_{sw} = 50 \text{ kHz.} \dots \dots \dots \dots \dots$                                                                             | 144 |

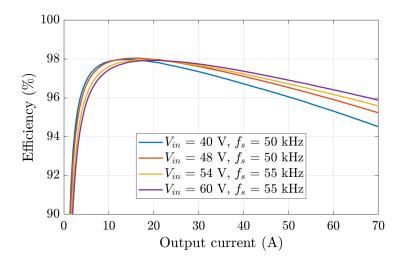

| 7.17 | Efficiency curves including gate drive loss for $V_{\rm in}=40~{\rm V}$ to $V_{\rm in}=60~{\rm V}$                                                                     | 145 |

|      | 48-to-6 V load regulation curve.                                                                                                                                       | 146 |

|      | Thermal image at 48 $V_{\rm in}$ and 70 A                                                                                                                              | 147 |

| 7.20 | Load transient response of the converter for a (a) step-up and (b) step-down                                                                                           |     |

|      | transition at 48 V to 6 V operation                                                                                                                                    | 147 |

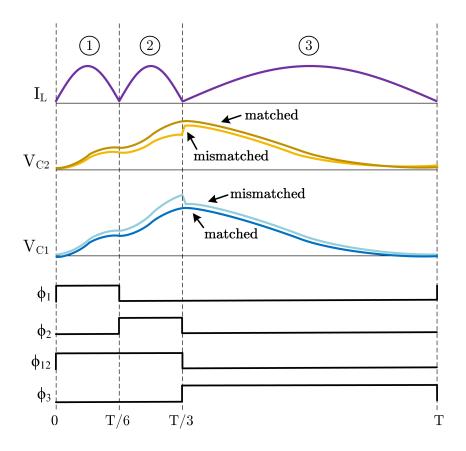

| 7.21 | 6-to-1 CaSP converter operated with and without split-phase signals. Gate signals                                                                                      |     |

|      | $\phi_1, \phi_2$ , and $\phi_{12}$ are the same as for normal operation described earlier in this                                                                      |     |

|      | chapter. The signals $\phi_{3a}$ and $\phi_{3b}$ are the modified "split-phase" gating scheme,                                                                         |     |

|      | used to handle component mismatch on the parallel capacitors                                                                                                           | 149 |

| 7.22 | Converter operating waveforms using the normal control sequence for the CaSP                                                                                           |     |

|      | 6-to-1 converter. Dark blue and gold waveforms are for the case where $C_1 = C_2$ .                                                                                    |     |

|      | Light blue and gold waveforms are for the case where $C_2 = 1.2 \times C_1$ . The mis-                                                                                 |     |

|      | matched capacitance leads to voltage step discontinuities on $C_1$ and $C_2$ , leading                                                                                 |     |

|      | to hard-charging.                                                                                                                                                      | 150 |

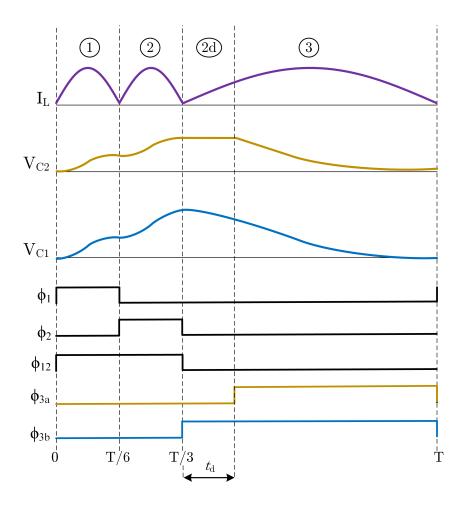

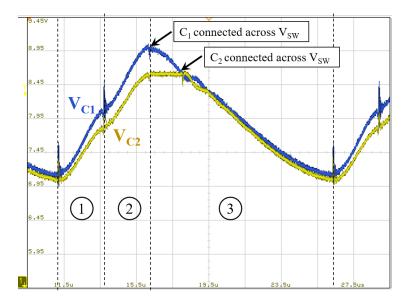

| 7.23 | Converter operating waveforms using the modified control sequence for the CaSP                     |     |

|------|----------------------------------------------------------------------------------------------------|-----|

|      | 6-to-1 converter. Here, the $\phi_{3a}$ and $\phi_{3b}$ gate signals are used to handle the capac- |     |

|      | itance mismatch of $C_2 = 1.2 \times C_1$ . The capacitor waveforms are now smooth and             |     |

|      | continuous, representing full soft-charging                                                        | 151 |

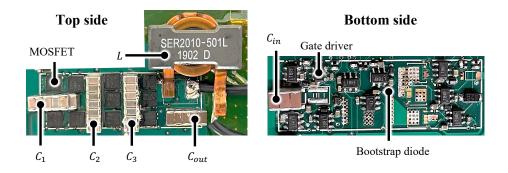

| 7.24 | 6-to-1 CaSP converter, populated with Class 1 capacitors to validate the control                   |     |

|      | technique on mismatched capacitance conditions                                                     | 152 |

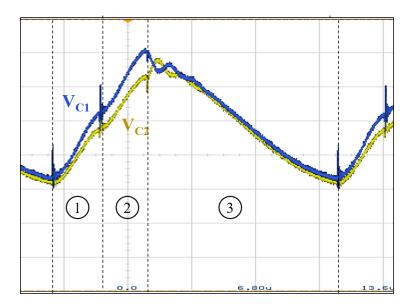

| 7.25 | Capacitor voltage waveforms for the parallel-connected capacitors $C_1$ and $C_2$ , us-            |     |

|      | ing the standard CaSP control waveforms shown Fig. 7.22. As these capacitances                     |     |

|      | are mismatched, there are hard-charging voltage discontinuities at the onset of                    |     |

|      | Phase 3                                                                                            | 153 |

| 7.26 | Capacitor voltage waveforms for the parallel-connected capacitors $C_1$ and $C_2$ ,                |     |

|      | using the modified split-phase CaSP control waveforms shown in Fig. 7.23. By                       |     |

|      | delaying the connection of $C_2$ to the switch-node, $V_{\rm SW}$ , smooth voltage transitions     |     |

|      | can be achieved (i.e. no hard-charging)                                                            | 154 |

## List of Tables

| 3.1  | ogy for small ripple and resonant operation, from [38]                          | 34  |

|------|---------------------------------------------------------------------------------|-----|

| 4.1  | Capacitor Voltages During Phase 1                                               | 41  |

| 4.2  | Branch Voltages During Phase 1                                                  | 43  |

| 4.3  | Split-Phase Charge Flow                                                         | 51  |

| 4.4  | Capacitor Voltages During Phase 1                                               | 52  |

| 4.5  | Capacitor Voltages for KVL Loops in Fig. 4.10 and Fig. 4.12                     | 54  |

| 4.6  | $V_{\rm ds,pk}$ for N = 6 DIH                                                   | 62  |

| 4.7  | Operating Parameters                                                            | 65  |

| 4.8  | Power Stage Components                                                          | 66  |

| 4.9  | Switch and Capacitor Voltages for $N=6$ DIH                                     | 68  |

| 5.1  | Power Stage and Control Components                                              | 83  |

| 5.2  | 8-to-1 Resonant Dickson Converter Operating Parameters                          | 84  |

| 5.3  | Component Listing of the 8-to-1 HISID Hardware Prototype                        | 91  |

| 5.4  | 8-to-1 HISID Converter Operating Parameters                                     | 92  |

| 6.1  | Definitions of Required Topological Vectors                                     | 99  |

| 6.2  | Operating Parameters for Passive Volume Comparison                              | 115 |

| 7.1  | General Parameters for the $N$ -Level CaSP                                      | 127 |

| 7.2  | Comparison of the number and voltage rating of components for 6-to-1 and 5-to-1 |     |

|      | resonant switched-capacitor converters                                          | 132 |

| 7.3  | Comparison of number and voltage rating of components for 8-to-1 resonant       |     |

|      | switched-capacitor converters                                                   | 134 |

| 7.4  | Main Power Stage Component Listing for 6-to-1 Prototype converter               | 137 |

| 7.5  | Converter Operating Conditions                                                  | 137 |

| 7.6  | Measured Converter Performance                                                  | 138 |

| 7.7  | Comparison of this work and existing high step-down ratio bus converters        | 141 |

| 7.8  | Main Power Stage Component Listing for 8-to-1 Prototype converter               | 143 |

| 7.9  | Converter Operating Conditions                                                  | 143 |

| 7.10 | Converter Efficiency Across $V_{in}$                                            | 145 |

| 7.11 | Comparison of this work and existing 8-to-1 converters                      | 148 |

|------|-----------------------------------------------------------------------------|-----|

|      | Main Power Components for Hardware Validation of Split-Phase Control on the |     |

|      | 6-to-1 CaSP Converter                                                       | 152 |

| 7.13 | Operation Conditions for Hardware Validation                                | 152 |

#### Acknowledgments

I would like to start by thanking Prof. Robert Pilawa-Podgurski. He has been an amazing advisor, and has fully welcomed all of us students into his family. Thank you for all your help throughout my PhD, both with my research questions and my life outside of lab. I have been able to work on a huge range of different things, not all of which panned out, because of your support and interest. The past six years have been incredibly rewarding and fun because of the research environment of the Pilawa group.

I also want to thank my Dissertation Committee: Prof. Jessica Boles, Prof. Kristofer Pister, and Prof. Hanh-Phuc Le. Your comments and questions throughout my qualifying presentation and dissertation talk have been incredibly helpful for shaping how I present my research.

I'd also like to thank Prof. Dave Perreault at MIT, for advising me as an undergraduate and Master's student. Thank you for introducing me to power electronics, and for paying for an undergrad to go to so many conferences! I am very appreciative of all the advice you gave me with job and grad school applications. My time in your group was incredibly rewarding and fun.

In addition, I'd like to thank Samantha Gunter, who mentored me during my time in Prof. Dave Perreault's group. Thank you so much for all the support you provided and everything you taught me about converter design. As I have become an older graduate student, it has only become more and more evident how amazing you were as a mentor, and I hope that I am half as good.

I would also like to thank Shirley Salanio. Thank you so much for your help with prelims, course questions, and everything in-between. The entire PhD experience was made better by your presence.

Thank you to everyone in the Pilawa group! You are all amazing people, who are not only brilliant, but kind and funny. Thank you to the older graduate students who all did such amazing research and set the bar very high: Enver Candan, Zichao Ye, Wen-Cheun (Joseph) Liu, Zitao Liao, Sophia Chou, Nate Pallo, and Pourya Assem. I'd especially like to thank Zichao Ye for introducing me to the data center application space, and for encouraging me to push converter performance as high as possible. The work you did with me at the beginning of my PhD has shaped my entire research focus, so thank you!

Thank you to everyone who has come through the Pilawa group in my time here: Ting Ge, Ivan Petric, Yong-Long (Max) Syu, Joseph Schaadt, Mads Graungaard Taul, Will Vavrik, Nicole Stokowski, Amanda Jackson, and Raya Mahony; and thank you to everyone currently here now: Rod Bayliss III, Elisa Krause, Logan Horowitz, Haifah Sambo, Tahmid Mahbub, Nathan Biesterfeld, Jiarui Zou, Ben Liao, Marrin Nerenberg, and Anya Shah. Huge thanks to Yicheng Zhu for being my partner in graduation, and for all the help with dissertation talk scheduling and thesis filing. It has been amazing to work with you in the data center space!

I'd also like to thank our hybrid switched-capacitor math "study group": Maggie Blackwell, Nathan Brooks, Sam Coday, and Nathan Ellis. I loved going through math and converter analysis with you, and am a stronger engineer for it. Thank you to Sam, for starting such a wonderful study group, and for convincing Robert to let us go to Fiji and present two tutorials.

I'd also like to thank Rahul Iyer, for all the time he has spent discussing converters, matrices, and life with me. Thank you for demystifying (parts of) linear algebra for me. Thank you to Nagesh Patle for your continual stream of amazing ideas, and for your creativity and enthusiasm. Thank you Haifah Sambo, for helping me test new things last minute for this thesis, and for continuing on the work building cool IBCs. Thank you Logan Horowitz, for putting up with me sitting next to your cube, and for figuring out something useful to do with all of Maggie's and my transformer data.

Also, thank you to Kelly Fernandez, Sam Coday, and Maggie Blackwell. It was incredibly helpful having you guys there going through PhD milestones with me. It made it much easier to navigate any red tape knowing that you three were also there with me.

I also want to thank some amazing friends I have made in the Pilawa group: Sam Coday, Maggie Blackwell, Sahana Krishnan, and Finn Giardine. You have supported me through major milestones in my life during my PhD. I want to thank Sam for being one of the best people to turn to for advice. I feel like you can solve any problem you ever encounter. Thank you so much for studying for prelims with me – I would not have gotten through them without you or our coffee breaks. Every conference is more fun when I can share a room or grab a drink with you there. I am so excited to see where your own research takes you!

Maggie, you are an incredibly impressive person, and I am so happy that I can call you a friend. I loved TA'ing power electronics with you, and designing labs together every week. I am so grateful that you sat next to me our entire PhD, so I could ask you about Youtube videos or Dickson converter charge flow. I already miss sharing a cubicle and whiteboard with you.

Sahana, you have been a fantastic research partner and a huge source of support. Thank you for all the late nights testing in lab or talking on the phone, and thank you for all your help in getting the results that are presented in this dissertation. The amount of papers and figures that you have reviewed for me could fill an olympic pool.

Finn, thank you for being my other desk partner, and for sometimes leaving me treats. I am so happy that you are my hiking buddy, and are always up for some adventure into the mountains. Please keep sending me updates on Alaskan bears coming out of hibernation, and thanks for appreciating all my memes and lame jokes. Thank you for being my sole source of info on the AC side of power electronics.

Finally, I want to thank my friends and family. Thank you to all my Solar Car friends (George, Alex, Dillon, Andrew) and the Boston yarn squad (Kelly, Julia, Evi, Michelle, Fabiola, Kathleen) even though half of you are no longer in Boston. Thanks for going out on ski trips and adventures with me throughout the past 10 years. I hope for decades more of your friendship!

Thank you to my family, who have supported me throughout my PhD. Thank you Rachel, Michael, and Isaac, for hosting me on trips up in Washington, and for always being up for

adventures. Thank you Molly, Gerald, Jake, Rory, and Billy, for all the dinners and relaxing weekends you've given me down in Santa Cruz. Thank you Mom and Dad, for everything you've done for me leading up to this point. My dissertation has quite a lot of math in it, and I have to say it probably has a lot to do with my mom being a math teacher and giving me "y=mx+b" puzzles to solve as a child, so thank you! Thank you Dad for all the cool science things you took me to throughout the years, and for our shared love of stargazing.

Thank you to my in-laws and second set of parents, Ba and Ma. You have been so supportive of my PhD, even though it moved us all the way across the country. Thank you for all the home-cooked dinners and goodies you've sent us back home with over the years.

Lastly, I'd like to my husband, Kai, for his overwhelming love and support. You drove across the country with me with a truck packed full of luggage, so that I could start this PhD. You have been my closest friend and partner for more than a decade, and am so happy to share our lives together. Thank you for waiting patiently for me to finish my PhD, and thank you for being part of the amazing future we have planned after. I am so grateful for your humor and adventurous spirit. And of course, thank you for your help answering questions about analog circuits and for letting me set up a field office at our house with your oscilloscope during COVID. Many of the pictures and data in this thesis were taken on that setup. I am so excited to see where life takes us next.

### Chapter 1

### Introduction

#### 1.1 Introduction

Hybrid switched-capacitor (SC) converters have seen increased use in applications that demand both high efficiency and high power density. These converters exhibit the traditional benefits of pure SC converters, such as efficient utilization of switches [1] and the use of energy-dense capacitors [2], along with lossless capacitor charge transfer due to the use of one or more augmenting inductors [3–6]. Hybrid SC topologies have become more popular in application spaces such as automotive drive-trains [7–11] and 48 V-bus data center power delivery [12, 13], including both single-stage and two-stage architectures.

For this latter application area, hybrid SC converters are especially well-suited for use as first-stage intermediate bus converters (IBCs). These IBCs step the 48 V bus down to some intermediate voltage, which is then stepped down to the low-voltages and high-currents seen at the point-of-load (PoL). By using a two-stage architecture, the first stage often does not need to satisfy stringent transient requirements or provide regulation, allowing for the use of dc transformer (DCX) topologies. In addition, as hybrid SC converters can achieve high step-down conversion without significant degradation to efficiency or power density, there is an opportunity to decrease the input voltage of the second-stage PoL converters from the more conventional 12 V bus to a lower (i.e. 4 to 8 V) voltage, to allow for increased PoL-stage efficiency [14–16]. There has been an increased interest in these higher step-down options for the first-stage IBCs, as can be seen by the following surveys analyzing performance trends across industry and academic intermediate bus converters.

Fig. 1.1 shows the power density in W/in<sup>3</sup> plotted against year-of-release for a variety of industry and academic offerings. As expected, there is a large amount of 4-to-1 IBC options overall (both regulated and unregulated), as these are used to provide the 12 V bus commonly used in two-stage data center power delivery designs. However, in the past five or so years, several higher step-down options have been released, initially primarily from academia. The 8-to-1 multi-resonant doubler (MRD) converter [17], and the 6-to-1 and 8-to-1 variants of the cascaded series-parallel converter (CaSP) [18,19] were some of the earlier

offerings in these higher conversion-ratios, and achieved state-of-the-art performance at the time of publishing. The CaSP hardware prototypes shown here will also be explored in more detail in Chapter 7. Another trend that can be seen from this survey is the increase in power density over time. This has been primarily driven by an increase in output current capability for many of these IBC implementations.

Fig. 1.2 shows the power density (W/in<sup>3</sup>) and peak efficiency (%) for the same grouping of industry and academic IBCs. As expected, unregulated 4-to-1 step-down converters have some of the best combined power densities and efficiencies, due to their lower conversion-ratios and the fact that they do not need to size their inductors for regulation. However, many 6-to-1 and 8-to-1 implementations (including the CaSP prototypes discussed in this thesis) can still obtain high performance.

In addition, it is important to note that while data center power delivery is a very well-suited use-case of hybrid SC converters in general, the analysis and design techniques detailed in this work have direct application to any high-performance, high-conversion ratio application.

Figure 1.1: Power density versus year-of-release, for a survey of 48 V / 54 V intermediate bus converters for data center applications. Converters are categorized by conversion ratio, regulation capability, and whether the work is academic or commercial.

Figure 1.2: Power density versus peak efficiency, for a survey of  $48~\rm V$  /  $54~\rm V$  intermediate bus converters for data center applications. Converters are categorized by conversion ratio, regulation capability, and whether the work is academic or commercial.

### 1.2 Organization of Thesis

Throughout this work, we will we explore general hybrid SC design and analysis methods, as well as operating techniques (such as split-phase switching and multi-resonant operation) that can be used to achieve higher performance than would be obtained using conventional two-phase operation. This thesis is organized as follows.

#### Chapter 2: Soft-Charging of Hybrid Switched-Capacitor Converters

This chapter presents an overview of the concept of soft-charging, in which the capacitor charge and discharge losses inherently present in pure switched-capacitor converters can be mitigated by the use of an inductive or controlled-current load. Fundamental analysis techniques to determine the soft-charging capability of different switched-capacitor topologies are also presented, including new extensions to topologies with multiple inductors and multiple operating phases.

#### Chapter 3: Split-Phase Switching Overview

The Dickson converter is a popular hybrid SC topology that can achieve very good switch stress performance. However, many variants cannot achieve soft-charging without modifications to the standard two-phase operation. Split-phase switching is a technique used to softly charge the flying capacitors, wherein additional operating phases are introduced which charge and discharge the flying capacitors in a staggered manner. Here, we illustrate the inherent reason for the hard-charging present in these types of converters, as well as the mechanism by which split-phase switching mitigates these capacitor charge and discharge losses.

#### Chapter 4: Effects of Split-Phase Sub-Phase Ordering

The exact implementation of split-phase control can be nuanced, depending on the specific ordering of these introduced sub-phases. This chapter details the effects of different split-phase ordering patterns on split-phase switch blocking voltage, overall switch stress, and sub-phase timings. General trends and rules of thumb are also provided for both step-up and step-down Dickson-variant converter topologies.

## Chapter 5: Active Splitphase Control Using Capacitor Voltage Discontinuity Detection

Due to the complex interaction of converter dynamics, parasitics, and component tolerances in a real hardware implementation, calculating precise split-phase timings can be nontrivial. This chapter therefore presents an active tuning method to automatically detect the presence of hard-charging events, which indicate incorrect split-phase timings for the given operating condition. The control then increases or decreases these split-phase timings in such a way as to restore the converter back to a soft-charging state. The technique as presented is general in nature, and can be applied to a variety of Dickson-derived topologies, switching both at and above the natural resonant frequency of the converter. In addition, the technique can be used to detect component tolerance mismatch in non-Dickson converter topologies, as will be explored more in Chapter 7.

#### Chapter 6: Passive Volume Analysis Using Peak Energy Storage Requirements

The volume of the passives in a hybrid SC converter can represent a large fraction of the overall converter volume. Therefore, in order to increase power density and minimize footprint, it can be desirable to shrink the passive volume as much as possible. This chapter details an analytical framework for comparing multiple hybrid SC topologies on the basis of peak energy storage for each passive component. This peak energy storage requirement is then converted into a passive volume, using empirical trends for capacitor and inductor energy densities. This chapter also presents a new extension to the analysis technique, which allows

for the inclusion of multi-resonant hybrid SC topologies such as the multi-resonant-doubler (MRD) and cascaded series-parallel (CaSP) converters.

#### Chapter 7: The Cascaded Series-Parallel (CaSP) Converter

The cascaded series-parallel (CaSP) converter is a multi-resonant hybrid SC topology that can achieve the same conversion ratio as conventional two-phase hybrid SC converters with a significantly reduced component count. This can lead to greatly improved power density and efficiency. This chapter presents the general theory of operation for the CaSP converter, as well as an example application of the soft-charging analysis presented in Chapter 2 and the passive volume analysis presented in Chapter 6. Two high-performance hardware prototypes designed for data center applications are also presented, which are capable of 6-to-1 and 8-to-1 step-down conversion, respectively. Finally, a "split-phase" control scheme for handling capacitance mismatch in the CaSP converter is introduced and validated in hardware.

#### Chapter 8: Conclusion

This chapter concludes the thesis, and presents possible extensions to split-phase and multiresonant operation of hybrid SC capacitor converters. This chapter also summarizes the overall contributions of this work.

## Chapter 2

## Soft-Charging of Hybrid Switched-Capacitor Converters

#### 2.1 Introduction

While pure switched-capacitor (SC) converters can achieve high power density due to their use of energy dense capacitors [2, 20], their performance has been limited in higher power applications due to the inherent capacitor charge sharing losses. Pure SC converters can experience large transient currents spikes when they switch from one circuit state to another during the switching cycle, termed "hard-charging". These current spikes result from pulsed charge redistribution as the capacitors are disconnected from one network and reconnected into another, and can lead to increased losses, increased device stress, and worsened electromagnetic interference (EMI) performance. Reducing these effects in pure switched-capacitor converters requires either increasing the switching frequency or increasing the capacitance – both of which reduce the voltage ripple on the capacitors. However, the first modification can result in increased switching losses, while the later can result in reduced power density. Fig. 2.1 shows an example 2-to-1 SC converter, which would see large transient inrush current in the capacitor,  $C_1$ .

The undesirable effects of hard-charging can be mitigated by adding an inductor or controlled current load in the charge and discharge path of the capacitors (illustrated in Fig. 2.2a and Fig. 2.2b, respectively), as first demonstrated in [3]. In doing so, the capacitors will experience resonant or constant currents, rather than the large transient spikes that lead to hard-charging losses. The converter can therefore "soft-charge" its flying capacitors. The addition of this inductor or current load is referred to as "hybridizing" a SC converter, and the resulting topology is termed a hybrid switched-capacitor (SC) converter.

However, the placement of these inductive elements can require significant analysis to ensure that their addition results in the full soft-charging of all flying capacitors. Furthermore, many topologies require specific ratios of capacitances to ensure that there are no capacitor voltage mismatches when the converter transitions from one operating phase configuration

Figure 2.1: Example pure SC converter, showing a 2-to-1 conversion ratio.

Figure 2.2: Example hybridized SC converter, showing a 2-to-1 conversion ratio. (a) shows hybridization with a controlled-current source load, and (b) shows hybridization with an inductor.

to another. Both of these considerations must be taken into account when analyzing how a pure SC converter can be successfully hybridized. The following sections will detail prior analysis techniques that can be used for this purpose, as well as present new extensions to this method designed to handle a broader range of hybrid SC topologies.

### 2.1.1 Output Impedance

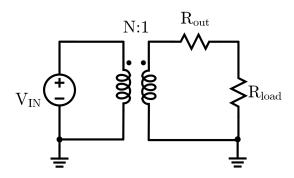

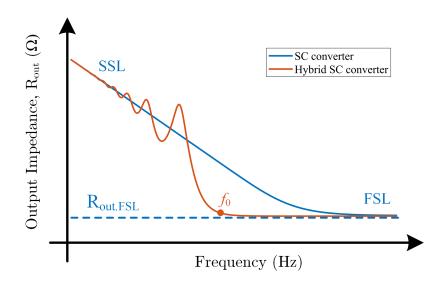

Throughout this and other chapters, we will refer to the output impedance of a hybrid SC converter as a proxy for loss or efficiency performance. Here, we briefly introduce how this impedance is characterized. Both pure SC and hybrid SC converters can be modeled using the circuit shown in Fig. 2.3. The N:1 transformer models the fixed-ratio N:1 conversion of a general SC converter, while the output impedance,  $R_{\rm out}$ , models the loss in the converter. The output impedance curves for both a pure SC converter and a hybrid SC converter are shown in Fig. 2.4. General equations for these curves can be found in [6]. The slow-switching limit (SSL)—where losses are dominated by capacitor charing sharing losses—and the fast-switching limit (FSL)—where losses are dominated by parasitics in the circuit such as switch

ON-state resistance, capacitor ESR, or inductor DCR—are also labeled, as described by [1]. The hybrid SC converter is able to achieve the FSL output impedance at a much lower frequency than the pure SC converter, near the hybrid SC converter's resonant frequency.

Figure 2.3: Switch-capacitor converter model, using an N:1 transformer to model the N:1 fixed-ratio conversion, and some output impedance,  $R_{\text{out}}$ , to model loss.

Figure 2.4: Output impedance,  $R_{\text{out}}$ , versus frequency for a pure SC converter and a hybrid SC converter.

### 2.2 Analyzing Arbitrary Switched-Capacitor Topologies for Soft-Charging Capability