# Circuit Design for Scalable and Fast Optical Circuit Switching

Erik Anderson

## Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2024-213 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2024/EECS-2024-213.html

December 14, 2024

Copyright © 2024, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Circuit Design for Scalable and Fast Optical Circuit Switching

By

Erik Francis Anderson

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Vladimir Stojanović, Co-chair Professor Ming C. Wu, Co-chair Professor Martin White

Fall 2024

Circuit Design for Scalable and Fast Optical Circuit Switching

Copyright 2024 by Erik Francis Anderson

#### Abstract

#### Circuit Design for Scalable and Fast Optical Circuit Switching

by

Erik Francis Anderson

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor Vladimir Stojanović, Co-chair

Professor Ming C. Wu, Co-chair

Data centers and large-scale distributed computers have become limited by the latency, throughput, and inflexibility of traditional electronic packet switches (EPSs). As evidenced by the recent introduction of optical circuit switches (OCSs) into Google's datacenters and TPU clusters, OCSs provide a way to circumvent many of the limitations of EPS networks. Silicon-Photonic (SiPh) MEMS-based OCSs have been shown to offer a scalable and low-latency approach compared to other integrated and non-integrated OCSs. Yet to be realized, however, is the electrical control and digital interface required for integrating high-radix MEMS SiPh chips into an application environment. This work demonstrates two novel approaches to controlling SiPh MEMS OCSs in both a scalable and efficient manner.

To my parents.

# Contents

| Co | onter                                         | nts                                                                                                                                                                                                       | ii                  |

|----|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Li | st of                                         | Figures                                                                                                                                                                                                   | iii                 |

| Li | st of                                         | Tables                                                                                                                                                                                                    | $\mathbf{iv}$       |

| 1  | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4       | coduction to Optical Circuit Switching         Circuit vs. Packet Switching         Current Applications         Future Applications         OCS Technologies                                             | 23                  |

| 2  | Sup<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | DerSwitch 1: A Digital Approach         Problem Statement         CMOS Design & Simulation         3D SiPh-CMOS Packaging         PCB Design         Electro-optic Characterization Setup         Results | 9<br>21<br>23<br>24 |

| 3  | Sup<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5        | <b>DerSwitch 2: An Analog Alternative</b> Problem Statement                                                                                                                                               | $37 \\ 52 \\ 53$    |

| 4  | Con<br>4.1<br>4.2<br>4.3                      | nclusionFinal Results                                                                                                                                                                                     | 62                  |

# List of Figures

| 1.1  | (a) Optically-connected 4x4 electronic packet switch (EPS). (b) All-optical 4x4 optical circuit switch (OCS)                                                                                                   | 2  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | (a) Initial uniform ring topology. (b) Traffic matrix extracted from a specific application showing the relative amount of transmitted data. (c) New ring topology optimized for the extracted traffic matrix. | 3  |

| 2.1  | (a) Schematic of (a) OFF state and (b) ON state of vertical MEMS coupler -                                                                                                                                     |    |

|      | figures taken from $[14]$ (c) SEM of MEMS switch cell - figure taken from $[22]$ .                                                                                                                             | 7  |

| 2.2  | A representative transfer function of a MEMS switch element                                                                                                                                                    | 8  |

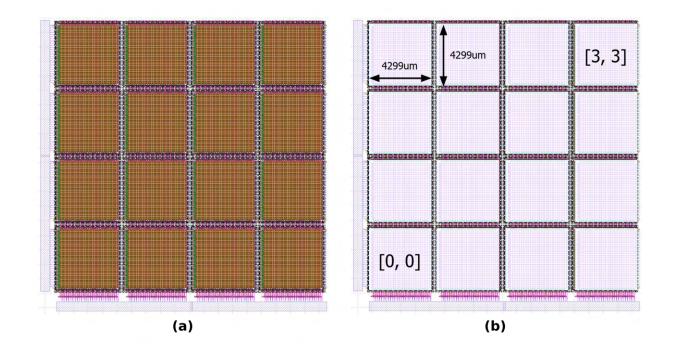

| 2.3  | GDS screenshots of (a) $128x128$ SiPh MEMS crossbar switch (b) $4x4$ CMOS high                                                                                                                                 |    |

|      | voltage driver chiplets flip-chip bonded to SiPh MEMS chip                                                                                                                                                     | 9  |

| 2.4  | (a) Micrograph of SuperSwitch 1 high voltage driver chiplet (b) Cartoon floorplan                                                                                                                              |    |

|      | of driver chiplet.                                                                                                                                                                                             | 10 |

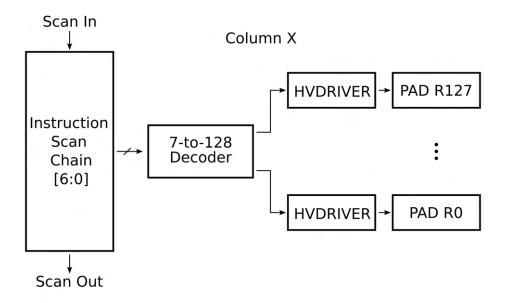

| 2.5  | Simple schematic for activating 1 of 128 rows assuming a single CMOS chiplet                                                                                                                                   | 11 |

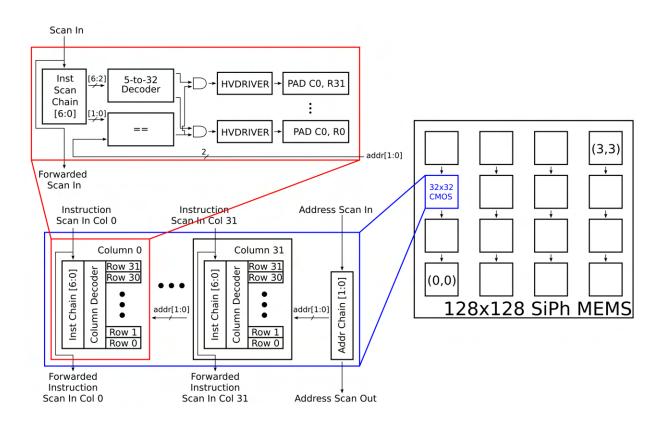

| 2.6  | Schematic for controlling a 128x128 switch assuming a 4x4 array of CMOS chiplets.                                                                                                                              | 12 |

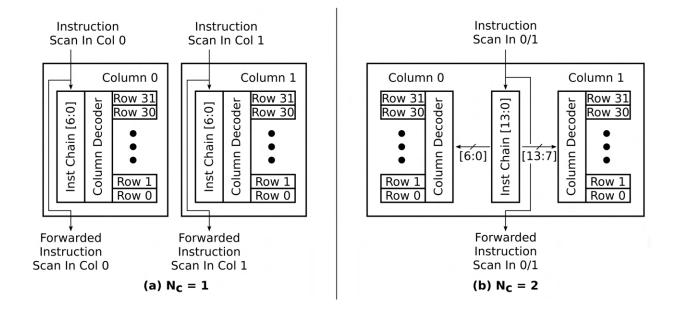

| 2.7  | (a) Logic for columns 0 and 1 for $N_c = 1$ (b) Logic for columns 0 and 1 for $N_c = 2$ .                                                                                                                      | 13 |

| 2.8  | (a) Final schematic of SuperSwitch1 control chiplet scan architecture w/ loopback                                                                                                                              |    |

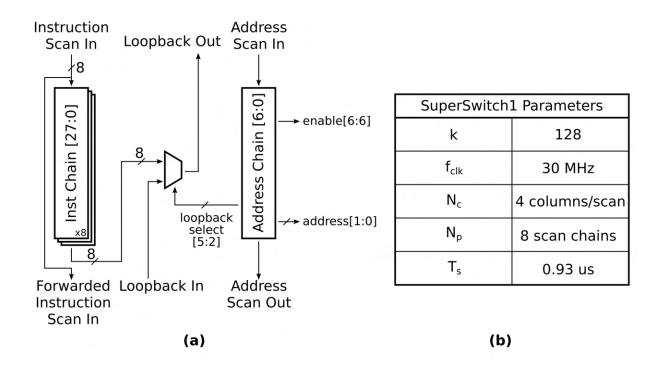

|      | mux for debug. (b) Final parameters for SuperSwitch1 controller chiplet                                                                                                                                        | 14 |

| 2.9  | (a) Schematic of SuperSwitch1 high voltage driver circuit. (b) List of all supplies                                                                                                                            |    |

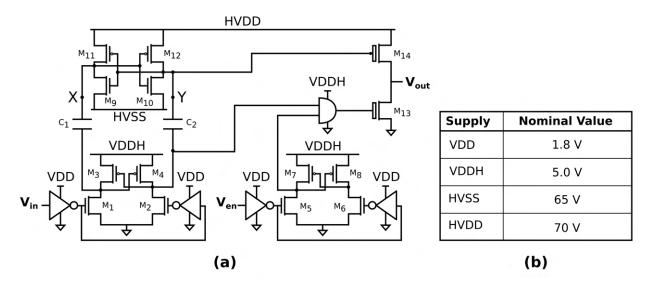

|      | and their nominal values                                                                                                                                                                                       | 15 |

| 2.10 | 1 1 1                                                                                                                                                                                                          | 17 |

| 2.11 |                                                                                                                                                                                                                | 18 |

| 2.12 | Equivalent circuit of supply and ground connection for a single chiplet column in                                                                                                                              |    |

|      | the flip-chip bonded CMOS-SiPh package.                                                                                                                                                                        | 19 |

| 2.13 | I /                                                                                                                                                                                                            |    |

|      | (b) Same plot but for $HVDD = 70 V$ , $HVSS = 66 V$                                                                                                                                                            | 20 |

|      | Rise (a) and fall (b) times extracted from post-layout simulations                                                                                                                                             | 20 |

| 2.15 | (a) Transient simulation of capacitance of MEMS model $(C_{MEMS})$ and output                                                                                                                                  |    |

|      | driver voltage $(V_{OUT})$ . (b) Parasitic output capacitance for all 1024 drivers (due                                                                                                                        |    |

|      | to short routes and pads).                                                                                                                                                                                     | 21 |

| 2.16 |                                                                                                                                                                                                                |    |

|      | micro-bumps. (c) Illustration of bonding process using differing thicknesses of                                                                                                                                |    |

|      | UBM on SiPh chip to compensate for CMOS pad height differences                                                                                                                                                 | 22 |

| 2.17      | (a) 4x4 CMOS flip-chip bonded to electrical interposer. (b) 1 CMOS flip-chip bonded to 32x32 subsection of 128x128 OCS                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.18      | (a) The chip board for wirebonding chips to. (b) The host board PCB used for                                                                                       |

|           | testing chip boards. $\ldots \ldots 24$                                               |

| 2.19      | Simplified diagram of the PC-to-chip interface with UART-controlled scan chain controllers                                                                         |

| 2.20      | Illustration of the SuperSwitch1 characterization test setup                                                                                                       |

| 2.21      | The physical test setup for fully automated switch characterization                                                                                                |

| 2.22      | (a) Location of switch cell being tested. (b) Captured scope waveforms used for                                                                                    |

|           | extracting rise and fall times. (c) Rise and fall times. vs applied voltage. (d)<br>Optical transfer curve                                                         |

| 2.23      | Measured on-chip loss (a/d), rise time (b/e), and fall time (c/e) for all $32^2 = 1024$ switch elements. Measurements were done at an HVDD of 60V and a wavelength |

|           | $\lambda = 1310 \text{nm}.  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                       |

| 2.24      | (a) Example 4x4 OCS w/ one driver "ON" per row/column. (b) Worst case                                                                                              |

|           | functional pattern for power measurements                                                                                                                          |

| 2.25      | (a) Measured worst case power for 32x32 OCS w/ HVDD=60V. (b) Power break-                                                                                          |

|           | down by supply for maximum reconfiguration frequency of $\approx 1.7$ MHz 30                                                                                       |

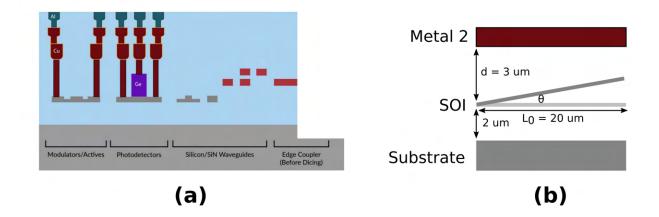

| 3.1       | <ul><li>(a) Cross section of AIM Photonics base active PIC process - figure taken from</li><li>[31]. (b) Simplified model of MEMS cantilever switch</li></ul>      |

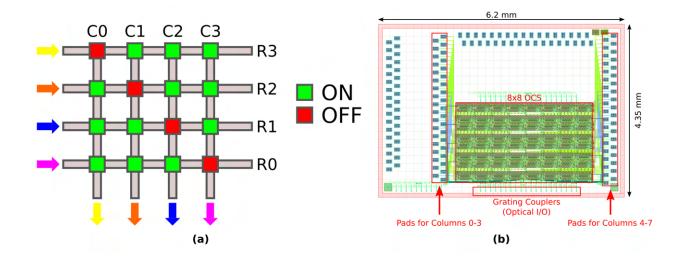

| 3.2       | (a) Cartoon of example 4x4 crossbar switch. "On" refers to a high voltage being applied. (b) Screenshot of GDS for SuperSwitch 2 silicon photonic MEMS 8x8         |

|           | OCS                                                                                                                                                                |

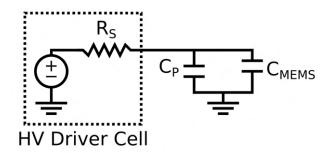

| 3.3       | Circuit model for high voltage driver and MEMS device                                                                                                              |

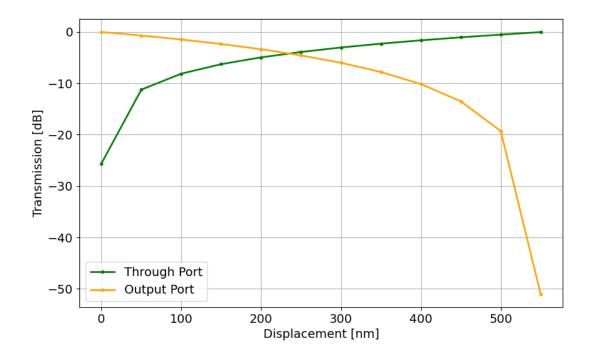

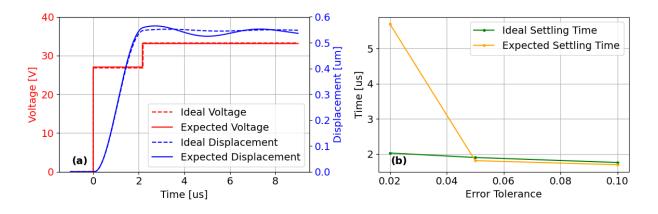

| 3.4<br>25 | Optical transmission vs. displacement for a single MEMS switch element 35<br>(a) Step regrange for 550 nm displacement (b) Dual step regrange for 550 nm           |

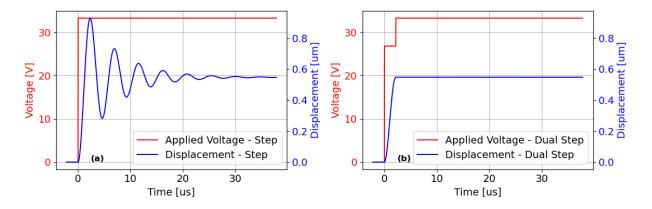

| 3.5       | (a) Step response for 550 nm displacement (b) Dual step response for 550 nm displacement                                                                           |

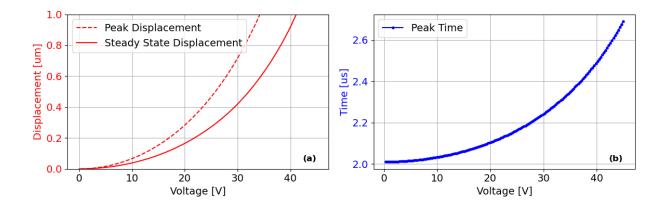

| 3.6       | (a) Step response peak displacement and time vs. applied voltage (b) Step re-                                                                                      |

| 0.0       | sponse steady state displacement vs. time                                                                                                                          |

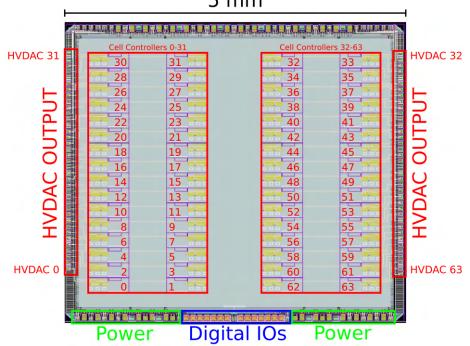

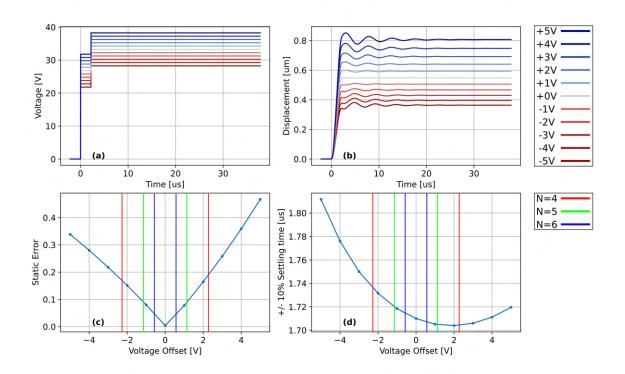

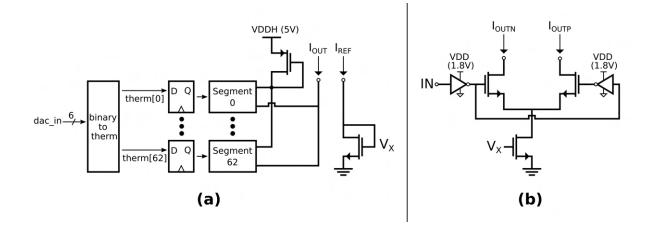

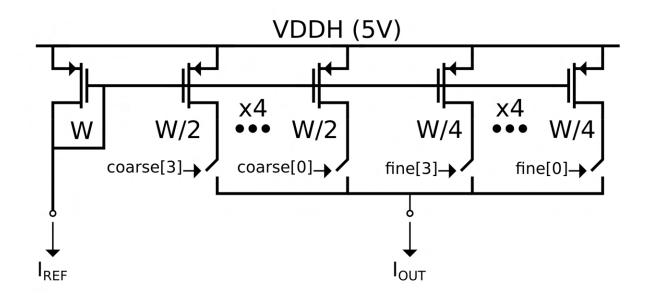

| 3.7       | SuperSwitch 2 - high voltage DAC array for analog MEMS control                                                                                                     |

| 3.8       | (a) Dual step waveforms w/ voltage offset (b) Cantilever displacement w/ voltage                                                                                   |

|           | offset (c) Static error (d) Settling time for $+/-10\%$                                                                                                            |

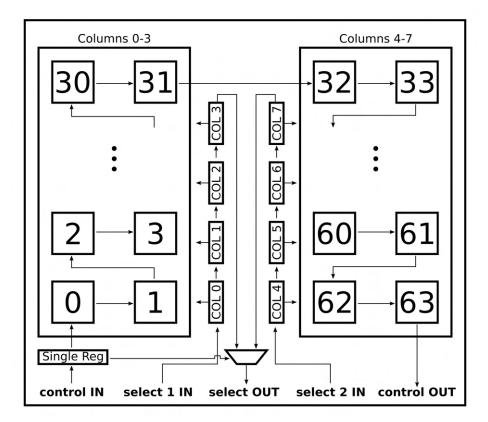

| 3.9       | Simplified chip-level digital architecture showing control and select scan chains . 40                                                                             |

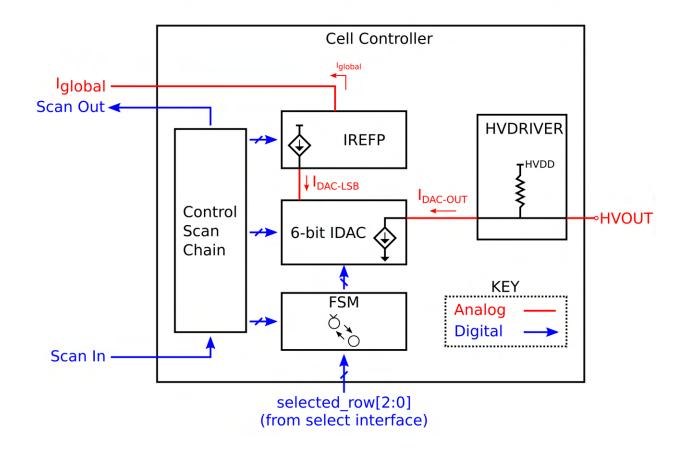

| 3.10      | i                                                                                                                                                                  |

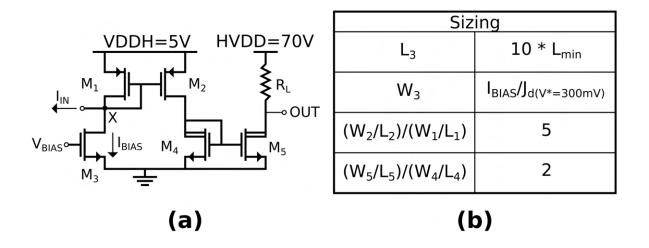

| 3.11      | (a) Schematic of high voltage driver cell - $M_4$ and $M_5$ are high voltage transistors.                                                                          |

|           | (b) Sizing guide for driver given a particular $I_{BIAS}$                                                                                                          |

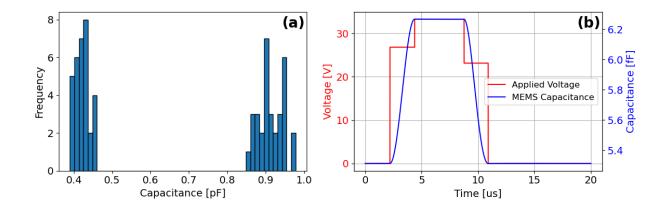

| 3.12      | (a) Histogram of parasitic output cap from all 64 HV DAC outputs to their                                                                                          |

| 0 10      | corresponding pads. (b) Capacitance of MEMS device as voltage is stepped $45$                                                                                      |

| 3.13      |                                                                                                                                                                    |

| 211       | current-steering DAC segment.       47         Schematic for current reference to set LSB current of current-steering DAC.       48                                |

| J.14      | schematic for current reference to set LSD current of current-steering DAC 48                                                                                      |

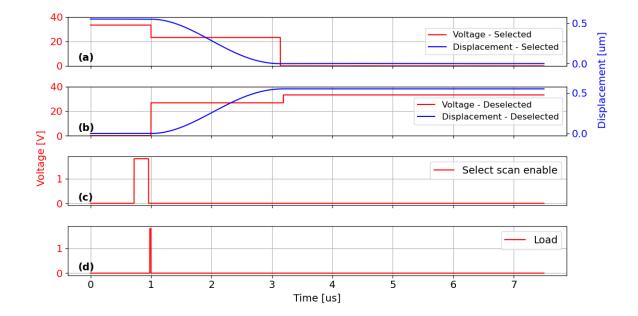

| 3.15 | Selected and deselected waveforms. The select scan enable signal is shown as         |    |

|------|--------------------------------------------------------------------------------------|----|

|      | well as the load signal that will trigger each cell controller's FSM to either start |    |

|      | cycling through the programmed selected or deselected waveform                       | 49 |

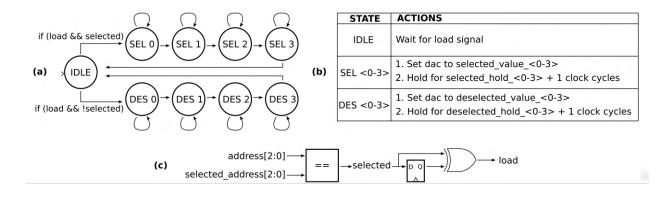

| 3.16 | (a) Simplified FSM diagram for stepping through selected and deselected wave-        |    |

|      | forms. (b) Description of FSM state actions. (c) Logic to generate the load signal   |    |

|      | that triggers the FSM                                                                | 51 |

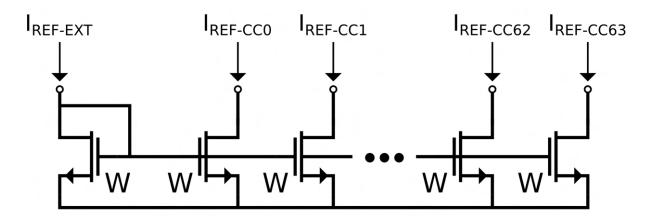

| 3.17 | Global current distribution circuit.                                                 | 51 |

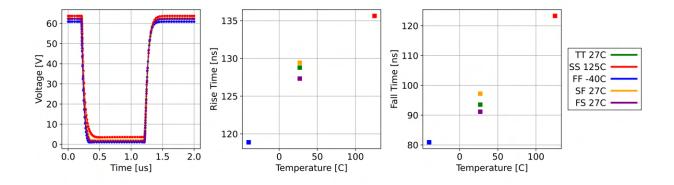

| 3.18 | (a) Output voltage of HV DAC going from minimum to maximum code driving              |    |

|      | a 1pF load. (b) Extracted rise times. (c) Extracted fall times                       | 52 |

| 3.19 | Wirebond diagram for SuperSwitch 2 using a 3-chip package for controlling the        |    |

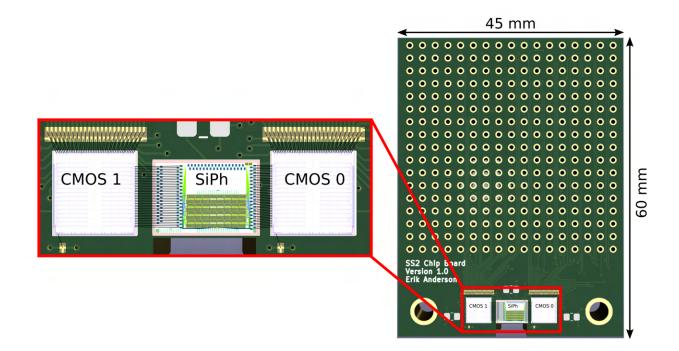

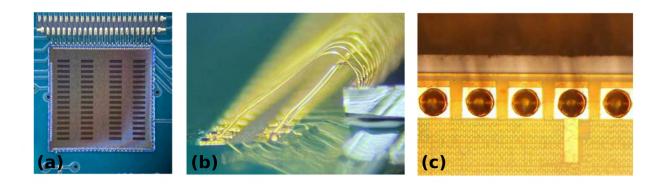

|      | 8x8 OCS                                                                              | 53 |

| 3.20 | CMOS only test package with (a) CMOS 1, the west side control chip from Fig.         |    |

|      | 3.19, (b) side-view of wirebonds, and (c) top-view of wirebonds                      | 53 |

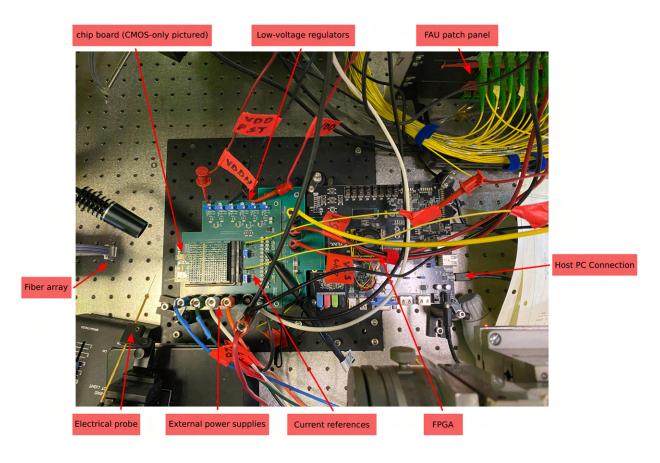

|      | The test setup for SuperSwitch 2                                                     | 54 |

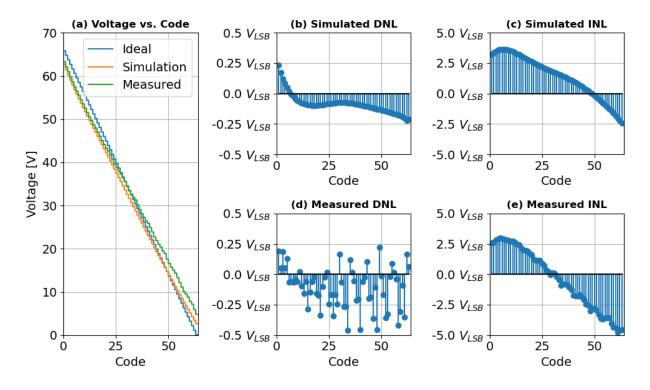

| 3.22 | Simulated and measured DNL and INL                                                   | 55 |

| 3.23 | (a) Ideal voltage vs. measured DAC voltages. (b) Ideal displacement and dis-         |    |

|      | placement using measured DAC values                                                  | 57 |

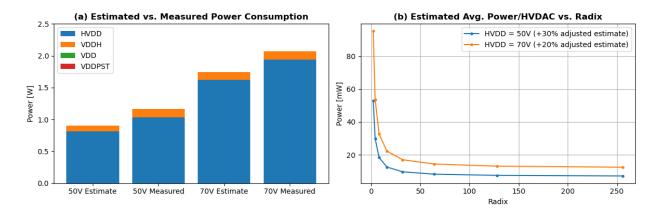

| 3.24 | (a) Estimated and measured power for an HVDD of 50V and 70V. (b) The esti-           |    |

|      | mated average power per high voltage DAC (HVDAC) vs. radix                           | 58 |

v

# List of Tables

| 2.1 | Global "address" scan chain bits listed in the order that they are connected                           | 14 |

|-----|--------------------------------------------------------------------------------------------------------|----|

| 3.1 | Model parameters for the SuperSwitch 2 MEMS unit cell.                                                 | 34 |

| 3.2 | Mapping between column (0-7 for 8x8 switch) and HVDAC IDs                                              | 40 |

| 3.3 | Global "Select" scan chain bits listed in the order that they are connected                            | 41 |

| 3.4 | Global "Control" scan chain bits listed in the order that they are connected                           | 42 |

| 3.5 | List of cell-controller control scan chain fields. Each cell controller has its own                    |    |

|     | unique set of these fields.                                                                            | 42 |

| 3.6 | List of all IDAC control scan chain registers. These bits are labelled as idac_cfg                     |    |

|     | in table 3.5                                                                                           | 47 |

| 3.7 | List of all IREFP control scan chain registers. These bits are labelled as irefp_cfg                   |    |

|     | in table 3.5 $\ldots$ | 48 |

| 3.8 | List of all FSM control scan chain registers. These bits are labelled as fsm_cfg in                    |    |

|     | table 3.5                                                                                              | 50 |

| 4.1 | Comparison table for optical circuit switches.                                                         | 61 |

| 4.2 | Comparison table for HV driver circuits.                                                               | 62 |

| _   | F                                                                                                      |    |

### Acknowledgments

Having the opportunity to pursue a PhD is an incredible privilege. My time at Berkeley has been transformative and will continue to shape me throughout my life. I am deeply grateful for this invaluable experience.

The biggest thanks must go to my advisor, Vladimir Stojanović, for believing in me from day one. Your passionate and patient approach to mentorship has made me a more confident engineer and person. I will strive to mentor young engineers in the same manner throughout my career.

I'd also like to thank Professors Ming Wu, Sophia Shao, and Martin White for providing invaluable feedback on my research. Ming has been a wonderful secondary advisor, and I deeply appreciate all the time he spent guiding me. It has been an absolute pleasure working with you.

Thank you to all my friends and peers who made this experience so enjoyable, despite COVID's attempts to derail our social lives: Derek, Ryan, Sunjin, Lars, Avi, Kevin, Johannes, Sidney, Kramnik, Sarika, Hyeong, and everyone from the Integrated Systems Group.

Balancing school and work hasn't been easy, and I absolutely could not have done it without the support of my boss, Norman Chan. Thank you for accommodating my odd hours and last-minute schedule changes. I've thoroughly enjoyed working with you and the rest of the ASIC team at Ayar Labs.

BWRC is truly a special place and it would cease to operate without the tireless efforts of Candy and Mikaela. Thank you for everything that you've done for me and for the many students before me!

Lastly, thank you to my family for supporting me through all my successes and failures. I would not be where I am without you. A special thanks to my partner, Megan, who stood by me through all the anxiety and challenges that came with pursuing a PhD. Your unwavering support and understanding mean the world to me, and I am so fortunate to have you in my life.

This work was supported by the DARPA PIPES program, BETR Center, Berkeley Wireless Research Center, and the SRC and DARPA co-sponsored CUbiC Research Center. I would also like to extend special thanks to Muse Semiconductor, S&C Micro, T-Microtec, and Micross for their chip fabrication and packaging support.

# Chapter 1

# Introduction to Optical Circuit Switching

This thesis explores new methods of optical circuit switching using specifically designed CMOS circuits for fast and scalable control. The following sections introduce the concept of optical circuit switching and identify the target application and key technology for the designs presented in Chapters 2 and 3.

## 1.1 Circuit vs. Packet Switching

Circuit switching gets its name from the old switchboard telephone days. The circuit, the phone in this case, was physically connected to another circuit (phone) through the switchboard. The operator had to physically disconnect one connection before they could establish another. Packet switching, on the other hand, allows for data transfer between many devices at once without physically reconfiguring the switch paths. Contention is handled by processing data coming into the switch and buffering it until a viable output path is available. Optical circuit switches (OCS) perform a similar function to the old telephone switchboards except that their data is optical in nature. As datacenters and high performance computing (HPC) systems continue to grow, more and more of the data is carried optically to benefit from low-loss and distance-indifferent high-speed operation compared to state-of-the-art electrical interconnects.

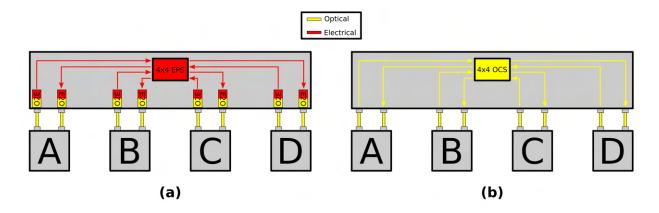

Fig. 1.1 (a) shows an illustration of an optically-connected electronic packet switch (EPS). These types of switches are prevalent in all HPC and datacenter networks as they leverage the benefits of both optical links and packet switching. All-optical packet switching has been heavily researched [3], but has never gained traction due to the difficulty of buffering data in the optical domain. Optically-connected EPSs are thus required to perform optical-to-electrical (O2E) and electrical-to-optical (E2O) conversions such that the data can be easily buffered in the electrical domain. These conversions add a huge power and latency penalty compared to the optical circuit switch (OCS) shown in Fig. 1.1 (b). The direct connections

offered by the OCS reduce the power and latency of the switching process but require that the connections be scheduled in advance. Bursty and random network traffic makes it hard to utilize a circuit switch as the primary switching element. Despite this, the replacement of some optically-connected EPSs with OCSs in a network can eliminate the inefficiencies of EPSs while maintaining, and in some cases augmenting, the network performance gains afforded by pure packet switching.

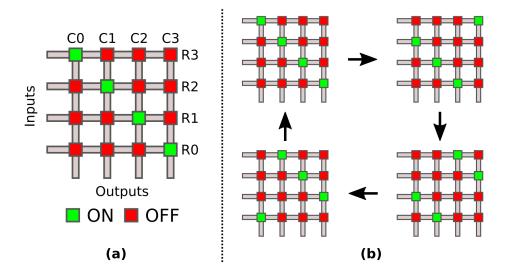

Figure 1.1: (a) Optically-connected 4x4 electronic packet switch (EPS). (b) All-optical 4x4 optical circuit switch (OCS).

## **1.2** Current Applications

Google published for the first time in 2022 on their use of OCSs within their datacenters [32]. They replaced the spine EPSs with an OCS connection layer to build a reconfigurable direct-connect mesh topology between aggregation blocks. Many of the stated advantages of using this OCS layer over the EPSs are related to the problem of deploying, upgrading, and maintaining large amounts of expensive equipment. Without the spine switches, the network can be more easily expanded and upgraded, as the OCS switching layer is trivially reconfigured via software. The OCSs are, in general, data rate agnostic and allow for incremental upgrades of the aggregation blocks without corresponding upgrades to the spine switching layer. All of these benefits save Google time, energy, and most importantly, money.

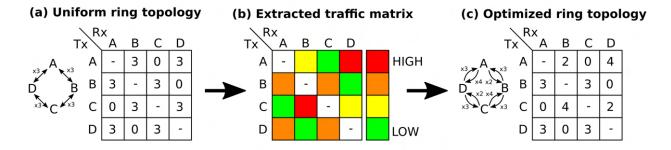

Perhaps the most interesting use of these OCSs is highlighted by Google's dynamic reconfiguration of their network topologies. Google detailed their so-called "topology engineering" for both their datacenters [32] and TPU clusters [18] but much research has already been done (and continues to be done) in this vein [47] [46] [42]. Google was simply the first major service provider to implement this type of topology optimization at scale. Fig. 1.2 shows a simple example of this topology optimization. The initial topology, Fig. 1.2 (a), is a basic uniform ring topology with each node having equal bandwidth between itself and its two neighboring nodes. This example allocates each node A-D 6 transmitters and 6 receivers (this number is chosen to make the example simple). This means that each row and column in the topology matrix shown in Fig. 1.2 (a) must sum to a maximum of 6. The traffic matrix for a given application is then extracted for a given period of time (Fig. 1.2 (b) shows the relative amount of transmitted data). Assuming that this extracted traffic matrix is representative of future traffic, the network topology can be reconfigured to better utilize the total available bandwidth (Fig. 1.2 (c)). Google was able to perform a more complicated topology optimization to improve specific network metrics relative to their baseline Clos topology.

Figure 1.2: (a) Initial uniform ring topology. (b) Traffic matrix extracted from a specific application showing the relative amount of transmitted data. (c) New ring topology optimized for the extracted traffic matrix.

## **1.3 Future Applications**

Google has shown that OCS-enabled dynamic topology optimization can be done to increase network performance. The frequency at which this reconfiguration is done is ultimately limited by the physical speed of switching. Google's current datacenter workloads only require topology optimizations at timescales much larger than even the slowest OCS switching speeds. Google reports optimizing their topology hourly [32], much longer than their quoted millisecond-scale switching speed [45]. Several papers, including those from Google, have highlighted the potential benefits of more frequent reconfiguration for different kinds of workloads, namely distributed AI/ML workloads [19] [24]. These workloads experience both repetitive and bursty network traffic, making them ideal candidates for pre-scheduled topology changes. Unfortunately, millisecond-scale switching will likely incur too high a latency penalty to make frequent topology changes beneficial. Future OCS technologies must investigate faster switching solutions if the full benefits of dynamic topology optimization are to be realized in distributed AI/ML applications.

### 1.4 OCS Technologies

The first technology to consider is the 3D MEMS mirror technology used by Google to create its 136x136 Palomar OCS [45]. The biggest advantage of these types of switches is their low insertion loss. Switches as big as 1100x1100 have been fabricated with only 4dB of maximum insertion loss [20]. Google's switch boasts a maximum insertion loss of only 2dB. The light itself only needs to bounce off two mirrors while making its way from input to output, reducing any loss associated with coupling into and out of waveguides as required by integrated photonic approaches. Low loss coupled with the 3D MEMS mirrors' inherent polarization insensitivity and broadband operation makes this technology a clear choice for the current OCS applications. Piezo-based switches, an alternative beam-steering technology commercialized by Polatis, have been shown to have loss as low or lower than 3D mems, with a commercial 576x576 switch reported to have a median insertion loss of 1.4dB and a maximum loss of 3dB [16] [17]. The switching speed for both technologies is quite slow, millisecond scale, and thus these switches may not provide a viable path forward for future applications as discussed in Section 1.3. Current applications, however, do not require fast switching and thus Piezo and 3D MEMS mirror based switches represent the current state of the art for optical circuit switches. Piezo-based switches, while also fabricated using standard MEMS processes, likely are more expensive to manufacture as the assembly process is more involved than 3D MEMS [10].

Significantly faster switching speeds, from microsecond [26] to even nanosecond scale [9], have been demonstrated by numerous silicon photonic (SiPh) OCSs. In addition, SiPh switches promise a lower potential cost than 3D MEMS as their manufacturing process is even closer to a standard CMOS process. Decently large radix switches (32x32) have been demonstrated using Mach-Zehnder interferometer (MZI) switches, but high per element losses and high crosstalk ultimately limit the scalability of such switches [33]. Benes style architectures can be used to minimize the total number of switching elements, and thus limit the per element losses, but this comes at the cost of increased cross talk compared to other MZI-based architectures [7]. Additionally, the rearrangeably non-blocking operation of these architectures is inherently bad for applications requiring frequent topology changes.

Micro-ring resonator (MRR) based SiPh switches generally experience the same fundamental scalability issue as MZI based switches as each additional ring adds significant loss in both the off and on states. Only switches up to 8x8 have been demonstrated thus far [13]. These types of switches also do not easily support wavelength division multiplexing (WDM) operation, an essential technology present in all modern datacenters [23]. The high thermo-optic coefficient in silicon also requires complex and power-hungry control for MRR switches. Recent work on multi-layer Si+SiN MRR OCSs solves many of these problems and shows promising scalability [25], but still does not provide pure WDM support with predefined wavelength channels limiting the type of transceivers that can be used.

There have been some promising results from indium phosphide (InP) based OCSs, as the presence of a direct bandgap material allows for the manufacture of semiconductor optical amplifiers (SOAs) on the same chip. This has allowed manufacture and testing of numerous

lossless (after amplification) switches. Unfortunately, III-V semiconductor processes such as InP are nowhere near as mature as CMOS processes, thus offering a more expensive and less economically scalable solution than MEMS or silicon photonics. In addition, the size of passive optical structures is much larger in InP processes meaning that the maximum port size of such switches is more limited than in other smaller photonic processes (such as SiPh) [5]. Hybrid architectures have been proposed to leverage the strengths of both SiPh and III-V, but port counts beyond 8x8 have yet to be demonstrated with larger switches only being proposed as a connection of multiple chips [49] [48] [43]. The SOAs themselves also consume a huge amount of power and degrade the signal-to-noise ratio through amplified spontaneous emission (ASE).

Crossbar style SiPh MEMS based OCSs, such as those demonstrated in [38] [22] [37], offer sub-microsecond switching speeds without the fundamental insertion loss and WDM issues of MZI and MRR based switches. This is due to the near zero off-state loss of the SiPh MEMS switch element and the fact that only 1 on-state switch element must be traversed per input. This means the total on-chip loss is limited only by the number of low-loss (0.015 dB) waveguide crossings and the propagation loss in silicon (<1.1 \text{dB/cm}) [37]. Recent work has also demonstrated a way to completely eliminate the waveguide crossings [12] such that the total loss is limited only by waveguide propagation loss. The fast speed and potential for low total insertion loss suggests that SiPh MEMS is an attractive solution for future OCS applications. Unfortunately, the crossbar style OCS requires  $k^2$  MEMS devices to be individually controlled for a kxk switch. At large port counts, the total number of devices becomes prohibitively large to control via off-chip drivers. Row/column addressing schemes have been shown to alleviate this issue, but at the cost of greatly increased power consumption and switching time [22]. To make matters worse, each SiPh MEMS device requires actuation voltages in excess of 40V. These control challenges have been cited as one of the biggest drawbacks to this type of OCS [8]. The remainder of this thesis explores two novel approaches to solving this control challenge to enable fast, low-power, and scalable crossbar style SiPh MEMS OCSs.

# Chapter 2

# SuperSwitch 1: A Digital Approach

## 2.1 Problem Statement

The goal of SuperSwitch 1 was to build a high voltage CMOS controller designed specifically for digital SiPh MEMS switches such as those described in [22]. As discussed in the previous chapter, compared to other SiPh switches, these switches have low loss and fast reconfiguration times ( $< 1\mu$ s). The remainder of this chapter will highlight how the SuperSwitch 1 CMOS controller was designed to complement the SiPh switch such that its fast speed and low loss can be fully realized.

### 2-Layer SiPh MEMS Switch

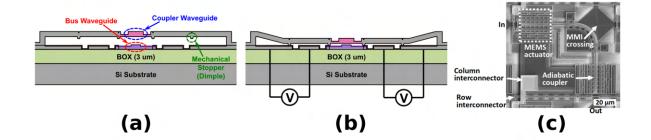

The MEMS devices are based on a 2-layer adiabiatic coupler architecture that has been researched in great detail in [14, 22]. Figures 2.1 (a) and (b) illustrate the OFF and ON state of the basic MEMS coupler device. The bottom waveguide layer is used as the bus layer. Fig 2.1 shows how this basic MEMS coupler can be turned into a crossbar switch element. The top coupler layer is pulled in towards the bus waveguide when a high voltage is applied across the device. Light is adiabatically coupled from the input bus waveguide (left side of Fig. 2.1 (c)) and is coupled up into the coupler layer. The coupler layer then bends 90 degrees before coupling light back into the bus waveguide layer, but now in the vertically oriented direction. This 90 degree bend is what allows this device to act as a crossbar switch element, coupling light from the horizontal input waveguides. When the MEMS device is in the OFF state the light remains in the horizontal input waveguide and continues on through the multi-mode interference (MMI) crossing. The MMIs are placed at all intersections of horizontal and vertical waveguides and help reduce the total on-chip loss.

Figure 2.1: (a) Schematic of (a) OFF state and (b) ON state of vertical MEMS coupler - figures taken from [14] (c) SEM of MEMS switch cell - figure taken from [22]

### Digital High Voltage MEMS Control

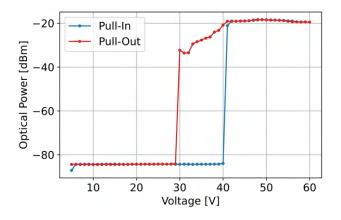

A representative transfer function of the MEMS device is shown in Fig 2.2. There are two things to note about this transfer function: 1. the voltage required to operate the device is in excess of 40 V and 2. there exists a hysteresis loop of around 10 V. The hysteresis in the transfer function is due to the fact that the MEMS device makes physical contact with a mechanical stopper, highlighted in green in Fig 2.1, when the applied voltage is greater than around 40 V. Once contact is made, surface forces, such as Van der Waals force, act in addition to the electrostatic force. The device retracts, or pulls-out, only when the applied voltage is lowered enough such that the elastic force of the MEMS device can overcome the combined contact and electrostatic forces.

The transfer function gives us a first order understanding of the type of high voltage driver that needs to be designed for this switch. Obviously the driver needs to operate in excess of 40 V in order to fully pull-in the device. It can also be seen that the optical power remains relatively constant once the voltage applied to the device is above a certain value. This suggests that as long as the driver can apply a voltage higher than the pull-in voltage, and lower than the pull-out voltage, that it can operate in a digital manner. This is very important as a digital high-voltage driver is much easier to design and burns much less power than a high voltage driver capable of outputting analog values.

### Scaling the OCS Radix

Given a standard fiber array unit pitch of 127µm, a 128x128 radix crossbar SiPh MEMS switch fits comfortably within the standard reticle size of 26mmx33mm. While reticle stitching has been shown to allow for scaling SiPh MEMS switches to port counts of 240 [37] (comparable to 256-port state-of-the-art packet switches [6]), SuperSwitch 1's radix was limited to 128 for an initial demonstration of co-packaged CMOS-SiPh operation. This radix choice was further validated when Google published on their own OCS that has a similar radix of 136 [45].

Figure 2.2: A representative transfer function of a MEMS switch element.

The 128-radix SiPh switch is shown in Fig. 2.3 (a). This switch was made in the same style as [22] but with individual connections to each MEMS switch element exposed throughout the center of the chip. This corresponds to 16,384 switch elements each w/ a positive and negative terminal that must be connected through the CMOS control chip. Fig. 2.3 (b) shows how a 4x4 grid of CMOS chiplets could be used to cover 16 separate 32x32 switch sections. This allows us to design the CMOS control chiplet through a multi-project wafer and use multiple chips to cover the nearly reticle-size SiPh chip.

Figure 2.3: GDS screenshots of (a) 128x128 SiPh MEMS crossbar switch (b) 4x4 CMOS high voltage driver chiplets flip-chip bonded to SiPh MEMS chip.

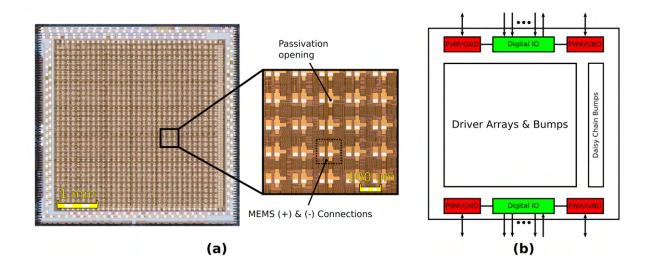

## 2.2 CMOS Design & Simulation

Fig. 2.4 (a) shows a micrograph of the finished chip which was taped out in TSMC's 180nm High Voltage BCD Gen2 process. At its core, the SuperSwitch 1 control chiplet is a 32x32 array of digital high voltage level shifters. A simple floorplan of the chip is shown in Fig. 2.4 (b). The MEMS electrode and back-bias pads, shown as MEMS (+) and (-) in Fig. 2.4 (a), are pitch matched to those on the SiPh chip.

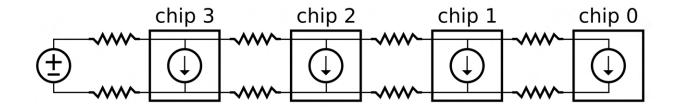

In order to connect the CMOS chiplets within each chiplet column, the power and digital control signals must be supplied from the north side of the chip and forwarded to the south side of the chip. For example, in Fig. 2.3 (b) the lower left CMOS chiplet is labeled as [0, 0], corresponding to the 0th chiplet row and 0th chiplet column. The northern most chiplet in the same column, chiplet [3, 0], will receive the digital signals and power and ground from the wirebonded connections on the north side of the SiPh chip. These signals will then be forwarded down all rows within the 0th column until they reach chiplet [0, 0]. The SiPh chip has a top routing layer that connects the south side of one CMOS chiplet and the north side of another. Each chiplet column has its own independent set of wirebond pads on the north side of the SiPh chip. The impact of forwarding the supplies from chip-to-chip is explored later in this chapter.

Figure 2.4: (a) Micrograph of SuperSwitch 1 high voltage driver chiplet (b) Cartoon floorplan of driver chiplet.

### **Digital Architecture**

The crossbar switch requires that only one switching element per column be actuated. Given this, the simplest digital control scheme would be to allocate a 7-bit scan chain per column to select 1 of 128 rows. Fig. 2.5 illustrates how this simple scheme would work for any given column X. The scan chain contains a 7-bit "instruction" that the decoder would use to produce a 1-hot 128-bit value. This 128-bit value then serves as the inputs to the 128 high voltage drivers (labelled as HVDRIVER in Fig. 2.5) within that column. The drivers are connected to the pads corresponding to the positive terminals of the MEMS switching elements.

Unfortunately, the scheme presented in Fig. 2.5 does not work as we have to control a 128-radix switch using 32-radix CMOS chiplets. Each column still has a 7-bit instruction scan chain but only 5 bits are decoded as there are only  $2^5 = 32$  rows and columns within each chiplet (this is highlighted in red in Fig. 2.6). The remaining 2 bits of the instruction are checked against 2 address bits loaded into a separate "address" scan chain (shown on the right side of the image highlighted in blue in Fig. 2.6). The decoder will produce a 1-hot output only if the instruction address is equal to the loaded address, otherwise it will output all 0s. This allows us to program the chiplet "addresses" at power-up such that every chiplet within a chiplet column has a unique address. Then, to actuate a specific row, the 2-bit chiplet address would be included in the instruction along with the 5-bits to denote the row within that selected chiplet.

One important thing to note about Fig. 2.6, is that the address scan chain is connected serially between chiplets in a single chiplet column. The instruction scan chains are connected in parallel across all chiplets within a column. This is done by forwarding the instruction

Figure 2.5: Simple schematic for activating 1 of 128 rows assuming a single CMOS chiplet.

scan chain input via the south side of the CMOS chiplet. In contrast, the address scan chain *output* is forwarded via the south side of the CMOS such that each address scan chain of each chiplet can be programmed independently.

#### **Column Folding**

The digital scan-in time directly adds to the switch reconfiguration time. If the scan-in time is large, then the fast reconfiguration time of the MEMS devices no longer affords us any benefit. In order to minimize the total switch reconfiguration time, all column instructions should ideally be scanned-in in parallel. This would require a scan-chain input signal for every column in the chip. For the 32x32 chiplet, this would mean dedicating 32 IOs just for the instruction scan chain inputs (not to mention the other signals required for operating the scan chains). To decrease the total number of scan chains, the column instructions can be "folded" such that multiple column instructions are contained w/in a single instruction scan chain. This "folding factor", or number of columns per scan chain, is denoted by the symbol  $N_c$ . Fig. 2.7 shows what the scan chains would look like for (a)  $N_c = 1$  and (b)  $N_c = 2$ . Naturally, the scan chain increases in length by 7, i.e.  $log_2 128$ , for each additional column contained within the scan chain.

Eq. 2.1 is used to calculate the total number of instruction scan chain pads,  $N_p$ , given the total switch radix, k, and the number of columns per instruction scan chain,  $N_c$ . The factor of 4 in the denominator comes from the fact that 128 columns are split across 4 chiplet columns.

Figure 2.6: Schematic for controlling a 128x128 switch assuming a 4x4 array of CMOS chiplets.

$$N_p = \frac{k}{4N_c} \tag{2.1}$$

Eq. 2.2 is used to calculate the additional reconfiguration time due to the scan chains,  $T_s$ , given the number of columns per scan chain,  $N_c$ , the radix of the switch, k, and the clock frequency of the scan chains,  $f_{clk}$ .

$$T_s = \frac{N_c log_2 k}{f_{clk}} \tag{2.2}$$

#### Final Scan-Chain Architecture

Unfortunately, 32 instruction chain inputs, i.e.  $N_c = 1$  and  $N_p = 32$ , for a chiplet w/ north side edge of approximately 4.3mm is prohibitively high. This is doubly true since the SiPh chip must route every signal from one chiplet to another over a single routing layer. For this reason, an  $N_c$  of 4 was chosen to reduce  $N_p$  to 8. The effects of this choice on the scan chain architecture are shown in Fig. 2.8 (a). The CMOS chiplet has a total of 8 instruction scan chains each with 28 bits for controlling 4 separate columns. The address scan chain is

Figure 2.7: (a) Logic for columns 0 and 1 for  $N_c = 1$  (b) Logic for columns 0 and 1 for  $N_c = 2$ .

comprised of 7 bits with only 2 of those bits actually dedicated for the chiplet address. The other bits include a global enable signal for the high voltage driver circuits, discussed later in this chapter, as well as a loopback-select field that controls the mux shown in Fig. 2.8 (a) (these fields are described in detail in Table 2.1). The loopback select allows us to test the functionality of the instruction scan chains. The mux can be configured to loopback any of the instruction scan chain outpus OR the loopback signal from the adjacent southern CMOS chiplet. This allows us to test any instruction scan chain within any given CMOS chiplet.

At an  $f_{clk}$  of 30MHz, this gives us a  $T_s$  of less than 1µs. Seeing as how similar style MEMS switches have observed switching times less than 1µs ([14, 22, 37]), this seems an appropriate target for  $T_s$ . A list of all final design parameters can be found in Fig. 2.8 (b).

### **HV** Driver Architecture

The schematic of the high voltage driver is shown in Fig. 2.9 (a). The various supplies and their nominal values are listed in Fig. 2.9 (b). This circuit is a modified version of a capacitive level shifter first introduced in [41] and then further detailed in [50]. The two digital inputs,  $V_{in}$  and  $V_{en}$ , are generated by the logic shown in Figures 2.6 and 2.8.  $V_{in}$  controls the output at  $V_{out}$  such that a 0 to 1.8 V swing at the input causes a 0 to 70 V swing at the output. The input signal is first level shifted to 5 V, via transistors  $M_1$ - $M_4$ , before being used to push/pull the voltage at the bottom plates of capacitors  $C_1$  and  $C_2$ . Via capacitive coupling, a changing voltage at the bottom plates of these capacitors will cause a corresponding change in voltage

Figure 2.8: (a) Final schematic of SuperSwitch1 control chiplet scan architecture w/ loopback mux for debug. (b) Final parameters for SuperSwitch1 controller chiplet.

Table 2.1: Global "address" scan chain bits listed in the order that they are connected.

| Field             | Width | Description                                                     |  |  |  |  |

|-------------------|-------|-----------------------------------------------------------------|--|--|--|--|

| driver_enable 1   |       | Global (at a chiplet level) high voltage driver enable signal.  |  |  |  |  |

| loopback_select 4 |       | Selects the loopback signal for debug purposes. Values 0-7 se-  |  |  |  |  |

|                   |       | lect the output of the 1st through 8th instruction scan chain.  |  |  |  |  |

|                   |       | Any value above 7 selects the loopback input from the con-      |  |  |  |  |

|                   |       | nected chiplet to the south.                                    |  |  |  |  |

| chiplet_address   | 2     | Sets the address of the chiplet for decoding instructions. This |  |  |  |  |

|                   |       | field should be set to a unique value for each chiplet within a |  |  |  |  |

|                   |       | chiplet column.                                                 |  |  |  |  |

at nodes X and Y. Assuming X and Y are pushed above/below the switching threshold of the latch made up by transistors  $M_9$ - $M_{12}$ , then positive feedback from the latch will continue pushing/pulling X and Y to HVDD and HVSS respectively. Node Y can then be used to drive the gate of the high voltage PMOS in the output stage of the high voltage driver.  $M_{13}$ , the high voltage NMOS in the output stage, is driven by the logical AND of the inverted and level shifted  $V_{in}$  and the level shifted  $V_{en}$ . When the driver is enabled, i.e.  $V_{en} = 1.8V$ ,  $M_{13}$  is driven high when  $V_{in} = 0$ V such that only one transistor in the output stage is ever turned on. On power-up,  $V_{en}$  is set to 0 which forces  $M_{13}$  to be off. This is desired as we do not know the initial state of the latch immediately after power up. As discussed in a following section, a specific initialization routine must be completed to place the latch in a known state before  $V_{en}$  can be set to 1.8V. Otherwise, there is a chance that both  $M_{13}$  and  $M_{14}$  could be turned on after power-up.

70 V corresponds to the highest voltage transistor offered in TSMC's 180nm HV BCD Gen2 process. These transistors were chosen for  $M_{13}$  and  $M_{14}$  as their area was not prohibitively large and the 70 V limit gives ample margin for error given the required 40 V range estimated by Fig. 2.2.

Figure 2.9: (a) Schematic of SuperSwitch1 high voltage driver circuit. (b) List of all supplies and their nominal values.

#### **Optimizing Bootstrap Capacitance**

Perhaps the most important parameter when sizing the circuit in Fig. 2.9 is the size of the bootstrap capacitors  $C_1$  and  $C_2$ . The larger we make these capacitors the better capacitive coupling we will have from the drains of  $M_1$  and  $M_2$  to nodes X and Y. The primary failure mechanism of this circuit, discussed in detail in [50], is the failure to flip the latch when transitioning  $V_{in}$ . This can occur if the capacitances,  $C_1$  and  $C_2$ , or the pullup/pulldown resistances of the latch itself, become too small. When either of these values become too small then any change in voltage on nodes X and Y will be quickly neutralized through the pullup/pulldown paths in the latch. The capacitances and resistances must be large enough such that the voltages on nodes X and Y can increase/decrease beyond the switching

threshold of the latch. This is the only way that we can get the latch to change states when toggling  $V_{in}$ .

Given a standard 2:1 sizing of PMOS-to-NMOS widths (w/ minimum sized NMOS), the key question becomes rather simple: how large should we make the bootstrap capacitors? Fig. 2.10 shows the results of transient simulations as the bootstrap capacitance is swept from 10fF to 100fF. The goal is to find a capacitance value that is small enough that it does not dominate the area of the driver but large enough that switching is gauranteed across all corners. The corners, shown on the y-axis, denote the process corner (NMOS strength followed by PMOS strength) and the temperature at which the simulation is run (m40c referring to *minus* 40 degrees celsius). Failure occurs when the driver is not able to flip the state of the latch and thus the output cannot be driven between HVDD (70 V) and VSS (0 V).

As shown very clearly by Fig 2.10, only the mismatched corners, fs27c and sf27c, seem to affect the performance of the circuit relative to the nominal corner tt27c. For this particular circuit, the worst performance occurs when the NMOS process corner is slow and the PMOS process corner is fast. This is due to the operational mechanism of the input level shifter (transistors  $M_1$ - $M_4$ ). As discussed in [50], the rate of change in voltage on the bottom plates of  $C_1$  and  $C_2$  is directly related to the change in voltage seen on nodes X and Y. The rate of change of voltage is governed by the speed at which the input level shifter shifts. Because the inputs of the level shifter, transistors  $M_1$  and  $M_2$ , are NMOS, the speed of shifting depends on the strength of NMOS relative to the PMOS. For stronger NMOS, i.e. corner fs27c, the outputs of the input level shifter will change sharply as the NMOS quickly overpowers the PMOS. For the other corner, sf27c, the NMOS transistor will more slowly overcome the PMOS transistor and thus give us a smaller change in voltage on nodes X and Y. This is why sf27c gives the worst circuit performance and fs27c gives the best. Despite this, Fig. 2.10 tells us that a capacitance value of 30fF or above should allow us to switch under any process corner.

The capacitors themselves are made from standard MOM caps. This type of capacitor is preferred as it can withstand voltages up to 70 V without experiencing dielectric breakdown. Other more area efficient capacitors, such as MIM caps, cannot withstand high enough voltages to be used in this circuit. Using 3 metal layers, 90fF capacitors were designed for  $C_1$  and  $C_2$ . Fig. 2.10 shows that this size gives us ample margin across all corners. The size of each capacitor is approximately 240µm<sup>2</sup>. The total driver size is  $\approx 9160µm^2$  which means the capacitors account for less than 6% of the total area. The high voltage transistors, on the other hand, account for greater than 50% of the total area of the high voltage driver.

#### **Initialization Procedure**

As previously stated, the latch shown in Fig. 2.9, formed by transistors  $M_9$ - $M_{12}$ , will initially be in an unknown state after power up. The latch must be initialized before the driver is enabled in order to ensure that a short never occurs from HVDD to VSS. The following initialization procedure must be followed to properly enable the high voltage driver circuits.

| fs27c  | Fail | Fail | Pass  |

|--------|------|------|------|------|------|------|------|------|------|-------|

| ss125c | Fail | Fail | Fail | Pass  |

| tt27c  | Fail | Fail | Fail | Pass  |

| ffm40c | Fail | Fail | Fail | Pass  |

| sf27c  | Fail | Fail | Fail | Fail | Fail | Pass | Pass | Pass | Pass | Pass  |

|        | 10fF | 20fF | 30fF | 40fF | 50fF | 60fF | 70fF | 80fF | 90fF | 100fF |

Bootstrap Capacitance vs. Corners

Figure 2.10: Shmoo plot for 10-100 fF bootstrap capacitance.

- 1. Ramp the digital voltages VDD and VDDH to their nominal values (1.8 and 5 V). All input and enable signals for all drivers should remain at 0 V.

- 2. Ramp both HVDD and HVSS to HVSS's nominal value (65 V).

- 3. Ramp HVDD to its final and nominal value (70 V).

- 4. Toggle  $V_{in}$  of all drivers from 0 V to 1.8 V and back to 0 V. This will place all latches into a known state.

- 5. Set the global enable signal to 1.8 V such that the high voltage NMOS of each driver circuit is turned on. The previous step ensured that the HVPMOS was turned off so there is no danger in turning the HVNMOS off. All drivers are now enabled.

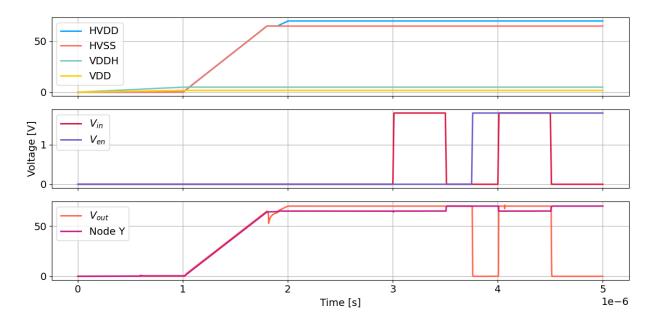

Fig. 2.11 shows a transient simulation of the above initialization procedure. For this particular simulation, node Y of Fig. 2.9 settles to 65V after all supplies are ramped. If  $V_{en}$  signal is set to 1.8V immediately after power up then both the HVNMOS (on when  $V_{in} = 0V$ ) and HVPMOS (on after power-up) would be on causing a short between HVDD and VSS. Fig. 2.11 shows the keeper being placed into a known state around 3.5µs once  $V_{in}$  is set to 0 V after being set to 1.8V.  $V_{en}$  is then set to 1.8V around 3.75µs.  $V_{in}$  is then toggled

one more time to show that the output correctly rises to HVDD (70V) when  $V_{in} = 1.8V$  and correctly falls to VSS (0V) when  $V_{in} = 0V$ .

Figure 2.11: Basic initialization procedure for SuperSwitch1 high voltage driver circuit.

#### Simultaneous Switching

The circuit model for a single column of flip-chip bonded chiplets is shown in Fig. 2.12. The supply and ground resistances between chiplets are due to the flip-chip bonds between the SiPh and CMOS chips as well as the short amount of interconnect on the SiPh chip. One concern with this design is that given a large enough supply and/or ground resistance, the chip may cease to function properly. The ground or VSS resistance is the most sensitive as all current from all supplies will return via the same ground path. For this reason, a transient simulation experiment was done to understand the maximum allowable ground resistance. The results of this experiment are shown in Fig. 2.13. During the simulation 32 high voltage drivers simultaneously turn on while 32 separate high voltage drivers turn off. This gives us the worst-case/maximum current draw that any chiplet column should ever experience. This is because of the crossbar nature of the switch and the fact that only 1 device/column ever needs to be actuated. The simulation assumes that all the current from all supplies is forced through the same resistance. This would occur only when all 32 drivers turning off and on are located in chip 0 of Fig. 2.12.

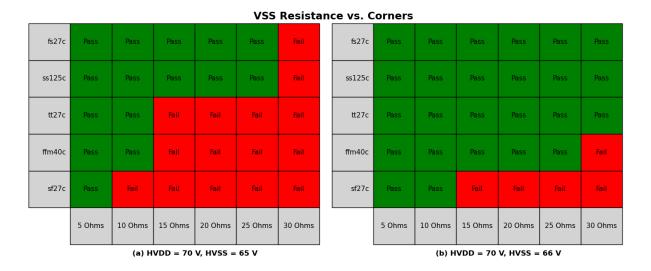

Alarmingly, Fig. 2.13 (a) indicates that only 10 ohms of ground resistance is needed to cause circuit failure at the sf27c corner. This is the same worst case corner discussed in Section 2.2. In contrast to the experiment of Fig. 2.10, there also seems to be some

Figure 2.12: Equivalent circuit of supply and ground connection for a single chiplet column in the flip-chip bonded CMOS-SiPh package.

performance degradation associated with the tt27c and ffm40c corners relative to the ss125cand fs27c corners. This is likely due to the fact that the stronger the transistors are the more current that will be drawn and thus the more voltage drop across the ground resistance. Thankfully, there is a relatively simple remedy to this problem. Fig. 2.13 (b) shows the same experiment but with HVSS set to 66V instead of 65V. This slightly degrades the rise time of the high voltage driver (as the HVPMOS can now only be turned on w/ a  $|V_{gs-max}|$ of 4V instead of 5V) while affording significantly improved resilience to ground resistance. This improved resilience is due to the increased HVSS reducing the switching threshold of the latch circuit inside the high voltage driver. The increased HVSS will also decrease the peak current drawn by the HVPMOS and thus reduce the voltage drop across the ground resistance. HVSS can be increased further to accomodate even larger ground resistance.

Figure 2.13: (a) VSS resistance show plot for all corners for HVDD = 70 V, HVSS = 65 V. (b) Same plot but for HVDD = 70 V, HVSS = 66 V.

### **Transient Simulations**

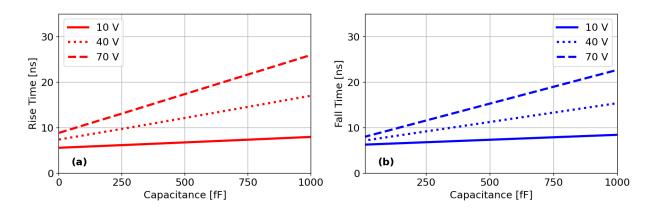

The simulated rise and fall times of the high voltage driver circuit, shown in Figures 2.14 (a) and (b) respectively, are well below 1µs even for 70V operation and an output load of 1pF. These simulations are done on the extracted post layout netlist with an ideal capacitor as the output load.

Figure 2.14: Rise (a) and fall (b) times extracted from post-layout simulations.

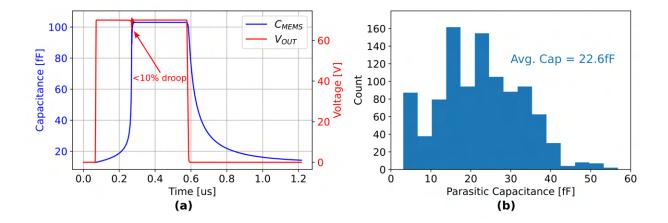

The actual load of the driver consists of both the MEMS device and the parasitic output capacitance of the driver. The MEMS device acts as a variable capacitor, having a high capacitance when pulled in and a lower capacitance when pulled out. In order to understand the effects of the variable capacitance on the driver, a Verilog-A model was developed similar to the model detailed in Chapter 2 of [40]. Fig. 2.15 (a) shows the results of a transient simulation using the MEMS model as the output load. The output voltage drops as the MEMS device pulls in and the capacitance suddenly increases from around 10fF to around 100fF. The sudden drop in voltage at the output could potentially affect the state of the latch controlling the HVPMOS (through  $C_{qd}$  of  $M_{14}$  in Fig. 2.9 (a)). Thankfully, even the minimum sized HVPMOS in this process was strong enough to limit the maximum voltage droop to less than 10%, resulting in a minimal change in voltage on Node Y of Fig. 2.9 (a). The effects of this changing capacitance are further reduced by any additional output capacitance. Fig. 2.15 (b) shows the extracted parasitic output capacitance for all 1024 drivers. Each driver has a slightly different parasitic output cap because of the way the pads are arrayed in relation to the driver array. The average parasitic capacitance is only  $\approx 23$  fF, suggesting the MEMS capacitor will be the majority of the capacitive load.

Figure 2.15: (a) Transient simulation of capacitance of MEMS model  $(C_{MEMS})$  and output driver voltage  $(V_{OUT})$ . (b) Parasitic output capacitance for all 1024 drivers (due to short routes and pads).

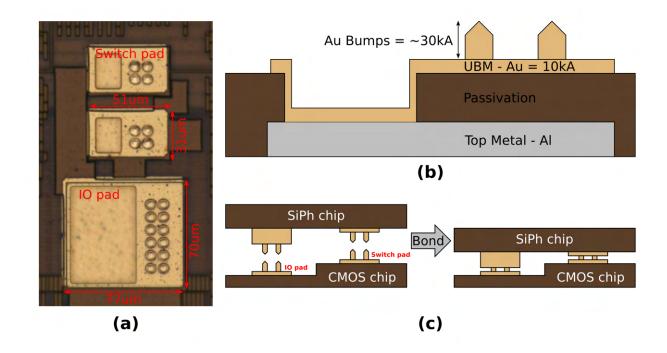

## 2.3 3D SiPh-CMOS Packaging

The SiPh and CMOS chips were bonded together using a process that relies on deformable Au micro-bumps patterned using nano-particle deposition. The process bonds the micro-bumps together as result of mechanical pressure and does not require reflow (max temperature is 200C). This reduces the thermal cycling stress as each package must be temperature cycled 16 times, once for each CMOS chip. It also completely eliminates the need for flux. This is essential as flux or other similar substances could inflitrate the released MEMS structures rendering the switch inoperable post bonding. More details on the specifics of this bonding process are given in [21].

The post Au micro-bumped CMOS chips are shown in Fig. 2.16 (a). Two types of pads are present on the CMOS: a small 51µmx31µm pad for the switch connections and a larger 77µmx70µm pad for the north and south IO connections. Fig. 2.16 (b) shows an illustration of the cross section of a switch pad. A small passivation opening is made over the CMOS Al pad so that the deposited Au UBM can make contact. The UBM covers only the area above the CMOS pad such that there exists a flat surface for bumping and bonding (right side of Fig. 2.16 (b)). After several failed attempts at bonding, a surface height difference of nearly 1µm was discovered between the switch and IO pads on the CMOS chip. Fig. 2.16 shows how this difference was compensated for by adjusting the thickness of the SiPh chip's UBM for the two pad types.

A 4x4 test package is shown in Fig. 2.17 (a). 16 CMOS chips were bonded to an electrical interposer as an early first attempt at bonding. Fig. 2.17 (b) shows a single CMOS chip bonded to a 32x32 subsection of the 128x128 SiPh OCS. This was the highest yielding package and was used for generating all results in Section 2.6. A fully yielding 128x128

Figure 2.16: (a) Micrograph of bumped CMOS pads. (b) Cross section of Au UBM and Au micro-bumps. (c) Illustration of bonding process using differing thicknesses of UBM on SiPh chip to compensate for CMOS pad height differences.

package has not yet been accomplished and is part of the future work for this project. The resistance of all supplies through the 32x32 switch was measured to be below  $10\Omega$  with the VSS resistance under  $2\Omega$ , well under the maximum resistance for all corners as shown in Fig. 2.13 (b). [21] measures an average resistance of  $0.25\Omega$ /bump suggesting that the bumps are likely not the limiting factor.

Figure 2.17: (a) 4x4 CMOS flip-chip bonded to electrical interposer. (b) 1 CMOS flip-chip bonded to 32x32 subsection of 128x128 OCS.

## 2.4 PCB Design

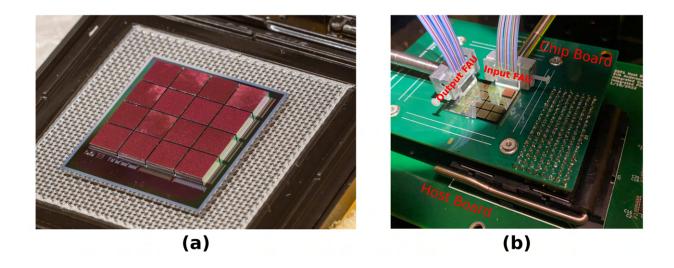

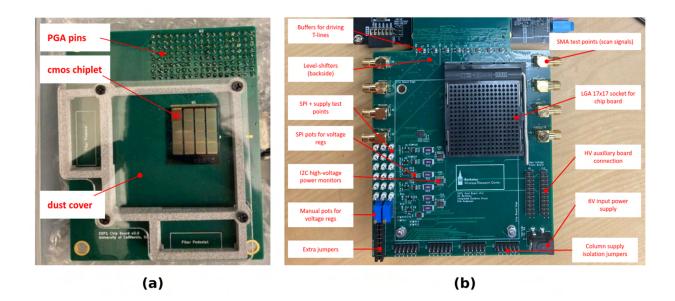

The PCB design was split into two different boards. The first board, shown in Fig. 2.18 (a), serves as the wirebond package for the flip-chip bonded SiPh-CMOS assembly. Wirebonds are made from the north side of the SiPh chip directly to this "chip board" PCB. The chip board then fans out the signals and connects them to a set of pins that fit into a standard 17x17 pin-grid-array (PGA) socket. A dust cover is also fit on top of the chip board to protect the released MEMS structures from getting contaminated. Fig. 2.18 (a) shows a picture of a chip board w/ only a single CMOS chiplet bonded to the upper lefthand corner of the SiPh chip.

The second board, shown in Fig. 2.18 (b), or "host board", contains the PGA socket that the chip board plugs in to. The host board then contains all ICs required to test the chip. These ICs include power regulators, power monitors, level shifters, buffers, and other miscellaneous ICs. The separation between the chip and the host board allows reuse of the host board across all assembled chip boards.

Figure 2.18: (a) The chip board for wirebonding chips to. (b) The host board PCB used for testing chip boards.

## 2.5 Electro-optic Characterization Setup

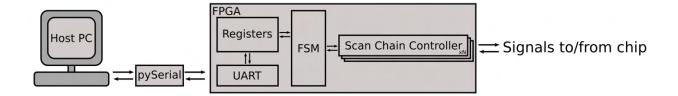

The first step to setting up a full electro-optic characterization setup is establishing electrical communication with the chip itself. As the CMOS chips use a custom scan chain architecture (detailed in Section 2.2), an FPGA provides a simple and reliable way to generate compatible scan controllers. Fig. 2.19 shows how the host PC communicates to the chip through the scan controllers instantiated on the FPGA. First, the PC sends UART commands (via pySerial) to read and write registers connected to a custom UART implementation. These registers set and get values inside a finite-state-machine that controls N scan chain controllers. N can be more or less depending on the number of CMOS chiplet columns bonded to the SiPh chip. For example, Fig. 2.18 (a) shows a single chiplet row in a single chiplet column. An accompanying FPGA image would have N = 9 scan chain controllers to control the 8 instruction scan chains and the 1 additional address scan chain. Each additional chiplet column would require an additional 9 scan chain controllers.

The FSM can directly control the scan controllers through the UART interface OR it can be programmed to continuously scan-in bits written into the block-RAM of the FPGA. The latter mode is required in order to measure the worst-case power consumption of the device. Without this continuous mode, the scan chains become limited by the speed of the UART interface which can be quite slow. This will be discussed in more detail in a later section.

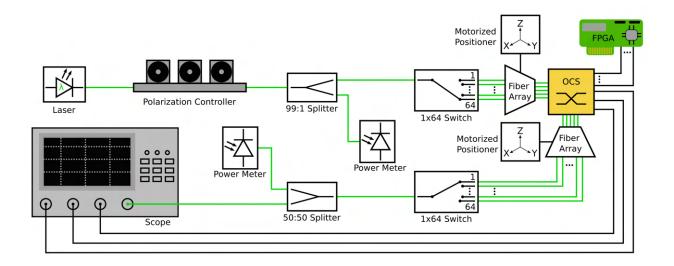

Once electrical communication between the OCS and the host PC has been established, the rest of the characterization setup can be constructed. A cartoon illustration of the final characterization setup can be seen in Fig. 2.20. The host PC is not shown in this figure. In

Figure 2.19: Simplified diagram of the PC-to-chip interface with UART-controlled scan chain controllers.

reality, the host PC is connected to every device in the figure besides the few passive optical components such as the 99:1 splitter and the 50:50 splitter. The input light is provided by a tunable O-band laser. This light is then fed into a motorized polarization controller before being sent to the switch. This is required as the switch uses vertical grating couplers optimized for TE polarization of light. The poalriziation controller helps optimize the input polarization such that the minimum loss can be measured. After the polarization controller, the light is split and 1% is sent to a digital power meter and the other 99% is sent to a 1x64 OCS. This OCS is used to switch the light into any of 64 input ports of a fiber array unit (FAU). The FAU is responsible for shooting the light into the SiPh OCS, shown in yellow in Fig. 2.20. The reading from the digital power meter at the end of the 1% tap can be used to back calculate the input power to the switch. The FAU is initially aligned by hand but is continuously fine-aligned by the motorized positioners during the characterization routine. This compensates for any drift experienced by the FAU as well as allowing for optimized coupling for each individual input and output. While the FAU's fibers are nominally pitch matched to the SiPh OCS at 127µm, there is some nonuniformity in the fiber spacing. By fine-aligning the FAUs for each input to the SiPh OCS, the minimum loss through each input can be observed. A similar coarse and fine alignment is done on the output FAU as well. There is also another 64x1 OCS to select a specific output for measurement. The light from the selected output is then fed into a 50:50 splitter which sends half the light to another digital power meter and the other half to an oscilloscope with an optical input. The power meter gives us a low noise-floor measurement of the output power. This measurement, combined with the input power measurement, allows us to calculate the loss through any given switch element in the SiPh OCS. The oscilloscope is used to measure the rise and fall time of the optical signal.

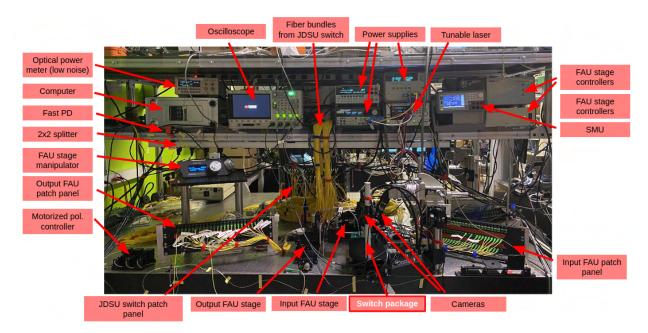

An annotated picture of the actual electro-optic characterization setup is shown in Fig. 2.21. For full 128x128 characterization, a total of 16,384 devices must be characterized. This is a massve number of devices and requires a reliable and repeatable measurement setup. Almost everything in the measurement setup is fully automated including the oscilloscope waveform capture, the polarization optimization algorithm, and the fine-alignment of the FAUs. The external 1x64 OCSs limit the automation to only  $64^2 = 4096$  devices. After characterizing 4096 devices the FAUs either need to be realigned to a new set of 64

Figure 2.20: Illustration of the SuperSwitch1 characterization test setup.

input/output ports or the patch panels (shown in lower left and lower right of Fig.2.21) must be rewired. A more complete setup would make use of 1x128 OCSs such that coarse alignment must only be done once at the beginning of the characterization routine.

Figure 2.21: The physical test setup for fully automated switch characterization.

# 2.6 Results

As of writing this thesis, the only complete characterization that has been done was on the 32x32 OCS pictured in Fig. 2.17 (b). This figure also shows the package with both the input and output FAUs aligned to the switch's vertical grating couplers. Only 1 CMOS chiplet is bonded to the 128x128 SiPh switch and thus the radix is reduced to 32. Looking back at Fig. 2.3 (b) the bonded CMOS chiplet has index [3, 0] (chiplet column 0 row 3).

### Single Cell Characterization

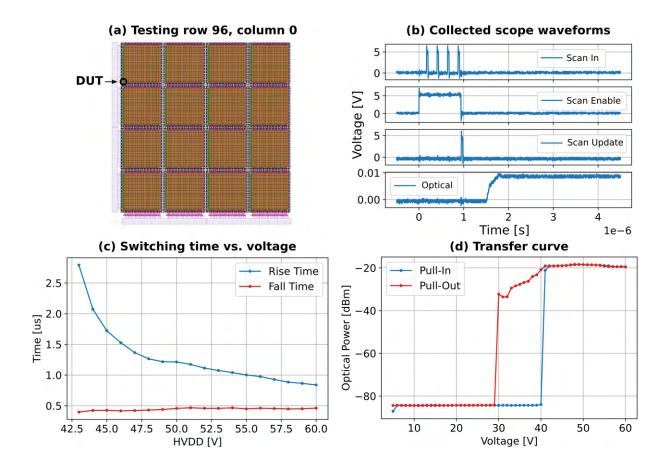

The switching speed, optical loss, and optical transfer curve were measured for each of the 1024 MEMS switch elements. Fig. 2.22 shows these characterization results for the lower left switch element (row 96, column 0) of the 32x32 OCS. The switch rise and fall times are extracted from captured oscilloscope waveforms such as the one shown in Fig. 2.22 (b). The top 3 signals are the instruction scan chain control signals for the CMOS chip (scan clock signals are not shown). The scan enable signal enables shifting of bits specified via the scan-in signal. The scan update signal latches the new shifted-in value of the scan chain into the design. This means the high voltage driver begins driving the switch element as soon as the scan update signal is asserted. The bottom signal shown in Fig. 2.22 (b) is the optical output from the switch (translated into a voltage through a PD+TIA). The rise time is calculated from the instant scan update is asserted to the time at which the optical signal has reached 90% of its final value. Fig. 2.22 (c) shows the rise and fall times for different values of HVDD. At 60V, both rise and fall are less than 1µs, 0.83µs and 0.46µs respectively. The rise time shows a strong dependence on HVDD as larger HVDD increases the maximum electrostatic force that pulls the device in, thus pulling it in quicker. The fall time shows the opposite trend as increased HVDD simply means the driver takes longer to discharge the MEMS capacitor to the point at which the combined surface and electrostatic forces are less than the elastic force of the MEMS. Once the surface forces are no longer acting on the device, the elastic force of the MEMS structure quickly overpowers the relatively weak electrostatic force. Fig. 2.22 (d) shows the optical transfer curve for this device.

#### 32x32 OCS Results

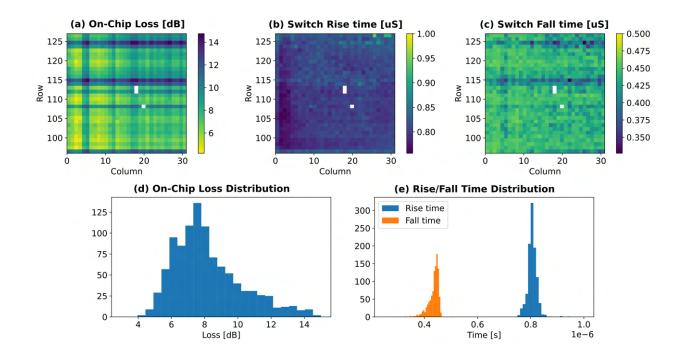

The full characterization results for the 32x32 OCS are shown in Fig. 2.23. Figures 2.23 (a)-(c) show the on-chip loss, rise time, and fall time for each switch element at an HVDD of 60V and a wavelength of 1310nm. Only 3 switch elements, shown in white, were found to be non-operational. This corresponds to a yield of 99.7%. The on-chip loss distribution is shown in Fig. 2.23 (d). This switch includes excess loss of  $\approx 3.8$ dB as the output ports of the 32x32 OCS must propagate through an additional 96 rows of unused switch elements before reaching the output vertical grating couplers. This could be avoided by designing (or dicing) the SiPh OCS to only have a radix of 32. As shown by Fig. 2.23 (e), the rise and fall times for all elements are below 1µs for an HVDD of 60V.

Figure 2.22: (a) Location of switch cell being tested. (b) Captured scope waveforms used for extracting rise and fall times. (c) Rise and fall times. vs applied voltage. (d) Optical transfer curve.

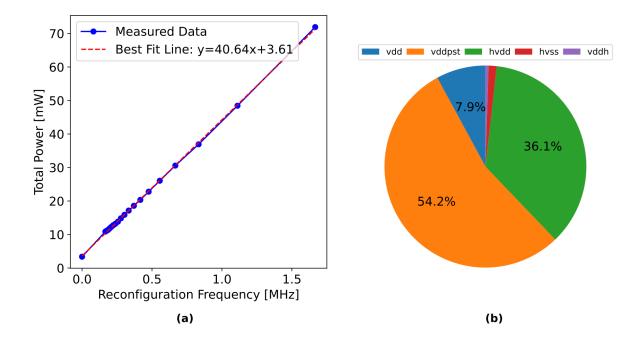

### **Power Consumption**

The digital nature of the driver circuit shown in Fig. 2.9 (a) results in nearly 0 static power consumption. This leaves only the dynamic power consumption which can be measured by periodically turning off and on switch elements. The worst case dynamic power consumption is illustrated in Fig. 2.24. Fig. 2.24 (a) shows a cartoon representation of a 4x4 switch. The crossbar switch requires only 1 switch element to be ON, shown in green, in each row/column. This means that for any valid switch configuration a total of k switch elements are ON, k being the radix of the switch. The worst case dynamic power would then be observed when k new elements are turned ON and the previous k elements are turned OFF. Fig. 2.24 (b) shows the worst case pattern for a 4x4 switch.

A similar pattern to the one shown in Fig. 2.24 (b) is used to measure the power for the 32x32 OCS. In contrast to Fig. 2.24 (b), each frame, or individual switch configuration, will have 32 switch elements actuated. The speed at which the pattern iterates through its frames

Figure 2.23: Measured on-chip loss (a/d), rise time (b/e), and fall time (c/e) for all  $32^2 = 1024$  switch elements. Measurements were done at an HVDD of 60V and a wavelength  $\lambda = 1310$ nm.

Figure 2.24: (a) Example 4x4 OCS w/ one driver "ON" per row/column. (b) Worst case functional pattern for power measurements.

is called the switch reconfiguration frequency. The total power, including both the dynamic and static contributions, is shown as a function of switch reconfiguration frequency in Fig. 2.25 (a). As previously mentioned, the static power is quite small at only 3.61mW. The maximum observed power is 72mW which was measured at the maximum reconfiguration frequency of 1.7MHz. This frequency corresponds to the time required to scan in 28 instruction bits at the maximum digital clock frequency, 50MHz:  $f_{reconfig-max} = 1/\frac{28+1}{50MHz} \approx 1.7MHz.$ 72mW represents the absolute maximum power for this 32x32 OCS. Typical power consumption will likely be much less as at least some consecutive frames will leave a few elements unchanged. The reconfiguration frequency will also likely not remain constant at the maximum frequency during typical operation. Fig. 2.25 (b) shows the power breakdown by supply for the maximum reconfiguration frequency. HVDD is set to 60V while all other supplies are set to their nominal values as shown in Fig. 2.9 (b). 60V is chosen as it is the minimum voltage required to ensure all rise and fall times are less than 1µs. VDDPST, not shown in Fig. 2.9 (b), is the IO supply voltage and is set to 5V. This supply consumes over 50% of all power at the highest reconfiguration frequency and is highly dependent on the PCB layout. A more optimized PCB layout than what is shown in Fig. 2.18 could be used to further reduce the power consumption. A lower IO supply voltage could also be used to reduce power (down to 1.8V for this chip) but would also reduce the maximum attainable reconfiguration frequency.

Figure 2.25: (a) Measured worst case power for 32x32 OCS w/ HVDD=60V. (b) Power breakdown by supply for maximum reconfiguration frequency of  $\approx 1.7$ MHz.

# Chapter 3

# SuperSwitch 2: An Analog Alternative

## 3.1 Problem Statement