# Hybrid Baud-Rate CDR and Clock Distribution Techniques for High-Speed 100Gbps Wireline Receiver

Yi-Hsuan Shih

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2025-165 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2025/EECS-2025-165.html

August 15, 2025

Copyright © 2025, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Hybrid Baud-Rate CDR and Clock Distribution Techniques for High-Speed 100Gbps Wireline Receiver

By

Yi-Hsuan Shih

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Vladimir Stojanovic, Co-Chair Professor Borivoje Nikolic, Co-Chair Professor Martin White

Summer 2025

# Hybrid Baud-Rate CDR and Clock Distribution Techniques for High-Speed 100Gbps Wireline Receiver

Copyright 2025 by Yi-Hsuan Shih

#### Abstract

Hybrid Baud-Rate CDR and Clock Distribution Techniques for High-Speed 100Gbps Wireline Receiver

by

#### Yi-Hsuan Shih

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Vladimir Stojanovic, Co-Chair

Professor Borivoje Nikolic, Co-Chair

With increasing demands in AI and MIMO systems, wireline link speeds have surged beyond 100Gbps, intensifying inter-symbol interference (ISI), and challenging traditional feedback-based equalization techniques like decision feedback equalizers (DFE) due to timing constraints. To overcome feedback loop limitations, feedforward MLSE was proposed, avoiding complex feedback but still introducing significant computational complexity.

This thesis presents a new hybrid clock data recovery algorithm (CDR) that leverages the complexity of the feedforward MLSE to improve the CDR locking performance and robustness to channel variations. Our approach combines the Mueller-Muller algorithm with a data-level maximization algorithm, achieving baud-rate CDR locking with reduced hardware overhead and steady-state stability without additional dithering.

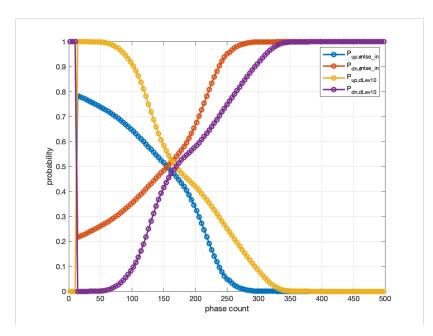

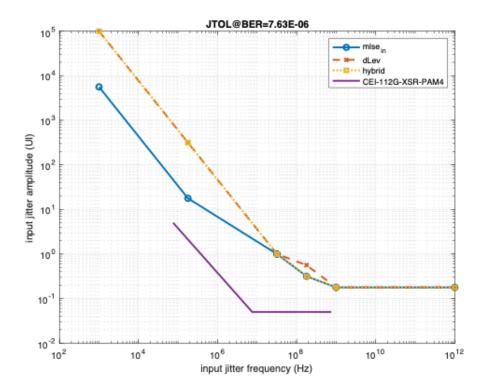

An evaluation framework is developed to compare various CDR algorithms (Mueller-Muller, dLev maximization, and hybrid CDR) in terms of locking position and steady-state jitter by Markov chain analysis. The results indicate that hybrid CDR outperforms in locking accuracy and jitter resilience.

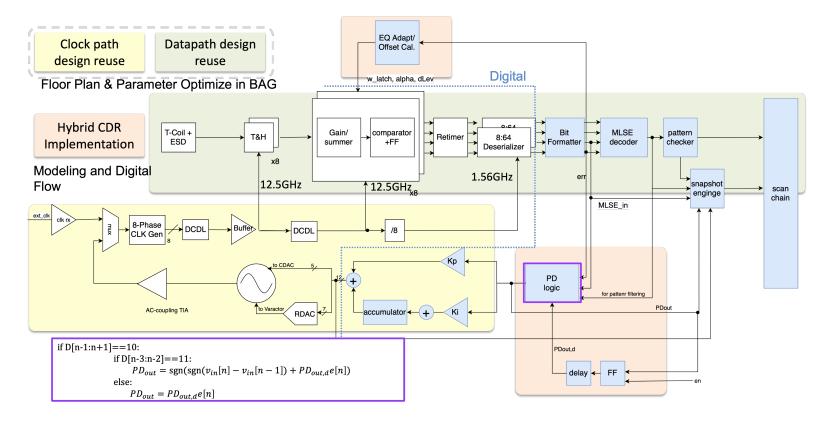

Our hybrid CDR, implemented in 16nm technology node, includes an innovative octature generator with an injection-locked oscillator for clock distribution. Verification using a digital SystemVerilog environment improves simulation accuracy and reduces overall verification time for the receiver system.

To my family

# Contents

| Co | onter                                          | nts                                                                                                                                                                                             | ii                                     |

|----|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Li | $\mathbf{st}$ of                               | Figures                                                                                                                                                                                         | iv                                     |

| Li | $\operatorname{st}$ of                         | Tables                                                                                                                                                                                          | viii                                   |

| 1  | Intr<br>1.1<br>1.2                             | Poduction  Background                                                                                                                                                                           | 1<br>1<br>10                           |

| 2  | Clo<br>2.1<br>2.2<br>2.3                       | ck Generation and Distribution for 100+ Gb/s Transmitter Clock Path Overview                                                                                                                    | 12<br>12<br>16<br>35                   |

| 3  | ML<br>3.1<br>3.2<br>3.3                        | SE and CDR Overview  Inter-symbol Interference (ISI) and Equalization                                                                                                                           | 42<br>42<br>50<br>56                   |

| 4  | Star<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | tistical Analysis of the CDR Algorithm  Overview  Mueller-Muller $mlse_{in}$ update Analysis  Data level (dLev) Maximization Analysis  Hybrid Algorithm Analysis  Performance Matrices  Summary | 63<br>63<br>66<br>70<br>71<br>87<br>91 |

| 5  | Des 5.1 5.2                                    | ign of 100Gb/s 1-Tap MLSE Receiver with Baud-rate CDR  Overview                                                                                                                                 | 92<br>92<br>93                         |

| 6            | Inte  | gration and Verification of 100 Gb/s 1-Tap MLSE Receiver with |     |

|--------------|-------|---------------------------------------------------------------|-----|

|              | Bau   | d-rate CDR                                                    | 110 |

|              | 6.1   | Integration                                                   | 110 |

|              | 6.2   | Verification                                                  | 112 |

|              | 6.3   | Testing                                                       | 117 |

|              | 6.4   | Performance                                                   | 124 |

| 7            | Con   | clusions                                                      | 126 |

|              | 7.1   | Thesis Summary                                                | 126 |

|              |       | Future Works                                                  |     |

| Bi           | bliog | raphy                                                         | 128 |

| $\mathbf{A}$ | Sing  | gle Variable Markov Chain Analysis for Hybrid Algorithm       | 132 |

|              | A.1   | Transition Probability Derivation                             | 132 |

|              | A.2   | 3-state Markov Chain Transition Matrix                        | 133 |

| В            | Driv  | ver Model and Channel Fitting                                 | 137 |

# List of Figures

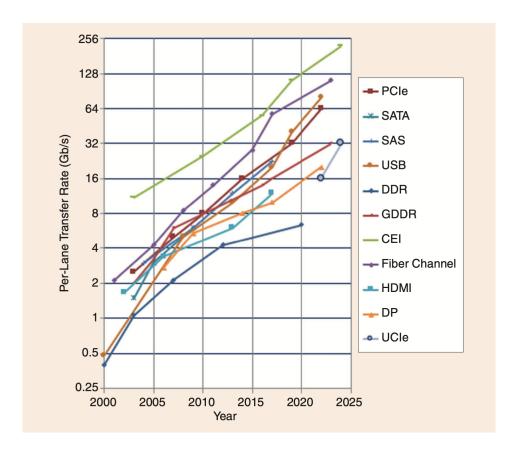

| 1.1  | Per-lane data rate vs. year for a variety of common I/O standards[34] |  |  |  |  |

|------|-----------------------------------------------------------------------|--|--|--|--|

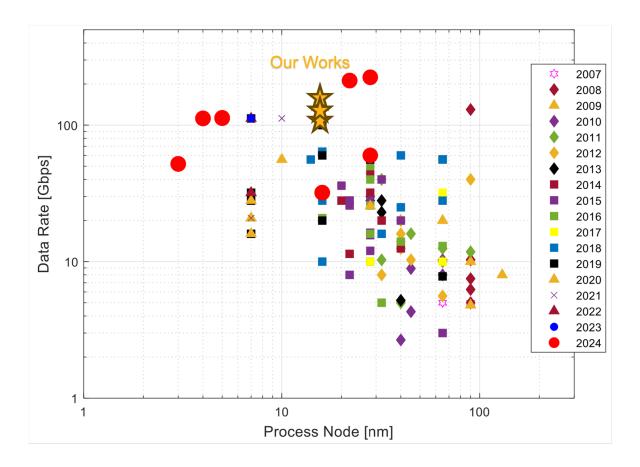

| 1.2  | Wireline data-rate trend[34]                                          |  |  |  |  |

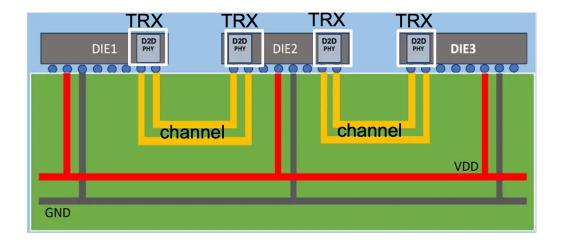

| 1.3  | Die-to-die communication [25]                                         |  |  |  |  |

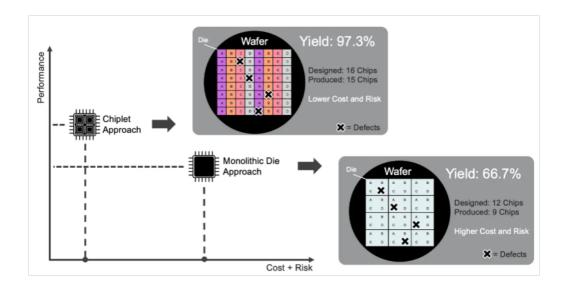

| 1.4  | Monolithic die vs. chiplet [25]                                       |  |  |  |  |

| 1.5  | Examples of chiplet design                                            |  |  |  |  |

| 1.6  | High-speed link block diagram                                         |  |  |  |  |

| 1.7  | IEEE P802.3ba 8dB nAUI channel characteristics [19]                   |  |  |  |  |

| 1.8  | Comparisons of different signaling schemes [33]                       |  |  |  |  |

| 1.9  | Structures of commonly used equalizers                                |  |  |  |  |

| 1.10 | Project development                                                   |  |  |  |  |

| 2.1  | Clock distribution                                                    |  |  |  |  |

| 2.1  | 160GHz transceiver clock path                                         |  |  |  |  |

| 2.3  | •                                                                     |  |  |  |  |

| 2.3  | 128GHz receiver clock path                                            |  |  |  |  |

| 2.4  | <b>-</b>                                                              |  |  |  |  |

| 2.6  |                                                                       |  |  |  |  |

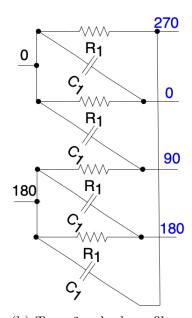

| 2.7  | Polyphase filter for octature clock generation                        |  |  |  |  |

| 2.1  | Schematic simulation of polyphase filter octature clock generation    |  |  |  |  |

| 2.9  | Two rings oscillate independently                                     |  |  |  |  |

| 2.9  |                                                                       |  |  |  |  |

| 2.10 | ring oscillator                                                       |  |  |  |  |

| _    | Quadrature corrector                                                  |  |  |  |  |

|      |                                                                       |  |  |  |  |

|      |                                                                       |  |  |  |  |

|      | 8                                                                     |  |  |  |  |

|      |                                                                       |  |  |  |  |

|      | v                                                                     |  |  |  |  |

|      | Current DAC structures                                                |  |  |  |  |

|      | Current and delay line branches                                       |  |  |  |  |

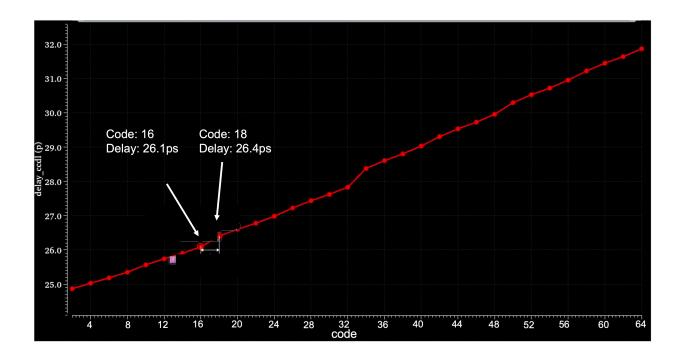

|      | Current dac code vs. delay                                            |  |  |  |  |

|      | Global buffer schematic                                               |  |  |  |  |

|      | One pair of CCDL and global buffer                                    |  |  |  |  |

| 2.21 | Quadrature divider schematic                                          |  |  |  |  |

| 2.22 $C^2MOS$ latch schematic and floorplan.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37<br>38<br>39<br>39<br>40<br>41                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

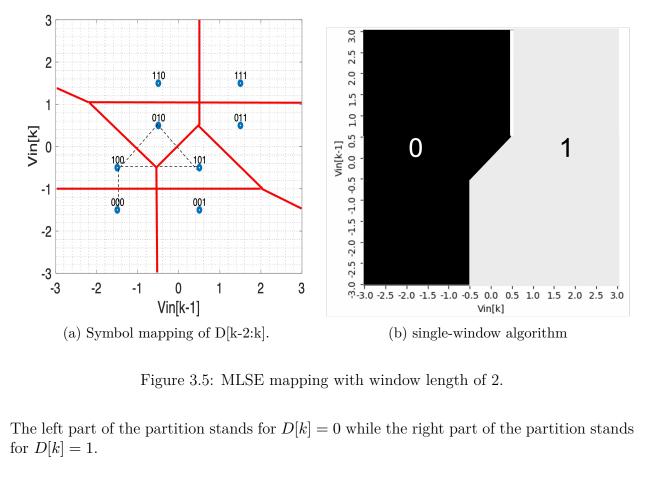

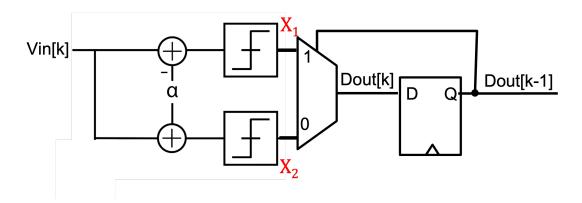

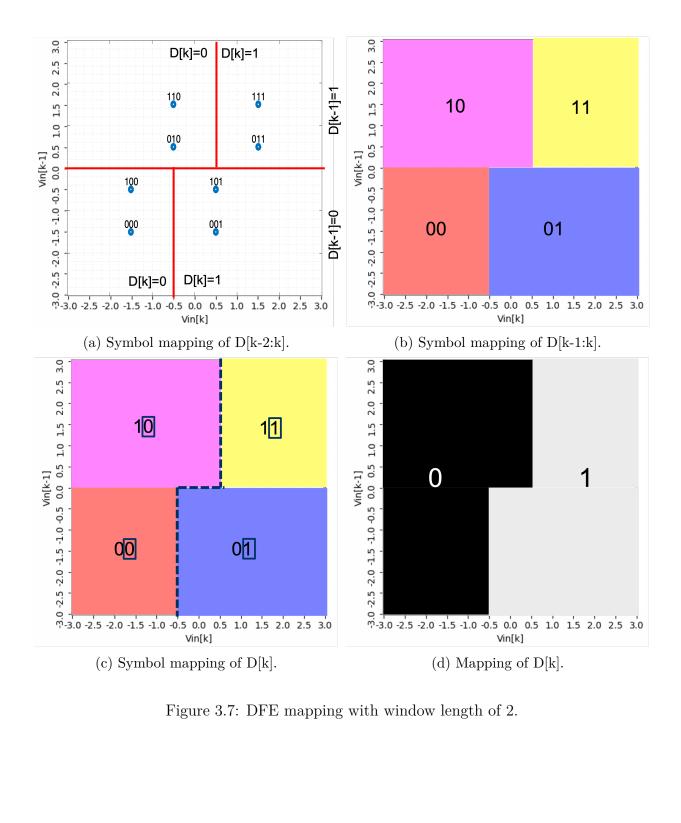

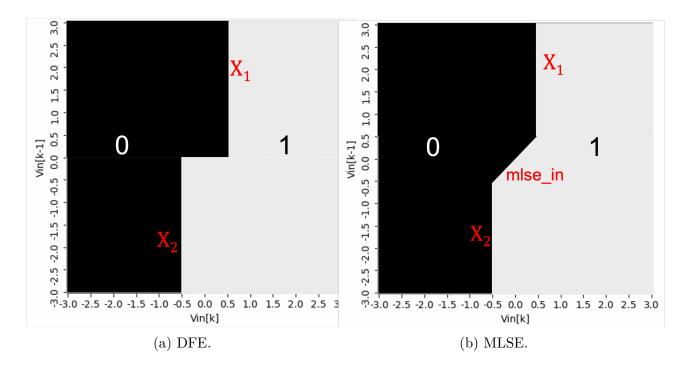

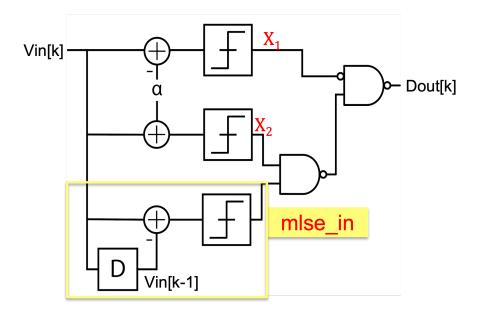

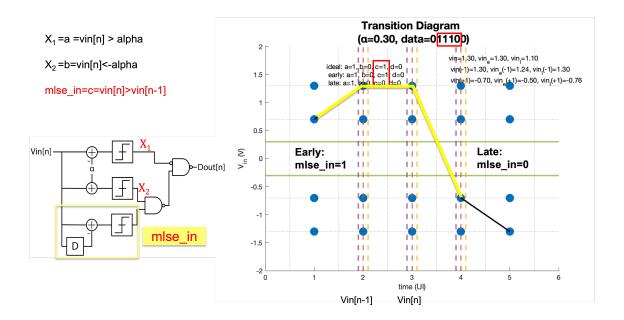

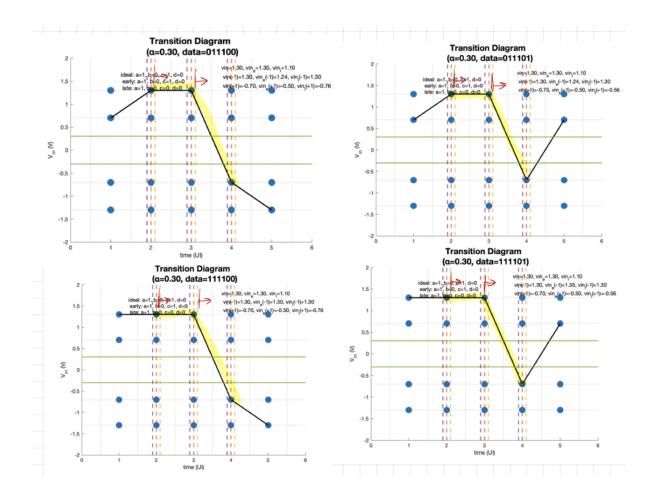

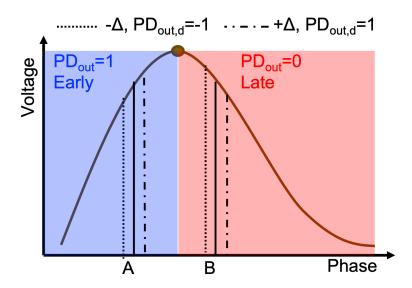

| 3.1 High-speed link block diagram[25]. 3.2 High-speed link with low-pass channel. 3.3 High-speed link with equalizer. 3.4 MLSE illustration. 3.5 MLSE mapping with window length of 2. 3.6 DFE circuit implementation. 3.7 DFE mapping with window length of 2. 3.8 DFE/ MLSE mapping. 3.9 MLSE circuit implementation (adapted from Figure. 2.14 in [31]). 3.10 Function of the CDR. 3.11 Type A Muller-Mueller CDR. 3.12 Transition diagram analysis for 011100 pattern. 3.13 Pattern filtering of 1110 for mlse_in-update. 3.14 dLev maximization illustration (adapted from Figure. 4.5(a) in [26]). 3.15 Integrated loopback pulse response. 3.16 Sweeping of timing function. | 42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>51<br>52<br>53<br>57<br>58<br>60<br>61<br>62 |

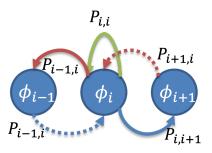

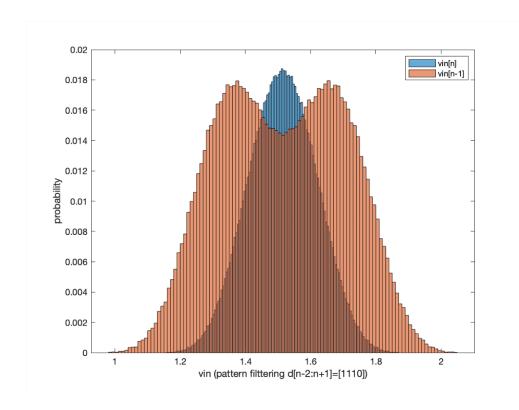

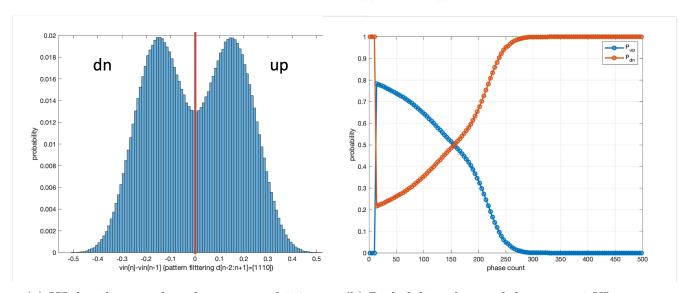

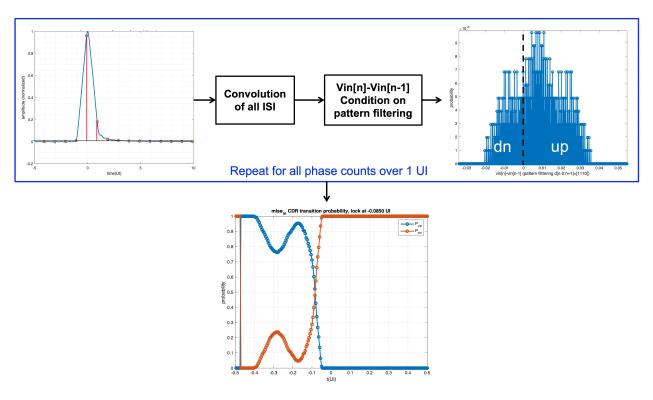

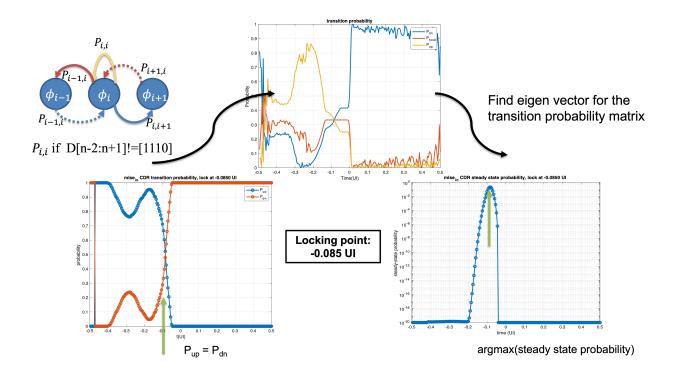

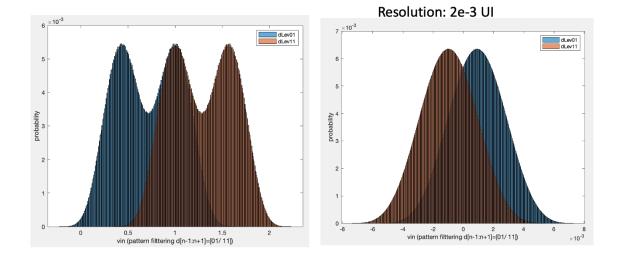

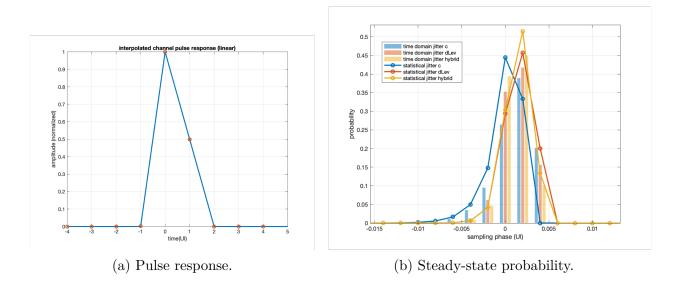

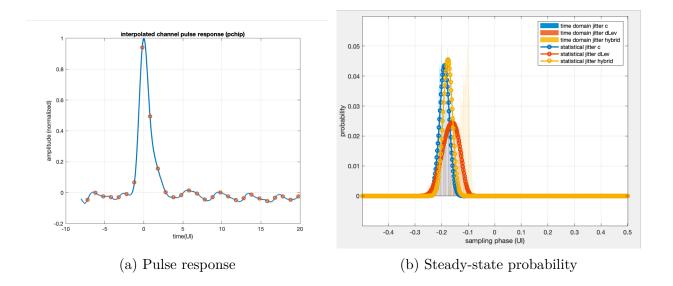

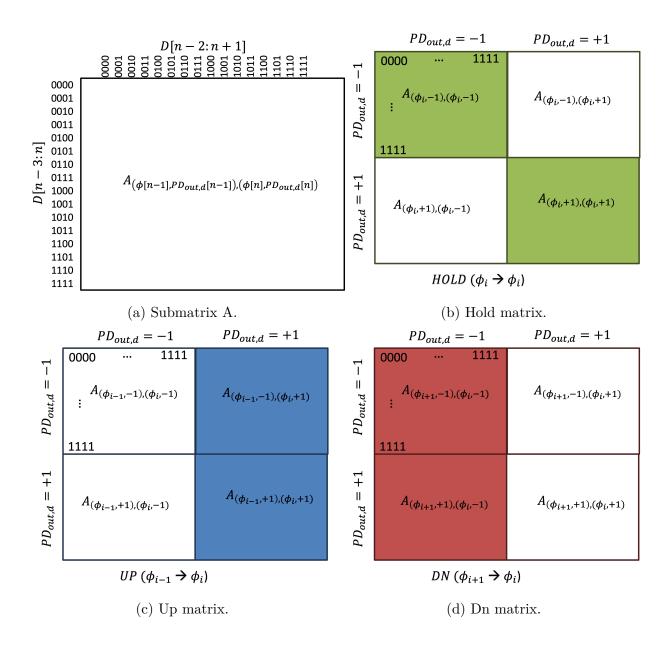

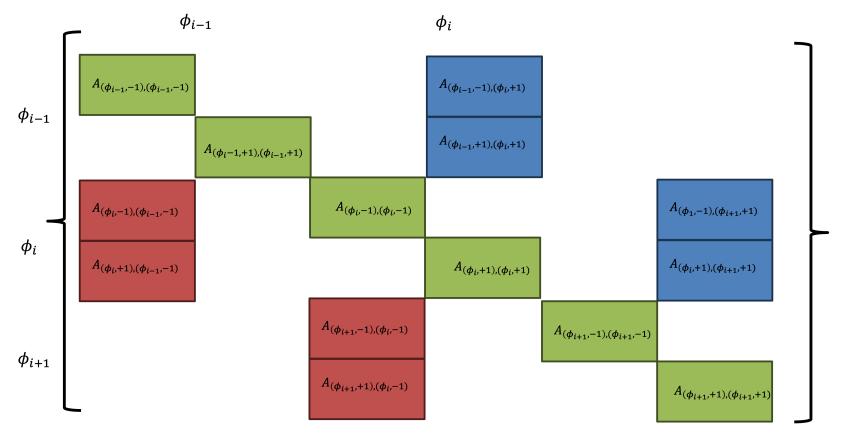

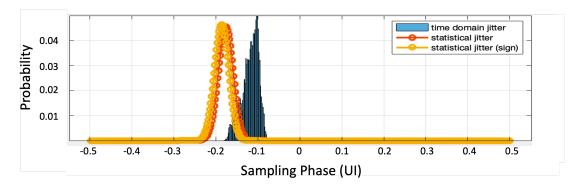

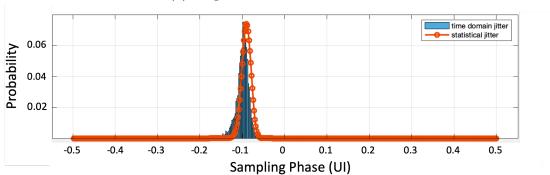

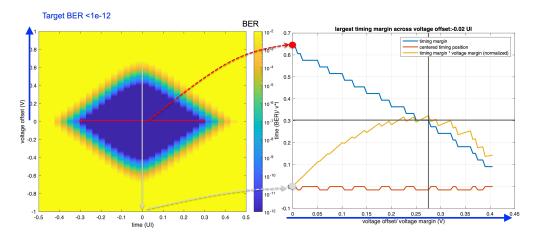

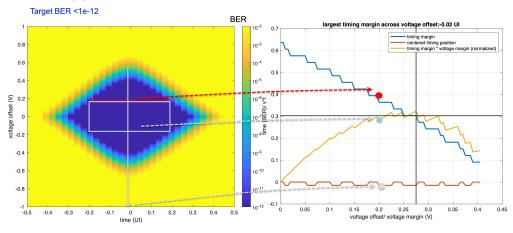

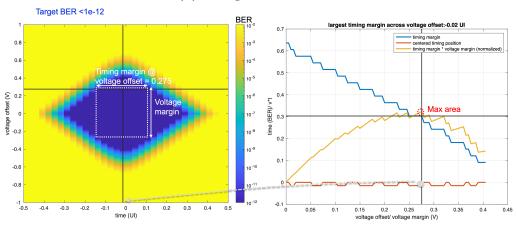

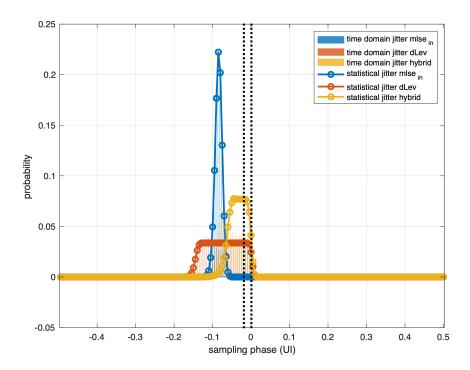

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65<br>67<br>67<br>68<br>69<br>71<br>72<br>76<br>77<br>79<br>80<br>86<br>88                   |

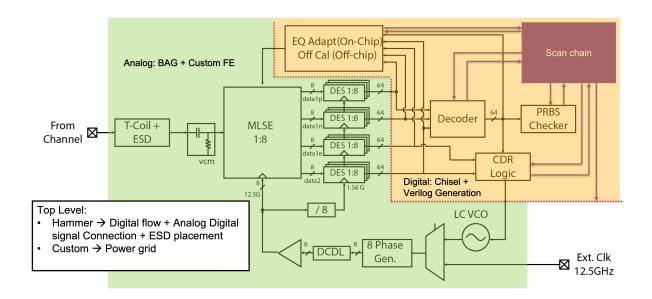

| 5.1  | Block diagram of the receiver                               |

|------|-------------------------------------------------------------|

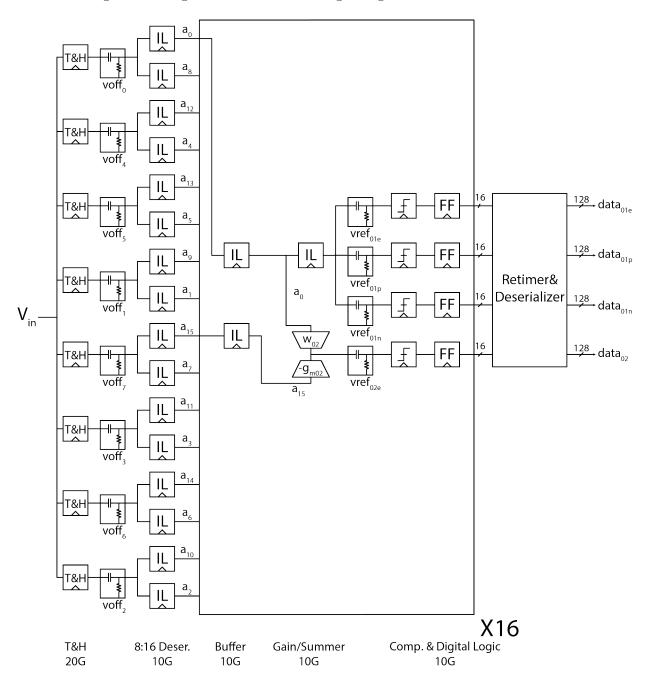

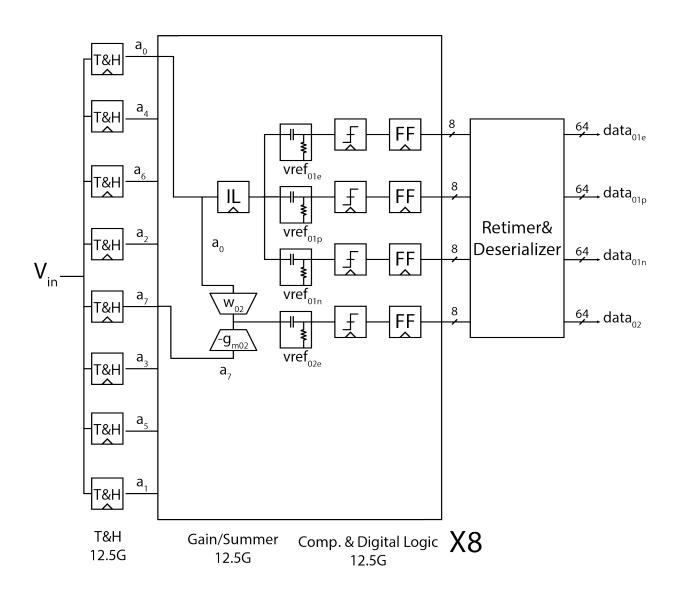

| 5.2  | 160Gbps receiver[31] analog datapath block diagram          |

| 5.3  | 100Gbps receiver analog datapath block diagram              |

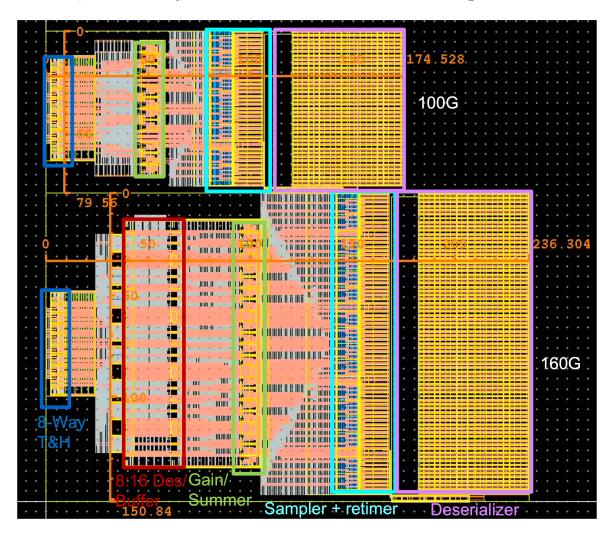

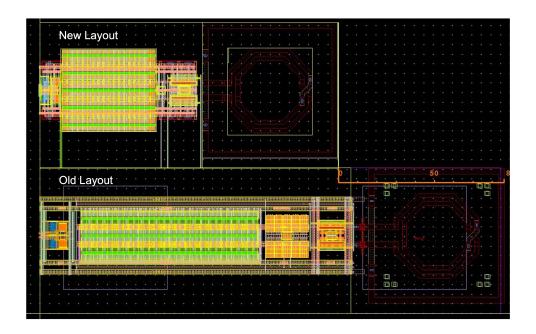

| 5.4  | 160Gbps vs. 100Gbps MLSE analog datapath layout comparison  |

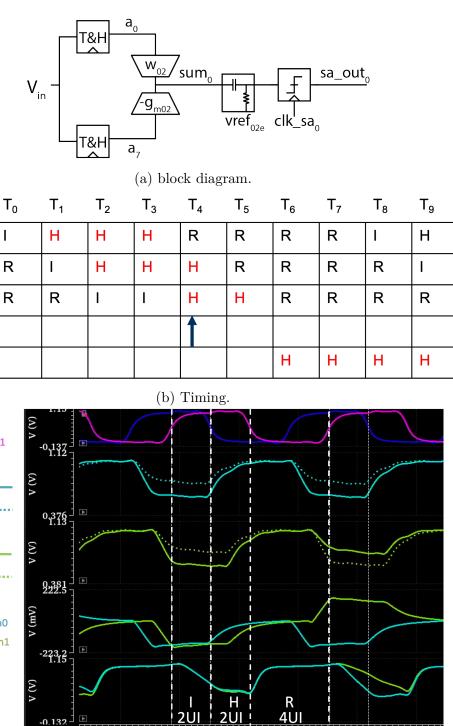

| 5.5  | Summer schematic and 160 Gbps waveforms                     |

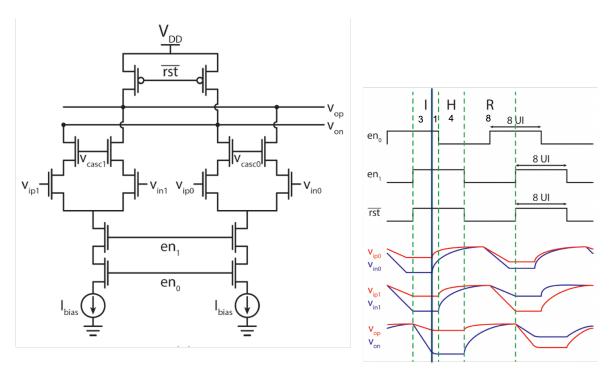

| 5.6  | Summer path and its timing                                  |

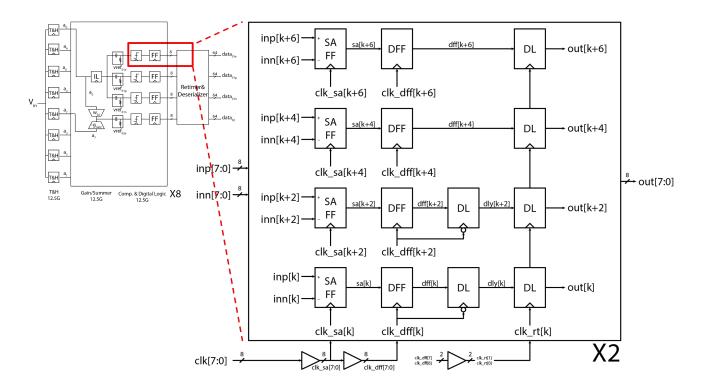

| 5.7  | Sampler and retimer                                         |

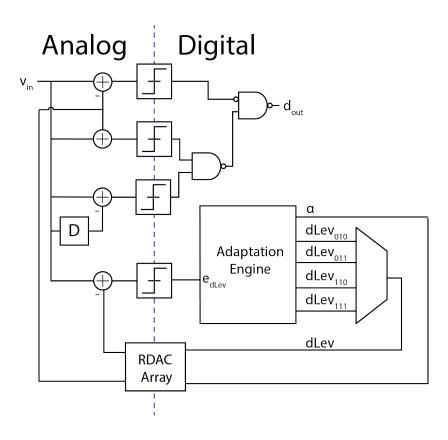

| 5.8  | Adaptation Loop                                             |

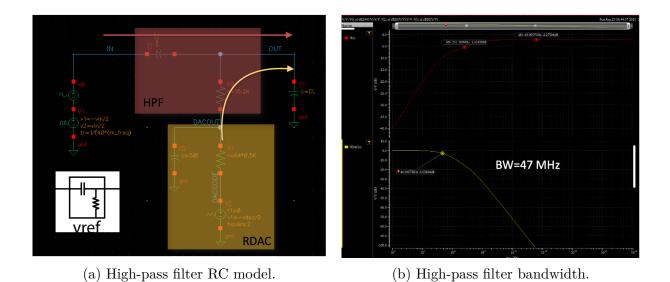

| 5.9  | Pole introduced by RDAC                                     |

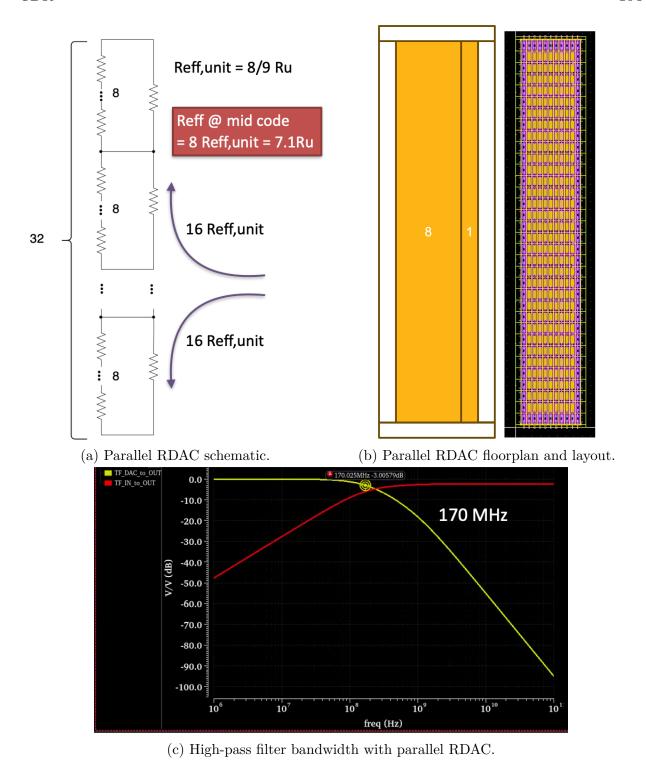

| 5.10 | Parallel RDAC                                               |

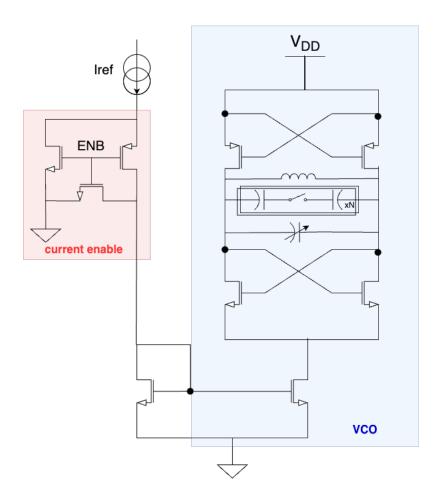

| 5.11 | Schematic of VCO                                            |

| 5.12 | Layout of VCO                                               |

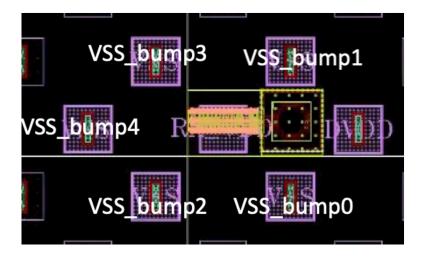

| 5.13 | VCO placement with C4 bump                                  |

| 5.14 | Block Diagram of CDR digital backend                        |

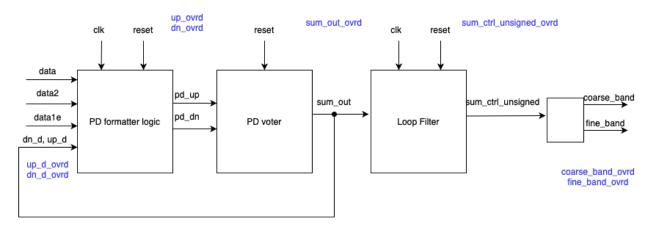

| 5.15 | Block diagram of CDR loop                                   |

| 0.1  |                                                             |

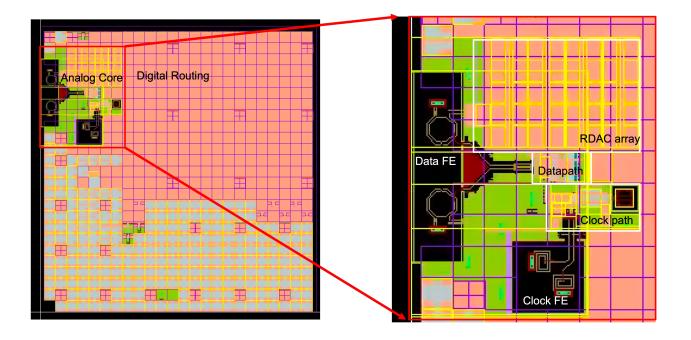

| 6.1  | Top-level integration flow                                  |

| 6.2  | Top-level layout integration                                |

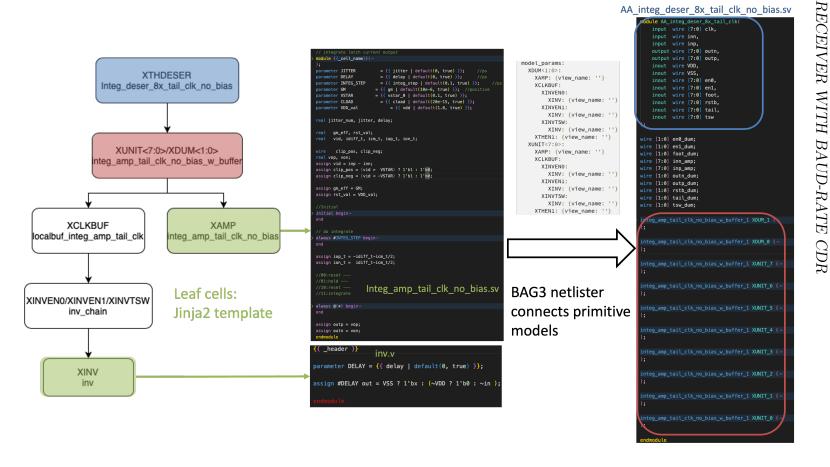

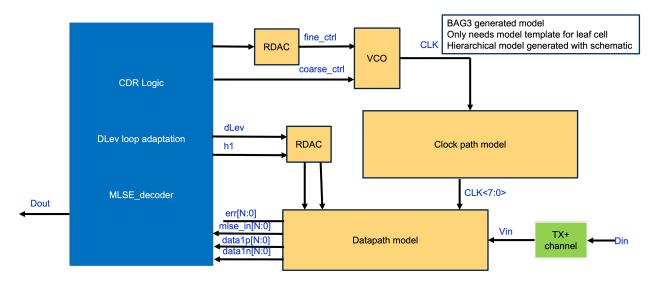

| 6.3  | Hierarchical behavioral model generation                    |

| 6.4  | Event driven SystemVerilog testbench                        |

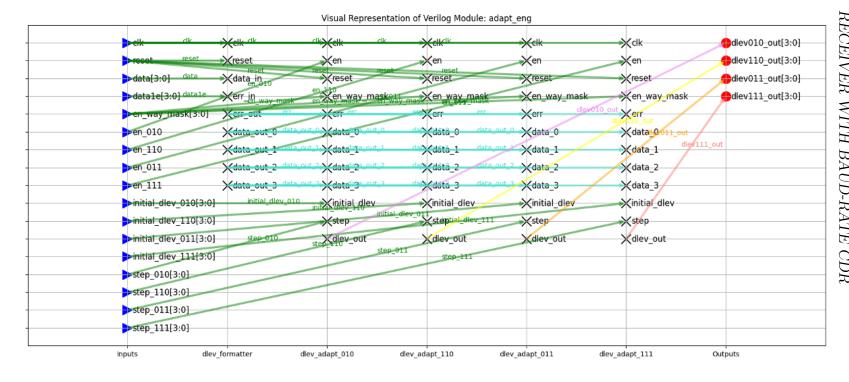

| 6.5  | Adaptation engine visualization                             |

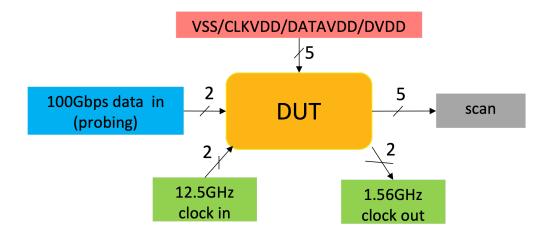

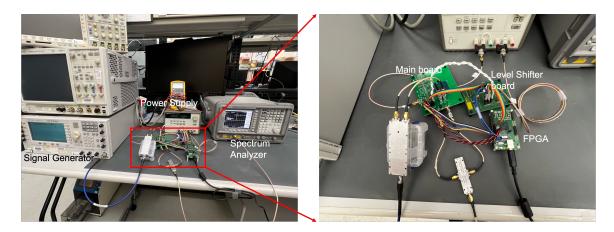

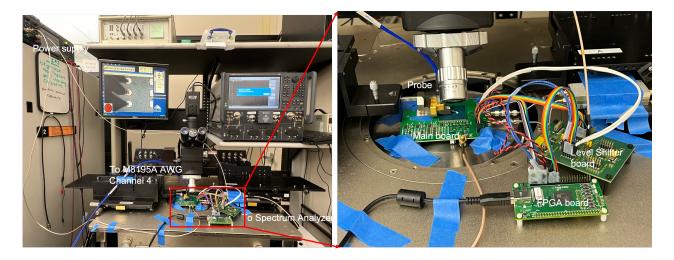

| 6.6  | Testing setup                                               |

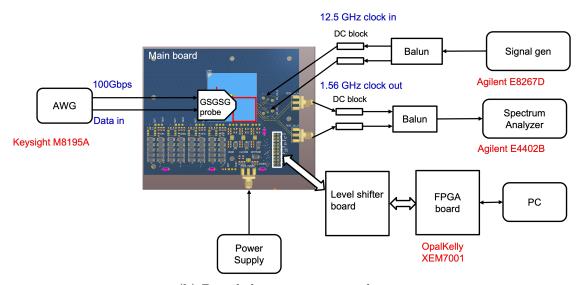

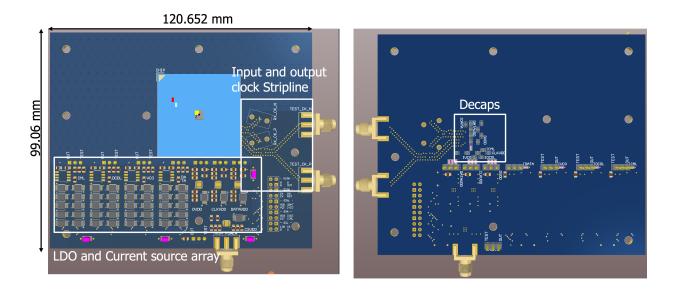

| 6.7  | Top view and bottom view of PCB                             |

| 6.8  | 6-layer PCB stack-up                                        |

| 6.9  | Testing setup for clock path                                |

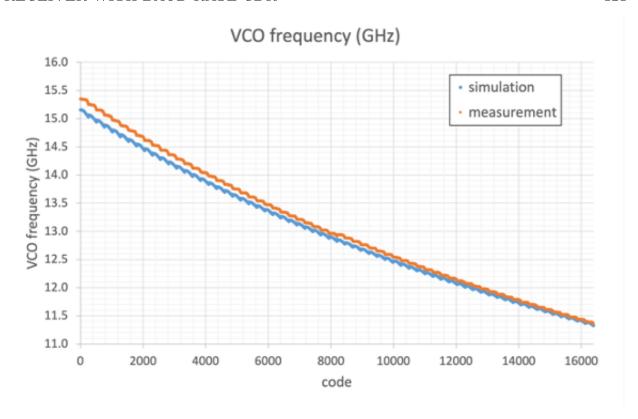

| 6.10 | VCO measurement results                                     |

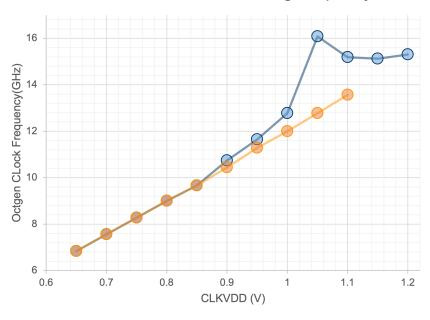

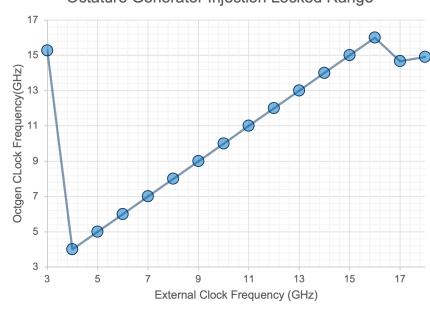

| 6.11 | Octature generator measurement                              |

| 6.12 | Testing setup with probe station                            |

| Λ 1  | 3-state Markov chain                                        |

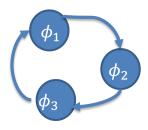

| A.1  | 3-state Markov chain                                        |

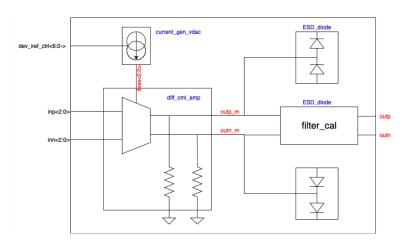

| B.1  | CML driver schematics                                       |

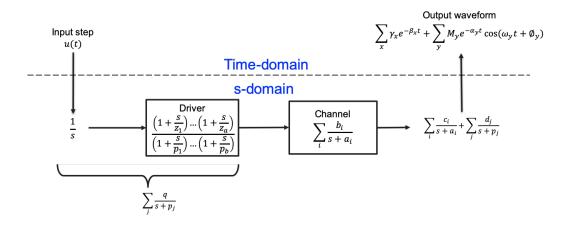

| B.2  | Overall modeling steps                                      |

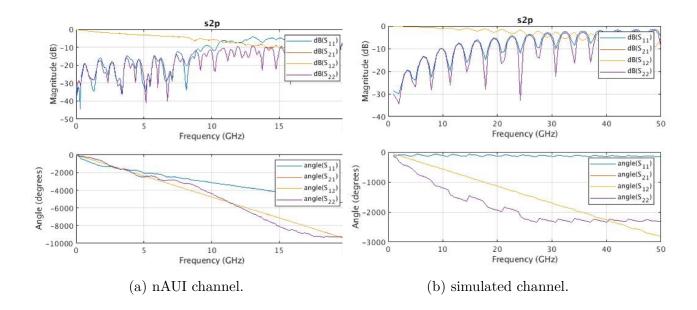

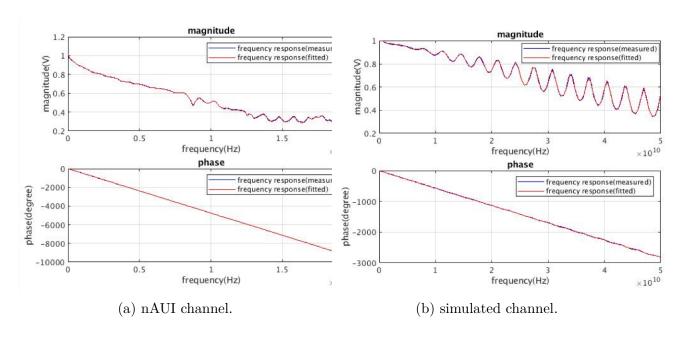

| В.3  | s-parmeter of channels                                      |

| B.4  | Transfer functions derived from s-parameters                |

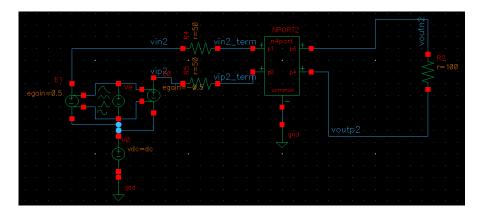

| B.5  | Testbench for pulse and step response simulation in Cadence |

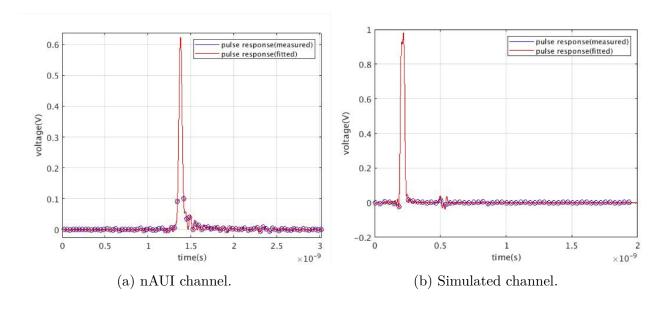

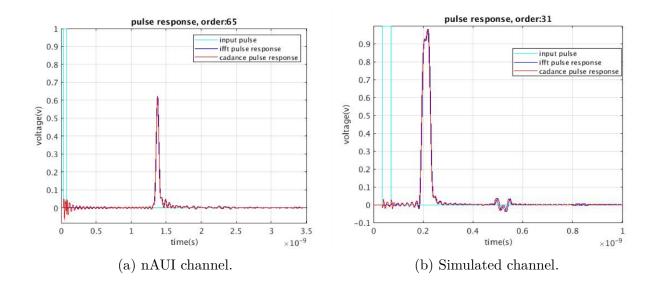

| B.6  | Pulse response: data rate = $28$ GHz                        |

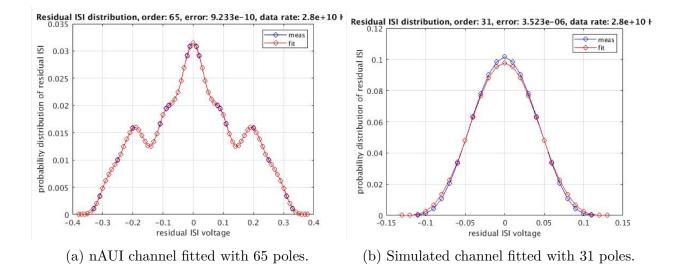

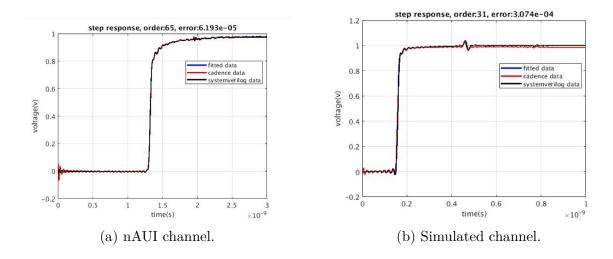

| B.7  | Comparison of pulse response                                |

| B.8  | Residual ISI distribution                                   |

| B.9  | Step response                                               |

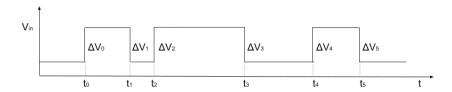

|      | Timing diagram of input signal                              |

|      | Block diagram                                               |

|      |                                                             |

| vii |

|-----|

|     |

| B.12 Tx datapath simulation |  | 146 |

|-----------------------------|--|-----|

|-----------------------------|--|-----|

# List of Tables

| 1.1 | Project information and contributors                                  | 1  |

|-----|-----------------------------------------------------------------------|----|

| 2.1 | 25GHz octature clocks performance (simulation)                        | 29 |

| 3.1 | RX equalizer comparison table                                         | 4  |

| 3.2 | TX output and RX input mapping                                        | 4( |

| 3.3 | Truth table for MLSE decoder                                          | 5( |

| 3.4 | Truth table of dLev maximization (adapted from Figure. 4.5(b) in [26] | 6( |

| 3.5 | Table of sweeping of timing function                                  | 62 |

| 4.1 | Sample space of $PD_{out}$                                            | 64 |

| 4.2 | Sample space of $PD_{out}$                                            | 73 |

| 6.1 | Power breakdown (simulation)                                          | 2  |

| 6.2 | Bandwidth power efficiency (simulation)                               | 2! |

| 6.3 | Performance comparison table                                          | 2! |

#### Acknowledgments

I feel deeply fortunate to have had the opportunity to pursue my PhD at University of California, Berkeley and conduct research in Berkeley Wireless Research Center (BWRC). This has been a long and challenging journey, but I have been lucky to receive the guidance and support of exceptional faculty and talented peers.

First and foremost, I would like to express my sincere gratitude to my advisors, Professors Vladimir Stojanovic and Elad Alon. During the past few years, Professor Vladimir helped me learn to see the whole picture and think from a system perspective technically. I learned from him how to manage the research and tape-outs strategically, especially when the system is too large for a single individual. I am really grateful that he always motivated me and recognized the value of my work. He has been supportive not only in my research but also in the challenges that I face in life. I cannot thank Professor Vladimir enough for his warm support and understanding during my most difficult times. Professor Elad introduced me to the world of high-speed wireline links and guided me through the initial phase of exploring the field and defining my own research topics. He always provided guidance with his sharp intuition for circuits and profound technical understanding whenever I felt stuck.

I also thank Professors Borivoje Nikolic and Martin White for serving on my qualifying exam and dissertation committees. I am grateful for their invaluable feedback and guidance on my research. I greatly appreciate Professor Bora's technical advice, which significantly improved the quality of my dissertation.

I would like to extend my appreciation to Farhana Sheikh and Intel's University Shuttle Program for granting me the opportunity to implement my research work in advanced technology nodes.

During the PhD journey, I am grateful to have met and learned from many brilliant people. I would like to especially thank Paul Kown, Ayan Biswas, Wahid Rahman, Kunmo Kim for working together as a team during multiple tape-outs. I would also like to thank Zhongkai Wang, Bob Zhou, Zhaokai Liu, Kwanseo Park, Zhenghan Lin, Yikuan Chen, Yu-Chi Lin, Hesham Beshary, Rohit Braganza for their tape-out and testing assistance. My sincere thanks also go to Rebekah Zhao, Yue Dai, Meng Wei, Rozhan Rabbani, Bozhi Yin, Ruocheng Wang for their friendship that made my graduate life more colorful. A special thanks to the BWRC staff and EECS department staff for their support.

Last but not least, I owe my deepest thanks to my family for their unwavering love, patience, and encouragement throughout my life. Their belief in me has been the foundation that supports me through the tough PhD life. Without them, I could not have navigated the challenges in my journey.

# Chapter 1

## Introduction

### 1.1 Background

Today, data are being created and transmitted on a massive level as a huge wave of connectivity everywhere through a multitude of modern devices such as wearables, smart home appliances, connected cars, medical devices, fitness bands, etc. Furthermore, the surge of artificial intelligence (AI) requires high computational power, which requires integration and cooperation between multiple chips.

Among these explosive growing connections, high-speed links have been widely used to provide wide-bandwidth wireline connectivity on various scales, ranging from on-chip to chip-to-chip and system-to-system interconnects. The data rate of the common I/O standards is shown in Figure. 1.1 reflects the constantly increasing demand for a higher data rate in recent years. Most recent publications in the wireline domain focus on data rates exceeding 100Gbps, reflecting this shift. However, achieving these rates presents challenges. Data rate capabilities are restricted not only by the process node but also by packaging constraints, which can limit performance and reliability. Our research group is addressing these challenges by targeting 100Gbps, 128Gbps, and 160Gbps designs by using a 16-nm process node to meet this demand.

In contrast to this rapid increase in bandwidth, the power consumption becomes the bottleneck to overcome due to the severe thermal restrictions of the entire system. In the vision for the future technology stated in the IRDS roadmap [22], it is expected that the power consumption of communication and routing will be reduced by a factor of 10 while the data will increase by a factor of more than 10. Therefore, the energy efficiency of high-speed links should be constantly improved as the data rate increases. While the bandwidth and power constraints are very challenging by themselves, to make matters worse, the scaling of the CMOS process is slowing down and the performance gain from scaling is not as dramatic as in the past. Therefore, innovative design techniques that push the limits of electrical signaling are essential to meet those bandwidth and energy efficiency goals in advanced CMOS processes.

Figure 1.1: Per-lane data rate vs. year for a variety of common I/O standards[34].

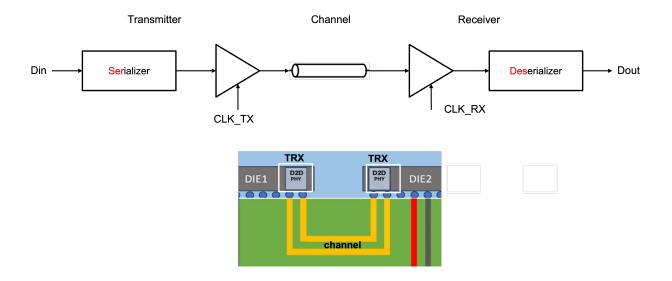

The chiplet is a way to implement a system-in-package (SIP) [46] design, using a modular approach that partitions functional blocks into different dies and connects them with a standardized interface, i.e., die-to-die communication. Shown in Figure. 1.1, Universal Chiplet Interconnect Express (UCIe) [45][36][44], is an open industry standard developed to establish a ubiquitous interconnect at the package level and covers the die-to-die I/O physical layer. Instead of having a large monolithic die that includes all functions of the system, we can use several small dies that perform different functions and connect them together in the package. Shown in Figure. 1.3, the die-to-die communication includes the transceiver (TRX) on each die and the connection (channel) between the dies. In this way, the area of the individual die is reduced so that the yield can be improved with similar defect rates, ultimately lowering the cost (Figure. 1.4).

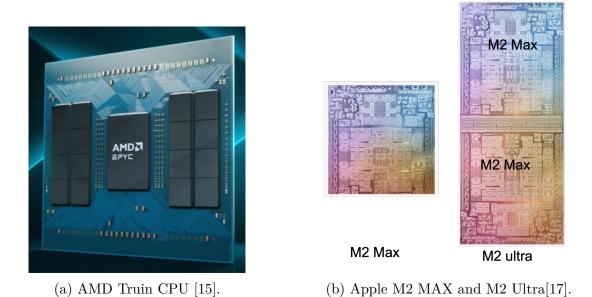

The AMD EPYC CPU[15] for the data center and the Apple M2[17] ultra for the Mac Studio laptop are the real-world example of the chiplet implementation (Figure. 1.5). 192 cores and 384 threads are enabled by 16 CPU dies and 1 IO die connected with Infinity fabric packaging in Turin CPUs ( $5^{th}$  Gen EPYC). The Apple M2 Ultra SoC is built with an UltraFusion silicon interposer packaging architecture to connect the die of two M2 Max

Figure 1.2: Wireline data-rate trend[34].

Figure 1.3: Die-to-die communication [25].

Figure 1.4: Monolithic die vs. chiplet [25].

chips to achieve twice the performance of one M2 Max chip.

Figure 1.5: Examples of chiplet design

Another example is high-performance computing (HPC). It offers reduced power consumption by connecting the compute node via 112GT/s, 1mm reach, and 1pJ/bit XSR standard electrical link within the electro-optic engine for HPC [22].

#### Wireline Transceiver

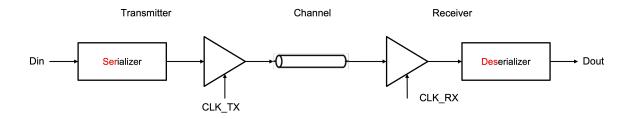

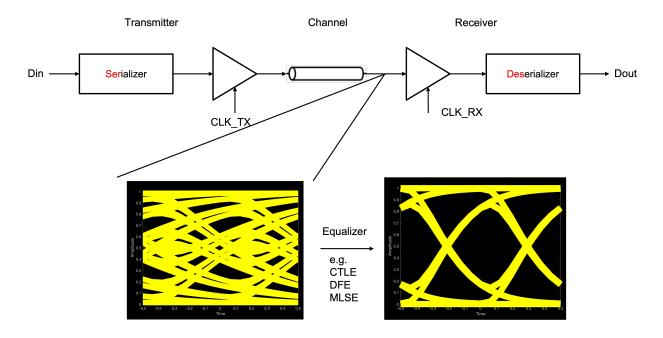

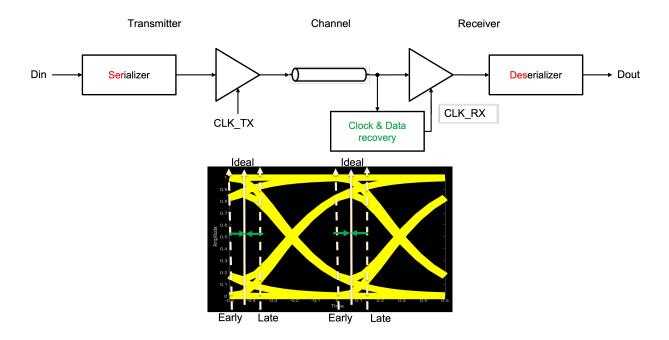

Figure 1.6: High-speed link block diagram.

A typical high-speed link is shown in Figure 1.6, consisting of transmitter and receiver circuits and the wire as a channel. At high speeds (> 3Gb/s), the bandwidth of the wire begins to limit the operating speed of the electric links [42]. Equalization techniques have been developed to compensate for the low-pass filtering effect of the channel (Figure 1.7). Multi-level signaling schemes are also proposed for higher throughput at the same bandwidth. Timing in the receiver is especially important to sample the data correctly in terms of frequency and phase.

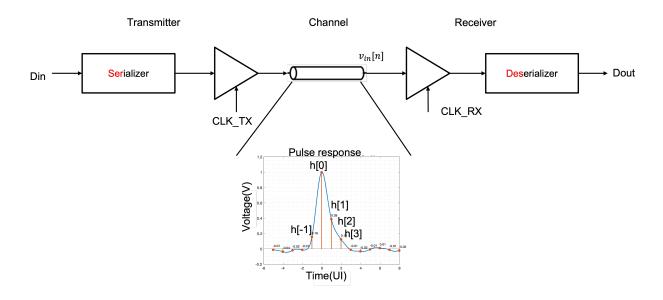

#### Link Environment: Channel

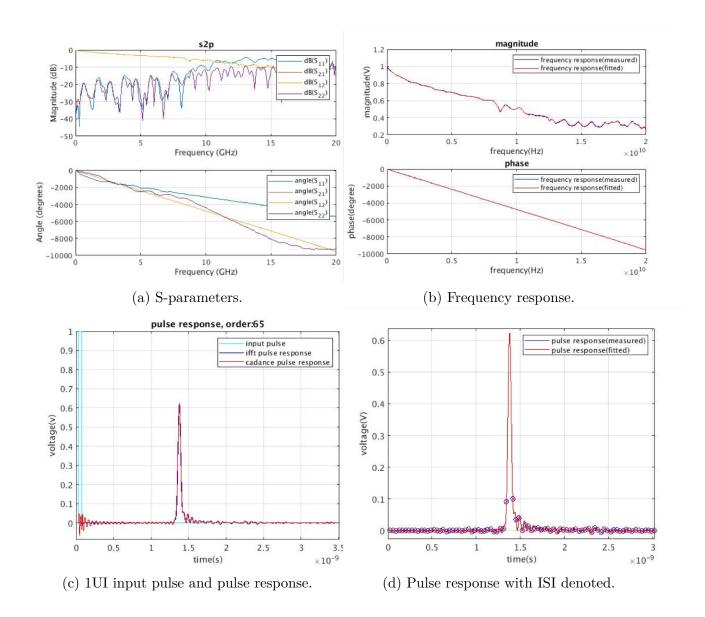

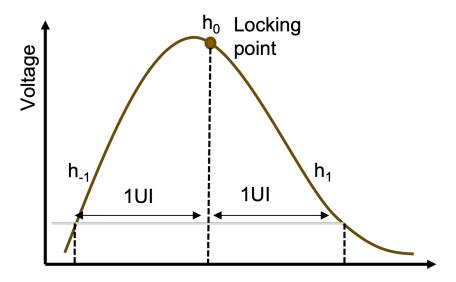

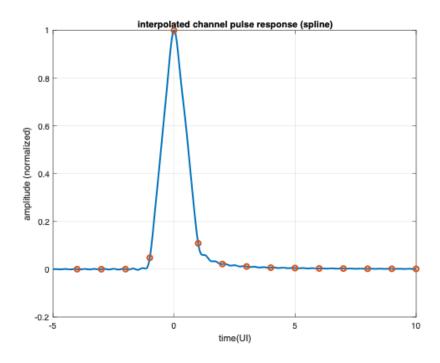

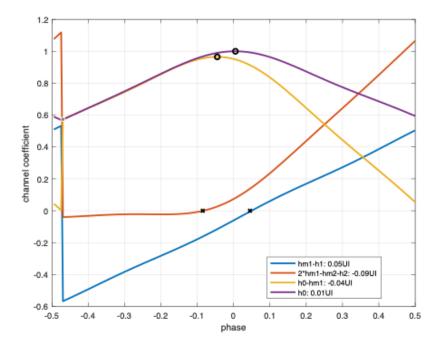

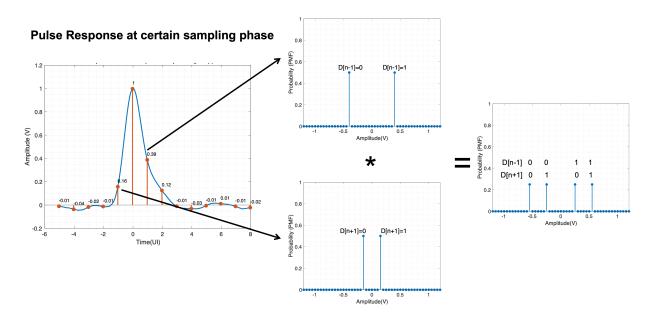

As the data rate reaches the 10Gb+/s range specified by the per-lane transfer rate of UCIe, the non-ideality caused by the channel has become a critical issue for signal integrity. A typical channel characteristic is shown in Figure 1.7 [19]). The channel is usually characterized as the s parameter (Figure. 1.7a). S21 or the corresponding frequency response shows the low-pass feature with notches at some frequencies in Figure. 1.7b. The notch and highly reflective transients in the pulse response could be generated from impedance discontinuities in complex PCB structures, such as packages and connectors. The corresponding time-domain pulse response is obtained from passing a 1 UI (unit interval, i.e. 1/data rate) square pulse as input to the channel. With low-pass characteristics, the pulse response has a lower peak amplitude and spread wider than 1UI (Figure. 1.7c. The inter-symbol interference (ISI) is the value measured in time that space nUI (n is nonzero integer) from the peak and are denoted in Figure. 1.7d.

#### Signaling: Signaling Scheme and Equalizers

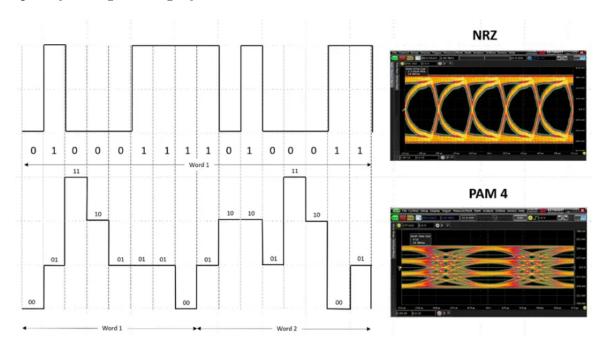

Non-return-to-zero (NRZ) is the intuitive and simple way to transmit the bit streams with two levels for 0 and 1 respectively. To increase spectral efficiency, complex modulation schemes, such as the Pulse Amplitude Modulation 4-level (PAM4) scheme, have been widely explored in recent transceiver designs to relax the baud rate requirements. In Figure. 1.8, the waveform of the ideal levels of PAM4 and NRZ with the input data streams is shown

Figure 1.7: IEEE P802.3ba 8dB nAUI channel characteristics [19].

on the left, while the corresponding eye diagram is shown on the right. Although PAM4 transceivers are capable of handling high-loss channels, most PAM4 designs require error coding and/or complex digital equalization due to a lower signal-to-noise ratio (SNR) and a higher impact of residual ISI and nonlinearity on eye opening, which typically leads to their power consumption being higher than the Non-Return-to-Zero (NRZ) counterpart. For example, PCIe 6.0 required forward error correction (FEC) to compensate for the loss of 9.5 dB SNR due to the lower eye height (1/3 of the NRZ eye). For the XSR link, NRZ is often preferred for its simplicity and power efficiency, while PAM4 provides an option to

realize a higher date rate at the same bandwidth at the cost of increased power and design complexity for signal integrity issue.

Figure 1.8: Comparisons of different signaling schemes [33].

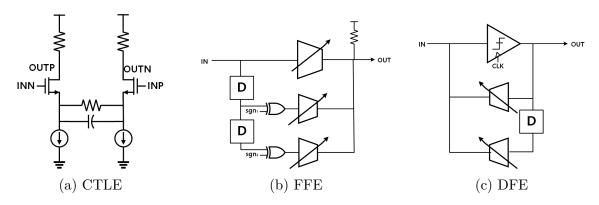

Significant ISI due to the channel effect contributes to higher bit error rates (BER). Equalizers in transmitter and/ or receiver are implemented to compensate ISI and meet the BER specs at high data rate. If the amount of channel loss remains within a reasonable range (<25dB for NRZ and <15dB for PAM4), which is the short-link case we are targeting, analog and mixed signal equalizers are preferred over digital approaches to address ISI. Conventionally, various analog and mixed-signal equalizers have been implemented, including continuous-time linear equalizers (CTLE), feedforward equalizers (FFE), and decision-feedback equalizers (DFE).

FFEs (Figure 1.9b) are often used to correct pre-cursor ISI and usually perform at the transmitter side of the mixed-signal based link for simplicity of implementation. Since the transmitter output power is limited, the summation of the FFE taps has to be fixed, and therefore the signal power is decreased. The reduced signal power will cause noise enhancement. Both DFE and CTLE are usually placed on the receiver side. DFE(Figure 1.9c) outperforms CTLE for canceling major post-cursor ISI near the main cursor since DFE summer taps do not have the linearity constraints present in CTLE, and are more tolerant to noise. Furthermore, adapting DFE taps for irregular pulse responses is easier than CTLE. CTLE(Figure 1.9a) is commonly placed in the first few stages at the receiver and configurable to cancel both pre-cursor and post-cursor ISI. CTLE uses frequency-dependent gain degradation of the common source (CS) amplifier to create peaking around the channel

bandwidth to extend the bandwidth. In contrast to the finite impulse response filter (FIR)-based FFEs and DFEs, CTLE serves as an infinite impulse response filter (IIR) and can be used for long-tail cancellations.

Figure 1.9: Structures of commonly used equalizers.

#### Timing: Clock and Data Recovery Circuits (CDRs)

To correctly decide the data transmitted on the receiver side, it is extremely important to sample at the correct timing, i.e., accurate spacing of transmitted data symbols and sampling of the signal waveforms at the receiver. Clock and data recovery (CDR) is used to recover the clock with the received data and align the recovered clock to the locking position decided by the CDR loop. The CDR loop compensates for the phase skew between the received signal and the receiver's internal clock, and filters out the input jitter which causes the sampling uncertainty at the sampler. This is the main topic we will focus on in the following chapters.

### Berkeley Analog Generator (BAG)

The wireline links used for different applications will have different specs to meet. Even developing a link with higher data rates based on existing links requires essential efforts to redesign each block and verify performance. The subtle change in the routing or via style can have a non-negligible degradation of performance. Thus, substantial layout iteration would be needed in the design process. To make matters worse, the design rule sets are more complicated in the advanced nodes, making the layout iteration more time consuming. These are the non-returning engineering (NRE) costs when the specs evolve. It is crucial to reduce design costs to increase profit margins for high volumes and enable custom design for low volumes.

Berkeley Analog Generator (BAG) [20] is an open-source hierarchical Python framework that allows the design procedure to be specified in executable manners. It defines and implements a process-portable interface to layout [29][2]. It has already been used mainly

for analog and mixed signal (AMS) layout automation [6][50]. BAG is a software wrapper for hardware design that focuses on reusing the unit design hierarchically instead of designing from scratch. Instead of doing manual layout with graphical polygons, circuit designers write executable generator in Python which capture designer's knowledge. In other words, the generator itself is an implementation of the circuit design methodology of designers.

The generator nomenclature is as follows:

#### • Schematic generator

Produces schematic/ netlist based on low-level parameters (width, length, number of finger, etc.)

#### • Layout generator

Produces DRC/ LVS clean layout based on low-level parameters (width, length, number of finger, etc.)

#### • Model generator

Produces SystemVerilog model based on low-level parameters, netlist of the schematic, and parameter characterized from the simulation (delay, rising time, falling time, setup time, hold time, etc.)

With generator-based design methodology, it can truly close the entire design loop from design (schematic and layout) to verification (behavioral model and testbench).

The other advantage of automatic layout is the manageable layout process in advanced technology and portability among different technologies. The design rules are different from technologies to technologies, which makes porting an existing design from one technology to another not a trivial work. In fact, the complex design rules of the FinFET process further reduce layout portability and increase the time required to port the design. Within the BAG framework, the complicated design rules, such as the quantized width and spacing of the metal in different layers, are parameterized and assigned to the technology files. In this way, circuit designers do not need to bother knowing each design rules and can easily port one design to different technology nodes. With BAG, productivity gains come from parameterization, incremental extension, and process portability.

### 1.2 Thesis Organization

There are a variety of data-rate target die-to-die XSR link projects included in the thesis. The main contributions in these projects are outlined in Figure. 1.10. The detailed information and contributors of the projects are listed in Table. 1.1

In Chapter 2, the clock path targeting multiple data-rate links has been explored. The building blocks of clock generation and distribution are explained. The reconfigurability of the generator-based design makes it possible to adopt a circuit topology similar to the different target data rates in short cycle time and resources.

Chapter 3 to 6 focus on the theory and implementation of the baud rate CDR algorithm. Chapter 3 starts with a review of the literature on the CDR algorithm and the theory of the hybrid CDR algorithm. Statistical analysis is used to evaluate the performance of the innovative CDR algorithm and also serves to compare with the state-of-the-art CDR algorithm. In Chapter 4, the focus is on the implementation of the hybrid CDR algorithm in the design of the 100Gbps XSR receiver. 200Gbps receiver in [31] is modified for the hybrid CDR proposed in Chapter 3. The change in the datapath and the clock path achieves a more compact design and lower power consumption. Next, Chapter 6 describes the integration flow of the 100Gpbs receiver with hybrid CDR design and the packaging, PCB design for the testing in lab. The testing setup and results are discussed at the end of Chapter 6.

Finally, Chapter 7 concludes the thesis with the summary and potential future work based on the proposed work.

#### 200Gbps TRX

- TX clock path

- · RX clock path

#### 160Gbps TRX

- TX clock path

- RX clock path

#### 100Gbps RX

- RX datapath

- datapath topology change

- on-chip dLev adaptation

- RX clock path

- hybrid CDR

- clockpath topology change

- RX digital

- hammer flow

- · Package design

- Integration and Verification

#### 128Gbps RX

- RX clockpath

- clock path optimization

Figure 1.10: Project development.

| Projects         | 200Gbps TRX                  | 160Gbps TRX                | 100Gbps RX                 | 128Gbps RX                   |           |

|------------------|------------------------------|----------------------------|----------------------------|------------------------------|-----------|

| Technology       | 22nm FinFET                  | 16nm FinFET                | 16nm FinFET                | 16nm FinFET                  |           |

| Taped out time   | 2021 Nov.                    | 2022 Aug.                  | 2023 Dec.                  | 2024 Nov.                    |           |

| TX datapath      | Ayan Biswas <sup>3</sup>     | Ayan Biswas <sup>3</sup>   | -                          | -                            |           |

| TX clock path    | Yi-Hsuan Shih <sup>1</sup> / | Yi-Hsuan Shih <sup>1</sup> | Vi Hayan Chih <sup>1</sup> |                              |           |

| 1 A Clock path   | Wahid Rahman                 | i i-iisuan siiii           | _                          | -                            |           |

| RX datapath      | Paul Kwon <sup>4</sup>       | Paul Kwon <sup>4</sup>     | Paul Kwon <sup>4</sup> /   | Kunmo Kim                    |           |

| TtA datapatii    |                              |                            | Yi-Hsuan Shih <sup>2</sup> |                              |           |

| RX clockpath     | Yi-Hsuan Shih <sup>1</sup> / | Yi-Hsuan Shih <sup>1</sup> | Yi-Hsuan Shih <sup>2</sup> | Yi-Hsuan Shih <sup>1</sup> / |           |

| Tex clockpath    | Wahid Rahman                 | i i-risuan 5iiii           | i i-iisuan Siiii           | 11-11Suan Siiii              | Kunmo Kim |

| Digital Backend  | Paul Kwon <sup>4</sup>       | Paul Kwon <sup>4</sup>     | Paul Kwon <sup>4</sup> /   | Kunmo Kim/                   |           |

| Digital Dackellu | 1 aui ixwoii                 |                            | Yi-Hsuan Shih <sup>2</sup> | Sunjin Choi                  |           |

| Passive Frontend | Kunmo Kim                    | Kunmo Kim                  | Kunmo Kim                  | Kunmo Kim                    |           |

<sup>&</sup>lt;sup>1</sup>Chapter 2

Table 1.1: Project information and contributors.

$<sup>^2{\</sup>rm Chapter}$ 5 and Chapter 6

<sup>&</sup>lt;sup>3</sup>Ayan Biswas thesis [18]

<sup>&</sup>lt;sup>4</sup>Paul Kwon thesis [31]

## Chapter 2

# Clock Generation and Distribution for 100+ Gb/s Transmitter

### 2.1 Clock Path Overview

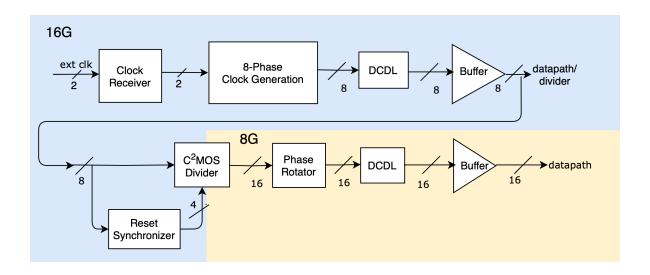

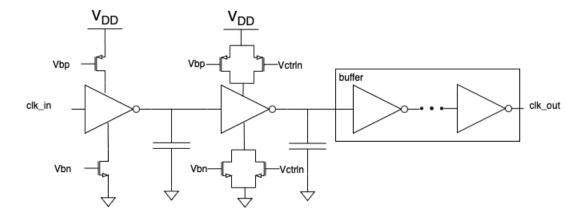

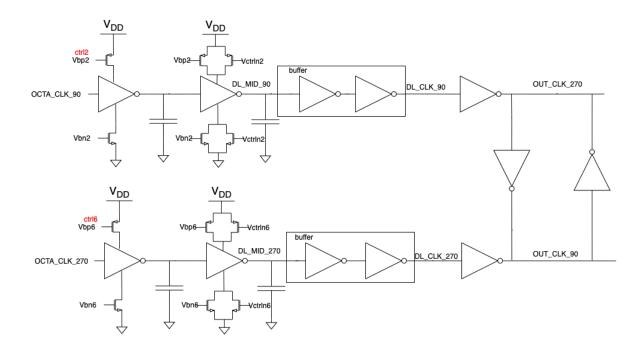

The basic topology of clock distribution and the building block layout generator are inherited from [47] designed by Zhongkai Wang. The prior work [47] was done in 28nm planar technology and the design is listed in Figure. 1.10 were done in 16nm/22nm FinFET technology. Key changes were made to adapt to the change from quadrature path to octature path due to the double interleaving of the datapath to push the data rate limited by the technology. The octature generator and the reset synchronizer are newly added to adapt to the change in interleaving. The duty cycle correction is added in the delay line and the change in the current DAC topology to provide a linear delay step. The clock path design for the 160Gpbs transceiver, the 128Gbps receiver, and the 100Gbps receiver will be discussed in this chapter. The clock path of links with different data rates shares a similar structure as summarized in Figure 2.1. The design is built hierarchically with Berkeley Analog Generator (BAG) which gives portability and flexibility to configure with different data-rate of the building blocks and the system.

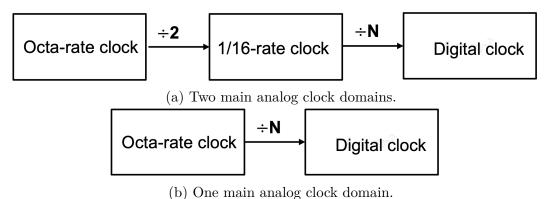

For 160Gbps and 128Gbps links, the two main analog clock domains are used considering the fanout and the speed limit of the latches as shown in Figure. 2.1a. For the 100Gbps link, the computation can be resolved without further describilization and thus only one analog clock domain (Figure. 2.1b) is used for simplicity and compactness of the layout.

Both of the clock distribution topology further divide the analog domain clock to the digital clock along with the descrialization after the MLSE computation.

<sup>&</sup>lt;sup>1</sup>The initial clock path design and the newly added blocks (octature generator, reset synchronizer, global buffer, duty cycle correction) for 200Gbps TRX clock path is in collaboration with Wahid Rahman. The 160 Gbps TRX follows essentially the same structure, but with an improved layout and an added debug clock.

Figure 2.1: Clock distribution.

#### 160Gbps TRX Clock Distribution Overview

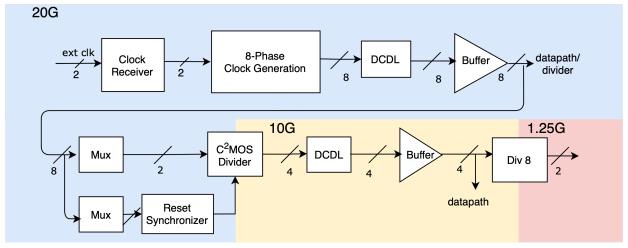

The clock distribution structure for the transmitter (TX) and receiver (RX) is designed similarly with minor modifications devoted to specific needs, as shown in Figure 2.2. This simplifies the design, and the layout generator can be reused with different configurations.

There are two clock domains (20G and 10G) in RX and three clock domains (20G, 10G, 1.25G) in TX, respectively. The 20G 8-phase clock domain contains the clock receiver, the octature generator, the current control delay line, and the global buffer for both TX and RX.

Four quadrature divider divide the 8 phase 20G clock to the 16 phase 10G clock in RX. The 10G clocks then feed into the phase rotator for the coarse tuning and the delay line for the fine tuning.

In TX clock path, only 4-phase is needed in 10G domain, thus only one quadrature divider is used. The mux is used to choose the clock phase for the divider input and the reset path to compensate for the delay across the corner. DCDL is enough to correct for the 4 phase skew compared to the RX counterpart. The divided clock followed by the Div-by-8 divider is generated by the clock path and sent to the TX datapath.

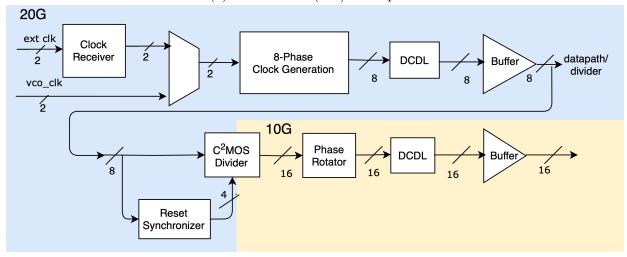

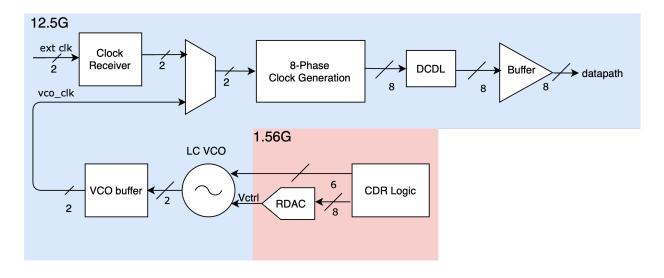

### 128Gbps RX Clock Distribution Overview

The 128Gbps RX clock distribution (Figure. 2.3) is built on the basis of the topology of the 160Gbps RX clock distribution (Figure. 2.2b). The main modification is the sizing and stacking change of the oscillator inside the 8-phase clock generation to achieve 128 GHz frequency with decent phase error across PVT corners. The  $C^2MOS$  divider is redesigned for robustness to the input clock skew which causes failure in the 160GHz RX measurement.

(a) Transmitter (TX) clock path.

(b) Receiver (RX) clock path.

Figure 2.2: 160GHz transceiver clock path.

### 100Gbps RX Clock Distribution Overview

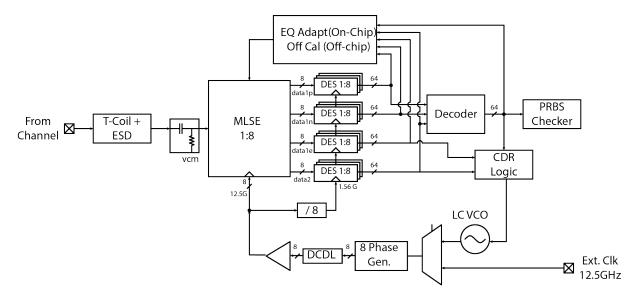

The 100Gbps RX clock path (Figure. 2.4) follows the topology of Figure 2.1b where only one main analog clock domain is presented due to the relaxation of the speed limit from the down scale of the data rate. Since the sampler can be clocked at 12.5GHz, there is no need for the divided 1/16 rate clock. The change simplifies the design of the clock path and reduces the area of the 16-phase 1/16 rate clock distribution. The other difference is that the input of the 8-phase generation comes from either an external clock or the VCO clock generated by the LC VCO on chip controlled by the CDR logic in the digital domain.

Figure 2.3: 128GHz receiver clock path.

Figure 2.4: 100GHz receiver clock path.

### 2.2 Octa-Rate Clock Distribution

#### **Octature Generator**

#### Multiphase generation

Multiple phase clocks are essential for the high-speed SerDes to enable the interleaving path in the datapth. There are several ways to generate the multiple phase clocks, which can be mainly categorized to closed-loop and open-loop methods. For closed-loop method, DLL and PLL can be used for multiphase clock generation, but the power consumption is high, and large area and long lock-in time are required.

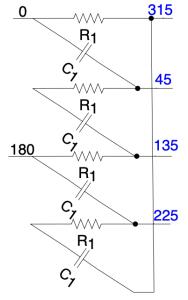

On the other hand, an open loop inverter-based ring oscillator and polyphase filter can be used to generate multiphase clocks[7]. There are two types of quadrature generation of polyphase filters depending on the connection of the input clocks. Both types provide a 90 degree phase shift and a matched amplitude at the pole frequency ( $\omega = \frac{1}{RC}$ ). Type 1 is constant phase, which means that the phase shift is constant across the frequency, while the amplitude of the outputs only matches at pole frequency. Type 2 in contrast is constant-amplitude which has constant matched amplitude response across the frequency while the phase shift is 90 degree only at pole frequency. The sensitivity to component mismatch ( $\Delta R$ ,  $\Delta C$ ) of Type 1 is twice higher than of Type 2 [40] and the phase error is tunable in the following delay line; we chose the Type 2 polyphase filter for quadrature and octature generation.

(b) Type 2 polyphase filter.

Figure 2.5: Polyphase filter for quadrature phase generation.

To implement octature generation with Type 2 polyphase filter, we can use the phase shift property of the following stage to achieve a 45 degree phase shift. The octature generator is shown in 2.6 where 8 phases are generated by one-stage and two-stage polyphase filters, respectively. To determine the values of the components, we rewrite the relation between  $R_1$  and  $R_2$  as

$$R_2 = \alpha R_1 \tag{2.1}$$

Since the pole frequency needs to be the target frequency for exact phase shift, we have

$$R_1 C_1 = R_2 C_2 = \frac{1}{\omega} \tag{2.2}$$

Therefore,

$$C_2 = \frac{C_1}{\alpha} \tag{2.3}$$

Assuming that the loading of each phase is  $C_L$  and  $\frac{1}{\omega C_L} >> R_1, R_2$ , we have the following.

$$|V_{o1}| = |V_{in}| \tag{2.4}$$

$$|V_{o2}| = \sqrt{2}|V_m| = \sqrt{2}(\frac{\alpha}{\alpha + 1}|V_{in}|)$$

(2.5)

To match  $V_{o1}$  and  $V_{o2}$ ,

$$\frac{\alpha}{\alpha+1} = \frac{1}{\sqrt{2}} \tag{2.6}$$

By solving the above equation, we have

$$\alpha = 2.414 \tag{2.7}$$

Let us take 25GHz clock generation for example. If we have  $C_L=6fF$  for each phase, we can implement the octature generator by choosing  $R_1=93\Omega, C_1=68.5fF, R_2=217\Omega, C_2=29.3fF$ . With an input clock of a perfect 25GHz differential sine wave, the output schematic simulation results are shown in Figure 2.7. However, if the input is not a sinusoidal wave, then the output has significant distortion and phase error.

The polyphase filter only consists of passive circuits, and thus has the advantage in terms of the power consumption. However, the narrow-band frequency filtering characteristics strictly require the input clock to be a sinusoidal wave. For square waves containing harmonic frequency components, the phase shift will not be the same as the fundamental frequency, causing the phase error and the distortion of the output clocks. The input frequency range can be extended by cascading more stages of the polyphase filter. However, the signal attenuation will be significant with more stages. To ensure sinusoidal input, the resonant buffer is needed before the polyphase filter, increasing the area and the power consumption.

The inverter-based injection-locked ring oscillator is an alternative open-loop multiphase generation. It consumes more power than the polyphase filter due to its active circuit nature.

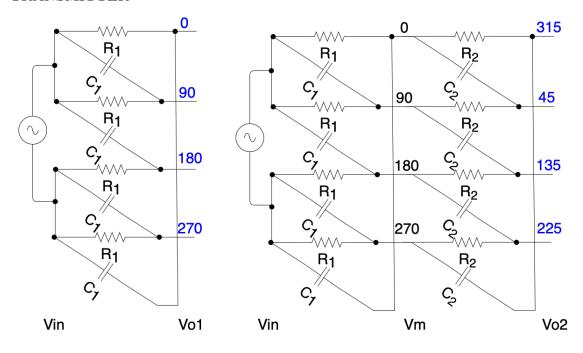

Figure 2.6: Polyphase filter for octature clock generation

Figure 2.7: Schematic simulation of polyphase filter octature clock generation.

However, it provides a wide frequency locking range with sufficient injection strength. The MOSFET-based layout is compacter than that of the passive resistor and capacitor. The quadrature generator based on the injection-locked ring oscillator is proposed in [8] and used in [32] [48][51]. Due to the wide-bandwidth input and wide locking range, the inverter-based structure is chosen to be the multiphase clock generation structure. It is intuitive to generate the octature generator from the single ring oscillator by having 8 inverters connected in one loop. However, it is difficult to achieve high speed due to the process-dependent minimum inverter delay.

#### Phase Interpolation

Suppose that the clock waveform is a sinusoidal wave with amplitude A, radian frequency  $\omega$ , and phase angle  $\phi$  to allow for any position of the time origin. The clock waveform can be written in the following general form.

$$x(t) = A\cos(\omega t + \phi). \tag{2.8}$$

For two clock waveforms with the same amplitude and radian frequency but different phases, we can express them as follows.

$$x_1(t) = A\cos(\omega t + \phi_1)$$

$$x_2(t) = A\cos(\omega t + \phi_2).$$

(2.9)

The corresponding non-rotating phasors taken by taking a snapshot of t=0 of both clock waveforms are

$$\begin{split} \underline{X_1} &= A \angle \phi_1 = A(\cos\phi_1 + j\sin\phi_1) \\ \overline{X_2} &= A \angle \phi_2 = A(\cos\phi_2 + j\sin\phi_2). \end{split} \tag{2.10}$$

To interpolate between two clock phases, we weighted the sum of two clock waveforms. Assuming that the weighting is the same for both waveforms, i.e.  $w_1=w_2=\frac{1}{2}$ , then we have

$$\begin{split} \underline{X_3} &= w_1 \underline{X_1} + w_2 \underline{X_2} \\ &= \frac{1}{2} (\underline{X_1} + \underline{X_2}) \\ &= \frac{1}{2} A [(\cos \phi_1 + \cos \phi_2) + j (\sin \phi_1 + \sin \phi_2)] \\ &= A_3 \angle \phi_3. \end{split} \tag{2.11}$$

In Equation. 2.11,  $A_3$  and  $\phi_3$  are the interpolated amplitude and the phase, respectively. We would like to rewrite it using the input amplitude A and the input phases  $\phi_1$  and  $\phi_2$ .

1. find  $A_3$

$$\begin{split} A_3^2 &= ||\underline{X_3}||^2 = \underline{X_3 X_3^*} \\ &= (\frac{A}{2})^2 [(\cos\phi_1 + \cos\phi_2)^2 + (\sin\phi_1 + \sin\phi_2)^2] \\ &= \frac{A^2}{4} [(\cos^2\phi_1 + \sin^2\phi_1 + \cos^2\phi_2 + \sin^2\phi_2) + 2\cos\phi_1\cos\phi_2 + 2\sin\phi_1\sin\phi_2] \\ &= \frac{A^2}{4} [2 + (\cos(\phi_1 + \phi_2) + \cos(\phi_1 - \phi_2)) - (\cos(\phi_1 + \phi_2) - \cos(\phi_1 - \phi_2))] \\ &= \frac{A^2}{4} [2 + 2\cos(\phi_1 - \phi_2)] \\ &= \frac{A^2}{2} [1 + \cos\Delta\phi] \end{split} \tag{2.12}$$

2. find  $\phi_3$  To easily calculate  $\phi_3$ , we can rotate both  $\phi_1$ ,  $\phi_2$ ,  $\phi_3$  by  $-\phi_2$ .

$$\begin{split} \underline{X_3'} &= w_1 \underline{X_1'} + w_2 \underline{X_2'} \\ &= \frac{1}{2} A [(\cos(\phi_1 - \phi_2) + \cos 0) + j (\sin(\phi_1 - \phi_2) + \sin 0)] \\ &= \frac{1}{2} A [(\cos \Delta \phi + 1) + j \sin \Delta \phi] \\ &= A_3 \angle (\phi_3 - \phi_2) \end{split} \tag{2.13}$$

We can take arctan to calculate  $\phi_3 - \phi_2$ .

$$\begin{split} \phi_3 - \phi_2 &= tan^{-1} \frac{sin\Delta\phi}{cos\Delta\phi + 1} \\ &= \frac{\Delta\phi}{2} \qquad \forall -\frac{\pi}{2} < \frac{\Delta\phi}{2} < \frac{\pi}{2} \\ \phi_3 &= \frac{\Delta\phi}{2} + \phi_2 \\ &= \frac{\phi_1 - \phi_2}{2} + \phi_2 \\ &= \frac{\phi_1 + \phi_2}{2} \qquad \forall -\pi < \Delta\phi < \pi \end{split} \tag{2.14}$$

Here is the caveat that the difference of the phase must be within  $-\pi$  to  $\pi$  to use the interpolation of the phase. In other words, the phase has to be wrapped within  $-\pi$  to  $\pi$  for Equation 2.14 to hold.

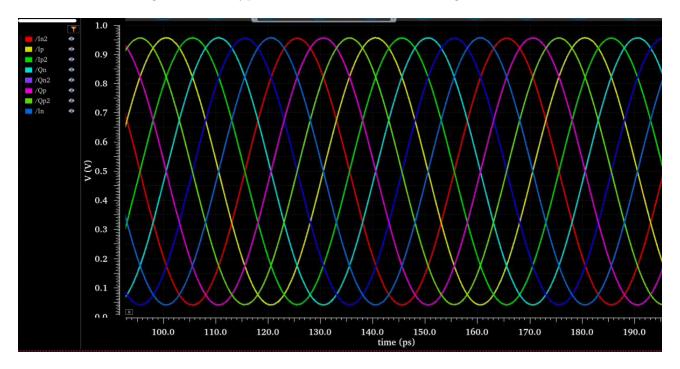

#### Octature Generation Theory

Based on the theory of coupling between two rings from [39], we designed the octature generator consisting of two coupled ring oscillators that generate quadrature clocks individually. By doing so, we can achieve almost 2x the speed that a single ring oscillator can achieve. The phase interpolation between the two quadrature generators creates a 45-degree phase shift between them. The phase of the ring oscillator is decided by the input of the ring inverters, the input of the coupling inverters, and the condition to make the ring oscillator oscillator.

Let us assume that there are two identical rings that oscillate at the same frequency. Without any coupling, the two rings will oscillate independently and have the phase shift  $\phi$  shown in Figure. 2.8 which is undetermined and unpredictable. The cross-coupled pair within the ring to ensure the oscillation of even stages oscillator is omitted in the figures just for simplicity.

Figure 2.8: Two rings oscillate independently.

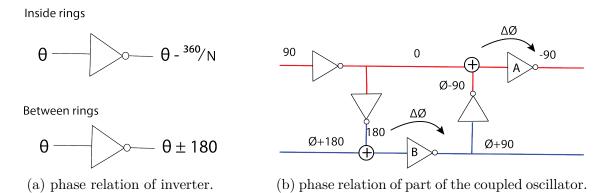

To make the ring oscillate, the phase shift of the whole ring should be 360 degrees. Therefore, the phase shift of an inverter within the ring should be  $\frac{360}{N}$  for N stages. For the inverter between rings without phase interpolation with the other inverter output, the phase change should be 180 degrees, as shown in Figure 2.9a. Based on the inverter phase relation, we can zoom in on a part of the ring and analyze the phase relation between the two rings after adding the coupling inverter. In Figure 2.9b, we decompose the phase interpolation into two parts, the input from the previous ring inverter and the input from the coupled inverter. The two inputs are combined at the input of the ring inverter and then experience

a  $\Delta\phi$  phase shift to the output of the ring inverter. For the ring oscillator to oscillate, the output of each stage must have a phase shift of -90 degrees. In Figure 2.9b, the output of inverter A is rewritten as -90 from 270 to ensure the -90-degree shift of the ring oscillator. We can find the phase relation  $\phi$  between two rings by examining the phase summation and the change in inverter A and inverter B. Assuming that the coupled inverter has the same driving strength as the ring inverter, we can use Equation 2.14 for the input summation.

Inverter A has the phase relation as the following equation.

$$\frac{1}{2} \times 0 + \frac{1}{2} \times (\phi - 90) + \Delta \phi = -90 \tag{2.15}$$

Using the same analysis, the phase relation at inverter B can be written as follows.

$$\frac{1}{2} \times (\phi + 180) + \frac{1}{2} \times (180) + \Delta \phi = \phi + 90 \tag{2.16}$$

By solving Equation 2.15 and Equation 2.16, we have

$$\phi = 45$$

$$\Delta \phi = -112.5$$

(2.17)

The results in Equation 2.17 show that with the same driving strength coupling between two rings, we can make the phase shift between two rings exactly 45 degrees apart. If we place the coupling inverter around the full ring oscillators, we can get the coupled ring oscillator shown in Figure 2.10 running at the same frequency as the quadrature generator, but generate 8 phases with 45 degrees apart.

Figure 2.9: Phase relation of input and output of the inverter. N: number of stages in the ring oscillator.

Figure 2.10: Two rings oscillate coupled with each other.

#### Quadrature generation

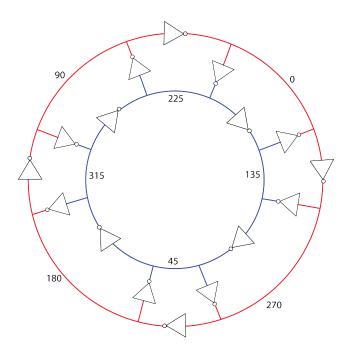

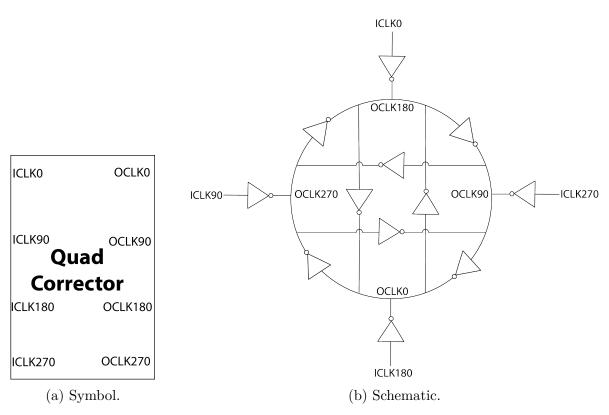

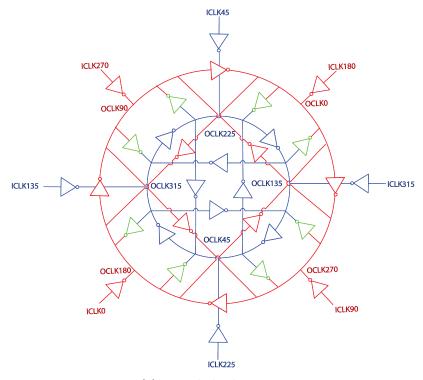

The quadrature generation can be achieved with the quadrature correlator proposed in [8]. It contains the main structure of the ring, the cross-coupled inverters inside the ring, and the injection inverters shown in Figure 2.11. The four inverters form the ring structure and generate four-phase clocks (OCLK0, OCLK90, OCLK180, OCLK270) when entering oscillation states. The cross-coupled pairs are set to be half of the main ring strength to help prevent metastability. The input clocks (ICLK0, ICLK90, ICLK180, ICLK270) inject through the injection inverters to the ring to lock the frequency and the phases are interpolated between the input clocks and the 90 phase shift inside the ring.

Figure 2.11: Quadrature corrector.

In [8], the structure of the quadrature generator is based on the cascading quadrature correlator to convert the differential clock to the quadrature clocks. The phase error can be minimized when more stage of quadrature correctors are cascaded with the expanse of power.

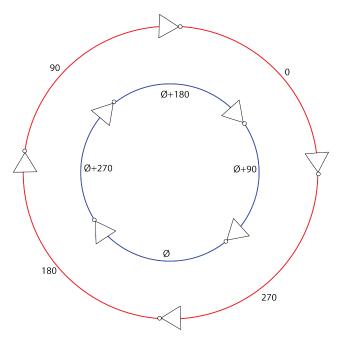

#### Octature genreator structure

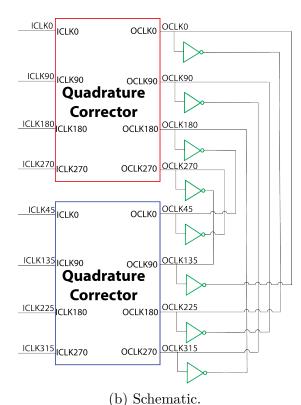

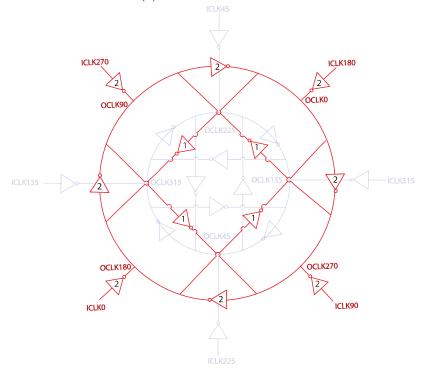

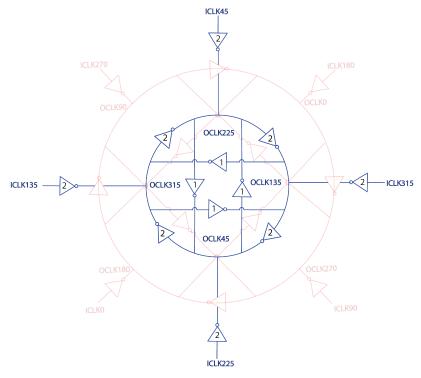

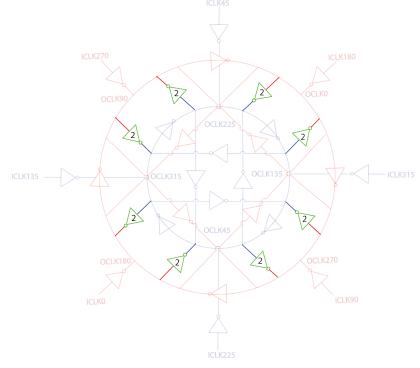

In the octature generation theory section, we explored a way to interpolate two quadrature rings to generate eight phases with a 45-degree phase shift. We can apply the theory to the quadrature corrector we introduced in the previous section. The conceptual schematic of the implementation is shown in Figure 2.12b. The outputs of the two quadrature correctors are coupled through the coupling inverters in green to achieve phase interpolation between two quadrature rings. The detailed schematic is shown in Figure 2.12c with the two ring oscillators shown in red and blue ,respectively. The inverter strength of ring 1 and ring 2 is shown in Figure 2.12d and Figure 2.12e with the same philosophy as stated in the previous section. The coupling inverters shown in Figure 2.12f have the same driving strength as the main ring structure in ring 1 and ring 2 to perform the octature generation.

| ICLK0     | OCLK0              |  |  |  |  |

|-----------|--------------------|--|--|--|--|

| ICLK45    | OCLK45             |  |  |  |  |

| ICLK90    | OCLK90             |  |  |  |  |

| ICLK135   | OCLK135            |  |  |  |  |

| Octature  |                    |  |  |  |  |

| Corrector |                    |  |  |  |  |

| ]         |                    |  |  |  |  |

| ICLK180   | OCLK180            |  |  |  |  |

|           |                    |  |  |  |  |

| ICLK180   | OCLK180            |  |  |  |  |

| ICLK180   | OCLK180<br>OCLK225 |  |  |  |  |

### (c) Detailed schematic.

(d) Ring 1, with inverter strength annotated.

(e) Ring 2, with inverter strength annotated.

(f) Coupling inverters between two rings with inverter strength annotated.

Figure 2.12: Octature corrector.

The octature generator shown in Figure 2.13 is implemented by cascading 4 stages of the octature correctors (Figure 2.13b. The input of the octature generator is the differential clock  $CLKP\_IN$ ,  $CLKN\_IN$ . The octature corrector is locked to the frequency of the input differential clocks. The phase of the output clocks of each octature generator is the interpolation of the 45 phases shift inside the quadrature rings and the input of the octature corrector. Thus, the output clocks would be closer to the ideal 8-phase clocks with more octature correctors cascading in series. The layout strategy is to have the two quadrature

|         |           | CLK0_OUT   |

|---------|-----------|------------|

|         |           | CLK45_OUT  |

| CLKP_IN |           | CLK90_OUT  |

|         | Octature  | CLK135_OUT |

|         | Generator | CLK180_OUT |

| CLKN_IN |           | CLK225_OUT |

|         |           | CLK270_OUT |

|         |           | CLK315_OUT |

(a) Symbol.

|          | ICLK0                   | OCLK0                         | IOCLK0<0>   | ICLK0                         | OCLK0                         | IOCLK0<0>   | ICLK0   | OCLK0                         | IOCLK0<0>   | ICLK0                         | OCLK0                         | CLK0_OUT                 |

|----------|-------------------------|-------------------------------|-------------|-------------------------------|-------------------------------|-------------|---------|-------------------------------|-------------|-------------------------------|-------------------------------|--------------------------|

|          | ICLK45                  | OCLK45                        | IOCLK45<0>  | ICLK45                        | OCLK45                        | IOCLK45<0>  | ICLK45  | OCLK45                        | IOCLK45<0>  | ICLK45                        | OCLK45                        | CLK45_OUT                |

|          | ICLK90                  | OCLK90                        | IOCLK90<0>  | ICLK90                        | OCLK90                        | IOCLK90<0>  | ICLK90  | OCLK90                        | IOCLK90<0>  | ICLK90                        | OCLK90                        | CLK90_OUT                |

| CLKP_IN  | ICLK135                 | OCLK135                       | IOCLK135<0> | ICLK135                       | OCLK135                       | IOCLK135<0> | ICLK135 | OCLK135                       | IOCLK135<0> | ICLK135                       | OCLK135                       | CLK135_OUT_              |

|          | Octatu                  | ıre                           |             | Octati                        | ure                           |             | Octat   | ure                           |             | Octati                        | ure                           |                          |

|          |                         | - 1                           |             |                               |                               |             |         | -                             |             |                               |                               |                          |

|          | Correc                  | tor                           |             | Correc                        | tor                           |             | Correc  | ctor                          |             | Correc                        | tor                           |                          |

| _CLKN_IN |                         |                               | IOCLK180<0> |                               |                               | IOCLK180<0> |         |                               | IOCLK180<0> |                               |                               | CLK180_OUT               |

| CLKN_IN  | ICLK180                 | OCLK180                       | IOCLK180<0> | ICLK180                       | OCLK180                       | IOCLK180<0> |         | OCLK180                       | IOCLK180<0> |                               | OCLK180                       | CLK180_OUT<br>CLK225_OUT |

| CLKN_IN  | ICLK180                 | OCLK180                       |             | ICLK180<br>ICLK225            | OCLK180<br>OCLK225            | IOCLK225<0> | ICLK180 | OCLK180<br>OCLK225            |             | ICLK180<br>ICLK225            | OCLK180<br>OCLK225            |                          |

| CLKN_IN  | ICLK180 ICLK225 ICLK270 | OCLK180<br>OCLK225<br>OCLK270 | IOCLK225<0> | ICLK180<br>ICLK225<br>ICLK270 | OCLK180<br>OCLK225<br>OCLK270 | IOCLK225<0> | ICLK180 | OCLK180<br>OCLK225<br>OCLK270 | IOCLK225<0> | ICLK180<br>ICLK225<br>ICLK270 | OCLK180<br>OCLK225<br>OCLK270 | CLK225_OUT               |

(b) Schematic.

Figure 2.13: Octature generator.

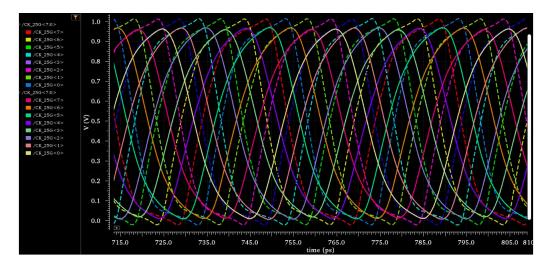

generators placed on top and bottom, which make one stage of the octature corrector. Then, the next stage can be cascaded by placing on the right. The size of each stage and the number of stages are configurable using BAG. Figure. 2.14 shows the simulation results of the octature clocks operated at 25GHz. The design includes four-stage quadrature correctors.

The solid clock waveforms include the power grid in the RC extration while the dotted clock waveforms only include block-level RC extraction. The performance of 25GHz is summarized in Table. 2.1. Here, we only show the representative simulation results for 25GHz used in 200Gbps TRX since it was the most challenging specs among the TRX clock path in Figure. 1.10 we have built. The phase error is less than 3 degrees and the locking range is larger than 20%.

Figure 2.14: Octature clocks post-layout simulation results for 25GHz clock.

| Phase error | Locking range |             |                  |       |        |  |

|-------------|---------------|-------------|------------------|-------|--------|--|

| < 3°        | > 20%         | $0.8V_{DD}$ | $48\% \sim 52\%$ | 35 mW | 23.7fs |  |

Table 2.1: 25GHz octature clocks performance (simulation).

### Digitally Controlled Delay Line (DCDL)

The digitally controlled delay line (DCDL) is used to adjust each phase of the clock to minimize the phase error. The basic structure of the delay element in DCDL is the current-starved inverter. Current-starved devices are on top and bottom of the inverter with the biases controlled by the current DAC. The current is adjusted by controlling the gate voltage of current-starved devices, which change the speed of charging and discharging the cap. The slower the charging and discharging, the longer the output delay. Extra pull-up and pull-down devices in parallel with current-starved devices are used to fine-tune the duty cycle with the digital input signal at the gates.

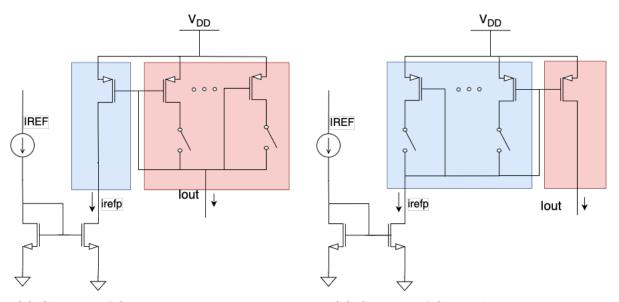

Figure 2.15: Delay line structure.

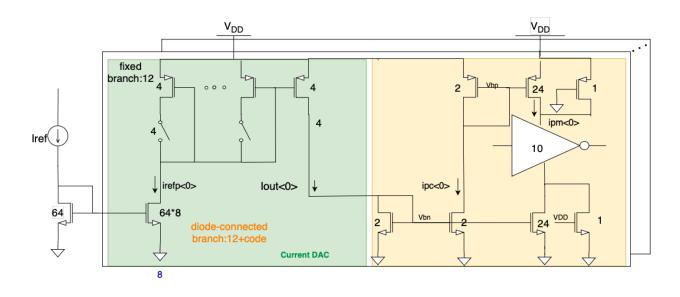

The conventional current DAC structure is shown in Figure 2.16a, where the reference branch in blue is fixed and the output current is decided by how many unit branches are turned on of the output branches N in red. Suppose that the unit output branch is the exact same size as the reference branch. In this case, the output current is proportional to the input code assuming that the input code directly indicates the number of branches turned on. If n represents the input code and  $I_{refp} = \alpha_{ref}I_{REF}$  the relationship between the output current and the input code can be written in the following equation.

$$I_{out} = nI_{refp} = n\alpha_{ref}I_{REF} \tag{2.18}$$

Assuming the capacitance load for the delay line is C, the voltage swing of the delay line is  $\Delta V$ , and the current mirror ratio between the current-starved device in the delay line and the output branch is  $\alpha_{DAC}$ , the delay D can be represented as

$$D = \frac{C\Delta V}{n\alpha_{ref}\alpha_{DAC}I_{REF}} \propto \frac{1}{n}.$$

(2.19)

As shown in Equation 2.19, the input code is inversely proportional to the delay generated by the delay line.

To have a linear delay step on the delay line, the current DAC for the delay line is designed with the input code proportional to the delay instead of inversion proportional to the delay shown in Figure 2.16b. Given the same sizing condition as that for the unit branches, the output current can be written as

$$I_{out} = \frac{I_{refp}}{n} = \alpha_{ref} \frac{I_{REF}}{n} \tag{2.20}$$

Using the same symbol as before, we can find the delay D of the delay line as

$$D = \frac{nC\Delta V}{\alpha_{ref}\alpha_{DAC}I_{REF}} \propto n \tag{2.21}$$

- (a) Current DAC with linear current step.

- (b) Current DAC with linear delay step.

Figure 2.16: Current DAC structures.

The connection between the current DAC and the delay line is shown in Figure 2.17. For the 8-phase clock domain, there are eight copies of the current DAC and delay line dedicated for the tuning of each phase. Delay line for each phase is controlled by the current DAC with the topology in Figure. 2.16b shown in the green block in Figure. 2.17. The output current of the current DAC then mirrors the bottom and top current-starved devices to control the delay of the inverters shown in the yellow block.

The example simulation results are shown in Figure. 2.18 with 500  $\mu A$  reference current and 7 ps tuning range (0.7UI). The nonlinearity occurs mainly in MSB switching due to the binary DAC structure. The step size is around 150fs. By increasing the reference current, the step size and tuning range will decrease accordingly.

Figure 2.17: Current and delay line branches.

Figure 2.18: Current dac code vs. delay.

#### Global Buffer

The global buffer is used to drive the datapath loading and the divider to generate the C16 clocks. The resonant buffer could be used with the inductor to resonate out the loading cap to reduce the needed driver size. However, the inductor will take up a substantial area, which may make routing longer and more complicated. For a high-speed circuit, the more compact the layout, the less routing is involved, leading to lower parasitic capacitance and resistance. For the matching of the clocks, the parasitic resistance is desired to be reduced as much as possible. Even if we can match the routing length so that the capacitance matched for all clock phases, it is more difficult to make the routing resistance the same for all. Therefore, to make the overall layout more compact, we place the clock path close to the datapath to minimize the routing parasitic. With less routing capacitance, we can eliminate the need for a resonant buffer and implement the differential pair of inverters with cross-coupled inverter pairs in between as the global buffer.

The schematic of the global buffer is shown in Figure 2.19. The cross-coupled pair inverters are sized much smaller than the main forward inverters so that the main inverter still dominates the signal path. The positive feedback cross-coupled pair adds hysteresis to the outputs that helps sharpen the edge and also couples the two outputs differentially. Positive feedback at the output helps the main inverter drive a larger capacitance load than the typical fanout. However, it also loads the previous stage more, i.e. the previous stage needs more driving power to fight with the cross-coupled pairs.

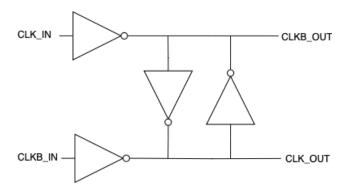

Figure 2.19: Global buffer schematic.

Figure 2.20 shows one of the four pair connections between the DCDL and the global buffer. The inverter chain serves as the buffer in between to be size with the global buffer.

Figure 2.20: One pair of CCDL and global buffer.

# 2.3 1/16-Rate Clock Distribution

The 16-phase clocks are required for the buffer array and the MLSE slices on the datapath. Four quadrature  $C^2MOS$  dividers with the reset synchronizer are implemented to generate a 16-phase clock from the C8 distribution. The 16 phase clocks are buffered with the inverter chain array and feed into the phase rotator and delay line for coarse and fine control of the phase skew. The last stage is the global buffer array to provide enough driving strength for the datapath loading stages.

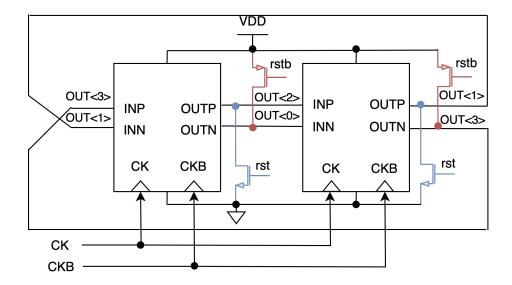

#### Divider

The quadrature divider is implemented by connecting the  $C^2MOS$  latch back-to-back as shown in Figure. 2.21. The input of the divider is differential clocks which are divided to quadrature output clocks.  $C^2MOS$  frequency divider is able to provide large output swing and eliminate the need for the CML-to-CMOS converter. To generate 16 phase clocks, we need 4 quadrature dividers to start dividing in the appropriate order. The reset signal is added to ensure that the divider starts with an initial known state and can be manipulated to have correct orders in the case that k quadrature dividers are used to generate 4k phase clocks. In our case, there are four quadrature dividers to divide 8-phase clocks into 16-phase clocks. The reset synchronizer serves this purpose to make sure that the dividers are reset in the correct order to generate the 16 phases correspondingly.

Figure 2.21: Quadrature divider schematic.

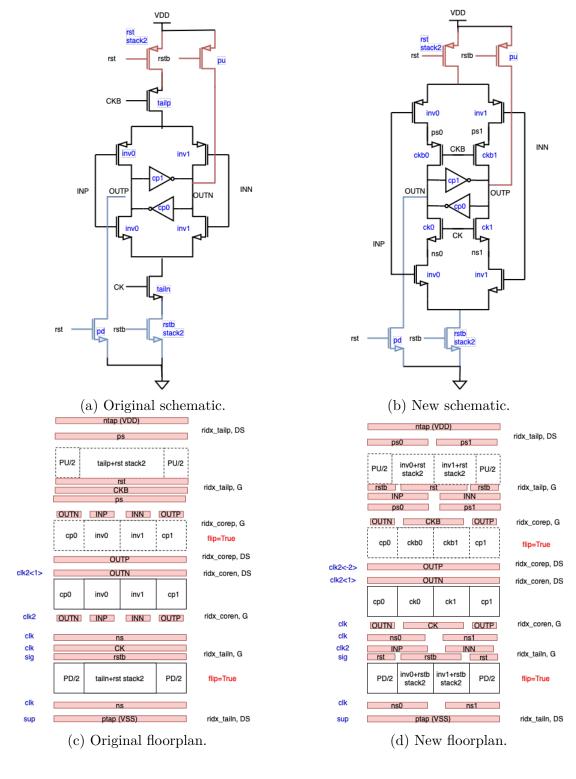

In the 160 Gbps transceiver design [31], the divider is followed by a cascade of  $C^2MOS$  latches with devices clocked outside the signal path. While measuring the 160 Gbps chip, we

found that the 1.25 GHz digital clock divided from the main clock path fails at the nominal operating speed, but can be observed at lower speed with the tuned current DAC code[31]. The phase skew of the differential phases at the input of the divider is suspected to cause the error. This is the known issue described in [38]. This topology can achieve higher frequency but suffers from charge sharing. The charge-sharing problem induces the kink in divided clocks which is more sensitive to the phase skew of input clocks[38]. Although the kink disappears at very high speeds, it is suspected to cause the failure in the 160 Gbps RX clock path [31].

The original divider structure used in 160Gbps link can support higher speed but is sensitive to clock phase skews. To enhance robustness against clock phase skews, clock devices are moved in the signal path to prevent distortion due to charge sharing for 128Gbps link.

Figure. 2.22 shows the schematics of the original and new dividers and the corresponding floorplan. The layout generator can be modified without significant change to generate new divider layout. The new divider layout is verified to be robust to input clock phase skew.

Figure 2.22:  $C^2MOS$  latch schematic and floorplan.

### Reset Synchronizer

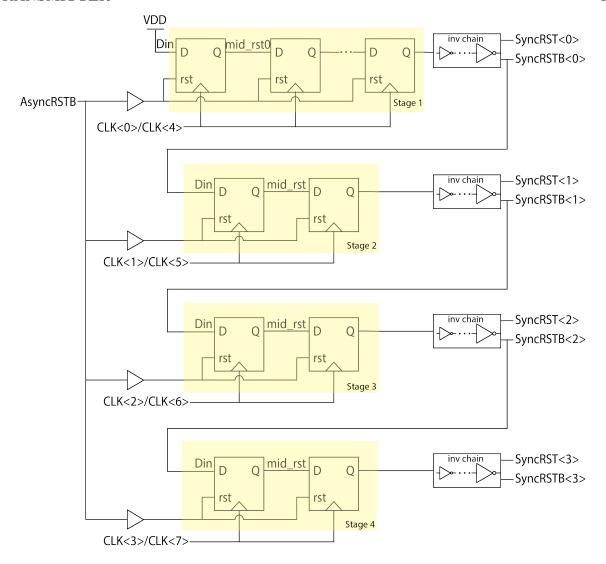

To generate C16 from C8 clocks, four  $C^2MOS$  dividers are needed to generate 4 pairs of the 4 phases clocks in the C16 domain from differential clocks in the C8 domains. Without proper reset signals, the initial state of the divider is not predictable. The reset signals define the initial state of the output of the dividers and thus make the phase alignment between the C8 and C16 domains more controllable. However, the asynchronous reset from the scan chain has an unknown relationship with the clock phases, and some dividers could potentially enter the metastability. In other words, the dividers run independently with the divided clock occurring at two possible states that are 180 degrees apart. The purpose of the reset synchronizer is to generate the synchronized reset signals with the input of the asynchronized reset from the scan chain for each divider in specified order and spacing in time so that the dividers can be reset and started in desired order. All reset signals are synchronized with clock phase 0 to preserve clock phase order after the dividers.

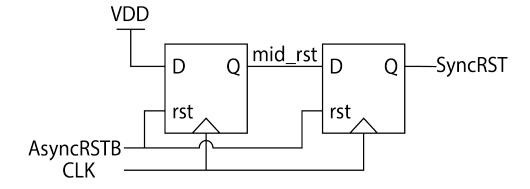

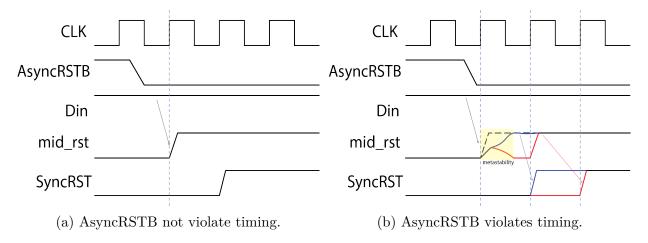

A typical reset synchronizer contains two flip-flops as shown in Figure. 2.23 The first flip-flop synchronizes the reset signal with the clock edge, while the second flip-flop removes the potential metastability during activation of the asynchronous active low reset (AsyncRSTB), where AsyncRSTB goes from high to low. The corresponding output is the assertion of the synchronized reset (SyncRST) that goes to the clock dividers.

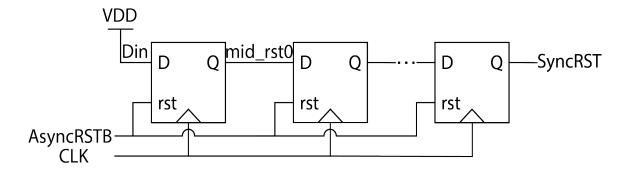

The timing diagram of the standard reset synchronizer is shown in Figure 2.24. If the transition of AsyncRSTB from high to low does not violate the timing of the flip-flop, then node mid\_rest will be synchronized with the following rising clock edge. However, when the transition of AsyncRSTB from high to low violates the timing of the flip-flop, it will cause the metastability issue in node mid\_rst and it is no longer clean synchronized reset. The second flip-flop in Figure 2.23 is used to remove the possible metastability in mid\_rst. If the metastability fails to resolve before the next clock cycle, then multiple flip-flops need to be added to remove the metastability. In this case, the depth of the reset synchronizer must be greater than two flip-flops to ensure the generation of the clean synchronized reset shown in Figure 2.25.

Figure 2.23: Standard unit reset synchronizer.

Figure 2.24: Standard reset synchronizer timing diagram.

Figure 2.25: Unit reset synchronizer with depth larger than 2.

The reset synchronizer consists of four stages of the unit reset synchronizer to generate four reset signals to the four quadrature dividers shown in Figure 2.26. Each stage requires CLK and CLKB that correspond to the input of each divider. The first stage contains four flip-flops cascaded in series (Figure. 2.25) to ensure that the timing of the last flip-flop is met with the asynchronous reset as the input. The Din of the following stages would be the synchronized reset of the previous unit reset synchronizer. The synchronized reset transition from low to high occurs with at least 4 C8 clock delay (depth of the first stage) after the AsyncRSTB transition from high to low. Therefore, a standard two flip-flop typical unit reset synchronizer (Figure 2.23) in series is enough for metastability and creates 2 C8 clock delays between each reset signal. To ensure a match of loading between the C8 clocks, the CLK/CLKB input of the stage 2 3 are also connected to the dummy load to compensate for the extra flip-flop load in the first stage.

Figure 2.26: 4-stage reset synchronizer for the dividers.

## Phase Rotator and Delay Line

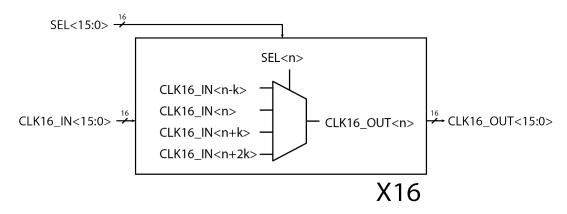

The phase rotator and the digitally controlled delay line (DCDL) are implemented as coarse and fine control of the phase errors, respectively. The phase rotator is inspired by [30] to adjust the clock phases due to the common skew among the 16 phases. Instead of using the phase interpolator (PI), which mixes and weighted two phases to get the interpolated phase, we directly apply 4-to-1 mux to choose the clock phase with minimum error that compensate over PVT corner. The simplicity of the 4-to-1 mux is more power and area efficient than the phase interpolator. The phase skew is minimized by relabeling the C16 clocks generated from the quadrature divider to align the C8 clocks, that is, phase n of C16 aligns with phase

n of C8, to compensate the logic delay and the routing delay in the post-layout simulation. Then the 4 phases (n-k, n, n+k, n+2k) of the 16 phases centered on the default phase n are chosen to cover the PVT corner. The detailed schematic is shown in Figure 2.27, where n is the index of the clock phase (0 < n < 15) and k is the select phase step to cover all variation of PVT. The delay line after the phase rotator has a linear relationship between the delay and the digital code that can be used to fine-tune the phase error between the C16 clocks and the alignment between C8 and C16.

Figure 2.27: Phase rotator schematic.

# Digitally Controlled Delay Line (DCDL)

The DCDL is basically the same as the one implemented in the C8 clock domain. Since the speed is twice slower than the C8 clock, the duty cycle due to the NMOS and PMOS driving strength is relieved. The duty cycle correction is therefore not included in the C16 CCDL for simplicity. The number of phases that must be tuned is double in the C16 domain, and 16 DCDLs and current DACs dedicated to each phase are needed. The tuning range needs to cover the phase step in the phase rotator (at least k UI is needed) and the DCDL step is also linear.

### Global Buffer

The global buffer structure is the same as the C8 global buffer shown in Figure 2.19. The total number of the global buffer is doubled to deal with twice clock phases in the C16 clock domain.

# Chapter 3

# MLSE and CDR Overview

Figure 3.1: High-speed link block diagram[25].

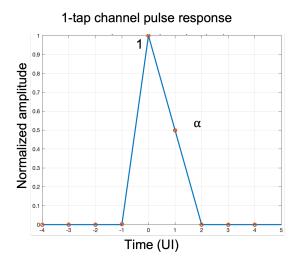

# 3.1 Inter-symbol Interference (ISI) and Equalization

# Inter-symbol Interference (ISI)

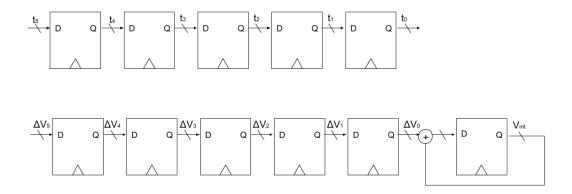

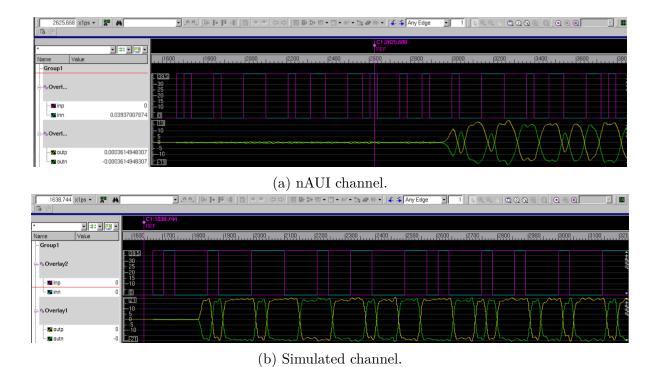

Inter-symbol interference (ISI) is a form of distortion of a signal consisting of a sequence of data symbol where one symbol is affected by other symbols in the sequence. The impulse digital input 0, 0, ...,0, 1, 0, ...0 before the serializer in the TX ideally converts into the 1-UI square pulse at the input of the receiver. However, the pulse response will smear out due to the finite bandwidth of the TX output driver and the low-pass channel between the TX and the RX. In Figure. 3.2, we take the pulse response of 200Gbps PAM4 TX in [47] as an