# Abstracting Architectures: Two Techniques in Formal Hardware Security Verification

Alejandro Sanchez Ocegueda

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2025-169 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2025/EECS-2025-169.html

August 15, 2025

# Copyright © 2025, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Acknowledgement

I would like to express my deepest gratitude to Adwait Godbole and Sanjit Seshia, who have been guides and mentors throughout the better part of three years. Thank you for your guidance in these exciting and challenging projects, and for your unwavering encouragement.

Abstracting Architectures: Two Techniques in Formal Hardware Security Verification

by

Alejandro Sanchez Ocegueda

A technical report submitted in partial satisfaction of the requirements for the degree of

Master of Science

in

Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Sanjit A. Seshia, Chair Professor Christopher W. Fletcher

Summer 2025

### Abstracting Architectures: Two Techniques in Formal Hardware Security Verification

Copyright 2025 by Alejandro Sanchez Ocegueda

#### Abstract

Abstracting Architectures: Two Techniques in Formal Hardware Security Verification

by

Alejandro Sanchez Ocegueda

Master of Science in Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Sanjit A. Seshia, Chair

Recent years have seen a dramatic increase in cyberattacks that target vulnerable hardware. One of the most effective ways to mitigate such vulnerabilities is to formally verify that hardware designs adhere to security standards. However, in a world with an insatiable need for performance, tight development cycles, and ever-evolving technical demands, verification efforts often fail to keep pace with hardware development. In this work, we present two approaches to making formal verification more efficient.

Our first contribution is a formal model for pointer-encryption schemes, U<sup>2</sup>. This model serves as a formal foundation for any system that enforces memory safety by using cryptography to protect pointers and data. We implement our model in UCLID5, and prove that it satisfies all desired security properties.

Our second contribution is BTORSEC, a security-aware extension of the popular BTOR2 format. By adding new cryptographic instructions, BTORSEC enables formal reasoning about cryptography in real-world RTL designs. Additionally, we implement a compiler and a proof-of-concept solver for security queries on BTORSEC programs.

Together, these contributions advance the state of the art in hardware security verification, enabling earlier detection of vulnerabilities and lowering the barrier to adopting formal methods in modern hardware design. To everyone who has been a part of this journey. Maybe the real thesis was the friends we made along the way.

# Contents

| Co           | ontents                                                                                                                                                                            | ii                                           |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Li           | st of Figures                                                                                                                                                                      | iv                                           |

| Li           | st of Tables                                                                                                                                                                       | $\mathbf{v}$                                 |

| 1            | Introduction 1.1 Contributions and Organization                                                                                                                                    | <b>1</b><br>2                                |

| 2            | U²: A Formal Model of Pointer Encryption Schemes   2.1 Introduction   2.2 Contributions   2.3 Background   2.4 Formal Model   2.5 UCLID5 Model   2.6 Related Work   2.7 Conclusion | 4<br>4<br>5<br>6<br>11<br>13<br>18<br>20     |

| 3            | BTORSEC: A Model-Checking Format for Hardware Security 3.1 Introduction                                                                                                            | 21<br>22<br>22<br>29<br>37<br>44<br>48<br>49 |

| 4            | Conclusion                                                                                                                                                                         | 51                                           |

| $\mathbf{A}$ | ${f U}^2$ Types                                                                                                                                                                    | 52                                           |

| $\mathbf{B}$ | ${f UCLID5\ Model\ of\ U^2}$                                          | 54  |

|--------------|-----------------------------------------------------------------------|-----|

|              | B.1 Common Module                                                     | 54  |

|              | B.2 $U^2$ Module                                                      |     |

|              | B.3 Main Module                                                       |     |

|              | B.4 Operations Module                                                 |     |

|              | B.5 Cryptography Module                                               |     |

|              | B.6 Contracts Module                                                  |     |

|              | B.7 Shadow $U^2$ Module                                               | 76  |

|              | B.8 Shadow Memory Module                                              |     |

| $\mathbf{C}$ | Formal Foundations of SSV                                             | 79  |

|              | C.1 Introduction                                                      | 79  |

|              | C.2 System Model                                                      |     |

|              | C.3 Threat Model                                                      |     |

|              | C.4 Verification                                                      |     |

| D            | Proof of Equivalence of the Secret Inference Problem and the Security |     |

|              | Verification Condition                                                | 88  |

| ${f E}$      | BTORSEC Language Details                                              | 99  |

|              | E.1 The Syntax of BTORSEC                                             | 100 |

|              | E.2 A JSON Schema for SecSpecs                                        | 101 |

| Bi           | bliography                                                            | 104 |

|              |                                                                       |     |

# List of Figures

| 2.1  | C <sup>3</sup> 's Cryptographic Address Format   | 7   |

|------|--------------------------------------------------|-----|

| 2.2  | Flow of $C^3$ Pointer Encryption                 |     |

| 2.3  |                                                  | 8   |

| 2.4  |                                                  | 9   |

| 2.5  |                                                  | 10  |

| 3.1  | Flip-Flop Verilog Module                         | 23  |

| 3.2  | Btor2 Code for Flip-Flop Module                  | 24  |

| 3.3  | BTORSEC Program of the Double Encryptor          | 35  |

| 3.4  | A Sample Top-Level Module                        | 35  |

| 3.5  |                                                  | 36  |

| 3.6  | A Complete SecSpec                               | 37  |

| 3.7  | The BTORSEC Compilation Pipeline for Users       | 38  |

| 3.8  |                                                  | 39  |

| 3.9  | A Sequential Encryptor Design                    | 10  |

| 3.10 | BTOR2 Representation of the Sequential Encryptor | 11  |

|      | BTORSEC Program of the Sequential Encryptor      | 12  |

|      | Conditional Encryptor                            |     |

|      | BTOR2 Program of Encryptor with MUX              |     |

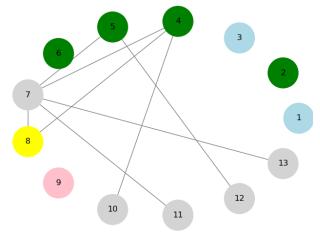

| 3.14 | Dependency Graph Created by MarkInsts Pass       | 14  |

| E.1  | Syntax of BTOR2                                  | )() |

# List of Tables

| 2.1 | $U^2$ State Variables                             | 12 |

|-----|---------------------------------------------------|----|

| 2.2 | The $U^2$ API                                     | 12 |

| 3.1 | Cryptographic Instructions Supported by BTORSEC   | 30 |

| 3.2 | Verification Results for Perfect Encryption Model | 48 |

| 3.3 | Verification Results for XOR Model                | 48 |

| A.1 | Types of $U^2$                                    | 52 |

| A.2 | Ghost Memory Record                               | 52 |

| A.3 | Observation Record                                | 53 |

#### Acknowledgments

First and foremost, I would like to thank my M.S. advisor, Professor Sanjit Seshia, initially for allowing me to join his Formal Methods class back in Spring 2023, and for later introducing me to the Learn&Verify group. Thank you for the continued mentorship and guidance throughout these years—I have learned (and verified) a lot in my time in the group. Thank you for taking the time to read and give feedback on my drafts.

I would also like to thank my second reader, Professor Christopher Fletcher, for the continued support and advice throughout the Spring 2025 semester. Your comments, suggestions, and encouragements in the CS 252A discussions have helped shaped the work in this report tremendously.

The next round of thank-yous goes to the Learn&Verify group members, for sharing your wisdom and for the lovely group lunches every Friday. A special thank you goes to the UCLID folks, who have been following the development of this project for a very long time. Your feedback and suggestions have greatly influenced the development of SSV, and I cannot thank you enough. And, of course, a big shoutout to my fellow 5th Year M.S. students, Anirudh and Kai.

I also want to take the time to thank the friends I made at UC Berkeley, who have made my time as a student here both a pleasure and a privilege. Thank you to all my friends at I-House, especially Bryant, Natalie, Melanie, Tatsu, Serena, and the Dwellers. Thank you to the Smash at Berkeley people for giving me the opportunity to grow and develop a passion outside of academics. And thank you to the all the HKNers for always having my back in all of my EECS classes.

I want to extend my deepest gratitude to Adwait Godbole, who has been my mentor and closest collaborator for the past two years. Thank you for the guidance. Thank you for the patience as I stumbled my way across the vast sea that is research. Thank you for the long debugging sessions. This project quite literally would not have been possible without your help.

Por último, quiero agradecer a mi familia, quienes han estado conmigo desde hace 24 años. Gracias Baba, gracias Babi, y gracias Yoyi por siempre estar a mi lado, estén en donde estén. Juntos hemos cruzado fronteras, mares, y ahora, la meta final. ¡Lo conseguimos, lo conseguimos!

# Chapter 1

# Introduction

With the advent of technologies like generative artificial intelligence, cryptocurrencies, and cloud-based services, the demand for computing power around the world has never been higher. Models must be trained, transactions must be committed, requests must be fulfilled. In this age of unprecedented competition and innovation, there is not a second to waste.

To satiate the industry's ever-growing need for speed, engineers work across the stack and around the clock, looking to squeeze as much performance out of their systems as possible. One particularly effective method of improving performance that has gained much traction recently is *hardware acceleration*, a technique that involves directly implementing important functionality in custom hardware circuits. These tailor-made circuits often provide massive increases in performance, easily outperforming software-based optimizations by large margins.

One particular class of hardware accelerators has received much attention in recent years: cryptographic accelerators. Cryptography is often framed as a necessary evil—components of the system that hinder performance, but prevent much more dire consequences, like the leakage of sensitive data. Indeed, cryptography presents itself as the perfect candidate for hardware acceleration: it is a necessary operation that could lead potentially be a bottleneck for performance. By implementing custom circuits to provide cryptographic functionality, we can offset this performance penalty, achieving the dream of having both security and performance.

Unfortunately, the solution to secure and efficient hardware designs is not that straightforward. Well-designed and properly implemented cryptographic accelerators are not enough. Much like in the software realm, if cryptographic primitives are not used appropriately, the security of a hardware design can still be compromised, even if the primitives work exactly as intended. Thus, to fully achieve the vision of secure and efficient hardware, we must also ensure the correct integration of cryptographic primitives into the larger design. It is not enough to have all the right pieces of the puzzle—we must also ensure that it is assembled correctly.

#### Challenges

Guaranteeing the security of hardware designs in the modern age is no small feat, and doing so poses a number of challenges, which we outline below:

- (I) How can we develop formal models to reason about the high-level security properties of our designs? What kinds of abstractions allow us to reason about the security of our hardware?

- (II) Once we implement a design in RTL, how can we verify its security properties?

- (III) Lastly, how can we develop tools that are easy to use and provide meaningful feedback on the security of hardware designs, in an era where hardware implementations can change from one day to another?

#### This Report

The work presented in this text represents our approach to addressing the challenges laid out above. Our vision is that by combining techniques in the areas of formal methods, security, and computer architecture, we can make some progress towards developing effective solutions for verifying security of hardware designs.

# 1.1 Contributions and Organization

The work presented in this report is the culmination of a collaborative effort. The work for Chapter 2 started as a class project for the Spring 2023 iteration of EECS 219C at UC Berkeley. The initial work was done with my classmates Tommy Joseph and Nigel Chen, with guidance from Adwait Godbole and Sanjit A. Seshia. The work that followed, and that constitutes the majority of said chapter, was done in collaboration with Adwait Godbole and Sanjit A. Seshia. The work on Chapter 3 was done in collaboration with Adwait Godbole, with input and guidance from Sanjit A. Seshia, Tianrui Wei, and Christopher W. Fletcher. Below we present a brief overview of this report, along with the primary contributions of each piece of work:

Chapter 2: U<sup>2</sup>: A Formal Model of Pointer Encryption Schemes. This chapter provides our approach to modeling and verifying a complex hardware cryptosystem with the UCLID5 toolkit [1], [2]. This allows us to reason about the correctness and memory safety guarantees of the C<sup>3</sup> cryptosystem at a high level. Additionally, the modeling techniques utilized therein can be used to tackle similar high-level system verification problems. Chapter 2 is organized as follows:

• Section 2.4 presents our formal model of the U<sup>2</sup> cryptosystem. This section also specifies the main security properties that our model provides.

• In Section 2.5, we present our UCLID5 implementation of U<sup>2</sup>. We highlight key abstractions and design decisions that went into the implementation.

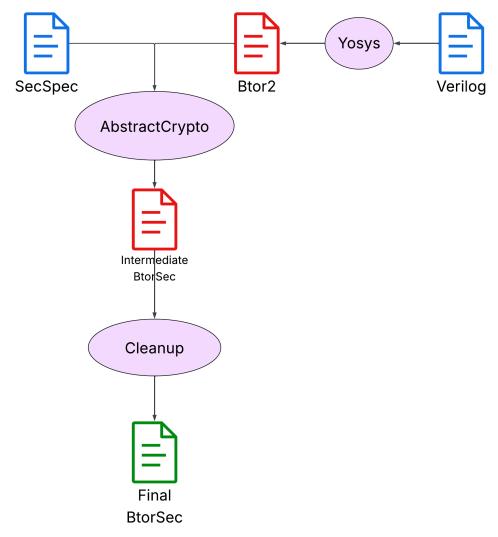

Chapter 3: BtorSec: A Model-Checking Format for Hardware Security. This chapter presents BtorSec, our novel extension of the popular Btor2 [3] format. Our extension, which consists of abstract cryptographic instructions, allows us to reason about the correct usage of cryptographic primitives in RTL design. This chapter also provides proof-of-concept tools for (almost) automatically compiling and verifying BtorSec designs, thus minimizing overheads and effort required on the engineering side.

Chapter 3 is organized as follows:

- Section 3.4 describes BTORSEC, our security-centric extension of the popular BTOR2 model-checking format. Specifically, Section 3.4.1 presents the new abstract cryptographic instructions of the format, while Section 3.4.2 introduces the SECSPEC format, which is used to annotate a Verilog design with security-relevant metadata.

- In Section 3.5, we explain the BTORSEC compilation pipeline, which allows users to create BTORSEC files from existing Verilog designs and an associated SECSPEC.

- Section 3.6 dives into the implementation of SSV, our prototype bounded model checker for BTORSEC programs.

Chapter 4: Conclusion. This final chapter summarizes this report and provides suggestions for future research stemming from our work.

The chapters of this report are self-contained. Each chapter includes the necessary background required to understand it, as well as the related work most relevant to its focus. We assume only a basic familiarity with first-order logic (FOL), including the negation operator  $(\neg)$ , the logical connectives—conjunction  $(\land)$ , disjunction  $(\lor)$ , conditional  $(\Rightarrow)$ , and biconditional  $(\Rightarrow)$ —and a basic understanding of the existential  $(\exists)$  and universal  $(\forall)$  quantifiers.

# Chapter 2

# U<sup>2</sup>: A Formal Model of Pointer Encryption Schemes

#### Are we building the right thing?

Cryptographic systems claim to provide a number of security guarantees, but how can we be sure this is indeed the case? Formal models allow us to rigorously reason about the security properties of such systems. We provide a formal model  $U^2$  that provides cryptographic memory safety guarantees. We also present an implementation of  $U^2$  in the UCLID5 language. This chapter addresses Challenges (I).

### 2.1 Introduction

Certain low-level languages, such as C and C++, allow programmers to directly manipulate a program's memory. This flexibility lets programmers take full advantage of the underlying hardware, often enabling high performance. However, the burden of correct memory management falls entirely on the programmer, creating opportunities for a wide range of memory-related bugs.

This class of memory corruption bugs—also known as memory safety vulnerabilities—often leads to undefined and potentially dangerous behavior. Furthermore, malicious attackers can take advantage of these vulnerabilities to perform a number of attacks. For instance, an attacker may index beyond the bounds of an array to access other parts of memory, or they may use a pointer that was previously freed to manipulate the data inside the new allocation. These attacks can have serious consequences, ranging from leaking sensitive data to allowing an attacker to take control of the machine running the vulnerable code.

Several solutions have been proposed to deal with the threat of memory corruption. Many propose rewriting code written in vulnerable languages. Most of the effort on this front involves translating code into Rust, as this ideally would provide both performance and safety [4]. Other solutions involve statically analyzing the source code for vulnerabilities

[5]–[7] or monitoring the code during runtime to detect any vulnerabilities when they happen [8], [9].

Recently, researchers have introduced mitigations that operate at the hardware level. These solutions introduce specialized hardware that performs the necessary checks required to enforce memory safety, ensuring that software that runs on these machines is secure. The philosophy behind this approach is that by utilizing dedicated hardware, users will enjoy security guarantees and minimal performance overheads. A classic example of hardware-based memory safety enforcement is the use of hardware-based pointer tagging mechanisms, like ARM's Memory Tagging Extension (MTE) [10] and SPARC's Application Data Integrity (ADI) [11]. These solutions use tags to enforce that pointers are not improperly modified. Another prominent example is capability architectures, such as CHERI [12]. Capability architectures replace pointers with *capabilities*, which are objects that store additional information like permissions, bounds, and more. This additional information is used in hardware-based checks that enforce correct memory management.

Intel recently proposed a hardware-based architecture for enforcing memory safety: the Cryptographic Capability Computing microarchitecture, stylized as C<sup>3</sup> [13]. C<sup>3</sup> is a capability architecture that defends against memory-based attacks through cryptography. In a nutshell, C<sup>3</sup> protects the heap address space by encrypting pointers to memory, and then uses these encrypted pointers as part of the key used to access the data. The authors claim that this scheme is sufficient to provide confidentiality and integrity of all data in the heap, effectively mitigating vulnerabilities that target the heap altogether.

It is natural to have some skepticism at such bold claims. The authors show  $C^3$ 's effective protection on a comprehensive suite of vulnerable code, but how can we be sure that it was not just good luck? Furthermore, if the  $C^3$  scheme is indeed secure, we would like a general model or framework that future work can build upon.

To move beyond empirical evaluation and provide principled security guarantees, we develop a formal model for C3-like pointer-encryption schemes. We name our model Unobservably Unbreakable, or U<sup>2</sup>, for short. Formal models allow us to reason about systems and their properties soundly. Additionally, they enable—and indeed require—us to precisely specify properties that are often ambiguous, such as "memory safety," "integrity," and "confidentiality." Given that hardware-based memory safety mitigations like C³ involve the interaction of hardware and software, we employ the UCLID5 language [2]. The language's multi-modal modeling capabilities allow us to specify and verify complex systems like C³ seamlessly.

# 2.2 Contributions

Concretely, the contributions of this chapter can be summarized as follows:

- 1. We formulate U<sup>2</sup>, an abstract model for C<sup>3</sup>-like pointer encryption systems.

- 2. We give a characterization of memory safety properties for pointer encryption schemes.

3. We implement and verify a model of  $\mathrm{U}^2$  in UCLID5, showing that our model satisfies our memory safety properties.

# 2.3 Background

This section provides the necessary background information for this chapter. We begin with a quick treatment of memory safety. Then, we proceed to explain the design of C<sup>3</sup>. Finally, we give a short primer on UCLID5.

### 2.3.1 Memory Safety

Memory safety is the property of a program or system that ensures all memory accesses are valid—meaning the program only reads from and writes to memory it has been allocated, and only while that memory is still in scope. Violations of memory safety, such as buffer overflows, use-after-free errors, or accessing uninitialized memory, can lead to crashes, data corruption, or exploitable security vulnerabilities. Enforcing memory safety can be done through safe programming languages, runtime checks, or hardware-based protections. We refer interested readers to [14] for a more detailed survey of this topic.

# 2.3.2 The C<sup>3</sup> Microarchitecture

As stated in the introduction to this chapter, Cryptographic Capability Computing ( $C^3$ ) [13] is a capability architecture developed by Intel to provide memory safety in the heap.  $C^3$ 's novelty stems from the fact that it relies entirely on cryptography to provide its memory safety properties. This allows the architecture to remain efficient, and it has the added benefit of not needing to keep track of any additional state, unlike other hardware-based mitigations. The most salient aspect of  $C^3$  is the way in which the architecture encrypts pointers, and then utilizes these encrypted pointers as part of the keystream used to access the associated data. This has the effect of 'entangling' the pointer with the data that it points to in the heap.

In what follows, we give a brief introduction to how  $C^3$  works. The diagrams presented in this section have been adapted from [13] and [15].

### Pointer Encryption

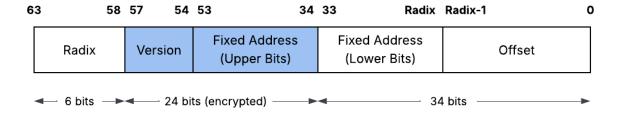

One of the innovations of  $C^3$  is its use of cryptographic addresses (CAs). CAs are a special format for pointers that only encrypt a specific portion of a plaintext linear address (LA). They are created at the time of memory allocation (i.e. after a call to malloc). The format as specified in the original  $C^3$  paper can be seen in Figure 2.1.

The fields of the format are the following:

Figure 2.1: C<sup>3</sup>'s Cryptographic Address Format

- Radix: This 6-bit field specifies the size of the allocation<sup>1</sup>, in power of two.

- Version & upper fixed address: This 24-bit range consists of the upper 20 bits of the original pointer and the 4 bits of the Version field put together. The Version field is used to avoid temporal safety issues stemming from the underlying LA being the same for two CAs that were allocated at different times.

- Lower fixed address & offset: This 34-bit range is left unchanged from the original LA. This is done so that software can perform pointer arithmetic without requiring cryptographic intervention.

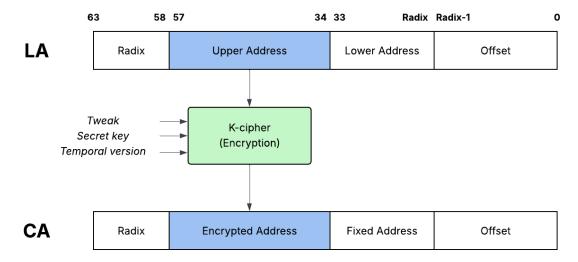

CAs can be created from LAs by encrypting the corresponding fields.  $C^3$  achieves this by using a tweakable block cipher named "K-cipher" [16]. The flow for generating a CA from an LA is shown in Figure 2.2.

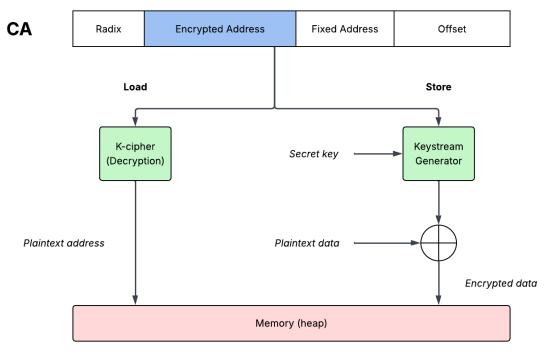

#### **Data Encryption**

The next important component of  $C^3$  is data encryption and decryption. Encryption happens at the time data is stored into a memory slot allocated by  $C^3$ . Decryption happens whenever data is loaded from a memory slot. One key aspect of how these operations are performed is that the pointer to the data itself is part of the key. The flow of how data encryption and decryption happens during load and store operations can be seen in Figure 2.3.

#### 2.3.3 UCLID5 Primer

UCLID5 is a software toolkit for the formal modeling, specification, verification, and synthesis of computational systems. In this section, we briefly familiarize the reader with UCLID5. For a more thorough discussion of UCLID5, we refer the reader to the tutorial<sup>2</sup> or to the original UCLID5 papers [1], [2].

<sup>&</sup>lt;sup>1</sup>In the C<sup>3</sup> scheme, the size of all allocations is a power of two, by design,

<sup>&</sup>lt;sup>2</sup>https://github.com/uclid-org/uclid/blob/master/tutorial/tutorial.pdf

Figure 2.2: Flow of C<sup>3</sup> Pointer Encryption

Figure 2.3: Flow of C<sup>3</sup> Data Encryption and Decryption

We now give two examples of UCLID5 in action. First, we show how we can model state transition systems by modeling the Fibonacci sequence. Second, we show an example of how we can construct and use algebraic data types in UCLID5 .

#### **State Transition Systems**

The UCLID5 language allows us to seamlessly model, specify, and verify state transition systems like the one shown in Figure 2.4. This example module of the Fibonacci sequence, while simple, is enough to show the power of UCLID5.

```

module main {

2

// Part 1: System description

3

var x, y : integer;

4

6

init {

x = 0;

8

y = 1;

9

10

11

next {

12

x' = y;

13

y' = x + y;

14

16

// Part 2: System specification

17

property y_le_x : y <= x;</pre>

property ind_strengthen : x >= 0 && y >= 0;

18

19

20

// Part 3: Proof script

21

22

control {

v = induction;

23

24

check;

print_results;

25

}

26

}

27

```

Figure 2.4: A simple UCLID5 module of the Fibonacci sequence

Part 1: System Description. We can describe the system's behavior, as the module does in lines 4-14. Intuitively, we are describing what the system does. First, we declare the integer variables x and y. Then, in the init block on lines 6-9, we declare the initial values of x and y (0 and 1, respectively). Below that, in lines 11-14, the next block specifies how the variables will change after one step of the transition relation is executed. This is denoted with the primed variable notation: x' = y indicates that the next value of x in will be the current value of y. Similarly, the notation y' = x + y indicates that the next value of y will be the sum of the current values of y and y. This aligns with the behavior of the Fibonacci sequence.

Part 2: System specification. UCLID5 also allows us to create specifications for our models. Intuitively, the specification allows us to clearly define what the system is supposed

to do. In this example, we have two properties that describe the correctness of our system: y\_le\_x on line 17 and ind\_strengthen on line 18. y\_le\_x is the property we wish to prove, whereas ind\_strengthen is a property that is used to strengthen the induction and avoid spurious counterexamples.

Part 3: Proof script. Finally, the we have the control block on lines 22-26. This block consists of a sequence of commands that are used to verify the properties we specified earlier. In this model, we use induction to verify our properties. The check command checks whether the proof obligations are satisfied and the print\_results command prints out the results of these checks.

#### Algebraic Data Types

We now proceed to show an example of how we can construct and utilize algebraic data types (ADTs) in our systems. Consider the example shown in Figure 2.5.

```

module main {

2

3

// Part 1: System description

datatype list = cons(head: integer, tail: list) | nil();

var l : list;

init {

1 = nil();

9

11

next {

12

l' = cons(1, 1);

13

14

16

// Part 2: System specification

17

invariant test : 1.head == 1;

18

19

20

// Part 3: Proof script

21

22

control {

23

induction;

24

check;

print_results;

25

}

26

}

27

```

Figure 2.5: A UCLID5 module of a linked list

Part 1: System description. This module consists of a single variable 1 of type list (line 6). The list type is a user-specified algebraic data type. Users can create their own ADTs

by using the datatype keyword, followed by the type name, as is done on line 4. Then, users can specify a grammar of *constructors*. In our example, we have two constructor: the 0-ary nil, which represents a null value and the binary cons constructor. cons recursively builds a list by creating a head node from an integer value and appending it to the tail list.

Initially, we create an empty list by declaring 1 = nil() in the init block (lines 8-10). Then, at every state transition, we grow the list by appending a 1 to the head

Part 2: System specification. The only property we wish to verify is that in this system, the head of our list 1 always has a value of 1.

Part 3: Proof script. Much like the previous example, we verify the correctness of this system by induction. We then use the check command to check that our module meets the proof obligations. Finally, we print out the results with the print\_results command.

### 2.4 Formal Model

In this section, we present our formal model of the abstract  $U^2$  system. We define our model as the triple  $U^2 = (\Sigma, T, init)$ .  $\Sigma$  is a set of states, or a valuation of the state variables of the model.  $T \subseteq \Sigma \times \Sigma$  is the transition relation, subject to the operations described later in this section. Finally,  $init \subseteq \Sigma$  is the set of allowed initial states.

We begin by introducing the  $U^2$  model, followed by a description of the  $U^2$  adversary. To end the section, we outline the key security properties that we require the  $U^2$  model to satisfy.

#### 2.4.1 State Variables

We now present the state variables of  $U^2$ . These give a characterization of our system's states, as any  $\sigma \in \Sigma$  is merely a valuation of these variables. The state variables of  $U^2$  can be found in Table 2.1. A detailed description of all types can be found in Appendix A.

#### **Initial States**

We model our initial state as a fresh start in which no allocations have been made. In other words, any initial state  $\sigma_i \in init$  must satisfy the following condition:

$\forall a. \text{ alloc\_map}[a] = \text{false}.$

# 2.4.2 Operations

We now describe the operations that our  $U^2$  model allows. We model these as an API that all processes running in the system must use to manipulate memory. These give a characterization of the transition relation T.

| State Var.         | Type                | Description                                           |

|--------------------|---------------------|-------------------------------------------------------|

| msv_curr           | $\mathbb{B}$        | Variable denoting whether a memory safety vulnerabil- |

|                    |                     | ity has occurred in the current step.                 |

| alloc_map          | $W \to \mathbb{B}$  | Map indicating whether a given memory address has     |

|                    |                     | been allocated.                                       |

| mem                | $W \to W$           | Physical memory.                                      |

| ${	t ghost\_mem}$  | $W \to \mathcal{G}$ | Memory augmented with ghost metadata.                 |

| lmem               | $I \to W$           | Local memory (per-process registers).                 |

| ${	t ghost\_lmem}$ | $I \to \mathcal{G}$ | Local memory augmented with ghost metadata.           |

| observable         | $\mathcal{O}$       | Microarchitectural observable variable.               |

| opcode             | O                   | Opcode for non-memory instructions.                   |

| $l_{-}i$           | I                   | Local memory indices.                                 |

| action             | A                   | The current operation to be executed.                 |

Table 2.1: U<sup>2</sup> State Variables

| Operation                                              | Description                                                                |

|--------------------------------------------------------|----------------------------------------------------------------------------|

| $	exttt{malloc}(l_{dest}, k_p, k_d)$                   | Creates a new allocation in memory, ensuring pointer                       |

|                                                        | is encrypted under $k_p$ and data is encrypted under $k_d$ .               |

|                                                        | Stores resulting pointer in $l_d$ .                                        |

| $\mathtt{load}(l_{dest}, l_{addr}, k_p, k_d)$          | Uses pointer at register $l_{addr}$ and $k_p$ to load value from           |

|                                                        | memory, decrypted under key $k_d$ . Stores the result in                   |

|                                                        | $l_{dest}.$                                                                |

| $\mathtt{store}(l_{addr}, l_{val}, k_p, k_d)$          | Encrypts value at register $l_{val}$ under $k_d$ . Then, stores            |

|                                                        | the encrypted value at the address computed using $l_{addr}$ and $k_{p}$ . |

| $\mathtt{free}(l_{addr}, k_p)$                         | Computes physical address $a$ using $l_{addr}$ and $k_p$ . Then,           |

|                                                        | frees the memory by setting alloc_map[a] == false.                         |

| $\mathtt{hanop}(op, l_{dest}, l_{src_1}, l_{src_2})$   | Performs pointer arithmetic using the values at register                   |

|                                                        | indices $l_{src_1}$ and $l_{src_2}$ . Stores the result in $l_{dest}$ .    |

| $\mathtt{arithop}(op, l_{dest}, l_{src_1}, l_{src_2})$ | Performs an abstract arithmetic operation and returns                      |

|                                                        | a non-pointer value.                                                       |

Table 2.2: The  $U^2$  API

### Memory Safety Vulnerabilities

In addition to the behaviors described in Table 2.2, the load and store operations can potentially trigger a memory safety vulnerability by using an invalid pointer. This has the effect of setting the msv\_curr to true during that step.

# 2.4.3 The $U^2$ Adversary

The U<sup>2</sup> adversary  $\mathcal{A}$  is allowed to start any number of processes and perform arbitrary operations with them. Additionally,  $\mathcal{A}$  comes equipped with an observation function Obs, which enables them to observe certain parts of the state. To model an adversary similar to the one described in the C<sup>3</sup> paper, we let  $\mathcal{A}$ 's Obs function be such that they are allowed to observe any values in their process, in addition to the observable system variable. Intuitively, this means that the adversary has access to any of the values seen by their process, in addition to a microarchitectural side channel that leaks information.

### 2.4.4 Security Properties

We aim to prove two key security properties: confidentiality and integrity. Informally, confidentiality means that the adversary is unable to read the contents of a valid allocation in plaintext through a memory safety vulnerability. Meanwhile, we define integrity to mean that any values stored through a memory safety vulnerability cannot be decrypted back as plaintext, ensuring that  $\mathcal{A}$  is not able to inject arbitrary values or code into other users' memories.

#### Definition 2.1. Confidentiality:

```

msv_curr = true ⇒

(observable.valid = false ∨ observable.g_data.enc_state ≠ Plain)

```

The formula above says that whenever a memory safety vulnerability is triggered, either the data observed through the observable channel is invalid, or the data must not be in plaintext.

#### Definition 2.2. Integrity:

```

\forall a. \  \, \text{alloc\_map}[a] = \text{false} \qquad \qquad \lor \\ \left( isDenc(\text{ghost\_mem}[a].enc\_state) \qquad \qquad \land \\ \left( \text{ghost\_mem}[a].enc\_state.DEnc\_nonce = ghost\_mem}[a].nonce\_true) \right) \qquad \lor \\ isGarbled(\text{ghost\_mem}[a].enc\_state)

```

This formula specifies that at all time steps, any valid allocation must either be decrypted with the correct nance, or it must be garbled.

# 2.5 UCLID5 Model

In this section, we provide an overview of implementation of  $U^2$  in the UCLID5 language. We begin with a brief treatment of the different modules in Section 2.5.1. Then, we move

on to the verification results in Section 2.5.2. For the sake of brevity, we highlight only the most important aspect of each module. We direct readers interested in learning more to either Appendix B or our GitHub repository [17].

#### 2.5.1 Modules

#### The Common Module

We begin our description of our UCLID5 model with a description of the common module. This module contains basic type declarations that the other modules rely on.

```

module common {

type word_t = bv2;

type size_t = word_t;

type opcode_t;

type lmapind_t = bv3;

// Attacker, and Victim keys

```

We note that we model the word type as a 2-bit bit-vector, and the lmap\_ind type as a 3-bit bit-vector. This is done mainly for the sake of simplicity, as larger bit-vectors would likely have no effect on the verification, and would likely only cause the proof to take much longer to finish.

```

// Attacker, and Victim keys

type key_t = enum { AtKey, ViKey };

```

The key\_t type is used to model the keys for each process. Implicitly, this also specifies the number of processes in the system. In our case, we only model the adversary and the victim processes. We argue that there is no need for modeling more processes, as there are no new behaviors introduced with the presence of extra processes. This, again, would only lead to verification being less tractable, which is something we want to avoid at all costs, given that we are modeling a system as complex as U<sup>2</sup>.

The next type declaration we highlight is the algebraic data type used to model cryptography. This consists of a base Pln() constructor, and appropriate constructors for the other states of encryption, for both data and pointers.

Note that we do not model the **free** operation, as this was difficult to model and caused issues with proof convergence<sup>3</sup>.

```

type ghost_data_t = record {

// Raw value

value: word_t,

3

// Value state (i.e. is this a handle or a raw value?)

6

vtype: value_t,

// Handle elements

// Base address (inclusive)

9

10

h_base: word_t,

// This is the current handle offset

11

h_offset: word_t,

// Allocation is [h_base, h_base+h_length)

13

14

h_length: word_t,

// Only modified by the encryption function

17

// Encryption state

enc_state: enc_state_t,

18

// True nonce for that allocation (used for authentication)

19

ca_nonce_true: nonce_t

20

};

21

```

The final type declaration we highlight is the ghost\_data\_t type. This type contains not only the real value stored in physical memory, but also several metadata fields that are necessary for verification:

- The vtype field indicates whether this allocation contains a pointer or raw data.

- The h\_base, h\_length, and h\_offset comprise the allocation's handle. This handle is used to check memory bounds and detect memory safety violations during verification.

- enc\_state tells us which state of encryption this allocation is in. Symbolically, we should know whether the value is in plaintext, encrypted, or decrypted, reagardless of the real value that memory may hold.

- ca\_nonce\_true indicates the true nonce that was created when this allocation was made (by making a call to malloc). This corresponds to keeping track of which CA was made to create the allocation, and ensure that it is that same CA that is used by ensuing memory access in the original C<sup>3</sup> paper.

#### The U<sup>2</sup> Module

We now describe the u2 module. In this module, we create all the necessary state variables, and we also specify the behavior of the init and next blocks. This gives a full description

<sup>&</sup>lt;sup>3</sup>Moreover, the behavior of free is not defined in the original C<sup>3</sup> paper.

of our  $U^2$  system, as the state variables characterize  $\Sigma$ , the init block gives us the set of initial values (*init*), and the next block gives us our transition relation T.

```

// Ghost state

var ghost_mem : ghost_mem_t;

var ghost_lmap : ghost_lmap_t;

// Allocated map

var alloc_map: alloc_map_t;

```

The ghost\_mem and ghost\_lmap variables shown above correspond to the main memory and local memory variables, respectively (augmented with extra data). The alloc\_map variable is used to keep track of which sections of memory have been allocated through calls to malloc.

```

// Current operation was a memory safety vulnerability

var msv_curr : boolean;

// Architectural observable

var observable : observable_t;

```

These msv\_curr variable describes whether a process has triggered a memory safety vulnerability by performing an illegal memory access. The observable variable is used to model the adversary's ability to observe certain parts of memory through other side channels.

```

init {

// Initially all cells are unallocated

assume (forall (a: word_t) :: (!alloc_map[a] && !shadow_mem[a].

alloc));

// Initially all values (in lmap and memory) hold raw data (not

pointers)

```

These variables describe a process's local map. This allows users to keep a private collection of values at any given time.

The init block specifies the initial state of our system. We have three assumptions in the code above:

(1) Initially, all cells are unallocated.

- (2) Initially, all values in the local map are not pointers.

- (3) Initially, all values in main memory are not pointers.

Assumption (1) is used to model a system starting fresh and with all memory available. This aligns with our definitions in Section 2.4. Assumptions (2) and (3) are mostly a matter of simplifying the design. We believe that constraining the program such that all values in main and local memory are initially RAW (i.e. not used as pointers to access memory) is a fairly reasonable assumption to make. Moreover, this drastically reduces the initial state space, and speeds up the verification effort.

Moreover, they simplify verification drastically by constraining the possible initial states of our system.

This block also specifies that the observable variable holds invalid data, and that no memory safety vulnerability has occurred.

```

havoc action;

case

(action == LOAD) : { call load(l1, 12, ViKey, ViKey); }

(action == STORE) : { call store(l1, 12, ViKey, ViKey); }

(action == MALLOC) : { call malloc(l1, ViKey, ViKey); }

(action == HANOP) : { call hanop(opcode, 11, 12, 13); }

(action == ARITHOP) : { call arithop(opcode, 11, 12, 13); }

esac

}

```

Finally, the next block specifies how our C<sup>3</sup> model must transition from one state to the next. In our UCLID5 model, this means that the victim can choose to arbitrarily perform a standard load, store, malloc operation, by following the C<sup>3</sup> scheme. Alternatively, they can perform pointer arithmetic via the hanop operation to create new pointers from data they hold. Finally, we also allow the user to perform some computation on the values in their local map, with the restriction that the result is not used as a pointer later. This last restriction is included to simplify the modeling, but does not change the expressivity of our system.

#### Other Modules

We provide a brief overview of the other modules in our UCLID model.

- The main module contains all the formal properties, and is responsible for performing verification.

- The operations module defines the behavior of the load, store, malloc, hanop, and arith procedures used in the next block of the u2 module.

- The cryptography module defines procedures that implement the behavior of the cryptography using our ADT encoding.

- The contracts module defines a number of macros that are useful for the procedures in the operations and cryptography modules.

- Finally, the shadow\_common, shadow\_u2, and shadow\_operations modules all define the shadow memory, which is a structure that independently keeps track of the allocations of the system, which allocations each address belongs to, and which nonce has been used to encrypt it (if any). The shadow memory serves mostly as an aide in verification.

#### 2.5.2 Verification Results

We proved a total of 24 properties to the correctness of our UCLID5 model. Notably, this includes our confidentiality and integrity properties from Section 2.4.4. Our model was able to prove the properties inductively for the two-process case in a total of 11.64 seconds. The full model, along with instructions of how to run the proofs, can be found in our GitHub repository [17].

### 2.6 Related Work

### Security Analyses of C<sup>3</sup>

C<sup>3</sup> has been the subject of much scrutiny in the security community. Mahzoun, Kraleva, Posteuca, and Ashur show that the K-cipher–the main component used to encrypt pointers in the real C<sup>3</sup> system–is susceptible to differential cryptanalysis attacks [18]. Additionally, Hassan presents four different attacks on the C<sup>3</sup> system in their PhD dissertation [15]:

- 1. They exploit the use of XOR as an encryption primitive to leak confidential values for allocations with known initial values.

- 2. They leverage the lack of bounds-checking during pointer arithmetic operation to forge CAs.

- 3. They take advantage of the low entropy in the Version field of the CA format to violate temporal memory safety.

- 4. They show how the system-level design decision to only protect the heap can be abused to break C<sup>3</sup>'s memory safety guarantees.

We note that these attacks work at a much finer level of detail than what our formal model considers in scope. This only reinforces the vision of our report that security verification must be present at all points of the design process: from the ideation and system specification all the way to the implementation.

#### **UCLID5** for Hardware Security

The work presented in this project builds off prior work in verifying hardware security properties using UCLID5. Prior endeavors in UCLID5 modeling include but are not limited to:

- Creating verifiable models of secure hardware enclaves [19], [20], building off the formal groundwork laid out by Subramanyan et al. in their seminal paper on the Secure Remote Execution of Enclaves [21].

- Creating models of programs and simulating their execution on a speculative processor while exposing certain state to the adversary's observations. [22], [23].

- Formally verifying an open-source hardware implementation of physical memory protection (PMP) in RISC-V [24].

Our work is yet another testament to the versatility of the UCLID5 toolkit to model and verify complex systems where hardware and software interact.

#### Dedicated Cryptographic Verifiers

We would be remiss to overlook the work surrounding other dedicated cryptographic verifiers in recent years. We give a brief overview of some of the most popular verifiers in the literature. We refer the reader to Barbosa et al.'s SoK paper on computer aided cryptography [25] for a more detailed overview into this line of research.

**Tamarin:** A rather popular cryptographic verifier is Tamarin [26]. This prover operates by using multiset rewrite rules and backwards reasoning to automatically find attacks for an unbounded number of sessions. Tamarin has been used in a number of projects to model and verify the security of protocols such as TLS 1.3 [27], 5G Authentication [28], and more.

**ProVerif & CryptoVerif:** ProVerif [29] and CryptoVerif [30] both developed at INRIA, are other examples of cryptographic verifiers. These tools leverage the applied pi calculus [31] to allow users to verify cryptographic protocols in the symbolic and computational models of cryptography, respectively. ProVerif has been used to verify election protocols [32], secure messaging protocols [33], and to automatically find attacks based on hash function weaknesses [34]. CryptoVerif, on the other hand, has been useful for analyzing the soundness of post-quantum security protocols [35] and a number of protocols involving dynamic key compromise [36].

The tools outlined above—being primarily designed with security verification in mind—support cryptographic primitives and constructs natively. This functionality allows users

to use these tools and focus on the modeling and verification of cryptographic protocols. This is an excellent choice when reasoning about the use of cryptography in isolation. We could very well have used any one of these tools to create our formal, abstract model of  $C^3$ . Ultimately, however, we were more interested in modeling  $C^3$  as a hardware-software system. These small details are why we opted to use UCLID5 with ADTs instead.

### 2.7 Conclusion

This chapter introduced  $U^2$ , an abstract system model for  $C^3$ -like systems, modeled in the UCLID5 language. We also proved that our model satisfies our security properties. This work provides a rigorous framework to reason about  $C^3$ -like systems. It is our hope that this project enables architects of  $C^3$ -like systems to think about the security of their designs, or that they are inspired to integrate modeling in UCLID5 or other similar tools into their workflows.

#### 2.7.1 Future Work

#### Modeling

One way in which the work presented in this chapter could be extended is by creating a lower-level model that accurately reflects the behavior of the actual  $C^3$  system more closely. This could include microarchitectural details, such as registers, TLBs, caches, and more. Then, we could show that this lower-level  $C^3$  model refines our  $U^2$  model, which would provide a high degree of confidence on the soundness of the  $C^3$  scheme.

#### UCLID5

Our decision to model cryptographic primitives as ADTs was in part due to necessity. Indeed, UCLID5 does not natively support the kind of probabilistic or computational reasoning that is required to verify a cryptographic system at such a fine level of detail. The best we can do at the time of writing is to model cryptography symbolically. Consequently, one interesting line of research would be to equip UCLID5 with computational and probabilistic reasoning capabilities, which would allow users to make more accurate models and have more precise security guarantees.

# Chapter 3

# BTORSEC:

# A Model-Checking Format for Hardware Security

#### Are we building the thing right?

After validating a high-level system design with a formal model—much like we did with U<sup>2</sup> in Chapter 2—the natural next step is to implement it in RTL. But implementations often introduce bugs that cannot be caught by higher-level specifications. This chapter aims to provide microarchitects and verification engineers with tools to check their implementations for security vulnerabilities with minimal overhead. This chapter addresses Challenges (II) and (III).

# 3.1 Introduction

The previous chapter focused on the specification and verification of security properties in high-level system designs. Using the UCLID5 language, we showed that we can reason about our design by omitting several implementation details and focusing only on the core properties that we wish to satisfy. But while having high-level assurance that our abstract models are secure is useful, the ultimate goal is to ensure that the *implementations* of the models are secure, too. Many things can go wrong when moving from a high-level specification to the real implementation. The devil, as usual, is in the details.

Addressing this implementation-to-specification gap requires new verification approaches that combine the precision of RTL analysis with the abstraction of cryptographic reasoning. To this end, this chapter introduces BTORSEC, a word-level model checking format for hardware designs that employ cryptographic modules. By nature of being a language extension, BTORSEC enjoys many of the properties of BTOR2, such as its simplicity and ease of parsing. Additionally, the new instructions introduced in BTORSEC allow us to express and reason about security-related properties of an RTL design. Notably, these sorts of security prop-

erties are not expressible in the base BTOR2 language. This design philosophy—abstracting cryptographic details while preserving RTL precision—enables a new class of security verification that was previously impractical.

This chapter details both the technical design of BTORSEC and its practical application to hardware verification. Section 3.4 provides an overview of the new instructions added to BTORSEC, explaining our extension of the BTOR2 format in more detail, and what the purpose of each new instruction is. Next, Section 3.5 gives a detailed explanation of the compilation pipeline, from the initial (System)Verilog design to the final BTORSEC file. Section 3.6 introduces SSV, our prototype model checker for BTORSEC security properties. Section 3.7 compares and contrasts our approach to hardware security verification to existing approaches in the literature. Finally, we conclude the chapter in Section 3.8 by summarizing our work and providing directions for future research.

### 3.2 Contributions

In summary, this chapter makes the following contributions:

- 1. We propose BTORSEC, an extension of the BTOR2 model-checking format that adds abstract cryptographic instructions.

- 2. We introduce a compilation pipeline that allows users to create BTORSEC files from existing Verilog designs with minimal engineering overhead.

- 3. We implement a bounded model checking tool, SSV, for checking confidentiality properties of BTORSEC programs.

# 3.3 Background

This section provides some relevant technical background that is useful in understanding the approach to hardware verification we present in this chapter. We begin with a quick introduction to the Verilog and BTOR2 languages. We emphasize the usefulness of the BTOR2 format as an intermediate representation of hardware designs, motivating our decision to create its BTORSEC extension, presented in Section 3.4. We then proceed to cover some basic formal verification techniques that will be useful in describing our approach to verifying BTORSEC programs in Section 3.6.

# 3.3.1 Hardware Design

This subsection provides a brief introduction to the Verilog, SystemVerilog, and BTOR2 languages, focusing on the aspects most relevant to hardware modeling and formal verification. We give a simple introduction of the popular Verilog and SystemVerilog hardware description languages. We also stress the BTOR2 format's role as an intermediate representation

#### A MODEL-CHECKING FORMAT FOR HARDWARE SECURITY

for model checking. This background will equip the reader with the necessary context to understand the modeling choices and verification workflows presented in subsequent sections.

#### Verilog and SystemVerilog

Verilog [37] is a hardware description language (HDL) originally developed in the 1980s for modeling and simulating digital circuits. It provides a C-like syntax for describing hardware behavior at multiple levels of abstraction, from gate-level implementations to high-level behavioral descriptions. Verilog became an IEEE standard (IEEE 1364) and remains one of the most widely used HDLs in the semiconductor industry for designing everything from simple logic circuits to complex processors and system-on-chips (SoCs).

SystemVerilog [38], introduced in the early 2000s, is a significant extension and enhancement of Verilog that addresses many of the original language's limitations. Beyond traditional hardware description capabilities, SystemVerilog adds powerful verification features including object-oriented programming constructs, constrained random testing, assertions, coverage metrics, and interfaces.

Given the similarity of these two languages, we will use the terms "Verilog" and "SystemVerilog" interchangeably. Below is a simple example of a (System)Verilog module describing a flip-flop register:

```

module top (

input clk,

input [31:0] in,

output [31:0] out

);

5

6

reg [31:0] ff;

// Sequential logic

9

always @(posedge clk) begin

ff <= in;

11

12

end

13

14

assign out = ff;

endmodule

```

Figure 3.1: Flip-Flop Verilog Module

Lines 1-5 declare the module. Since this is the top-level module, it is named top. These lines also declare the input and output ports, in this case:

- a 1-bit input port, clk, corresponding to the clock,

- a 32-bit input port, in, corresponding to the input data, and

- a 32-bit output port, out, corresponding to the output data.

24

#### A MODEL-CHECKING FORMAT FOR HARDWARE SECURITY

Line 7 declares a 32-bit register named ff. Then, lines 10–12 describe the behavior of the module:

- Line 10 indicates that the behavior in the block should happen at each rising edge of the clk signal (always @posedge clk).

- Line 11 indicates that the register ff should store the value in.

Finally, line 14 declares that the out port should have the same value as the ff register.

#### B<sub>T</sub>or2

BTOR2 [3] is a word-level model checking format for capturing models of hardware in a bit-precise manner. It is largely similar to its predecessor, BTOR, with the main difference between the two being the addition of explicit sort declarations. By design, the BTOR2 format is minimalist and line-based. Consequently, it is also easy to parse, making it well-suited to interface with solvers and other verification tools. Let us continue our simple flip-flop module example. The BTOR2 representation of the Verilog module is shown in Figure 3.2.

Figure 3.2: Btor2 Code for Flip-Flop Module

Let us break down this simple BTOR2 program line by line. Each line of a BTOR2 program consists of a line identifier (which we will refer to as lid), followed by the name of the instruction, followed by the arguments of the instruction. These line identifiers are then used as references for other instructions. Comments are denoted with a ';' and any text following the ';' is ignored¹. In general, BTOR2 instructions look something like this:

```

<lid> inst <params>*

```

<sup>&</sup>lt;sup>1</sup>The comment at the top of the file is simply output created by the Yosys at the time of compiling the program.

The first line of the program is 1 sort bitvec 1, which means that any subsequent instruction that uses this sort will be a 1-bit bit-victor.

The second line, 2 input 1 clk indicates that the lid 2 is associated with an input of sort 1 (i.e. a 1-bit bit-vector) named clk.

Similarly, the third line of the program, 3 sort bitvec 32, declares the lid 3 as a 32-bit bit-vector.

Line 4, much like line 2, indicates that lid 4 now refers to an input of sort 3 (a 32-bit bit-vector) named in.

Line 5 declares a state variable (i.e. a reg in Verilog terms) of sort 3 named ff.

Line 6 declares that the value of lid 5 is an output named out.

Finally, line 7 states that, at each transition, the state variable at 5 of sort 3 will take on the value of 4.

Despite BTOR2's simple syntax, it is rather difficult to glean the purpose of a BTOR2 program by simply looking at one. Thankfully, BTOR2 files are not meant to be written or read by humans in the way Verilog files are. For the purposes of this project, the role of BTOR2 is mostly to act as an intermediate representation of Verilog modules that is easier to work with.

#### 3.3.2 Formal Verification Techniques

We now provide a brief overview of some formal verification techniques referenced in this chapter. Of particular relevance are the symbolic simulation and fixed-point computation techniques. This is because our prototype checker for BTORSEC, SSV, employs a combination of these methods. While SAT and SMT solving serve as the underlying engines that implement these techniques, they are not the primary focus of this work; nonetheless, a basic understanding of them is beneficial for context.

#### **Boolean Satisfiability**

We provide a brief overview of the Boolean Satisfiability problem, better known as SAT. The SAT problem consists of asking the following question: given a Boolean formula<sup>2</sup>  $\phi$  with variables  $v_1, v_2, v_3, ...$  that are all either True or False, is there some assignment of True and False to these variables such that the overall value of the formula  $\phi$  is True? As an example, consider the following Boolean formula:

$$\phi \coloneqq (v_1) \land (\neg v_1 \lor \neg v_2).$$

Then if we assign  $v_1 = True$  and  $v_2 = False$ , we have that  $(v_1)$  evaluates to True and  $(\neg v_1 \lor \neg v_2)$  evaluates to True as well. Therefore,  $(v_1) \land (\neg v_1 \lor \neg v_2)$  also evaluates to True. Since there exists some assignment of True and False to  $v_1$  and  $v_2$  that makes  $\phi$  evaluates

<sup>&</sup>lt;sup>2</sup>That is, a formula that can only be evaluated to *True* or *False*.

to True, we say that  $\phi$  is satisfiable (or SAT, for short). We also say that  $v_1 = True$  and  $v_2 = False$  is a satisfying assignment.

The counterpart of a satisfiable formula is an unsatisfiable (UNSAT) formula, in which no assignment of True and False can make the overall formula True. For instance, the formula

$$\psi \coloneqq (v_1) \land (\neg v_1)$$

is very clearly unsatisfiable. If we assign  $v_1 = True$ , then  $\neg v_1 = False$ ; similarly, if we choose to make  $\neg v_1 = True$ , then  $v_1 = False$ . In any case,  $\psi$  will always be False.

SAT solvers essentially check *every possible assignment* of variables until they find a satisfying assignment. If at any point such an assignment is found, then the solver declares the formula in question to be SAT and returns the satisfying assignment to the user. On the other hand, if the solver exhausts all the assignments and does not manage to make the formula SAT, then it terminates and declares the formula to be UNSAT.

SAT technology has proven exceptionally useful in practice. It has been used to solve longstanding problems in mathematics, such as the Pythagorean Triples problem [39], and it is also a fundamental tool used in hardware verification in industry [40], [41]. Readers interested in learning more about SAT solving are directed to the wonderful papers *The Science of Brute Force* [42] by Heule and Kullmann and *Boolean Satisfiability: From Theoretical Hardness to Practical Success* [43] by Malik and Zhang.

#### Satisfiability Modulo Theories

Satisfiability Modulo Theories (SMT) is the natural extension of SAT to more expressive theories. We now provide a formal definition of SMT, as well as some theories of interest for the present study. We have obtained these definitions from the *Handbook of Satisfiability* [44] and from Marker's *Model Theory: An Introduction* [45]. We refer the reader to those texts for a more thorough treatment on SMT and model theory, respectively.

**Problem Statement:** Let us define the SMT problem more rigorously. A signature  $\Sigma$  is a set of *predicate* and *function* symbols, each with an associated *arity*. For clarity, we let  $\Sigma^P \subseteq \Sigma$  be the set of predicate symbols and  $\Sigma^F \subseteq \Sigma$  be the set of function symbols. We call the 0-arity function symbols *constant* symbols and the 0-arity predicate symbols *propositional* symbols. A  $\Sigma$ -structure  $\mathcal{M}$  is a pair consisting of a set M, called the underlying universe, and a mapping  $(\cdot)^{\mathcal{M}}$  that assigns

- 1. to each constant symbol  $c \in \Sigma^F$  an element  $c^{\mathcal{M}} \in M$ ,

- 2. to each function symbol  $f \in \Sigma^F$  of arity n > 0 a total function  $f^{\mathcal{M}} : M^n \to M$ ,

- 3. to each propositional symbol  $B \in \Sigma^P$  a value  $B^{\mathcal{M}} \in \{True, False\}$ , and

- 4. to each predicate symbol  $p \in \Sigma^P$  of arity n > 0 a function  $p^{\mathcal{M}} : M^n \to \{True, False\}$ .

Furthermore, we denote the set of  $\Sigma$ -terms as the smallest set  $\mathcal{T}$  such that

- (i)  $c \in \mathcal{T}$  for every constant symbol  $c \in \Sigma^F$ ,

- (ii) each variable symbol  $c_i \in \mathcal{T}$  for i = 1, 2, ..., and

- (iii) if  $t_1, ..., t_{n_f} \in \mathcal{T}$  and  $f \in \Sigma^F$  with arity  $n_f$ , then  $f(t_1, ..., t_{n_f}) \in \mathcal{T}$ .

Conceptually, the set of terms  $\mathcal{T}$  contains all the constant symbols, the variable symbols, and all applications of functions to other terms.

Let  $\phi$  be a formula with free variables from  $\overline{v} = (v_{i_1}, v_{i_2}, ..., v_{i_m})$ , and let  $\overline{a} = (a_{i_1}, a_{i_2}, ..., a_{i_m}) \in M^m$ . We inductively define  $\mathcal{M} \models \phi(\overline{a})$  as follows:

- (i) If  $\phi$  is  $t_1 = t_2$ , where  $t_1, t_2 \in \mathcal{T}$ , then  $\mathcal{M} \models \phi(\overline{a})$  if  $t_1^{\mathcal{M}}(\overline{a}) = t_2^{\mathcal{M}}(\overline{a})$ .

- (ii) If  $\phi$  is  $B \in \Sigma^P$ , then  $\mathcal{M} \models \phi(\overline{a})$  if  $B^{\mathcal{M}} = True$ .

- (iii) If  $\phi$  is  $p(t_1,...,t_{n_n})$  where  $p \in \Sigma^P$ , then  $\mathcal{M} \models \phi(\overline{a})$  if  $p(t_1^{\mathcal{M}}(\overline{a}),...,t_{n_n}(\overline{a})^{\mathcal{M}}) = True$ .

- (iv) If  $\phi$  is  $\neg \psi$ , then  $\mathcal{M} \vDash \phi(\overline{a})$  if  $\mathcal{M} \not\vDash \psi(\overline{a})$ .

- (v) If  $\phi$  is  $(\psi \wedge \theta)$ , then  $\mathcal{M} \models \phi(\overline{a})$  if  $\mathcal{M} \models \psi(\overline{a})$  and  $\mathcal{M} \models \theta(\overline{a})$ .

- (vi) If  $\phi$  is  $(\psi \vee \theta)$ , then  $\mathcal{M} \models \phi(\overline{a})$  if  $\mathcal{M} \models \psi(\overline{a})$  or  $\mathcal{M} \models \theta(\overline{a})$ .

- (vii) If  $\phi$  is  $\exists v_j \ \psi(\overline{v}, v_j)$ , then  $\mathcal{M} \vDash \phi(\overline{a})$  if there is some  $b \in M$  such that  $\mathcal{M} \vDash \psi(\overline{a}, b)$ .

- (viii) If  $\phi$  is  $\forall v_j \ \psi(\overline{v}, v_j)$ , then  $\mathcal{M} \vDash \phi(\overline{a})$  if for every  $b \in M$ ,  $\mathcal{M} \vDash \psi(\overline{a}, b)$ .

If  $\mathcal{M} \vDash \phi(\overline{a})$ , then we say that  $\mathcal{M}$  satisfies  $\phi(\overline{a})$ . Naturally, we say that for any formula  $\phi(\overline{v})$ , if there exists some  $\Sigma$ -structure  $\mathcal{M}$  and  $\overline{a} \in M^n$  such that  $\mathcal{M} \vDash \phi(\overline{a})$ , we say that  $\phi$  is satisfiable.

A sentence is a formula with no free variables. A  $\Sigma$ -theory<sup>3</sup> T is a set of sentences that uses only symbols from  $\Sigma$ . We say that a  $\Sigma$ -structure  $\mathcal{M}$  is a model of a theory T if  $\mathcal{M} \vDash \phi$  for every  $\phi \in T$ . We denote this as  $\mathcal{M} \vDash T$ .

Therefore, the problem of Satisfiability Modulo Theories can be stated as follows: given a signature  $\Sigma$ , a formula  $\phi(\overline{v})$ , does there exist some  $\Sigma$ -structure  $\mathcal{M}$  and  $\overline{a} \in M^n$  such that  $\mathcal{M} \models T$  (i.e.  $\mathcal{M}$  is a model of T) and  $\mathcal{M} \models \phi(\overline{a})$  (i.e.  $\phi(\overline{v})$  is satisfied in  $\mathcal{M}$ )?

We now give a brief description of some theories of interest, courtesy of [44].

Fixed-Width Bit-Vectors: Given that we are working with digital circuits, the theory of fixed-width bit-vectors is of great importance to us. There are many formulations for the theory of fixed-width bit-vectors. Generally, they all share the characteristic that constant symbols are used to represent bit-vectors and that each bit-vector has an associated width (i.e. the number of bits it contains). In this work, we consider the theory as specified by the SMT-LIB standard [46], which is also the theory that is used by Z3 [47], the SMT solver that SSV uses for its backend.

<sup>&</sup>lt;sup>3</sup>Oftentimes abbreviated to just theory if the signature  $\Sigma$  in question is clear from context.

What differs among the different theories are the predicate and function symbols, which may include extraction, concatenation, bit-wise Boolean operations, and arithmetic operations. Reasoning at the level of bit-vectors offers a more compact representation of the problem, which lends to more efficient verification than using bit-level reasoning.

Arrays: This theory captures our intuitive notion of how arrays behave by characterizing and axiomatizing the *read* and *write* operations. Formally, we let  $\Sigma_A$  be the signature (*read*, *write*). We consider the following sentences as the axioms that comprise the theory of arrays (with extensionality),  $T_A$ :

```

\forall a \forall i \forall v. \ (read(write(a, i, v), i) = v)

\forall a \forall i \forall j \forall v. \ (i \neq j \Rightarrow read(write(a, i, v), j) = read(a, j))

\forall a \forall b. (\forall i. (read(a, i) = read(b, i)) \Rightarrow a = b)

```

#### Model Checking

Model checking is a verification technique that provides an algorithmic means of determining whether an abstract model—representing, for example, a hardware or software design—satisfies a formal specification expressed as a temporal logic formula [48]. It systematically explores all possible states of a system to check properties like safety ("nothing bad happens") and liveness ("something good eventually happens"). If the property fails, model checking provides a counterexample showing exactly how the system can reach an undesired state. It is widely used in hardware verification, protocol analysis, and concurrent software systems because it can catch subtle bugs that are hard to detect through testing alone.

Bounded Model Checking (BMC) is a variant of model checking where, instead of exploring all possible states, BMC unrolls the system's transition relation for a limited number of steps and encodes it as a logical formula, typically solved with a SAT or SMT solver. If the formula is satisfiable, a counterexample of that length exists; if not, the property holds within the bound. BMC is especially useful for finding bugs quickly in hardware designs and software with loops, though it cannot prove correctness beyond the chosen bound.

#### Symbolic Simulation

Symbolic simulation is a verification technique where, instead of running a system with concrete input values, the system is executed using symbolic inputs that represent many possible values at once [49]. The outputs are expressed as symbolic expressions, allowing the analysis of multiple execution paths simultaneously. This approach is useful for detecting errors in hardware or software designs, exploring corner cases efficiently, and generating test cases.

#### Fixed Point Computation

Fixed-point computation is a method used in program analysis and formal verification to find a stable state of a system or function—one where applying the function again produces the same result. In verification, it's often used to compute properties like reachable states, invariants, or loop behaviors by iteratively applying a transition relation until no new states are discovered. This technique is fundamental for reasoning about recursive systems, loops, and other repetitive behaviors in both hardware and software models. This kind of reasoning is often implemented by using mathematical objects called constrained Horn clauses, and it has shown to have a number of applications to program verification [50], [51].

# 3.4 Language Extension

When it comes to security verification, BTOR2 programs face several fundamental limitations. For one, the format has no support for cryptographic primitives. But even if we were to add native cryptographic instructions to BTOR2, how would we even get the security-relevant information in the first place? In this section, we describe the BTORSEC, our extension of the BTOR2 language, in more detail. Section 3.4.1 provides an overview of the new abstract cryptographic instructions of the language. Section 3.4.2 introduces the SECSPECS, a construct that allows users to easily specify security-relevant metadata about a hardware design.

## 3.4.1 Cryptographic Instructions

BTORSEC adds 15 new instructions to the base BTOR2 language. These include a new sort, acsort, which represents abstract cryptographic objects like messages and keys. It also includes primitives for key generation, encryption, and more. A summary of all the new instructions can be found in Table 3.1. The rest of this subsection will be dedicated to explaining the functionality of each of these instructions in further detail. Readers who desire a more formal description of the syntax of BTORSEC are directed to Section E.1.

#### General

These instructions are the core foundations of any BTORSEC design. They include a new sort declaration, acsort, as well as the acnondet, public, and confidential instructions. Below, we provide a detailed breakdown of this class of cryptographic instructions.

#### d> acsort <width>