## Low Voltage Silicon Dioxide Reliability

by

Klaus Florian Schuegraf

B.S. (Rensselaer Polytechnic Institute) 1987 M.S. (Stanford University) 1988

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering- Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY of CALIFORNIA at BERKELEY

Committee in charge:

Professor Chenming Hu, Chair Professor Andrew Neureuther Professor Leo Falicov

# The dissertation of Klaus Florian Schuegraf is approved:

j/fre April 28, 1994

Chair Date

LM. FALION APR 28 1994

Date

Andrew Murultus Amezo, 1994

University of California at Berkeley

# Low Voltage Silicon Dioxide Reliability

Copyright © 1994

by

Klaus Florian Schuegraf

#### Abstract

# Low Voltage Silicon Dioxide Reliability

by

### Klaus Florian Schuegraf

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California at Berkeley

# Professor Chenming Hu, Chair

This study investigates the low voltage breakdown and conduction properties of thin thermal silicon dioxides with thickness ranging from 25 Å to 130 Å using silicon metal-oxide-semiconductor (MOS) capacitors and transistors.

Investigation of oxide breakdown shows that anode hole injection is the likely mechanism responsible for silicon dioxide wearout. A quantitative model for oxide breakdown based on anode hole injection is proposed. This model not only agrees with the predictions of an empirical inverse oxide field model ("1 over E model"), it offers a methodology to extrapolate high field oxide breakdown data into the low voltage operating regime. Investigation of low voltage silicon dioxide tunneling current shows that leakage current increases dramatically above that predicted by the Fowler-Nordheim theory for oxide voltages less than 3.15 Volts, possibly setting a scaling limit on thickness at 40 Å.

The model is also used to compare the breakdown of p<sup>+</sup> and n<sup>+</sup> polysilicon gate, showing no change in damage initiation mechanism. The temperature dependence of breakdown is also investigated, showing that anode hole injection models the breakdown characteristics accurately for temperatures below 150° C. The temperature

acceleration of breakdown is attributed to the oxide's reduced hole immunity at higher

temperatures.

The anode hole injection model is thereby shown to model the breakdown

characteristics of defect-free, "intrinsic" oxide very accurately. A defect model

combining the breakdown mechanism of anode hole injection with "effective thinning"

is able to characterize defect breakdown distributions by attributing the breakdown to

an effective thinning of the oxide at some localized point.

Substrate current measurements during electrical breakdown stress establish the basis

for the anode hole injection model. Investigations of substrate current in oxides thinner

than 55 Å show that the anode hole injection current becomes dominated by the

tunneling of valence-band electrons by means of either trap-assisted-tunneling through

stress-induced traps in oxides between 45 and 55 Å or direct tunneling in oxides thinner

than 45 Å. Nevertheless, the anode hole injection model derived for thicker oxides

holds for the thinner oxides as well, despite the impediment to direct verification.

The dissertation of Klaus Florian Schuegraf is approved:

Professor Chenming Hu

Date

in the April 28, 1994

Committe Chairman

2

To my family

# Table of Contents

| Chapter | 1 Introduction                          | 1  |

|---------|-----------------------------------------|----|

| 1.1     | Introduction                            |    |

| 1.2     | Time-dependent dielectric breakdown     |    |

| 1.3     | Intrinsic breakdown                     |    |

| 1.4     | Hole-induced breakdown model            |    |

| 1.5     | References                              |    |

|         |                                         |    |

| Chapter | 2 Intrinsic Low Voltage Breakdown Model | 12 |

| 2.1     | Introduction                            |    |

| 2.2     | Experiment                              |    |

| 2.3     | Anode Hole Injection Model              |    |

| 2.4     | Oxide Tunneling Current                 |    |

|         | 2.4.1 Polysilicon Depletion             |    |

|         | 2.4.2 Thin Oxide Conduction Model       |    |

| 2.5     | Breakdown Lifetime                      |    |

| 2.6     | Supply Voltage Limits                   |    |

| 2.7     | Summary and Conclusions                 |    |

| 2.8     | References                              |    |

| Chapter 3 Gate Material Dependence of Anode Hole Injection | 40 |

|------------------------------------------------------------|----|

| 3.1 Introduction                                           |    |

| 3.2 Experiment                                             |    |

| 3.3 Results and Discussion                                 |    |

| 3.4 Conclusions                                            |    |

| 3.5 References                                             |    |

|                                                            |    |

| Chapter 4 Temperature Acceleration of Breakdown            | 51 |

| 4.1 Introduction                                           |    |

| 4.2 Temperature Acceleration                               |    |

| 4.2.1 Charge to Breakdown                                  |    |

| 4.2.2 Time to Breakdown                                    |    |

| 4.3 Summary and Conclusions                                |    |

| 4.4 References                                             |    |

|                                                            |    |

| Chapter 5 Effect of Defects                                | 64 |

| 5.1 Introduction                                           |    |

| 5.2 Defect-Related Breakdown Model                         |    |

| 5.3 Supply Voltage Limits                                  |    |

| 5.4 Summary and Conclusions                                |    |

| 5.5 References                                             |    |

| Chapter 6 Limit of Substrate Current in Predicting SiO <sub>2</sub> Breakdown | <b>7</b> 8 |

|-------------------------------------------------------------------------------|------------|

| 6.1 Introduction                                                              |            |

| 6.2 Experiment                                                                |            |

| 6.3 Substrate Current: Anode Hole Injection                                   |            |

| 6.4 Substrate Current: Valence-Band-Electron Tunneling                        |            |

| 6.5 Substrate Current: Valence-Band-Electron Trap-Assisted Tunneling          |            |

| 6.6 Oxide Reliability Prediction: Anode Hole Injection Model                  |            |

| 6.7 Summary and Conclusions                                                   |            |

| 6.8 References                                                                |            |

|                                                                               |            |

| Chapter 7 Summary, Conclusions and Future Work                                | 96         |

| 7.1 Introduction                                                              |            |

| 7.2 Breakdown Process                                                         |            |

| 7.3 Oxide Technology Developments                                             |            |

| 7.3.1 Bulk and Interface Charge Trapping: Incorporation of                    |            |

| Cl, F, and N in SiO <sub>2</sub>                                              |            |

| 7.3.2 Stacked Thermal/CVD SiO <sub>2</sub>                                    |            |

| 7.4 Future Dielectric Needs for Silicon MOS Technology                        |            |

| 7.5 Summary and Conclusions                                                   |            |

| 7.6 References                                                                |            |

|                                                                               |            |

| Appendix I List of Acronyms                                                   | 118        |

# Acknowledgments

This thesis begets my most sincere gratitude for Professor Chenming Hu who served as my research advisor. Without Chenming's dedicated support, guidance, encouragement, and, above all, belief in my ability, I doubt very much that this thesis or my doctoral program would have reached fruition. I am very grateful for the "second chance" granted me and hope this thesis is but the first opportunity to display the education that Chenming has invested so much of his time and energy in. His enthusiasm, insight, standards of rigor and excellence will be sorely missed. His modesty, friendliness and approachability set the standards we should all aspire to.

I would also like to acknowledge the late Professor Shyh Wang, my previous research advisor, for his commitment to the belief that an education in the natural sciences requires schooling in fundamental math and physics. His patience and provision of the resources necessary to pursue graduate coursework in the physics department attests to this vision. He wished his students would pursue research of long-term and fundamental value to industry; I hope that my attempts satisfied this hope.

I am grateful to Professors Ping Ko, Andy Neureuther and Leo Falicov for serving on my qualifying examination committee and their subsequent role in providing the feedback leading to this manuscript. I would also like to thank the Microfabrication Laboratory staff, especially Katalin Voros, Robert Hamilton and Tariq Haniff, for their help in providing a friendly and functioning environment for device fabrication. I would also like to express my utmost gratitude to the Joint Services Electronics Program (JSEP) for its financial support in the form of a most generous fellowship grant. It is my deepest hope that this work satisfies the JSEP Technical Coordinating

Committee's mission of fertilizing technological research vital to our national security interests. I reiterate my thanks for the trust that James Mink, Kenneth Davis and Horst Wittman placed in my abilities, not to mention the privilege of being supported by a program rooted in the legacy of Vannevar Bush.

It has been a privilege to interact with the students belonging to the solid-state device and quantum electronics research groups. They have brought insight, intelligence, entertainment and friendship to my tenure at Berkeley. Although by no means exhaustive, I would like to thank Fariborz Assaderaghi, Olga Blum, Mansun Chan, Jian Chen, Kai Chen, Gary Fedder, Mark Hadley, Patrick Harshman, Jian-Hui Huang, Kelvin Hui, Mike and Jack Judy, Julie Kenrow, Joe King, John Krick, Scott Kuusinen, Chester Li, Zhi-Hong Liu, Dave Loconto, James Ma, Eric Minami, Reza Moazzami, Donggun Park, Steve Parke, Khandker Quader, Bob Ried, Elyse Rosenbaum, Hyungcheol "Huck" Shin, Yaron Simler, Jay Tu, Robert Tu, Ashish Verma, Clement Wann, Kirt Williams and George Zhang for the interactive and fertile environment they shaped.

I would also like thank a few key friends and mentors who provided the support and encouragement for perseverance when it was most sorely needed. Firstly, I would like to thank Professor Robert M. Gray at Stanford University for suggesting the transfer to the University of California, Berkeley. I could not have surmised at the time how fortuitous I would discover this advice to be. I would like to thank Raymond and Vara Kraft, Rana "Ellen" Khayata, John Kibarian, Eric Boskin, Fariborz Assaderaghi, Patrick Harshman and Scott Silverman for believing in me, listening to me and helping me weather the storms; they have proved instrumental and I wonder who I would be without the time and energy they have given so selflessly.

# Chapter 1

### Introduction

### 1.1. Introduction

This chapter introduces the problems pertaining to the reliability of thin silicon dioxide in its use as an insulating material in silicon based integrated circuit technology. Silicon dioxide, a natural oxide of silicon, is an amorphous insulator displaying excellent interfacial properties, i.e. high silicon-silicon dioxide barrier height, excellent reproducibility and stability, etc., which enable the realization of commercially viable, high density integrated circuits of bipolar and field effect transistors (FET) on silicon substrate. Since the successful commercialization of silicon gate FET circuits in 1972, scaling of all device features, i.e. channel length, gate oxide thickness, junction depths, etc., has led to a more than 16000-fold increase in circuit density and a concommitant increase in circuit performance, enabling technological advance from centralized to personalized information processing and computing.

This scaling [1.1,1.2,1.3] has led to a reduction in FET gate length from 5 microns in 1976 to 0.5 microns in 1992, with 0.25 micron development efforts being vigorously pursued world-wide by leading-edge industrial concerns. The gate insulator thickness has also been scaled from more than 1000 Å, to below 100 Å. Due to adherence to industry standards, supply voltages have generally not been decreased; therefore, transistors belonging to subsequent generations of technology operate under everincreasing electric fields. These high operating fields pose considerable risk to reliable circuit operation and have fertilized active research in the understanding of the

mechanisms which lead to the high-field degradation and wear-out observed in silicon MOSFETs.

A major recent industry trend is a move toward decreased power supply voltages, motivated by the desire to deliver integrated circuits with lower power consumption. Not only does this trend have important reliability ramifications, it also marks the arrival of "environmentally correct" applications. For instance, Digital Equipment Corporation has repeatedly advertised its "green" personal computer in the New York Times this spring[1.4]. Federal government procurement regulations also promise to accelerate the advance of low-power, energy-efficient computing. In addition to promising more energy efficient circuits and systems, this trend will enable an accelerated introduction of portable electronic systems, since reduced power consumption translates directly into extended battery life, not to mention enhanced consumer mobility and applications flexibility.

Therefore, understanding transistor reliability issues in the low voltage regime is a crucial milestone in the advance of silicon integrated circuit technology. This thesis focuses on one particular aspect of integrated circuit reliability, the breakdown of thin silicon dioxide at low voltages. The remainder of this first chapter introduces the important breakdown issue by reviewing the previous state of the art.

### 1.2. Time-dependent dielectric breakdown

The scaling of device dimensions, resulting in the thinning of oxide dielectrics in VLSI (Very Large Scale Integration) technologies, is driven by the desire to deliver more MOSFET current and, hence, circuit speed at low voltages for digital logic applications, to provide the same capacitance within a smaller area for DRAMs (Dynamic Random Access Memories), and to offer lower programming voltages for

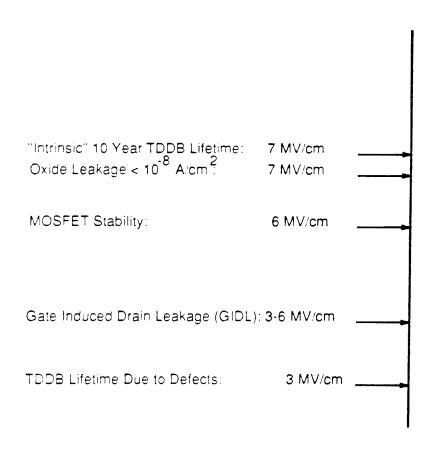

non-volatile memories. Due to the high fields present in the silicon oxide mandated by this aggressive dielectric scaling and the presence of oxide defects, catastrophic failure of the dielectric has always been the predominant oxide reliability concern, thereby limiting scaling. Figure 1.1 illustrates the oxide fields at which specific reliability concerns are raised [1.1,1.5].

Since practical considerations limit the oxide integrity assessment on actual circuits, the oxide integrity question is usually abstracted to the breakdown study of capacitors whose area is comparable to or larger than the area of active transistor area in the circuit. We need to arrive at an accelerated testing paradigm which allows the engineer to extrapolate the lifetime of good product, based on a minimal number of short time, high field accelerated tests. This research focused on the development of techniques which allow an engineer to determine whether or not his or her oxide technology is sufficiently robust to guarantee the lifetime specification of her product at its intended operating voltage, including today's operating voltages at or below 3.3 Volts.

### 1.3. Intrinsic Breakdown

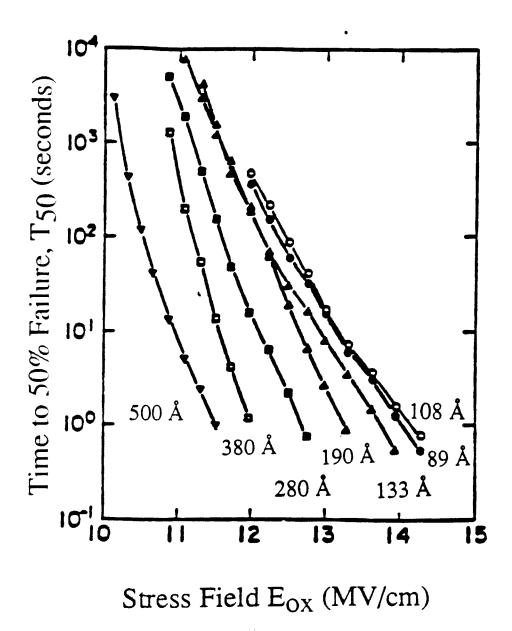

The term intrinsic breakdown refers to the breakdown of an oxide that is free of defects, thereby reflecting the practical upper limit of oxide reliability. Intrinsic lifetime can be determined either from the 100% cumulative failure point in the failure distribution or by measuring breakdown lifetime of small area test structures. Figure 1.2 illustrates the use of widely used E-method introduced by Berman [1.6,1.7] for projecting the lifetime from high-field stress data. This extrapolation method assumes an empirical linear relationship between the logarithm of the breakdown lifetime and applied stress field  $E_{OX}$ , such that

$$t_{bd} = \tau \exp\left(\frac{-\beta V_{ox}}{X_{ox}}\right)$$

(1.1)

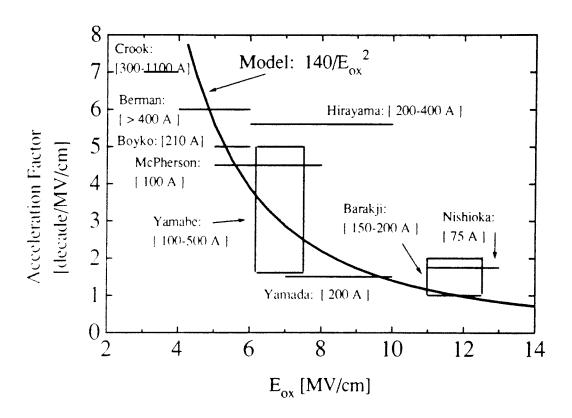

where the electric field acceleration factor  $\beta$  reported in the literature has varied widely, from 7 to 1.5 decade/(MV/cm) as shown in Figure 1.3 [1.8]. Since a small variation in  $\beta$  can lead to orders of magnitude error in the extrapolated lifetime, the wide variation of  $\beta$  cast considerable doubt on this technique as an acceptable accelerated testing paradigm. Using Eq. (1.1), the statistical  $t_{bd}$  data under a high stress voltage can be used to predict the statistical distribution of oxide lifetime at a low operating voltage.

### 1.4. Hole-induced breakdown model

Unlike the aforementioned E-model, this model rests on a physical model for breakdown. As a result of the passage of electrons at high field, holes are created in the oxide or at the interfaces. Furthermore, experiments [1.9,1.10,1.11] have shown that an oxide's lifetime is the time required for the hole fluence,  $Q_p(t)$ , to reach some critical value  $Q_p$ , independent of the stress voltage. The hole fluence can be modeled as

$$Q_p(t) \propto J_p \alpha t$$

(1.2)

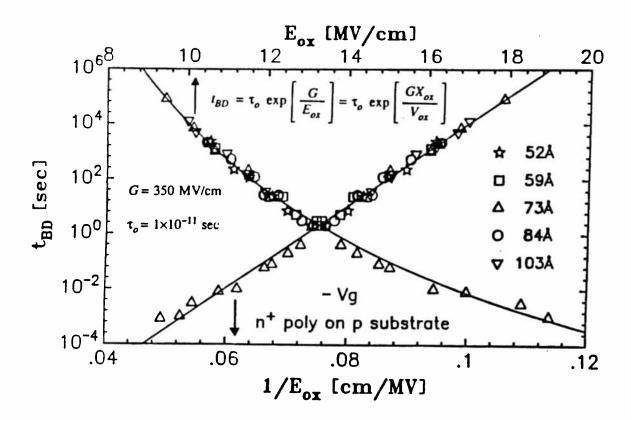

where  $J_n \propto e^{-B/E_{ox}}$  is the Fowler-Nordheim tunneling current density with  $B \approx 270~\text{MV/cm}$  (the slightly larger value of B than the usual 250 MV/cm) accounts for the omission of the  $E_{ox}^2$  term in the  $J_n$  expression) and  $\alpha \propto e^{-H/E_{ox}}$  is the hole generation coefficient [1.12] with  $H \approx 80~\text{MV/cm}$ . Therefore the hole fluence follows

$$Q_{p}(t) \propto e^{-G/E_{ox}} \cdot t$$

(1.3)

where  $G = B + H \approx 350 \text{ MV}$  / cm. The breakdown time,  $t_{bd}$ , corresponds to the point at which  $Q_p(t)$  reaches its critical value; therefore,  $t_{bd}$  has the following field dependence:

$$t_{bd} = \tau_o \cdot e^{5/E_{co}}$$

(1.4)

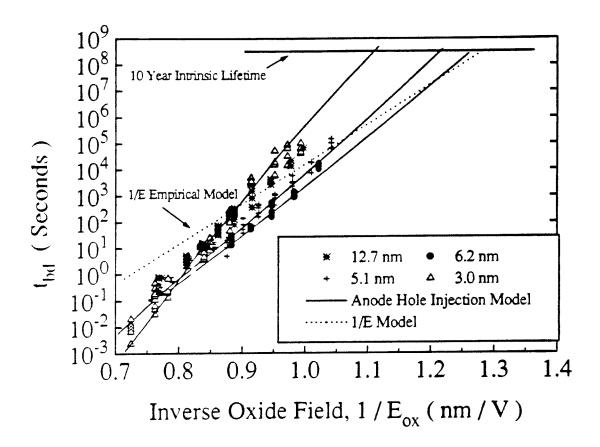

$\tau_{\rm O}$  was empirically found [1.13] to be  $10^{-11}$  seconds. This theory, corroborated by the data in Figure 1.4, indicates that linear extrapolation of lifetime with respect to inverse field,  $1/E_{\rm OX}$ , is more accurate than the  $E_{\rm OX}$  extrapolation. Moreover, the "electric field acceleration factor,"  $\beta$ , which is defined as the slope of  $\log$  ( $t_{\rm BD}$ ) versus  $E_{\rm OX}$  curve, can be written as

$$\beta = \frac{-d \left(\log \left(t_{bd}\right)\right)}{d E_{ox}} = \frac{G}{2.3 E_{ox}^2} = \frac{140}{E_{ox}^2} \left[\frac{decade}{MV/cm}\right]$$

(1.5)

such that  $\beta$  cannot be constant, but is instead proportional to  $\frac{1}{E_{ox}^2}$ . Figure 1.3

demonstrates that this model agrees well with the published results for  $\beta$  thereby supporting the notion that lifetime is better extrapolated with respect to  $1/E_{OX}$  than  $E_{OX}$ .

The above model works well for thin oxides, thinner than 120 Å. For thicker oxides, B in the Fowler-Nordheim expression is known to become large at large electric fields (> 8 MV/cm) due to hole accumulation in the oxide [1.8,1.14]. As a result, G is often larger than 350 MV/cm for accelerated test data of thick oxides. It is advised that 350 MV/cm rather than the measured G be used for thicker oxides in order to obtain a conservative projection of low field lifetime. (This is equivalent to extrapolating  $Q_{bd}$  to low field, using Fowler-Nordheim theory rather than measured large B to extrapolate the low field current density, and predicting low field lifetime by dividing  $Q_{bd}$  by  $J_n$ ). This well documented complication makes it inadvisable to use the straightness of the  $log(t_{bd})$  versus E curve of a thicker oxide to verify or disprove the

hole-induced breakdown model. Moreover, this complication is fortuitously absent when evaluating state-of-the-art and future thin oxides.

Also, note the good agreement between model and data in Figure 1.3, even when the oxide is quite thick. The thick oxide tests summarized in Figure 1.3 were concerned with non-intrinsic, defect induced early failures. Apparently, defects in thick oxides tend to behave like thinner oxides.

The rest of this thesis discusses the continued development of this hole-induced breakdown toward a comprehensive quantitative thin oxide breakdown model. This model enables low voltage silicon dioxide reliability characterization. discusses anode hole injection, supplying theoretical underpinning to the empirical holeinduced breakdown model. The anode hole injection breakdown model enables the prediction of oxide charge- and time-to-breakdown, Qbd and tbd, respectively, at voltages below 5 Volts. Chapter 2 also discusses the low voltage, direct tunneling phenomenon. Chapter 3 examines the dielectric breakdown of the p<sup>+</sup> polysilicon gate, a technology receiving considerable attention in order to realize "surface" p-channel MOSFETs. Chapter 4 examines the role of temperature on accelerating oxide lifetime tests. Chapter 5 examines the role of defects in limiting the lifetime achievable from "intrinsic" quality oxide. Chapter 6 scrutinizes the correlations between substrate hole current and oxide breakdown, analyzing the contributions to substrate current in the thin oxide MOS system, establishing the validity of the anode hole injection model for oxides thinner than 55 Å. Chapter 7 discusses the expansive literature surrounding oxide breakdown and develops a model for oxide damage and breakdown that integrates the reported diverse observations and correlations into a coherent view of oxide breakdown. Chapter 7 also discusses innovations in silicon dioxide processing, trends in silicon oxide technology, and future needs for alternative dielectrics.

# Maximum Acceptable Oxide Field

Fig. 1.1 Illustration of oxide fields at which specific device reliability concerns are raised.

Fig. 1.2 Empirical linear extrapolation of breakdown lifetime with respect to oxide field[1.7].

Fig. 1.3 Theoretical field acceleration  $\beta$  compared with reported results [1.8].

Fig. 1.4 Extrapolation of breakdown lifetime with respect to inverse oxide field consistent with 1/E hole-induced breakdown model [1.13].

### 1.5. References

- [1.1] C. Hu, "Future CMOS Scaling and Reliability," *Proceedings of the IEEE*, vol. 81, no. 5, p. 682, 1993.

- [1.3] P.K. Ko, "Approaches to Scaling," in <u>VLSI Electronics Microstructure Science:</u> Advanced MOS Device Physics, edited by N. G. Einspruch and G. Gildenblat, vol. 18, p. 3, 1989.

- [1.3] R.H. Dennard, F.H. Gaensslen, H.N. Yu, V.L. Rideout, E. Bassous and A.R. LeBlanc, "Design of Ion-Implanted MOSFETs with Very Small Physical Dimensions," *Proceedings of the IEEE*, vol. 81, no. 5, p. 682, 1993.

- [1.4] New York Times Business Day, January 18, 1994.

- [1.5] K.F. Schuegraf and C. Hu, "Reliability in Thin SiO<sub>2</sub>," to appear in Semiconductor Science and Technology, May, 1994.

- [1.6] A. Berman, "Time-Zero Dielectric Reliability Test by a Ramp Method," International Reliability Physics Symposium, p. 204, 1981.

- [1.7] Y. Ozawa and K. Yamabe, "Film Thickness Dependence of TDDB Characteristics for Thermal Oxide," Extended Abstracts of the 1991 International Conference on Solid State Devices and Materials, p.240, 1991.

- [1.8] I.-C. Chen and C. Hu, "Accelerated Testing of Time-Dependent Breakdown of SiO<sub>2</sub>," *IEEE Electron Device Letters*, vol. 8, no. 4, p.140, 1987.

- [1.9] I.-C. Chen, S. E. Holland and C. Hu, "Oxide Breakdown Dependence on Thickness and Hole Current Enhanced Reliability of Ultra-Thin Oxides," *International Electron Devices Meeting*, p. 660, 1986.

- [1.10] I.-C. Chen, J. Y. Choi, T. Y. Chan, and C. Hu, "The Effect of Channel Hot Carrier Stressing on Gate-Oxide Integrity in MOSFETs," *IEEE Transactions on Electron Devices*, vol. ED-35, no. 12, p. 2253, 1988.

- [1.11] K. R. Mistry, D. B. Krakauer, and B. S. Doyle, "Impact of Snapback-Induced Hole Injection on Gate Oxide Reliability of N-MOSFETs," *IEEE Electron Device Letters*, vol. 11, no. 10, p. 460, 1990.

- [1.12] M. Knoll, D. Braunig, and W. R. Fahrner, "Comparative Studies of Tunnel Injection and Irradiation on Metal Oxide Semiconductor Structure," *Journal of Applied Physics*, vol. 53, no. 10, p. 6946, 1982.

- [1.13] R. Moazzami, J. Lee, I.-C. Chen, and C. Hu, "Projecting the Minimum Acceptable Oxide Thickness for Time-Dependent Breakdown," *International Electron Devices Meeting*, p. 710, 1988.

- [1.14] Y. Nissan-Cohen, J. Shappir, and D. Frohman-Bentchkowsky, "Measurement of Fowler-Nordheim Tunneling Current in MOS Structures Under Charge Trapping Conditions," Solid State Electronics, vol. 28, no. 7, p. 717, 1985.

# Chapter 2

# Intrinsic Low Voltage Breakdown Model

### 2.1. Introduction

This chapter focuses on the intrinsic SiO<sub>2</sub> low-voltage breakdown characteristics, namely, the field and voltage dependence of charge to breakdown, Qbd, and breakdown lifetime, tbd, thereby refining the empirical hole-induced 1/E breakdown model [2.1] by providing improved theoretical basis, that is, anode hole injection. Once again, the term intrinsic breakdown refers to the breakdown of an oxide that is free of defects, thereby reflecting the practical upper limit of oxide reliability. In practice, intrinsic breakdown is studied by examining oxides having small enough areas such that the breakdown reliability is independent of the area. The intrinsic breakdown reported here corresponds to less than 400 µm<sup>2</sup> capacitor and transistor test structures. Previous research [2.2,2.3,2.4,2.5] has demonstrated the interaction of holes with the oxide in initiating the damage which leads to catastrophic oxide failure. This chapter proposes a quantitative model for the physical process responsible for hole generation and injection into silicon dioxide during high-field electrical stress. The strength of this model lies in its ability to predict oxide breakdown at the very low operating voltages which are being introduced in state-of-the-art VLSI circuits. This chapter also discusses a model for the enhanced low-voltage leakage current due to direct tunneling in ultra-thin oxides.

## 2.2. Experiment

The devices used in this study were either capacitors or transistors with gate oxide thickness varying between 25 Å and 130 Å. Oxidation process was dry oxidation at 750-950°C. All devices have an in-situ phosphorus doped polysilicon gate deposited at  $605^{\circ}$ C. The capacitors were on n-type <100> 8-12  $\Omega$ -cm substrate. Constant-voltage stressing of capacitors was performed using an HP4140B picoammeter. Constant-voltage hole separation experiments[2.5,2.6] with transistors were performed using an HP4145B parameter analyzer. All the instruments were controlled by a PC using GPIB interface.

### 2.3. Anode Hole Injection Model

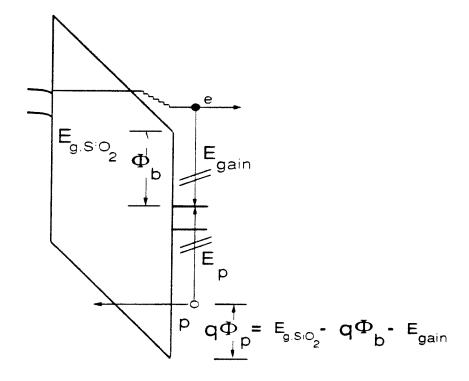

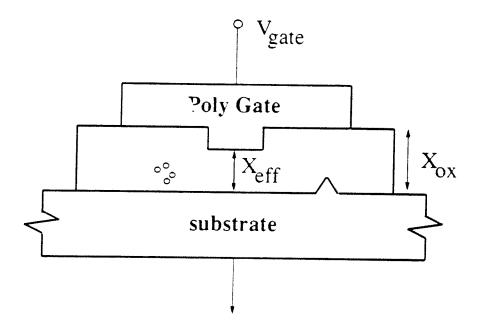

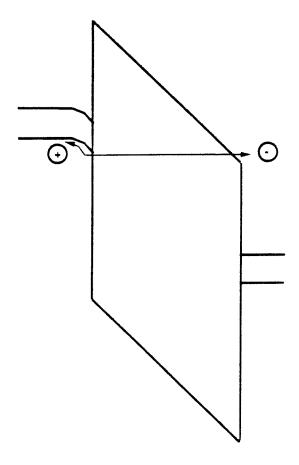

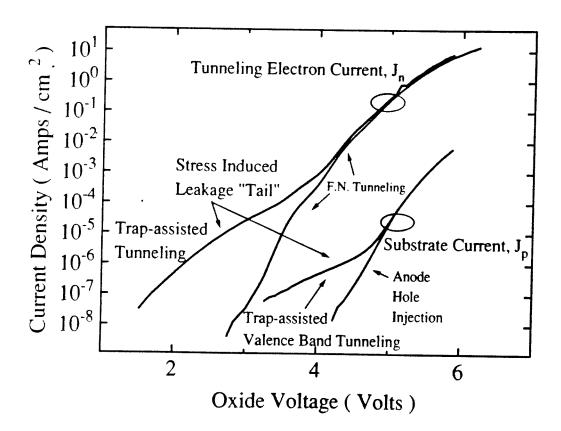

This model proposes that breakdown is a two-stage process [2.1], divided between the time where the oxide is slowly damaged under electrical stress and a much shorter, rapid runaway process, where a rapid final acceleration of damage due to electrical and/or thermal run-away leads to the formation of a permanent conductive path through the oxide. Since the first process dictates the breakdown time, our model addresses the period of accumulation of damage. Recent studies [2.2,2.3,2.4,2.5] clearly show that hole transport through the oxide precedes breakdown, indicating that holes cause damage to the oxide. This conclusion is not at all surprising when one realizes that holes have been found to generate bulk oxide electron traps [2.7,2.8,2.9,2.10] and interface traps [2.11]. Therefore all models of oxide breakdown variably emphasizing the roles of electron trapping [2.12], interface trapping [2.11], hole trapping [2.1] or resonant tunneling through electron traps [2.13] can all be reconciled by recognizing the role of hole injection. This model addresses the generation of holes for an oxide biased into the high-field tunneling regime as shown in

Figure 2.1, representing the conditions of accelerated test for determining oxide reliability. A fraction of the tunneling electrons reaching the anode are able to elastically transfer their entire energy to a deep valence-band electron [2.14,2.15,2.16,2.17]. Such an electron is promoted to the lowest available electron energy state, that is, the conduction band edge of the anode, thereby creating a "hot" hole, which tunnels back into the oxide. These injected holes act to increase the current density (at localized spots), probably through hole-induced trap generation [2.7,2.8,2.9,2.10] (see Chapter 7), until the final runaway process leads to catastrophic breakdown.

Mathematically, the hole tunneling current is given as  $J_p = \alpha_p \ J_n \ \Theta_p$ , where  $J_n$  is the incident electron tunneling current,  $\alpha_p \ \Theta_p$  is the probability for a hole to be generated and to tunnel through the barrier. The quantum efficiency of the hole generation process is

$$\frac{J_p}{J_n} = \alpha_p \Theta_p = \alpha_p \exp\left(-\frac{\hat{B}}{E_{ox}} \left[\Phi_p(V_{ox})\right]^{\frac{3}{2}}\right)$$

(2.1)

where

$$\mathring{B} = 8\pi \sqrt{2m_{p,ox}} / 3hq$$

, (h is Planck's constant),  $m_{p,ox} = 0.2 m_o$  and [2.6]  $q\Phi_p = E_{g,SiO_2} - q\Phi_b - E_{gain}$  (2.2)

The energy gained from the oxide field before arrival at the anode in the Fowler-Nordheim tunneling regime, where  $V_{OX} > \Phi_b$ , calculated by means of a phenomenological energy relaxation model [2.18], is given as

$$E_{gain} = \Phi_b + (E_{ox}\lambda) \left[ 1 - exp \left( \frac{-1}{\lambda} \left[ X_{ox} - \frac{\Phi_b}{E_{ox}} \right] \right) \right]$$

(2.3)

where  $\lambda = 15$  Å is the mean free electron scattering length in the oxide conduction band [2.19]. In contrast, in direct tunneling, i.e. for  $V_{OX} < \Phi_b$ , electrons do not experience such scattering, thus the arrival energy of electrons at the anode is simply

$$E_{gain} = V_{ox} \text{ for } V_{ox} < \Phi_{b}. \tag{2.4}$$

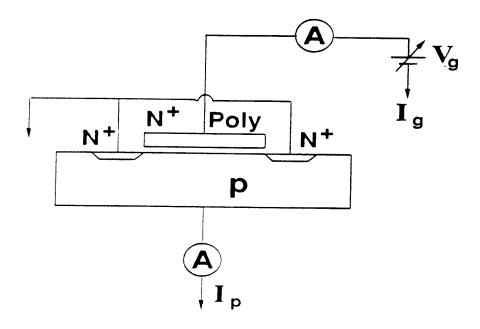

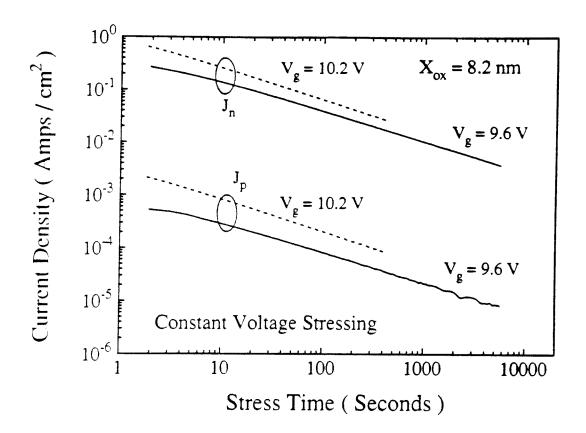

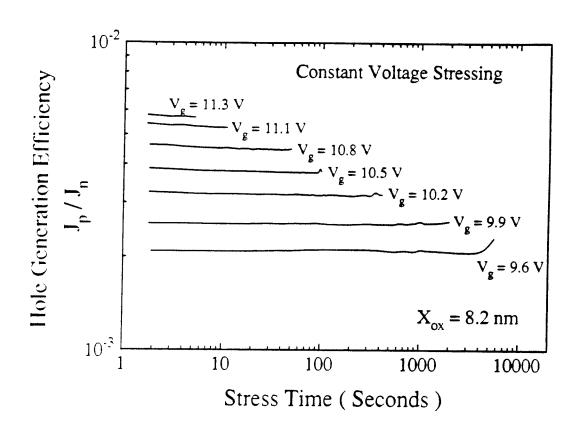

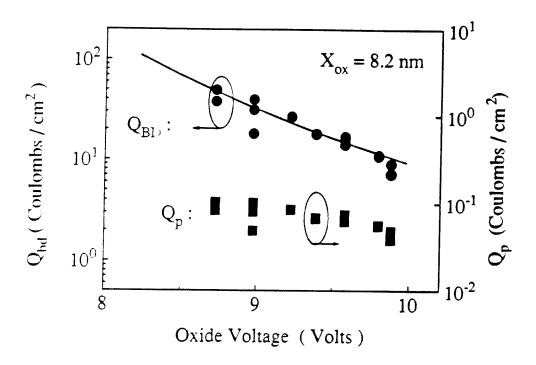

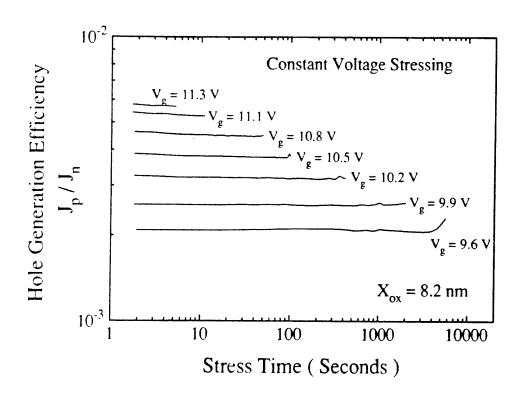

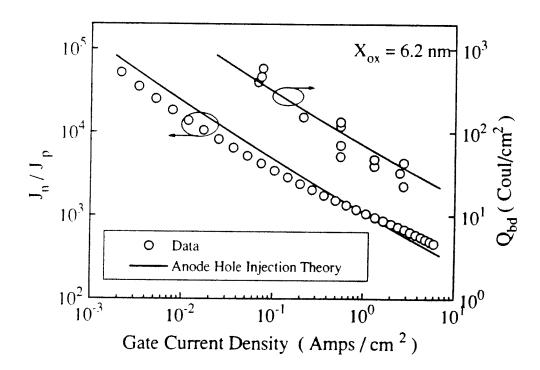

Using nMOS transistors biased as in Figure 2.2, the tunneling electron current can be easily measured as gate current and the anode-injected hole current can be measured as the substrate current [2.5,2.6]. Figure 2.3 shows that the tunnel current density  $J_n$  decreases by over an order of magnitude during the oxide lifetime due to electron trapping. Moreover, as more clearly illustrated in Figure 2.4, the quantum hole generation efficiency remains constant for the duration of the oxide lifetime showing that the hole generation rate is strictly determined by the applied bias, consistent with Eq. (2.1) for  $\alpha_p \equiv 0.08$ .

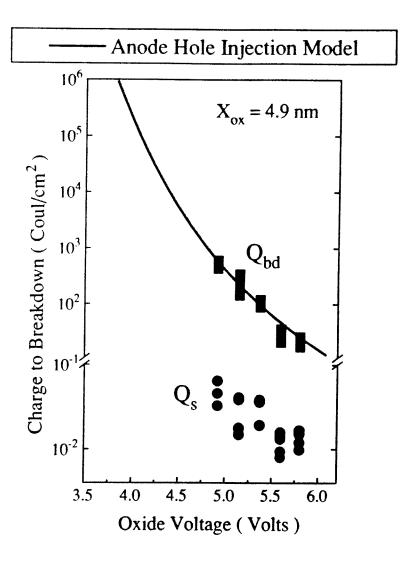

The injected hole quantity increases with time as  $Q_p(t) = \int_0^t J_p(\hat{t}) d\hat{t}$  until a critical hole

fluence,  $Q_p$ , is reached, marking the breakdown event. The charge to breakdown,  $Q_{bd}$ , follows as

$$Q_{bd} = \frac{Q_p}{\alpha_p} \exp\left(\frac{\hat{B}}{E_{ox}} \left[\Phi_p(v_{ox})\right]^{\frac{3}{2}}\right)$$

(2.5)

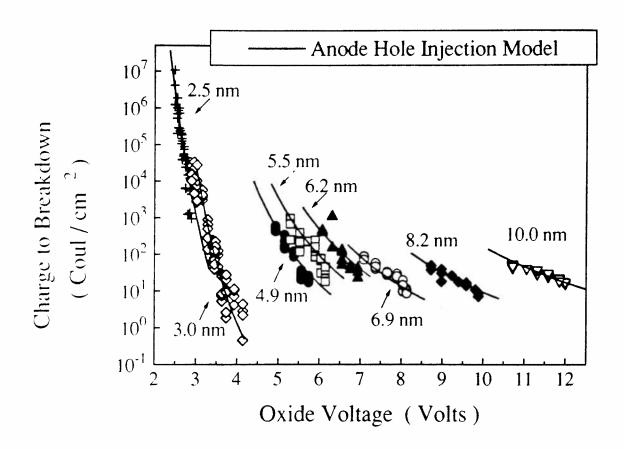

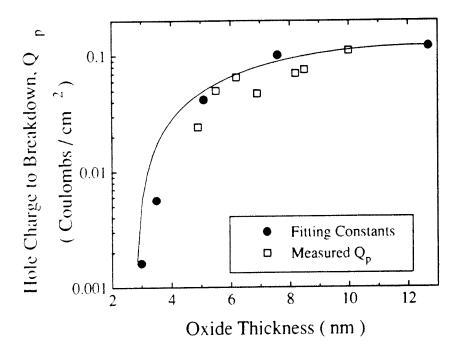

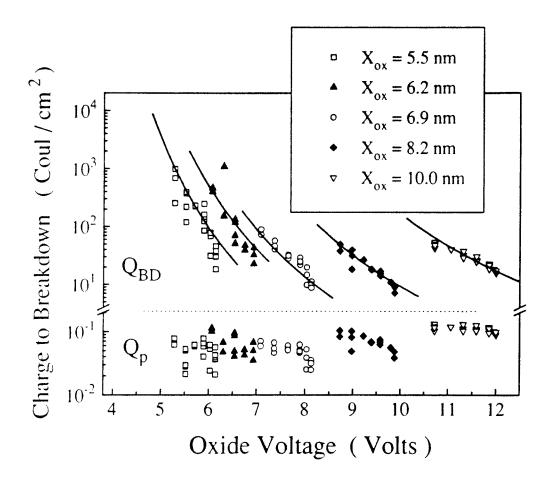

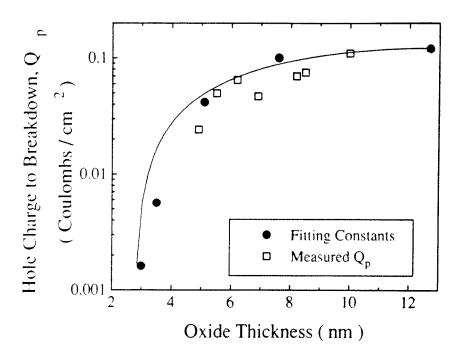

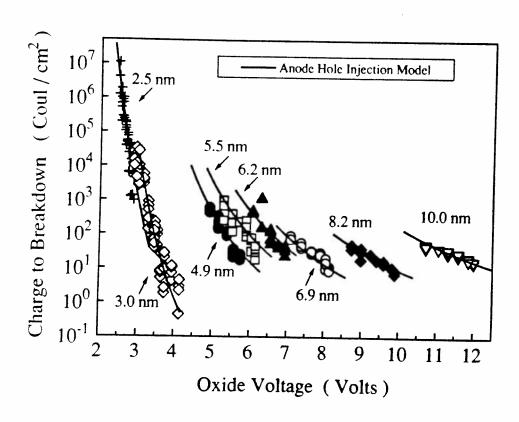

Figure 2.5 shows that the critical hole fluence at breakdown, Q<sub>p</sub>, is independent of the stress voltage, while Q<sub>bd</sub> decreases with increasing stress voltage according to Eq. (2.5). Figure 2.6 shows the excellent ability of Eq. (2.5) to predict intrinsic charge to breakdown for oxide thickness varying between 25 and 100 Å. The low voltage predictive ability of Eq. (2.5) attests to the hypothesis of anode hole injection since tunneling electrons cannot gain the energy necessary for impact ionization in the silicon dioxide at these low voltages. The rapidly rising Q<sub>bd</sub> behavior in thinner oxides can be attributed to the fact that the hot hole energy, E<sub>gain</sub>, becomes more sensitive to V<sub>ox</sub> when scattering becomes weaker. The formalism leading to Eq. (2.5) may also be used in modeling thin oxide Q<sub>bd</sub> derived from constant current stressing, by performing a

path integral between the initial and final stress voltages needed to maintain the constant current condition. Figure 2.7 compares values of  $Q_p$  measured using hole separation and those deduced fitting capacitor breakdown data to Eq. (2.5), showing that  $Q_p$  decreases with decreasing oxide thickness, reflecting a weakened hole immunity for thinner oxides.

### 2.4. Oxide Tunneling Current

This section discusses the calculation of oxide voltage from the applied voltage and introduces a model for tunnel current,  $J_n$ , which facilitates the modeling of the breakdown lifetime,  $t_{bd}$ . First, the necessity of accounting for polysilicon depletion in thin-oxide current conduction is demonstrated. Next, quantitative models for Fowler-Nordheim and direct tunneling are introduced.

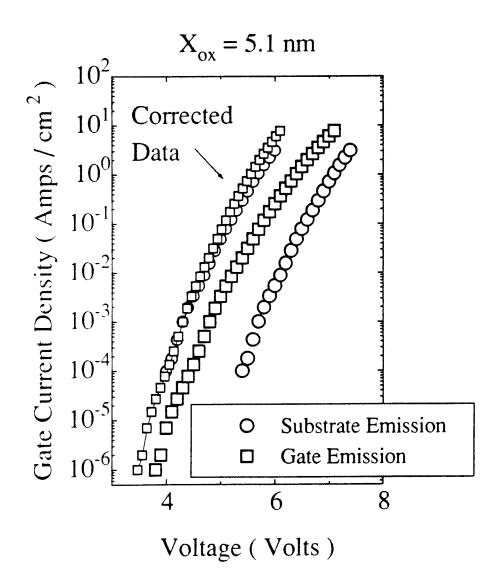

### 2.4.1. Polysilicon Depletion

In order to model the leakage currents of thin oxides, it is necessary to relate the oxide voltage to the applied bias. Figure 2.8 compares the measured positive bias (substrate electron emission: SE) and negative bias (gate electron emission: GE) tunneling currents for a thin oxide capacitor. Whereas thicker oxides display parallel tunneling characteristics with an offset due to band-bending [2.20], these data show that the measured JV characteristics in very thin oxides are not parallel, which can be attributed to the depletion of the heavily in-situ doped n+ gate polysilicon [2.21,2.22,2.23]. Computation of the oxide voltage for each curve by subtracting for band bending in the poly-gate and the substrate reduces them to a single tunneling characteristic dependent only on V<sub>OX</sub>, consistent with the notion that tunneling should be a unique function of the oxide voltage and thickness, independent of polarity. The polysilicon band

bending induces a voltage drop correcting the GE and SE curves under the transformations given in Table 2.1 [2.20,2.23] where  $V_{poly} = \frac{\varepsilon_{ox}^2 E_{ox}^2}{2q\varepsilon_{Si}N_{poly}}$  until

$V_{poly}$  is pinned at 1.12 V due to the saturation of band bending in strong inversion. The maximum electrically active doping concentration appears to be bounded by approximately 5 x  $10^{19}$  cm<sup>-3</sup> for this in-situ doped polysilicon, with even lower dopant activation for implanted polysilicon [2.21,2.23]. The single tunneling characteristic dependent only on  $V_{ox}$  attests to the applicability of the depletion approximation [2.22]. Figure 2.9 shows that Eq. (2.5) is valid for predicting  $Q_{bd}$  for either positive or negative bias, providing the oxide voltage is calculated consistently with Table 2.1. However,  $Q_p$  for the gate emission case (negative gate voltage) was found to be 2 to 5 times lower than its substrate emission (positive voltage) counterpart. This indicates that the poly-SiO<sub>2</sub> interface is not as robust as the Si-SiO<sub>2</sub> interface.

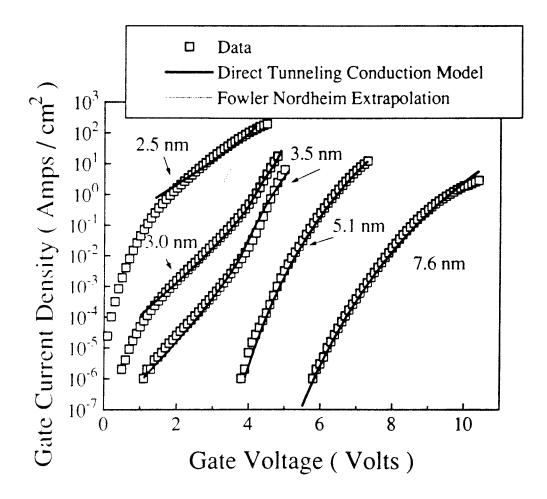

### 2.4.2. Thin Oxide Conduction Model

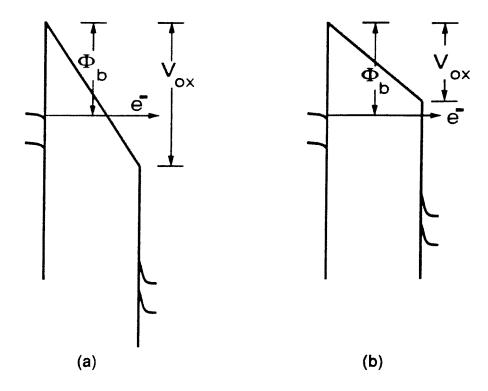

This section introduces a model for quantitative modeling of the tunnel current,  $J_n$ , of Figure 2.8. Figure 2.10 illustrates the difference between direct and Fowler-Nordheim (FN) tunneling. The standard FN expression [2.24] is

$$J_n = A E_{OX}^2 e^{-\frac{R}{E_{OX}}},$$

(2.6)

where B =  $\frac{8\pi\sqrt{2m_{OX}}\Phi_b^{\frac{3}{2}}}{3 \text{ h q}}$ , and the electron effective mass, m<sub>OX</sub>, is 0.5 m<sub>O</sub>. Equation

(2.6) represents tunneling through the triangular potential barrier of Figure 2.10(a), valid for  $V_{OX} > \Phi_b$ . However, for  $V_{OX} < \Phi_b$ , where the tunneling barrier is trapezoidal as in Figure 2.10(b), Eq. (2.6) is no longer valid but becomes [2.25],

$$J_{n} = A E_{ox}^{2} \left(\frac{\Phi_{b}}{V_{ox}}\right) \left(\frac{2\Phi_{b}}{V_{ox}} - 1\right) exp \begin{bmatrix} -B\left(1 - \left(1 - \Phi_{b}^{3/2}\right)\right) \\ E_{ox} \end{bmatrix} . (2.7)$$

This analytical formula does not approach zero as  $V_{\rm ox}$  approaches zero. Therefore, it does not apply to the regime of  $V_{\rm ox} < 1$  Volt. An alternative approximation that overcomes this limitation is

$$J_{n} = A E_{ox}^{2} exp \begin{bmatrix} -B(1-(1-\Phi_{b}^{3/2})) \\ E_{ox} \end{bmatrix}$$

(2.8)

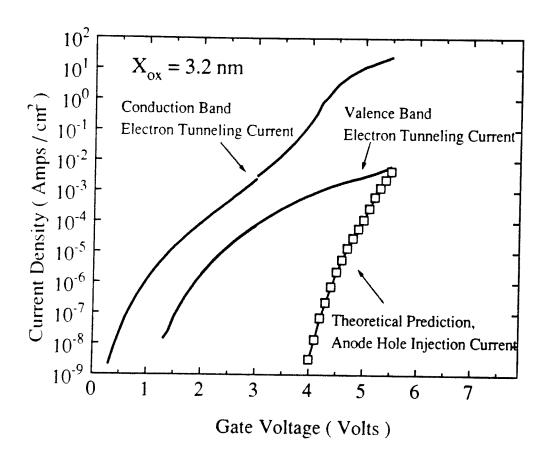

Figure 2.11 demonstrates the utility of this model, highlighting the dramatic effect the changed barrier shape, from triangular to trapezoidal, exerts on increasing the leakage current for  $V_{OX} < \Phi_{b}$ . Observation of direct tunneling is generally limited to oxides thinner than 50 Å because the tunneling probability for thicker oxides is small. Thus, experimental constraints (i.e. current sensitivity of measurement equipment and capacitor area) limit observation of direct tunneling currents.

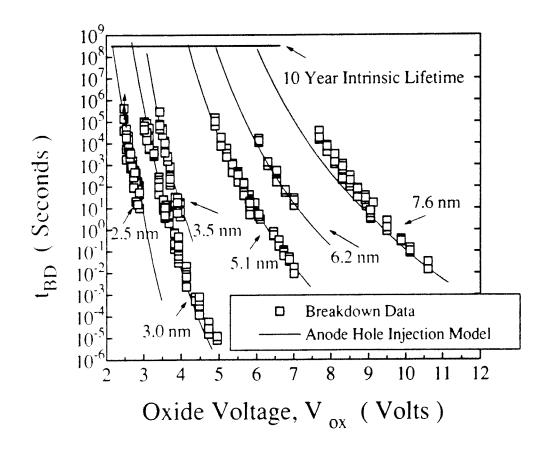

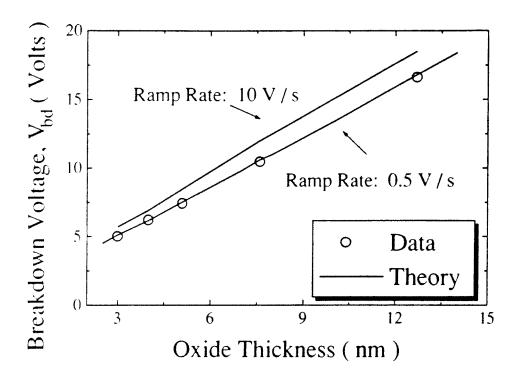

### 2.5. Breakdown Lifetime

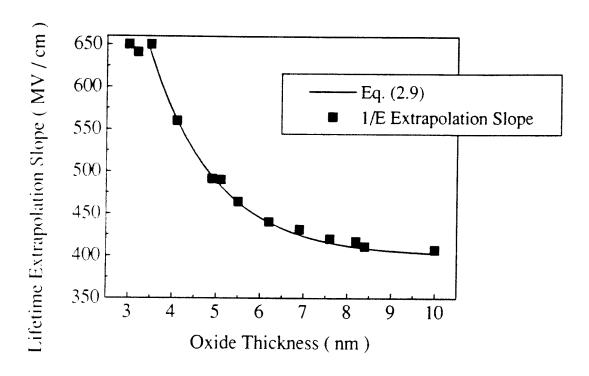

Combining this closed form current model of Eq. (2.6) and (2.7) with the  $Q_{bd}$  model expression of Eq. (2.5) leads to a simple model to predict oxide lifetime, i.e.  $t_{bd}=Q_{bd}/J_n$ . Although carrier trapping can lead  $J_n$  to increase or decrease with stress time, this trapping is negligible for thin oxides so that  $t_{bd} \approx Q_{bd}/J_n$ . Figure 2.12 demonstrates exceptional agreement between  $t_{BD}$  theory and intrinsic breakdown data for thin oxide samples, highlighting the ability of the anode hole injection model to predict oxide lifetime at low operating voltages. Whereas the hole-induced 1/E extrapolation model predicts a constant extrapolation slope of 350 MV/cm [2.1,2.26], Figure 2.13 illustrates that  $log(t_{bd})$  may still be linearly extrapolated with respect to

1/E, albeit with increasing extrapolation slope for decreasing oxide thickness. Figure 2.14 shows this lifetime extrapolation slope follows

$$G = 400 + 190 \exp\left(-\frac{X_{ox} - 39}{\lambda}\right) \qquad \left[\frac{MV}{cm}\right]$$

(2.9)

for oxides thickness greater than 39Å, with  $\lambda = 15$  Å. For thinner oxides, the extrapolation slope is about 650 MV/cm. Despite this increase in extrapolation slope, the maximum acceptable oxide field for 10 year lifetime varies by only about 10 % for a wide range of oxide thickness as shown in Figure 2.13.

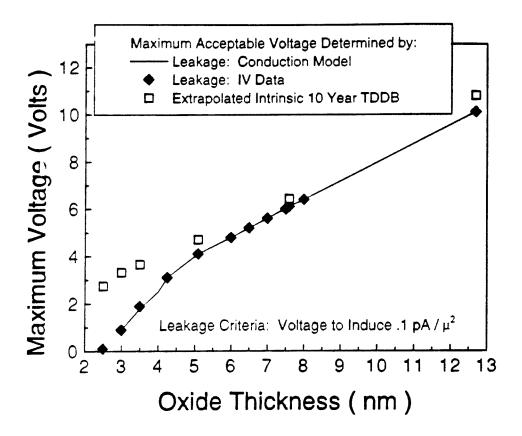

# 2.6. Supply Voltage Limits

Figure 2.15 examines the role of two competing criteria, intrinsic TDDB (10 Year Lifetime at 25° C) and leakage current (0.1 pA/μm²), in determining maximum acceptable operating voltage. Although these two criteria track each other in scaling from 130 Å to 60 Å, further scaling leads these criteria to diverge. The enhanced leakage current due to direct tunneling may require a rapid derating of supply voltage, posing an additional constraint on aggressively scaled oxide technologies below 40 Å. Different leakage requirements may relax the constraint on minimum oxide thickness; however, the rapid increase in direct tunneling current below 40 Å requires rapid supply voltage derating regardless of how much leakage current is permissible. While intrinsic breakdown sets the ultimate reliability limit, in practice, certain thickness margin is needed to cushion against defects whose breakdown is modeled by an effectively thinnest spot [2.27,2.28]. In practice, the ability to manufacture high quality, low defect ultra-thin oxides will limit the usable oxide thickness for a given operating voltage.

# 2.7. Summary and Conclusions

This chapter presented a new quantitative model for silicon dioxide breakdown, based on the concept of anode hole injection, valid for predicting insulator reliability performance for thicknesses between 25 and 130 Å. This model is suitable for predicting dielectric lifetime for reduced supply voltages and aggressively scaled oxide thicknesses. Additionally, a quantitative model for enhanced low voltage silicon dioxide leakage current due to the direct tunneling mechanism shows this current may pose additional oxide scaling constraints for oxides thinner than 40 Å. This criterion along with the manufacturability of defect-free ultra-thin silicon dioxide will ultimately determine the usable oxide thickness and supply voltage -- and hence the CMOS speed performance.

| $ V_{OX}  =  V_g $ - the following: |                   |                   |  |  |  |

|-------------------------------------|-------------------|-------------------|--|--|--|

|                                     | n+ poly on p sub  | n+ poly on n sub  |  |  |  |

| +V <sub>g</sub>                     | V <sub>poly</sub> | V <sub>poly</sub> |  |  |  |

| -V <sub>g</sub>                     | 1.2               | 1.2               |  |  |  |

Table 2.1 J-V Experiments show how V<sub>OX</sub> may be determined for different bias polarity and gate and substrate doping types. The 1.2 Volt offset for negative biases is due to band bending in the MOS system; it reflects an average across a variety of oxide thicknesses and technologies [2.22].

Fig. 2.1 Diagram of Anode Hole Injection Process. An incident tunneling electron arrives at the anode with energy, Egain, to thermalize. This energy is transferred to a deep valence band electron, thereby exciting it to the lowest available energy state, the anode conduction band. This excitation creates a "hot" hole capable of tunneling back into the oxide.

Fig. 2.2 Bias configuration of NMOSFET which enables separate measurement of tunneling electron and injected hole currents. Time integrated electron tunneling current is  $Q_{bd}$ , whereas time integrated hole current is  $Q_p$ .

Fig. 2.3 Time evolution of gate current density,  $J_n$ , and injected hole density.  $J_p$ , during constant voltage stress of a 82 Å oxide, showing that electron trapping decreases the gate and injected hole tunneling currents while the ratio  $J_p/J_n$  is determined by the applied bias.

Fig. 2.4 Time evolution of the quantum hole generation efficiency,  $J_p/J_n$ , during constant voltage stress of a 82 Å oxide, clearly demonstrating that the applied bias determines this efficiency.

Fig. 2.5 Charge to breakdown,  $Q_{bd}$ , and hole fluence to breakdown,  $Q_p$ , for a 82 Å oxide, showing that  $Q_{bd}$  increases with decreasing stress voltage, while  $Q_p$  remains constant.

Fig. 2.6 Voltage dependence of thin oxide charge to breakdown, demonstrating ability to extrapolate to low voltages.

Fig. 2.7 Comparison of experimentally measured  $Q_p$  values using hole separation and those deduced from fitting capacitor breakdown data.

Fig. 2.8 J-V characteristics for 51 Å oxide capacitors with in-situ doped n<sup>+</sup> polysilicon gate. The corrected data for substrate emission and gate emission is computed according to the rules in **Table** 2.1.

Fig. 2.9 Shows that Anode Hole Injection Model accurately predicts breakdown for positive and negative bias stresses.

Fig. 2.10 Illustrates the physical difference between Fowler-Nordheim and Direct Tunneling. (a) Fowler-Nordheim Tunneling is associated with transversal of a triangular barrier. (b) Direct Tunneling is associated with transversal of a trapezoidal barrier, i.e. when  $V_{\text{OX}} < \Phi_{\text{b}}$ .

Fig. 2.11 Comparison between data and closed form oxide conduction current model which accounts for both Fowler-Nordheim and Direct Tunneling. The extension of Fowler-Nordheim theory for ultra-thin oxides illustrates the dramatic increase in leakage current caused by the subtle change in barrier shape, i.e. from triangular to trapezoidal, used to model the low voltage Direct Tunneling regime.

Fig. 2.12 Voltage dependence of breakdown lifetime for thin oxides predicted down to low voltages using Anode Hole Injection Model.

Fig. 2.13 Inverse field dependence of breakdown lifetime is linear with increasing extrapolation slope for thinner oxides.

Fig. 2.14 Thickness dependence of inverse field oxide breakdown lifetime slope. Slope increases for thinner oxides due to reduced hole generation efficiency.

Fig. 2.15 Comparison of maximum acceptable operating voltages from viewpoint of 10 year intrinsic TDDB lifetime and Gate Leakage.

These two criteria track each other in scaling from 130 Å to 60 Å, but further scaling leads them to diverge, as the enhance leakage current of direct tunneling mandates rapid voltage scaling.

### 2.8. References

- [2.1] I.-C. Chen, S. E. Holland, and C. Hu, "Electrical Breakdown in Thin Gate and Tunneling Oxides," *IEEE Transactions on Electron Devices*, vol. ED-32, no. 2, p. 413, 1985.

- [2.2] I.-C. Chen, J. Y. Choi, T. Y. Chan, and C. Hu, "The Effect of Channel Hot Carrier Stressing on Gate-Oxide Integrity in MOSFETs," *IEEE Transactions on Electron Devices*, vol. ED-35, no. 12, p. 2253, 1988.

- [2.3] K. R. Mistry, D. B. Krakauer, and B. S. Doyle, "Impact of Snapback-Induced Hole Injection on Gate Oxide Reliability of N-MOSFETs," *IEEE Electron Device Letters*, vol. 11, no. 10, p. 460, 1990.

- [2.4] E. Rosenbaum, R. Rofan, and C. Hu, "Effect of Hot Carrier Injection on n- and p-MOSFET Gate Oxide Integrity," *IEEE Electron Device Letters*, vol. 12, no. 11, p. 599, 1991.

- [2.5] I.-C. Chen, S. E. Holland and C. Hu, "Oxide Breakdown Dependence on Thickness and Hole Current Enhanced Reliability of Ultra-Thin Oxides," *International Electron Devices Meeting*, p. 660, 1986.

- [2.6] B. Eitan and A. Kolodny, "Two Components of Tunneling Current in Metal-Oxide-Semiconductor Structures," Applied Physics Letters, vol. 43, no. 1, p. 106, 1983.

- [2.7] S. K. Lai, "Interface Trap Generation in Silicon Dioxide when Electrons are Captured by Trapped Holes," *Journal of Applied Physics*, vol. 54, no. 5, p. 2540, 1983.

- [2.8] I.-C. Chen, S. E. Holland, and C. Hu, "Electron-trap Generation by Recombination of Electrons and Holes in SiO<sub>2</sub>," *Journal of Applied Physics*, vol. 61, no. 9, p. 4544, 1987.

- [2.9] H. Uchida and T. Ajioka, "Electron Trap Center Generation Due to Hole Trapping in SiO<sub>2</sub> Under Fowler-Nordheim Tunneling Stress," *Applied Physics Letters*, vol. 51, no. 6, p. 433, 1987.

- [2.10] S. Ogawa, N. Shiono, and M. Shimaya, "Neutral Electron Trap Generation in SiO<sub>2</sub> by Hot Holes," *Applied Physics Letters*, vol. 56, no. 14, p. 1329, 1990.

- [2.11] D. J. DiMaria, D. Arnold, and E. Cartier, "Degradation and Breakdown of Silicon Dioxide Films on Silicon," *Applied Physics Letters*, vol. 61, no. 19, p. 2329, 1992.

- [2.12] E. Harari, "Dielectric Breakdown in Electrically Stressed Thin Films of Thermal SiO<sub>2</sub>," *Journal of Applied Physics*, vol. 49, no. 4, p. 2478, 1978.

- [2.13] B. Ricco, M. Ya Azbel, and M. H. Brodsky, "A Novel Mechanism for Tunneling and Breakdown in Thin SiO<sub>2</sub> Films," *Physics Review Letters*, vol. 51, p. 1795, 1983.

- [2.14] Z. A. Weinberg, W. C. Johnson, and M. A. Lampert, "High-Field Transport in SiO<sub>2</sub> on Silicon Induced by Corona Charging of the Unmetallized Surface," *Journal of Applied Physics*, vol. 47, no. 1, p. 248, 1976.

- [2.15] Z. A. Weinberg, M. V. Fischetti, and Y. Nissan-Cohen, "SiO<sub>2</sub>-Induced Substrate Current and its Relation to Positive Charge in Field-Effect Transistors," *Journal of Applied Physics*, vol. 59, no. 3, p. 824, 1986.

- [2.16] S. E. Holland, I.-C. Chen, and C. Hu, "Ultra-Thin Silicon-Dioxide Breakdown Characteristics of MOS Devices with n<sup>+</sup> and p<sup>+</sup> Polysilicon Gates," *IEEE Electron Device Letters*, vol. 8, no. 12, 1987.

- [2.17] K. F. Schuegraf and C. Hu, "Hole Injection Oxide Breakdown Model for Very Low Voltage Lifetime Extrapolation," *International Reliability Physics Symposium*, p. 7, 1993.

- [2.18] C. Chang, C. Hu, and R. W. Brodersen, "Quantum Yield of Electron Impact Ionization in Silicon," *Journal of Applied Physics*, vol. 57, no. 2, p. 302, 1985.

- [2.19] G. Lewicki and J. Maserjian, "Tunneling in MOS Structures," *Journal of Applied Physics*, vol. 46, no. 7, p. 3032, 1975.

- [2.20] E. Rosenbaum, R. Moazzami and C. Hu, "Implications of Waveform and Thickness Dependence of SiO<sub>2</sub> Breakdown on Accelerated Testing," *Proceedings of the International Symposium on VLSI Technology, Systems, and Applications*, p. 214, 1991.

- [2.21] B. J. Fishbein and D. B. Jackson, "Performance Degradation of N-Channel MOS Transistors During DC and Pulsed Fowler-Nordheim Stress, *Proceedings of the International Reliability Physics Symposium*, p. 159, 1990.

- [2.22] S. J. Wang, I.-C. Chen, and H. L. Tigelaar, "Effects of Poly Depletion on the Estimate of Thin Dielectric Lifetime", *IEEE Electron Device Letters*, vol. 12, no. 11, p. 617, 1991.

- [2.23] K. F. Schuegraf, C. C. King and C. Hu, "Impact of Polysilicon Depletion in Thin Oxide MOS Technology," Proceedings of the International Symposium on VLSI Technology, Systems, and Applications, p. 86, 1993.

- [2.24] M. Lenzlinger and E. H. Snow, "Fowler-Nordheim Tunneling into Thermally Grown SiO<sub>2</sub>," *Journal of Applied Physics*, vol. 40, p. 278, 1969.

- [2.25] K. F. Schuegraf, C. C. King and C. Hu, "Ultra-Thin Silicon Dioxide Leakage Current and Scaling Limit," Symposium on VLSI Technology Digest of Technical Papers, p. 18, 1992.

- [2.26] R. Moazzami, J. Lee, I.-C. Chen, and C. Hu, "Projecting the Minimum Acceptable Oxide Thickness for Time-Dependent Breakdown," *International Electron Devices Meeting*, p. 710, 1988.

- [2.27] J. C. Lee, I.-C. Chen and C. Hu, "Modeling and Characterization of Gate Oxide Reliability," *IEEE Transactions on Electron Devices*, vol. ED-35, no. 12, p. 2268, 1988.

[2.28] K. F. Schuegraf and C. Hu, "Effects of Temperature and Defects on Breakdown Lifetime of Thin SiO<sub>2</sub> at Low Voltages," *International Reliability Physics Symposium*, p. 126, 1994.

# Chapter 3

# Gate Material Dependence of Anode Hole Injection

#### 3.1 Introduction

This chapter presents the investigation of the breakdown mechanism of  $p^+$  and  $n^+$  polysilicon gate MOS structures. This comparison is of considerable technological relevance since realization of dual gate p+/n+ polysilicon CMOS technology [3.1] promises "surface" p-channel MOSFETs with superior off-state characteristics. We show that anode hole injection satisfactorily models this breakdown process, leading to accurate predictions of low voltage  $t_{bd}$  and  $Q_{bd}$ . The  $p^+$  doped polysilicon exhibits poorer  $Q_{bd}$  than its n+ counterpart, not as the result of "enhanced hole generation efficiency," but rather as the result of reduced immunity to injected holes.

### 3.2. Experiment

The devices used in this study had oxide thickness varying between 30 Å and 75 Å. Oxidation process was dry oxidation at 750-950°C, depending on oxide thickness. The n<sup>+</sup> polysilicon devices have an in-situ phosphorus doped polysilicon gate deposited at 605°C. The p<sup>+</sup> polysilicon devices have boron implanted (dose: 3·10<sup>15</sup> cm<sup>-2</sup>, energy: 20 keV) polysilicon gates, deposited undoped at 605°C. Capacitors were on n-type <100> epitaxial substrate. Constant-voltage stressing of capacitors was performed using an HP4140B picoammeter. Constant-voltage hole separation experiments using nMOSFETs [3.2,3.3] were performed using an HP4145B parameter analyzer. All the instruments were controlled by a PC using GPIB interface.

#### 3.3. Results and Discussion

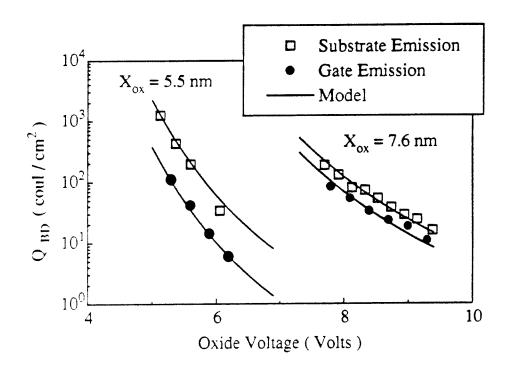

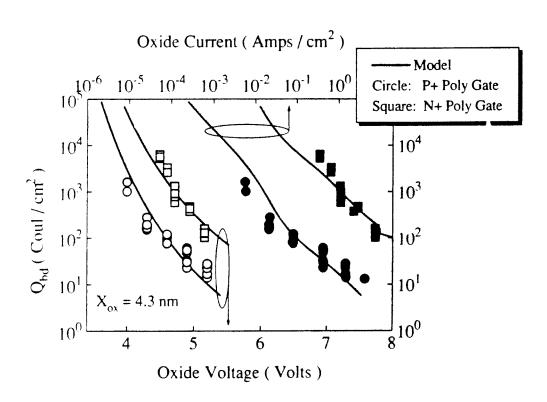

A basic understanding of the voltage dependence of intrinsic charge-to-breakdown,  $Q_{bd}$ , for  $n^+$  and  $p^+$  polysilicon gate determined by constant voltage stress requires a comparison at the same oxide, not gate voltage. Oxide voltage can be calculated from the gate voltage according to Table 3.1, deduced from J-V experiments as in [3.4,3.5] which account for band bending and polysilicon depletion [3.6,3.7,3.8]. Figure 3.1 plots  $Q_{bd}$  against the oxide voltage. The  $Q_{bd}$  dependence on  $J_{ox}$  is also shown for a second set of x-axes. Each  $J_{ox}$  corresponds to a certain  $V_{ox}$  (with electrons injected from the substrate) regardless of polysilicon doping type. Charge-to-breakdown,  $Q_{bd}$ , is lower for  $p^+$  polysilicon gate, especially for oxide of smaller thickness.

To understand the difference better, we examine the data in light of an anode hole injection model which enables prediction of low voltage oxide breakdown parameters [3.9]. A fraction of the tunneling electrons reaching the anode are able to elastically transfer their entire energy to a deep valence-band electron [3.10,3.11,3.12]. Such an electron is promoted to the lowest empty electron energy state, i.e. the conduction band edge of the anode (the polysilicon gate), thereby creating a "hot" hole, which tunnels back into the oxide where it generates oxide traps enhancing electron tunneling. Breakdown occurs when a critical hole fluence, Qp, has been reached. This critical hole fluence is thickness dependent, but independent of bias for a given thickness [3.2,3.9]. Charge-to-breakdown, Qbd, may be lower for p+ polysilicon gate because either Qp is lower, i.e. oxides under p+ polysilicon gate are more susceptible to hole injection, or more holes are injected into the oxide for each coul/cm<sup>2</sup> of electrons tunneling through the oxide. The latter explanation was thought possible [3.12] because "hotter" holes might be created in a p+ polysilicon anode as the lowest empty electron states might be found at the top of the valence band rather than the bottom of the conduction band.

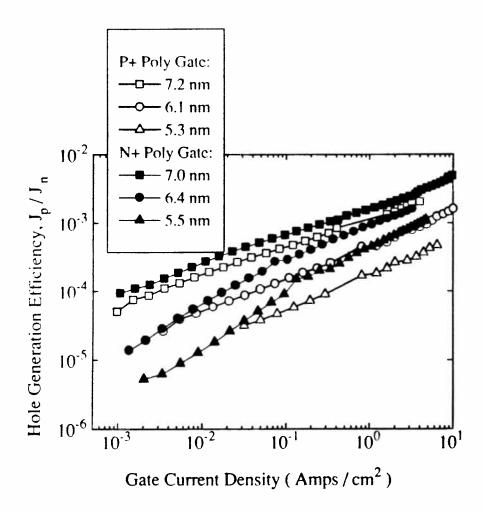

This line of reasoning suggests that hole injection from p<sup>+</sup> poly gate might be significantly enhanced, possibly explaining the reduced Q<sub>bd</sub> for the p<sup>+</sup> gate. We performed hole separation measurements of p<sup>+</sup> and n<sup>+</sup> gate nMOSFETs. In this technique, the tunneling electron current is easily measured as gate current and the anode-injected hole current can be measured as substrate current [3.2,3.3]. Figure 3.2 shows no enhanced hole generation for the p<sup>+</sup> gate. This suggests that the density of available states at the valence band edge for accepting electrons promoted from deep in the valence band is not large enough to appreciably contribute to the anode hole injection current.

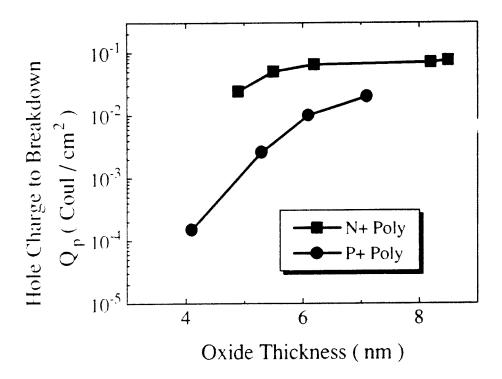

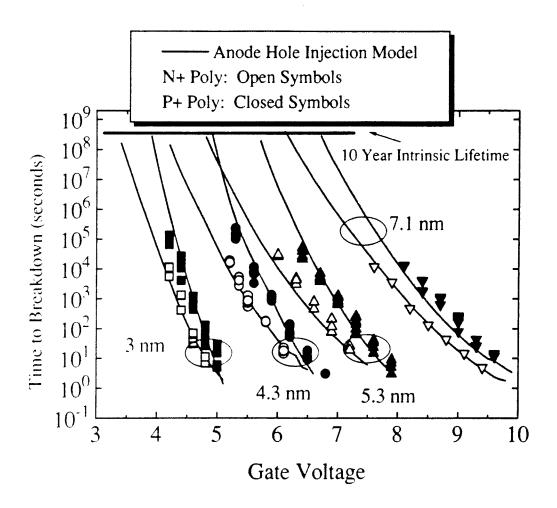

On the other hand, Figure 3.3 demonstrates that the measured hole fluence at breakdown,  $Q_p$ , is lower for  $p^+$  than for  $n^+$  poly-Si. This explains the reduced  $Q_{bd}$  for  $p^+$  gate in Figure 3.1, where using the measured  $Q_p$ , the anode hole injection model [3.9] accurately predicts both  $n^+$  and  $p^+$  breakdown characteristics. A larger difference in  $Q_{bd}$  for thinner oxides is a direct result of the larger difference in  $Q_p$  for thinner oxides. Figure 3.4 shows the measured breakdown lifetime. It also shows the predicted lifetime,  $t_{bd} = Q_{bd} / J_n$  (both  $Q_{bd}$  and  $J_n$  can be accurately predicted), down to low operating voltages.

#### 3.4. Conclusions

This chapter has shown that the anode hole injection model is able to predict the breakdown characteristics of both p<sup>+</sup> and n<sup>+</sup> polysilicon MOS structures. Hole charge to breakdown is lower for p<sup>+</sup> structures reflecting a decreased immunity to hole injection, suggesting an interaction between injected holes and boron which is present in the oxide under the p<sup>+</sup> polysilicon. This process is further complicated due to the possible intermediary role that hydrogen [3.93.13,3.14], released by holes flowing through the

oxide, may play in reducing  $p^+$  polysilicon  $Q_{bd}$ . This study suggests that "enhanced hole injection" [3.15] cannot explain bias temperature instability of  $p^+$  pMOSFET device parameters. Instead, oxide under  $p^+$  polysilicon is more vulnerable to injected holes. Finally, although  $Q_{bd}$  is lower for  $p^+$  structures, the maximum allowable voltage which satisfies 10 year intrinsic breakdown lifetime requirements is higher for  $p^+$  structures due to band bending considerations.

| $ V_{OX}  =  V_g $ - the following: |                 |                   |

|-------------------------------------|-----------------|-------------------|

|                                     | +V <sub>g</sub> | -V <sub>g</sub>   |

| n+ poly on n substrate              | $V_{ m poly}$   | 1.3               |

| n+ poly on p substrate              | $V_{ m poly}$   | 1.3               |

| p+ poly on n substrate              | 1.3             | V <sub>poly</sub> |

| p+ poly on p substrate              | 1.3             | V <sub>poly</sub> |

Table 3.1 J-V Experiments show how V<sub>OX</sub> may be determined for different bias polarity and gate and substrate doping types. The numerical voltage offsets reflect band bending in the MOS system.

numerical voltage offsets reflect band bending in the MOS system.

$$V_{poly} \ \text{is calculated as} \quad V_{poly} \ = \ \frac{\epsilon_{ox}^2 E_{ox}^2}{2q\epsilon_{Si} N_{poly}} \ \text{until} \ V_{poly} \ \text{is}$$

pinned at 1.12 V due to the saturation of band bending in strong inversion. Another  $\sim 0.5$  V is to be taken off the "effective  $V_{OX}$ " in calculating the tunneling current when the cathode is  $p^+$  polysilicon on account of low surface electron concentration. With these "corrections," tunneling characteristics are reduced to a unique curve predicted by Fowler-Nordheim and direct tunneling conduction theory [3.4,3.5].

:

Fig. 3.1 Voltage and Current Dependence of  $Q_{bd}$  for oxide with  $n^+$  and  $p^+$  polysilicon gate. The bias dependence follows the prediction of the anode hole injection model [3.9].  $Q_{bd}$  is lower for  $p^+$  polysilicon gate.

Fig. 3.2 Quantum Efficiency of Hole Generation Process,  $J_p / J_n$ , inversely proportional to  $Q_{bd}$  and  $t_{bd}$ , measured by the hole separation technique [3.2,3.3], is similar for both  $n^+$  and  $p^+$  polysilicon, showing no enhanced hole generation for the  $p^+$  gate. Bias configuration for hole separation measurement is shown in Fig. 2.2. Tunneling electrons are supplied by the source and drain regions with current density  $J_n$ . Holes generated in the anode tunnel towards the substrate where they are collected as substrate current,  $J_p$ . Time integrated electron tunneling current is  $Q_{bd}$ , whereas time integrated hole current is  $Q_p$ .

Fig. 3.3 Comparison of  $\mathbf{Q_p}$  values measured using hole separation for n<sup>+</sup> and p<sup>+</sup> polysilicon showing that oxide under p<sup>+</sup> gate can sustain less hole injection at breakdown.

Fig. 3.4 Voltage dependence of breakdown lifetime for thin oxides showing that the Anode Hole Injection Model can accurately predict breakdown lifetime at low voltages for oxide under both n<sup>+</sup> and p<sup>+</sup> polysilicon gate.

### 3.5. References

- [3.1] L. C. Parrillo, S. J. Hillenias, R. L. Field, E. L. Hu, W. Fichtner and M.-L. Chen, "A Fine-line CMOS that Uses P+ Polysilicon Silicide Gates for NMOS and PMOS Devices," *International Electron Devices Meeting*, p. 418, 1984.

- [3.2] I.-C. Chen, S. E. Holland and C. Hu, "Oxide Breakdown Dependence on Thickness and Hole Current - Enhanced Reliability of Ultra-Thin Oxides," *International Electron Devices Meeting*, p. 660, 1986.

- [3.3] B. Eitan and A. Kolodny, "Two Components of Tunneling Current in Metal-Oxide-Semiconductor Structures," *Applied Physics Letters*, vol. 43, no. 1, p. 106, 1983.

- [3.4] E. Rosenbaum, R. Moazzami and C. Hu, "Implications of Waveform and Thickness Dependence of SiO<sub>2</sub> Breakdown on Accelerated Testing," Proceedings of the International Symposium on VLSI Technology, Systems, and Applications, p. 214, 1991.

- [3.5] K. F. Schuegraf, C. C. King and C. Hu, "Impact of Polysilicon Depletion in Thin Oxide MOS Technology," *Proceedings of the International Symposium on VLSI Technology, Systems, and Applications*, p. 86, 1993.

- [3.6] B. J. Fishbein and D. B. Jackson, "Performance Degradation of N-Channel MOS Transistors During DC and Pulsed Fowler-Nordheim Stress, *Proceedings of the International Reliability Physics Symposium*, p. 159, 1990.

- [3.7] S. J. Wang, I.-C. Chen, and H. L. Tigelaar, "Effects of Poly Depletion on the Estimate of Thin Dielectric Lifetime", *IEEE Electron Device Letters*, vol. 12, no. 11, p. 617, 1991.

- [3.8] C.-L. Huang and N. D. Arora, "Measurements and Modeling of MOSFET I-V Characteristics with Polysilicon Depletion Effect," *IEEE Transactions on Electron Devices*, vol. ED-40, no. 12, p. 2330, 1993.

- [3.9] K. F. Schuegraf and C. Hu, "Hole Injection SiO<sub>2</sub> Breakdown Model for Very Low Voltage Lifetime Extrapolation," to appear in *IEEE Trans. on Elec. Dev.*

- [3.10] Z. A. Weinberg, W. C. Johnson, and M. A. Lampert, "High-Field Transport in SiO<sub>2</sub> on Silicon Induced by Corona Charging of the Unmetallized Surface," *Journal of Applied Physics*, vol. 47, no. 1, p. 248, 1976.

- [3.11] Z. A. Weinberg, M. V. Fischetti, and Y. Nissan-Cohen, "SiO<sub>2</sub>-Induced Substrate Current and its Relation to Positive Charge in Field-Effect Transistors," *Journal of Applied Physics*, vol. 59, no. 3, p. 824, 1986.

- [3.12] S. E. Holland, I.-C. Chen, and C. Hu, "Ultra-Thin Silicon-Dioxide Breakdown Characteristics of MOS Devices with n<sup>+</sup> and p<sup>+</sup> Polysilicon Gates," *IEEE Electron Device Letters*, vol. 8, no. 12, 1987.

- [3.13] N. S. Saks and D. B. Brown, "Observation of H<sup>+</sup> Motion During Interface Trap Formation," *IEEE Transactions on Nuclear Science*, vol. 37, no. 6, p. 1624, 1990.

- [3.14] D. J. DiMaria, E. Cartier and D. Arnold, "Impact Ionization, Trap Creation, Degradation, and Breakdown in Silicon Dioxide Films on Silicon," *Journal of Applied Physics*, vol. 73, no. 7, p. 3367, 1993.

- [3.15] Y. Hiruta, F. Matsuoka, K. Hama, H. Iwai, K. Maeguchi and K. Kanzaki, "+BT Instability in P+ Poly Gate MOS Structure," *International Electron Devices Meeting*, p. 578, 1987.

# Chapter 4

# Temperature Acceleration of Breakdown

#### 4.1. Introduction

This chapter presents a study of the temperature acceleration of oxide breakdown within the framework of the anode hole injection model. This study shows that the shape of the oxide breakdown characteristic, that is that of  $Q_{bd}$  and  $t_{bd}$ , is virtually independent of temperature for temperatures less than 150 °C. However, the oxide's immunity to hole injection, as measured by  $Q_p$ , decreases with increasing temperature with an activation energy of about 250 meV. This increased susceptibility to hole injection indicates that holes are more efficient mediators of the oxide damage leading to breakdown at higher temperatures.

### 4.2. Temperature Acceleration

It is generally accepted that higher temperatures degrade the oxide breakdown characteristics. This section discusses the temperature acceleration of oxide breakdown within the framework of the low-voltage anode hole injection model, showing that the degraded oxide integrity at higher temperatures is attributable to the oxide's reduced immunity to injected holes at higher temperatures.

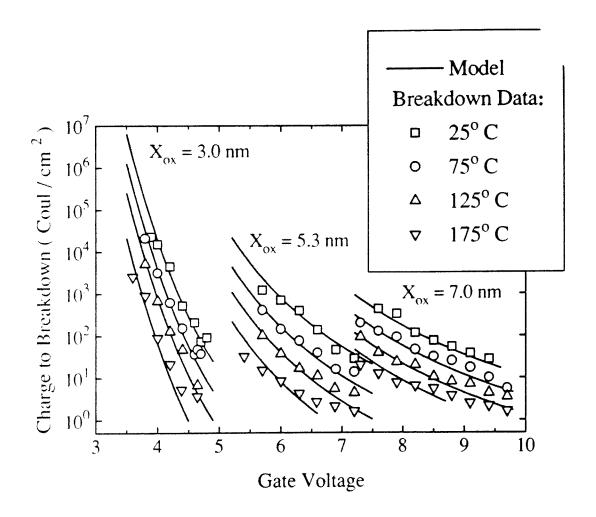

## 4.2.1. Charge to Breakdown

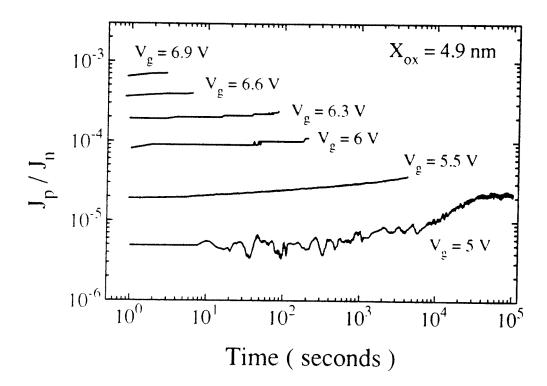

The field dependent ratio of hole current to electron tunneling current,  $J_p / J_n$ , i.e. the quantum efficiency that a tunneling electron induces the injection of a hole into the oxide from the anode can be measured using the hole separation technique [4.1,4.2] of

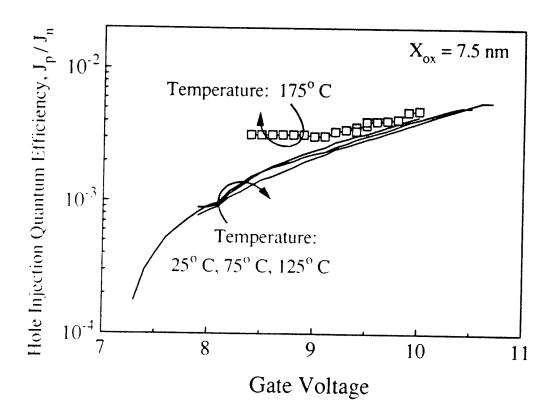

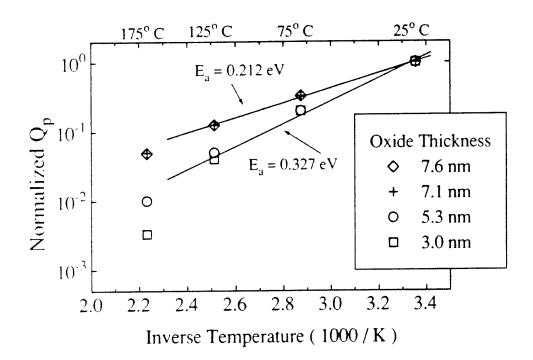

an nMOSFET biased as described in Chapter 2. Figure 4.1 illustrates the temperature independence of the quantum efficiency of the hot-hole injection between 25 °C and 125 °C. Therefore the voltage dependence of  $Q_{bd}$  should follow the prediction of Eq. (2.5) as shown in Figure 4.2. The reduction in  $Q_{bd}$  in Figure 4.2 with increasing temperature is modeled solely by a reduction in  $Q_p$ , as shown in Figure 4.3. This reduction in  $Q_p$  shows that an oxide is more vulnerable to hole transport at higher temperatures. That is, holes are more effective agents of damage to the oxide at higher temperatures. The activation energy of  $Q_p$  was found to be 0.212 eV for 70 Å and 76 Å oxides and 0.327 eV for oxides thinner than 55 Å.

The number of holes flowing through an oxide to reach breakdown,  $Q_p$ , has been empirically observed to be constant independent of applied bias [4.1,4.3]. Moreover, hole injection has been shown to lead to bulk oxide trap generation [4.4,4.5,4.6,4.7] as well as interface trap generation [4.8]. This establishes a correlation between hole fluence and oxide damage. The temperature activation of  $Q_p$  therefore reflects an acceleration of the hole-mediated oxide damage mechanism.

The appearance of a temperature dependence of the injected hole quantum efficiency between 125 and 175 °C may explain the reported increase in activation energy at temperatures above 150 °C [4.9,4.10,4.11]. Not only is the oxide immunity to injected holes diminished above 150 °C, but the tunneling electrons become more efficient in generating and injecting holes into the SiO<sub>2</sub>. Thus, the hole separation measurement offers insight into the physical mechanism responsible for increased activation energies of oxide breakdown above 150 °C. That is, the activation energy above 150 °C is the sum of two components: the first represents the decrease in Q<sub>p</sub> at higher temperatures, the second the significantly increased efficiency of the anode hole injection process above 150 °C.

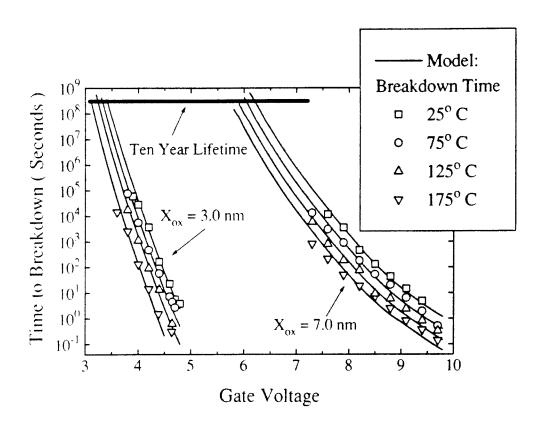

#### 4.2.2. Time to Breakdown

Since breakdown time,

$$t_{bd}$$

, is related to  $Q_{bd}$  as

$$t_{bd} = \frac{Q_{bd}}{J_{n}}$$

(4.1),

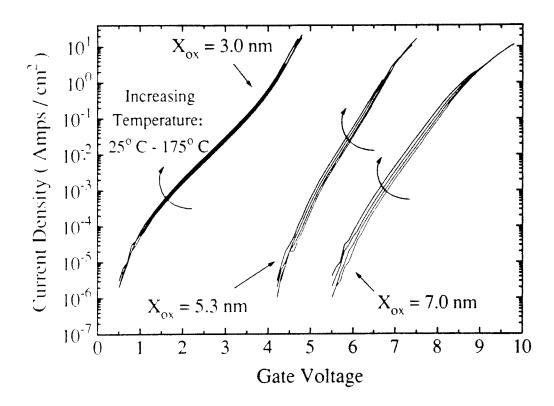

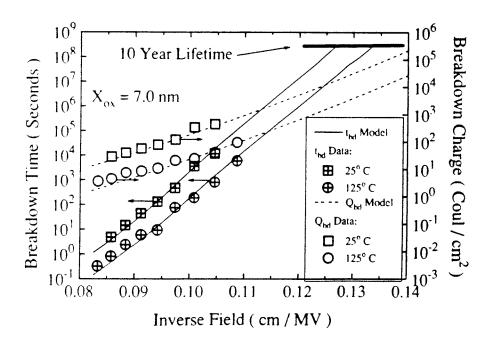

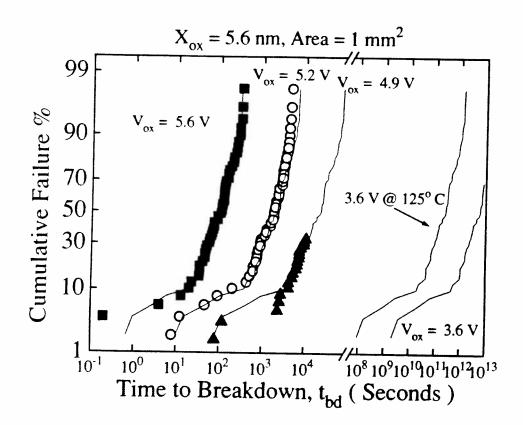

understanding the voltage and temperature dependence of the electron tunneling current,  $J_n$ , is essential. For applied voltages greater than 3.15 Volts, electrons tunnel through a triangular barrier and the tunneling current follows the Fowler-Nordheim relationship. For lower voltages, electrons tunnel through a trapezoidal barrier; this direct tunneling oxide leakage current is significantly enhanced over that predicted by the Fowler-Nordheim relationship[4.12]. Figure 4.4 shows that the increase of Fowler-Nordheim and direct tunneling current due to increased temperature is secondary compared with its exponential increase with increasing voltage. Moreover, the sensitivity on temperature decreases with decreasing thickness. The reduction in  $t_{bd}$  for increased temperature is accurately predicted using Eqs. (2.5) and (4.1) as shown in Figure 4.5, establishing that the anode hole injection model is able to predict very low voltage intrinsic breakdown lifetime.

Figure 4.6 shows that the logarithms of  $Q_{bd}$  and  $t_{bd}$  are linear functions of inverse field with a slope that is insensitive to temperature. Both  $Q_{bd}$  and  $t_{bd}$  are seen to decrease by a factor of approximately 20 between 25 °C and 125 °C. This acceleration factor holds true for oxides between 30 Å and 80 Å.

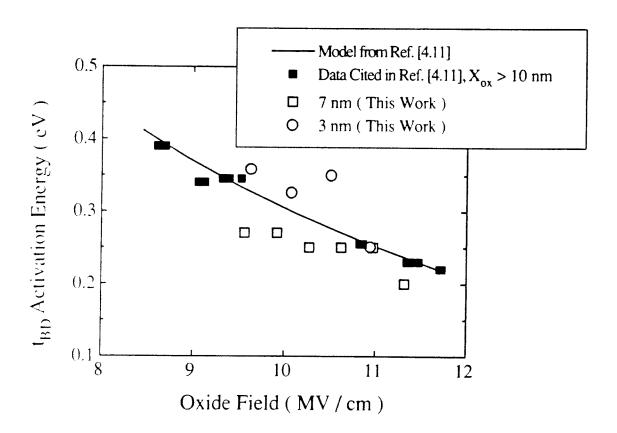

Figure 4.7 compares the t<sub>bd</sub> activation energies for the thin oxides in this study with those reported in other studies [4.9,4.13,4.14,4.15]. While the activation energy appears to be independent of field for oxides thinner than 80 Å, it has been shown to decrease with increasing field for oxides thicker than 100 Å [4.11]. Perhaps the electron energy gained inside the oxide, significant for thick oxides, is temperature dependent. This is consistent with a temperature dependent scattering length [4.16].

## 4.3. Summary and Conclusions

This chapter completes the development of a comprehensive quantitative model for "intrinsic" silicon dioxide breakdown, based on the concept of anode hole injection, accounting for the effects of field and temperature acceleration. This model enables prediction of insulator reliability at operating voltages, 3.3 Volts and below for oxides below 100 Å. The next chapter considers the role of defects in limiting the realization of the high intrinsic oxide quality in large area structures, i.e. integrated circuits or canonical test structures that resemble them, developing a means of quantifying an oxide technology's defectivity using the physically-based intrinsic breakdown models.

Fig. 4.1 Quantum Efficiency of Hole Generation Process,  $J_p/J_n$ , inversely proportional to  $Q_{bd}$  and  $t_{bd}$ , is independent of temperature between 25° C and 125° C, measured by the hole separation technique [4.1]. Bias configuration for hole separation measurement is shown in Fig 2.2. Tunneling electrons are supplied by the source and drain regions with current density  $J_n$ . Holes generated in the anode tunnel towards the substrate where they are collected as substrate current,  $J_p$ .

Fig. 4.2 Voltage dependence of  $\mathbf{Q_{bd}}$  for several different temperatures. Reduction in  $\mathbf{Q_{bd}}$  with increasing temperature is due to oxide's lower hole immunity at higher temperatures.

Fig. 4.3 Temperature dependence of  $Q_p$ , normalized as  $Q_p(T)/Q_p(T=25^{\circ}C)$ , for several different oxide thicknesses. Reduction of  $Q_p$  reflects oxide's lower hole immunity at higher temperatures. Only  $Q_p$  is adjusted to model the breakdown data in Fig. 4.2.

Fig. 4.4 Temperature dependence of electron tunneling current is negligible and decreases for thinner oxides.

Fig. 4.5 Breakdown lifetime, t<sub>bd</sub>, decreases with increasing temperature, but Anode Hole Injection Model maintains its ability to predict the breakdown characteristics.

Fig. 4.6 Inverse field dependence of  $t_{bd}$  and  $Q_{bd}$  for 70 Å oxide shows nearly linear slope that is independent of temperature.

Fig. 4.7 Survey of temperature activation energies for breakdown lifetime reported in the literature. This work concludes that activation energy is independent of field for oxides thinner than 80 Å.

#### 4.4. References

- [4.1] I.-C. Chen, S. E. Holland and C. Hu, "Oxide Breakdown Dependence on Thickness and Hole Current - Enhanced Reliability of Ultra-Thin Oxides," *International Electron Devices Meeting*, p. 660, 1986.

- [4.2] K. F. Schuegraf and C. Hu, "Hole Injection SiO<sub>2</sub> Breakdown Model for Very Low Voltage Lifetime Extrapolation," *IEEE Trans. on Elec. Dev.*, May, 1994.

- [4.3] K. R. Mistry, D. B. Krakauer, and B. S. Doyle, "Impact of Snapback-Induced Hole Injection on Gate Oxide Reliability of N-MOSFETs," *IEEE Electron Device Letters*, vol. 11, no. 10, p. 460, 1990.

- [4.4] S. K. Lai, "Interface Trap Generation in Silicon Dioxide when Electrons are Captured by Trapped Holes," *Journal of Applied Physics*, vol. 54, no. 5, p. 2540, 1983.

- [4.5] I.-C. Chen, S. E. Holland, and C. Hu, "Electron-trap Generation by Recombination of Electrons and Holes in SiO<sub>2</sub>," *Journal of Applied Physics*, vol. 61, no. 9, p. 4544, 1987.

- [4.6] H. Uchida and T. Ajioka, "Electron Trap Center Generation Due to Hole Trapping in SiO<sub>2</sub> Under Fowler-Nordheim Tunneling Stress," *Applied Physics Letters*, vol. 51, no. 6, p. 433, 1987.

- [4.7] S. Ogawa, N. Shiono, and M. Shimaya, "Neutral Electron Trap Generation in SiO<sub>2</sub> by Hot Holes," *Applied Physics Letters*, vol. 56, no. 14, p. 1329, 1990.

- [4.8] D. J. DiMaria, D. Arnold, and E. Cartier, "Degradation and Breakdown of Silicon Dioxide Films on Silicon," Applied Physics Letters, vol. 61, no. 19, p. 2329, 1992.

- [4.9] C. F. Chen, C. Y. Wu, M. K. Lee, and C. N. Chen, "Dielectric Reliability of Intrinsic Thin SiO<sub>2</sub> Films Thermally Grown on a Heavily Doped Si Substrate-Characterization and Modeling," *IEEE Transactions on Electron Devices*, vol. ED-34, no. 7, p. 1540, 1988.

- [4.10] Y. Hokari, T. Baba and N. Kawamura, "Reliability of 6-10 nm Thermal SiO<sub>2</sub> Films Showing Intrinsic Dielectric Reliability," *IEEE Transactions on Electron Devices*, vol. ED-32, no. 11, p. 2485, 1985.

- [4.11] R. Moazzami, J. C. Lee, and C. Hu, "Temperature Acceleration of Time-Dependent Dielectric Breakdown," *IEEE Transactions on Electron Devices*, vol. ED-36, no. 11, p. 2462, 1989.

- [4.12] K. F. Schuegraf, C. C. King and C. Hu, "Ultra-Thin Silicon Dioxide Leakage Current and Scaling Limit," Symposium on VLSI Technology Digest of Technical Papers, p. 18, 1992.

- [4.13] D. L. Crook, "Methods of Determining Reliability Screens for Time Dependent Dielectric Breakdown," *International Reliability Physics Symposium*, p. 1, 1979.

- [4.14] K. Yamabe and K. Taniguchi, "Time-dependent Dielectric Breakdown of Thin Thermally Grown SiO<sub>2</sub> Films," *IEEE Transactions on Electron Devices*, vol. ED-32, no. 2, p. 423, 1985.

- [4.15] D. A. Baglee, "Characteristics and Reliability of 100 Å Oxides," *International Reliability Physics Symposium*, p. 152, 1984.

- [4.16] D. J. DiMaria, "Trap Creation in Silicon Dioxide Produced by Hot Electrons," *Journal of Applied Physics*, vol. 65, no. 6, p. 2342, 1989.

# Chapter 5

## **Effect of Defects**

#### 5.1. Introduction

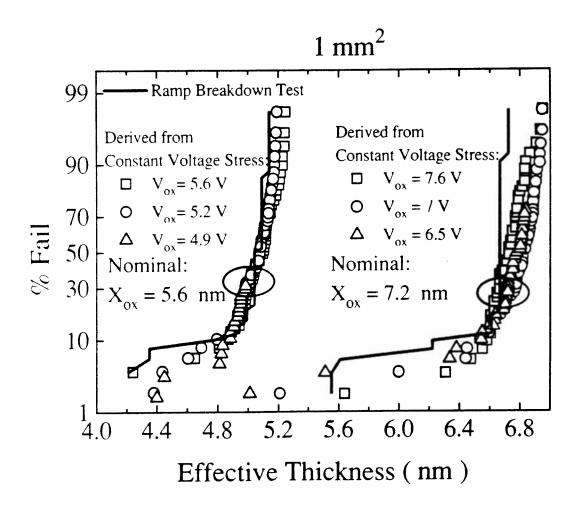

This chapter presents the results leading to the development of simple methodology for characterizing the defectivity of a thin oxide technology. Whereas the preceding discussion focused on understanding the voltage and temperature dependence of intrinsic breakdown, i.e. the breakdown of small area oxide samples, this chapter examines the role of defect-induced breakdown observable in large area oxide samples, i.e. those with a higher probability of containing gross oxide defects. Precisely these gross oxide defects limit the oxide yield and reliability of VLSI circuits. The following defect breakdown model offers a framework for determining whether an oxide technology offers ample lifetime at the circuit's operating voltage based on the physical anode hole injection model, by combining the intrinsic anode hole injection model with an "effective" thinning model [5.1].

### 5.2. Defect-Related Breakdown Model

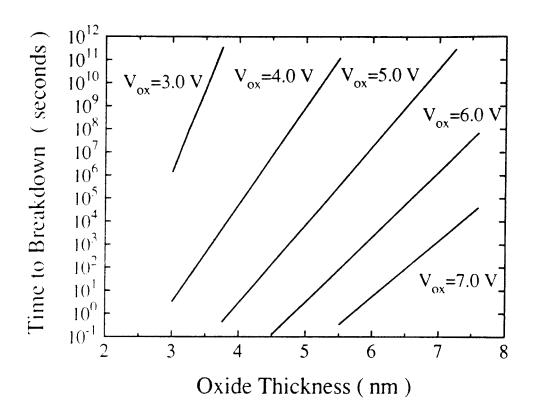

Figure 5.1 summarizes the intrinsic 25 °C breakdown lifetime as a function of oxide thickness for several oxide voltages. This breakdown lifetime can be approximated as

$$t_{bd} = \tau_o e^{\frac{GX_{ca}}{V_{ca}}}$$

(5.1)

where G = 390 MV/cm and  $\tau_0 \approx 5 \cdot 10^{-13}$  sec. Despite increasing extrapolation slope, G, and decreasing pre-exponential constant as oxide thickness decreases (see Figure 2.14), Eq. (5.1) serves as an excellent approximation, thereby minimizing computational complexity of the effective thinning model. An intrinsic 400 year

lifetime (equivalent to 20 years at  $125^{\circ}$  C) is achievable with a 40 Å oxide for  $V_{OX}$  = 3.3 V; however, in practice, some thickness margin needs to be provided for defects in order to guarantee adequate dielectric reliability. This section uses the concept of effective thinning to model oxide defects in order to determine the density of defects that would cause premature breakdown.

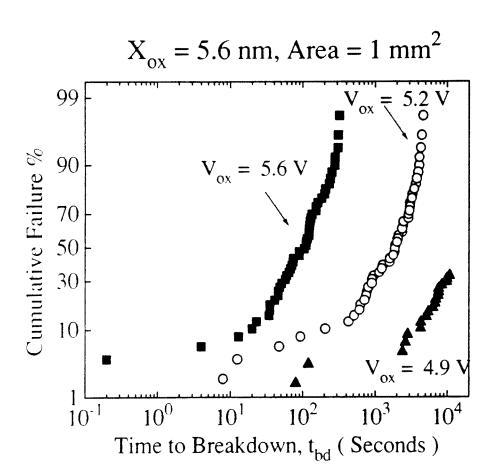

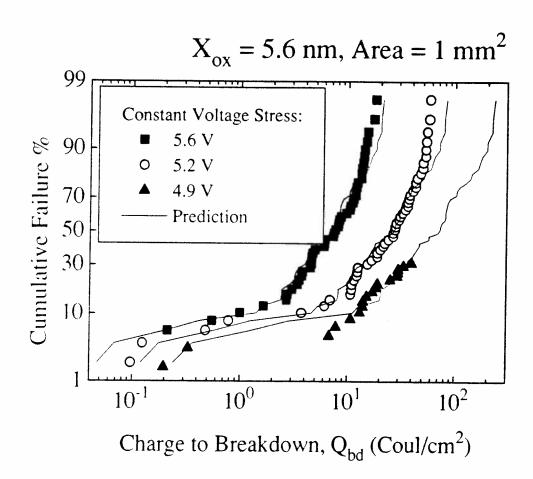

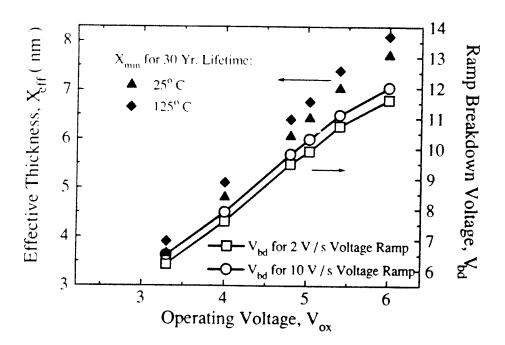

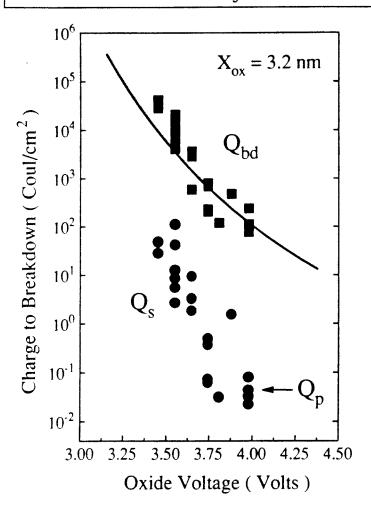

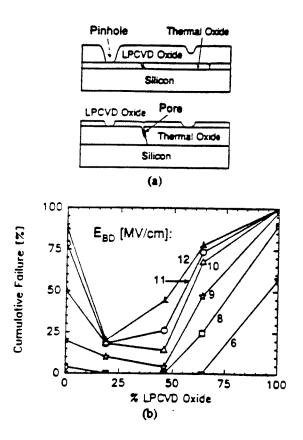

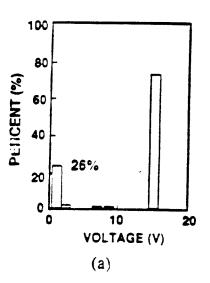

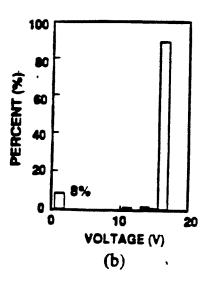

Figure 5.2 shows the time-dependent dielectric breakdown data in cumulative percentage versus time for large area (1 mm²) capacitors under positive bias. For each of the 5.6 V, 5.2 V, and 4.9 V bias conditions, there is a broad lifetime distribution spreading several orders of magnitude only approaching the intrinsic breakdown lifetimes. This distribution of breakdown lifetimes is due to defects of varying severity. The concept of "effective thinning" [5.1], illustrated in Figure 5.3, enables quantitative analysis of these statistical distributions of high field breakdown lifetime to accurately predict low field breakdown distributions. All oxide defects are modeled by an effective oxide thickness less than the nominal thickness determined by the breakdown lifetime as follows: each lifetime data point in Figure 5.2 is translated into an effective thickness according to the intrinsic breakdown model predictions of Figure 5.1. Alteratively, interpreting  $X_{\rm OX}$  as  $X_{\rm eff}$  in Eq. (5.1), the effective thickness follows from the breakdown lifetime as

$$X_{\text{eff}} = \frac{V_{\text{ox}}}{G} \cdot \ln \left[ \frac{t_{\text{BD}}}{\tau_{\text{o}}} \right]$$

(5.2)

where  $X_{eff} < X_{OX}$  defines the effective thickness for a sample with nominal oxide thickness  $X_{OX}$ . The  $X_{eff}$  term may reflect "real" oxide thinning, surface asperities which enhance  $E_{OX}$  (mathematically equivalent to a reduction in  $X_{eff}$ , see Eq. (5.2)), or a locally reduced tunneling barrier height (reducing G in Eq. (5.2), again,

mathematically equivalent to a reduction in  $X_{eff}$ ). All these effects can decrease  $t_{bd}$ . The device's "thinnest" spot, i.e. smallest  $X_{eff}$ , determines  $t_{bd}$ .