# Copyright © 1975, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# A STRUCTURED STUDY OF PARALLEL PIPELINED SYSTEMS

bу

Hon Fung Li

Memorandum No. ERL-M530

13 August 1975

### ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

# A STRUCTURED STUDY OF PARALLEL PIPELINE SYSTEMS

Doctor of Philosophy

Hon Fung Li

Electrical Engineering and Computer Sciences

C.V. Ramamoorthy

Chairman of Thesis Committee

## <u>Abstract</u>

An attempt is made to tackle some design and operational problems related to parallel pipeline systems in a unified way, hoping to represent some initial efforts towards the development of a structural theory for such a powerful and versatile processing scheme. Previous work in related areas will be reviewed to form the background of research work reported here. Specific areas studied include: (1) sequencing algorithms and control in different classes of parallel pipeline systems, (2) system partitioning and decomposition to improve system throughput and control complexity, (3) availability improvement via proper redundancy allocation and graceful degradation, (4) restructure architecture and a suggested implementation to increase system flexibility to cope with the requirements of specific application environments.

The classification of different parallel pipeline systems

permits one to pursue further the relevance of different optimi

zation aspects to different classes. In sequencing, fast heuristics

are necessary to dynamically optimize the instruction processing

in an ordinary pipelined processor. The design criteria developed in this thesis are useful in validating one's initial design or conjecture. As throughput and availability are now primary performance measures of a system, the algorithms introduced here will be oriented towards the improvement of either or both measures.

Finally the modularity of a parallel pipeline system is further examined. In proposing a future design where restructuring of system components physically and logically is allowed many related aspects are discussed. Restructuring permits the system control to match the system configuration with the application requirement. Consequently, the system utilization, throughput and availability can be enhanced. The internal routing structure in a restructurable pipeline system is also investigated. The proposed scheme tries to reduce the need of memory fetches (therefore reducing memory interference) and to simplify the switching hardware involved. It is in fact quite similar to an extended data flow architecture that has recently received quite a lot of attention.

The wide scope of this thesis does not represent an overflow of ambition. The areas studied are chosen to provide a more global picture of parallel pipeline systems in computers which otherwise may be misinterpreted in many respects.

### Acknowledgment

The author wishes to express his sincere gratitude to a number of individuals who have either directly or indirectly provided him with generous assistance throughout his education at Berkeley. Uncountably infinite thanks are due to his supervisor Professor C.V. Ramamoorthy who was also the dissertation committee chairman and who has contributed in every way to his development at Berkeley. Through his constant advice, support, guidance and encouragement, especially at time when the inevitable evil of disillusionment arose, this thesis has finally come into shape. Without his help, none of this would have been possible.

Special thanks are also due to Professor I. Lee for his valuable advice and encouragement, and Professor K. Doksum for serving on his thesis committee. Professors D. Ferrari and E. Lawler are also thanked for their guidance during his years at Berkeley. Thanks are also due to our excellent secretary, Ms. Ruth Suzuki, for her unequalled skill of accurate and helpful typing.

He also wants to thank the National Science Foundation for its support through grants NSF GJ-35839 and DCR 72-03734-A01 under which the reported work has been accomplished.

Finally, and above all, this author wishes to acknowledge the spiritual and financial support of his most unselfish and devoted parents in Hong Kong. His former fiancée, Lisa, now his wife, is also much appreciated for her typing the draft and patience throughout.

# Table of Contents

|       |                                                                                             | Page |

|-------|---------------------------------------------------------------------------------------------|------|

| 1.    | Introduction                                                                                | 1    |

| 2.    | Sequencing and Dynamic Reconfiguration In Reconfigurable Shared Resource Pipeline Systems . | 28   |

| 2.1   | Scheduling and Sequencing Problems in General                                               | 28   |

| 2.2   | Modeling                                                                                    | 42   |

| 2.3   | Collision Avoidance                                                                         | 49   |

| 2.4   | Theoretical Basis of Sequencing                                                             | 56   |

| 2.5   | Sequencing Heuristics                                                                       | 77   |

| 2.6   | Experimental Demonstration                                                                  | 82   |

| 3.    | System Partitioning and Decomposition                                                       | 92   |

| 3.1   | System Partitioning                                                                         | 92   |

| 3.2   | Problem Formulation for Partitioning                                                        | 97   |

| 3,3   | Solutions                                                                                   | 100  |

| 3.4   | An Optimal Algorithm                                                                        | 107  |

| 3.5   | Resource Decomposition Via Pipelining and Other Techniques                                  | 115  |

| 3.6   | Problem Formulation and Algorithms                                                          | 120  |

| 4.    | Design of Ultra-reliable and Available RSRP Systems                                         | 151  |

| 4.1   | Ultra-reliable Fault-Tolerant Techniques                                                    | 151  |

| 4.2   | Optimal Redundant Selection in Linear Pipes                                                 | 158  |

| 4.3   | Optimal Redundancy Allocation in RSRP                                                       | 164  |

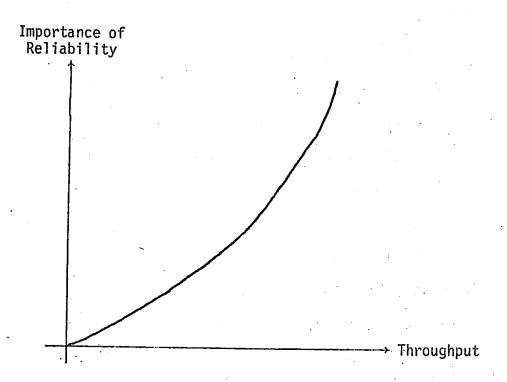

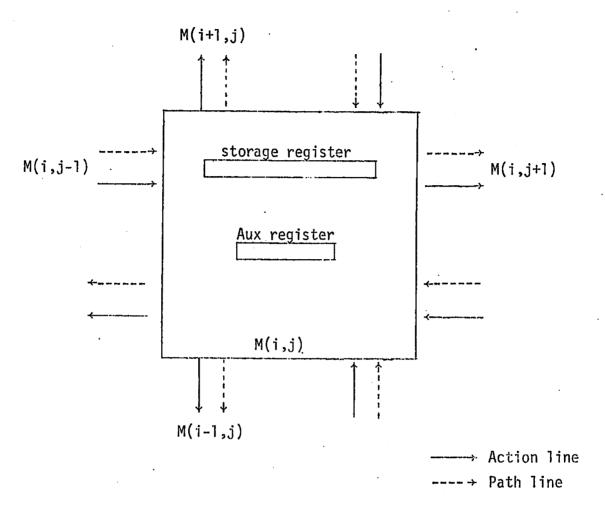

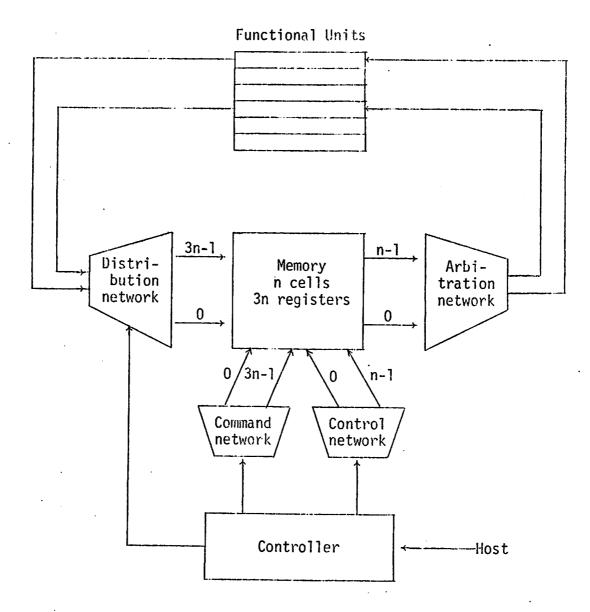

| 5.    | Restructurable (Reconfigurable) Architecture for RSRP Systems                               | 184  |

| 5,1   | Origin of Restructurable Architecture                                                       | 184  |

| 5.2   | Detection of Restructuring Criterion                                                        | 189  |

| 5.3   | Decision Making                                                                             | 199  |

| 5.4   | Implementation                                                                              | 209  |

| 6.    | Conclusion and Future Extension                                                             | 226  |

| Refer | rences                                                                                      | 238  |

#### A STRUCTURED STUDY

#### OF PARALLEL PIPELINED SYSTEMS

H.F. Li

Computer Science Division

Department of Electrical Engineering and Computer Sciences

University of California at Berkeley

December 1975

#### CHAPTER 1

## Introduction

In the growth of computer architecture, many innovative designs were studied and developed. Deviations from Von Neuman's type of computer organization readily emerged and have significant impact on the power and processing capability of a conventional computer system. For many applications, a fast processing speed and turnaround time are demanded. To cope with this requirement, and considering the cost-effectiveness or flexibility of the resulting system, a multiprocessor type of design is often adopted. In almost all cases, the multiprocessor system can be identified as consisting of parallel processors, pipelined processors or both. Then why is parallel or pipeline processing advantageous?

Before attempting to discuss the various characteristics of parallel and pipeline processing, the basic philosophy behind a multiprocessor design should be revealed. In the past decade, hardware technology, especially large scale integration circuit techniques, has advanced so much that the logical elements (processing facilities) no longer dominate the cost of a hardware system. Disregarding the peripherals, the cost of a hardware

5

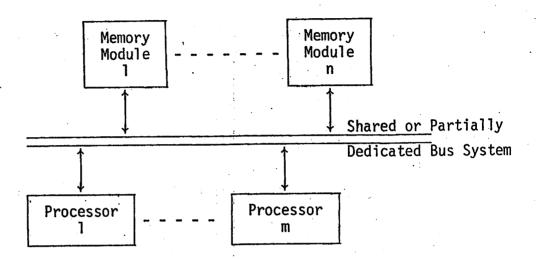

system is more likely dominated by the main memory capacity and it is most desirable to incorporate more logical elements if the latter can increase the throughput of the system, with little control overhead. The study of modular memory and processing systems also facilitates the growth in multiprocessor designs. With modular memory banks, in a dedicated assignment or interleaved arrangement, a higher throughput or bandwidth is available [1]. And with modular processing systems, additional processors can be added and a global controller can monitor all processing activities. A general multiprocessor system can be as illustrated in Figure 1.1. In this example system, concurrent processing among the processors is allowed so that more useful outputs may be produced by the overall system. It should be noted, however, that the real obstacle in a multiprocessor system is not on the inclusion of additional processors, but the efficient control and exploitation of its power. The cost of adding a processing element often can be ignored compared to the other additional control and memory overhead (hardware or software) needed. Therefore, many crucial and complicated decisions are involved in a multiprocessor design.

While both parallel and pipeline processing are techniques to speed up the throughput rate of a processing system because of application requirements, they are similar and different in many respects. There are two situations where a multiprocessor system is being used. One is for executing a single program and the other is for executing multiple programs simultaneously. Naturally the former can be called a uniprogramming environment and the latter a multiprogramming environment. In the former case, parallel

Figure 1.1

A Multiprocessor System

processing is employed to reduce the execution time of some important applications programs. Normally, the program will be partitioned into parallel tasks to be executed by the parallel processors. The 'partitioning' of programs can be accomplished in different ways. Sometimes, a programmer can explicitly indicate these 'partitions' and sometimes, the system has to 'detect' these 'partitions'. Then the parallel tasks can be executed by the available processors and consequently a shorter execution time may be achieved. Parallel processing is extremely useful and important in some applications that have real time urgency, such as weather forecasting, air traffic control, ABM defense and other real time problems. In many of these cases, the objective is to execute some programs as fast as possible at all costs in terms of system resources.

In a multiprogramming environment, the partitioning of a single program is no longer a prime concern. Now different programs (processes) can be run on different processors sharing some crucial system resources such as memory in an effective way. The system does not worry about the execution time of a single job only, but has to manage its resources carefully to satisfy the demands of all users, subject to some priority criterion. Under this situation, therefore the system increases its production of useful outputs in a most desirable way.

Hence, parallel processing can be characterized by the overlapped operations among processing elements in a computer system Sometimes, multiple instruction streams may be identified and sometimes, only multiple data streams are noticeable. This is

because parallel processing is a technique implementable in several levels of design. In a high level, independent processors can execute independent program segments concurrently. Then, a multiple instruction multiple data stream is clearly visible with a resulting speed-up of the original sequential program. Although from the surface it seems this is a logical way to speed up a system and upgrade the utilization of other system resources such as memory, peripheral devices, it has tremendous operational problems that often beat the original objectives in mind. These problems include the task specification or detection, sychronization, scheduling and other management problems which will be discussed shortly afterwards. So in a uniprogramming environment, except for special applications, real time problems or process control systems, parallel level is yet to be justified. Because processing in such a high of this reason, parallel processing systems (for a uniprogramming consideration) are quite rare. The PEPE machine exhibits some form of parallel processing of this kind [2]. In PEPE, each of the three control units contains program segments to be executed by the processing elements they control, in an array type of organization. But in a lower level, array processing is a special form of parallel processing where autonomous processing elements execute the same instruction simultaneously, in their own data stream. Hence, a single instruction multiple data stream characterization fits the system quite well [3]. Examples of array processors are numerous. They include the ILLIAC IV with 64 processing elements under a central control, the STARAN associative array processor which includes associative processing capability to the processing

. K

elements, as well as the PEPE system mentioned previously [4,5]. It should be noted that the STARAN and PEPE systems are designed especially for the purpose of air traffic tracking and therefore special functional facilities for associative and correlation processing are incorporated.

In a lower level still, parallel processing can be observed among special purpose processing facilities such as arithmetic units for performing different kinds of arithmetic operations.

Here, the smaller types of parallelism in programs can be exploited. Many computer systems exhibit this characteristic including the more common CDC 6400, 6600, 7600, and some IBM System 360 machines [6,7]. With multiple arithmetic units, multipliers, adders, etc., independent operations can be performed in parallel. These logical elements help to increase the utilization and throughput of the rest of the system because more work can be performed by the system per unit time. For if multiple instructions are executable by these adders, multipliers, etc., more effective memory fetches and stores per unit time are achievable, and more productive outputs generated. The system as a whole benefits.

So the idea of overlapped processing as exemplified by parallel processing can reduce the execution time of programs by a satisfactory amount. In a fairly analogous way, pipelining can also produce the same effect. Pipelining is a common technique in almost all processing systems to satisfy some cost-effective and speed criteria. Ranging from manufacturing assembly lines in industry to minute LSI chips for performing some fast operations such as multiplication, pipelining has been a common tool. The philosophy

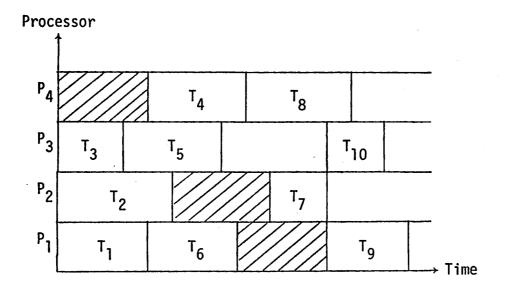

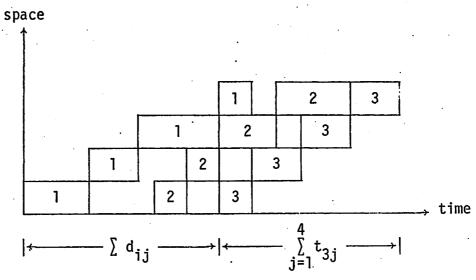

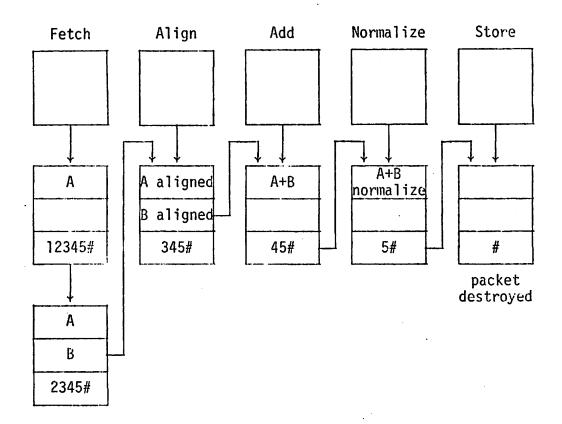

behind pipelining is to subdivide a long, complicated process into sequential subprocesses each executed or accomplished by an individual autonomous station or facility which operates in an overlapped mode with the others. Overlapping exists among subprocesses for a sequential set of input (to be processed), the so-called tasks. The idea of pipelining and parallel processing can be best demonstrated using a space-time diagram, the Gantt chart in Figure 1.2 [8]. The horizontal axis represents time, and the vertical space. From this figure, the overlapping mechanism in both techniques are fully manifested.

Similar to parallel processing, pipelining in computer systems also exists in many levels of consideration. In the highest level, the overlap between the central processor unit and the input-output mechanism can be viewed as a primitive pipeline for processing tasks from programs. After streaming through the CPU, a task will be operated upon by the next station, the input-output. By so doing, precious CPU and I/O times are saved so that none has to wait and waste time before the next task is ready for execution. In a slightly lower level, pipelining is a technique used to speed up the central processor unit. When the speed of a central processor unit is not fast enough to generate a satisfactory throughput rate, the instruction execution process is partitioned into subprocesses executed by autonomous modules. This is typically found in many systems including the original IBM STRETCH, 7094, System 360 Model 91, 195, etc. [9,10]. In the latter system, the instruction execution process is subdivided into five phases: instruction fetch, decode, effective address calculation, operand

Multiprocessor Version

Figure 1.2

Gantt Chart Representation

fetch, and execute. Each of these units can process independent instructions simultaneously for the specific subphases. This more flexible structure permits a higher throughput.

In an even lower level, pipelined execution units are quite popular. In many systems, the other phases of pipelined instruction processing are still faster than the action taken by the execution unit which performs different kinds of arithmetic operations or logical operations. To remedy this effect, the execution unit can be effectively pipelined, with the aid of present day hardware technology. So at least two levels of pipelining action can be visualized in many systems. With the advancement in integrated circuit technology, pipeline action can be used to construct faster special purpose chips or modules such as multipliers where each phase of the multiplication algorithm is essentially pipelined. In its ultimate form, very fast pipelined circuits are implementable as demonstrated in [11]. A distinction of the various possible levels of pipelining that appear in a computer system may be constructed directly from the level of the local control immediately supervising the particular pipelined segment.

Hence parallel and pipeline processing are complementary techniques to speed up a computation process. Equipped with parallel processing capability, independent tasks can be initiated and processed at the earliest possible time. Coupled with pipelined facilities, the throughput rate of an individual processor can be multiplied to a large extent, depending the feasibility of practical implementation (in many situations, the subdivision of a process is governed by the feasibility in practice). Looking at a lower

level, there is some tradeoff consideration involved between an array type of processing system and a pipelined processor. Usually pipelining is favorable compared to array processing if the following guidelines are satisfied.

- (1) The process can be subdivided most efficiently into subprocesses each executed by an independent module or facility in a

compatible speed with respect to the others. When a certain facility

in the pipe has a much slower speed than the rest, it will be the

sole bottleneck and hence uniquely affects the throughput rate of

the pipe. In fact, the throughput rate of a pipe is limited precisely by the throughput rate of its bottleneck, just analogous to

the fluid flow in a physical pipeline.

- (2) The submodules in the pipe are cheaper than the original nonpipelined module. This is equivalent to a cost-effectiveness consideration. For if not, the system may consider array processing as well.

- (3) Intermediate buffering is relatively cheap. Therefore the size of intermediate data packet or information transfer should be reasonably small, depending on the level of the pipelining action.

- (4) Routing of intermediate information is easily accomplished. If very complicated decision or switching is involved, perhaps the overhead and interference defeat the purpose of pipelining entirely.

- (5) Sharing of system resources, including buses, memory, registers, etc. does not result in severe interference that degrades actual throughput to a large extent. In a pipelined or parallel processor system, the memory-processing facility interconnection

and control often create tremendous amounts of headache not easily resolvable. In the end, the inadequate operand supply or lack of parallel executable tasks (instructions) destroys the power of the pipelined processor. There is some basic argument or debate about the appropriateness of a Von Neuman type of computer design with centralized memory for the purpose of multiprocessing. But, drastic changes and their justification in practice are yet to be sought.

3

These five guidelines are merely suggested to evaluate the suitability of a process (hardware or software) to be pipelined. Here, it is intended to stress that pipelining is a technique applicable to any suitable process, whether it be a pure hardware process (hardwired or microprogrammed control) or a software and hardware process (such as compilation, or the different states that a process goes through in the consideration of an operating system [12]). Though most of the discussion in this thesis will be illustrated with well-defined hardware examples, the reader is reminded that the general theories developed are applicable to any kind of pipeline system that fits the characterization or specified properties.

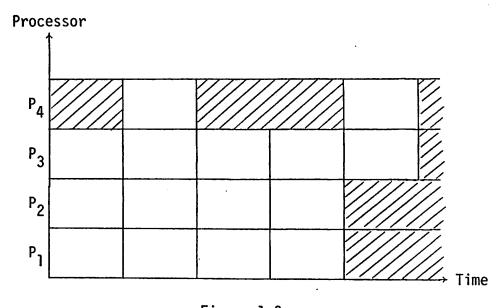

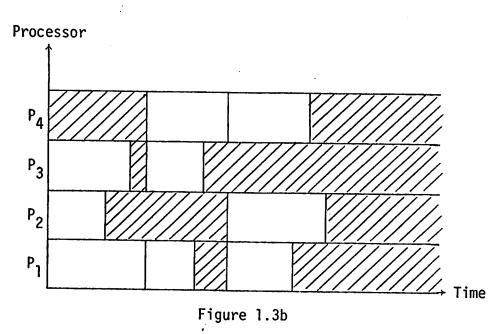

The efficiency and throughput of a multiprocessor system are often representable by a space-time diagram. A space-time diagram is most suitable to reveal precisely how the different processing facilities operate. Analytical evaluation and representation of a parallel or pipelined processing system are possible if provided with such a space-time diagram [13,14]. Specifically, for a parallel processor system, assuming all tasks have the same execution speed on each processor, the space-time diagram is as shown

in Figure 1.3a. If the execution times are different, and the next set of tasks cannot be initiated unless the previous set is completely finished, a similar space-time diagram is in Figure 1.3b.

Observe that the idle time of a processor can be explicitly measured. If we define efficiency of the processor system by:

$$\xi = \frac{total\ weighted\ space-time\ span\ of\ all\ tasks}{total\ weighted\ space-time\ span\ of\ all\ processors}$$

.

Then, for the case in Figure 1.3b,

$$\xi = \frac{\sum \left[\alpha_{k(i)}^{t_i}\right]}{\sum_{j=1}^{p} \left\{\max_{i \in S_j} \left[t_i\right] \sum_{i \in S_j} \alpha_{k(i)}\right\}}$$

where  $\alpha_i$  = weight designating importance of facility or processor i (e.g. cost × speed product)

$t_i$  = execution time of task i

k(i) = processor assigned to task i

L = total number of processors

$S_j$  = set of tasks executed in the  $j^{th}$  set

p = total number of sets of tasks considered

So if all tasks have the same execution time, and  $\alpha_{\bm i}{}'s$  are the same, then the efficiency reduces to

$$\xi = \frac{\sum_{j=1}^{p} |S_{j}|}{Lp}$$

(Note  $|S_j| \le L$ .)  $\xi \to 1$  if  $|S_j| = L$  for all j.

. J.

Figure 1.3a

Uniform Processing Time

Variable Processing Time

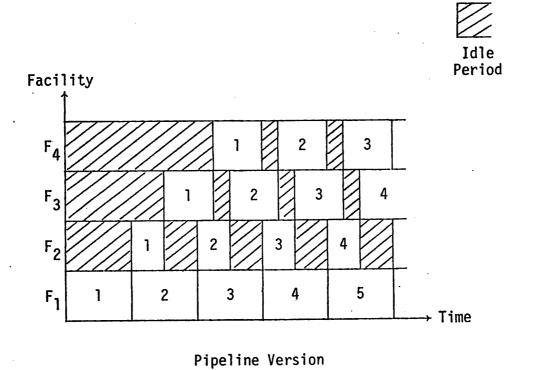

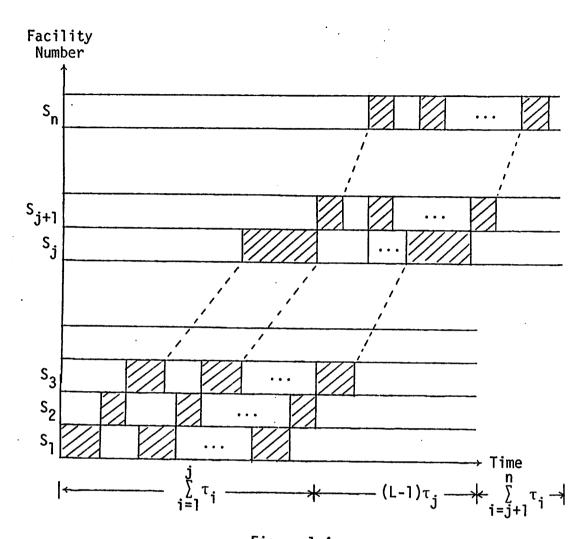

In a similar way, a space-time span can facilitate understanding the pipeline principle. In the case of a linear pipeline, the efficiency is (see Figure 1.4):

$\xi = \frac{\text{total weighted space-time span of L tasks}}{\text{total weighted space-time span of n facilities}}$

$$= \frac{L\left(\sum_{\alpha_{i}}^{n} \tau_{i}\right)}{\sum_{\alpha_{i}}^{n} \left(\sum_{\alpha_{i}}^{n} \left(L-1\right) \tau_{j}\right)}$$

where

$\tau_{i}$  = speed of bottleneck

$\tau_i$  = speed of i<sup>th</sup> facility in the pipeline

$\alpha_i$  = weight attached to the space-time space of the i<sup>th</sup> facility as determined by the cost and speed of the facility, for example, cost-speed product

L = number of tasks pumped into the pipeline in a

certain period of time. For maximum efficiency, it

will be assumed that the tasks are pumped in con tinuously, that is, the buffer at the entrance of

the pipeline is never empty. (True for some repeti tive tasks.)

n = number of facilities in the pipeline

In the ideal situation where all facilities have the same speed and importance,

$$\xi = \frac{L}{n + (L-1)}$$

so that when L approaches infinity, the efficiency approaches unity.

Figure 1.4

Efficiency of a Linear Pipeline

In all other cases, as L approaches infinity, the efficiency approaches

$$\frac{\sum_{\alpha_{i}\tau_{i}}^{n}}{\sum_{\alpha_{i}\tau_{j}}^{n}} < 1.$$

Having gone through how parallel or pipeline processing helps to impove throughput, one can immediately suggest an incorporation of both techniques in a design, just to receive the best out of the two kinds of systems. With this objective in mind, this thesis endeavors to explore such a possible parallel-pipelined mode of processing. In particular, the investigation will be generalized to the study of parallel processing paths (pipes) sharing strategic resources wherever appropriate. Three aspects will be emphasized: throughput, availability and flexibility (reconfigurability). Demonstrations of such a mixed mode of processing in some existing computer systems will also be included wherever possible.

Before proceeding to the individual topics, the problems associated with the design and operational decisions of a parallel pipelined system will be reviewed. First of all, in order to fully utilize the overlapping power in a parallel or pipelined system, the system should have available a continuous stream of independent tasks (instructions) to be executed in an overlapped mode. This poses the first problem, namely, parallelism detection. Parallelism exists in many levels and in many forms. Sometimes, a programmer can explicitly indicate where parallel tasks or instructions exist, exploiting special language features or primitives designed for this

purpose. A huge amount of effort has been spent in the study of such primitives which result in the implementation of some useful ones in some existing array processors or general multiprocessor systems. TRANQUIL, IVTRAN for ILLIAC IV, PARTRAN for PEPE, APPLE for STARAN are some examples [15,16,17,18]. Some example primitives are: while, do; For, do; Fork, Join, etc. With these primitives, the system can recognize immediately where instructions or tasks are parallel processable or pipelinable.

But to avoid the additional responsibility on programmers, implicit parallelism in programs can also be detected. In order that two sequential statements or tasks are parallel processable, their "input-set" and "output-set" have to be compared to check for any precedence constraint. [19] includes a proposed set of conditions for parallel processability and also proved formally that complete deterministic detection of parallelism is an undecidable problem. The reasoning is based on the same argument as the determination of proper program behavior and termination which are well known undecidable problems.

Hence complete parallelism detection is undecidable. But most often, partial detection is very hard to define. In other words, how much parallelism should be detected is a sensitive but important question, which unfortunately is often overlooked. In many situations, excessive parallelism being detected brings more disadvantages than advantages. The reason is quite simple. In detecting more parallelism, more parallel tasks will be 'created' and monitored. This incurs a dynamic control overhead which appears in every run. Such overhead can offset the gain in throughput by promoting overlapped

-1

operation. Besides, if the system resources are insufficient to process all parallel tasks in parallel (or in a pipelined fashion), their existence or creation as individual entities merely represents waste which otherwise could and should be avoided.

In the light of developing automated tools for detecting parallelism in programs written in a certain high level language, [20] describes a Fortran Parallel Task Recognizer. Such a recognition process actually consists of comparing the operand requirements of adjacent statements to construct a precedence graph whose nodes represent statements and arcs the precedence relationship. There is a large amount of analysis required if the detection mechanism is to be applied to a large program. Thus a suitability criterion for expending this detection cost for individual programs is also proposed in [21]. By so doing, via a simple scanning, the suitability of a program will be decided very quickly.

An alternative but very meaningful approach is to invest the detection cost only to a certain segment of programs most actively involved during execution. This is especially important because in many programs [22] results indicated only 4% of the program is executed for more than half of the time. These portions of the program therefore should be executed as fast as possible for the sake of fast turnaround and highest throughput. Logically, to avoid the exhaustive overhead in implicit detection, the latter is applied to those 'busy' segments of a program. In detecting these busy portions, some simple strategy may be used. For deterministic loops, the number of iterations per entry will be known easily. But for nondeterministic loops, a run time monitoring system may be inserted

at chosen locations so that the desirable frequency estimates are obtainable. Then from the collected statistics, an estimate of the traffic intensity of program segments will be available for the application of the parallelism detection algorithm. For the purpose of path frequency counting, the algorithm in Section 5.2 is also adaptable for implementation. The parallelism detection problem can be tackled by many ad hoc approaches, since theoretically, it is an exhaustive process in nature and practical implementation seems to be the only meaningful effort in this area. For this reason, this thesis will not try to tackle this problem and will concentrate on other aspects of parallel pipeline systems.

A second problem is the memory organization and processor interconnection. Interleaved memory is a popular choice in many multiprocessor or pipelined systems [23]. By interleaving, memory bandwidth increases, and with the aid of sufficient buses, the memoryprocessor system has a satisfactory coupling that results in good utilization of the entire system. In many cases of parallel and pipeline processing, local memory buffer units are of special interest. For example, in ILLIAC IV, PEPE, array processors, individual processing elements or control units have dedicated memory modules so that during execution, the least amount of interaction between any two instruction streams or processing phases will occur. In pipelined system, memory buffers for pre-fetching and arrangement of operations are used to increase the effective memory bandwidth needed to keep a pipe busy, as in the CPU of the TIASC system, the memory buffer units (MBU) serve this purpose [24]. These are practical methods to relieve the unpredicted bottlenecks of a

multiprocessor system that in many ways still resembles the highly sequential nonoverlapped Von Neuman computer organization.

In this thesis, the parallel pipeline system will be named a <a href="Reconfigurable Shared Resource Pipeline">Reconfigurable Shared Resource Pipeline</a> (RSRP) system. In particular, several areas of interest will be discussed and investigated.

- (1) Modeling of RSRP System

- (2) Sequencing Strategy

- (3) Sequencing Control

- (4) Performance Monitoring

- (5) Dynamic Reconfiguration

- (6) Restructurable Architecture and a Proposed Design

- (7) System Partitioning

- (8) Resource Decomposition

- (9) Reliability and Availability Enhancement

As a brief introduction to these topics, an outline description of each will be provided in the following.

deterministic and nondeterministic. The term deterministic refers to the fact that the facility speeds are known and fixed, whereas the term nondeterministic refers to the variable speeds of facilities for different tasks to be processed. For all studies in the consideration of throughput, unless otherwise stated explicitly, a deterministic RSRP will be assumed. But for the other areas such as availability, restructuring architecture and reconfiguration, the results are applicable to both types of RSRP systems. Almost all of the analysis in this thesis will be established around this graph representation of a RSRP system.

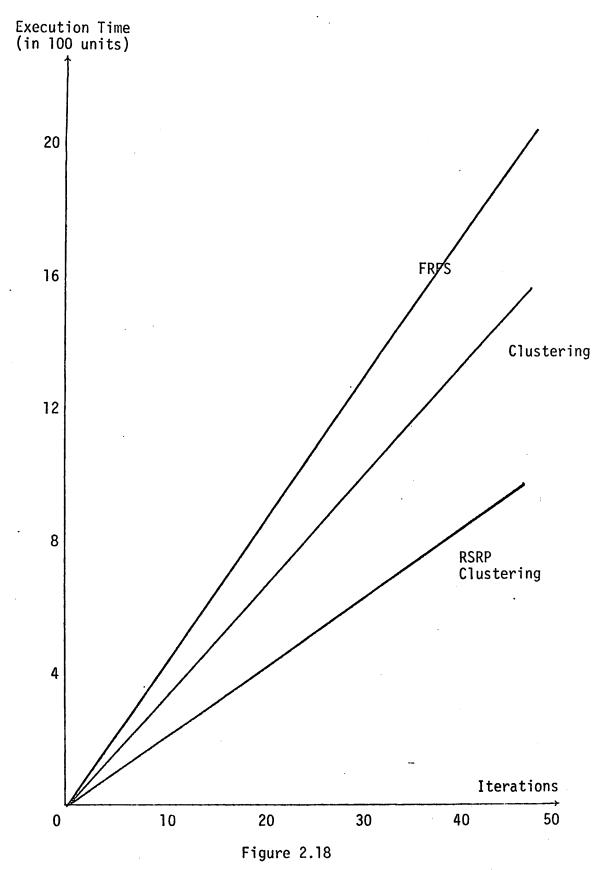

.4

(2) and (3) <u>Sequencing Strategy and Control</u>. Sequencing is the important activity in enhancing the throughput of a system by proper operational control and strategy. Chapter 2 of this thesis is devoted entirely to the scrutiny and derivation of sequencing strategies. First, the intrinsic difficulty of optimal sequencing is explored and characterized. From the characterization, a strong assertion as to the exhaustive nature of optimal sequencing under different control and RSRP systems is revealed. Consequently simple heuristics will also be developed and compared using experimental simulation on some models based on some existing systems. Their implementation schemes and complexity will also be covered.

Implementation of simple sequencing strategies using hardware or firmware is a meaningful approach to upgrade the utilization of system resources, especially for a highly overlapped system design where concurrent processing are allowed and encouraged to a large extent. But often a good strategy is measured not just from the

quality of sequences it develops for different sets of tasks (with the objective of minimal execution time or highest throughput), but also the implementation complexity. This complexity consists of two parts, the static hardware or software overhead for carrying out the strategy. The latter may consist of runtime delay as well as runtime interference to other processes in competing for the needed resources (for example, buses). Thus both aspects of the sequencing strategies will be evaluated in hoping to generate a meaningful study of the problem both from a theoretical point of view and from an engineering point of view. Hopefully, a complete and less biased picture may be obtained.

As a brief introduction to the significance of sequencing to the throughput of a pipelined system, some analytical evaluation may be helpful. Consider a linear deterministic pipeline and suppose

> p<sub>o</sub> = probability that a task (instruction) does not depend on anyone already in the pipe

$p_i$  = probability that task (instruction) depends on the  $i^{th}$  previous instruction still in the pipe, for i = 1,...,L.

Thus

$$\sum_{i=0}^{L} p_i = 1$$

.

$T_i = \text{relative initiation time of the } i^{th} \text{ instruction.}$

For simplicity, let all facilities have the same speed T. Then,

$$T_{i} = T_{i-1} + p_{0}T + p_{1}LT + \sum_{j=2}^{L} p_{j}[\max\{0, T_{i-j} + LT - T_{i-1}\}]$$

.

In the steady state, assume

$$T_{i} - T_{i-1} = T_{j} - T_{j-1} = d$$

(that is, expected delay in initiation between two consecutive tasks is d). Since

$$T_{i-j} - T_{i-1} = T_{i-j} - T_{i-j+1} + T_{i-j+1} - \cdots - T_{i-1}$$

=  $(j-1)d$

$$d = p_0^T + p_1^{LT} + \sum_{j=2}^{L} p_j^{\max\{0,LT-(j-1)d\}}$$

More precisely, there exists an r such that

$$LT - (r-1)d \ge 0$$

but  $LT - rd < 0$ . (1)

Then

$$d = p_0 T + p_1 LT + \sum_{j=2}^{r} p_j [LT - (j-1)d] .$$

(2)

Equations (1) and (2) can be used to solve for  $\, r \,$  and  $\, d \,$  given  $\, p_i, \, L, \, T. \,$  But due to the nonlinear characteristics, a closed form solution is not available and an iterative algorithm for specific values of  $\, p_i, \, L, \, T \,$  has to be used. The index  $\, r \,$  arises because the present instruction may depend only up to  $\, r \,$  previous instructions (on the average) still inside the pipe, instead of a maximum of  $\, L \,$ . This is because a cumulative delay may have resulted in these  $\, r \,$  previous instructions so that when considering the present instruction, the earlier ones (earlier than those  $\, r \,$  instructions) have already left the pipe.

Here, for the purpose of demonstrating the effects of sequencing, equation (2) is worth a second look. By proper sequencing,

for every step, one tries to increase  $p_0$  (no dependency) and other higher  $p_k$  ( $k \ge r$ ) (or depends on instructions that have effectively left the pipe) as much as possible and hence reduces  $p_1, \ldots, p_r$  effectively to reduce the value of d. The strategy to achieve this is often to allow higher priority to ready tasks with a lot of successors and promoting the existence of more ready tasks during execution. The sequencing problem in a more complex RSRP system will be studied thoroughly in Chapter 2.

- (4) <u>Performance Monitoring</u>. In monitoring the performance of difference resources in a RSRP system (possibly in the context of a higher level design), many useful observations can be obtained for reconfiguration or later modification purposes. But first of all, the insertion of monitors to the RSRP system for monitoring the paths or pipes should be minimized so as to reduce the overhead. Again, it should be noted that monitoring in general may incur both static and dynamic overheads. In Section 5.2, a methodology for generating this minimal cost set of monitors will be developed for the purpose of the restructuring control also studied in Chapter 5. The strategy is amenable to other applications even in the monitoring of program behaviors and to reduce unnecessary parallelism detection overhead as discussed previously.

- (5) and (6) <u>Dynamic Reconfiguration and Restructurable</u>

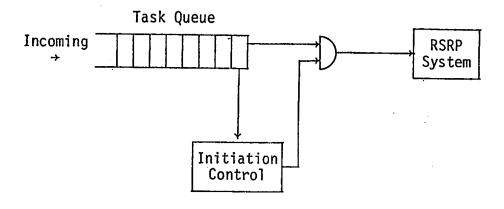

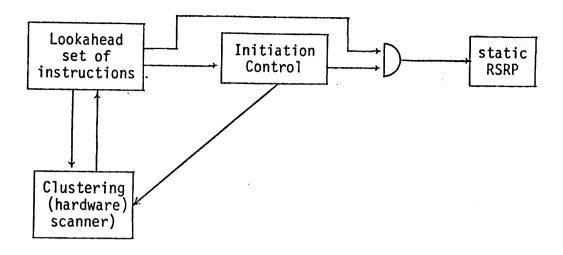

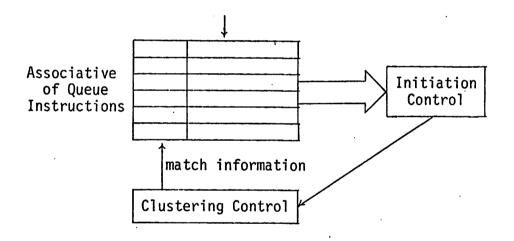

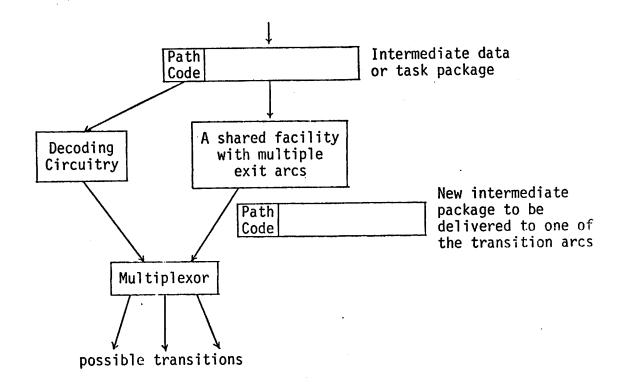

<u>Architecture</u>. Static and dynamic RSRP systems require different kinds of operational control for reconfiguration. In the static RSRP system, only one active path (pipe) may exist at any time instant. So the pipe configuration and operand routing are

relatively simpler. In dynamic RSRP systems, the concurrent processing in parallel pipes sharing resources demands more sophisticated control and routing methods which will be explored. The reconfiguration mechanism will be examined from an engineering viewpoint.

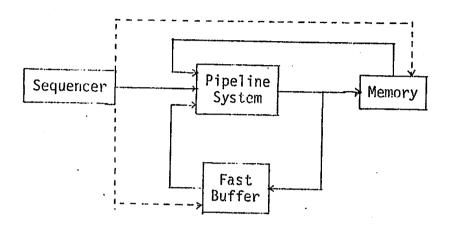

بن

Then a restructurable architecture related to RSRP systems will be proposed and studied. Restructuring may occur due to component failure or need to enhance throughput. Both directions will be sought in Chapter 5 which also includes a hypothetical design of a completely restructurable asynchronous design. The purpose of the design is to promote as much overlapped processing as possible by asynchronous execution and to enhance the graceful degradation ability of the system. It is completely restructurable because pipe configurations are dynamically specifiable. It can be foreseen that such a general purpose architecture is easily adaptable to some special purpose systems such as test-control systems, processcontrol systems, etc. and may be of great impact to future generation of systems where larger pieces of processing facilities such as microprocessors will be widely used throughout the system to perform specially dedicated functions.

(7) <u>System Partitioning</u>. System partitioning is a well-known term in system designs and appears in many levels as well. The original interest of this problem here is to study the impact of "de-coupling". A RSRP system is said to be tightly-coupled if its graph model is a connected graph. To remove the magnitude of the coupling or interference effects at shared resources as well as to reduce control complexity of the RSRP system, sometimes a designer

may partition it into two or more disconnected parts (subgraphs), perhaps having duplicated some resources. Thus the system partitioning problem arises. The philosophy that lies behind the study is that the local control of a set of subsystems (for example, pipes) has a complexity that is a large function of the size of subsystems (number of pipes). Hence by de-coupling and partitioning effectively the control complexity and throughput may be improved simultaneously. In a lower level of application, system partitioning also appears in the actual fabrication of the system using LSI technology and the distribution of chips on PC boards with the objective of minimizing the cross coupling or wiring between the boards, as well as for testing, diagnostic and repair purposes. In all of these applications, algorithmic approaches to solve the problem will be the subject of Sections 3.1 to 3.4.

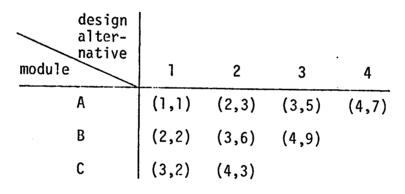

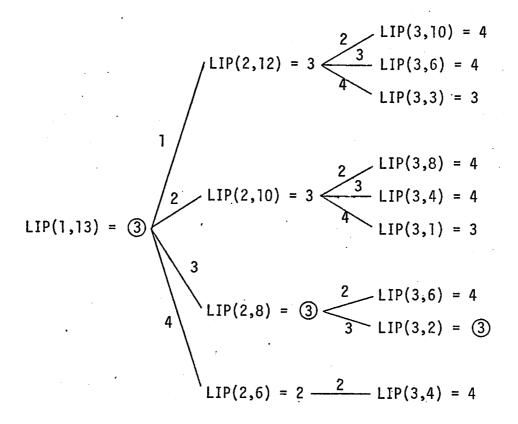

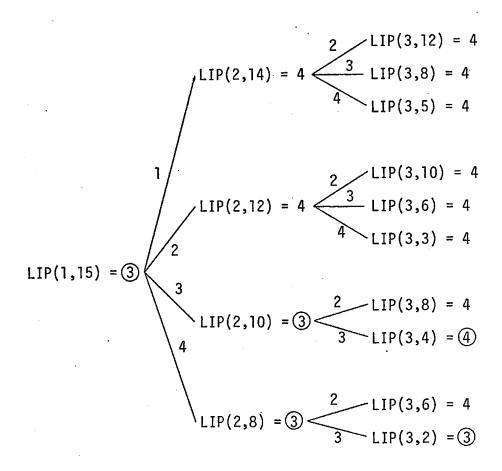

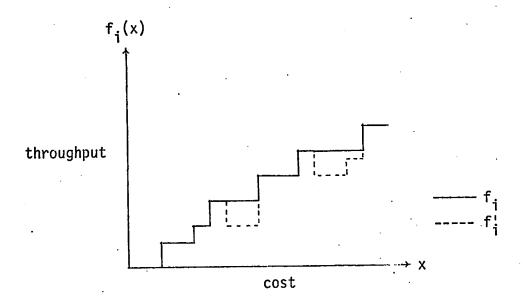

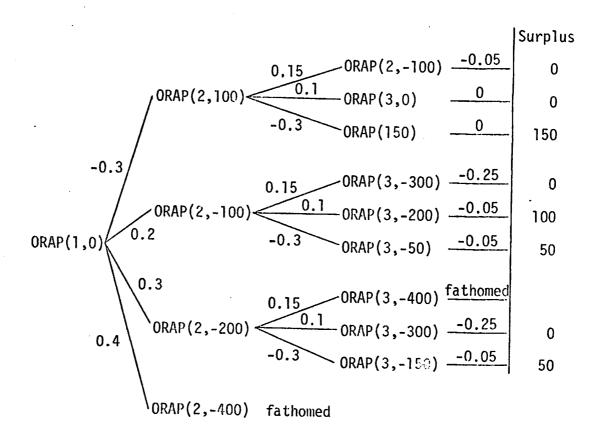

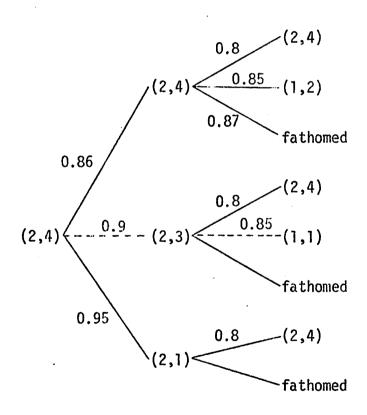

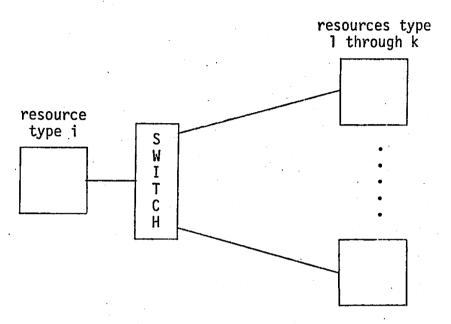

(8) Resource Decomposition. For a deterministic RSRP system, the ideal throughput rate is readily computable. To obtain a most cost-effective design given a budget constraint has always been an interesting topic. To begin with, there are many different techniques (such as parallel or pipeline processing) as well as many implementation schemes for each functional process. In considering the throughput rate of a complicated RSRP system from a global viewpoint, it results in the optimal choice of techniques and implementation schemes for each functional process. An obvious but exhaustive approach is always available to solve this problem, but to avoid exhaustive enumeration, a simple and algorithmic method is proposed in Sections 3.5 to 3.6. Dominance criteria will be set up to

eliminate unnecessary searches (enumerations) at the earliest possible time during the development of an ultimate design.

څ

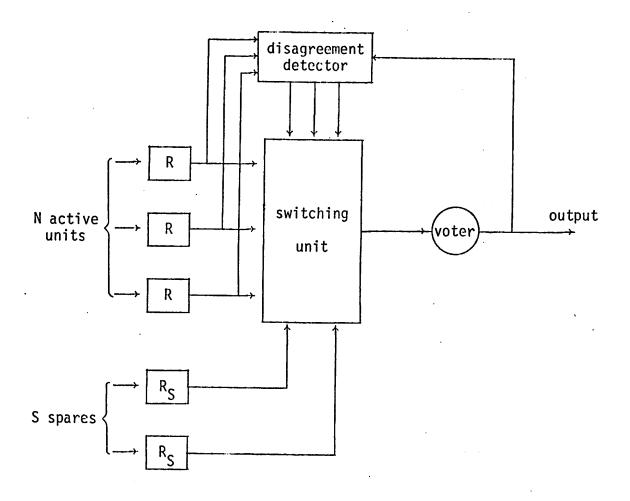

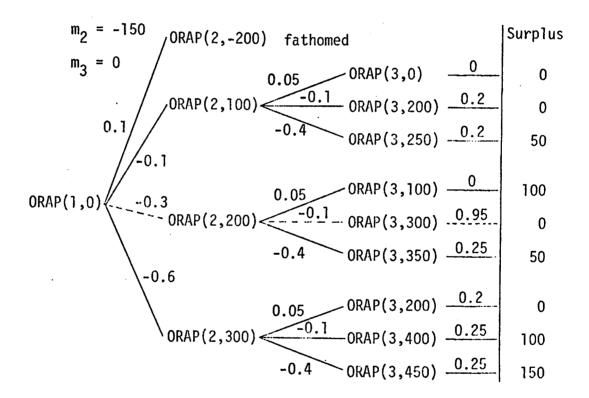

(9) Reliability and Availability Enhancement. A RSRP system consists of many parallel functional pipes. When some components malfunction, the system may still be able to satisfy all specified operations or functions it has to perform. The notion of graceful degradation flourishes. With graceful degradation power, a system can 'switch off' faulty components and reconfigure itself if necessary in order to maintain a specified set of services. Being a flexible and powerful design, an RSRP system is liable to this useful graceful degradation, and the natural question is how to improve its availability (which means effective throughput in the long run). An analytical approach will be adopted to tackle this problem in Chapter 4. Different redundancy techniques will be reviewed and an algorithmic approach to assign redundancy to functional modules in order to maximize the 'availability' via graceful degradation given a budget constraint will be formulated. The approximateness of the optimal solution and the mathematical rigor of the approach will be examined. These efforts regarding the system design hopefully will form a basis for designers to evaluate initial designs or conjectures in a more analytical manner.

#### CHAPTER 2

# Sequencing and Dynamic Reconfiguration In Reconfigurable Shared Resource Pipeline Systems

# 2.1 <u>Scheduling and Sequencing Problems in General</u>

In a multiprocessor system (including both parallel and pipeline systems), concurrency of execution on independent tasks is the major vehicle to increase the throughput of the system and decrease the computational time needed for some privileged programs. The maximization of overlapping is especially important in real-time applications and for lengthy computations, such as those involving experimental data reduction (for example, weather forecasting) where the conclusion or result is needed sooner than can be generated by a uniprocessor system. How best to expoit such a multiprocessor system to satisfy the application requirement or to maximize its utilization hinges upon the effectiveness of scheduling or sequencing the tasks to be executed by the system.

Throughout this thesis, unless stated otherwise, the term <u>task</u> is used to refer to a part of a program which once initiated can be executed to completion without pending on new data to be generated somewhere else in the processing system. In the lowest level, a task could be just a single instruction executable by a processing element. In a very high level, a task could be part or all of a subroutine or procedure. Then scheduling is the activity of properly ordering the tasks to be executed by the system so as to meet certain objectives, such as minimal computation time for some programs or maximal throughput from the system. Usually <u>scheduling</u> is used to describe this activity when the processors are identical and each

task is executable by any one of these processors. When a chain of processing facilities in a pipeline configuration is concerned, then 'sequencing' is often used to represent the above activity -- now a task is sequenced through a chain of pipeline modules. Though the two terms can be used inchangeably (by some authors), it is the intention of this thesis to follow the slight distinction.

٠

In this section, some previous work in the area of scheduling and sequencing will be reviewed. Most of the discussion will be devoted to a deterministic model adopted by many authors. In this model, the task systems to be scheduled or sequenced are assumed known in advance and they are simultaneously available for scheduling. Also, the execution time of each task on each processing facility is specified. It could be a rough estimate, a maximum execution time or a mixture of both. There are some basic limitations to this deterministic model, but it does have some validity when applied carefully. For example, the execution time estimates may be obtained using some past performance statistics. One noteworthy point is that even though erroneous estimates may sometimes occur, an erroneous, non-optimal list schedule does not cause any invalidity in the course of actual computation, provided the tasks are initiated according to the schedule with proper synchronization. In particular, tasks are initiated only if the precedence relationships among them are not violated. A centralized task table containing this precedence information may be used in this respect as implemented in the experimental decentralized operating system for a parallel processing system in [25]. Also, results in the deterministic model can be used to draw appropriate conclusions regarding a more realistic

adaptive or semi-stochastic model where the execution time and precedence relationships are not fixed permanently [26].

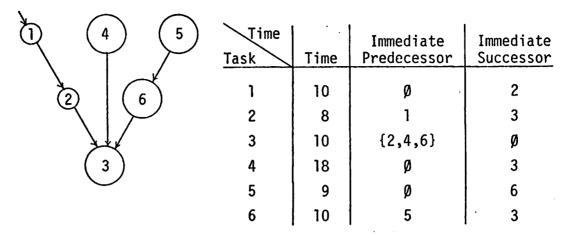

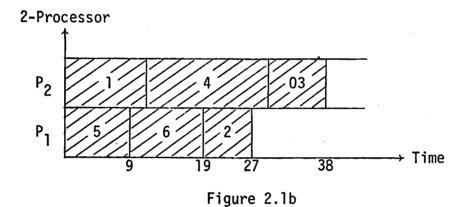

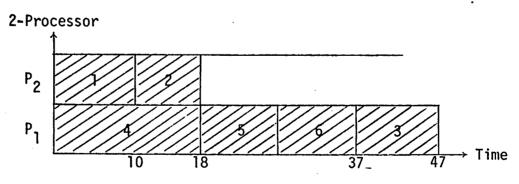

The usefulness and objectives of scheduling are best demonstrated with some examples. Consider the scheduling of related tasks in a parallel processing system first. Figure 2.1 tabulates the relationship among a 6-task system whose execution times are known a priori. The task system is executed on a 2-processor system. The gantt chart for the optimal schedule is shown in Figure 2.1b and the gantt chart for a non-optimal schedule is shown in Figure 2.1c. It is readily observable that optimally the task system can be completed within 38 units of time as compared to the inferior schedule which will require 47 units of time. Hence proper scheduling here can reduce the execution time of the whole task system by 24%.

With the objective of minimization of the computational time of a task system, numerous endeavors were made to find optimal scheduling algorithms [27,30,31,32,33,34,35]. The optimal algorithms should be able to derive an optimal schedule for the task system under specified conditions in a very efficient manner. Their qualities are judged mainly by their average speed, and sometimes, their worst case performance. Since 'average speed' is hard to define and compare both qualitatively and quantitatively in this case, the latter figure of merit is adopted by many people. For instance, essentially enumerative methods are considered poorer than systematic simple procedures which take a 'well-bounded' number of iterations and steps before its termination even in the worst situation.

Here a brief review of the successful attempts will be included

Ž,

Figure 2.1a

Task Table

Gantt Chart for Optimal Schedule

Figure 2.1c

Gantt Chart for Non-optimal Schedule

(the complexity of the general problem will dealt with in Section 2.4). Basically two special cases were studied and simple optimal algorithms were discovered.

### (1) Tree-type Precedence Graph, Uniform Execution Time

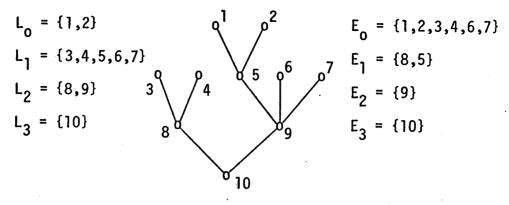

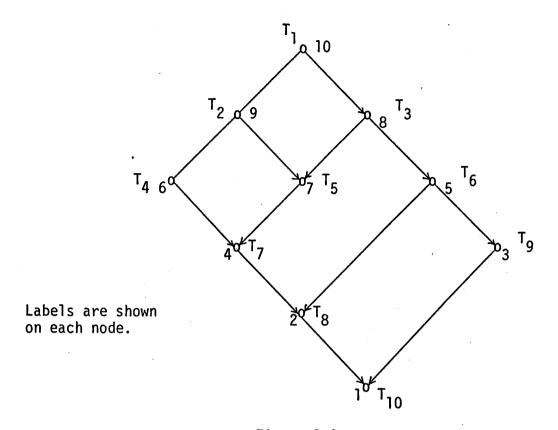

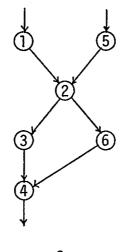

In [27], a very simple and appealing algorithm for deriving optimal schedules for a tree-type of task system with unit execution time for each task is proposed. A tree-typed precedence task system can be as depicted in Figure 2.2. It is characterized by the fact that either all of the tasks each has exactly one successor (except the set of terminal tasks) or all of the tasks each has exactly one predecessor (except one task, the entry root).

Before proceeding, some terminology has to be mentioned. Given a precedence graph, it can be partitioned into earliest partitions  $E_i$  such that  $E_0$  is the set which can be executed first (no predecessor), and  $E_1$  is the set that can follow after part or all of  $E_0$  is completed. Inductively therefore  $E_i$  is the set which has predecessors in the set  $E_{i-1}$ . In a unit execution time task system,  $E_i$ 's really represent the earliest times for executing that set of tasks without violating precedence requirements. In an analogous way, the set of latest partitions  $L_j$  can be defined.  $L_j$  will represent the set of tasks which have successors in  $L_{j+1}$ . For the tree in Figure 2.2,

$$E_0 = \{1,2,3,4,6,7\}$$

$E_1 = \{8,5\}$

$E_2 = \{9\}$   $E_3 = \{10\}$

and

خ

Figure 2.2

An Example Tree-Type Precedence Graph

Figure 2.3

Gantt Chart for an Optimal Schedule

J

$$L_0 = \{1,2\}$$

$L_1 = \{3,4,5,6,7\}$

$L_2 = \{8,9\}$   $L_3 = \{10\}$

The procedure to derive these earliest or latest partitions of a graph is very simple and can be found in [92].

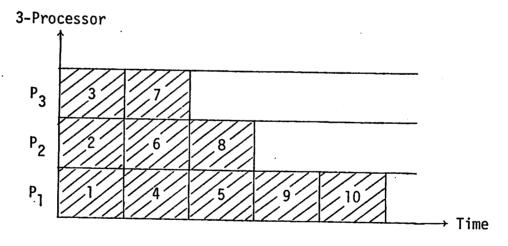

The appealing property of a unit execution time precedence tree is the fact mentioned in the beginning: all of the tasks (except the root or terminal nodes) have exactly one successor (predecessor). Consequently, if they are scheduled according to their membership in the latest partitions which describe their urgency, the result will be optimal. The uniform execution time requirement helps to guarantee optimality since it does not pay to keep a processor idle to wait for some future task. For the example, in a 3-processor system, the gantt chart representing the optimal schedule is shown in Figure 2.3. To derive this schedule, whenever a processor is available, the task at the lowest latest precedence partition whose predecessors are completed will be assigned the processor. If more than one task satisfies this condition, it will be chosen randomly among them.

Unfortunately, in practice, many programs do not exhibit this nice property, and even if some do, their task execution times may not be the same. However, the above method still works fairly well as near-optimal heuristics as discovered in [28,29].

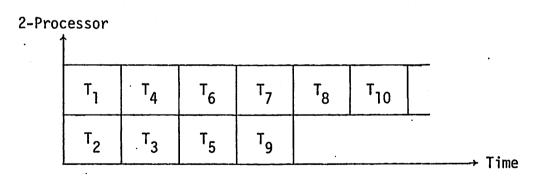

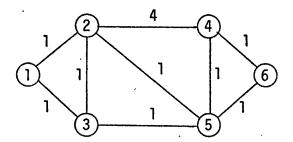

## (2) <u>2-processor System, Unit Execution Time Task System</u>

[30] introduces an optimal algorithm for scheduling a unit execution time task system on a 2-processor system. It is comparatively more complicated than the previous algorithm and consists of

a bottom-up labeling procedure of the graph, taking into account the significant implications of a latest partition characterization. Very briefly, the procedure may be summarized as follows. First label tasks in the highest latest partition (last) with 1,2,.... At each stage afterwards, for those tasks whose immediate successors are labeled, compare their values lexicographically in descending order. Label the one whose successor labels are smallest lexicographically with k. Increment k by 1 and repeat the procedure until the entire graph is labeled. Then at run time, the ready tasks are assigned according to descending order of labels as illustrated in the example in Figure 2.4. Some attempts have been made to generalize this approach to n-processor systems or unequal execution time task systems but no success has been reached. In fact, the intrinsic complexity of this general problem will be discussed in Section 2.4.

ج

Except for these two special cases, in a nonpre-emptive deterministic model, no other success has been known up to now. There were other attempts in deriving efficient scheduling algorithms (but not well-bounded in complexity) using partial enumeration, branch and bound or dynamic programming (where the number of state variables is huge) techniques as reported in [31,32]. In general, dominance criteria may be used to speed up the partial enumeration procedure. For practical situations, efficient heuristics are more useful. A likely acceptable candidate is the method using the latest partition characterization. It is noteworthy that optimal scheduling of independent tasks is still among those without a fast algorithm, although they exhibit total freedom as regards to

Figure 2.4

An Example Graph for 2-processor Scheduling

Gantt Chart for Optimal Schedule

precedence relationship.

A different scheduling situation arises when a task can be preempted by another during processing. Under an idealistic assumption, then optimal pre-emptive scheduling of independent tasks may be achieved, because the scheduler only has to split long tasks into subtasks and fill up all of the processors. However, this is not very realistic especially when preemption introduces overhead which is not considered in the model.

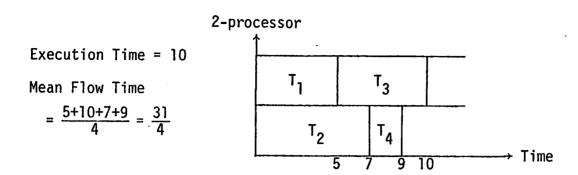

Under the same deterministic model, another possible scheduling objective has been investigated [33,34]. Sometimes, instead of minimization of the execution time of task system, it is more advantageous to minimize the average response time, the so-called mean flow time. Figure 2.5 represents a situation where minimal execution time does not necessarily yield minimum mean flow time. However, this aspect of scheduling will be out of the scope of this chapter.

Sometimes, the deterministic model may be insufficient because the execution time of a task varies from one run to another. But, it has been reported in many simulation experiments, the effectiveness of some scheduling method is not very sensitive to small changes in the execution time [29]. Yet for analytical evaluation, a stochastic or adaptive model may be used in some cases. Then optimal scheduling based on a stochastic model is difficult to grasp unless some nice distribution (such as memoryless) is assumed for the task execution times. In [35], a preemptive scheduling is proposed assuming the task execution times obey exponential distributions. Even so, the dynamic programming formulation requires

Minimum Execution Time Schedule

Execution Time = 12

Mean Flow Time

$$= \frac{5+12+2+7}{4} = \frac{26}{4}$$

$$T_1$$

$$T_2$$

$$T_4$$

$$T_3$$

Minimum Mean Flow Time Schedule

Figure 2.5

n state variables (n = number of tasks) and therefore resembles the similar formulation for the traveling salesman problem which is known to be complicated. For the nonpreemptive case, it is not possible to derive or define strictly optimal schedules for the stochastic model; rather, comparisons have to be performed based on simulation or queueing models over a long run situation [36,37].

چ.

These previous worksand experiences indicate that even though sufficient simplicity has been assumed in the scheduling model, in the large majority of situations, no efficient optimal algorithms are implementable. When more realistic parameters are included, an optimal schedule may turn out to be nonoptimal. Observe that the task system has been assumed to be available for scheduling and the transitions in a program are known a priori. Also operating system overheads are ignored throughout so that implementation details of any scheduling technique are left out of the model. An attempt to include such runtime overhead into a scheduling model has been reported in [38], but simple and successful results are yet to emerge in future research. Meanwhile, the analytic modeling and evaluation of scheduling disciplines still suffer a lot of handicap and the validity of the derived optimality remains questionable.

Having discussed so much about scheduling of tasks on parallel processors, let us come back to sequencing on pipeline machines.

Sequencing may be viewed as a more complicated activity because now not only the tasks have precedence relationship but also the system possesses certain pipeline configuration(s) for processing. Multiple pipeline systems (the pipes may be heterogeneous) can be treated as parallel processors as well so that a pipe is regarded as a

\$

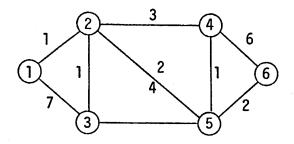

processor. In some cases, the execution of a task on a facility (pipeline segment) is variable. Adopting the same deterministic model of a task system, [39] proposed a simple optimal algorithm for processing independent tasks to be executed on a 2-facility pipeline. The method is very simple as illustrated in Figure 2.6. First the two columns of execution time requirements are scanned. The smallest entry is detected. If it appears in the first column, the corresponding task is placed after the first part of the partial schedule generated. If not, the task is placed ahead of the second part of the partial schedule. The corresponding row is removed and the process repeated until all tasks are scheduled. Finally the two parts are joined together as shown in Figure 2.6.

Apart from this simple result, other attempts to produce simple optimal sequencing algorithms are rather fruitless. In [40], the many facets of pipeline systems characterized by flow-shop and job-shop problems are studied. A flow-shop problem involves tasks executed by the pipeline facilities arranged in a fixed sequence, whereas a job-shop problem relaxes the constraint on the fixed ordering by which all tasks will traverse the facilities. Many ingenous efforts [41,42] were devoted to produce improved sequencing algorithms using techniques such as branch and bound or longest path where non-enumerative termination is not guaranteed. But because of their enormous implementation overhead and the weakness of a deterministic model, they may not be very suitable for a computer system. Together with the experience encountered in a parallel processor system, it seems simple effective heuristics are more desirable and realistic. One problem arises: how can the

| Exec.<br>Time |            |            |

|---------------|------------|------------|

| Task          | Facility 1 | Facility 2 |

| 1             | 2          | 7          |

| 2             | 6          | 2          |

| 3             | 3          | ①          |

| 4             | 4          | 3          |

| 5             | 5          | 7          |

|               |            |            |

Task Table

|                     |          | Result    | Intermediate Table               |  |  |  |

|---------------------|----------|-----------|----------------------------------|--|--|--|

| •                   | eration: | 3         | 1 ② 7<br>2 6 2<br>4 4 3<br>5 5 7 |  |  |  |

| 2 <sup>nd</sup> Ite | eration: | 1 2 3     | 2 6 ②<br>4 4 3<br>5 5 7          |  |  |  |

| 3 <sup>rd</sup> Ite | eration: | 1 4 2 3   | 4 4 ③<br>5 5 7                   |  |  |  |

| 4 <sup>th</sup> Ite | ration:  | 1 5 4 2 3 | 5 5 7                            |  |  |  |

Figure 2.6

Illustration of Johnson's Algorithm

heuristics be compared? Analytical comparison may be derived using either the deterministic or adaptive model [43,44] but such comparisons mostly can only deal with worst case situations. As mentioned earlier, average performance is hard to characterize with reasonable validity. So in this chapter, our evaluation of the sequencing heuristics will be based primarily on simulation for a long run behavior where more parameters and wider spectra of applications may be included.

#### 2,2 Modeling

The processing phase within a computer system can be described by many possible models, based on the objective of modeling. For some purposes, a very detailed modeling is necessary. But for others, a simplified model helps the analysis and reveals the most critical characteristics of the actual system. In most cases, system modeling revolves around a graph representation. Sometimes, additional semantics of tokens provide the additional information desirable. Because of the space and time structure of a processing system, the exact operation and synchronization of an asynchronous modular system are well illustrated using Petri-Nets or marked graphs [45,46,47].

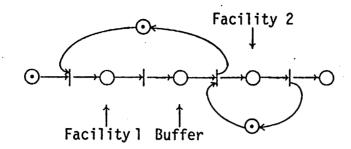

Very briefly, a typical Petri-net may be characterized as having three types of constituents. First there is a set of transitions where actual events take place. They may represent the processing modules in the system. Then there is a set of places which are responsible for holding some condition information such as status or control words. Finally there is a set of directed

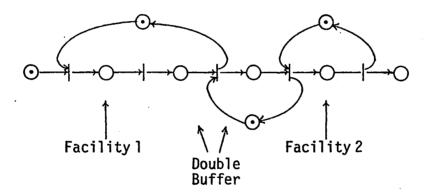

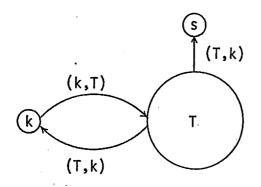

arcs liking input places to transitions and transitions to output places. Places are used to hold tokens which mark the presence of certain conditions. A place without a token is empty and denoted  $\bigcirc$ , and if it is full, it is denoted by  $\bigcirc$ . An event may occur if all of its input places are full so that the corresponding transition is fired. After firing (corresponding to the processing operation of the facility or module concerned), a token is removed from each input place and a token added to each output place. A ·simple Petri-net representation of a two-facility pipeline with or without buffer can be as shown in Figure 2.7. For specific purposes, such a Petri-net representation may be modified to cope with the application. For instance, a transition can fire under some logical condition such as exclusive OR instead of when all input places are full (analogous to multiplexing in systems). Liekwise, queues may be included in the model to hold tokens in places to fully describe the capability of the system.

Hence, very detailed modeling may be derived using some form of Petri-net. Such modeling is useful for performing some analysis on the correctness and synchronization property of a processing system [48], because the exact control and data flow are represented explicitly in the model.

But much of the information extractable from a detailed Petrinet representation is redundant when optimization aspects in both the design and operation of a processing system where the correctness and synchronization problems are assumed to be solved or handled by other means. Rather, only those features pertinent to the optimization aspects need be considered. Under the scope of this thesis,

Petri-net Model for Single Buffered 2-facility Pipeline

Petri-net Model for Double Buffered 2-facility Pipeline

Figure 2.7

where sequencing and resource allocation are the main problem areas, a graph model simpler than the Petri-net seems sufficient. Both the throughput and the cost-effectiveness of the system are readily computable analytically from a simple graph model as suggested in the following.

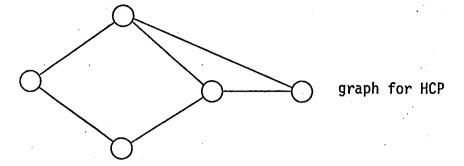

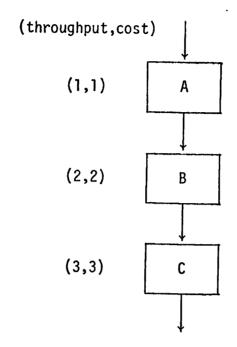

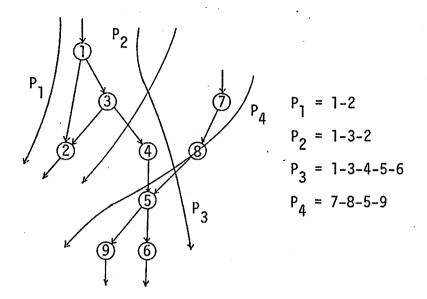

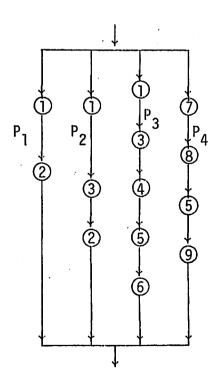

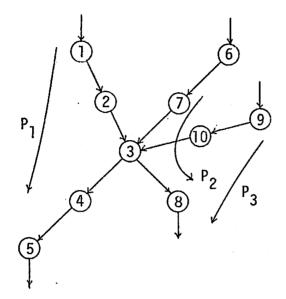

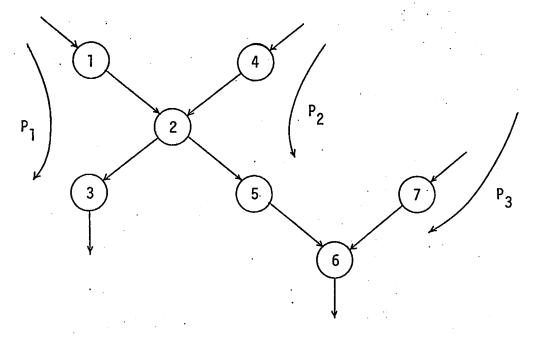

For the purpose of this thesis, we are concerned with the throughput and cost-effectiveness of the design of a complex system which has a structure describable by the various functional paths (pipes) within the system, sometimes with some strategic resources being shared among the functional paths. Under this processing organization, both parallel and pipelining characteristics are noticeable. Pipelining is recognized because a functional path is composed of a sequence of modules each performing some phase of processing in an overlapped mode with the others. So the speed of processing is faster than that of a non-pipelined path. Simultaneously parallel processing may be achieved because concurrency of execution may take place among the various functional paths (pipes), quite analogous to the Multiple Instruction Multiple Data (MIMD) stream type of computer systems [3]. As a result, independent instruction or task streams are guided through the different required functional paths in a pipelined manner with the objective of getting the most utilization from the system resources and hence the highest throughput rate possible.

It is to this type of mixed mode processing that this thesis endeavors to address; and for obvious reasons such a processing system will be named Reconfigurable Shared Resource Pipeline (RSRP) system. Apparently it is actually a pipeline system consisting of

ď

one to several multifunctional pipelines each of which possesses different configurations or path structures for performing different types of operations or functions. Examples of RSRP systems can be recognized from some existing multifunctional pipelines in computer systems including the CDC STAR-100 and TI-ASC [49,50]. In the example of TI-ASC system, the arithmetic unit has fourteen groups of instructions. Groups 1 to 11 are synthesized such that instructions from the same group can follow one another without delay in the arithmetic unit. As an example, most of the load, store and logical instructions can be grouped together because their arithmetic processing requires the same configuration in the arithmetic unit pipe. Hence in the ideal case, where the operands are pre-fetched fast enough, the arithmetic unit can produce a fastest throughput rate of one output per minor cycle. On the other hand, groups 12 to 13 contain instructions that require additional waiting or latency so that a smaller throughput rate is attainable. Finally group 14 includes instructions that do not require any processing within the arithmetic unit.

There are actually two types of RSRP systems which will be considered here -- static and dynamic RSRP systems. A static RSRP system is less flexible and less intelligent in the sense that at any time instant, only one configuration or functional pipe may be active. Therefore pure pipeline characteristics exist, though over a time period different pipes may be excited. This design has the advantage of less control circuitry and overhead needed in monitoring the routing of operands and gating activities in the pipeline segments. It has also the disadvantage of less overlapping in the

other inactive paths and hence reducing the opportunity to achieve maximum throughput. The examples in TI-ASC and STAR-100 mentioned previously fall into this category [51,52]. On the other hand, a dynamic RSRP system permits concurrent processing in the various functional paths (pipes) with some additional control to route operands to correct transitions. Then, simultaneously several functional pipes may be active, although collisions at a shared resource have to be either avoided or resolved by proper buffering and sequencing control. There are certainly some tradeoffs between a static and dynamic RSRP system. These will become more apparent later.

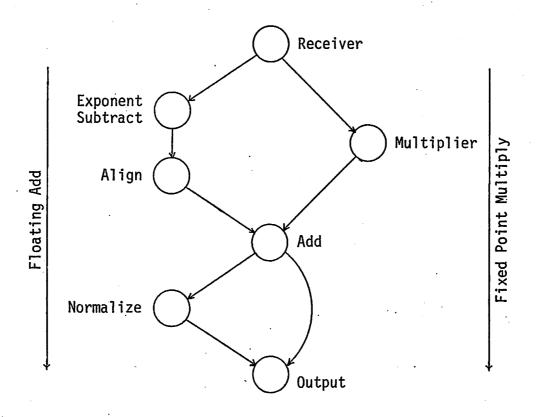

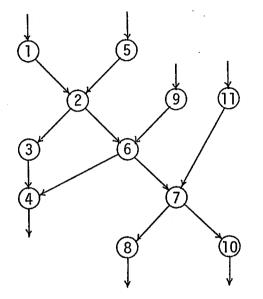

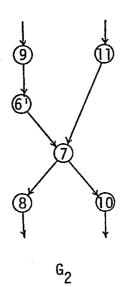

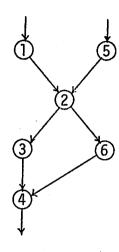

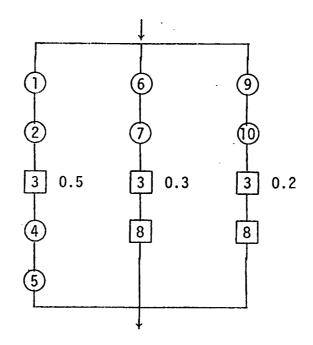

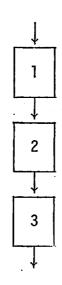

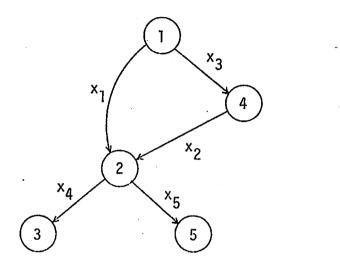

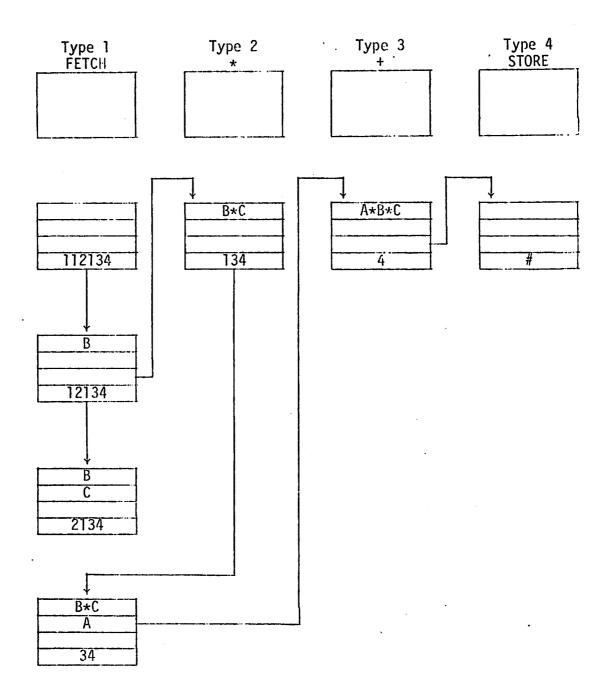

Hence, formally a RSRP system can be represented by a modified digraph consisting of a three-tuple G = (N,A,P) where N denotes the set of facility modules or nodes, A the set of transition arcs among the nodes, and P the set of legal functional paths (pipes) in the system. Sometimes when used in a deterministic model, it can be extended to a quadruple G = (N,A,P,T) where T provides the additional information about the execution speeds of the facilities in N such that the execution time, throughput rate, etc. of the functional pipes under no interference condition are computable. A simple graph representation of the configurations of the arithmetic unit in TI-ASC for carrying our floating point addition and fixed point multiplication can be as drawn in Figure 2.8. Since all segments of the facilities have the same speed (synchronized by the same clock), the vector T can be omitted here. Using this model, the throughput rate and reliability of the system as a function of cost associated with different designs can be evaluated

# TIASC ARITHMETIC UNIT

Figure 2.8

, i

Ŧ

with little trouble as we will see in later chapters. Observe that not all possible paths in the digraph are legal paths because there may exist configurations that do not have logical meaning and hence their activation will introduce erroneous outputs.

### 2.3 Collision Avoidance

Given a RSRP system, some deterministic analysis will be useful for controlling the operation of the system for optimization purposes under different operating conditions. Because of the presence of shared resources and multiple tasks currently being executed in a dynamic RSRP system, care must be taken to accommodate the occurrence of collisions. A collision occurs when two or more tasks try to access the same facility at the same time. When a collision has occurred, the system control must have built-in (hardware or software) collision resolvers and/or buffers of some kind in order that proper execution can continue at its normal pace.

Similar to other undesirable events, collisions can be either prevented or resolved. If prevention is the goal adopted, some global sequence controller may be designed so that a task (instruction), once initiated, will not cause any collision with other tasks still inside the pipeline system. This further implies that a task will flow through the pipeline system without waiting inside after its admission. This goal has the advantage that no explicit requirement on intermediate buffer storage between facilities is imposed. The disadvantage is that it may lose the flexibility to enhance more overlapped operations provided by sufficient buffering. Also this scheme is safe only for a completely deterministic system.

હ

An almost exactly analogous situation between a dynamic RSRP system and a traffic network in this respect can be drawn up easily. A shared resource corresponds to a junction in a traffic road. Under the deterministic model, the exact speeds of vehicles and the lengths of blocks of roads are assumed known and fixed. Also it is assumed that there are distinct entrance points to the traffic network if necessary. The junction of a road represents a facility which may be controlled by a traffic signal as in the case of a clock pulse. Cars may be admitted under a global controller which will allow entrance at some pre-determined sequence of the synchronization signals. On the other hand, internal buffering may be used to avoid collision at a junction in a similar way as the use of traffic signals. Of course, excessive traffic congestion on one route will result in the overload of 'buffers' -- an expected phenomenon of an ill-balanced RSRP system. Sometimes, remedy may be sought by dynamically changing the periodic ratio of traffic signals for the junctions concerned so that the heavily loaded direction is favored to relieve the unbalance -- similar to a dynamic priority assignment to shared resources among the different related processing paths.

So there are many similarity aspects of a general dynamic RSRP system and a traffic network. For our immediate discussion, we will try to tackle specifically the collision avoidance technique in a dynamic RSRP system. This is especially important when pipelining is implemented at a very low level (in order to achieve the ultimate speed) such as ordinary LSI chip level. Under this level of consideration, the speed of a facility node may be of the order of 10 nsec

and therefore intermediate buffering demands comparatively large static and dynamic overhead. The cost of intermediate buffer will be almost the same as other component costs and the total delay of the pipeline may be doubled. Hence except for simple operand routing, additional buffering between facilities may be undesirable when pipelining is performed in a lower level, for instance, in the arithmetic unit of TI-ASC or STAR-100.

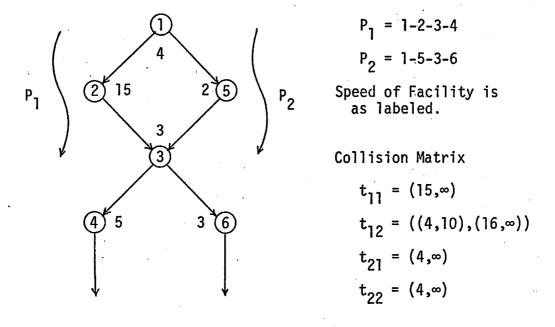

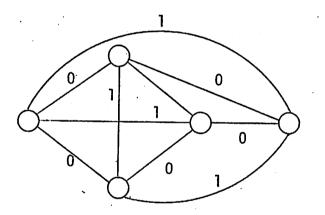

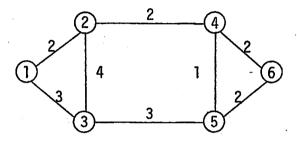

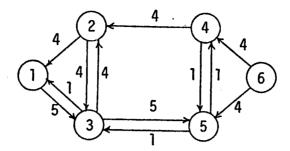

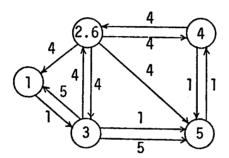

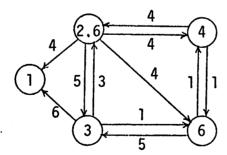

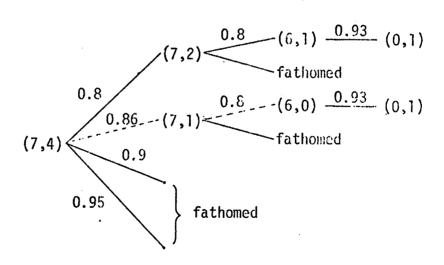

When sufficient buffering is absent, collision inside the pipeline system has to be avoided by the global control mechanism. In [53], a reservation table approach is suggested for sequence control of a linear pipe with a single configuration. From a static reservation table, the initiation procedure (of a certain periodic length) is chosen such that higher throughput rate is attainable for complete collision avoidance. The idea behind a reservation table can be depicted by the example in Figure 2.9. For a multifunctional pipeline system, a similar approach utilizing a two-dimensional collision matrix is proposed here [14]. As the name implies, a collision matrix is a generalization of a one dimensional collision vector characterizing a unifunctional pipeline.

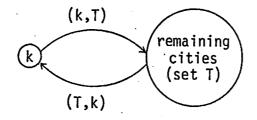

Each entry in the collision matrix contains information regarding the collision relationship between the two pipes concerned. Specifically, the  $(i,j)^{th}$  entry represents the time intervals after the initiation of pipe i so that the excitation of pipe j will not cause collision inside. For example,  $\{(2,6),(10,17),(20,\infty)\}$  in the  $(i,j)^{th}$  entry means the excitation of pipe j after pipe i can take place between the  $2^{nd}$  and  $6^{th}$  cycles, or  $10^{th}$  and  $17^{th}$  cycles, or after the  $20^{th}$  cycle, so that between the  $7^{th}$  and  $9^{th}$

|                | 1 | 2 | 3  | 4 | 5 | 6 | 7 | 8              | 9 | 10 | → Time                                |

|----------------|---|---|----|---|---|---|---|----------------|---|----|---------------------------------------|

| s <sub>1</sub> | Х |   | •  |   |   |   |   |                |   |    | · · · · · · · · · · · · · · · · · · · |

| s <sub>2</sub> |   | X |    |   |   |   |   |                |   |    |                                       |

| S <sub>3</sub> |   |   | Χ. |   | X |   |   |                |   |    |                                       |

| s <sub>4</sub> |   |   |    | X |   |   |   |                |   |    |                                       |

| S <sub>5</sub> |   |   |    |   |   |   | X | X <sub>.</sub> |   |    |                                       |

| s <sub>6</sub> |   |   |    |   |   |   |   |                | X |    |                                       |

| s <sub>7</sub> |   |   |    |   |   |   |   |                |   | X  |                                       |

X = occupied

Figure 2.9

Reservation Table

cycles or 18<sup>th</sup> and 19<sup>th</sup> cycles, collision will result. Each entry in a collision matrix may contain several time intervals instead of a single one because the two pipes involved may share more than one resource, thus introducing more sites where collision can take place. Of course, multiple shared resources do not necessarily imply a compound entry in the collision matrix. As an example, the RSRP system in Figure 2.10 has a collision matrix as shown. The (1.1) entry is  $(15,\infty)$  indicating that pipe 1 can be excited at regular intervals of 15 cycles or more because the slowest facility in pipe 1 generates an output in every 15 cycles and therefore forms the bottleneck of this pipe. (The term "bottleneck" is often used to describe the slowest facility which places the limitation on the speed of flow of instruction or task stream in much the same way as in physical bottlenecks.) The (1,2) entry is  $\{(4,10),(16,\infty)\}$ because pipe 2 may collide with pipe 1 at facility 1 as well as facility 3. During the (4,10) time interval after pipe 1 has been excited, if pipe 2 is excited, the two instructions or tasks will not collide anywhere inside the pipe. But after the  $10^{th}$  cycle and before the 16<sup>th</sup> cycle concerned, if pipe 2 is excited, a collision will occur in facility 3. So excitation in pipe 2 must be delayed in order to avoid collision, a consequence of the second task catching the first one in the system. Notice that the (2,1) entry is single-valued, despite the fact that pipes 1 and 2 share two resources. This is so because once pipe 2 is excited and the task has left the first collision site, there is no way for the task in pipe 1 to catch up.

4

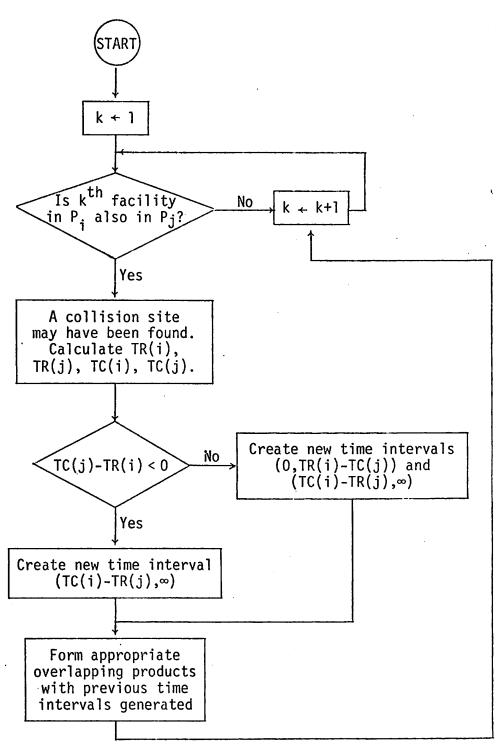

The flow chart of the algorithm which can be used to construct

Figure 2.10

Example Collision Matrix

Figure 2.12

Flow Chart for Constructing Collision Matrix

Notation: TC(i) = time to leave the collision site via pipe i

TR(i) = time to reach the collision site via pipe i

Overlapping product: Illustration - Suppose previous time interval is  $(4,\infty)$  and the newly generated are (0,7) and  $(10,\infty)$ . The resulting intervals will be (4,7),  $(10,\infty)$ .

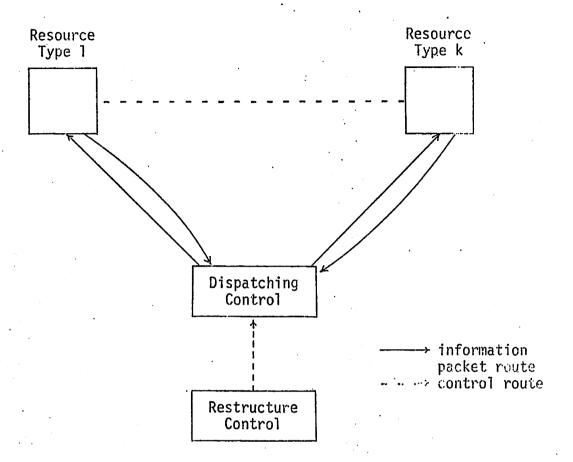

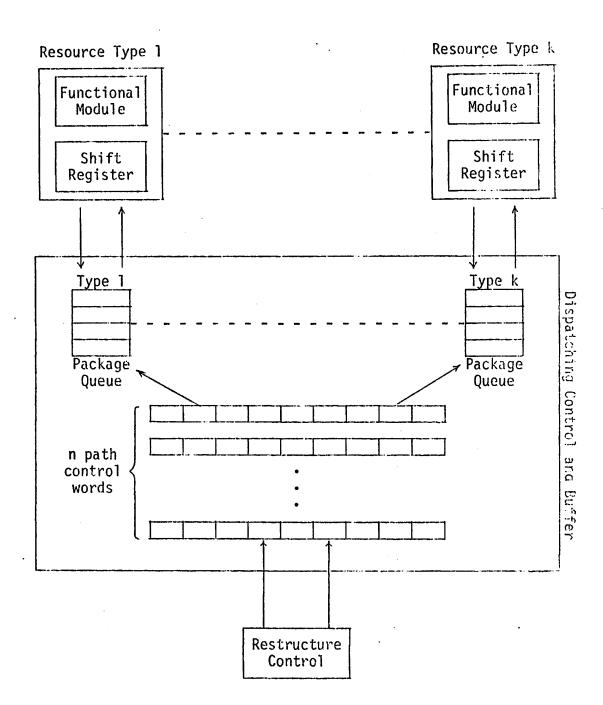

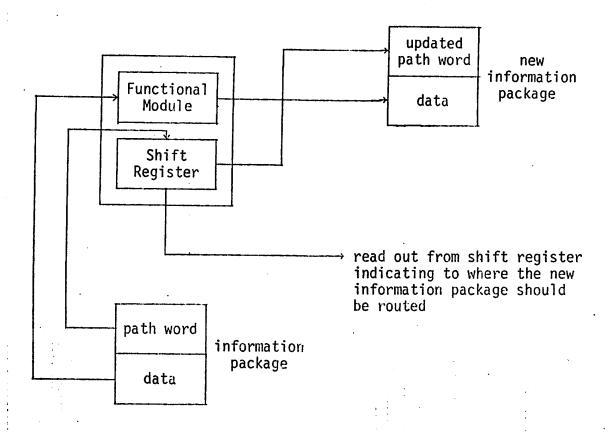

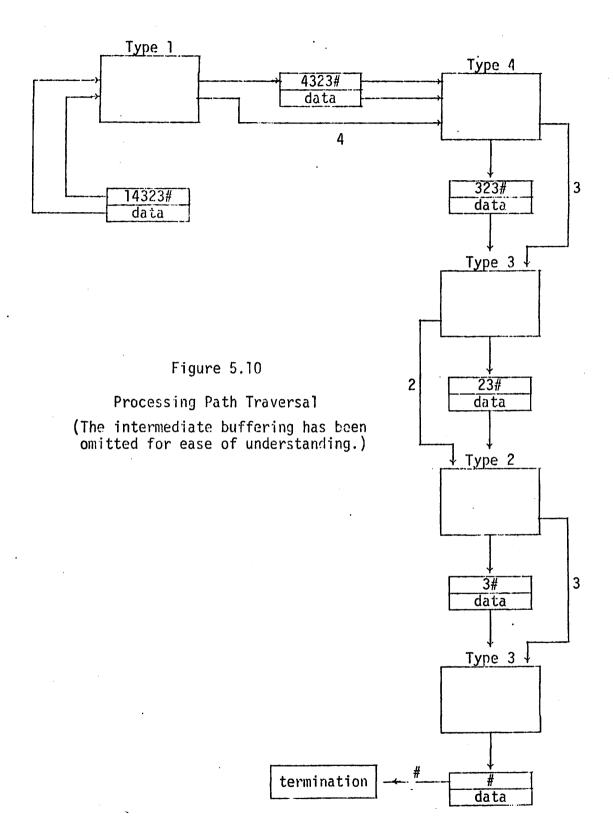

the collision matrix given (N,A,P,T) is illustrated in Figure 2.11 which gives the procedure for deriving the (i,j)<sup>th</sup> entry. For simplicity, if pipe i and pipe j share a sequence of consecutive facilities, the latter are grouped together with a throughput rate corresponding to that of the slowest facility in this group. Also the time to reach and leave the composite facility will correspond to that for the slowest facility.