Copyright © 1985, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. A DESIGN METHODOLOGY FOR VLSI PROCESSORS

-

VOLUME I

by

Joan Marie Pendleton

Memorandum No. UCB/ERL M85/88

21 November 1985

#### A DESIGN METHODOLOGY FOR VLSI PROCESSORS

VOLUME I

by

Joan Marie Pendleton

Memorandum No. UCB/ERL M85/88

21 November 1985

ELECTRONICS RESEARCH LABORATORY

XITIE Stiff

College of Engineering University of California, Berkeley 94720

Research sponsored, in part, by Defense Advance Research Projects Agency (DoD) Contract No. N00039-83-C-0107 and, in part, by a Fellowship from Eastman Kodak Corporation.

## A DESIGN METHODOLOGY FOR VLSI PROCESSORS

#### VOLUME I

bу

Joan Marie Pendleton

Memorandum No. UCB/ERL M85/88

21 November 1985

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

· · · · · ·

.

···· <u>--</u> .--

.

Research sponsored, in part, by Defense Advance Research Projects Agency (DoD) Contract No. N00039-83-C-0107 and, in part, by a Fellowship from Eastman Kodak Corporation.

-

i

## A Design Methodology for VLSI Processors

Joan Marie Pendleton

#### ABSTRACT

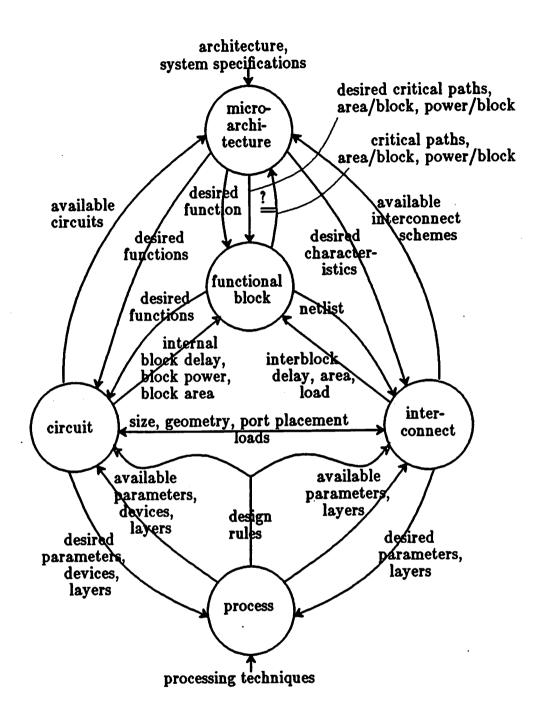

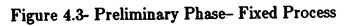

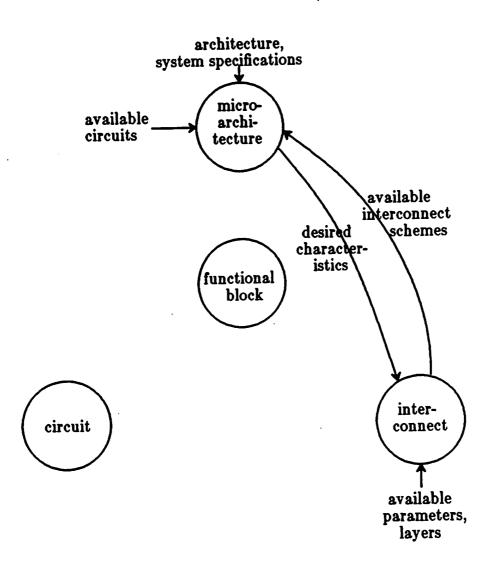

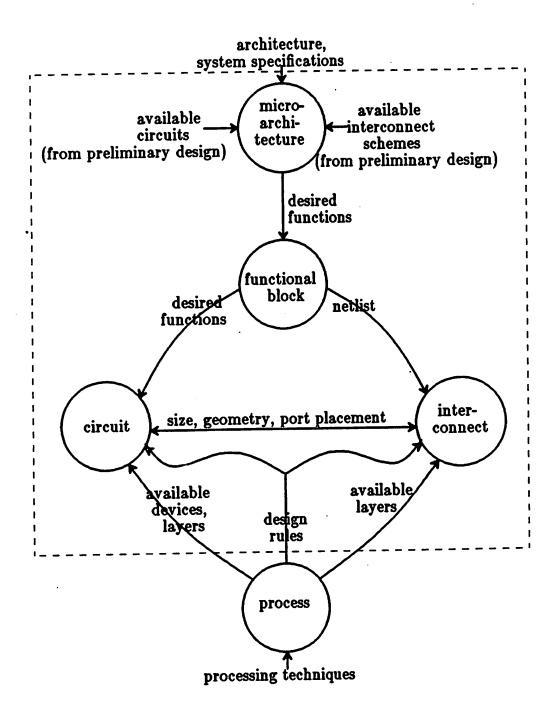

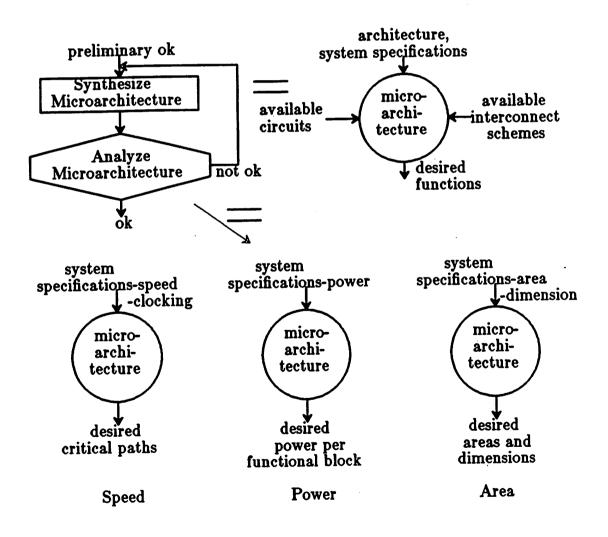

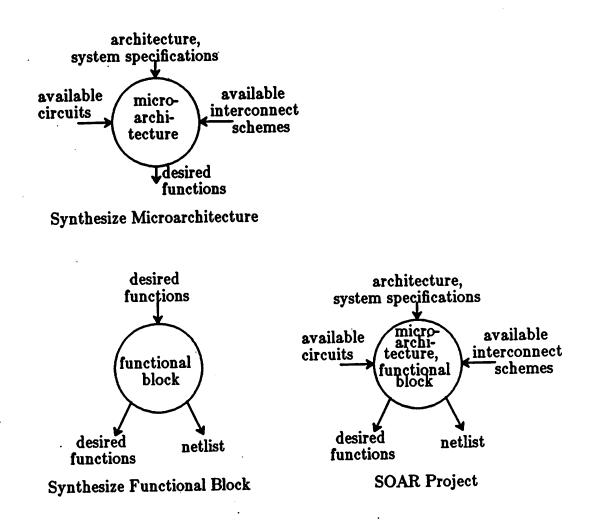

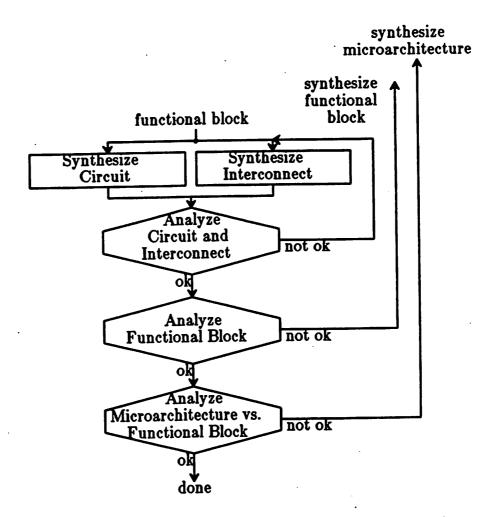

A design methodology for VLSI processors has been developed. It is based on five major design levels – microarchitecture, functional block, circuit, interconnect, and process – and the interactions between them. In addition to top-down synthesis, this method formally incorporates the feedback of information from the lower design levels to the higher levels. A preliminary design phase that considers the effects of the lowest levels – circuit, interconnect, and process – on design at the highest level – microarchitecture – is described. After preliminary design, design alternates between synthesis and analysis steps as the designers proceed from the highest level to the lower levels.

SOAR (Smalltalk on a RISC), a 32 bit microprocessor designed for the efficient execution of compiled Smalltalk provides a case study of this methodology. The chip, implemented in 4 micron, single-level metal NMOS technologies, has a cycle time of 400 ns. Pipelining allows an instruction to start each cycle with the exception of loads and stores. The processor contains 35,700 transistors, is 320x432 mils, dissipates 3 watts, and is assembled in an 84-lead pin grid array package. The methodology that included a large CAD effort provided functioning chips on first silicon.

Dand Gr Hodge

Chairman

# **Table of Contents**

| Preface                                     | 1  |

|---------------------------------------------|----|

|                                             |    |

| Chapter 1- Introduction                     | (  |

| 1. VLSI Issues                              | (  |

| 2. Thesis Organization                      | ٤  |

| Chapter 2- Present Methodologies            | 10 |

| 1. Design Levels                            | 10 |

| 2. Hierarchy                                | 12 |

| 3. Design Levels and Hierarchy              | 14 |

| 4. Mead-Conway Style                        | 18 |

| 5. CMU–DA System                            | 17 |

| 6. Bell Laboratories- Bellmac-32 Techniques | 2  |

| 7. IBM– Philo VLSI Design System            | 23 |

| 8. Summary                                  | 28 |

| 9. References                               | 27 |

| Chapter 3– Design Levels                    | 29 |

| 1. Microarchitecture Level                  | 30 |

| 2. Functional Block Level                   | 34 |

| 3. Circuit Level                            | 37 |

| 4. Interconnect Level                       | 4  |

| 5. Process Level                            | 45 |

| 6. Interrelationship Overview               | 43 |

| 6.1. External Inputs                        | 4  |

| 6.2. Iteration                              | 50 |

| 6.3. Unidirectional Design                  |                |

|---------------------------------------------|----------------|

| 7. Methodology Implications                 |                |

| 8. Summary                                  |                |

| 9. References                               |                |

| Chapter 4– Design Methodology               |                |

| 1. Preliminary                              |                |

| 2. Synthesis                                |                |

| 2.1. Microarchitecture Synthesis            |                |

| 2.2. Functional Block Synthesis             |                |

| 2.3. Circuit Synthesis                      |                |

| 2.4. Interconnect Synthesis                 |                |

| 3. Analysis                                 |                |

| 4. Optimization                             |                |

| 5. Methodology                              |                |

| Chapter 5– External Inputs– SOAR Case Study |                |

| 1. Architecture                             |                |

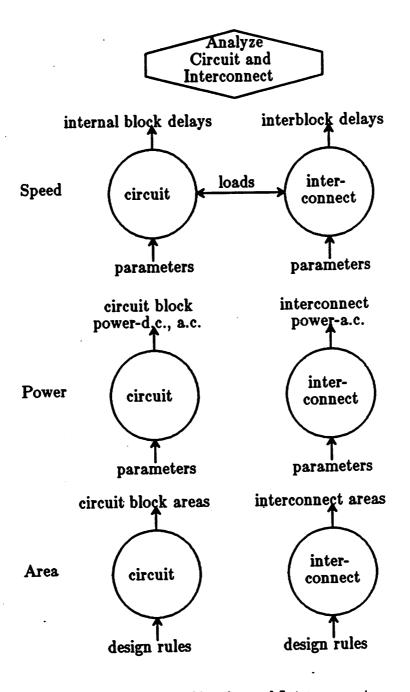

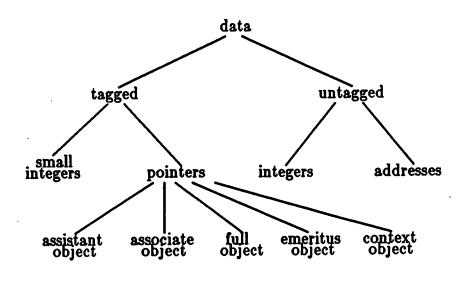

| 1.1. Data Types                             |                |

| 1.2. Word Size                              | <del>_</del> , |

| 1.3. Addressing Modes                       |                |

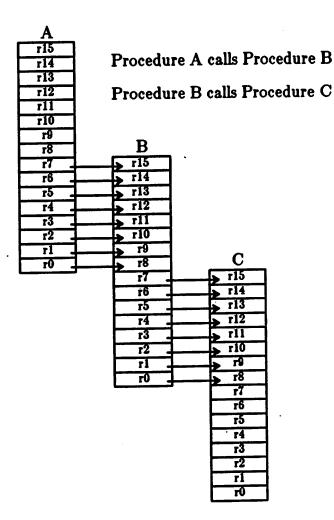

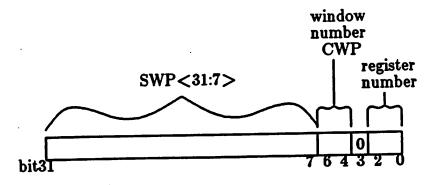

| 1.4. Register Organization                  |                |

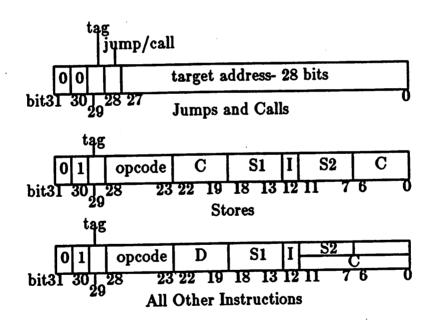

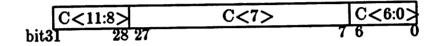

| 1.5. Instruction Set                        |                |

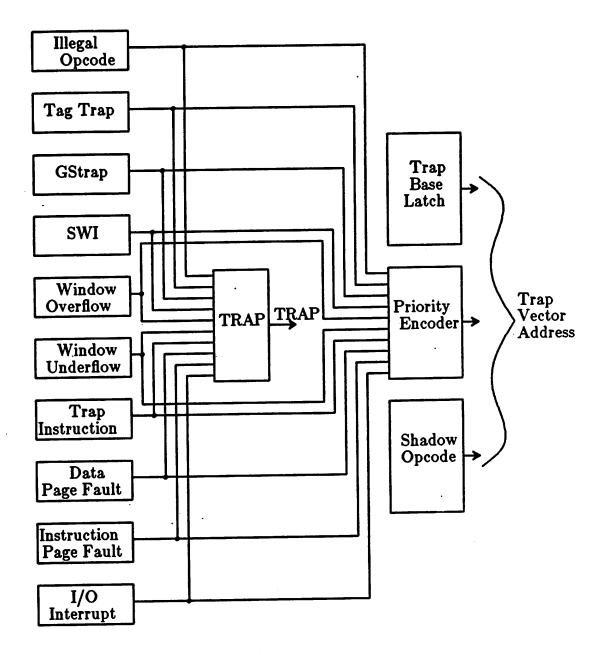

| 1.6. Internal Exceptions and Traps          |                |

| 2. System Specifications                    |                |

| 2.1. Memory Requirements                    |                |

| 2.2. Clocking                               |                |

•

•

•

.

| 2.3. External Interrupts and Wait                 | 121   |

|---------------------------------------------------|-------|

| 2.4. Fast Shuffle Control                         | 121   |

| 2.5. Reset                                        | 123   |

| 2.6. Loading Characteristics                      |       |

| 2.7. Size and Power                               |       |

| 3. Process                                        | , 124 |

| 3.1. Devices and Device Parameters                |       |

| 3.2. Layers and Layer Parameters                  | 128   |

| 3.3. Design Rules                                 | 129   |

| 4. References                                     | 130   |

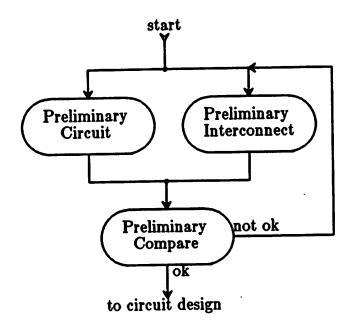

| Chapter 6– Preliminary Design– SOAR Case Study    | 132   |

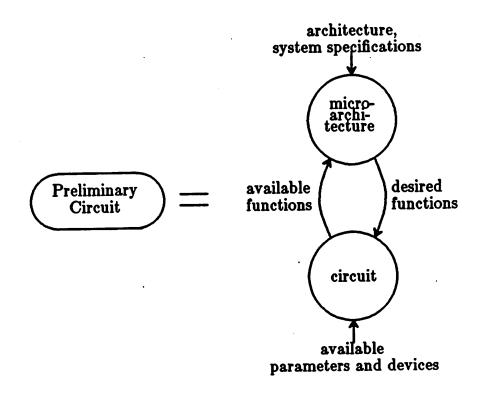

| 1. Preliminary Circuit                            | 135   |

| 1.1. Desired Functions                            |       |

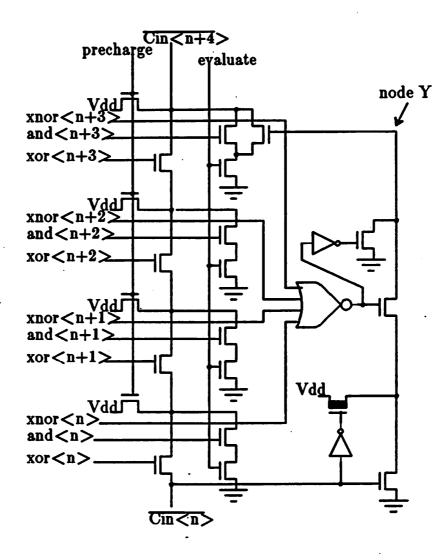

| 1.1.1. ALUs                                       | 135   |

| 1.1.2. Storage                                    |       |

| 1.1.3. Random Logic                               | 138   |

| 1.1.4. Drivers                                    | 139   |

| 1.1.5. Summary                                    |       |

| 1.2. Circuits Available                           | 142   |

| 1.2.1. ALUs                                       | 142   |

| 1.2.2. Storage                                    | 150   |

| 1.2.3. Random Logic                               |       |

| 1.2.4. Drivers                                    |       |

| 1.3. Initial Microarchitecture Design             | 166   |

| 1.4. Further Preliminary Microarchitecture Design |       |

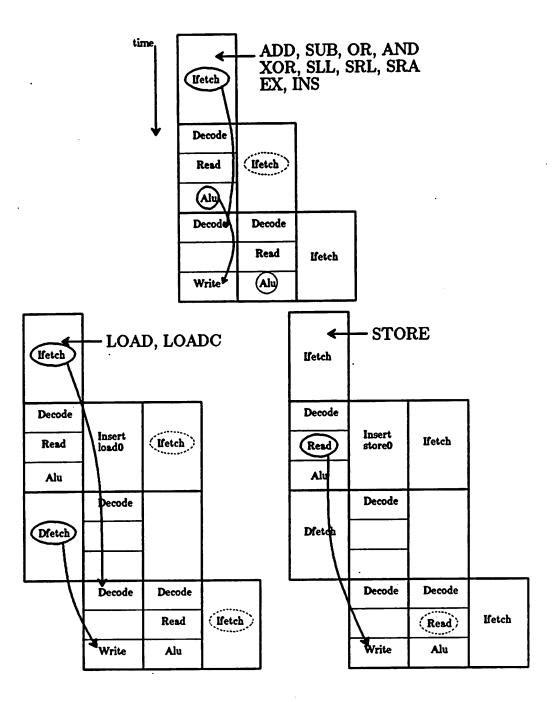

| 1.5. Pipeline                                     | 175   |

- -

•

| 1.6. Resource Allocation                                      | 183 |

|---------------------------------------------------------------|-----|

| 1.7. Pipeline Exceptions                                      | 190 |

| 1.8. Preliminary Circuit Summary                              | 198 |

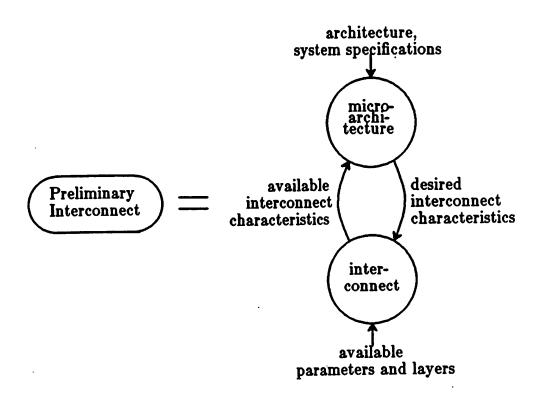

| 2. Preliminary Interconnect                                   | 201 |

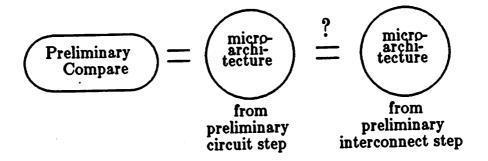

| 3. Preliminary Compare                                        | 204 |

| 4. References                                                 | 204 |

|                                                               |     |

| Chapter 7- Microarchitecture Design-SOAR Case Study           | 206 |

| 1. Microarchitecture Synthesis                                | 207 |

| 1.1. Functional Blocks                                        | 209 |

| 1.2. Bus Structures                                           | 219 |

| 1.3. Resource Usage                                           | 225 |

| 1.4. Complete Functional Block Input and Output Specification | 226 |

| 1.5. Microarchitecture Verification                           | 228 |

| 1.6. Microarchitecture Synthesis Summary                      | 234 |

| 2. Microarchitecture Analysis                                 |     |

| 2.1. Speed Analysis                                           | 235 |

| 2.2. Area and Power Analysis                                  | 240 |

| 3. References                                                 | 241 |

| Chapter 8- Functional Block Design-SOAR Case Study            | 242 |

| 1. Functional Block Synthesis                                 | 244 |

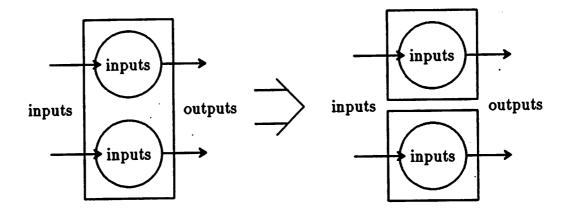

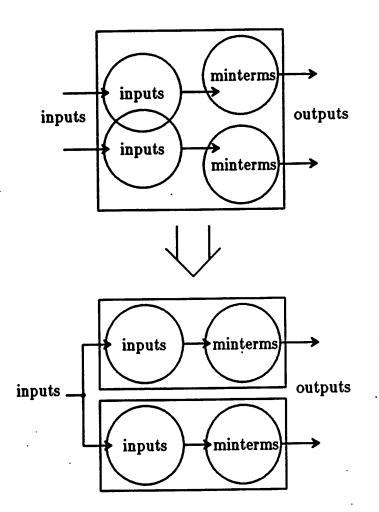

| 1.1. Merging                                                  | 244 |

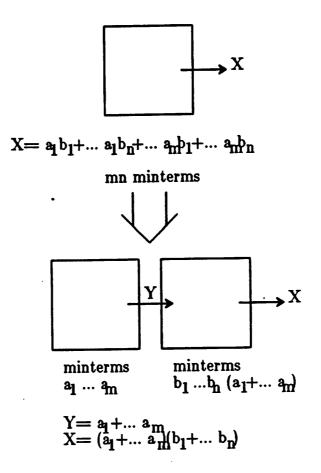

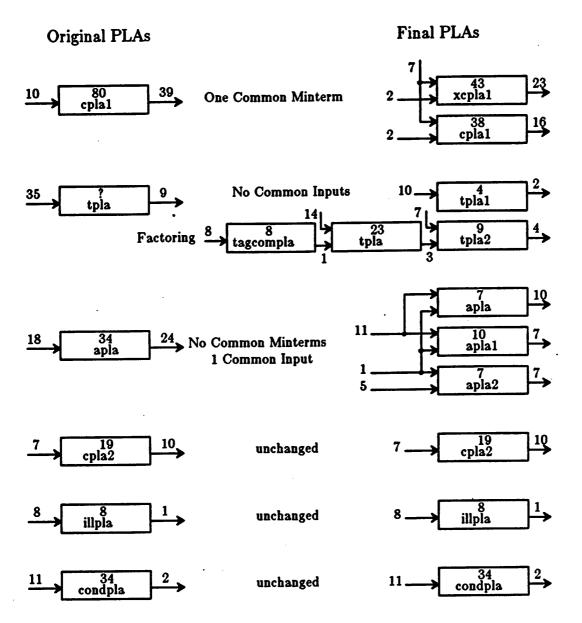

| 1.2. Splitting                                                | 249 |

| 1.3. Summary                                                  | 258 |

| 2. Functional Block Analysis                                  | 265 |

| 2.1. Speed Analysis                                           | 265 |

.

•

.

| 2.1.1. Method              | 266 |

|----------------------------|-----|

| 2.1.2. SOAR Speed Analysis | 273 |

| 2.2. Power Analysis        | 285 |

| Chapter 9- Circuit and Interconnect Design-SOAR Case Study _ | 284 |

|--------------------------------------------------------------|-----|

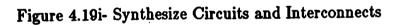

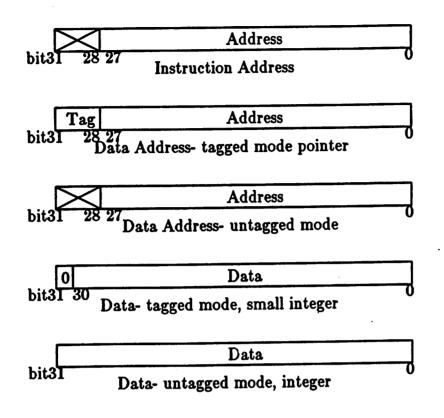

| 1. Circuit and Interconnect Synthesis                        | 285 |

| 2. Circuit and Interconnect Analysis                         | 286 |

| 2.1. ALU                                                     | 288 |

| 2.2. Inserter/Extractor                                      | 297 |

| 2.3. SWP Comparator                                          | 297 |

| 2.4. Register File Decoders                                  | 298 |

| 2.5. Sign Extender                                           | 300 |

| 2.6. Summary                                                 |     |

| 3. Functional Block Analysis                                 | 302 |

| 4. Microarchitecture vs. Functional Block Analysis           | 307 |

| 4.1. Phase 1 Analysis                                        | 307 |

| 4.2. Phase 2 Analysis                                        | 309 |

| 4.3. Phase 3 Analysis                                        | 311 |

| 4.4. TRAP Analysis                                           | 312 |

| 4.5. Decode for Phase 3 Analysis                             | 315 |

| 4.6. Microarchitecture Analysis                              | 317 |

| 5. Optimized Pipeline Analysis                               |     |

| 6. Split Datapath Analysis                                   | 326 |

| 7. References                                                | 328 |

| Chapter 10– Results– SOAR Case Study |   | 528 |

|--------------------------------------|---|-----|

| 1. Methodology                       | • | 330 |

|                                      |   |     |

|                                      |   |     |

•

•

| 2. Processor Results                                | _ 333 |

|-----------------------------------------------------|-------|

| 2.1. Test Setup                                     | _ 336 |

| 2.2. Functionality                                  | _ 339 |

| 2.3. Speed                                          | _ 341 |

| 2.3.1. Phase 1                                      | 342   |

| 2.3.2. Phase 2                                      | _ 343 |

| 2.3.3. Phase 3                                      | _ 344 |

| 2.4. Process Effects                                | _ 346 |

| 2.5. Summary                                        | _ 351 |

| 3. Architecture Results                             | _ 352 |

| 3.1. Overview                                       | _ 353 |

| 3.2. Area and Geometry                              | _ 354 |

| 3.3. Complexity                                     | _ 356 |

| 3.4. Speed                                          | _ 358 |

| 3.5. Summary                                        |       |

| 4. References                                       | _ 361 |

| Appendix A– 4 Micron NMOS Design Rules              | _ 362 |

| Appendix B- SOAR SLANG Description                  | _ 368 |

| Appendix C- Circuit Block Logic Diagrams            | _ 471 |

| Appendix D- SOAR Input/Output Timing Specifications | _ 589 |

.

.

۰.

-

## Acknowledgements

First and foremost I wish to thank Professor David A. Hodges for joining this project and promptly providing whatever support was necessary. Due to his continuous interest the SOAR processor became a reality. I would also like to thank Professor Carlo Sequin for reading this dissertation and his useful suggestions. Thanks also go to Professor David A. Patterson for his involvement with the SOAR project. And of course thanks also go to my third reader, Professor Alan Portis of the physics department.

I would also like to acknowledge all the people who worked on the CAD tools that were used in this project. In particular Bob Mayo, Walter Scott, and Professor John Ousterhout for the MAGIC layout editor and their prompt attention to any problems with it. Also Jim Larus and Grace Mah who made automatic layout a reality and saved much time with their PLA generation tools.

Thanks also go to the MOSIS crew for their special attention to this oversized die, prompt replies to all our questions, and for providing working chips to us. I also wish to thank the processing and packaging people at Xerox for fabbing SOAR for us. And special thanks to Kodak for providing my support while I was at Berkeley.

And thanks go to all the people on the SOAR project that made it a fun project to work on. To name just a few – Will Brown, Frank Dunlap, Shing Kong, Chris Marino, and Dain Samples. And to the people who made Berkeley a fun place to be – Mike Arnold, Ricki Blau, Gordon Hamachi, Paul Hansen, Bob Mayo, Rick McGeer, Dave Wallace, and many others.

Thanks also go to the many people who without realizing it, contributed in a variety of ways. To the people at the boathouse and other rowers, among the many Dede and Brian Birch, and Ron and Velma Owen. To Will Brown, Keith losso, Frank Dunlap, and Tricia Fordham. And to Peter Eichenberger, Dan Jablonski, Jim Moody, and Lynne Pollenz. And special thanks to my sisters and brother – Patti, Ann, and Dave – my cousin – Dix Brown – and my parents – Alta and Alvin Pendleton – for the wild and crazy times, proper (not too serious) perspective on the world, some key suggestions, and many interesting discussions about most anything.

#### Preface

The purpose of this thesis is to present a methodology for VLSI processor design. However, a methodology is only useful if it proves to be well suited for actual problems and leads to valuable decisions when applied to these problems. The Smalltalk On A RISC – SOAR – project at Berkeley was both a guinea pig and motivating factor behind this methodology. The intent of this methodology is to provide guidelines and insights into VLSI processor design for future use, based on experience from microarchitecture design through to layout. Although the test vehicle for this methodology was an NMOS RISC processor, it is hoped that the methodology is general enough to be used with other technologies and architectures also.

The SOAR project developed from the Berkeley Smalltalk system. Due to its basic nature, Smalltalk proves to be relatively slow on general purpose computers [Unga85]. Therefore, the idea of building a system with special purpose hardware for Smalltalk was proposed. This led to architectural studies of Smalltalk during the fall of 1982 and winter of 1983 [Patt83]. Among other things, the architecture of a special purpose Smalltalk processor was specified by these studies.

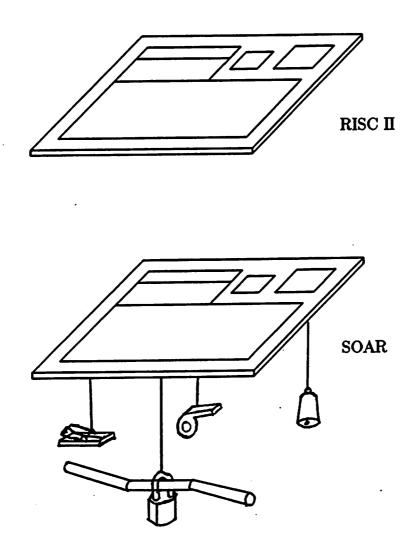

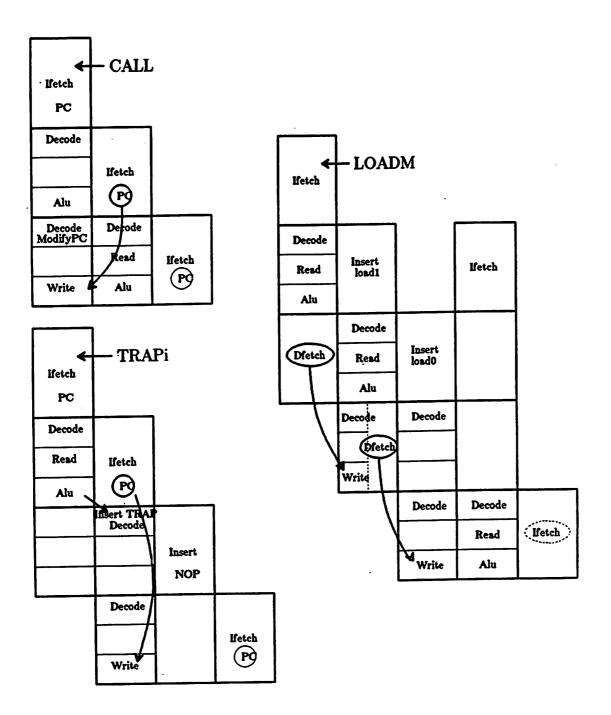

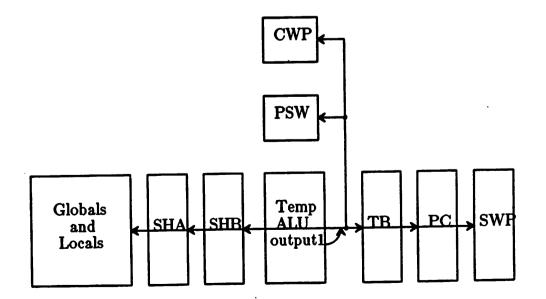

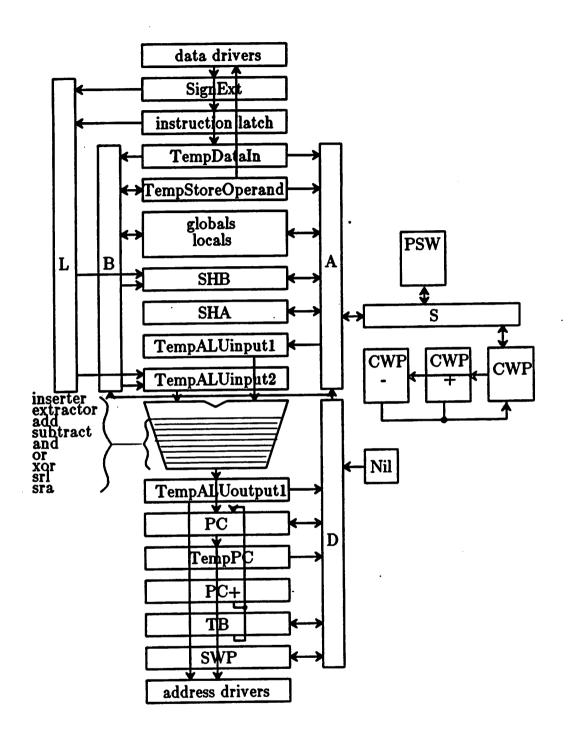

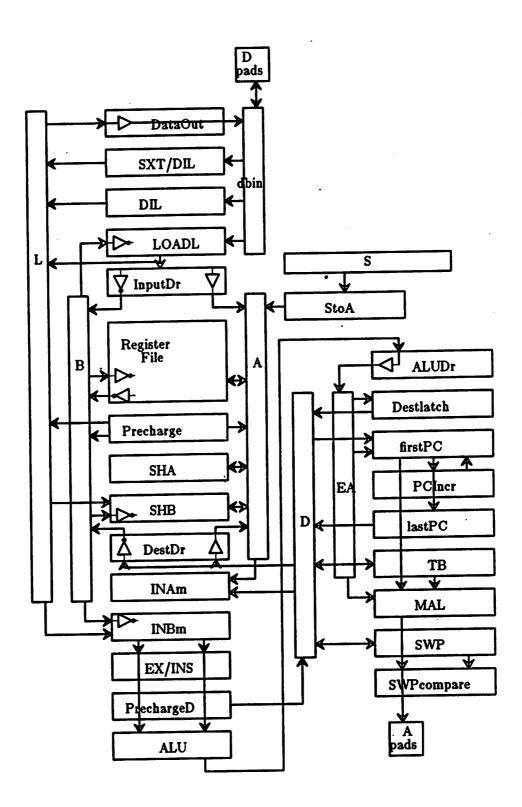

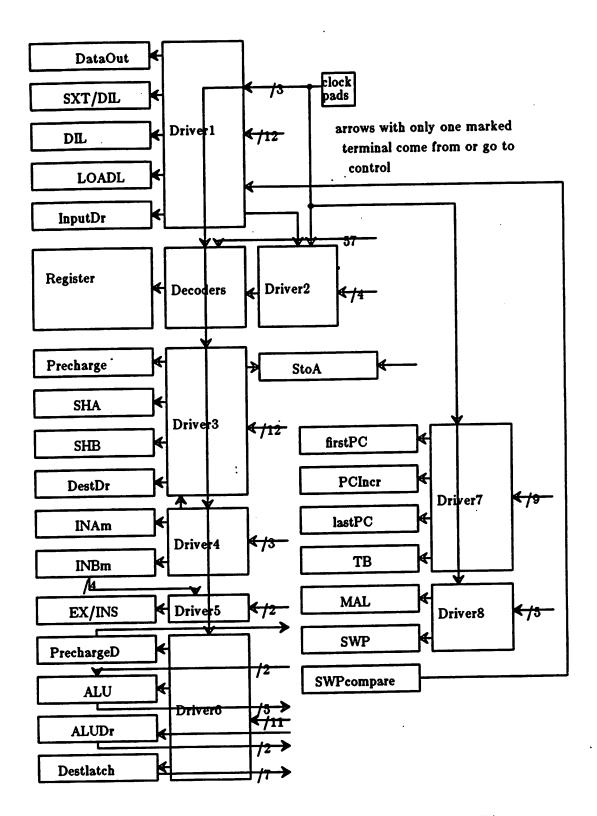

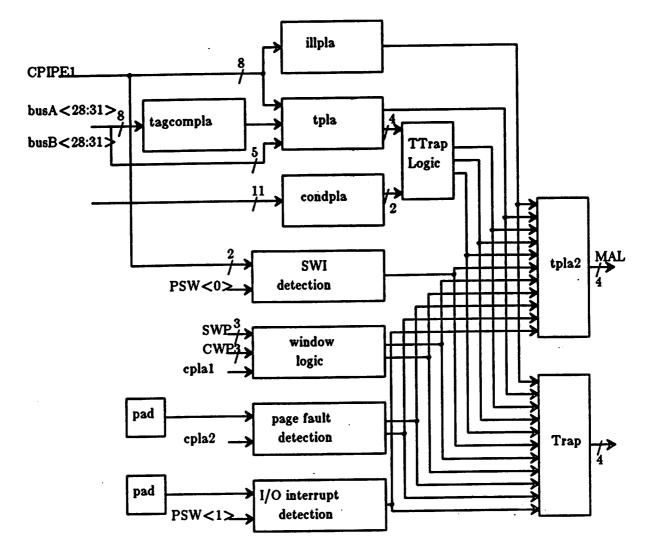

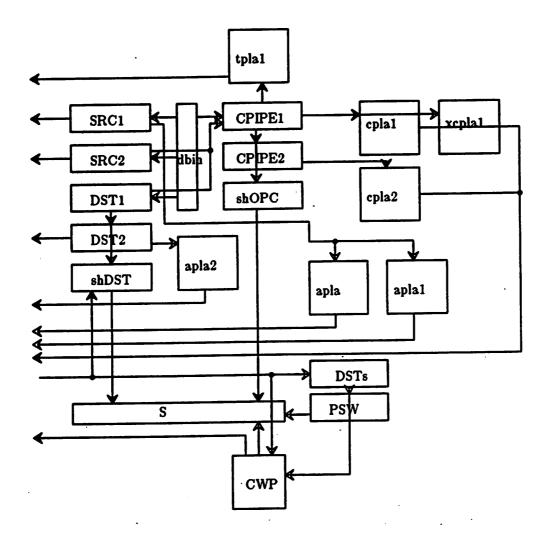

The microarchitecture design of the SOAR processor had its origins in previously designed RISC processors [Unga85]. However, it distinguished itself by containing many added features (Figure P.1). Pete Foley provided a solid microarchitectural design for the SOAR datapath. The author of this thesis completed the microarchitectural design. This included among other things a more sophisticated control section than those of previous RISCs, to handle the new features. Key items of this control section were the trapping mechanism and its variety of traps, and a way to handle multicycle instructions within the framework of the RISC pipeline.

Figure P.1- RISC II and SOAR

Circuit design and layout of an NMOS version of SOAR began with a group of four in the CS292X class – spring 1983. The role of the author in this class was to interface between the microarchitecture design and circuit design, contributing to both. A first cut at the datapath circuit design and layout was completed during this class. The author then continued microarchitecture, circuit, and layout design, along with Shing Kong. In this process the PLA tool – SPLAT – was debugged, diagnostics were written, optimizations for speed and power considerations were introduced, and a first version of an NMOS layout was completed, extracted, and logically verified. Timing verification led to the discovery of unacceptable, slow critical paths due to the multicycle instructions, in the first version of SOAR. A second version of the microarchitecture was then designed to eliminate this problem. Before complete implementation, analysis according to the author's methodology verified that it would not have the same problem or other unexpected slow paths. Design and layout of this version was completed by September 1984. Logic verification ensued, followed by timing analysis of the extracted layout. This design was fabricated in the winter and spring of 1985. Processor characterization and system development was done in the summer of 1985.

The development of a special purpose Smalltalk system is an ambitious project. It spans the disciplines of both electrical engineering and computer science. The success of a project like this relies on the efforts of individuals with a variety of talents (Figure P.2). Architectural studies culminating with CS292R, provided an efficient Smalltalk architecture [Unga85]. An architectural simulator was written in the early stages of the project [Samp85]. A CMOS version of SOAR was also implemented [Mari85]. Board design occurred concurrently with processor design [Blom83], [Dunl84], [Brow85]. System software in the form of an assembler and compiler was written [Bush85]. CAD tools proved invaluable in a project of this magnitude [Scot85]. And of course no project of this size could succeed without the resources and support of the faculty.

| Berkeley Smalltalk         | NMOS SOAR                   | CAD Support                       |

|----------------------------|-----------------------------|-----------------------------------|

| Peter Lee                  | Artie Chang                 | Gordon Hamachi                    |

| Dave Ungar                 | Mike Klein                  | Ken Keller                        |

|                            | Shing Kong                  | Jim Larus<br>Grace Mah            |

| Architectural Studies      | Joan Pendleton              | Bob Mayo                          |

|                            | Mike Remillard              | Peter Moore                       |

| John Blakken<br>Ricki Blau |                             | John Ousterhout                   |

| Wayne Citrin               | CMOS SOAR                   | Joan Pendleton                    |

| Bruce D'Ambrosio           | B. K. Bose                  | Dierdre Ryan                      |

| Pete Foley                 | Mark Hofmann                | Dain Samples                      |

| Carl Ponder                | Grace Mah                   | Walter Scott                      |

| <b>Richard Probst</b>      | Chris Marino                | George Taylor                     |

| Harry Rubin                | Peter Moore                 |                                   |

| Stuart Sechrest            | Dave Wallace                | <b>Faculty</b>                    |

| Dave Ungar                 | John Zapisek                | •                                 |

| Dave Wallace               |                             | Paul Hilfinger                    |

|                            | Board Design                | Dave Hodges                       |

| Software                   | •                           | Richard Newton<br>John Ousterhout |

|                            | Rich Blomseth<br>Will Brown | Dave Patterson                    |

| Ricki Blau<br>Bill Bush    | Frank Dunlap                | Dave I atterson                   |

| Pete Foley                 | Joan Pendleton              |                                   |

| Paul Hilfinger             |                             |                                   |

| Dain Samples               |                             |                                   |

| Part Somptoo               |                             |                                   |

#### Figure P.2- SOAR Design Groups

#### 1. References

Dave Ungar

[Blom83] Blomseth, R.; Davis, H.; 'The Orion Project- A Home for SOAR', (Unpublished) Proceedings of CS292R- Smalltalk on a RISC Architectural Investigations, Computer Science Division, EECS Dept., University of California, Berkeley, Ca., April 1983.

[Brow85] Brown, E. W.; 'A Virtual Memory CPU Board with a Large Cache', M.S. Thesis, Computer Science Division, EECS Dept., University of California, Berkeley, Ca., Jan. 1985.

[Bush85] Bush, W.; 'Smalltalk 80 to SOAR Code', (draft) Computer Science Division, EECS Dept., University of California, Berkeley, Ca., 1985.

[Dun184] Dunlap, F.; 'How To Make It Work', M.S. Thesis, EECS Dept., University of California, Berkeley, Ca., 1984.

[Mari85] Marino, C.; 'CMOS SOAR', M.S. Thesis, EECS Dept., University of California, Berkeley, Ca., 1985.

[Patt83] Patterson, D. (editor); 'Proceedings of CS292R- Smalltalk on a RISC Architectural Investigations' (Unpublished), Computer Science Division, EECS Dept., University of California, Berkeley, Ca., April 1983.

[Samp85] Samples, A. D.; 'Software for SOARing on a SUN' (draft), Computer Science Division, EECS Dept., University of California, Berkeley, Ca., February, 1985.

[Scot85] Scott, W.; Hamachi, G.; Ousterhout, J.; Mayo, R.; '1985 VLSI Tools: More Works by the Original Artists', T.R. UCB/CSD/85/225, University of California, Berkeley, Ca., February 1985.

[Unga85] Ungar, D.; 'The Design and Evaluation of a High Performance Smalltalk System', Ph.D. Thesis, University of California, Berkeley, Ca., August 1985.

:

# Chapter 1 Introduction

A method is an orderly way to arrive at a solution to a problem that has been posed. From Webster's dictionary:

method: An orderly procedure or process; regular way or manner of doing anything; hence a set form or procedure as in investigation or instruction.

Problems can range from very simple to extremely complex. For a simple problem, the solution may be readily apparent and no methodology is needed. As problems become more complicated solutions are not obvious and a procedure of some type is needed to arrive at a solution. Procedures can range from haphazard to highly organized. The disadvantages of haphazard procedures are many. A solution may never be reached. If one is reached, it may take a long time and not be very optimal. Organized procedures or methodologies ensure that a solution is reached, or reveal why it can not be reached if the problem is impossible. A good methodology provides a direct route to the solution and addresses all aspects of the problem. In this way a solution may be arrived at more quickly and its quality or optimality is higher than with a haphazard procedure.

#### 1. VLSI Issues

In the past decade integrated circuit technology has evolved so that it is now feasible to put on the order of one million transistors on a chip. As the number of available transistors has increased, the amount of circuitry has likewise increased. Complex systems that in the past were composed of many individual chips, are now being built on a single or a small number of chips. Thus, a

6

complex system may now be spread over only one or a few chips. This leads to greatly increased complexity within a single chip. The problem addressed by an individual chip has become much more complicated. Managing this complexity is a key issue that any VLSI methodology must face.

A second issue in VLSI design involves the time needed to realize a complicated chip such as a processor. The time necessary to take a VLSI design from concept to reality increases prohibitively with the increase in circuitry if new design methods are not developed. A good methodology identifies the most time consuming parts of design and tries to find faster ways of doing this work.

Once a solution to a problem is proposed, it must somehow be checked to verify its correctness. Increased complexity means many more opportunities for malfunction. First, all functions of the VLSI processor must be identified. This alone can be a major task. Once identified, provisions must be made for verifying the solutions at various stages in the design. Unlike board design, one can not cut a trace and rewire it if a bug exists in the prototype. Instead new masks must be generated and the processor is then refabricated. This can take a few months. Once the processor has been fabricated, problems that were unforeseen during the design phase can arise. Locating these errors in a complex processor can also be difficult and time consuming. Thus, debugging time is also an issue.

A fourth issue that must be addressed is that of optimality. Complex problems, such as VLSI design, usually have more than one solution. Different solutions address the many aspects of the problem with varying amounts of success. No solution is necessarily perfect. Furthermore, many factors influence the quality of the resulting characteristics. The way in which individual factors influence the final results should be understood so that tradeoffs may be made during the design process. These tradeoffs are made with the priorities of the final processor's characteristics in mind. In this way a solution that best answers all aspects of the problem may be chosen. This may be considered an optimal (non-theoretical) solution.

Thus, four key issues in VLSI processor design are:

- 1. Complexity

- 2. Time investment

- 3. Correctness

- 4. Optimality

This does not mean that there are no other issues. It simply means that these are four important issues. A good VLSI design methodology addresses all four of these issues.

#### 2. Thesis Organization

Many VLSI design methodologies exist. They all address the four key issues with varying degrees of emphasis. It is hard to categorize them because no hard and fast lines seem to exist. New methodologies evolve from the old, resulting in a spectrum of design styles. Chapter 2 discusses examples of present VLSI design methodologies. Examples were chosen on the basis of their popularity and to exemplify various possible design styles.

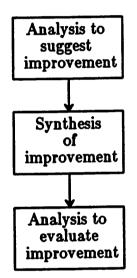

All VLSI design methodologies are structured around various design levels. Design is done at all levels in the course of realizing a VLSI processor. Many motivations exist behind the choices of design levels. Chapter 2 introduces some present design level schemes as today's methodologies are described. In Chapter 3 the design levels of the methodology proposed in this thesis are discussed. Interrelationships between the levels are described and reveal another source of the complexity in VLSI design. Implications for the methodology based on an understanding of level interrelationships, are identified. Chapter 4 discusses the methodology in great detail. The methodology is based on the design levels of Chapter 3 and their interrelationships. Although the nature of the problem is complex, the methodology breaks the large problem into a series of smaller, more straightforward problems. The ordering of these smaller problems is suggested by their natural order in the design process and with the goal of efficient use of design time.

The value of any methodology lies in its suitability to practical problems. In light of this, Chapters 5 through 10 take the Smalltalk On A Risc – SOAR – processor through the methodology. Portions of this methodology were used during SOAR design and lead to significant improvements that were subsequently put into the processor. Completion and further application of the methodology to SOAR revealed additional improvements after submittal for fabrication. The complete methodology also reinforced many design decisions on the realized chip.

## Chapter 2

### **Present Methodologies**

Presently, many differing design styles exist. These styles have developed from previous styles with the designers' backgrounds having a significant impact. All VLSI design styles address the four key issues outlined in Chapter 1 with varying degrees of emphasis.

Key VLSI Issues

1. Complexity

- 2. Time investment

- 3. Correctness

- 4. Optimality

#### 1. Design Levels

To realize a VLSI processor a description of the high level behavior or architecture of the processor, is transformed into a collection of geometric shapes made of various materials: silicon, silicon dioxide, aluminum, etc. When viewed from the outside world, this collection of geometries and the high level behavioral description function in the same way. Although their functions are equivalent, the forms of these two systems are entirely different. Thus, equivalent systems may be represented in more than one way. These different representations distinguish the levels of a design.

As a processor goes from an architectural description and set of system specifications to a small piece of silicon, it passes through many other representations and their corresponding design levels. Design is the process of transforming a problem from one representation to another until a final representation provides a solution to the original problem. Each intermediate transformation is a solution to one or more aspects of the problem posed by the previous representation level. The choice of levels reflects the designers' concerns and design strategy. Thus, the levels a design passes through can be determined by the methodology. The design levels may also influence a methodology. For example, more emphasis and consequently greater optimization, is usually placed on explicitly defined levels than on levels that are only implied.

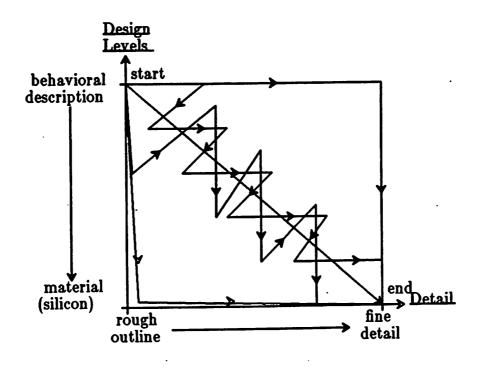

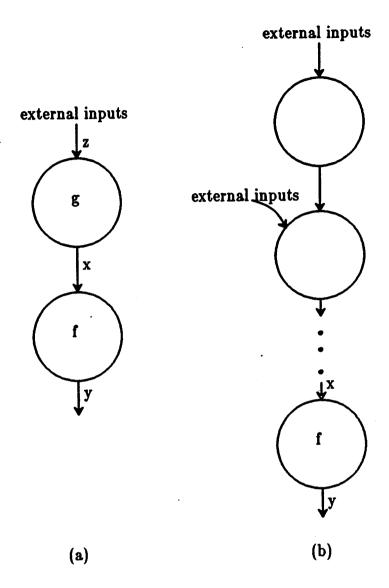

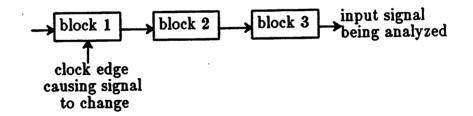

Design at any given level can range from very coarse to extremely detailed. For example, if a logic level is called for, the initial outline might only specify the logic blocks. Detailed logic design might specify the processor in terms of inverters, switches, NAND, and NOR functions. VLSI processor design begins with a rough idea for a solution at a level just below the outsider's behavioral description and is completed when a detailed representation in a material, such as silicon, is reached (Figure 2.1). Many different paths, corresponding to the many different design methodologies, may be taken from the starting point to the end point. Each path may graphically represent a methodology. Some of the possible paths would be very inefficient and therefore would not be used. Other efficient paths are in widespread use.

11

Figure 2.1- A Few of the Many Possible Design Paths

#### 2. Hierarchy

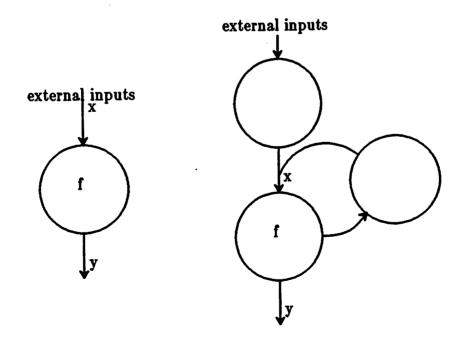

Hierarchy is an important concept in all VLSI design methodologies. Hierarchical structures are stratified. Levels are formed in an attempt to isolate the activities of any given level, from the activities of other levels. Isolation is desirable because it simplifies decisions, by eliminating considerations due to outside levels, at any given level. However, total isolation is also impossible since all levels contribute to the total structure.

Hierarchies have proven to be very useful in complex designs. The concept of isolating the pieces of a problem through the use of levels allows the overall complex problem to be broken into a set of simpler problems. Each of these simpler problems can be worked on separately and is further subdivided. Subdivision continues until the lowest level of the hierarchy is reached. This is known as top down design. Each level is composed of one or more entities. In a hierarchical structure each entity is made up of subentities. Subentities are the entities of the next lower strata of the hierarchy. For example, an ALU may be made up of 32 bit slices. All entities are specified in two ways. First, the entity is viewed as a black box with inputs and outputs. The behavior of these inputs and outputs is specified by the entity that the given entity is a subentity of. This represents the connection between levels. Then to realize the entity, the internal components – subentities – and their interconnections are specified. This internal specification must result in the required behavior as viewed from the inputs and outputs. Except for the inputs and outputs, this design is done in isolation from the other levels. Specification of the internal components of the entity leads to the input/output specifications of the subentities.

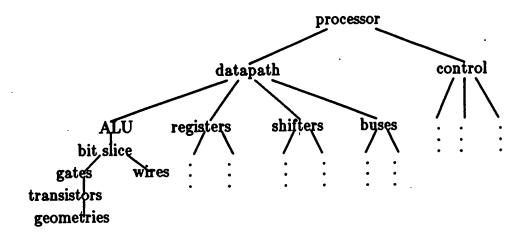

In VLSI processor design the highest hierarchical level is the entire processor chip (Figure 2.2). The first part of its behavior is the specification of the behavior at the pins. The processor may then be divided into a datapath and control section. The datapath can then be specified in terms of ALUs, registers, shifters, and buses. An ALU may then contain bitslices. Each bitslice is made up of logic gates and wires. The logic gates are composed of transistors which are formed by geometries of the various fabrication materials. The majority, but not all, of the design considerations at any one of these levels, are independent of the other levels.

Figure 2.2- Hierarchy Example in a VLSI Processor

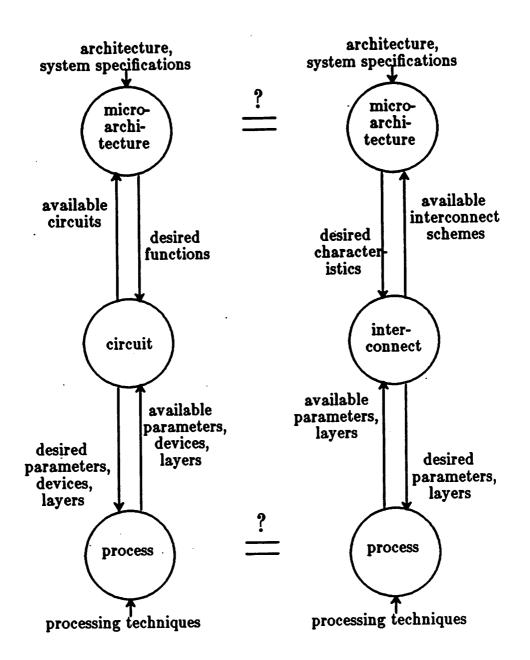

#### 3. Design Levels and Hierarchy

Both design levels and hierarchies are useful when solving a complex problem. Therefore, the next question becomes: How do the design levels relate to the levels of a hierarchy. Hierarchies can exist within a design level. In this type of hierarchy all hierarchical levels have the same representation. The levels of the hierarchy are distinguished by the amount of detail that they contain. This is typically called a structural hierarchy [LaPo83]. The coarse outline of a processor in a given representation corresponds to the high levels of the structural hierarchy. The structural hierarchy is then traversed to the lowest levels as detail in the same representation form, is added to the processor components.

A second possibility is that the design levels may correspond to one or more levels of a different hierarchy. As this type of hierarchy is traversed the representation form of a design changes. This is considered an abstraction hierarchy. For example, if the abstraction hierarchy contains a logic level, logic diagrams may form the basis of this logic level. Another possibility is that the logic level may correspond to a sublevel within a circuit design level. Depending on the methodology, hierarchies exist within design levels and across the design levels.

Top down design leads to both types of hierarchical structures. Each level explicitly specifies the characteristics of the next lower level. Using these characteristics the next lower level is designed. A drawback of this is that there is no obvious way to consider influences of lower levels when designing at higher levels, or influences from other branches of the hierarchy. Tradeoffs may be overlooked and optimality can suffer. For this reason most VLSI design methodologies are not purely hierarchical. Most recognize the need for feedback from the lower levels to the higher levels. Different methodologies place varying amounts of emphasis on these non-hierarchical paths and implement them differently, as will be seen in the next sections.

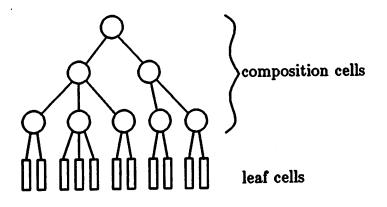

#### 4. Mead-Conway Style

The Mead-Conway design style was one of the first formalized design styles [Mead80], [Trim81], [Joha81]. It is still in widespread use today as an instructional tool. It also forms the basis of more sophisticated design methodologies. The Mead-Conway style emphasizes a top down hierarchical approach. Designs are composed of composition and leaf cells (Figure 2.3) Leaf cells make up the lowest level of the structural hierarchy. They contain circuit components and wires, but no instances of other cells. Composition cells occupy all but the lowest hierarchical level. They are composed of lower level cells and the interconnects between these lower cells.

Figure 2.3- Mead-Conway Structural Hierarchy

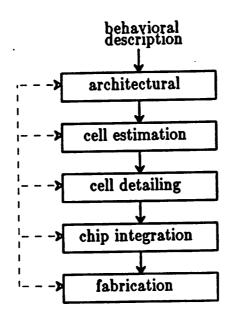

Figure 2.4 shows the design levels of this style. The formalized methodology concentrates on proceeding through these levels in a top down manner as indicated by the solid arrows. Design begins with a behavioral description. At the architectural level, the composition cells at the top of the structural hierarchy, that are needed to implement this behavior, are identified and assigned to areas of the floorplan. Wiring is considered and the critical paths of the chip are estimated. Subsequent levels fill in the details of all cells according to the requirements passed down from the higher levels. At the cell estimation level inputs and outputs of the blocks are specified and their areas estimated. To do this the large composition cells of the floorplan are decomposed into intermediate composition cells and leaf cells. The cell detailing level calls for layout of the leaf cells. During chip integration, cells are connected together starting at the bottom of the structural hierarchy and moving towards the top until all interconnections have been made. The design is then ready for fabrication. Thus, this design style emphasizes increased refinement of the design as the levels are traversed to the cell detailing level.

Figure 2.4- Mead-Conway Design Levels

The Mead-Conway style recognizes the need for feedback of information from the lower levels to the higher design levels as indicated by the dashed lines of Figure 2.4. It calls for iteration between the levels if pieces of the design are not compatible. However, it has not developed formalized guidelines for this process as it has done for the top down procedure.

#### 5. CMU-DA System

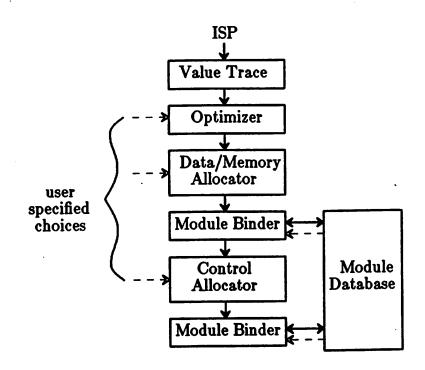

Research work at Carnegie Mellon University has developed a system that automates processor design from the behavioral description to the layout- the CMU-DA System [Hafe78], [Snow78], [Park78], [Dire81], [Thom83], [Kowa83], [Hitc83], [Tsen83], [Walk83]. It differs from other systems by automating the highest levels of design- the microarchitecture. Traditionally, microarchitecture design has been left to humans. A methodology is needed as the basis of any design automation system, if processor design is to be fully automated. The CMU design methodology, as reflected in the design automation system, is reviewed here. Figure 2.5 is a block diagram of the design automation system. Each block accepts input in an appropriate form for that block, and generates output of a form that can be used by the next piece of the system. Except for the optimizer, the system blocks transform the design from one representation to another. They therefore correspond to the design levels of the methodology.

Figure 2.5- CMU-DA System

The architecture and system specifications of the processor are originally specified in the ISP hardware description language. Due to the structure of this language, the ISP description of the processor will imply certain structures in the microarchitecture. For example, temporary registers can be specified in an ISP description. This implies the same temporaries in the microarchitecture, although there might be microarchitectures that do not need the specified temporaries. The first block in the CMU-DA system converts the ISP description to a data flow representation- the value trace. This translation removes artifacts of the ISP

18

language such as temporaries, data dependencies, and implied control sequences. The value trace is a more general representation than the ISP description. The value trace may then be optimized to improve the speed or cost of the processor and eliminate inefficiency. The optimizer output is an optimized value trace.

The allocators generate register transfer structures. The datapath structure is generated by the data/memory allocator. The control allocator generates a register transfer representation of the control section. These register transfer structures specify the physical blocks – modules – and their interconnections.

The module database contains a library of circuits, their layouts and characteristics such as speed, size, power, and cost. The module binders select circuits from this database according to the requirements passed down by the allocators.

The blocks of the CMU-DA system may be grouped into design levels according to their output representations (Table 2.1). The ISP description and module database provide input data to the design system.

| Design Level    | CMU-DA Block                               | Output                         |

|-----------------|--------------------------------------------|--------------------------------|

| 1               | Value Trace<br>Optimizer                   | Value Trace                    |

| 2               | Data/Memory Allocator<br>Control Allocator | Register Transfer<br>Structure |

| 3               | Module Binder                              | Layout                         |

| External Inputs | ISP<br>Module Database                     | -                              |

Table 2.1- CMU-DA Design Levels

This methodology provides for analysis and optimization within each level. Inputs for optimization come from requirements of higher levels or from human intervention. This does not rule out feedback from lower levels. However, there are no formal guidelines for it. Feedback from any of the lower levels can be carried out through human interaction with the system.

At the highest level, the value trace may be optimized for speed or cost improvements and to avoid inefficiency. The optimizer works with the existing value trace and optimizes according to the users specifications. The user may look at the results and try another optimizing criteria if the results are not satisfactory.

At the allocator level the user may choose the style for the datapath and control sections. Control may be microcode or PLA based. Styles for the datapath are distributed (highly parallel), bus oriented, and pipelined. Again tradeoffs are made by trying the options and choosing the best.

Higher levels pass a register transfer description and desired module characteristics to the module binder. Optimization occurs at the module binder level as circuits are chosen from the module database on the basis of their required speed, size, power, and cost as well as their function.

In Figure 2.5 the dashed lines indicate inputs for optimizations. These inputs are all external – either user generated or from the module database. As just described, the user can specify optimizing criteria to the optimizer and design styles to the allocators. The module database provides information on the speed, size, power, and cost of each module so that the module binder can choose the best module. Optimization inputs for a given level do not formally come from any lower design levels. Optimization occurs within a given level in response to requirements from higher levels, external inputs, and choices by the user.

### 6. Bell Laboratories- Bellmac-32 Techniques

The design methods used by Bell Laboratories in their Bellmac-32 processor project were distinguished in two significant ways [Murp81], [Kang82], [Murp83]:

1. Simultaneous design at all levels

2. Explicit feedback from lower design levels to higher levels during design

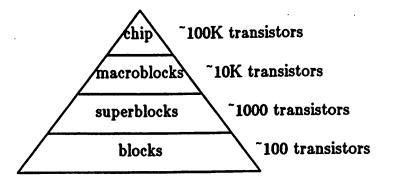

This project also explicitly defined the structural hierarchy of the processor (Figure 2.6). The highest level of this hierarchy was the chip level, with approximately 100,000 transistors. The chip was divided into macroblocks of about 10,000 transistors each. The macroblocks were then subdivided into 1,000 transistor superblocks. At the lowest level of the structural hierarchy were the blocks with about 100 transistors each.

Figure 2.6- Bellmac-32 Structural Hierarchy

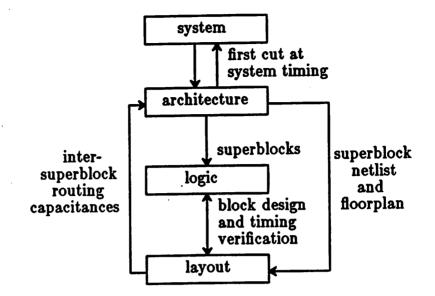

Design levels of this project were the system, architecture, logic, and layout levels. Unlike the Mead-Conway and CMU-DA design styles that emphasized topdown approaches, all design levels were worked on simultaneously in the Bellmac-32 project. The result of this was that information from the lower design levels was available early in the design process. Decisions at the higher levels were made with information available from the lower design levels.

Figure 2.7 illustrates the design process that included timing considerations. Design at the architecture level defined the superblocks, their function, and input/output specifications. It also generated a floorplan and the netlist for suberblock interconnections. The logic level continued with the design of the superblocks. Meanwhile the inter-superblock routing was laid out on the floorplan. Inter-superblock routing capacitances were calculated from this layout and used in a first cut at the timing analysis of the processor. This provided feedback to the system designers. Concurrently, logic, layout, and timing analysis of the blocks was also carried out.

Figure 2.7- Bellmac-32 Design Process with Timing Considerations

As can be seen in Figure 2.7, the arrows of the design process not only point from the higher levels to the lower levels. They also point from the lower levels to the higher. The Bellmac-32 design process sets explicit guidelines for feedback of lower level information into design decisions at the higher levels. This feedback from the lower design levels to the higher ones, can also be done for other characteristics such as area and power.

## 7. IBM- Philo VLSI Design System

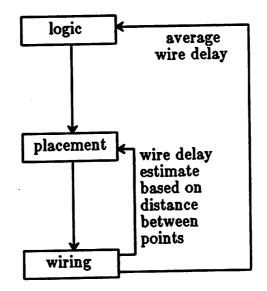

IBM's Philo design system is used in their master image designs [Donz82], [Ahdo83]. Master image designs emphasize both regularity and flexibility. Chip size for these designs is fixed. The chip is organized into a regular array of cell locations. Power buses and other routing are also fixed. Circuits are composed of cells and macros. The cells occupy one or two adjacent cell locations. A macro is any circuit that requires more than 2 cell locations. PLAs and RAMs are two types of macros. Layout complexity is reduced by this regularity. The Philo design system provides for logic design and layout. System behavior and architecture are outside the realm of this tool set. Layout is accomplished in two steps – placement and routing. Figure 2.8 shows the design levels and their interactions. Design proceeds in a top down manner with timing simulation at each level. This timing simulation uses information from the lowest level – the wiring level.

Figure 2.8- Philo Design Process with Timing Considerations

Design starts at the logic level. Accurate estimates of the wire lengths and loads are not available so an average delay is assumed. This average delay is based on characterization of the master image process. Using this rough estimate gross timing errors can be avoided.

After the logic has been verified, the cells and macros are placed onto the grid. After placement, the lengths of the wires may be estimated from the distances between their terminations. A more accurate estimate of routing delays than the logic level estimate, is now available based on this wire length estimate. Timing simulation at the placement level uses this refined wire delay estimate.

24

Design then moves to the wiring level. All interconnects are now routed and the actual length of each wire becomes known. Wire delays can now be accurately estimated from the actual wire lengths. Timing simulation is done once again with even greater accuracy now. Thus, the Philo design system has provided a formal method for feedback of delay information, from the lowest design level – wiring – to the highest level of the design system – the logic level.

#### 8. Summary

These are four design styles that portray many of the concepts and approaches that are characteristic of VLSI design methodologies. The four key issues of VLSI design are addressed by each of them. All of them rely heavily on computer aided design – CAD – tools to address these issues. Many CAD tools exist to aid in the synthesis, verification, and analysis of VLSI designs. Synthesis tools include such things as layout editors, placement tools, and routers to name a few. Logic verifiers, timing verifiers, and design rule checkers are just a few of the verification tools that are available. Examples of analysis tools are timing simulators and tools for power estimation. CAD tools can do much of the tedious, time consuming work of processor design. Thus, the issue of the time investment needed to realize a VLSI processor is directly answered by the development of CAD tools.

The issue of correctness can be answered in more than one way. Correctness must be verified at all levels and between the levels. One approach is to develop CAD tools that can check the correctness of these complex chips. For example, design rule checkers check the layout level for design rule violations. The layout may be checked against the logic by extracting the layout and then using a transistor level logic simulator on the extracted layout. A second approach is to develop tools that synthesize a lower level from a higher level description. Rules for correctness are built into the synthesizer. In this way the lower level representation is correct by definition (assuming a correct higher level description) if it can be synthesized.

These four design styles all depend on hierarchies. As previously discussed, hierarchy is very important in dealing with the complexity issue of VLSI design. It provides an organized way of viewing the complex problem. The efficiency of many CAD tools is also based on hierarchical organization.

Perhaps the least understood of the key issues is optimality. The four examples of design styles emphasize optimality to varying degrees. They ranged from mentioning iteration as a way to optimize, to providing analysis tools that could be used to calculate and improve optimality at specified places in the design process. Analysis tools help evaluate the optimality of a design but an understanding of relationships between the many aspects of a design is needed to be able to optimize efficiently. The optimizer of the CMU-DA system is an example of a CAD tool that has incorporated some understanding of these relationships. Another approach to optimality is to cut design time, through the use of CAD tools. With a shorter design cycle multiple alternatives can be tried and evaluated. The best one is then chosen and fabricated.

The experience of participating in all levels of the SOAR processor design provided valuable insight into the many interrelationships between design levels. This thesis outlines the interrelationships between the various design levels. These interrelationships are numerous and have many causes. This is another source of the complexity in VLSI design. The effects of tradeoffs may be predicted Many of these these interrelationships. understanding of from an interrelationships are influences of lower design levels on the higher levels. This thesis presents guidelines for incorporating these bottom up influences into the design process. This can lead to increased optimality in a shorter design time.

26

#### 9. References

[Ahdo83] Ahdoot, K.; Alvarodiaz, R.; Crawley, L.; 'IBM FSD VLSI Chip Design Methodology', Proceedings of the 20th Design Automation Conference, Miami Beach, Fla., June 1983.

[Dire81] Director, S.; Parker, A.; Siewiorek, D.; Thomas, D.; 'A Design Methodology and Computer Aids for Digital VLSI Systems', IEEE Trans. on Circuits and Systems, V.28, N.7, July 1981.

[Donz82] Donze, R.; Jenkins, M.; Sanders, J.; Sporzynski, G.; 'Philo- A VLSI Design System', Proceedings of the 19th Design Automation Conference, Las Vegas, June 1982.

[Hafe78] Hafer, L.; Parker, A.; 'Register-Transfer Level Digital Design Automation: The Allocation Process', Proceedings of the 15th Design Automation Conference, 1978.

[Hitc83] Hitchcock, C.; Thomas, D.; 'A Method of Automatic Datapath Synthesis', Proceedings of the 20th Design Automation Conference, Miami Beach, Fla., June 1983.

[Joha81] Johannsen, D. L.; 'Silicon Compilation', PhD. Thesis, Dept. of Computer Science, T.R. 4530, California Institute of Technology, Pasadena, Ca., 1981.

[Kang82] Kang, S.; Krambeck, R.; Law, H.; Lopez, A.; 'Gate Matrix Layout of Random Control Logic in a 32bit CMOS CPU Chip Adaptable to Evolving Logic Design', Proceedings of the 19th Design Automation Conference, Las Vegas, June 1982.

[Kowa83] Kowalski, T.; Thomas, D.; 'The VLSI Design Automation Assistant: Prototype System', Proceedings of the 20th Design Automation Conference, Miami Beach, Fla., June 1983.

[LaPo83] LaPotin, D.; Nassif, S.; Rajan, J.; Bushnell, M.; Nestor, J.; 'DIF: A Framework for VLSI Multi-Level Representation', T.R. CMUCAD-83-20, Carnegie Mellon University, Pittsburgh, Pa., Nov. 1983.

[Mead80] Mead, C.; Conway, L.; 'Introduction to VLSI Systems', Addison/-Wesley Publishing Co., Reading, Ma., 1980.

[Murp81] Murphy, B.; Thomas, L.; Molinelli, J.; Edwards, R.; 'A CMOS 32-bit Single Chip Microprocessor', International Solid State Circuits Conference Digest, V; Feb. 1981.

[Murp83] Murphy, B. T.; 'Microcomputers: Trends, Technologies, and Design Strategies', IEEE Journal of Solid State Circuits, V.18, N.3, June 1983.

[Park79] Parker, A.; Thomas, D.; Siewiorek, D.; 'The CMU Design Automation System: An Example of Automated Data Path Design', Proceedings of the 16th Design Automation Conference, 1979.

[Snow78] Snow, E.; Siewiorek, D.; Thomas, D.; 'A Technology – Relative Computer Aided Design System: Abstract Representations, Transformations, and Design Tradeoffs', Proceedings of the 15th Design Automation Conference, 1978.

[Thom83] Thomas, D.; Nestor, J.; 'Defining and Implementing a Multilevel Design Representation with Simulation Applications', IEEE Trans. on Computer Aided Design, V.2, N.3, July 1983.

[Trim81] Trimberger, S.; Rowson, J.; Lang, C.; Gray, J.; 'A Structured Design Methodology and Associated Software Tools', IEEE Trans. on Circuits and Systems, V.28, N.7, July 1981.

[Tsen83] Tseng, C.; Siewiorek, D.; 'Facet: A Procedure for the Automated Synthesis of Digital Systems', Proceedings of the 20th Design Automation Conference, Miami Beach, Fla., June 1983.

[Walk83] Walker, R.; Thomas, D.; 'Behavioral Level Transformation in the CMU-DA System', Proceedings of the 20th Design Automation Conference, Miami Beach, Fla., June 1983.

٠

# Chapter 3

# Design Levels

The concept of design levels and hierarchy was reviewed in Chapter 2. Two types of hierarchies were defined – the abstraction and structural hierarchies. Both types of hierarchy are composed of levels. Design levels as defined in this thesis, correspond to the levels of the abstraction hierarchy. The are distinguished by:

- 1. The type of problem addressed

- 2. Processor representation

- 3. The way that processor characteristics are analyzed

Levels of a structural hierarchy are defined by the amount of detail that they contain. Structural hierarchies exist within the design levels.

Levels are defined so that the initial complex design problem is broken into many smaller, simpler problems. Ideally, each smaller problem would be entirely self contained. Solutions to other problems would not influence this isolated problem. In practice this is not possible. To complete the design, solutions to all of the small problems are needed. These solutions affect each other and tradeoffs must be made. Although the smaller problems can not be entirely self contained, a judicious choice of levels can minimize the influences of other levels on a given level. This does not mean that tradeoffs are ignored. It simply means that the levels are organized so that the majority of considerations, decisions, and tradeoffs occur within a level – not across levels.

Levels of an abstraction hierarchy have different representations for the same structure. For example, at the higher levels a processor may be represented by a behavioral description written in an algorithmic language. At lower levels the same processor might be represented by logic diagrams or transistor schematics. Each representation provides a unique view of the overall problem that leads to a solution to some aspect of the original problem.

A consequence of these different representations is that processor characteristics are analyzed differently at the different levels. For example, the speed of a processor may be characterized by the number of instructions needed to run a benchmark at the higher levels. At a lower level it might be characterized by the number of gate delays in a given circuit block.

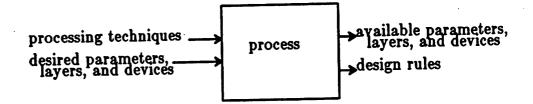

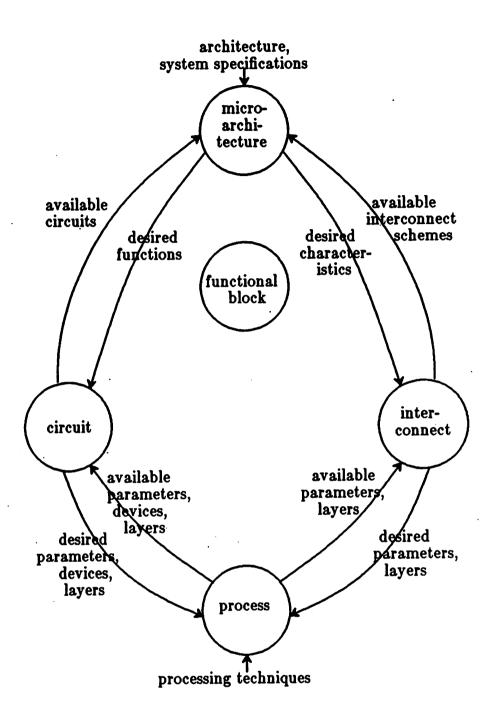

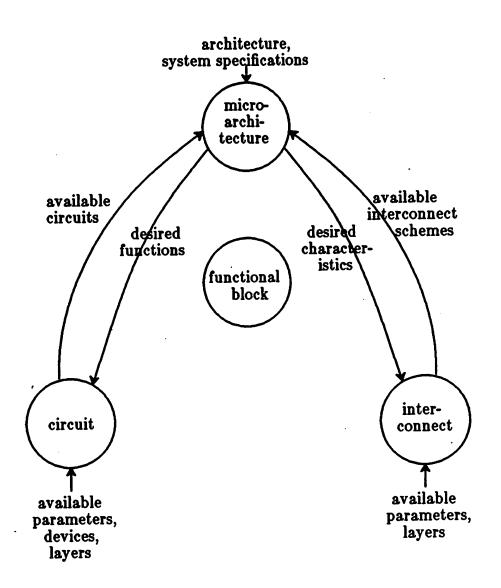

This thesis proposes five major design levels that a VLSI processor design can be partitioned into. Each level requires certain types of information as inputs to it. Design strategies are then formulated and decisions are made based on these inputs. This results in outputs from the given level. These outputs may be used as inputs to other levels. Level inputs may also be predetermined by factors outside the scope of the processor design. Design at any level satisfies the inputs for that level and results in outputs that affect other levels. The five design levels are:

> Microarchitecture Functional Block Circuit Interconnect Process

# 1. Microarchitecture Level

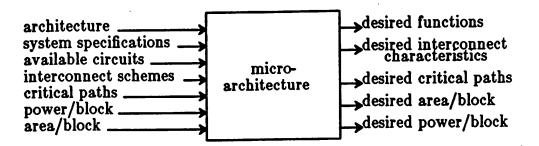

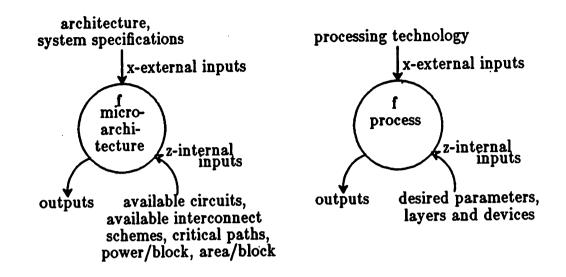

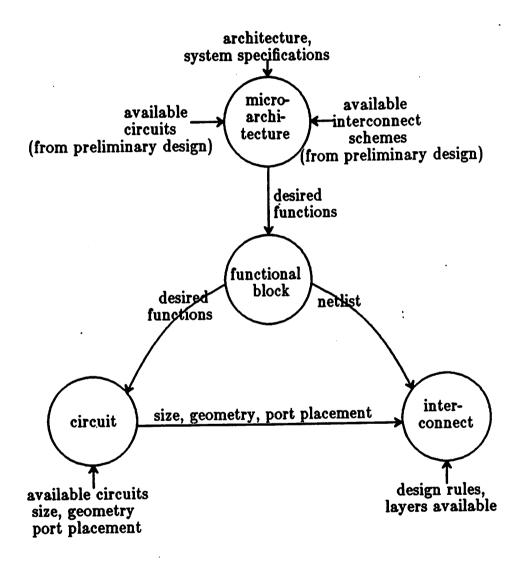

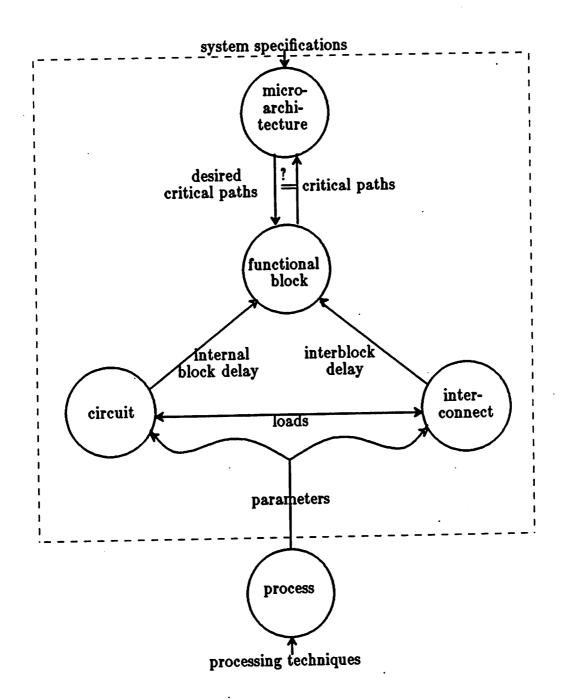

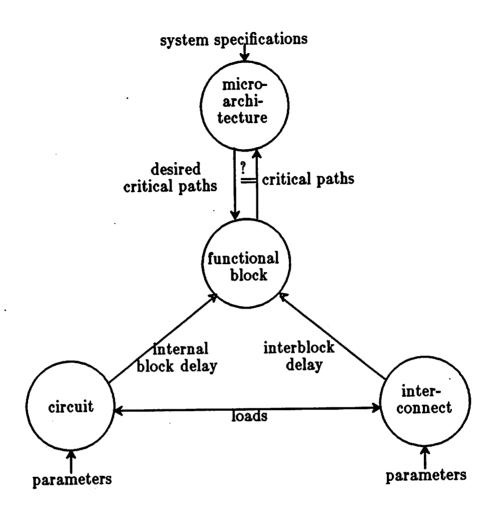

The highest level of processor design is the microarchitecture level. One set of external inputs to the microarchitecture is the architecture (Figure 3.1). This includes data types, word size, addressing modes, the instruction set, register organization, operations to be performed, and internally generated exceptions and trapping conditions. The system that the processor is to be a part of also places restrictions and requirements on the processor. Interfaces between the processor and other parts of the system determine processor behavior. System requirements include such things as timing specifications at the pins, bus protocols, coprocessor protocols, memory and I/O configurations, external interrupts, package, power budget, and test methods.

Figure 3.1- Microarchitecture Level

Another set of inputs to the microarchitecture level are the circuits that are available for use in the design. Various characteristics, such as speed, area, and power, of these circuits are important to the microarchitecture design. The available circuits and their characteristics are matched to the architecture and system requirements through the proposed microarchitecture.

Possible interconnect schemes are another input to the design at the microarchitecture level. This includes the number and configuration of data busses, distribution of control lines, and communication between various subsystems within the processor. Interconnect schemes are usually expressed in a floorplan of the processor.

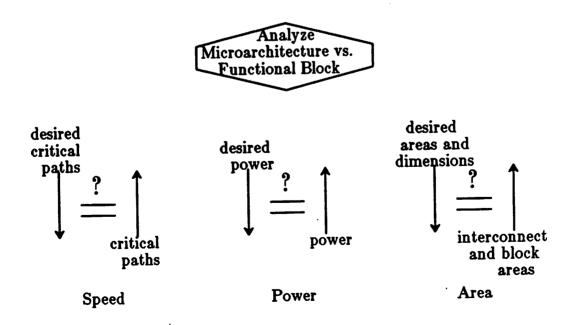

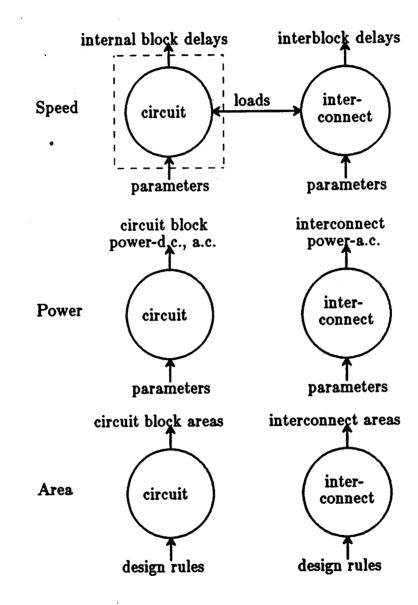

The critical paths that exist on a processor are also important to the microarchitecture. Once a microarchitecture is proposed, the critical paths can be estimated from an analysis of design at the lower levels: process, circuit, interconnect, and functional block levels. The proposed microarchitecture can

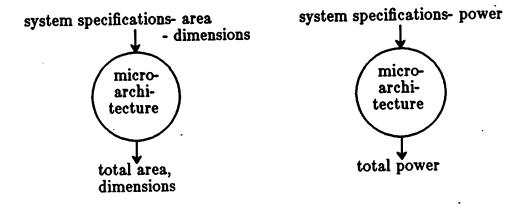

then be analyzed, using the critical paths, to see if it will meet the system specification inputs. This can result in further design of the microarchitecture or a viable compromise of the system specifications. Similarly, the power and area of each functional block is also an input to the microarchitecture level. These may also be determined by analysis at the lower levels. They can then be totaled to arrive at an estimate of the processor size and power. These estimates are then compared with the system specifications to determine if further optimization is needed.

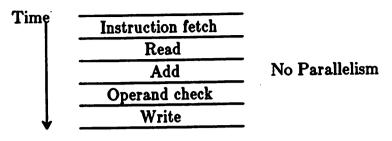

Given these inputs, design alternatives for the microarchitecture are proposed and analyzed. Design decisions concerning high level implementation issues are made. The choice of the microarchitecture should not be visible to the programmer or system designer. There are two major problems to be be solved during microarchitecture design. First, the functions that the processor must perform are identified. The instruction set and system specifications determine the basic functions of the processor. Secondly, the coordination – timing – of the blocks that perform these functions, must be specified. Good timing leads to correct and efficient execution of instructions. Examples of design at the microarchitecture level are parallelism, pipeline design, the use of microcode, resources needed and their allocation, and interrupt and trapping mechanisms.

Given a proposed microarchitecture, an important question is: How good is it? Typical characteristics that are analyzed to answer this question, are speed, power, and area. As previously discussed, the yardstick for measuring any characteristic depends on the design level being analyzed. At the architecture and system level, the number of instructions needed to complete a job using a given instruction set, is a measure of the speed of the architecture. The number of clock cycles needed for each instruction type is also a measure of the system and architecture speed if system factors influence this number. For example, if a

32

single instruction is to do eight loads, the memory speed will influence the number of cycles needed to complete this instruction. The number of clock cycles/instruction can also be a measure of the speed of the microarchitecture. For example, in a microcoded machine each instruction is typically implemented with a series of single cycle microinstructions. The number of microinstructions needed for a given instruction determines the number of cycles required for that instruction. Cycles are typically split into phases and processor activities are assigned to each phase during microarchitecture design. Therefore, a second measure of microarchitecture speed is the number of clock phases in each cycle. The total cycle time is the sum of the individual phase lengths. This leads to a third criteria for processor speed evaluation at the microarchitecture level: phase lengths. At the microarchitecture level, the processor activities assigned to each phase determine the phase length and are therefore the third measure of speed.

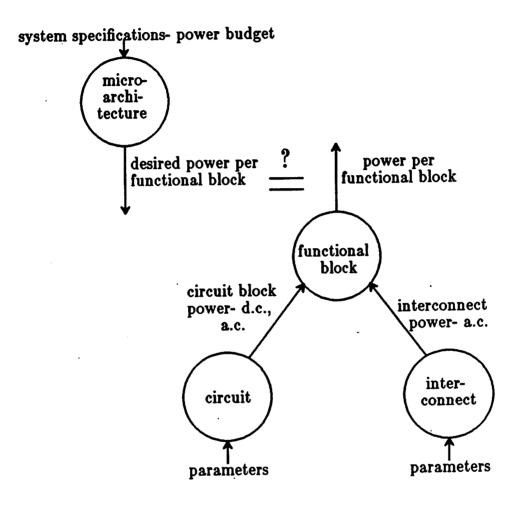

Power evaluation at the architecture and system level, is done by determining the power consumption of each chip in the system. Microarchitecture design divides a chip into functional blocks. The power budget of each functional block is the criteria for power analysis at the microarchitecture level.

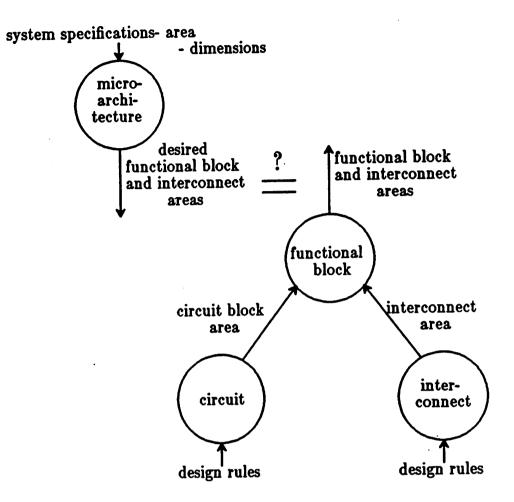

Similarly, the total processor area is used for the area measurement at the system level. At the microarchitecture level, the area of each functional block is important. Further design at the functional block level will divide this area into circuit and interconnect areas.

One set of outputs of the microarchitecture design are the desired functions and their characteristics. The proposed microarchitecture necessitates various functions that must be provided for by the lower levels. The characteristics of these functions are also important to the microarchitecture. For example the functions' speeds directly affect the timing. Desired interconnect characteristics are another set of outputs from the microarchitecture level. Examples of this are interconnect speed and the number and types of levels available. Interconnect speeds partially determine signal speeds which are important to the processor timing. The number of interconnect levels affects the interconnect scheme.

The desired critical paths are also outputs of the microarchitecture design. These evolve from the system specifications. The system specifications place timing requirements on the processor. For a proposed microarchitecture, each signal path will have to operate at a speed that will allow the system specifications to be met. These speeds are the desired critical paths. When doing design at lower levels these critical paths must be taken into consideration. Similarly, the microarchitecture design may specify the sizes and power budgets of the individual blocks. This is done so that the total power and area of the processor matches the system requirements.

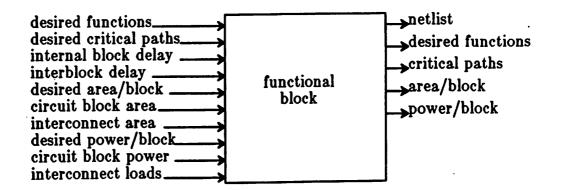

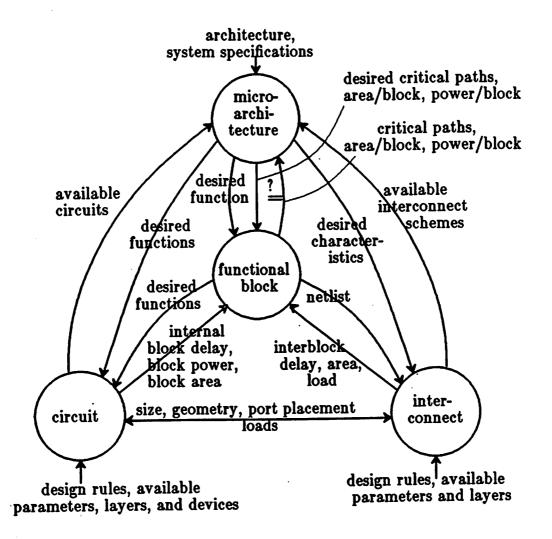

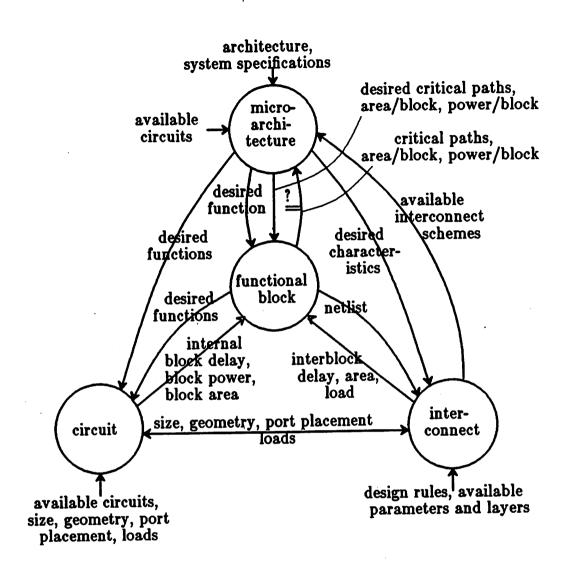

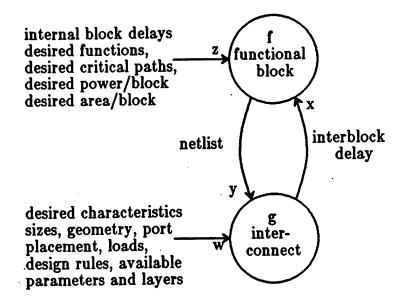

# 2. Functional Block Level

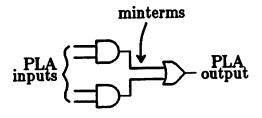

Design at the functional block level involves mapping the functional blocks specified during microarchitecture design, into the circuit blocks that will be used in the processor layout. As this is done the function of each circuit block and their interconnections are determined. Examples of datapath blocks are ALUs, counters, shifters, latches, various registers, sign extenders, and comparators. Typical control blocks are latches, counters, comparators, PLAs, ROMs, and random logic blocks.

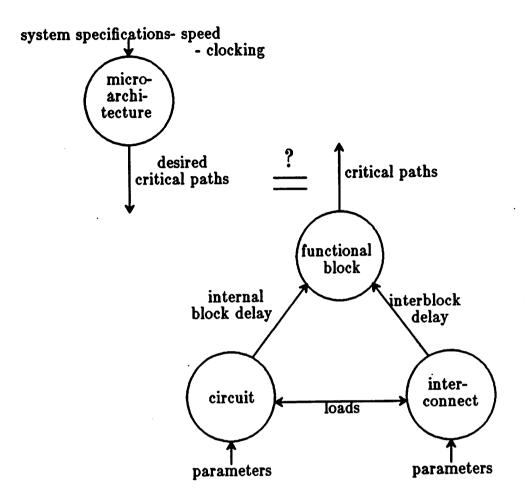

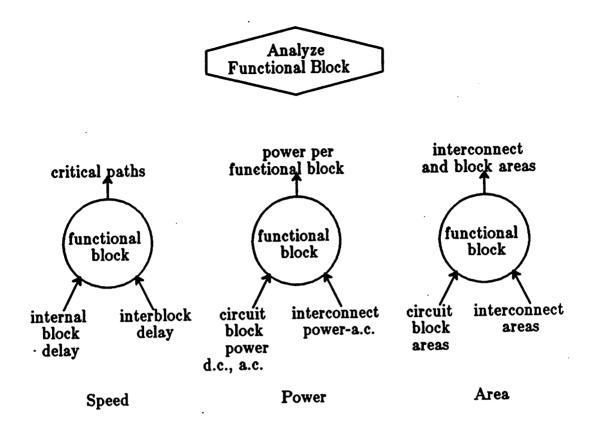

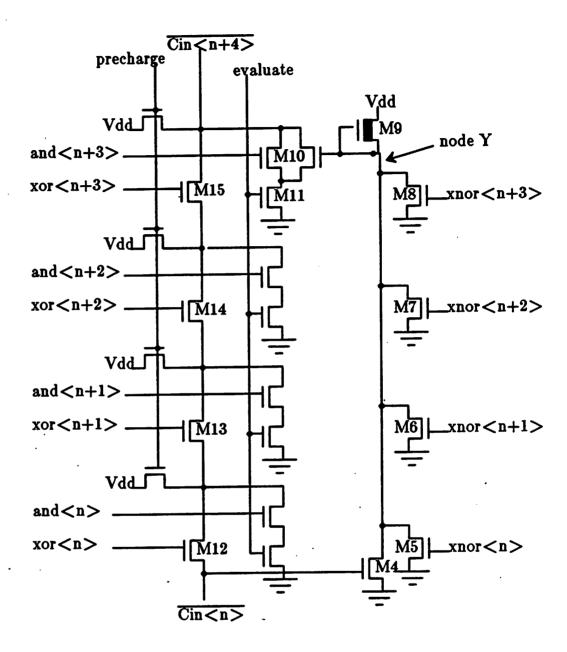

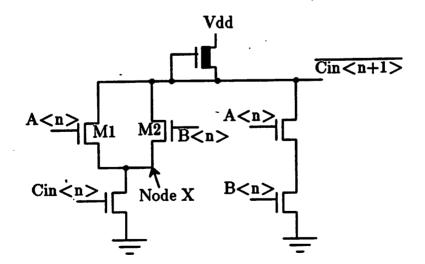

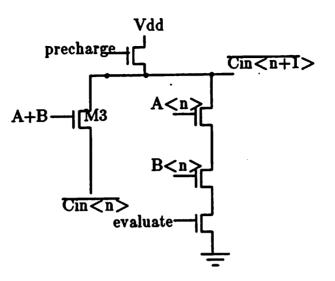

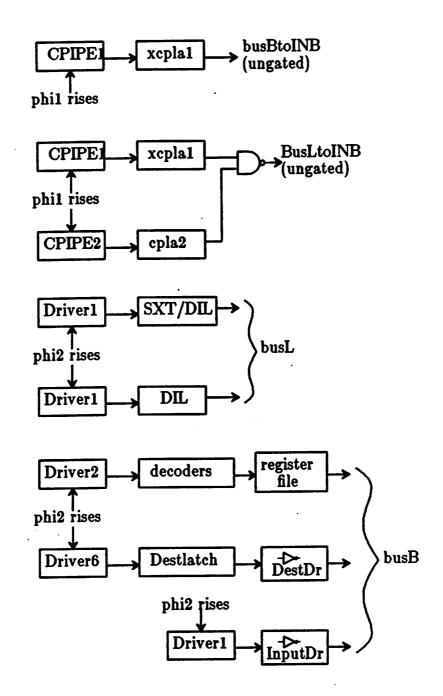

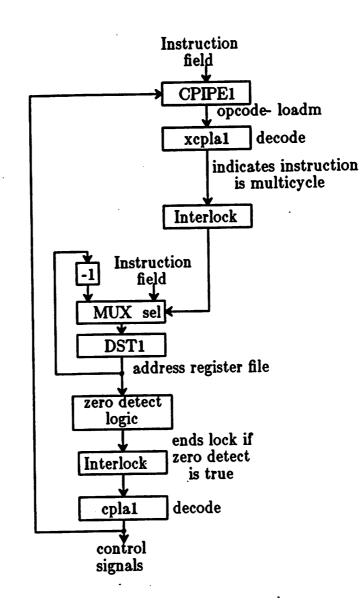

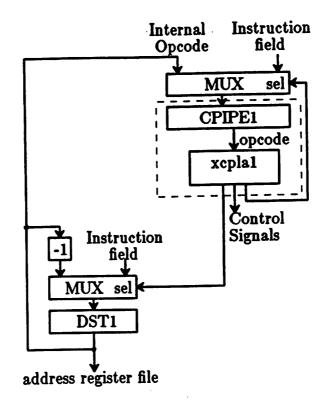

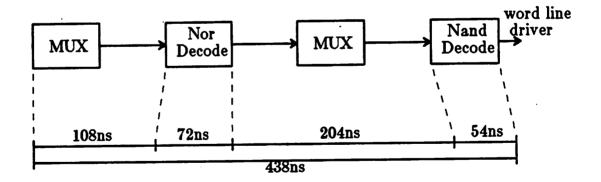

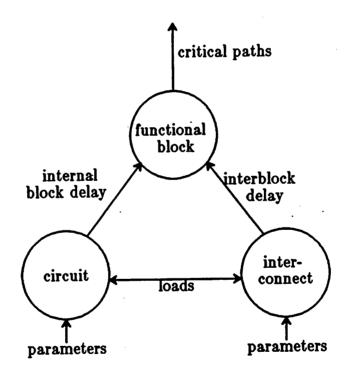

Microarchitecture design assigned processor activities to the clock phases. Speed analysis at the functional block level determines the time needed to complete each activity and identifies the major components of this delay. The delay of the output signals of an activity is a measure of the time needed for that activity to complete. These signals – critical paths – typically propagate through circuit blocks and across interconnects. For example, an instruction decode may start with the propagation of the opcode to a decode PLA. The decode PLA then determines control line values. These values then travel across other interconnects to the places where they are used. Decode delay is the sum of these two interconnect propagation delays and the PLA delay. Thus, the circuit block and interconnect delays determine the speed of each activity.

The power consumption of each functional block is the sum of the power dissipated in its circuit blocks and interconnects. Circuit blocks consume both d.c. and a.c. power. The interconnects require a.c. power according to their capacitive load and clock rate. Thus, power dissipation at the functional block level, is the sum of the power consumed by the individual circuit blocks and interconnects.

Functional block area is also the sum of the areas of the circuit blocks and interconnects. Therefore, circuit block and interconnect areas are of concern for area analysis at the functional block level.

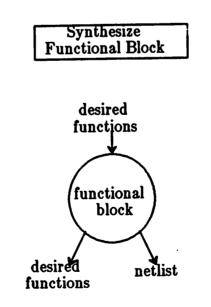

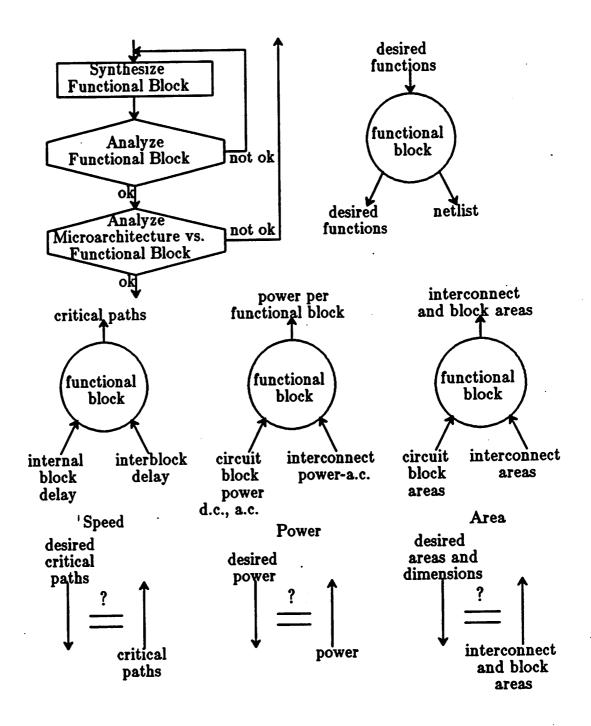

The first inputs to the functional block design level are the desired functions of the processor (Figure 3.2). These desired functions are specified at the design level above the functional block level – the microarchitecture level. Design at the functional block level assigns these functions to the circuit blocks.

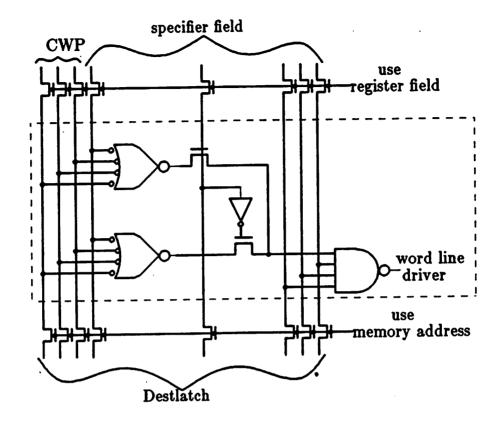

Figure 3.2- Functional Block Level

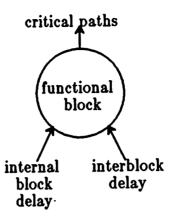

Another set of inputs to the functional block level are the desired critical paths of the processor. When doing timing analysis, these desired critical paths are compared to the predicted critical paths of the proposed functional block organization. The predicted critical paths are arrived at by considering the internal delays of each block and the delays between blocks, the interblock delays. Therefore, to do this type of analysis of the functional block design, the internal block delays and interblock delays must be inputs to the functional block design level.

Similarly, the desired areas and power budgets of the functional blocks are inputs to the functional block level. These are compared to the predicted areas and power budgets. To predict the area, the circuit block sizes and interconnect areas are needed. These are therefore inputs to the functional block level. A power estimate for the processor requires the power dissipation of the individual circuit blocks and interconnect loads to be an input to the functional block level. The circuit blocks consume both d.c. and a.c. power while the interconnects require a.c. power according to their loads and the clock rate.

One output of the functional block design is a netlist. Knowing the functions that are in each block and how they relate to each other, leads to a complete

netlist for the processor. Typically, the netlist will contain some nets that may limit processor speed. These critical nets are identified in the complete netlist.

Another set of outputs are the desired functions of the circuits in each circuit block. These desired functions and their characteristics are passed to the circuit design level for realization.

Analysis of the functional block design results in estimated critical paths for the proposed design. These critical path outputs are compared with the desired critical path inputs. Based on these comparisons, optimization and redesign of the functional block scheme is carried out. Analysis also provides estimates of the area and power consumption of the functional blocks. These estimates are compared with the desired areas and power budgets. Redesign is then done if necessary.

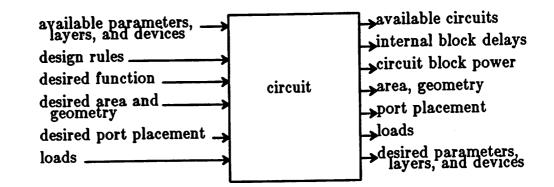

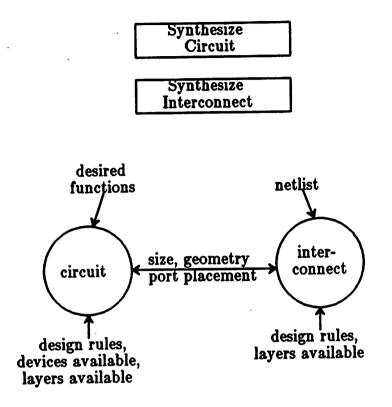

## 3. Circuit Level

Circuit level design results in a layout realization of the circuit blocks. This includes the logic design of each block. The logic design is then transformed into a gate level design. From the gate level description a transistor level design is specified. The transistor level schematics are the basis for the actual layouts of the functional blocks. The logic, gate, transistor, and layout representations are sublevels of the circuit level in this methodology. It is not uncommon for these sublevels to be distinct design levels in other methodologies [Thom83].

Speed analysis at the circuit level determines the speed of each circuit block. This may be done in a series of steps according to the sublevels. First, the circuit block speed may be expressed in terms of a number of logic block delays. Each logic block delay is the sum of the gate delays within that logic block. Gate delays are determined by the speeds of the transistors that make up the gate and the loads that they must drive. Finally, layout parasitics can be included in the gate delay analysis.

The concern of power analysis at the circuit level is the power consumption of each circuit block. This may also be analyzed according to the sublevels. Power dissipation of the logic blocks and gates can be determined. At the transistor sublevel, the transistor sizes determine power consumption.

Similarly, area analysis at the circuit level determines the area of each circuit block. Area may be evaluated at each of the sublevels also. The circuit block area can be estimated from the number of logic blocks that it contains. The size of each logic block is determined by it gate count. Gate size is determined by the number of transistors in each gate. Transistor sizes are found by consulting the layout.

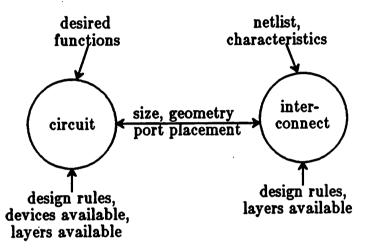

Inputs to the circuit level come from all other levels (Figure 3.3). The process level specifies the available devices, layers, and their parameters. These will partially determine the types of circuits that are used and their speeds. The process also specifies the design rules for the circuit design. These are used by the layout sublevel and influence the area and geometry of the circuits.

Figure 3.3- Circuit Level

Another important set of inputs to the circuit level are the desired functions of the circuits and their characteristics. Custom circuit design proceeds according to the desired circuit functions. Cell libraries can be built for popular functions. Circuit design attempts to satisfy the desired function and its characteristics for each circuit block. If this can not be done compromises are made at other levels.

Other inputs to the circuit design are the desired areas and geometries of each circuit block. The interconnect scheme leaves empty areas that the circuit blocks must fit into. The order of interconnect wires will also affect the placement of the terminals for each circuit block. Loading due to interconnects and other circuit blocks at their terminations, is another input to circuit design. Circuits must be designed to drive these loads at the speeds as specified by the desired function input.

Outputs from the circuit level are used by all other levels also. Circuit design will result in a list of circuits that are available for use in the processor and their characteristics. A knowledge of these is important to the higher design levels.

The internal delays of each circuit block is another output of circuit design. These delays are used in critical path analysis at the functional block level. The power consumption output is used to predict the total power required by the processor.

The area and geometry of circuit blocks is another output of circuit design. The circuit block areas are used by the functional block level to estimate the processor size. Interconnects must be routed around the circuit blocks and therefore use the area and geometry output of circuit design. The port placement on each circuit block is another output of circuit design used by the interconnect design. Another set of outputs are the loads of the input ports of each circuit block. Loads must be taken into consideration when designing other circuit blocks and their interconnects.

A final output is a set of desired parameters, layers, and devices. To meet certain aspects, such as speed or power, of the desired function input, various process parameters, layers, and devices are important.

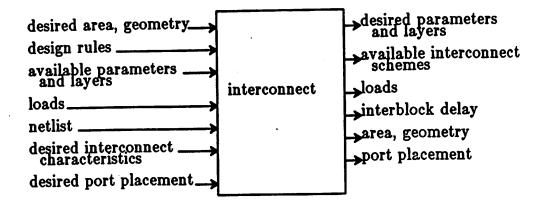

# 4. Interconnect Level

Communication between the circuit blocks of a processor is accomplished through the interconnects of the processor. Interconnects connect the circuit block inputs and outputs according to the scheme that was proposed by the functional block design level. Design at the interconnect level results in a layout realization of all required interconnects.

Speed analysis at the interconnect level is concerned with interconnect delays. Power analysis estimates the a.c. power required to drive the interconnect load at the given clock rate. Interconnect areas are also determined by analysis at the interconnect level.

The interconnect level also has inputs from all other levels (Figure 3.4). One important characteristic of the interconnects is the area that they occupy. The circuit blocks have certain sizes and geometries, and the interconnects must fit around them. Thus, one set of inputs to interconnect design are the sizes and geometries of the circuit blocks. The design rules are another input to the interconnect level. The dimensions specified for interconnect levels by the design rules, are a major factor in determining the area occupied by the interconnects. The available layers for the interconnects are another set of inputs to this level that will affect their area.

Figure 3.4- Interconnect Level

Speed is another important characteristic of the interconnections. Their speed is affected by such things as the resistance and capacitance of the interconnect layers. Therefore, the process parameters must be an input to the interconnect design. Another input that will affect the speed of the connection, is the load at the termination of the connection. This load partially limits the maximum speed of the interconnect.

The netlist for the processor is another input to the interconnect level. The netlist specifies all terminals that are to be connected together. Another set of inputs are the desired characteristics of the interconnects. Design at the higher levels may benefit if various characteristics are available. The placement of the ports to the circuit blocks is another input to the interconnect design. Ideally, the order of the ports should match the order of the interconnect lines.

Outputs of the interconnect level are used by all other levels. From a knowledge of the higher design levels, the interconnect level may generate an output of desired process parameters and layers. The interconnect design level also generates a set of available interconnect schemes for use by the higher levels. It does this from inputs that were generated by lower levels. Examples of things that affect interconnect schemes are double level metal and silicides.

Another set of outputs are the loads of the interconnects. The circuit blocks must have the capability to drive the interconnect loads at the desired speeds. Interconnect loading also contributes to the a.c. power consumption of the processor.

The interblock delay is another output. It is used to analyze the speed of a proposed functional block design.

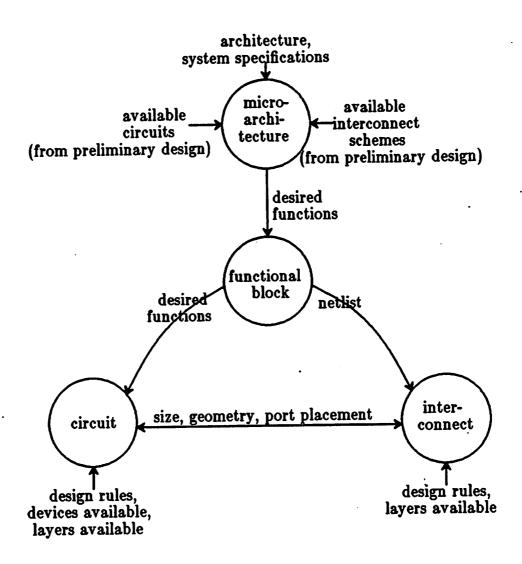

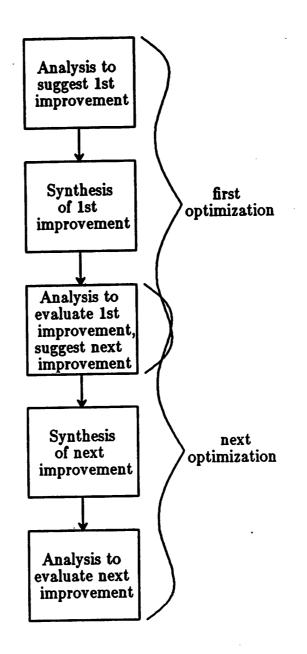

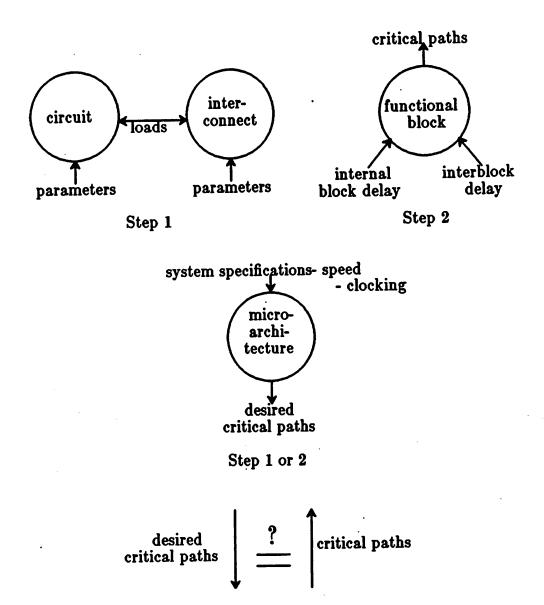

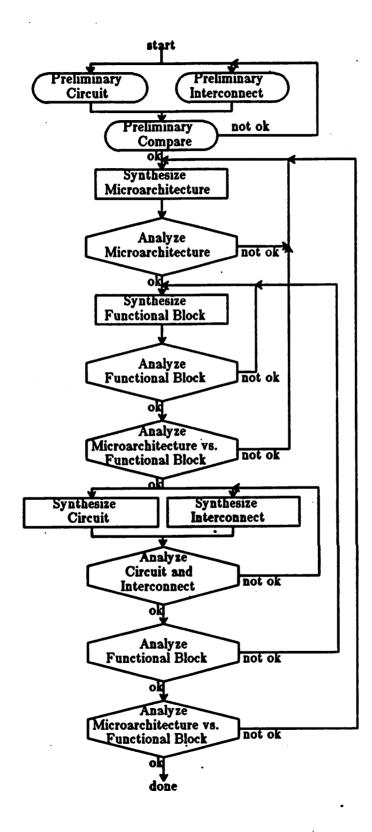

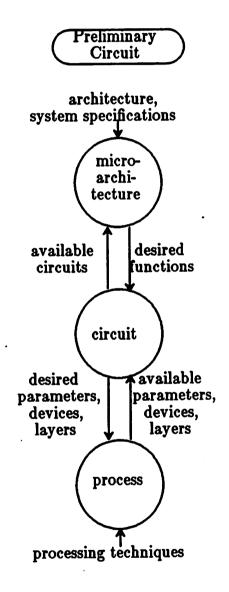

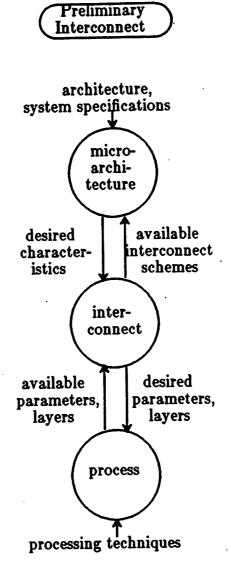

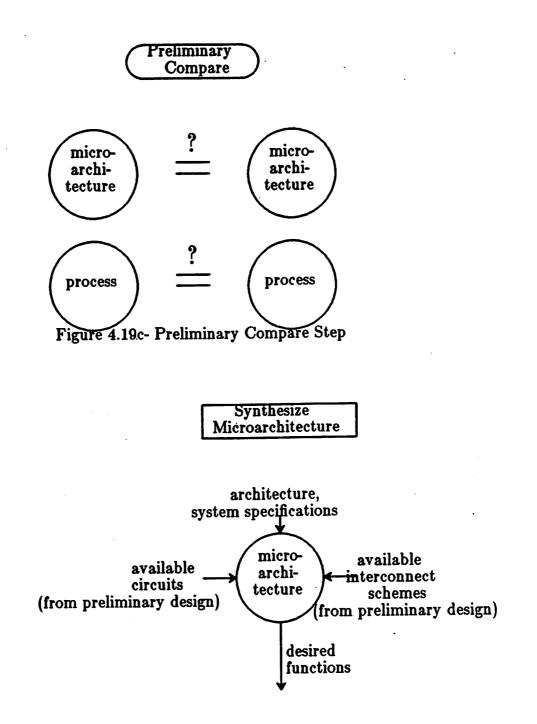

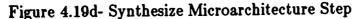

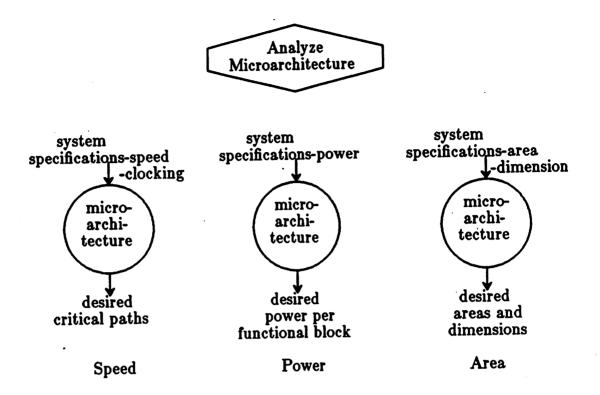

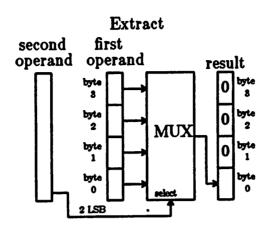

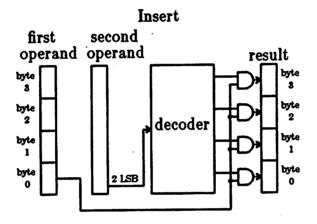

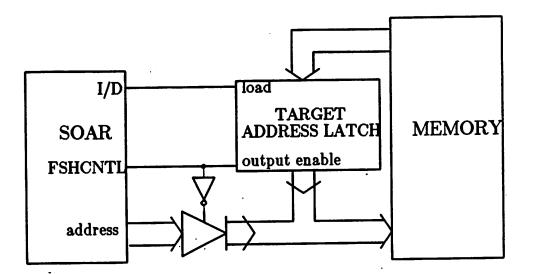

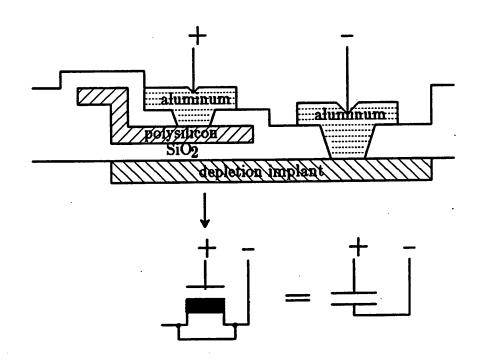

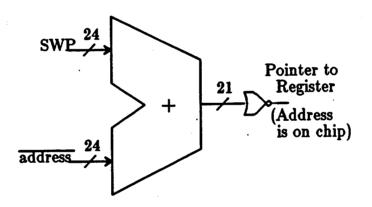

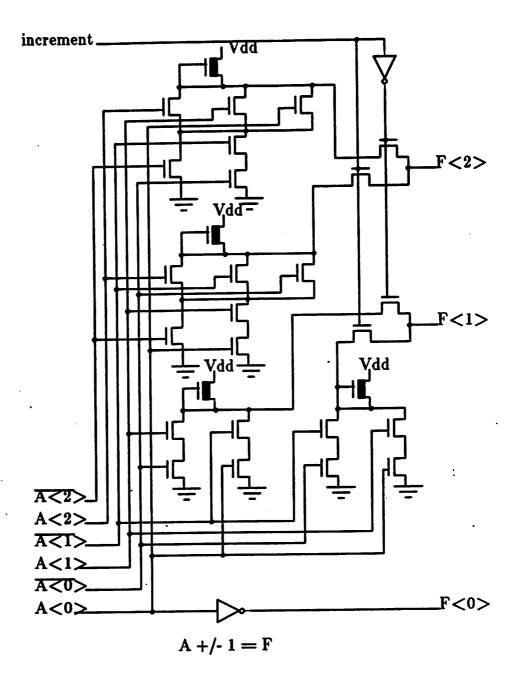

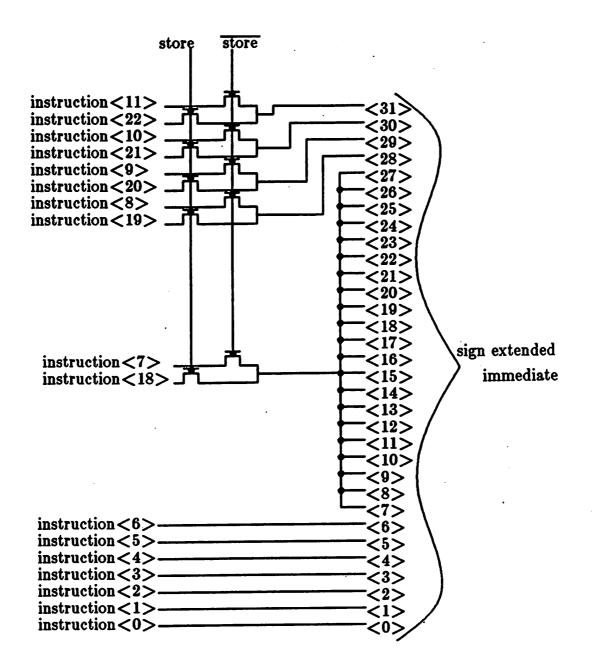

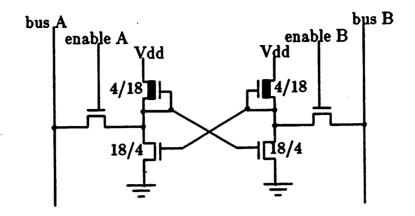

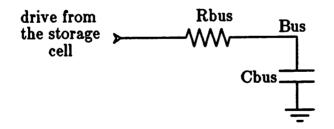

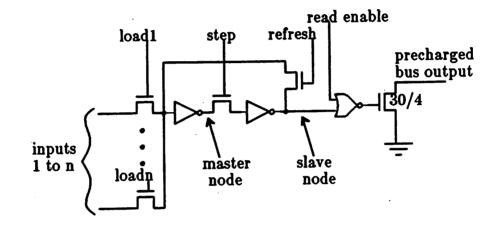

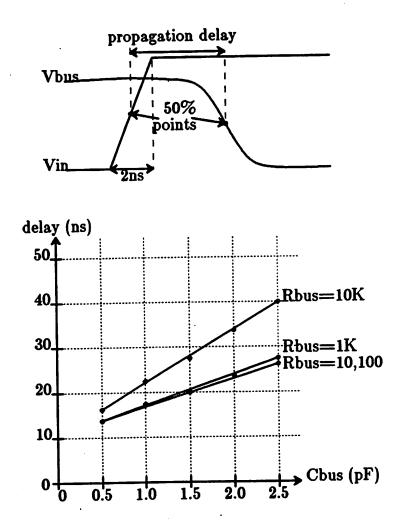

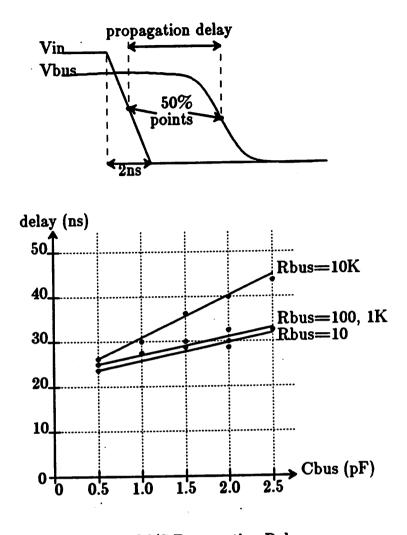

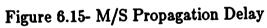

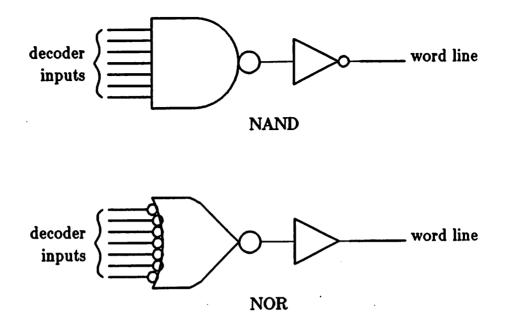

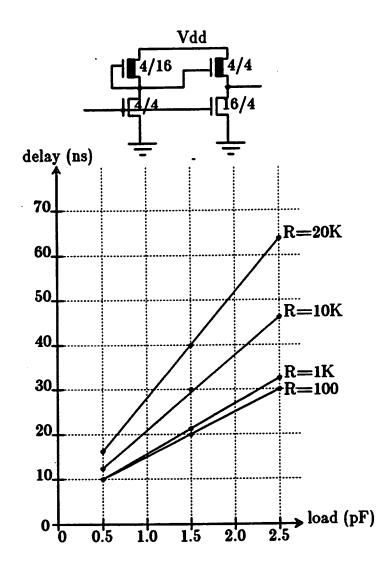

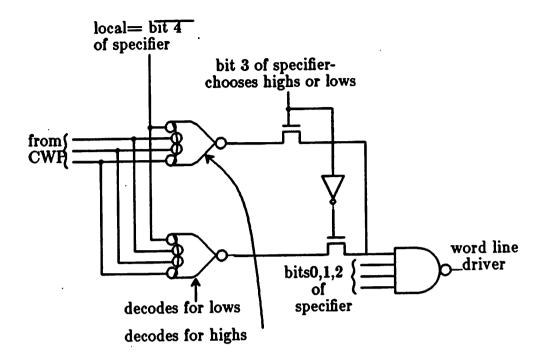

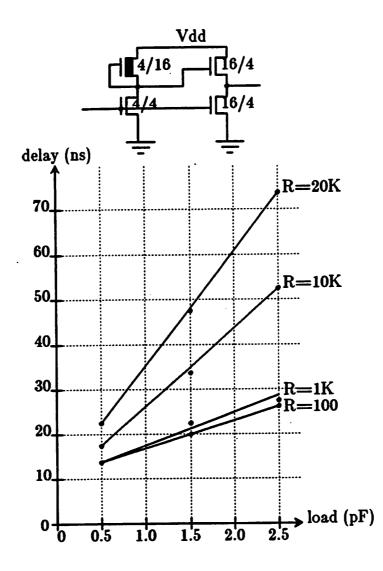

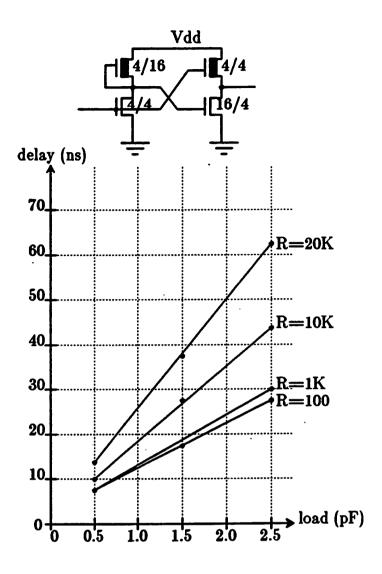

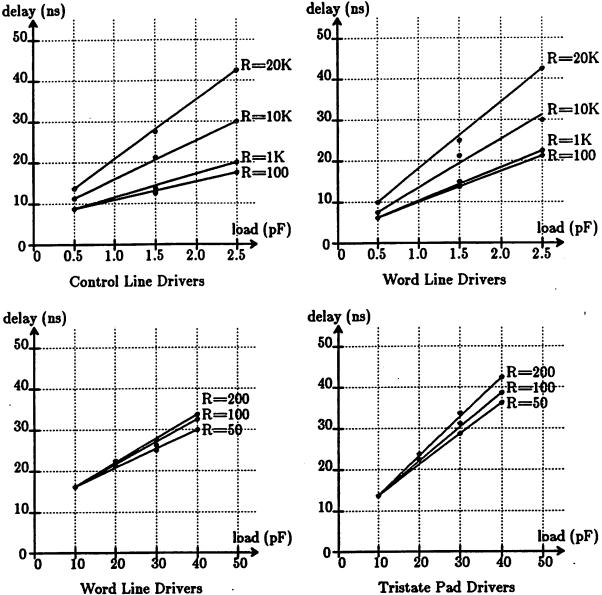

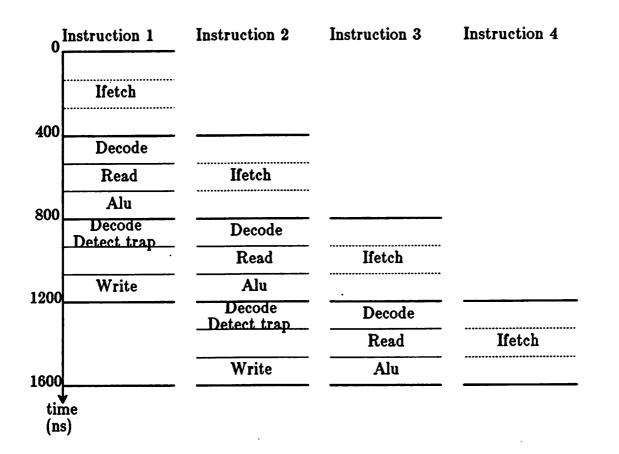

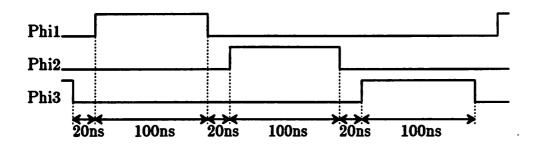

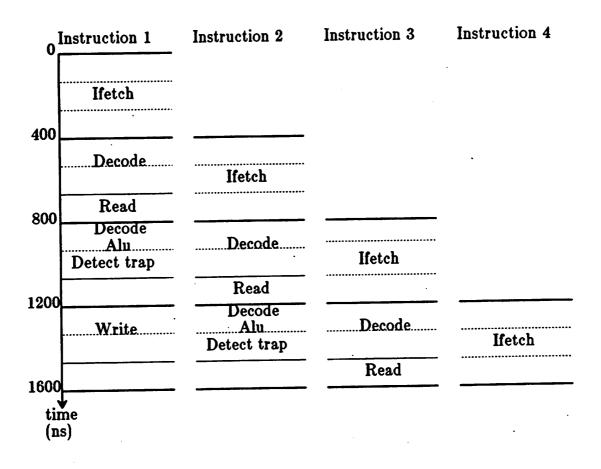

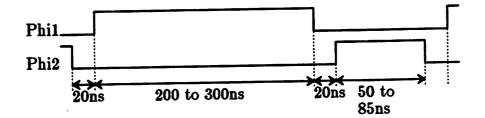

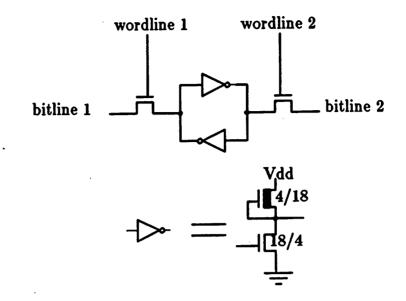

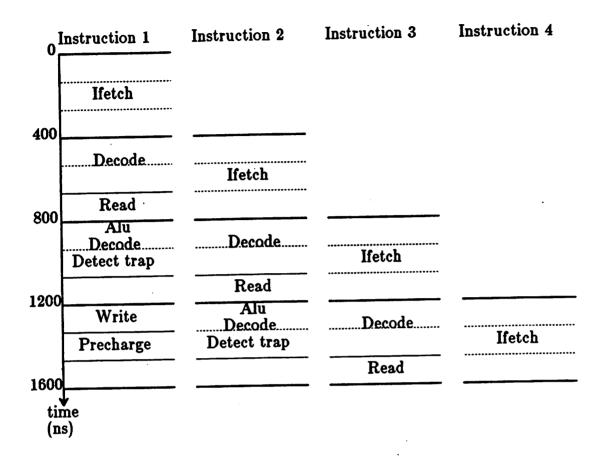

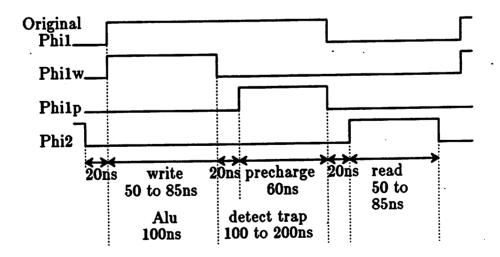

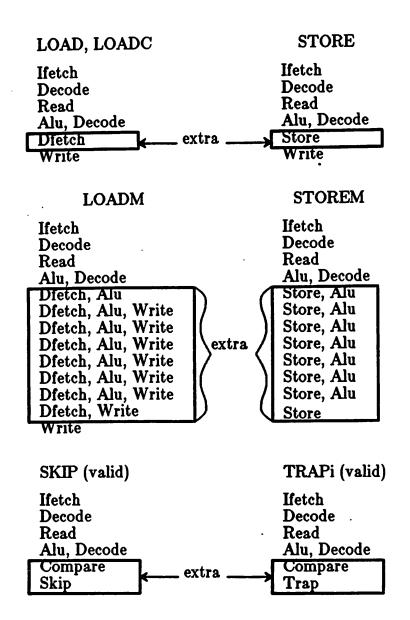

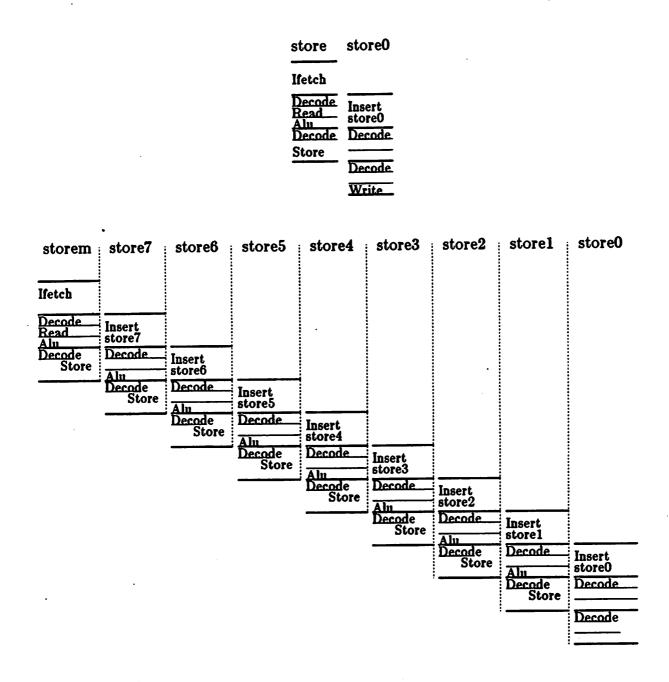

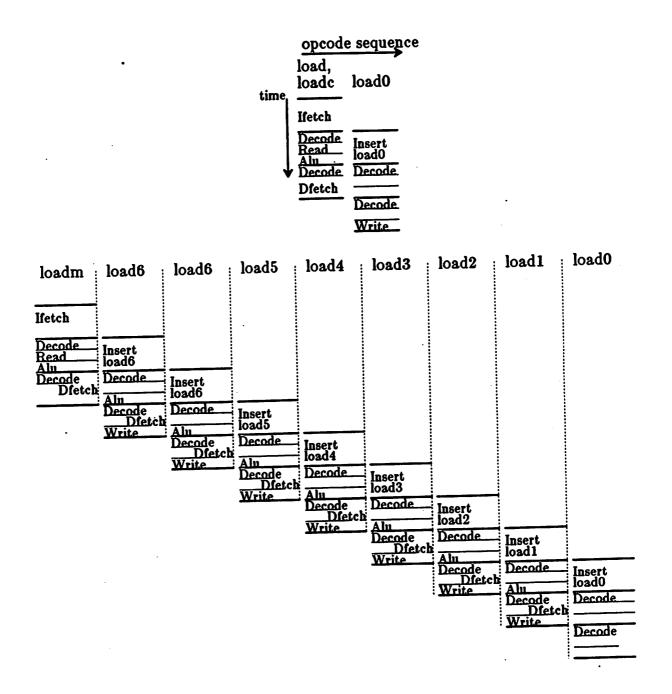

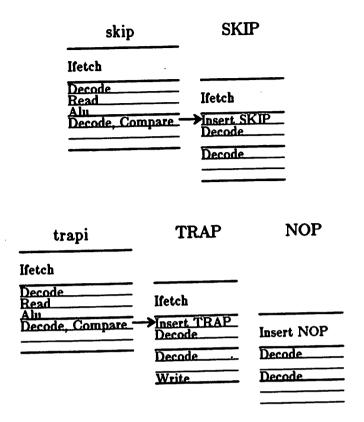

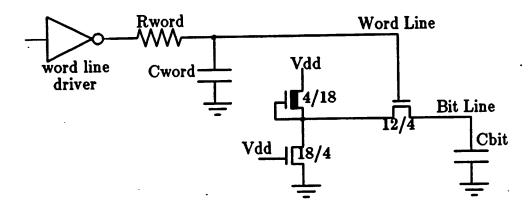

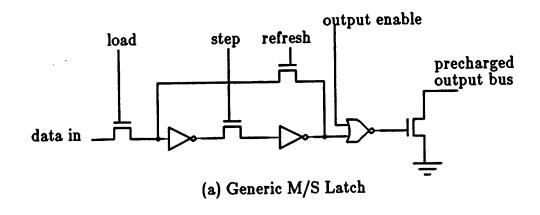

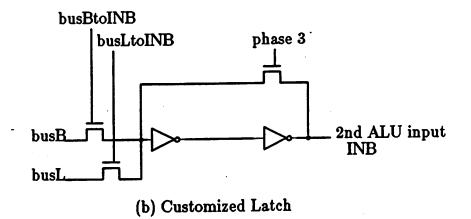

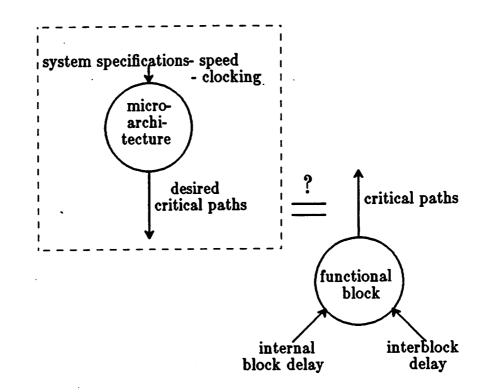

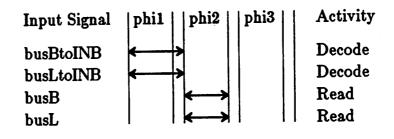

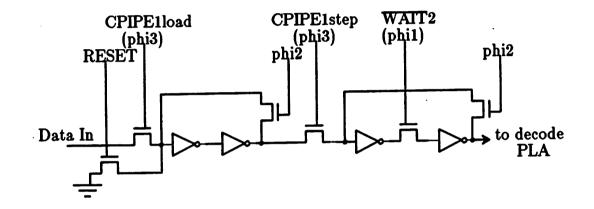

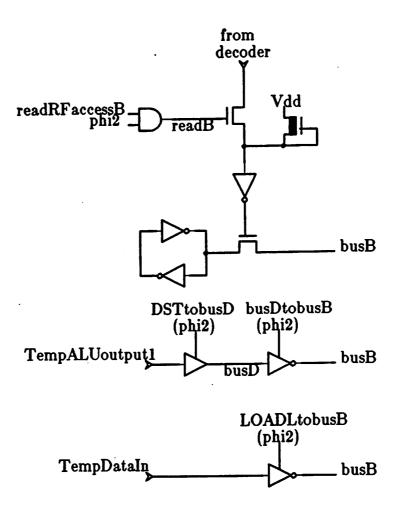

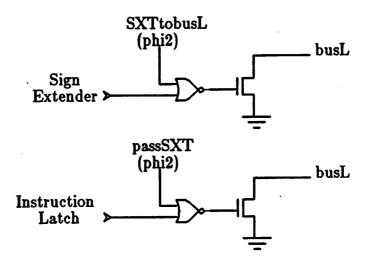

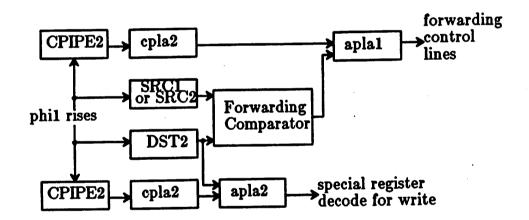

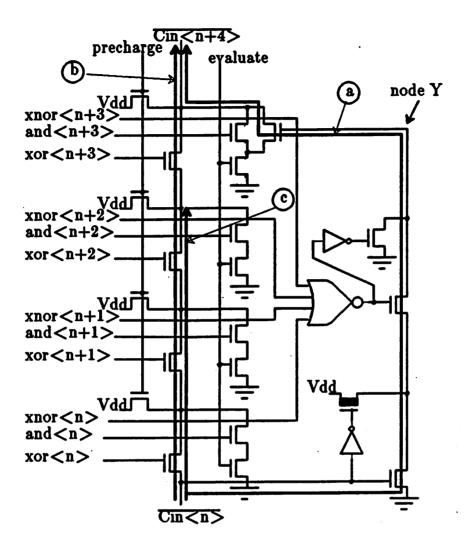

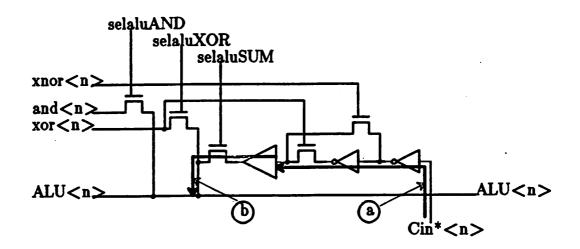

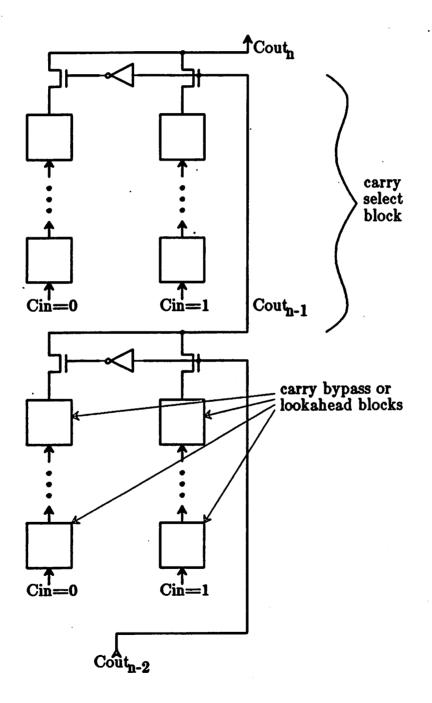

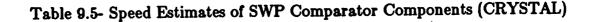

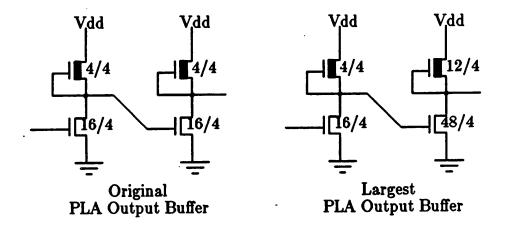

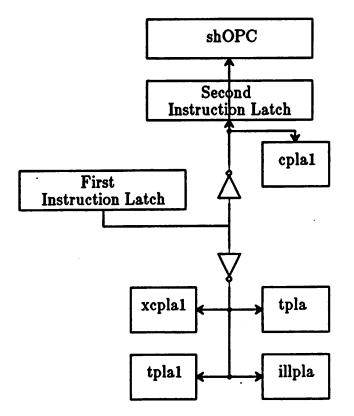

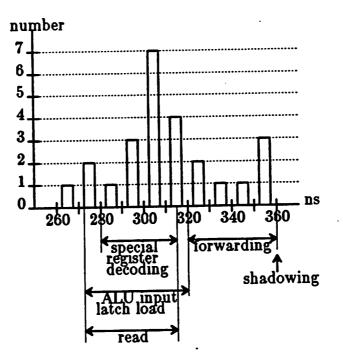

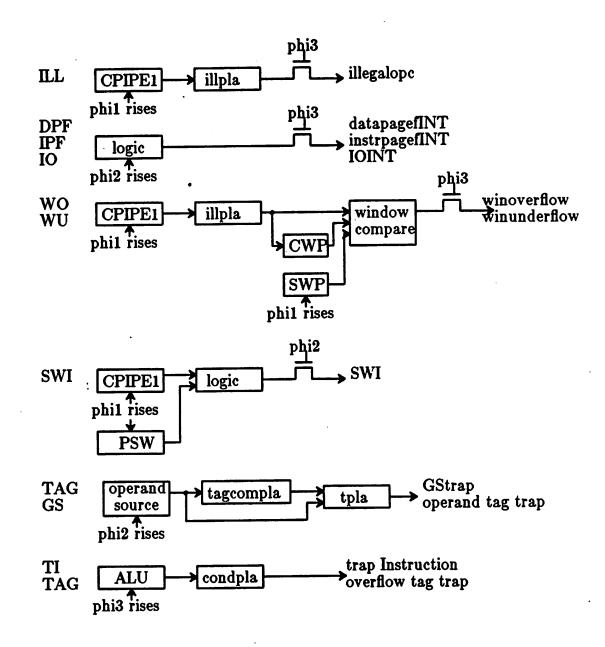

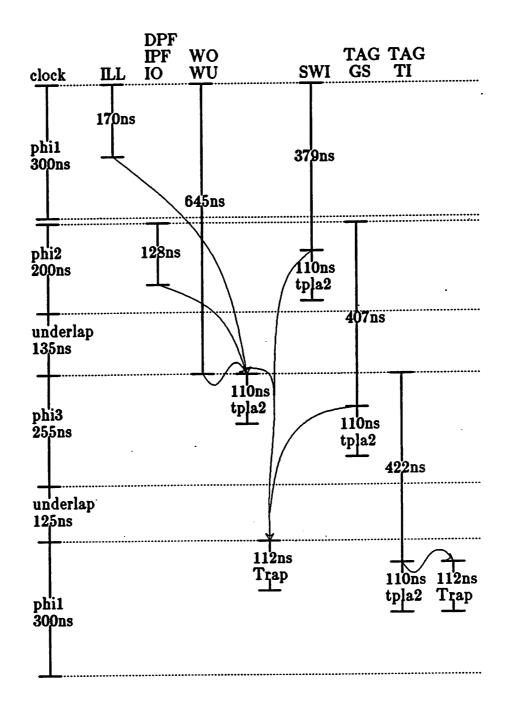

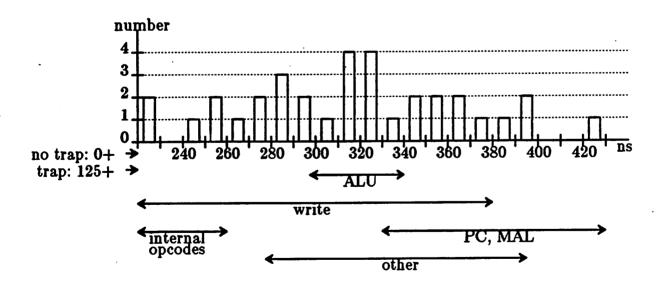

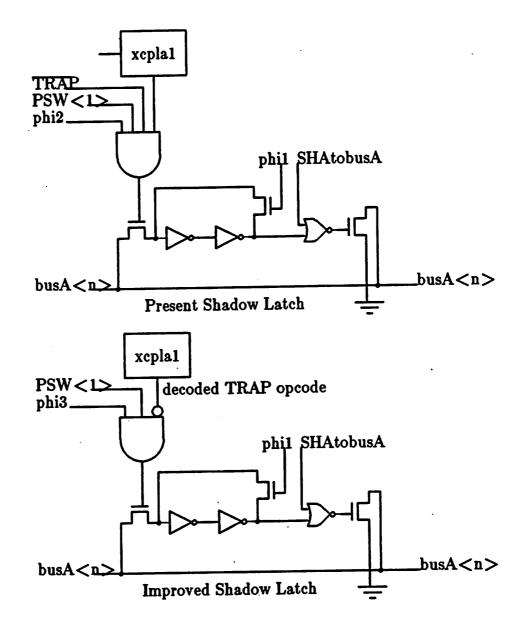

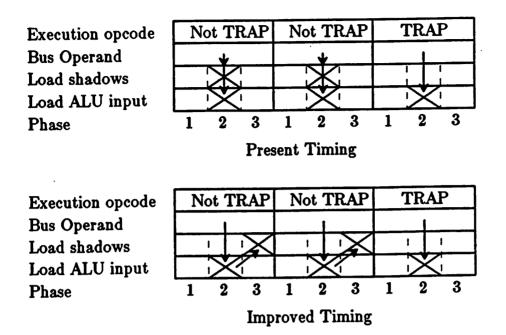

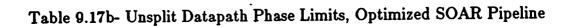

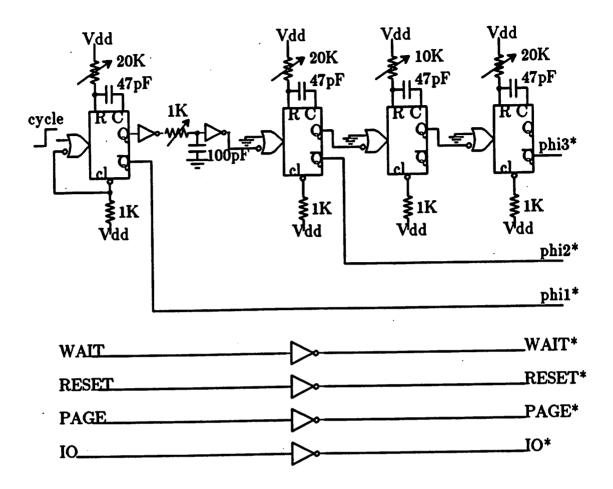

The area and geometry are other outputs of the interconnect level. Interconnects can occupy a significant area. This must be taken into consideration when estimating the chip size. The interconnect area and geometry output is also used when doing layout of the circuit blocks in order to leave a minimum of wasted space.