# Corner-based Geometric Layout Rule Checking for VLSI Circuits

Ву

Michael Helmut Arnold

B.S. (Michigan State University) 1978

# DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of DOCTOR OF PHILOSOPHY

in

Computer Science

in the

GRADUATE DIVISION

OF THE

UNIVERSITY OF CALIFORNIA, BERKELEY

1

| Approved: | Chairman Linde. | 0/3/85<br>Date |

|-----------|-----------------|----------------|

|           | Meall Punhet    |                |

# Corner-Based Geometric Layout Rule Checking for VLSI Circuits

Copyright © 1985 by Michael Helmut Arnold

# CORNER-BASED GEOMETRIC LAYOUT RULE CHECKING FOR VLSI CIRCUITS

Michael Helmut Arnold

#### Abstract

Layout rule checking is traditionally done through sequences of region-operations, and a few experimental systems use pixel-based processing. This dissertation examines these approaches in detail, and then proposes corner-based checking as an efficient and flexible alternative. In corner-based checking contextual rules, specifying conditions at corners matching patterns, are applied to the design. A rule compiler is used to convert the user-readable rule description to an efficient, indexed, internal form prior to checking. Hierarchical and incremental check algorithms that eliminate redundant checking are also developed. These algorithms greatly enhance the effectiveness of layout rule checking. Measurements from several systems implementing corner-based checking and the hierarchical and incremental algorithms demonstrate their viability and effectiveness.

Corner-based checking has several advantages. First, it checks all rules in a single pass over the data. This avoids the I/O bottleneck that is common in the multi-pass region-operation systems. The rule-based nature of corner-based checking provides inherent flexibility: variants of design rules that would require the coding of new operations in region-operation systems can often be accommodated by modifying the rule specification. Corner-based rules also permit directional context, which is notoriously difficult to establish in region-operation systems. Finally corner-based systems associate violations with points in a design rather than edges or regions. The consequent simplicity of piecewise processing facilitates hierarchical and incremental checking.

The work described here was supported in part by the Defense Advanced Research Projects Agency (DOD), ARPA Order No. 3803, monitored by the Naval Electronic System Command under Contract No. N00039-78-G-0013-0004.

|   | • | ,- <del>-</del> |

|---|---|-----------------|

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

| , |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

| · |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

| • |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

| • |   |                 |

|   |   |                 |

| • |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

|   |   |                 |

### Acknowledgments

I would like to thank Ann Lanfri, Chong Lee, and Bill Weir of MCV and Metheus Corporations for their continuing cooperation and support in my research. I am also in debt to Greg Cardell, Myron White and especially Keith Billings for their ideas and work on Leo and Leo45, the Metheus corner-based systems. I would also like to thank Jack Vernetti (for his help with the plots) and all the others who have helped make my association with Metheus productive and enjoyable.

I would like to thank Howard Landman and Stephen Pope for their help and comments with the development of the Lyra rulesets, and the many others at Berkeley and in industry who have enriched my research by their attention.

This research was funded, in part, by Defense Advanced Research Projects Agency.

Last, but not least, I am grateful to my research advisor, John Ousterhout. The corner-based idea was born out of a sequence of discussions with John in which I volunteered half-baked ideas and John shot them down (John is a crack shot). In addition to eventually leading to this dissertation, these meetings taught me the value of simplicity and precision in computer science. This is the single most valuable lesson I learned while at Berkeley, and I know it will continue to bear fruit in the years to come.

# Table of Contents

| C | HAP'  | TER 1. Introduction                                              | 1  |

|---|-------|------------------------------------------------------------------|----|

|   | 1.1   | Design Rules and Design Rule Checking                            | 1  |

|   | 1.2   | Scope of My Research                                             | 6  |

|   | 1.3   | Ideas in My Research                                             | 9  |

|   | 1.4   | Outline                                                          | 12 |

| C | HAP   | TER 2. The Nature of Design Rules                                | 13 |

|   | 2.1   | Introduction                                                     | 13 |

|   | 2.2   | Integrated Circuit Fabrication and the Origin of Design Rules    | 16 |

|   | 2.3   | The Form of Design Rules                                         | 22 |

|   | 2.4   | Automatic Design Rule Checking and Design Methodology            | 26 |

|   | 2.4.1 | The Spectrum of Methodologies                                    | 29 |

|   | 2.4.2 | Design Rules and Other Constraints Employed by the Methodologies | 30 |

|   | 2.4.3 | The Need for an Automatic Topo-Tolerance Checking Capability     | 30 |

|   | 2.5   | Summary                                                          | 33 |

|   | 2.6   | References                                                       | 34 |

| C | HAP'  | TER 3. The Region-Operation Approach                             | 36 |

|   | 3.1   | Introduction                                                     | 36 |

|   | 3.2   | Mask Artwork and Mask Artwork Functions                          | 37 |

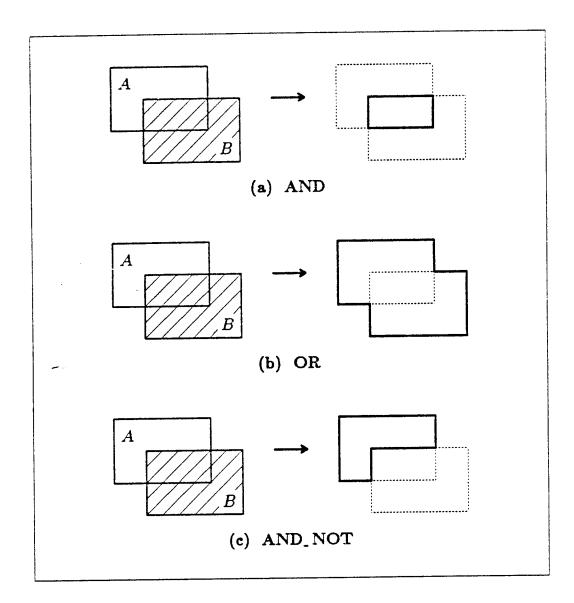

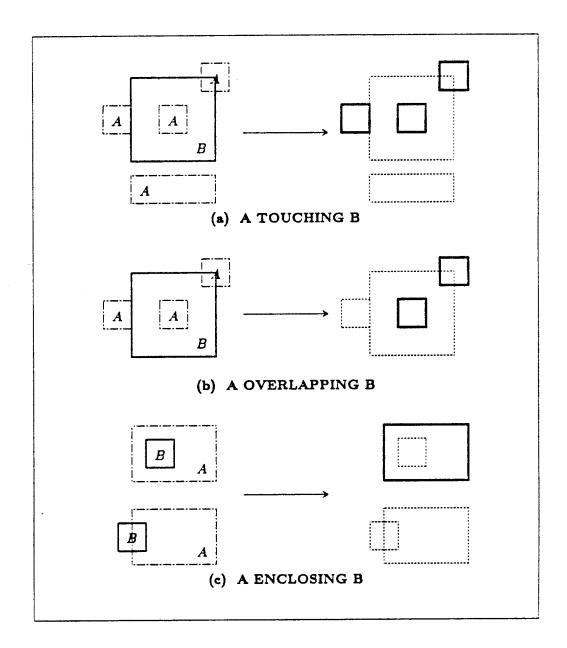

|   | 3.3   | Region Operations                                                | 38 |

|   | 3.3.1 | Tolerance Operations                                             | 40 |

|   | Ţ     | Boolean Operations                                               | 46 |

|   |       | Topological Operations                                           | 46 |

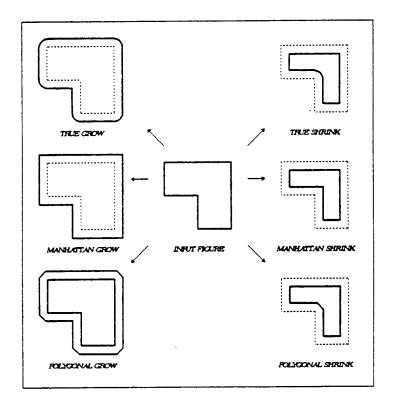

|   | 3.3.4 | Sizing Operations                              | 49 |

|---|-------|------------------------------------------------|----|

|   | 3.3.5 | Connectivity and Tag Operations                | 51 |

|   | 3.3.6 | Area, Length and Perimeter Checks              | 53 |

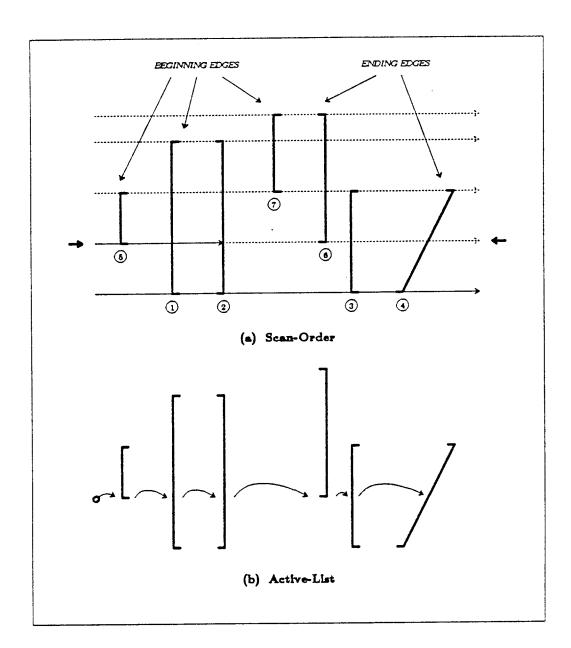

|   | 3.4   | Scanline Implementation of Region Operations   | 53 |

|   | 3.5   | Pros and Cons of the Region-Operation Approach | 56 |

|   | 3.6   | Summary                                        | 60 |

|   | 3.7   | References                                     | 61 |

| C | HAPT  | TER 4. Survey of Non-Corner-Based DRC Systems  | 64 |

|   | 4.1   | Introduction                                   | 64 |

|   | 4.2   | Region-Operation Systems                       | 65 |

|   | 4.2.1 | Baird's System                                 | 66 |

| _ | 4.2.2 | Lauther's Algorithm                            | 67 |

|   | 4.2.3 | Haken's System                                 | 67 |

|   | 4.2.4 | Hitachi                                        | 68 |

|   | 4.2.5 | NCA                                            | 68 |

|   | 4.2.6 | Phoenix Data Systems                           | 69 |

|   | 4.2.7 | ECAD                                           | 69 |

|   | 4.2.8 | Other Systems                                  | 69 |

|   | 4.3   | Pixel Systems                                  | 69 |

|   | 4.3.1 | Baker's System                                 | 71 |

|   | 4.3.2 | Seiler's System                                | 72 |

|   | 4.3.3 | Mudge's Approach                               | 74 |

|   | 4.3.4 | Eustace's System                               | 75 |

|   | 435   | Zech's Architecture                            | 77 |

|   |       |                                                | 77  |

|---|-------|------------------------------------------------|-----|

|   | 4.4   | Summary                                        | 1 ( |

|   | 4.5   | References                                     | 80  |

| C | HAPT  | TER 5. The Corner-Based Approach               | 82  |

|   | 5.1   | Introduction                                   | 82  |

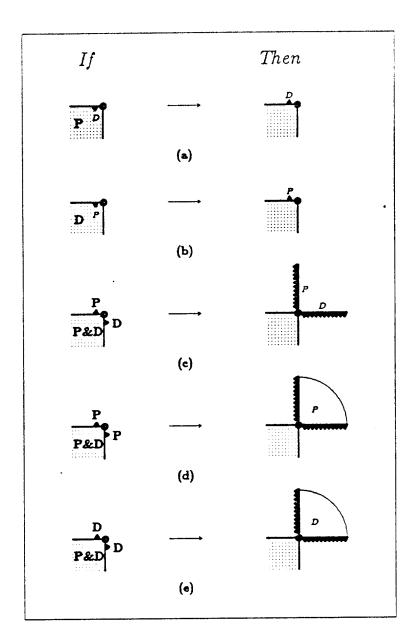

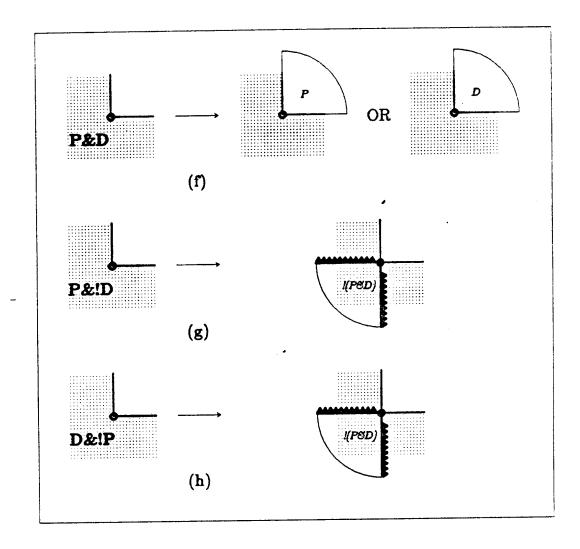

|   | 5.2   | Unconditional Rules                            | 86  |

|   | 5.3   | Geometric Conditional Rules                    | 97  |

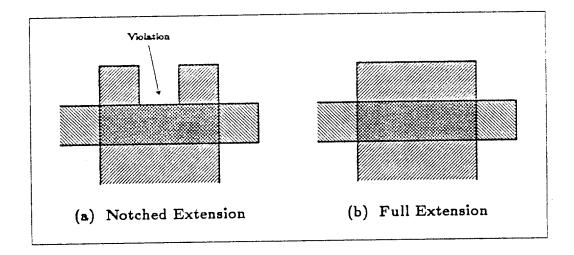

|   | 5.3.1 | Transistor Extension Rule                      | 98  |

|   | 5.3.2 | Reflection Rule                                | 104 |

|   | 5.4   | Nongeometric Conditional Rules                 | 107 |

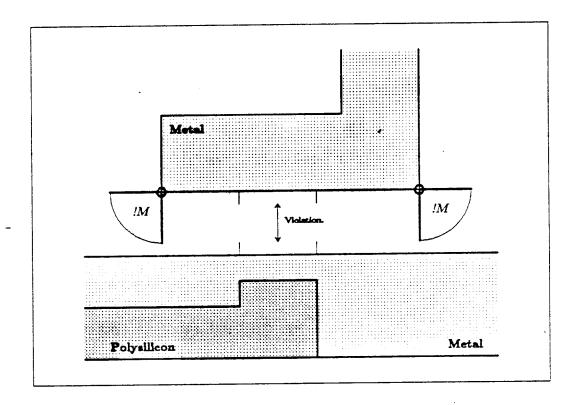

|   | 5.4.1 | Internode Spacing                              | 109 |

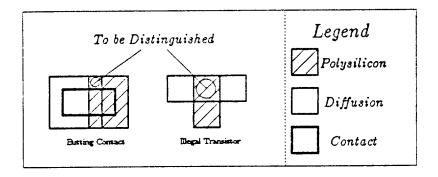

|   | 5.4.2 | Buried to Unrelated Polysilicon Spacing        | 109 |

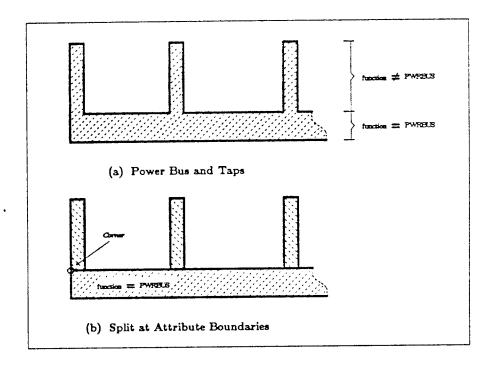

|   | 5.4.3 | Power and Ground Bus Width                     | 111 |

|   | 5.5   | Summary                                        | 112 |

| C | HAP'  | TER 6. Implementation of Corner-Based Checking | 116 |

|   | 6.1   | Introduction                                   | 116 |

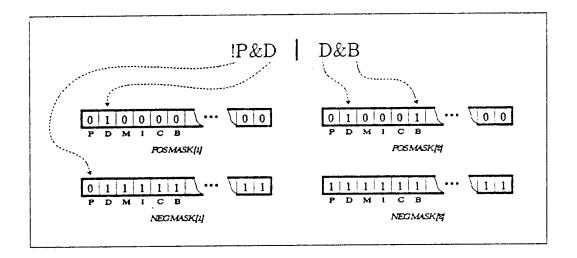

|   | 6.2   | Internal Rule Representation                   | 117 |

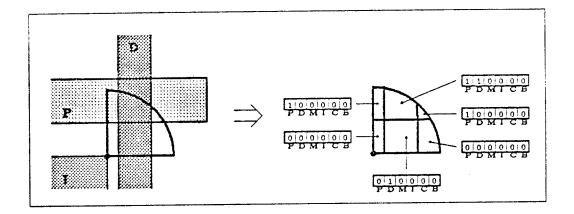

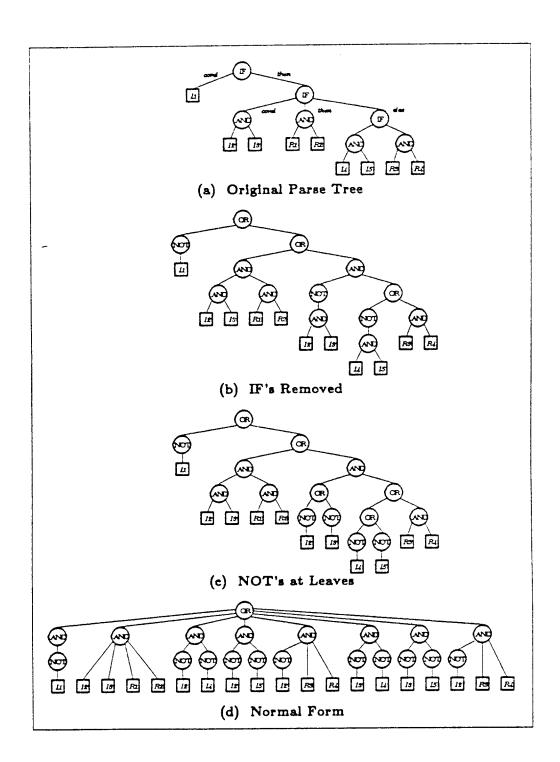

|   | 6.2.1 | Disjunctive Normal Form                        | 118 |

|   | 6.2.2 | Layer Expressions                              | 119 |

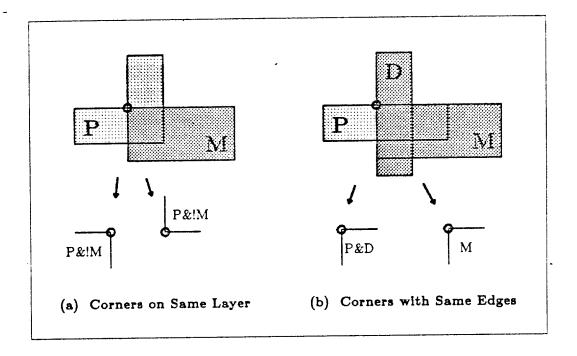

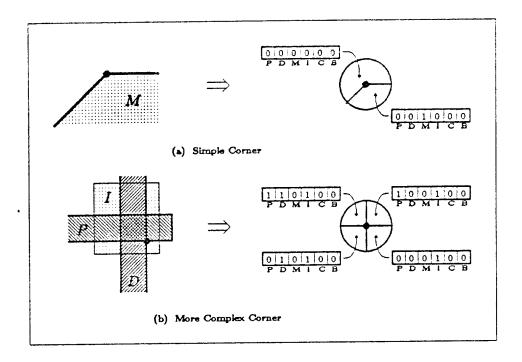

|   | 6.2.3 | Corners                                        | 120 |

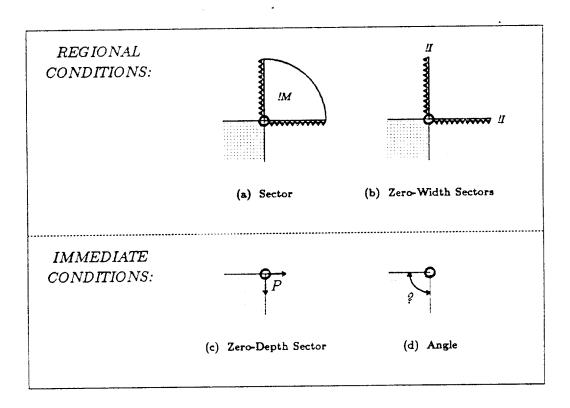

|   | 6.2.4 | Conditions                                     | 121 |

|   | 6.2.5 | Condition Expressions                          | 123 |

|   | 6.3   | Checking Algorithm                             | 126 |

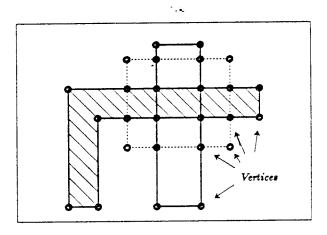

|   | 6.3.1 | Corner Detection                               | 126 |

|   | 6.3.2 | Condition Evaluation                           | 130 |

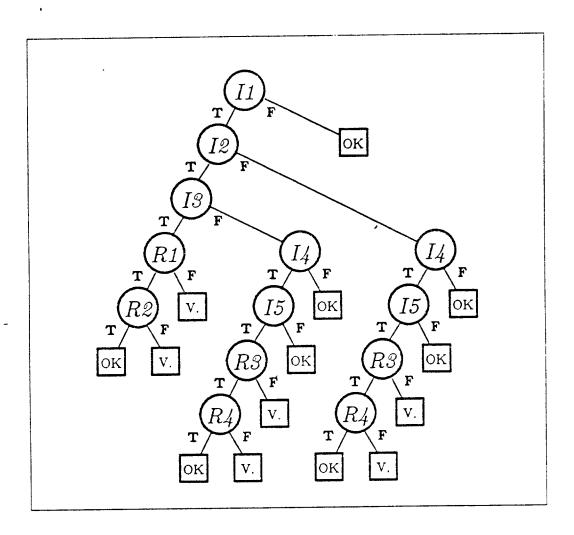

|   | 6.4   | The Rule Compiler                     | 131 |

|---|-------|---------------------------------------|-----|

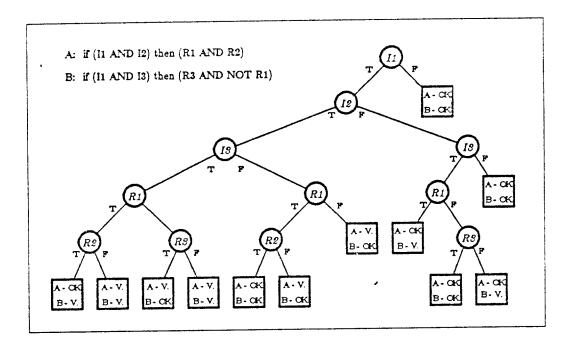

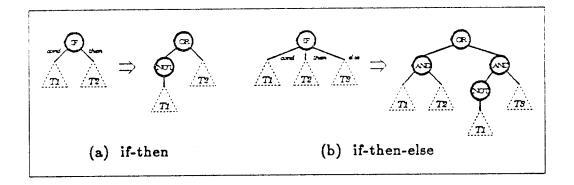

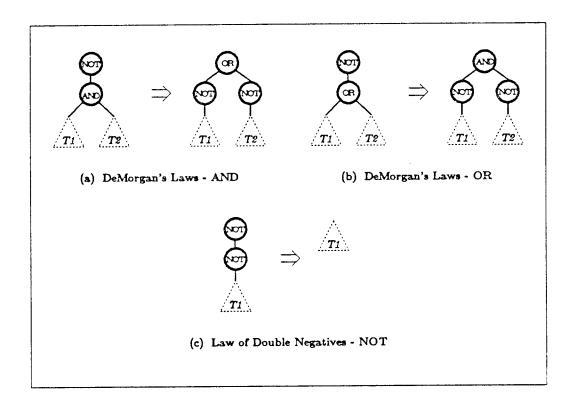

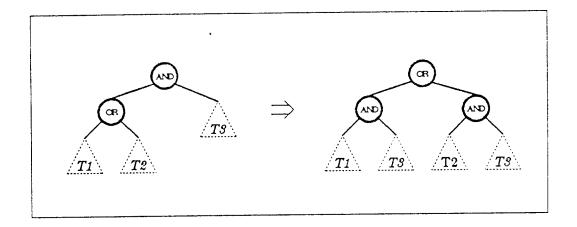

|   | 6.4.1 | Conversion to Disjunctive Normal Form | 133 |

|   | 6.4.2 | Generation of Relevant-Layers Table   | 136 |

|   | 6.4.3 | Conversion to Decision-Tree Form      | 137 |

|   | 6.5   | Summary                               | 138 |

|   | 6.6   | References                            | 140 |

| C | HAP   | TER 7. Survey of Corner-Based Systems | 142 |

|   | 7.1   | Introduction                          | 142 |

|   | 7.2   | Lyra                                  | 142 |

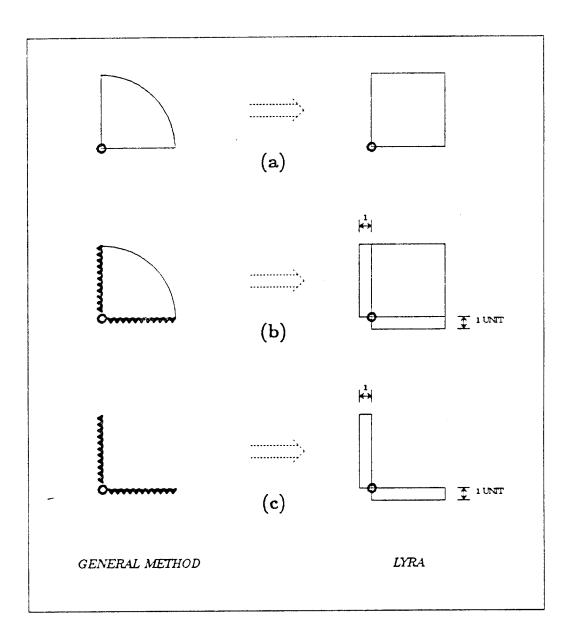

|   | 7.2.1 | Features and Restrictions             | 143 |

|   | 7.2.2 | Implementation                        | 146 |

|   | 7.3   | Mart                                  | 148 |

|   | 7.3.1 | Features and Restrictions             | 149 |

|   | 7.3.2 | Implementation                        | 150 |

| _ | 7.3.3 | Rule Checking Capabilities            | 151 |

|   | 7.4   | Leo45                                 | 151 |

|   | 7.4.1 | Features and Restrictions             | 152 |

|   | 7.4.2 | Implementation                        | 152 |

|   | 7.4.3 | Rule Checking Capabilities            | 153 |

|   | 7.5   | Magic                                 | 154 |

|   | 7.5.1 | Features and Restrictions             | 154 |

|   | 7.5.2 | Rule Checking Capabilities            | 156 |

|   | 7.6   | Intel DRC                             | 156 |

|   | 7.7   | Summary                               | 156 |

|    | 7.8    | References                                          | 157 |

|----|--------|-----------------------------------------------------|-----|

| C: | нарт   | TER 8. Hierarchical and Incremental Checking        | 158 |

|    | 8.1    | Introduction                                        | 158 |

|    | 8.2    | Hierarchical Checking - Background                  | 159 |

|    | 8.2.1  | Whitney's Filter                                    | 161 |

|    | 8.2.2  | Scheffer's Strict Hierarchy                         | 162 |

|    | 8.2.3  | Newell and Fitzpatrick's Derived Disjoint Hierarchy | 166 |

|    | 8.3    | Direct Processing of Unrestricted Hierarchy         | 167 |

|    | 8.4    | Incremental Checking                                | 171 |

|    | 8.4.1  | Leo45                                               | 172 |

|    | 8.4.2  | Magic 174                                           | 174 |

|    | 8.5    | Summary 175                                         | 175 |

|    | 8.6    | References 176                                      | 176 |

| M  | leasur | ements                                              | 178 |

|    | 9.1    | Introduction                                        | 178 |

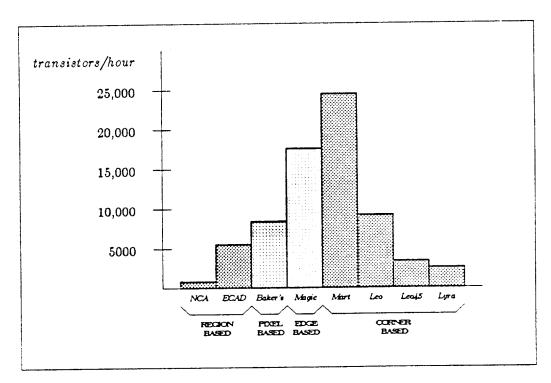

|    | 9.2    | Raw Performance                                     | 179 |

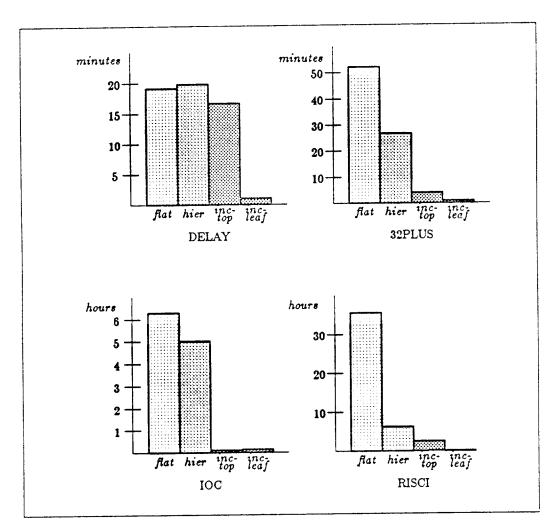

| _  | 9.3    | Hierarchical and Incremental Checking               | 181 |

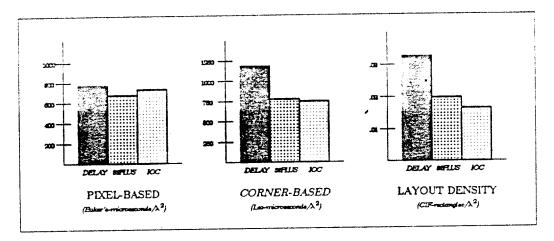

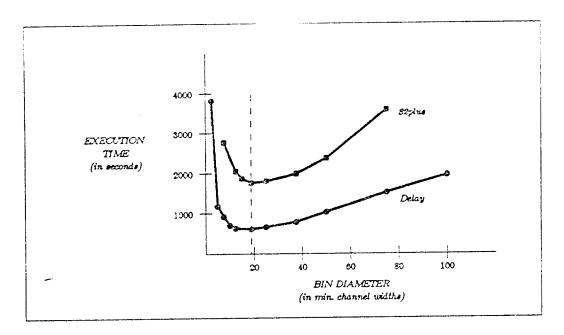

|    | 9.4    | Sensitivity of Check Rate to Design Density         | 183 |

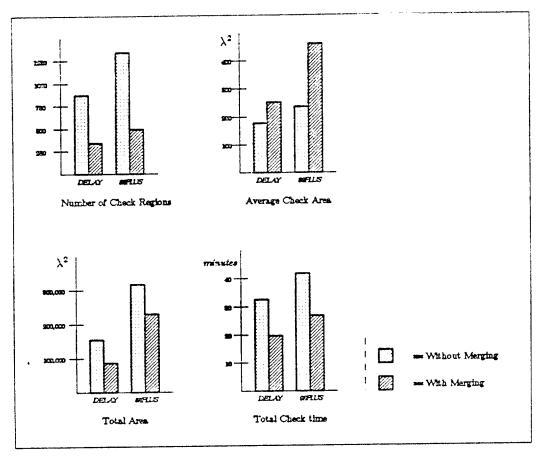

|    | 9.5    | Sensitivity to Data Organization                    | 185 |

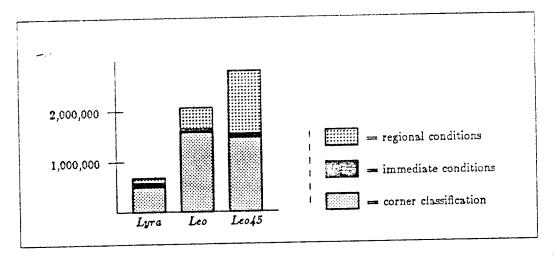

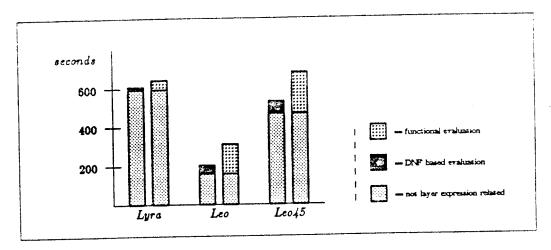

|    | 9.6    | Layer Expression Evaluation                         | 185 |

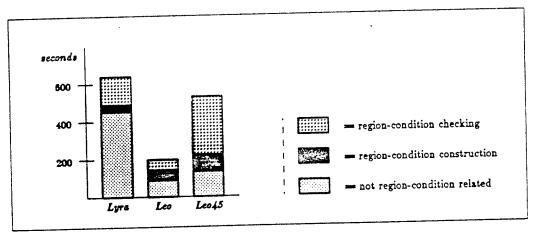

|    | 9.7    | Region Condition Processing                         | 188 |

|    | 9.8    | Rule Indexing                                       | 190 |

| (  | CHAP   | TER 10. Summary                                     | 192 |

|    | 10.1   | Previous Approaches to Design Rule Checking         | 192 |

| 10.2                          | The Corner-Based Approach             | 193 |

|-------------------------------|---------------------------------------|-----|

| 10.3                          | Hierarchical and Incremental Checking | 194 |

| 10.4                          | Implementations                       | 195 |

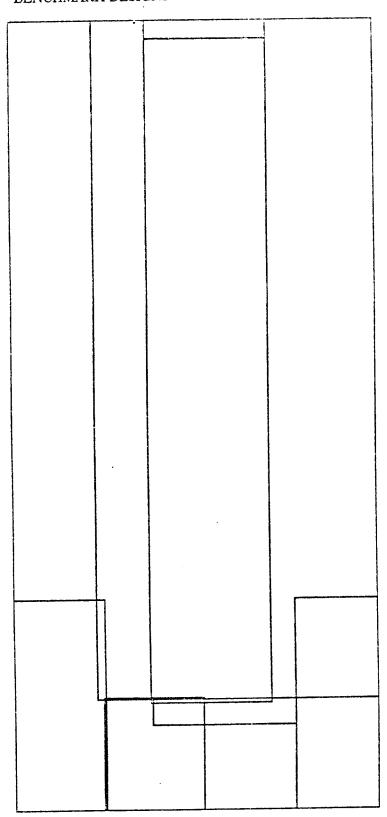

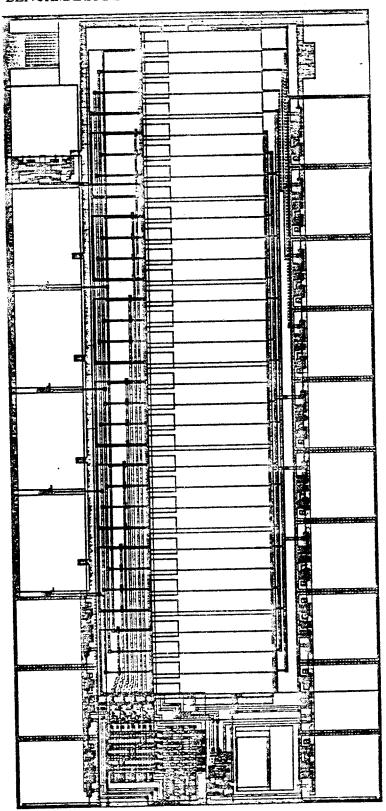

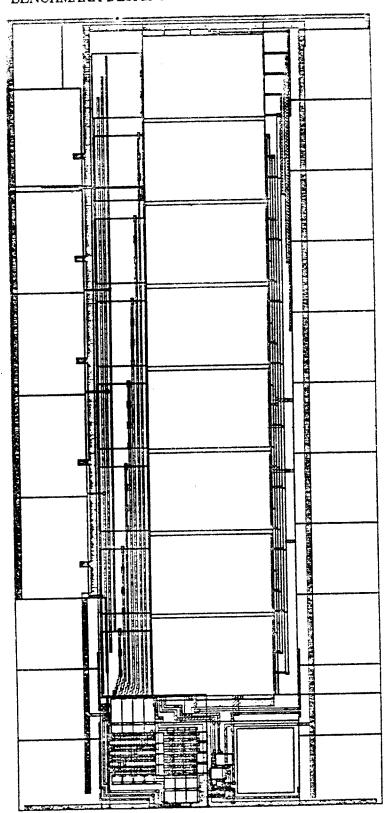

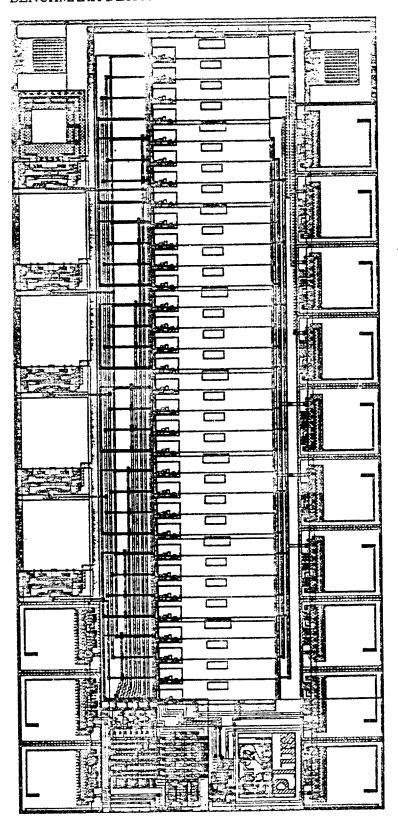

| APPENDIX A. Benchmark Designs |                                       |     |

| A.1                           | Statistics                            | 197 |

| A.2                           | Plots                                 | 198 |

|   |   | ps. ** |

|---|---|--------|

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   | • |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

| - |   |        |

#### CHAPTER 1

#### Introduction

This thesis presents my work in automatic design rule checking for integrated circuits (DRC). It introduces corner-based design rule checking as an efficient and flexible alternative to traditional region-based checking, that is well suited for hierarchical and incremetal checking. A general formalism for corner-based rules is developed that can handle all-angle data and complex conditional rules, and its implementation is considered. A rule compiler is introduced to preprocess the input rule description for efficient processing. Hierarchical and incremental check algorithms are also developed. The identification of violations with points rather than edges or regions, makes corner-based checking particularly well suited for hierarchical and incremental systems. Several corner-based systems, are discussed. In addition, background material on the nature of the design rule checking problem, and other work in the area, is provided.

This chapter gives an overview. It briefly describes design rules and design rule checking, discusses the nature and scope of my research, outlines the most important ideas arising from and/or validated by the research, and outlines the rest of the thesis.

### 1.1. Design Rules and Design Rule Checking

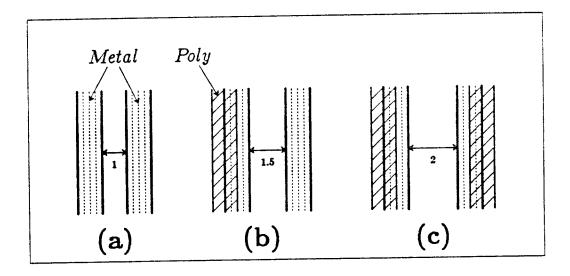

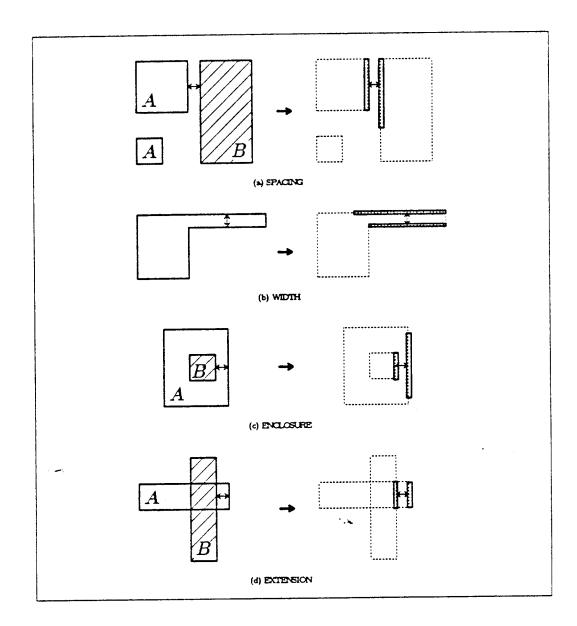

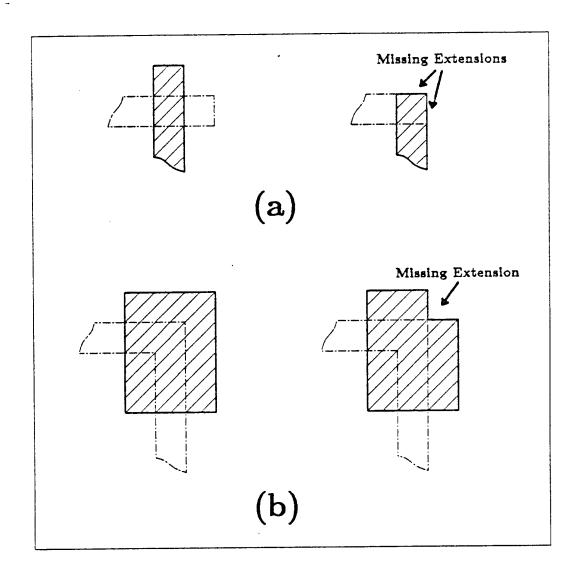

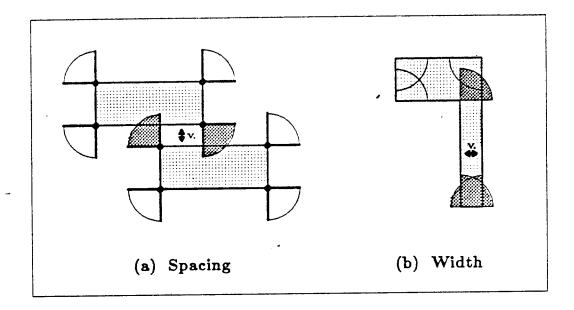

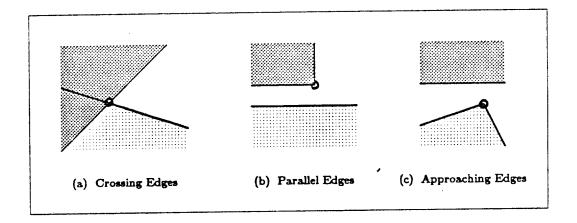

Integrated circuits are specified in terms of geometric mask patterns, or artwork, for each of the layers in the circuit; see Figure 1.1. Design rules specify tolerances on these patterns. Tolerances typically govern width and spacing on conducting lines and various extensions and enclosures on circuit constructs such as transistors and contacts; see Figure 1.2. Design rules stem from the limitations of the circuit fabrication process. They are an abstraction of these limitations that acts as the interface between circuit design and process engineering. They free the circuit designer from the intricate details of the fabrication process

INTRODUCTION

and its limitations: he need only make sure he obeys the design rules.

It is important that design rules are checked automatically. Current designs typically contain one million or more separate geometric figures, making for very tedious and error-prone manual checking. Manual checking is certain to result in missed design rule violations. Such violations necessitate expensive and time consuming additional fabrication cycles. In addition it is very difficult to locate design rule violations by probing a finished circuit. Some violations are likely to go completely undetected, and result in degraded performance and a lower yield of working parts throughout the lifetime of the product. The only acceptable solution is complete automatic design rule checking of the mask artwork prior to fabrication.

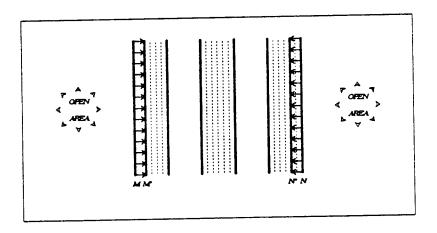

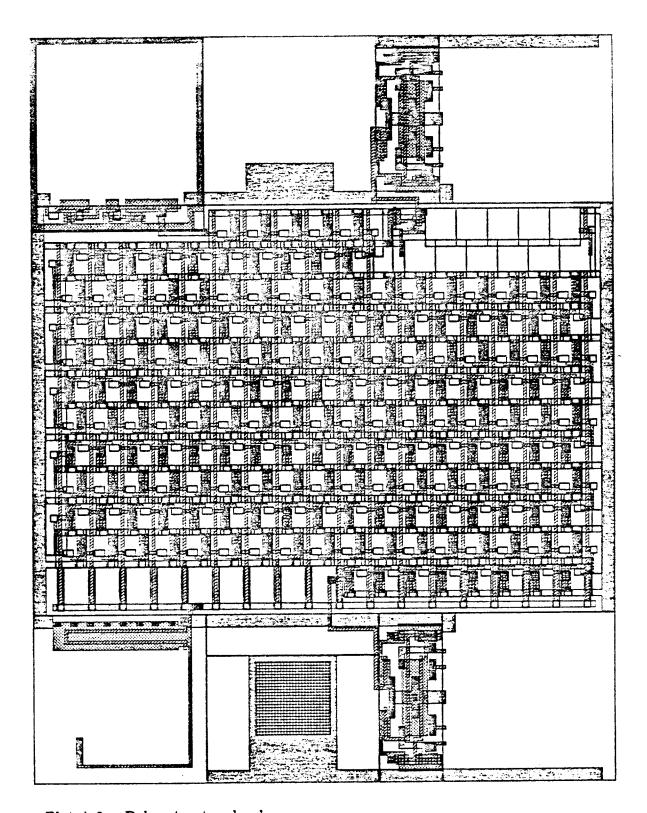

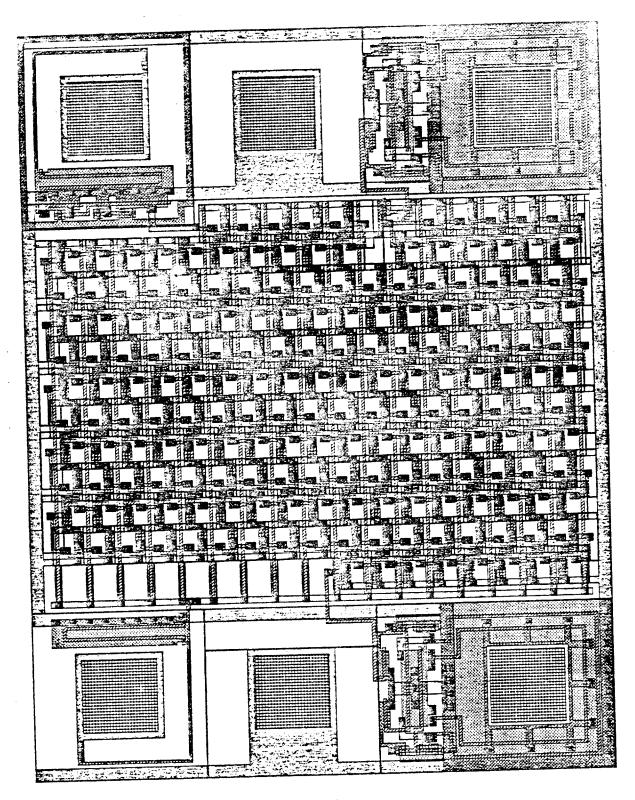

Figure 1.1. - Mask Artwork. This is the mask artwork for the basic register cell used in the RISC-II microprocessor chip developed at Berkeley. The RISC chip contains over 4000 such cells, comprising approximately one quarter of the total chip area. Each type of shading corresponds to a distinct mask layer in the design.

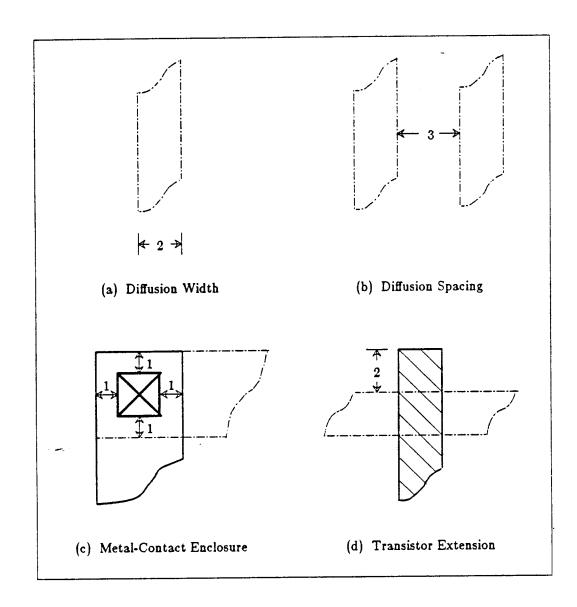

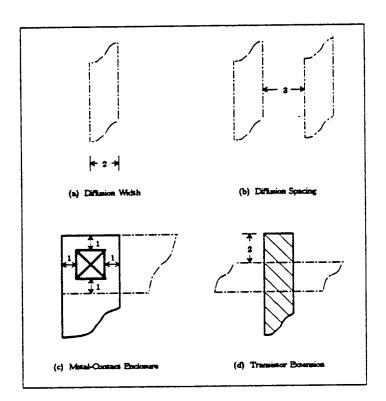

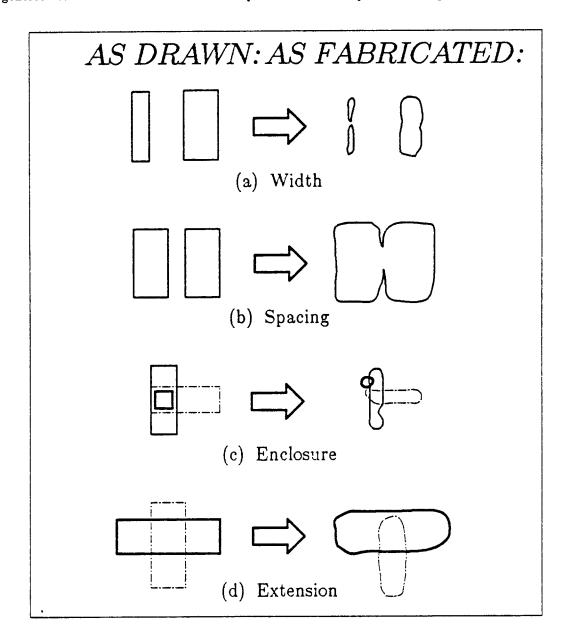

Figure 1.2. - Typical Design Rules. These examples are taken from the Mead-Conway rules for nMOS. Parts (a) and (b) give minimum widths and spacings (respectively) for lines on a particular layer. Parts (c) and (d) specify dimensional constraints on the formation of contacts and transistors (respectively). A design rule set contains anywhere from two dozen to over two hundred such rules. Some rules are more complicated; examples will be given in the next chapter.

To be useful, a design rule checker must meet several requirements. First it must be accurate. Since a single design rule violation can render an entire design nonfunctional, a design rule checker must miss no violations. In addition, a design rule checker that hides genuine violations in a sea of false alarms is almost as bad. This can happen if the checker

INTRODUCTION 4

inaccurately handles just one commonly occurring mask configuration. Thus a design rule checker must be accurate: it must miss no genuine violations, and generate few false alarms.

A useful design rule checker must also be flexible enough to check a variety of design rules. There are many integrated circuit technologies in use, and for each technology a number of fabrication lines. Each fabrication line has its own characteristic limitations, and hence its own design rules. In addition, as fabrication lines are refined and new ones introduced, design rules change over time. The natures of design rules are also diverse. Conditional design rules exist, that depend on factors as varied as the geometric context of a mask feature, the length of conducting lines, the electrical characteristics of a particular node, and even the intended function of the signal carried by a line. To be useful over time, and in more than a narrow context, a design rule checker must be flexible enough to check a variety of rulesets involving a variety of types of rules.

A design rule checker must also perform reasonably. As design complexity continues to grow, design rule checkers are faced with large and ever increasing amounts of data to process. A design rule check on a large design typically takes many hours or even days to complete. Such checking is expensive in terms of computer resources. In addition it makes design rule checking a batch process that is typically deferred until the end of the design cycle. Design rule violations detected so late can be quite difficult to fix: a significant amount of mask artwork in the vicinity of a violation may need to be altered to make room for the fix. Expensive design rule checking also inhibits design refinements, since any change in the design will require another costly design rule check. With the size and complexity of designs continually increasing, it is clearly important to look for efficient ways to do design rule checking.

In fact, the basic technique used almost universally for design rule checking was born more than a decade ago when designs were much smaller and less complex than today. This technique is poorly suited for processing designs of today's scale. In this approach, rule

checking is implemented through sequences of region-operations on one or two layers at a time. These operations typically yield a new, intermediate, layer as output. Layers frequently consist of over 100,000 figures, and typical rulesets require hundreds of these operations. This results in the generation of great amounts of intermediate data during a design rule check, and a great amount of I/O. The number of data items is very large, and the amount of computation per item relatively small. Hence processing is I/O bound, and slow.

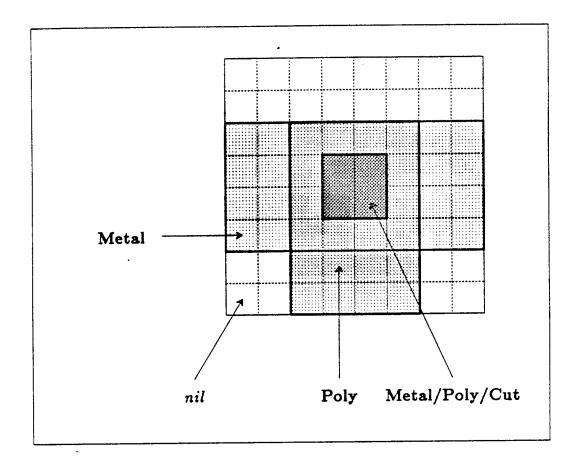

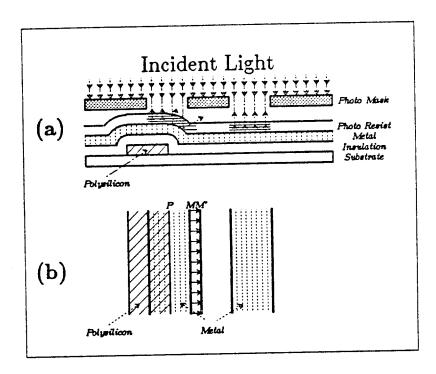

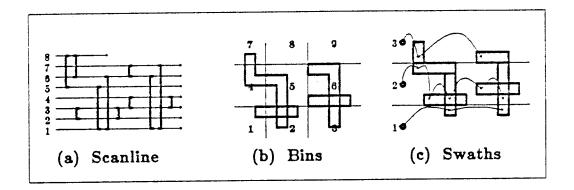

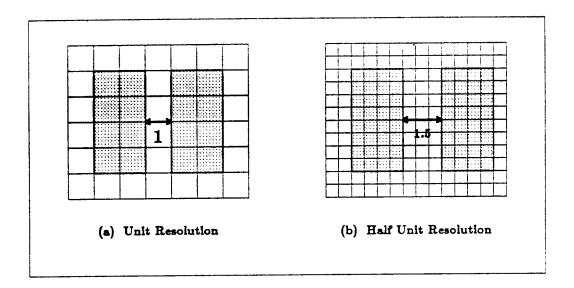

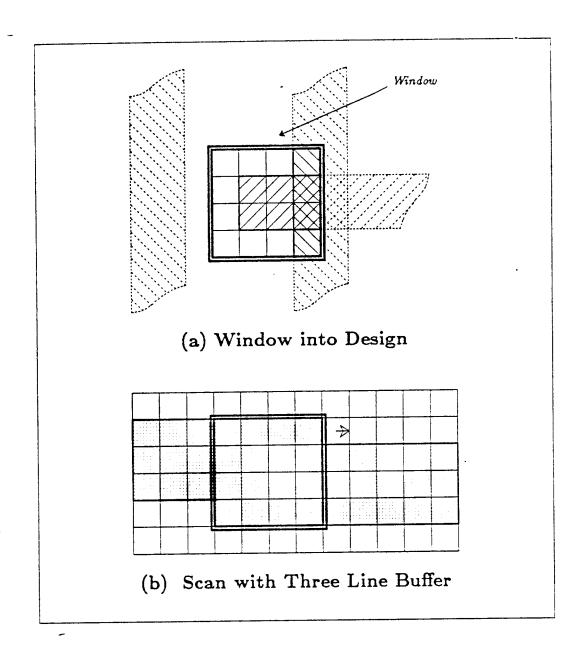

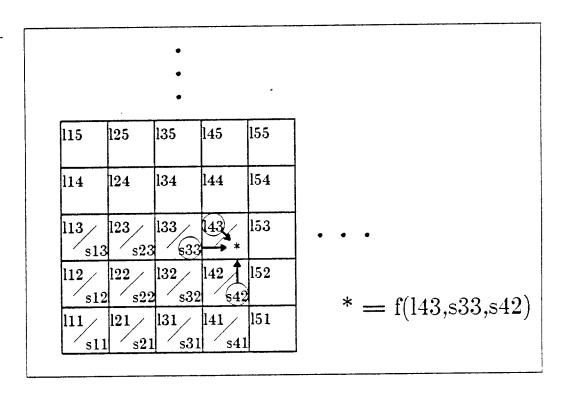

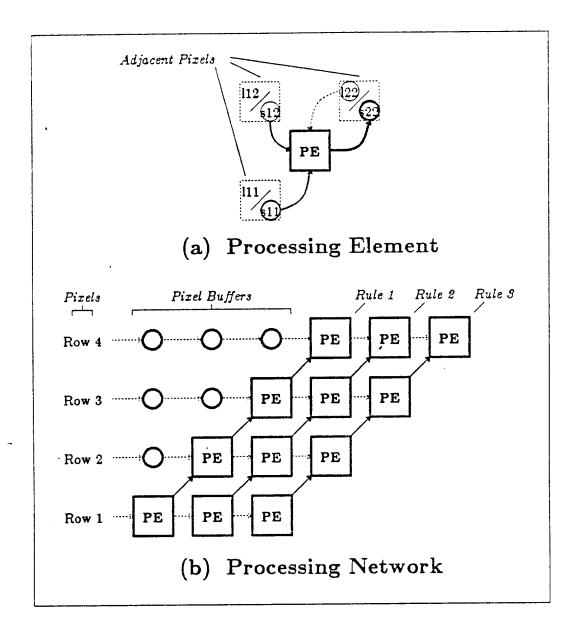

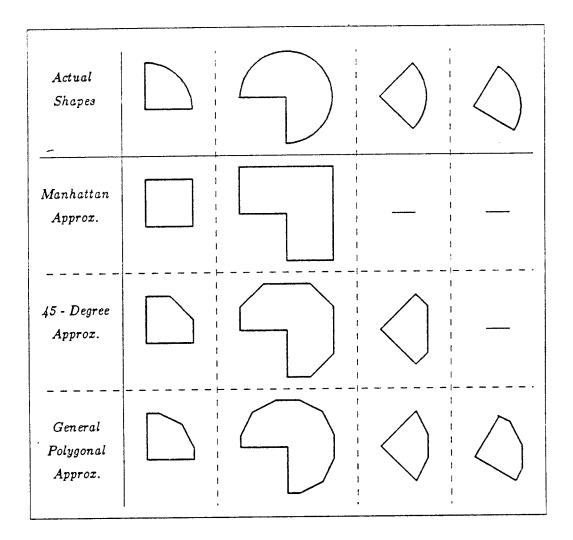

Several ideas for speeding up design rule checking have been proposed. One approach is to use special-purpose hardware. A number of hardware-assisted systems have been suggested. These systems employ pixel-based representations for the mask data; see Figure 1.3. An array of square pixels is laid over the design, and each pixel is marked with the mask layers occurring in it. In order to have sufficient resolution the pixel-array must be fine. A fine array over an entire VLSI design involves a very large amount of data. Thus, like the traditional region-operation approach, the hardware-assisted approaches involve a large amount of data, with relatively little processing per data item, and hence tend to be constrained by I/O bandwidth. Such special-purpose processing engines are also likely to be complex and expensive. No fully functional hardware-assisted design rule checker has yet been completed.

The elimination of redundant checking can be very effective in speeding up design rule checking. One such strategy, hierarchical processing, involves checking only one instance of repeated structures in a design. Since designs typically contain much repetition, such a strategy can reduce computation very significantly. For example, hierarchical checking of the RiscI microprocessor chip with Leo45 speeds up checking by almost a factor of 6. Another strategy, incremental checking, is to check only those portions of a design that have been modified since the last check. Again, this can greatly reduce the computation required for checking - particularly at the end of the design cycle, when minor modifications are typically

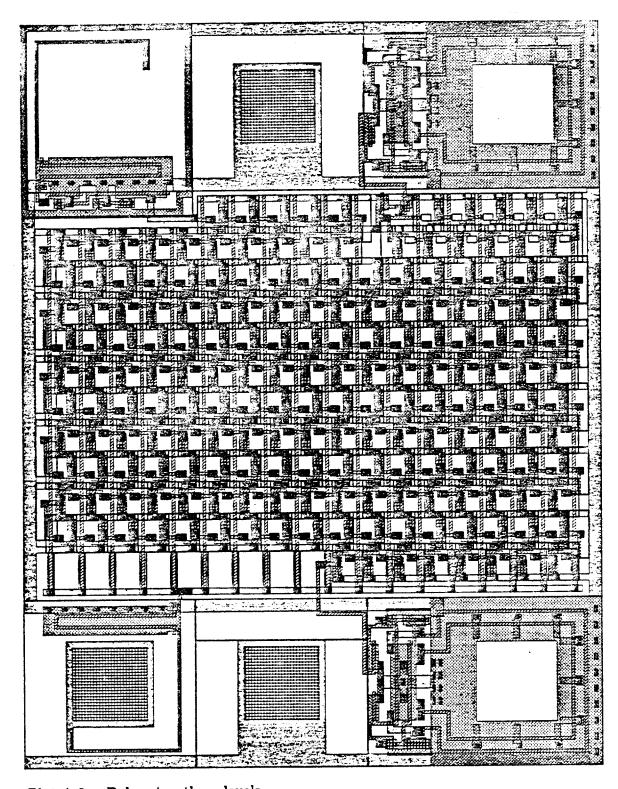

Figure 1.3. - Pixel-based Representation of Mask Artwork. In pixel-based systems, a square array of pixels is laid over the design, and each pixel is marked with the layers present within it. The pixel-array must be fine enough so that approximations at pixels that are only partially covered by mask layers don't result in false design rule violation reports or missed violations.

made to fix bugs detected by design rule checking or simulation. An incremental check of RiscI, (again by Leo45) after a minor modification to the design takes less than 1% of the time for a full check. Lyra and Leo, corner-based systems developed in conjunction with this research, pioneered hierarchical and incremental checking (respectively).

#### 1.2. Scope of My Research

My research has centered around an alternative approach to design rule checking: a corner-based approach where checking is done in terms of the corners in a design and their immediate environment. Corner-based checking is a fundamentally different approach to

design rule checking that addresses the I/O bottleneck problem traditionally plaguing design rule checking. The input rule description is preprocessed with a rule compiler to generate an efficient, indexed, internal rule form and all rules are processed in parallel in one pass through the design artwork. Corner-based checking is both accurate and flexible. It lends itself to checking rules involving directional context, which are notoriously difficult to check in traditional region-operation systems.

My research also included the development of *Hierarchical* and *incremental* algorithms that reduce redundant checking and hence make design rule checks more efficient and interactive. Although these algorithms could be implemented on top of a region operation system, the corner-based approach, which associates violations with points rather than edges or areas, is more convenient.

Corner-based checking was first implemented in the Lyra system, in 1981. Lyra was written to test the the basic soundness of the corner-based approach and fill the need for an accurate design rule checker at Berkeley. It demonstrated that corner-based checking can be both accurate and flexible. It has been used on a number of large design projects, including the RISC microprocessors at Berkeley, spanning a number of nMOS and CMOS rulesets. On its first real use (for the RISC-I chip), Lyra found violations that had been missed by a previous DRC as well as by manual checking. Even though written in Lisp, Lyra was about 3 times as fast as the region-based NCA system, which was the industry standard at the time.

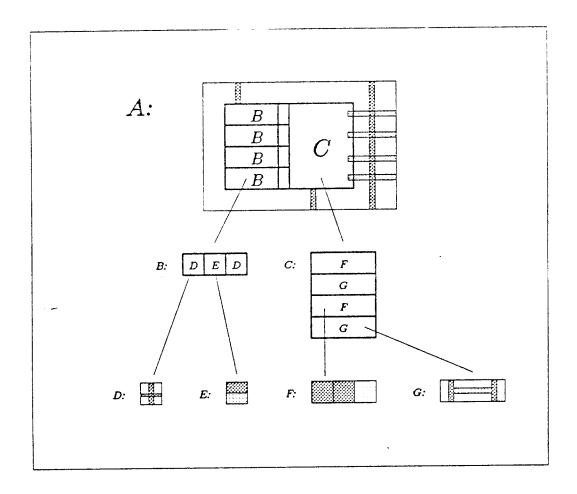

Lyra was the first hierarchical design rule checker. It demonstrated the feasibility and effectiveness of hierarchical checking. With interfaces to the Caesar and Kic geometric editors, Lyra also pioneered interactive design rule checking. The interface allowed designers to invoke Lyra on parts of the design currently being edited for "immediate" feedback on design rule violations. This feature proved quite useful to designers. Lyra is part of the Berkeley CAD tool distribution, and has been used at several hundred unviersity and industrial sites.

The viability of corner-based checking was further tested with Leo, a second, commercial, corner-based system. Leo was developed in conjunction with Metheus Corporation for use in their VLSI design workstation. Written in C with an eye toward efficiency, Leo is 3 times as fast as Lyra. In addition Leo is incremental, (it rechecks only the parts of a design that have been modified). Leo works quite well; its incremental and interactive checking capabilities have been selling points of the Metheus system.

The Lyra and Leo systems are useful only within a restricted context. They handle only manhattan designs, where all feature edges are lined up horizontally and vertically. A later version of Leo, Leo45, allows edges at 45 degree angles as well, but still excludes all other angles. The rulesets handled by these systems are composed of relatively simple, mainly unconditional rules. These restrictions are in the spirit of the simplified design philosophy popularized by Carver Mead and Lynn Conway. They are suitable for the Mead-Conway design style widely used in universities and a growing segment of the industrial community. They simplify the implementation of the systems, and improve performance.

Nevertheless, the question of the usefulness of corner-based checking in more general contexts must be addressed. To explore this issue, I have developed a general corner-based formalism and considered its implementation in detail. This formalism has provisions for processing all-angle mask data, specifying complex conditions on the interrelationship of features at corners (capable of capturing complex conditional rules), and provisions for the incorporation of nongeometric data, (again for checking conditional rules). This work shows that a general corner-based system is feasible, but that preprocessing would be required to generate any nongeometric contextual information used in the rules. The rule formalism is quite flexible. The proposed implementation uses standard compiler techniques as well as some tairly elaborate logical manipulations to transform the input rule specification into a simple regular internal form that can be efficiently checked. Though the performance of such a complex system can not be accurately predicted without implementation, it is encouraging

INTRODUCTION 9

that much of the complexity can be shifted to the rule compiler that transforms the input rule specification to an efficient internal form. The rule compiler is only run infrequently, so its efficiency is not a large concern. The actual rule checking is still relatively simple, though more complex and slower than in the more restricted systems that have been implemented. Many conditional rules rely on preprocessing to generate additional context information. Such preprocessing would presumably be done using traditional region-based operations. This suggests a hybrid system, involving region-based preprocessing to generate needed context information followed by the more efficient and flexible corner-based tolerance check.

# 1.3. Ideas in My Research

A number of key ideas on design rule checking have emerged out of my research. These ideas, more than particular systems or even particular algorithms, are my contribution to the field. Some of the ideas, such as pattern-directed, rule-based, processing and point/edge tolerance checks, were new. Others such as hierarchical, and incremental checking had previously been proposed, but were elaborated on (and validated) by my work. Still others involving more general corner-based systems, were just suggested by the research, and remain to be developed. The most important ideas are introduced below.

Corner-based checking uses pattern-directed, rule-based processing, a technique borrowed from Artificial Intelligence. The pattern-directed processing of corners works as follows. Each corner in a design is analyzed for certain mask patterns. The presence of certain predefined patterns triggers relevant rules. The rules in turn specify conditions to check at the corner. Care is given to index the triggering patterns so that the relevant rules at each corner can be identified quickly. Processing of a design involves one pass through the data (all rules, and layers are processed in parallel), and no intermediate layers are generated (the layers are checked "in-place"). This approach is radically different from the traditional region-operation approach, where rules are checked through sequences of operations, and each operation involves a separate traversal of the mask data. The pattern-directed processing concentrates

INTRODUCTION 10

the checking per data item scanned, and thus avoids the I/O bottle neck problem. Pattern-directed processing, looked at from another perspective, is rule-based. The rule-based nature of corner-based checking provides the characteristic flexibility of rule-based systems. Variants of design rules, that would require the coding of a new operation in region-based systems, can be accommodated in a corner-based system by the much simpler process of modifying a rule.

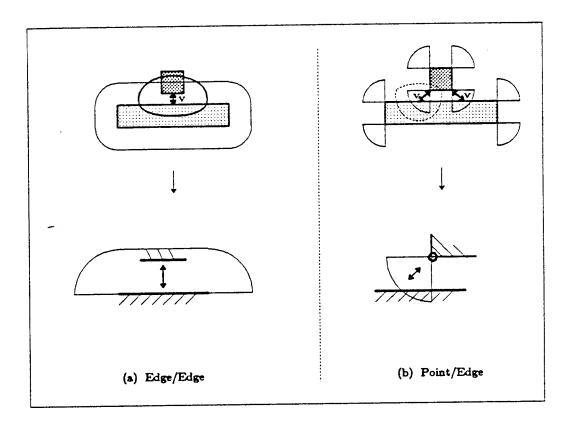

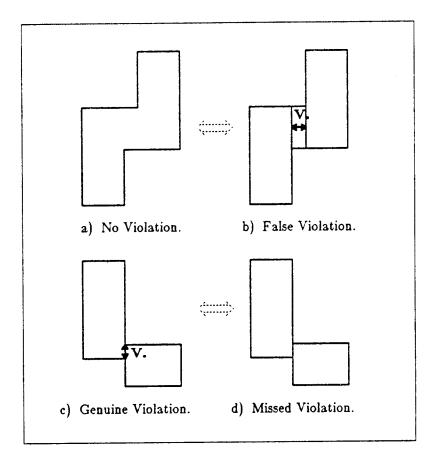

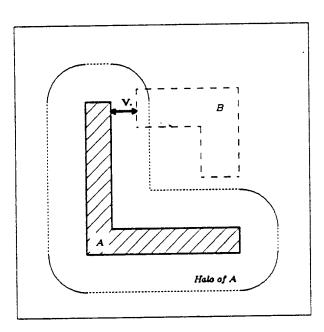

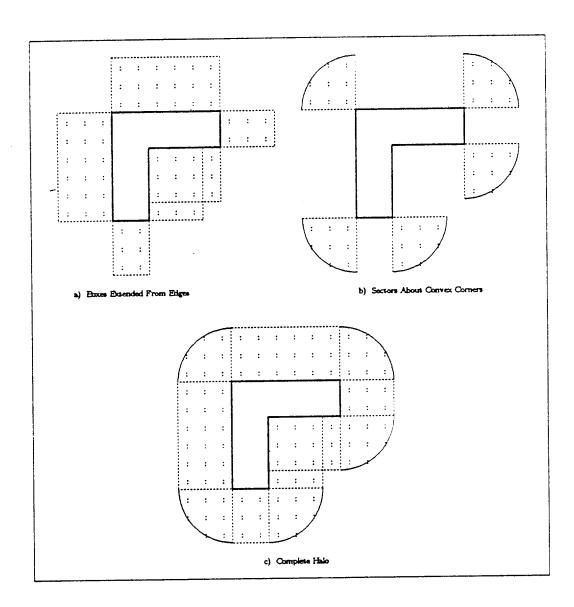

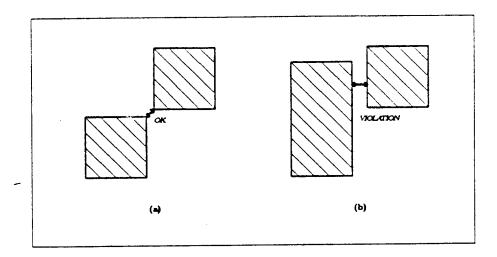

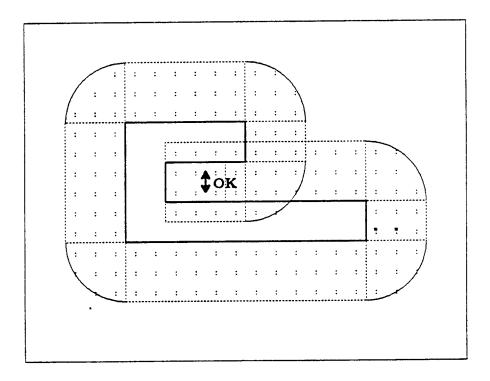

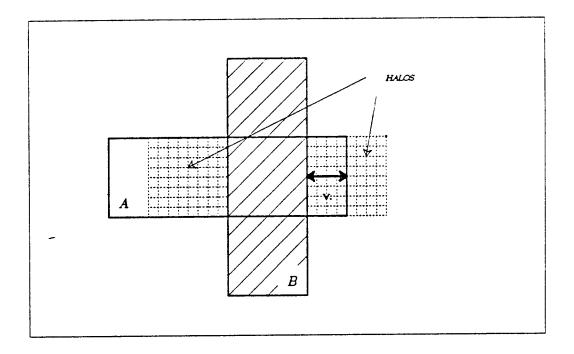

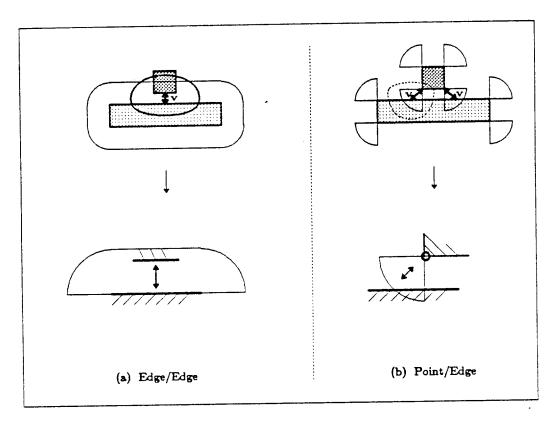

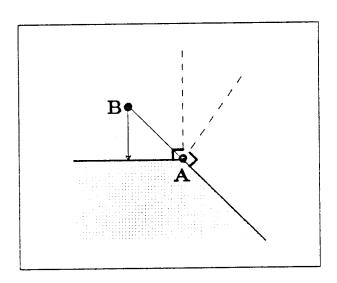

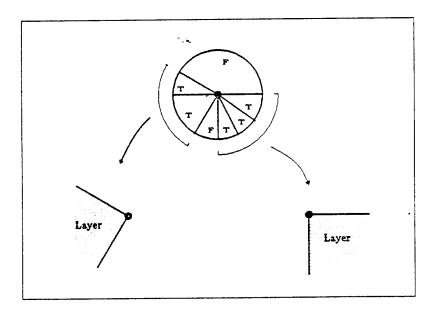

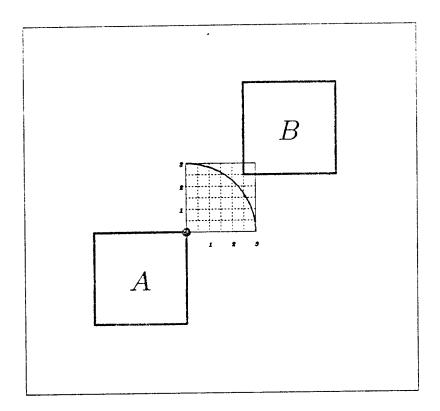

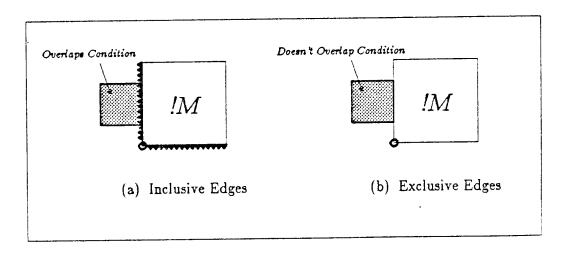

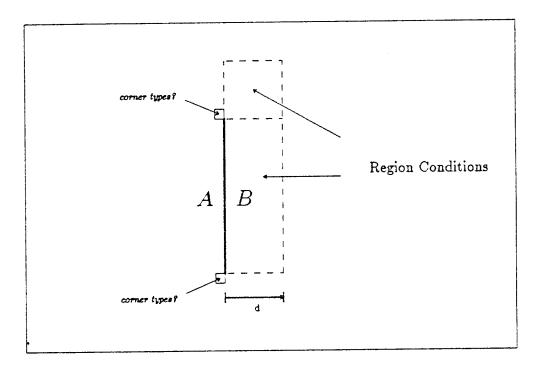

Another innovation of the corner-based approach, is the use of point/edge based tolerance checking, that is tolerance-checking involving the measuring of distances between corner-points and edges, rather than between pairs of edges; see Figure 1.4. This technique localizes checking to points in the design rather than edges or regions. Violations are associated with corner-points, and the independent checking of a piece of a design can be precisely defined as checking all the corner-points of that piece. The consequent simplicity of piecewise checking facilitates the implementation of hierarchical and incremental strategies.

Though hierarchical processing has been widely heralded as the solution to the excessive times required for design rule checking, hierarchical systems have been slow in coming. Lyra appears to have been the first fully-functional hierarchical design rule checker. Lyra demonstrated that hierarchical checking of structured designs can be effective, and that special restrictions on cell overlap are not required: as long as cell overlap remains relatively small, hierarchical checking in Lyra is effective. In addition Lyra's special handling of arrays proved very effective. Most of the regularity in VLSI designs is in the form of arrays. Special handling of arrays alone will give most of the advantages of hierarchical checking. There was also a negative result: checking of poorly-structured designs was as much as several times slower hierarchically than flat! This was because mask features involved in cell interactions ended up being checked at several distinct levels in the hierarchy.

Once hierarchical checking was in place, incremental checking proved easy to implement and very useful. User response to incremental checking in Leo was extremely favorable. Leo users frequently run design rule checks each day or so. Violations no longer go unnoticed

Figure 1.4. - Alternative Tolerance Check Methods. Traditionally, tolerance checks on mask regions have been done by checking the distance between region edges (a). In corner-based checking, tolerances are measured from corner points to region boundaries (b). Such point/edge checking has the advantage of very naturally splitting up into piecewise checks: checking a piece of a design, corresponds to checking tolerances from corner-points within that piece.

until after the design is complete and they are hard to fix.

Several new design rule check systems have incorporated some of the above ideas. The Mart design rule checker, developed by Bruce Nelson and Mark Shand at CSIRO is based directly on corner-based checking as in Lyra. The new internal Intel design rule checker uses point/edge tolerance checking to facilitate piecewise processing. The Magic design rule checker, recently developed by George Taylor and John Ousterhout at Berkeley, is strongly influenced by Lyra. Though edge-based rather than corner-based, the Magic system uses pattern-directed rule-based processing. Its hierarchical algorithm is similar to Lyra's, and its handling of arrays is identical. All these systems are discussed in Chapter 7, and references

INTRODUCTION 12

are given at the end of that chapter.

#### 1.4. Outline

About half of the material in the following chapters provides background. It discusses the origin and nature of design rules, and presents the various approaches to design rule checking. This material provides an introduction to the design rule checking problem, and the context for the discussion of the corner-based approach, and the hierarchical and incremental algorithms of Lyra and Leo.

The remaining chapters are organized as follows. Chapter 2 considers where design rules come from, what they look like, and their role in the various design methodologies. It develops the topo-tolerance model for design rules that is used through out the thesis. Chapter 3 presents the traditional region-operation based method of design rule checking. Chapter 4 surveys existing design rule checkers, giving examples of traditional systems as well as other approaches. Chapter 5 introduces corner-based checking in fully general form. It develops a corner-based formalism and explores the scope of rules that can be handled by it with a number of examples. Chapter 6 discusses how a general corner-based system might be efficiently implemented. Chapter 7 surveys actual corner-based systems, focusing on the restrictions of each: how they simplify the implementation and how they limit rule checking capabilities. Chapter 8 discusses hierarchical and incremental checking. It presents both the approaches I used in Lyra and Leo, and the approaches used in other systems. Numerical measurements are presented in Chapter 9. Chapter 10 is the the conclusion.

#### CHAPTER 2

## The Nature of Design Rules

#### 2.1. Introduction

Design rules specify constraints on the minimum size of circuit components, and the maximum component density for integrated circuits. These constraints are given as minimum tolerances on various spacings, widths, enclosures and extensions in the mask artwork for the circuit. See Figure 2.1 for examples.

Figure 2.1. - Typical Design Rules. These examples are taken from the Mead-Conway rules for nMOS. Parts (a) and (b) give minimum widths and spacings (respectively) for lines on a particular layer. Parts (c) and (d) specify dimensional constraints on the formation of contacts and transistors respectively. A design rule set contains anywhere from a couple dozen to over two hundred such rules. Some rules are more complicated; examples will be given later in this chapter.

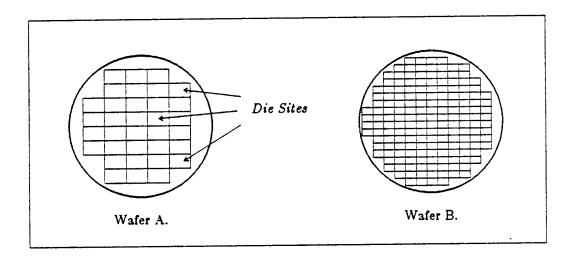

There are a number of reasons for making devices as small as possible and component density as high as possible. Most importantly, the probability of any given chip being fabricated correctly (the yield) decreases dramatically as overall circuit size grows. This is because fatal defects, caused by impurities in the silicon crystal or dust contamination during processing, occur with approximately fixed and independent probability in each unit-area of the circuit. Thus the probability of at least one (fatal) defect occurring in a circuit grows exponentially with the area of the circuit. Hence smaller circuits have much better yield and are more economical to produce. In addition, there is a practical limit on the maximum circuit size that can be fabricated: beyond some size, yield will be so astronomically small that no fabricated chip is likely to work. Thus smaller devices permit more complex chips. Even disregarding yield, smaller circuits are more economical simply because there are more chips per wafer fabricated; see Figure 2.2. Still another reason for minimizing component sizes is that circuits composed of smaller components are faster and consume less power.

Figure 2.2. - Wafers and Die Sites. Multiple copies of an integrated circuit are fabricated simultaneously on circular silicon wafers. After fabrication is completed, a wafer is fractured (or diced) into rectangular chips (or dice). Each chip contains an individual copy of the circuit. The smaller the area of a chip, the more copies can be fabricated per wafer, and the more economical production becomes.

Limitations on the minimum size of circuit components, and hence the design rules, arise primarily from imperfections in the mask preparation and fabrication process. These imperfections result in distortions of the artwork during the transfer from the original digital specification to the actual integrated circuit layers. They are numerous and varied, arising at every step in the fabrication process. Examples are imperfect optical resolution during certain processing steps, and imperfect alignment between masks or layers.

In addition design rules result from the physical properties of the fabricated circuit. For instance, to prevent shearing of brittle metal lines, some processes have design rules that prohibit metal from crossing over features that rise and fall abruptly. Similarly metal migration effects, involving the erosion of metal atoms under the influence of a strong electric current, necessitate wider metal lines in some cases. The gradual nature of diffusion boundaries also leads to width and spacing restrictions.

Design rules are an abstraction of the physical limitations of the fabrication process that permits the decoupling of process engineering and circuit design. A circuit designer need not be concerned with the complex details of the fabrication process: he need only conform to the design rules. Similarly, process engineers have flexibility in the development or modification of the fabrication process, as long as the final process meets the design rules.

The following sections explore the origin, form, and uses of design rules in more detail. First, the next section takes a closer look at the process engineering side of design rules: the physical structure of integrated circuits is described; the principle artwork transfer steps in the fabrication process are considered; and it is shown how limitations in the fidelity of these transfers, and physical limitations on the fabricated circuit lead to design rules. The following section discusses the form of design rules. A model for design rule form is presented and illustrated with a representative sample of design rules. The final section considers the role of design rules in the various design methodologies, and argues that a basic automatic design rule checking capability is important regardless of design methodology.

# 2.2. Integrated Circuit Fabrication and the Origin of Design Rules

Integrated circuits consist of layers of patterned conducting material stacked vertically on the surface of a silicon substrate and separated by insulating material. Electrical devices such as transistors and capacitors are formed through the interaction of certain layers across thin insulation. Electrical contacts between layers are formed by cutting through the insulating material between. Regions of the circuit are implanted with various impurities to selectively change the electrical characteristics of the layers and the devices formed by their interactions. A circuit is defined by geometric patterns giving the regions where each of these layers (conducting, insulating or implant) is present.

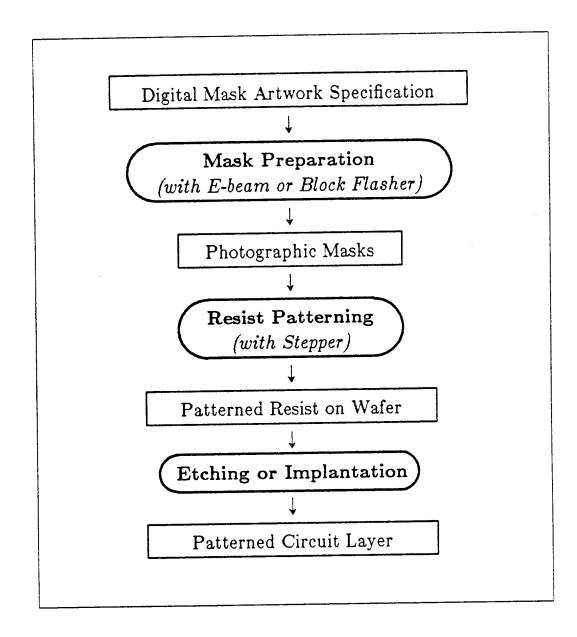

The physical design of a circuit is originally in the form of digital design files specifying the geometric pattern for each layer. To realize the circuit, the pattern for each layer must be transferred to a physical layer in the circuit. This transfer is generally effected in at least three stages, as illustrated in Figure 2.3. Prior to fabrication a photographic mask patterned with transparent regions on an opaque background (or vice versa) is created for each layer. The photomask is used to pattern a photosensitive resist, deposited uniformly over the surface of the circuit. The actual layer is then patterned from the resist. Typically the layer has been deposited immediately below the resist, and is patterned by an etchant that dissolves the layer everywhere it is not covered by the resist.

Each transfer of the patterning information introduces distortions. The type and degree of distortions is dependent on the procedure and equipment used. Mask generation is often done by a block flash technique. A photographic emulsion is exposed to flashes of light directed through a rectangular aperture, whose position, size and angle of rotation are digitally controlled by a pattern generation tape. The pattern generation tape is derived directly from the physical design files for the circuit. There are several sources of distortion during flashing. Optical diffraction effects at the edge of flashes cause a loss of edge acuity on the emulsion; over- or under-exposure due to imperfect control of the timing and intensity of

Figure 2.3. - Pattern Transfers in Integrated Circuit Fabrication. The fabrication of integrated circuits generally involves at least three transfers of the geometric pattern information: from the original digital specification to the photographic mask, from the mask to a photosensitive resist on the surface of the wafer, and finally from the resist to the actual circuit layer.

flashes can lead to slight edge motion; and mechanical imprecision in the flasher can result in inaccurate positioning of flashes. Also, decomposition of the original design into a sequence of rectangular flashes may require approximations, since the size, position, and angle of flashes can only be varied in discrete increments. Non-polygonal features, such as circles, require

approximation too.

Patterning of the resist typically involves a stepper that focuses an image of the photomask successively onto each chip site on the resist-coated wafer. After exposure, the resist pattern is developed using a solvent that dissolves the exposed (negative resist), or unexposed (positive resist) sections. Distortions introduced in the patterning of the resist are due mainly to the limited optical resolution of the imaging system, and diffraction effects at region edges. Distortions also result from other factors such as nonuniform resist thickness. Finally, imperfect alignment between masks, both translational and rotational, leads to uncertainty about the relative position of shapes on different layers.

The final transfer of the artwork pattern to the circuit layer is through an etching or implantation step. The fidelity of this transfer is limited by the diffusion of etchant or implant laterally underneath the resist boundaries. Imperfect control of the reactivity of the active species (e.g. etchant strength), or of timing, results in uncertainty about the size of the regions created.

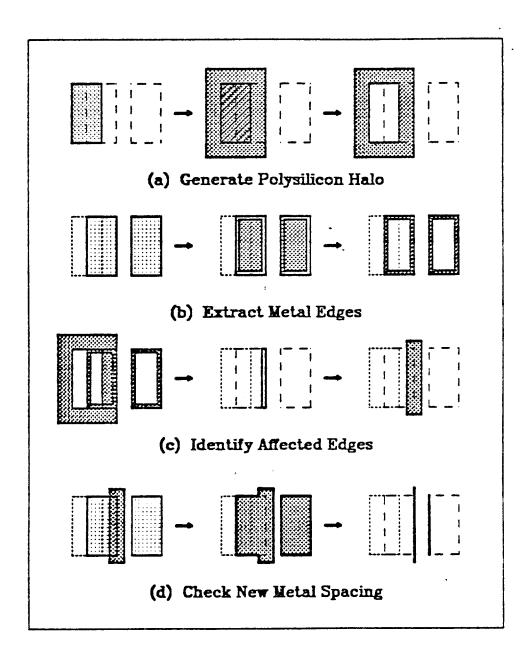

Some distortion effects are pattern dependent, that is, they vary with the circuit artwork. For example light reflected by metal-coated polysilicon during resist exposure for the metal layer, can cause edges on the metal layer to be displaced; see Figure 2. This reflection effect only occurs when a polysilicon edge runs near a metal edge. Another pattern dependent effect involves etching in open versus confined regions. The rate of etching may be less in more confined spaces. Thus, for instance, the outside edges of a set of parallel metal lines may be etched more than the internal edges, as in Figure 2.5.

The above description of circuit fabrication, while correct in outline is greatly simplified. Processing often involves additional transfers of the artwork pattern. For example working masks may be produced from master photomasks, or reduced (and repeated) masks called reticles may be used. A typical integrated circuit fabrication process involves over 100 distinct processing steps [Sze, 1983]. Imperfections in each step contribute to overall

Figure 2.4. - Reflections A Pattern Dependent Effect. During resist patterning of an aluminum layer, (a) above, the shiny aluminum-coated wafer reflects as much as 90% of the incident light back through the resist. Where the wafer is flat the light is reflected harmlessly straight back up. However, protrusions caused by underlying polysilicon edges scatter the light resulting in undesired resist exposure. This results in the displacement of metal edges where polysilicon edges run nearby, as shown in (b). In this case metal edge M is displaced to M' by light scattered from the nearby polysilicon edge P.

Figure 2.5. - Variable Etch: Another Pattern Dependent Effect. Etching can be more vigorous in open areas, such as outside a set of closely spaced parallel lines, than in confined areas, such as between closely spaced lines. This results in the narrowing of lines adjoining open areas.

distortion in the final circuit.

The sources of artwork distortion during fabrication are numerous and complex. In general the distortions lead to uncertainty about the exact position of region boundaries in the

Figure 2.6. - How Distortion Causes Circuit Fallure. This figure shows examples of how distortion can lead to circuit failure if minimum tolerances are not observed. Part (a) illustrates how a narrow line can be split. Part (b) shows the merging of features that are drawn too closely together. Part (c) shows how the desired connection between layers can be lost if a contact is drawn with insufficient enclosure. And part (d) shows how transistors can fail, if they are drawn with insufficient extension.

position, particularly between layers, will be inexact. This is illustrated in Figure 2.6. Narrow lines may not be resolved at all (i.e. may not appear in the fabricated circuit), while somewhat wider lines may be narrowed to the point where they are split into pieces, as in Figure 2.6(a). Similarly shapes that are too closely spaced may be merged during fabrication, as in Figure 2.6(b). Thus minimum width and spacing tolerances are needed to ensure that electrical nodes are neither split nor merged together during fabrication.

The formation of contacts and devices such as transistors and capacitors involves overlaps and extensions between layers. For example, in a typical MOS process a contact from the metal layer to the diffusion layer is formed as shown in Figure 2.1(c). In order for contact to be made it is necessary that all three layers, metal, diffusion and the cut in the insulation between them, overlap. Thus minimum overlap tolerances are needed to ensure all three layers will overlap sufficiently in the fabricated contact despite misalignments between layers, and shrinks on the individual layers; see Figure 2.6(c).

The formation of MOS transistors involves the extension of a polysilicon line over a diffusion line, as in Figure 2.1(d). The transistor will not function if the polysilicon fails to extend all the way across the diffusion line in the fabricated circuit, (see Figure 2.6(d)), so a minimum tolerance on the extension of the polysilicon beyond the diffusion is required.

In addition to causing circuit failure through broken or shorted nodes and inoperative contacts or devices, distortions can result in degradation of circuit performance through the formation of parasitic devices, e.g., capacitors formed by unintended overlap between layers, or voltage drops in lines that end up too narrow. Cumulatively such effects can lead to complete functional failure of the circuit, or simply degrade performance so the circuit will not meet design specifications. In a few cases, distortions can result in long-term failure of the circuit. For example, narrow metal lines carrying high current are subject to eventual failure due to metal migration: the metal atoms actually erode away under the influence of the

electric current.

Many of the factors contributing to artwork distortion during fabrication are random. They vary from wafer to wafer, and often from region to region on an individual chip, according to some probability distribution. The distortion of individual shapes and relationships between shapes results from the combined effects of these many random factors, and thus is best characterized in statistical terms. The maximum distortions occur when all the individual factors are by bad luck near their respective maxima and all work together in the same direction. The greatest distortion on an average chip will be much less than such a worst case since the many factors contributing to distortion will tend to average out and cancel each other.

Specifying design tolerances based on worst case distortions would be overconservative. Such a choice would lead to unnecessarily large devices and circuit areas, degrading circuit performance, increasing power consumption and quite possibly reducing the yield of working chips because of fatal random defects whose probability increases exponentially with chip area. Thus the specification of design rule tolerances is a compromise that seeks to make minimum tolerances small while, at the same time, keeping losses from pattern distortion low.

# 2.3. The Form of Design Rules

The last section showed how numerous factors cause distortions of the design artwork during fabrication. These distortions result in uncertainty about the eventual size and relative position of artwork shapes in the fabricated circuit. Coupled with physical requirements of the circuit, such as the need to maintain the integrity of nodes and minimize parasitic devices, these effects lead to the design rules for the process.

Design rules take the form of minimum tolerances on spacings, widths, enclosures and extensions on the artwork as designed. These tolerances are intended to be sufficiently large so that the corresponding relationships in the fabricated design will be maintained (and of sufficient dimension) despite distortions. Because these rules give tolerances on topological

relationships, I refer to them as topo-tolerance rules.

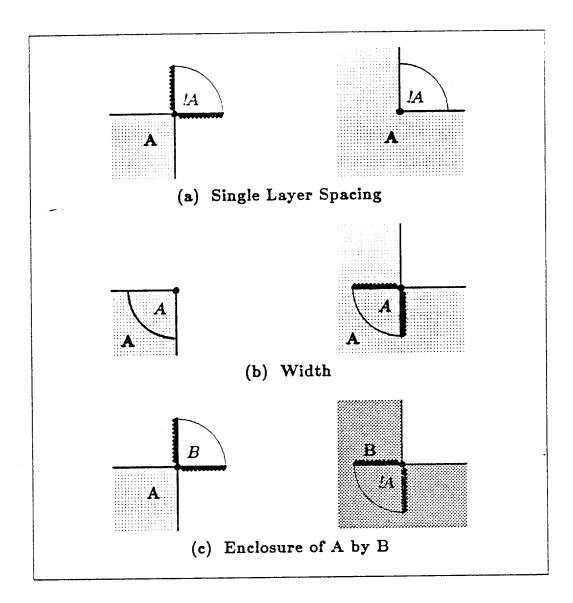

The simplest and most common design rules specify minimum width and spacing for the nodes of a single layer. See, for example, Figures 2.1(a) and (b). Here diffusion lines are required to be at least 2 units wide and distinct nodes are required to be spaced at least 3 units apart.

Enclosure and extension rules generally involve interlayer contact or device constructs. For example Figure 2.1(c) shows a typical rule for contacts between diffusion and metal in an nMOS process. Here both the diffusion and the metal must enclose the contact cut for a distance of at least one unit. Figure 2.1(d) shows an nMOS transistor rule that requires polysilicon to extend past the diffusion for at least two units.

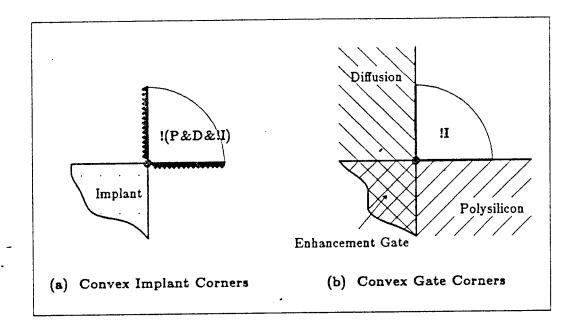

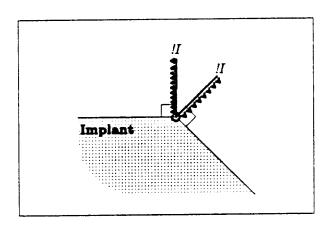

In addition to specifying tolerances on topological relationships for single layers and between pairs of layers, topo-tolerance rules can refer to regions defined by a combination of layers. For instance in nMOS processes, the operating characteristics of a transistor can be changed by implanting the transistor gate region: unimplanted transistors are enhancement mode, while implanted transistors are depletion mode. To ensure that the entire gate region of depletion mode transistors actually gets implanted, the implant layer is required to enclose depletion mode gate regions, by some tolerance. Similarly, to avoid accidental implantation of enhancement mode transistors, there is a spacing rule between enhancement mode gate regions and the implant mask. These rules are illustrated in Figure 2.7. Note here that depletion mode gate regions are defined as

Polysilicon AND Diffusion AND Implant,

and enhancement mode gate regions are defined as

Polysilicon AND Diffusion AND (NOT Implant).

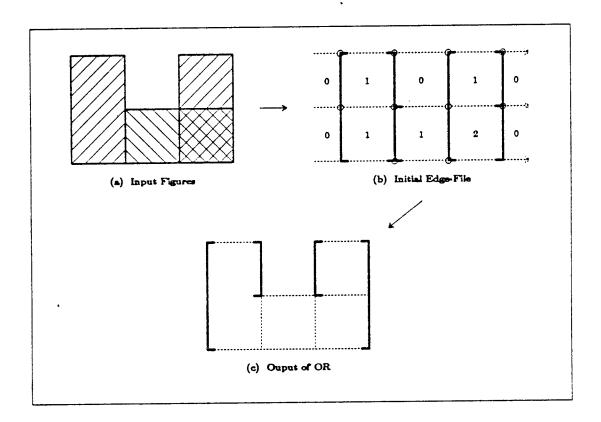

In general topo-tolerance rules can refer to regions on composite layers defined as arbitrary combinations of the mask layers. Such combinations are specified by boolean expressions on the mask layers, e.g. by using AND, OR and NOT operations.

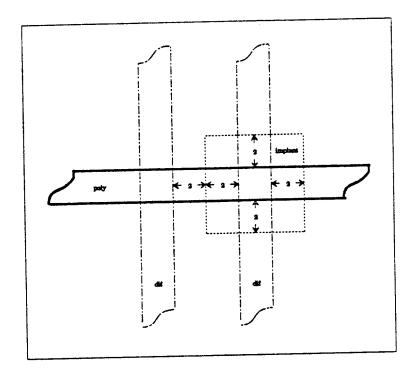

Figure 2.7. - Implant Tolerances Involving Combinations of Layers. Typical implant rules require implanted transistors to be enclosed by implant for a minimum of 2 units and nonimplanted transistors to be spaced at least 2 units from implant regions. These rules do not involve spacings between mask layers; rather they each involve a spacing between a mask-layer and a (boolean) combination of mask layers.

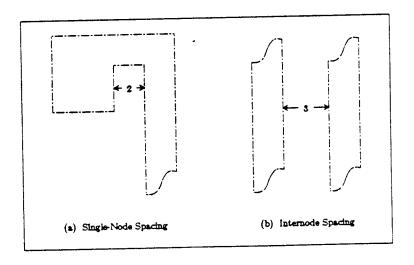

Figure 2.8. - Internode Spacing; a Conditional Rule. Frequently the spacing rule for distinct nodes specifies a greater minimum spacing than is required between segments of a single node. Such a spacing rule is *conditional* because it only applies in limited contexts, i.e., between boundary edges of distinct nodes.

Figure 2.9. - Reflection Rule. The spacing between metal lines may be greater when polysilicon edge(s) are nearby. This is because reflections from the metal coated polysilicon edges during patterning of the metal layer can cause the metal edges to move outward.

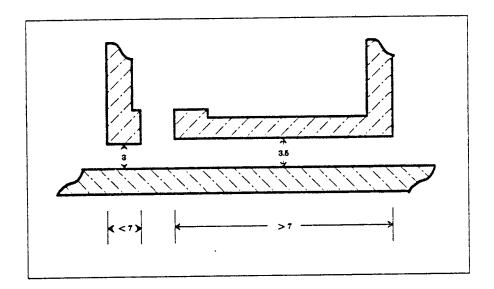

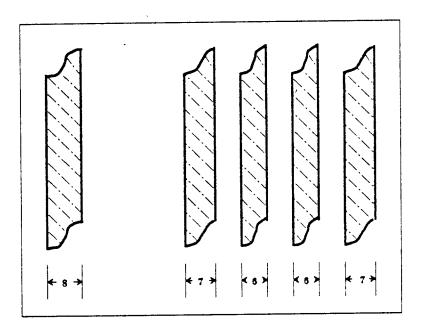

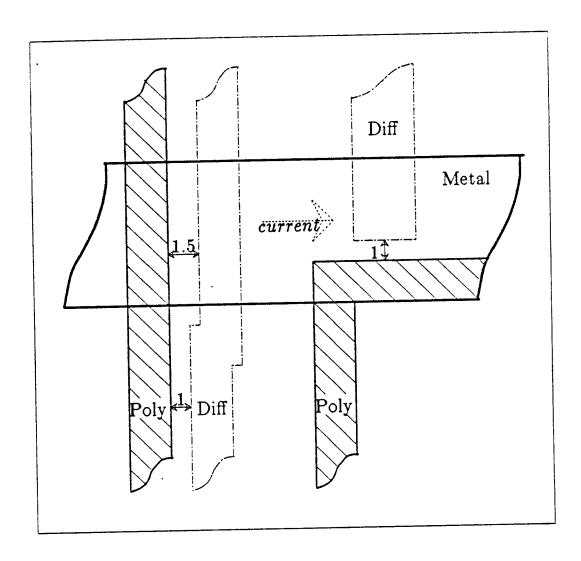

The above rules, with the exception of internode spacing, are unconditional: the specified spacings, widths, or enclosures apply unconditionally to the mask layers throughout the circuit. However design rules are often conditional, that is, the specified topo-tolerance is only relevant in certain contexts. The conditions on design rules can take many forms. The most common example of a conditional rule is internode spacing on a conducting layer. Such a spacing rule is conditional because it only applies to mask regions that belong to distinct nodes; see Figure 2.8. Another example of a conditional design rule involves the reflection phenomenon introduced in the previous section. To take reflection into account a rule might require that metal lines be spaced 1 unit apart when there are no polysilicon edges paralleling the facing metal edges, 1.5 units apart when a polysilicon edge runs near one of the two metal edges, and 2.0 units apart when polysilicon lines run near both the metal edges. Such a rule is illustrated in Figure 2.9. Some design rules require that long parallel lines be spaced more conservatively than short ones, to avoid capacitive coupling. Figure 2.10 gives an example. A tendency for etching to be more vigorous in open areas can lead to conditional width rules. For example minimum metal width might be 8 units if no other metal is present nearby, 7

units if metal is nearby on one side, and 6 units if metal is present on both sides of a line. Such a rule is illustrated in Figure 2.11. To avoid metal migration effects, metal width is sometimes dependent on the current density a line will carry; for instance, power and ground lines are often required to be wider than lines carrying other signals.

Conditional rules can get very intricate. As a final example, consider the following: To avoid metal shearing due to rough underlying terrain, greater spacing between polysilicon and diffusion edges may be required when a metal line runs perpendicularly across these edges; see Figure 2.12. Since shearing in the direction of current does not pose a problem, such a rule is actually dependent on the direction of current in the overlaying metal.

The above examples illustrate conditional rules that depend on the presence of nearby regions or edges on the same as well as different mask layers, rules that depend on the length, expected current density or function of lines, and even a rule that depends on current direction. In general design rule conditions may be very complex and may involve geometric information about circuit artwork, topological information (such as node connectivity), electrical information, and functional information about the circuit.

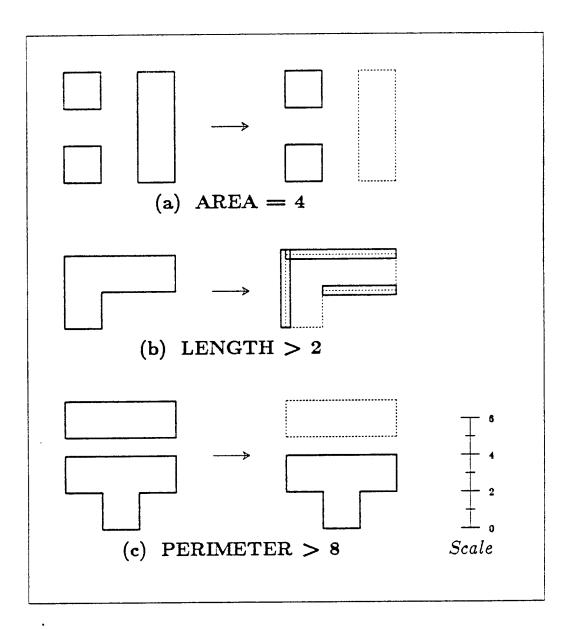

With the exception of an occasional rule concerning areas, perimeters, or exact (not minimum) dimensions, the examples of this section illustrate the nature and range of design rules for integrated circuits. Simple rulesets are comprised of a relatively small number of conservative primarily unconditional rules giving minimum tolerances on widths, spacings, enclosures and extensions for mask layers and layer combinations. More complex rulesets involve a greater number of conditional rules that give more precise tolerances by specializing the context in which each rule applies.

# 2.4. Automatic Design Rule Checking and Design Methodology

The topo-tolerance rules defined in the last section form the basis for the interface between process engineers and circuit designers. However, the nature of the design rules actually seen by circuit designers varies considerably with design methodology. This section

Figure 2.10. - Length-Dependent Spacing. Sometimes spacing rules are conditional on the length over which lines run parallel. For example, lines might be required to be separated by 3 units if they run parallel for less than 7 units, but be separated by at least 3.5 units if they run parallel for lengths of 7 units or more.

Figure 2.11. - Density Dependent Width. Because etching is more vigorous in open areas, width rules are sometimes conditional on the presence of nearby lines on the same layer. For example minimum width may be 6 units for interior minimum-spaced lines, 7 units for lines at the edge of a minimum-spaced set, and 8 units otherwise.

Figure 2.12. - Spacing Conditional on Current Direction in Overlying Metal. Sometimes minimum spacing between poly and diffusion is conditional on the presence of overlying metal. This is because nearly-coincident poly and diffusion edges result in an abrupt change in the vertical dimension that can cause overlying metal to shear. Since shearing in the direction of current flow does not cause problems, the more conservative spacing need only apply to polysilicon and diffusion edges running across the direction of current in the overlying metal.

explains why a spectrum of design methodologies is in use, and briefly describes the major methodologies and the nature of the design rules each presents to the designer. Then it argues that automatic topo-tolerance checking is important regardless of the methodology employed.

# 2.4.1. The Spectrum of Methodologies

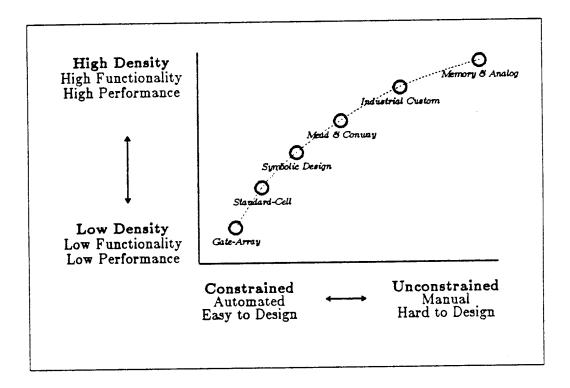

Design methodology and design automation are receiving much attention. There is a large spectrum of design styles in use, ranging from highly constrained, highly automated, low density, gate-array designs to full-custom designs finely tuned to a specific process to achieve maximum density and performance. These methodologies differ in the tradeoff they make between simplifying design constraints on the one hand and ultimate circuit size and performance on the other; see Figure 2.13. The nature of design rules and other constraints employed by the methodologies will be outlined below.

In general, properly chosen constraints can simplify the design process. Such simplifications improve designer productivity directly, since design decisions can be made

Figure 2.13. - Design Cost/Density Tradeoff. There is a basic tradeoff between the degree to which a design method is constrained, and hence automated, quick, and painless on the one hand, and the penalty in circuit density, performance, and functionality engendered by those constraints on the other. Different positions with respect to this tradeoff are appropriate to different projects. A wide spectrum of design methods ranging from fully automated gate-array to hand-tailored analog design are in use.

more quickly and accurately, and indirectly since they facilitate the automation of the design process. On the other hand, more constrained design styles generally lead to less dense and less efficient circuits, resulting in more stringent limits on the maximum functionality per chip, lower performance, and increased production cost. The best methodology to use for a particular product depends on the functionality and performance required, the volume of chips that will be produced, and the particular mix of resources available for design and fabrication. However, it is apparent that over time, as fabrication technology continues to improve, more constrained methodologies will be increasingly favored.

# 2.4.2. Design Rules and Other Constraints Employed by the Methodologies

Table 2.1 summarizes the characteristics of a number of design methodologies. The methods are given in order of increasing design rule complexity. In fully automatic gate array designs [Soukup 1981] the designer does not deal with topo-tolerance rules at all; he works at the netlist level, specifying the gate interconnections required to implement the circuit. A designer using the standard cell approach [Soukup 1981] need not deal with a full set of topo-tolerance rules either, since all devices and hence device rules are encapsulated in the predefined cells. Designers using symbolic design systems [Bales 1979] [Hsueh 1979] work with a more abstract representation than mask data: transistors, contacts, and their interconnections are represented explicitly. Layout is generated automatically and is usually guaranteed to be design-rule correct. The remaining methodologies, i.e., Mead-Conway [Mead & Conway 1980], traditional custom, and memory & analog design, all work directly with the mask layer specification, and all require a full set of topo-tolerance rules. They differ mainly in the number and complexity of the rules employed.

# 2.4.3. The Need for an Automatic Topo-Tolerance Checking Capability.

Regardless of the design methodology used, there must be some automatic method for guaranteeing that the final mask artwork for the design satisfies the topo-tolerance rules for

| Design Methodologies           |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                       |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Method                         | Description & Constraints                                                                                                                                                                                                                                                                                                                                                             | Design Rules                                                                                                                                                                                                                                                                          |

| Gate-Array                     | Predefined, fixed, regular, array of gates with horizontal and vertical wiring channels. Only netlist is specified by designer. Gate assignment and routing of netlist is done automatically.                                                                                                                                                                                         | None.                                                                                                                                                                                                                                                                                 |

| Standard-Cell                  | Predefined library of fixed-height cells. Power and ground routed horizontally through cells at standard locations. Designer selects cells of desired functionality, places cells in rows and routes the signals. External pads must also be placed and routed, and power and ground connections made. No transistors are permitted outside cells. Routing is usually semi-automatic. | Simple width and spacing rules for wiring, with stylized contacts. No transistor rules, since all devices encapsulated in predefined cells.                                                                                                                                           |

| Intelligent Layout<br>Systems. | Designer places and routes devices freely using abstract representations for devices and interconnect. Abstract representation permits stretch/compact operations that preserve integrity of design. Upon completion, abstract representation automatically converted to mask layers.                                                                                                 | Simple width and spacing of interconnect and devices must be considered during automatic generation of mask data. More complex device form rules are not relevant since correct, stylized, devices are automatically generated. Simple rules make automatic stretch/compact feasible. |

| Mead-Conway.                   | Designers strive for regular placement and interconnection schemes that take full advantage of the topological properties of the implementation medium. Simple conservative design rules are used to free designer from messy low-level details.                                                                                                                                      | Full set of topo-tolerance<br>rules. Rulesets are simple,<br>i.e., a small number of<br>mostly unconditional rules.                                                                                                                                                                   |

| Traditional Full<br>Custom.    | Devices are placed and interconnected with emphasis on high density and performance. A set of stylized layouts for gates, memory cells, etc., is developed and used whenever practical.                                                                                                                                                                                               | Elaborate full topotolerance ruleset. Conditional rules allow more precise tolerances to be used, permitting denser design.                                                                                                                                                           |

| Memory and Analog Designs.     | Designers work closely with a particular process to achieve maximum performance and density.                                                                                                                                                                                                                                                                                          | Large complex rulesets with many conditional rules. Rules often depend on anticipated power and signal strength in particular regions of a circuit.                                                                                                                                   |

Table 2.1

the particular process being used: manual checking is unacceptable. The size and complexity of VLSI designs makes manual checking an extremely tedious and error prone process. Even experienced people concentrating on a single rule with diligence miss rule violations [Fitzpatrick et. al. 1981]. Trial fabrication runs on circuits are time consuming (turn around is typically several weeks to several months) and expensive. In addition it is difficult to trouble-shoot finished circuits, even for fatal DRC violations that render the circuit completely nonfunctional. Nonfatal violations contributing to reduced yield, reliability, and performance of the circuit are likely to go completely undetected during circuit testing. Thus the mask artwork must be automatically generated, in a design rule correct way, or accurate automatic design rule checking must be used to eliminate all design rule violations prior to fabrication.

In fact an automatic topo-tolerance checking capability is important regardless of the methodology employed. Although the more constrained methodologies shield the user from much of the detail of topo-tolerance design rules, a topo-tolerance checking capability is still important. Topo-tolerance checking is used for the development and maintenance of systems employing constrained methodologies. For instance the library cells in standard cell systems and the templates for gate-arrays must be verified with a full topo-tolerance DRC. Further, automatic layout generation systems are complex and hence prone to error. Topo-tolerance checking is required to verify the correctness of automatically generated layout.

Topo-tolerance checking is also used to verify that no errors have been introduced during the composition of independently-generated pieces of a circuit into a complete design. Designs often combine elements developed with a variety of tools and within the framework of a variety of systems. Integration and composition of these components is an error-prone process involving multiple format conversions and often manual intervention to complete final placement and route where automatic tools are not available or not quite adequate. Topotolerance checking on the mask data has the advantage that it is done on the final

representation of the design, and thus can catch errors introduced during the final conversion and integration steps: it provides a check on the correctness of all the steps leading to the final design.

This thesis focuses on the automatic checking of full topo-tolerance rules on the mask data for designs.

#### 2.5. Summary

Dense designs are more economical, have better performance characteristics, and allow greater functionality per chip. Design rules codify limitations on the minimum size of circuit components, and hence on the maximum density achievable. These limitations originate from numerous distortions introduced during circuit fabrication and to some extent from the physical characteristics of the fabricated circuits.

Design rules provide an interface between the process engineers and the circuit designers. The process engineers need not concern themselves with the details of the circuits being fabricated as long as they can meet the specified design rules, and the circuit designers need not concern themselves with the details of the fabrication process, as long as they obey the design rules.

Design rules take a topo-tolerance form, that is, they specify tolerances on certain spacing, width, overlap, and extension relationships in the circuit artwork. The intention is that these tolerances are sufficient to maintain the relationships to some minimum acceptable dimension despite process distortions. In general topo-tolerance rules involve relationships between regions defined by combinations of mask layers. Many rules are unconditional: the specified tolerances apply to the artwork relationships wherever they occur throughout the designs. However rules can be conditional on nearby artwork on the same or different layers, on topological relationships (such as node connectivity), on electrical properties, and even on information about the function of the circuit.

Though topo-tolerance rules are the basis for the designer/process interface, the nature of the rules a designer sees directly varies with design methodology. Design methodologies range from highly constrained, automated, low density, methods such as gate-array, to hand-tailored, high-density, high-performance custom designs. The more constrained methodologies shield the designer from low-level details such as a complete set of topo-tolerance rules. Designers using these systems work with simpler, more abstract design rules.