# The SPUR Instruction Unit: An On-Chip Instruction Cache Memory for a High Performance VLSI Multiprocessor

Richard R. Duncombe

Department of Electrical Engineering and Computer Science University of California Berkeley, California 94720

#### ABSTRACT

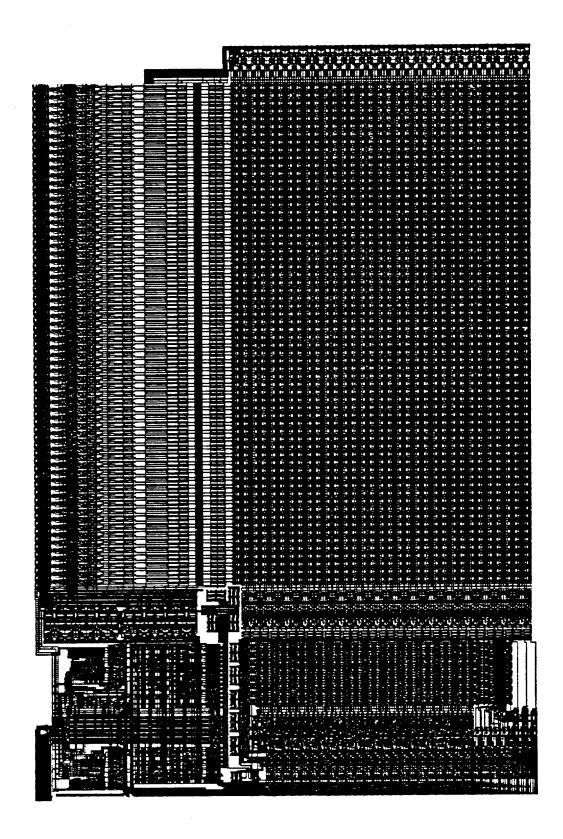

Microprocessor architecture is evolving rapidly as silicon integrated circuits increase in density. On-chip cache memories are becoming an established feature in 32-bit microprocessor designs because they significantly improve performance. Microprocessor performance is degraded by bus contention between instruction and data memory traffic. On-chip instruction caches reduce this contention problem by supplying many of the instructions executed by the microprocessor. The SPUR instruction unit is a direct mapped cache with 512 bytes or 128 instructions. It is organized in sub-blocks to provide efficient instruction fetching and prefetching from the external memory. The SPUR instruction unit is controlled by two finite state machines: one for instruction fetching and one for instruction prefetching. These control functions are implemented using PLA's and standard logic cells. The standard cells are implemented in domino logic to meet speed and area constraints. SPICE simulations indicate that the slowest signal delay path in the instruction unit is 14.7 ns. The SPUR instruction unit contains 39,400 transistors and occupies 4200 x 6000  $\mu m^2$  in a 2  $\mu m$  technology. Area and speed metrics for alternative instruction units indicate that implementations with either larger sub-blocks or two-way associativity will satisfy the SPUR CPU speed requirements. A two-way set-associative implementation would consume approximately 20% more silicon area.

August 8, 1986

#### TABLE OF CONTENTS

## 1. INTRODUCTION

- 1.1 On-Chip Cache Memory Research

- 1.2 On-Chip Cache Memory Implementations

- 1.3 MS Report Outline

## 2. THE SPUR INSTRUCTION UNIT ARCHITECTURE

- 2.1 Overview of the SPUR CPU

- 2.2 SPUR Instruction Unit Architecture

- 2.3 Instruction Unit Interface

- 2.4 Instruction Unit Operation Examples

#### 3. THE SPUR INSTRUCTION UNIT IMPLEMENTATION

- 3.1 Instruction Unit State Description

- 3.2 Control Implementation Philosophy

- 3.3 Fetch and Prefetch Control Implementations

- 3.4 Instruction Buffer Implementation

- 3.5 Tag Comparison & Prefetcher Implementation

## 4. ALTERNATIVE INSTRUCTION CACHE IMPLEMENTATIONS

- 4.1 Memory Array Size

- 4.2 Data Path Width / Sub-block Size

- 4.3 Two-way Associativity

- 4.4 Summary of Implementation Alternatives

## 5. CONCLUSIONS AND SUGGESTIONS FOR FUTURE RESEARCH

**ACKNOWLEDGEMENTS**

REFERENCES

APPENDIX A: LAYOUT PLOTS

APPENDIX B: PLA DESCRIPTIONS

APPENDIX C: SPICE SIMULATION DATA

#### 1. INTRODUCTION

Microprocessor architecture is evolving rapidly to incorporate advances in integrated circuit technology. The most dramatic progress in technology has been achieved in the density of transistors on a single chip. Computer architects must evaluate new alternatives to determine the optimum way to use this increased density.

#### 1.1 On-Chip Cache Memory Research

Research indicated that on-chip cache memories could provide significant performance benefits before technology would support their implementation. Smith commented that more research was necessary to best design on-chip caches [Smith82]. Goodman proposed that small local cache memories were essential for single chip or single board central processor units (CPUs) [Good83]. He argued that the bandwidth between the CPU and memory system would limit performance unless local cache memory was provided. Furthermore, the local cache must not further burden the bus resources. Goodman concluded that the amount of data transferred between the local cache and external memory system should be reduced in designs limited by bus bandwidth. Trace driven simulations by Hill demonstrated benefits of on-chip cache memories in several different computer architectures [Hill84]. Hill also presented data to support 'sub-block' cache memory organizations. Sub-blocks refer to the amount of data that is transferred between the local cache and the external memory system. Two or more sub-blocks and an address tag are contained in each block in the cache. Hill demonstrated that the use of sub-blocks in on-chip cache design reduces bus traffic. However, sub-blocks also reduce the hit ratio of the cache.

## 1.2 On-Chip Cache Memory Implementations

A number of recent microprocessor designs have implemented on-chip cache memories. Two examples are reviewed in this section. The Motorola MC68020 32-bit microprocessor contains a 256-byte instruction cache [Mac84]. The MC68020 instruction cache improves performance by reducing the number of accesses that must be made to the external memory system. The

MC68020 instruction cache only supports basic features. It is a direct mapped cache and does not support prefetching from memory. However, even this basic design has a significant impact on performance. System measurements indicate that 64% of the instructions executed by the MC68020 are contained in the instruction cache [Mac85]. Furthermore, the overall system performance improves by 30% when the instruction cache is enabled.

The Zilog Z80000 microprocessor contains a 256-byte cache memory that supports more complex features [Phil85]. For example, this cache may be configured in one of three ways: instruction cache, data cache, or a unified cache (instructions and data). It also supports fully associative mapping between the instructions address and cache blocks. Trace driven simulations of this cache indicate that the hit ratio should be 60% to 70%. Overall performance of the microprocessor should improve by 20% to 30% [Phil85].

## 1.3 MS Report Outline

This MS report describes an on-chip instruction cache designed for the SPUR project at U.C. Berkeley. The objective of the SPUR (Symbolic Processing Using RISCs) project is to design and build a multiprocessor workstation [Hill85]. A custom 32-bit RISC CPU, cache controller, and floating-point processor are being developed to support the multiprocessing Lisp environment. The instruction cache on the SPUR CPU is referred to as 'the instruction unit' to avoid confusion with the external cache memory in the SPUR system.

The information in this MS report is organized from high-level architectural descriptions to low-level circuit implementation details. Chapter 2 first provides a brief review of the SPUR CPU microarchitecture. The architecture of the instruction unit and its interface to the CPU are then described. The final section in Chapter 2 presents five examples to clarify the operation of the instruction unit. Chapter 3 focuses on the implementation of the SPUR instruction unit. State diagrams illustrate the two finite state machines that exist within the instruction unit. The next section describes the implementation philosophy for the instruction unit control. The final three sections of Chapter 3 discuss the circuit implementations of the control, instruction buffer, tag

comparison, and prefetcher functional blocks. Finally, Chapter 4 examines several implementation parameters including: memory array size, sub-block size, and associativity.

#### 2. THE SPUR INSTRUCTION UNIT ARCHITECTURE

The SPUR instruction unit architecture has been influenced by previous research at U.C. Berkeley. For example, a VLSI cache chip was designed and implemented as a U.C. Berkeley graduate class project [Hill82], [Patt83]. Hill studied trace driven simulations of cache memories suitable for on-chip implementations [Hill84]. The instruction unit architecture was further refined when the functional description of the CPU was written [Kong86a], [Kong86b].

I was not at U.C. Berkeley to participate in the evolution of this architecture. Therefore, I will not address many of the issues and ideas that were considered during its development. However, I describe the final instruction unit architecture in this chapter. In the next chapter I will combine the implementation issues that I faced with this architectural information to provide a cohesive description of the project.

#### 2.1 Overview of the SPUR CPU

This section provides an overview of the SPUR CPU microarchitecture. This information is needed to support the subsequent sections that examine the instruction unit architecture and implementation. The CPU microarchitecture will be documented in a dissertation by Shing Kong. The implementation issues for the execution unit will be written by Dave Lee and Wook Koh. The clock generation circuits and PLA templates will be documented by Deog-Kyoon Jeong.

CPU Functional Description: At the highest level, the SPUR CPU contains two functional units: the execution unit (EUnit) and the instruction unit (IUnit). These two functional units contain separate control blocks as in a traditional board-level CPU implementation. The SPUR CPU, however, takes advantage of the EUnit and IUnit integration by sharing four wide busses. The pin count for these busses alone (102 pins) uses most of the available SPUR CPU signal pins. The instruction unit interface is presented in section 2.3.

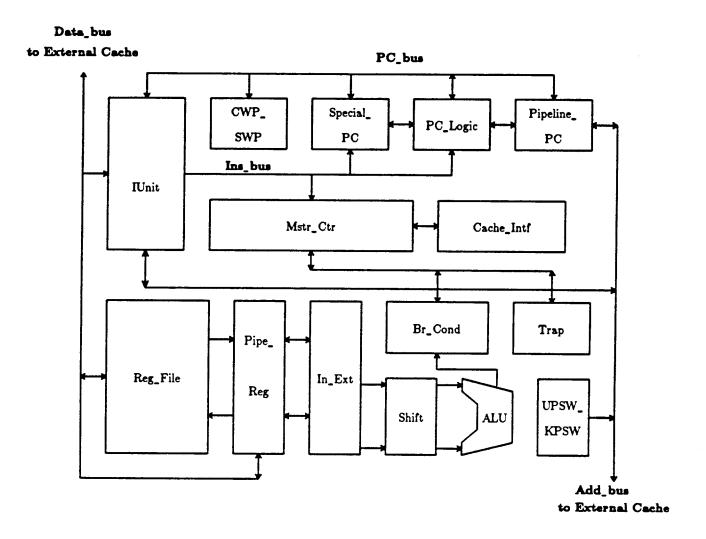

The block diagram in Figure 2-1 shows the key functional blocks of the CPU. The EUnit data path is naturally divided into two parts. The lower datapath performs most of the register to register instructions and initiates branch and trap activities. The upper datapath maintains

the program counter and register window pointers. It also calculates the destination address for all compare and branch instructions. The following paragraphs describe each block in Figure 2-1 from left to right and bottom to top [Kong86a].

Reg\_File:

A 138 word by 40 bit register file which supports dual port reads and single port writes. This register file is organized as 8 overlapping register windows with 32 registers in each window.

Pipe\_Reg:

This block contains three datapath latches. Each latch is 40-bits wide. Two latches store data read and written from the register file to make it available during the proper pipeline stage. The other latch stores data that will be transferred to the Data\_bus. The information on the Data\_bus is written to the external cache memory.

In\_Ext:

This block inserts and extracts bytes for tag manipulation.

Shift:

This is a 3-bit shifter for the ALU.

ALU:

Performs A+B, A-B, A XOR B, A AND B, and A OR B.

UPSW\_KPSW: Special Registers for the User Process Status Word and the Kernal Process

Status Word.

Br\_Cond:

Uses ALU information to evaluate the conditions for the compare and branch instructions.

Trap:

Generates trap requests for unusual conditions.

IUnit:

The IUnit receives instruction requests on the program counter bus (PC\_bus) from the EUnit. The IUnit sends instructions on the instruction bus (Ins\_bus) to the Mst\_Ctr block. The IUnit also initiates fetches and prefetches on the Add\_bus and loads instructions from the Data\_bus.

Mst\_Ctr:

The master control block decodes the instruction OP codes into high-level control signals for the rest of the CPU. High-level control signals from the Mst\_Ctr do not directly connect to the data path circuits. These signals

provide communication between the Mst\_Ctr block and other local control blocks within the CPU. Since the CPU supports a four stage pipeline, the master control must deliver each signal for an instruction during the correct cycle. Further decoding and control is performed locally in many of the other blocks. This will be clarified further in chapter 3 when the IUnit control is described.

Cache\_Intf: This block communicates with the external cache controller chip.

CWP\_SWP: Special registers for the Current Window Pointer and the Saved Window Pointer in the register file.

Special\_PC: Three special program counters are maintained in this block: TrapPC, CallPC, and KernalPC.

PC\_Logic: This block maintains the special program counters and the pipeline program counters. It contains a 30-bit adder to calculate the destination address for all the compare and branch instructions.

Pipeline\_PC: The program counter for each instruction in the execution pipeline is stored in this block.

Execution Unit Pipeline: The pipeline design in the EUnit influenced almost all other parts of the CPU microarchitecture. A four stage pipeline was selected to ideally allow one instruction to execute every cycle. Instruction unit misses and external cache misses prevent the ideal case from being achieved [Hill85]. A four phase non-overlapping clocking scheme was selected to support the pipeline. The pipeline stages are listed below [Kong86a]:

Ins\_Fet: Instruction is fetched from the IUnit to the EUnit.

Execution: The instruction is executed. Instructions that access memory calculate the effective address during this cycle.

Memory: All instructions that access memory do so in this cycle. This is a null cycle for other instructions.

Figure 2-1: CPU Block Diagram

Reg\_Write: The register file is written into during this cycle.

Pipeline Suspension: Two suspension mechanisms are provided in the SPUR EUnit pipeline: global and partial [Kong86a]. The IUnit responds differently for each case. In the former, everything in the pipeline is 'frozen'. The IUnit continues to send out the last instruction repeatedly until the suspension ends. Partial suspension allows the instructions already in the pipeline to complete execution. The IUnit feeds an internally generated 'MISS' instruction until the suspension ends.

Trap Request Handling: The trap request handling mechanism in the EUnit microarchitecture is also coordinated with the IUnit. When a trap occurs, the instructions in the first three

pipeline stages are 'killed' [Kong86a]. The IUnit then issues two internally generated instructions to the EUnit. First, a TRAP\_CALL instruction initiates execution of the trap handler software. The next instruction executed, READ\_PC, is also issued by the IUnit. This internally generated instruction saves the program counter for the 'killed' instruction. The trap handler software begins to execute after the READ\_PC instruction.

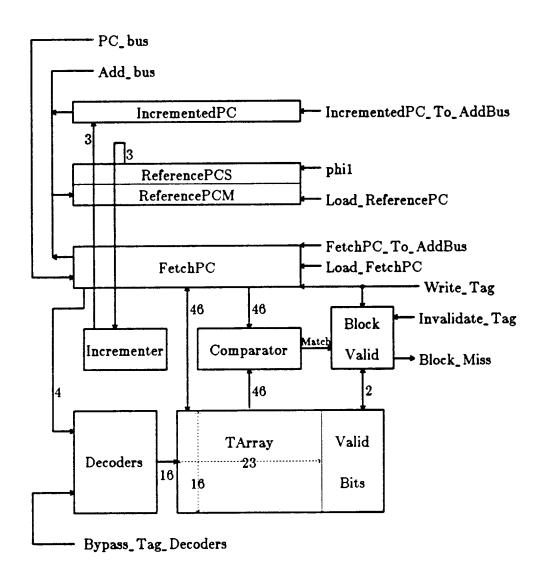

#### 2.2 SPUR Instruction Unit Architecture

The primary motivation for an on-chip instruction cache is to reduce contention for the external cache [Hill85]. If the CPU was dependent on the external cache for both instructions and data references, the pipeline would have to stall on every data reference. Other options such as two cache ports on the CPU or using an interleaved external cache were rejected because of the increased hardware cost [Hill86a]. The on-chip instruction unit relieves this external cache bottleneck by providing the illusion of a parallel memory port for the execution unit. Therefore, the execution unit may get an instruction and a data reference in the same cycle as long as there is a hit in the IUnit. A second benefit is that the latency time for instructions is reduced for the CPU. In the SPUR implementation, the IUnit has a latency time of approximately one half cycle. The external cache has a one cycle latency time. The CPU control takes advantage of this reduced latency. Control signals sent to the IUnit from the CPU Mst\_Ctr block arrive approximately one half cycle later than signals sent to the external cache.

Instruction Unit Organization: The IUnit is a 512-byte, direct mapped cache. It is organized into 16 blocks with each block containing 32 bytes. The cache contains 128 instructions (4-bytes per instruction). Therefore, each block contains 8 instructions which are referred to as 'sub-blocks'. Several advantages of using sub-blocks on small on-chip caches memories have been reported [Good83], [Hill84]. Perhaps the most significant advantage is that the memory traffic is reduced because only required sub-blocks are loaded. This is important for the SPUR IUnit because instruction memory traffic coinciding with data traffic forces the EUnit pipeline to stall. Unfortunately, sub-blocks also cause the miss ratio to increase because several misses may occur

in the same block [Hill84].

Instruction Virtual Address Fields: The IUnit divides the instruction address into three address fields. The implementation of the instruction memory array and tag comparison logic is based on the following address fields:

- 1. Sub-Block Address Field <3 bits> selects one of 8 sub-blocks

- 2. Block Address Field <4 bits > selects one of 16 blocks

- 3. Address Tag Field <23 bits> highest order instruction address bits that identify the present address tag for each block.

The advantages of using on-chip instruction cache memories have been demonstrated in both simulations and system measurements [Good83], [Hill84], [Mac85]. Implementing an on-chip cache introduces several system problems that must be overcome. For example, self modifying programs may alter the instruction stream stored in the main memory. The SPUR architecture avoids this problem by requiring that software invalidates the IUnit before executing a modified instruction stream. A similar problem is encountered when software changes the mapping of process-specific addresses to global addresses [Hill86b]. This typically occurs as a result of a context switch. The SPUR architecture solves this problem by requiring software to invalidate the IUnit whenever this mapping is changed.

The CPU design is simplified because the SPUR architecture forbids modifications in the virtual address space without software intervention Without this restriction, the EUnit pipeline and the IUnit would have to check for self modifying code [Hill86b]. In other words, the EUnit would have to determine whether instructions already in the pipeline had been modified and the IUnit would have to determine if it had 'stale' instructions cached.

Prefetching on Misses: The sub-block organization in the IUnit supports a prefetching algorithm that is initiated by misses. When a Miss occurs, the EUnit is passed a 'MISS' instruction from the IUnit and a memory fetch is initiated. The external cache returns one instruction or sub-block so that the EUnit may resume operation. The IUnit will then try to prefetch the

remainder of the block in sequential order. In the ideal case, the prefetcher will prevent any additional misses within the same block. The conditions that must be satisfied in the ideal case are: (1) the EUnit is executing sequential code in the same block, and (2) the EUnit must make no data references to the external cache. The prefetcher does not burden the CPU to external cache interface because it is overridden by either an instruction miss or a data reference. More detailed sequences of operation are described in section 2.4.

The 'prefetch-on-miss' algorithm and sub-block architecture implemented in the SPUR IUnit have several notable advantages and disadvantages. The primary advantage of only fetching a sub-block is that the instruction miss can be satisfied more quickly by the external cache [Hill85]. This assumes that the CPU package has a limited number of pins available and that a block is always larger than a single instruction. The first assumption was confirmed in the SPUR CPU implementation as the limited package pins had to be carefully allocated. Alternative data bus widths between the IUnit and external cache are discussed in chapter 4. The second assumption is also safe when considering the overhead for the address tag implementation. This overhead is reduced by a factor of n when a group of n sub-blocks are used [Hill84].

The disadvantages of supporting sub-blocks are increased silicon area and decreased speed. Each sub-block must have a valid bit in addition to its block valid bit. I estimate that 4% of the total IUnit area was used by the sub-block valid bits and associated circuitry. Speed is reduced because the sub-block valid bit must be read from the instruction array and sent to the IUnit control block. This is the critical signal delay path in the entire IUnit implementation (14.7 ns typical). The critical signal delay path would decrease by 2.2 ns if the sub-block valid bit was not necessary. Simulation results are presented in section 3.4.

The SPUR IUnit prefetching algorithm continuously prefetches from one demand miss to the next demand miss. When the prefetcher reaches the end of a block, it continues prefetching at the beginning of the same block. At first glance, this algorithm could be viewed as wasteful since the prefetcher may actually prefetch sub-blocks that are already valid (that it previously fetched or prefetched). However, the prefetcher is always overridden when there is real work to do like

instruction misses or data references, and the implementation is simplified because only a 3-bit incrementer is required.

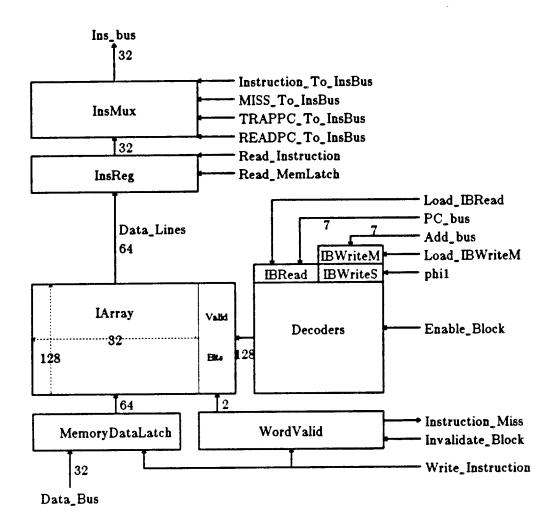

#### 2.3 Instruction Unit Interface

The instruction unit interface serves several purposes. It coordinates the two finite state machines in the IUnit, fetch and prefetch, with the CPU master control finite state machine. The interface also allows the IUnit to monitor the external cache controller chip. Finally, the interface provides four wide busses for instruction address and data movement. Previous work at U.C. Berkeley has helped refine this interface. A single-chip instruction cache explored CPU to cache interfaces so that on-chip caches could be effectively integrated when technology would permit [Patt83], [Hill84].

The control signals and busses that make up the IUnit interface are listed in Table 2-1. All signals or busses in the interface pass through the EUnit. However, the Cache\_Busy and Cache\_Data\_Valid signals are initiated by the external cache (ECache). To avoid confusion, I will always describe the state of signals as either true or false. If a signal is true, then the action or condition indicated by that signals name is presently valid. For example, if I state that Cache\_Busy is true, this indicates that the external cache is presently busy.

#### 2.4 Instruction Unit Operation Examples

This section will illustrate the architectural information presented so far with some examples. These examples emphasize the IUnits operation. Therefore, simplifications are often made about the EUnit or the external cache. The internal activity within the IUnit is also simplified in order to avoid unnecessary detail. The internal operation is further discussed in Chapter 3.

Each of the following five examples include a verbal description and a table. The table summarizes the IUnit operation during a sequence of CPU cycles. The IUnit inputs and outputs refer to the signals and busses presented in the previous section. Internal actions taken by the IUnit

| Signal or Bus Name                         | Functional Description                                    |  |  |  |

|--------------------------------------------|-----------------------------------------------------------|--|--|--|

| Execution Unit to Instruction Unit Signals |                                                           |  |  |  |

| Reset_IUnit                                | Resets the IUnit from any previous state                  |  |  |  |

| IUnit_KPSW_Set                             | Single Bit in the KPSW sets the enabled condition         |  |  |  |

| Prefetch_KPSW_Set                          | Single Bit in the KPSW sets the prefetch condition        |  |  |  |

| Pipeline_Not_Suspended                     | Indicates no Global Pipeline Suspension in EUnit          |  |  |  |

| Load_OPCode                                | Load Instruction is being executed by the CPU             |  |  |  |

| Store_OPCode                               | Store Instruction is being executed by the CPU            |  |  |  |

| lowTOup_OPCode                             | Lower and upper data paths are using the Add_bus          |  |  |  |

| Invalidate_OPCode                          | Invalidate IUnit Instruction is being executed by the CPU |  |  |  |

| Invalidate_Trap                            | EUnit is servicing a Trap that invalidates the IUnit      |  |  |  |

| External Cache to Instruction Unit Signals |                                                           |  |  |  |

| Cache_Busy                                 | Indicates that the ECache is busy                         |  |  |  |

| Cache_Data_Valid                           | Indicates that the ECache data is valid on the Data_bus   |  |  |  |

| Instruction Unit to Execution Unit Signals |                                                           |  |  |  |

| Fetch_Request                              | Indicates that the IUnit is fetching an instruction       |  |  |  |

| Prefetch_Request                           | Indicates that the IUnit is prefetching an instruction    |  |  |  |

| Instruction Unit / Execution Unit Busses   |                                                           |  |  |  |

| PC_bus <30 bits>                           | Transfers program counter from EUnit to IUnit             |  |  |  |

| Add_bus <30 bits>                          | Connects IUnit and EUnit to the ECache address pads       |  |  |  |

| Ins_bus <32 bits>                          | Transfers instructions from the IUnit to the EUnit        |  |  |  |

| Data_bus <40 bits>                         | Connects IUnit and EUnit to the ECache data pads          |  |  |  |

Table 2-1: Instruction Unit Interface

are also indicated in the table. For clarity, all the sequence examples assume that the IUnit starts in the same state: FET\_normal and PF\_prefetch. The IUnit is in the FET\_normal state if the last instruction requested by the EUnit was a hit. The PF\_prefetch state indicates that the IUnit is actively trying to prefetch sequential instructions. These instruction unit states are further described in section 3.1.

IUnit Operation Example - Ideal Instruction Miss: An ideal instruction miss refers to the shortest possible sequence to fetch a missed instruction. This corresponds to a two cycle delay in the SPUR CPU. In order for this ideal sequence to occur, the external cache must not be busy. This operation example is described in full to clarify some of the cryptic notations used in Table

Cycle 1: During phi1 of cycle 1, the EUnit requests an instruction from the IUnit. The program counter (ins\_add[i]) is the address of the next instruction needed by the EUnit. The IUnit detects that it does not contain this instruction (Miss) during phi2. The IUnit then initiates a partial pipeline suspension in the EUnit by sending an internally generated MISS instruction (ins[MISS]) on the Ins\_bus. During phi4, the instruction unit fetches the missed instruction with address (ins\_add[i]) from the external cache.

Cycle 2: The IUnit waits during phil and phil for the Data\_Valid signal from the external cache. A second internal MISS instruction is sent out during phil. In phil the IUnit accepts the fetched instruction (ins[i]) from the external cache and writes it into its memory array. It also initiates a prefetch for the next sequential instruction (ins\_add[i]+1).

Cycle 3: This cycle demonstrates a Hit in the IUnit. The EUnit again supplies the address of the program counter (ins\_add[i]) to the IUnit. Since this instruction was just fetched from memory, the IUnit detects a Hit in phi2. During phi3, the requested instruction is sent to the EUnit thereby ending the partial pipeline suspension. Finally, in phi4, the IUnit accepts the prefetched instruction (ins[i]+1) from the external cache and writes it into its memory array. It again initiates a prefetch for the next sequential instruction (ins\_add[i]+2) from the ECache.

## Instruction Unit Inputs

## Instruction Unit Outputs

| Cycle 1                                 |      | state(FET_normal, PF_prefetch)                   |  |

|-----------------------------------------|------|--------------------------------------------------|--|

| EUnit requests ins_add[i] on the PC_bus | phil |                                                  |  |

|                                         | phi2 | IUnit detects a Miss for ins_add[i]              |  |

| ECache is not Busy                      | phi3 | IUnit sends ins[MISS] to EUnit<br>on the Ins_bus |  |

|                                         | phi4 | IUnit sends ins_add[i] to ECache on the Add_bus  |  |

| Cycle 2                                             |      | state(FET_memPending, PF_waiting)                 |

|-----------------------------------------------------|------|---------------------------------------------------|

| IUnit ignores the PC_bus                            | phil |                                                   |

|                                                     | phi2 | IUnit waiting for ECache Data                     |

| ECache data is valid                                | phi3 | IUnit sends ins[MISS] to EUnit on the Ins_bus     |

| IUnit accepts ins[i] from ECache<br>on the Data_bus | phi4 | IUnit sends ins_add[i]+1 to ECache on the Add_bus |

| Cycle 3                                               |      | state(FET_normal, PF_prefetch)                    |  |

|-------------------------------------------------------|------|---------------------------------------------------|--|

| EUnit requests ins_add[i] on the PC_bus               | phi1 |                                                   |  |

|                                                       | phi2 | Unit detects a Hit for ins_add[i]                 |  |

| ECache data is valid                                  | phi3 | IUnit sends ins[i] to EUnit on the Ins_bus        |  |

| IUnit accepts ins[i]+1 from ECache<br>on the Data_bus | phi4 | IUnit sends ins_add[i]+2 to ECache on the Add_bus |  |

Table 2-2: IUnit Operation Example - Ideal Instruction Miss

IUnit Operation Example - Invalidate: The EUnit can invalidate the IUnit either by executing an invalidate instruction or servicing a trap that causes invalidation. The IUnit overwrites all block valid tags in phi2 of the cycle that receives the invalidate request. Table 2-3 shows that the instruction unit recovers quickly from an invalidate request. In the ideal case, an invalidate request only suspends the pipeline for two cycles. This is because the IUnit may start a fetch in phi4 of the cycle that receives the invalidate request.

#### Instruction Unit Inputs

## Instruction Unit Outputs

| Cycle 1                                 |      | state(FET_normal, PF_prefetch)                   |

|-----------------------------------------|------|--------------------------------------------------|

| EUnit requests ins_add[i] on the PC_bus | phil |                                                  |

| EUnit Invalidates IUnit                 |      |                                                  |

|                                         | phi2 | All block valid tags are invalidated             |

| ECache is not Busy                      | phi3 | IUnit sends ins[MISS] to EUnit<br>on the Ins_bus |

| IUnit ignores Data_bus                  | phi4 | IUnit sends ins_add[i] to ECache on the Add_bus  |

| Cycle 2                                             |      | state(FET_memPending, PF_waiting)                 |

|-----------------------------------------------------|------|---------------------------------------------------|

| IUnit ignores the PC_bus                            | phil |                                                   |

|                                                     | phi2 | IUnit waiting for ECache Data                     |

| ECache data is valid                                | phi3 | IUnit sends ins[MISS] to EUnit<br>on the Ins_bus  |

| IUnit accepts ins[i] from ECache<br>on the Data_bus | phi4 | IUnit sends ins_add[i]+1 to ECache on the Add_bus |

| Cycle 3                                               |      | state(FET_normal, PF_prefetch)                    |  |

|-------------------------------------------------------|------|---------------------------------------------------|--|

| EUnit requests ins_add[i] on the PC_bus               | phil |                                                   |  |

|                                                       | phi2 | IUnit detects a Hit for ins_add[i]                |  |

| ECache data is valid                                  | phi3 | IUnit sends ins[i] to EUnit on the Ins_bus        |  |

| IUnit accepts ins[i]+1 from ECache<br>on the Data_bus | phi4 | IUnit sends ins_add[i]+2 to ECache on the Add_bus |  |

Table 2-3: IUnit Operation Example - Invalidate

IUnit Operation Example - Reset Followed by a Hit: The EUnit can put the IUnit into a known state from any previous state by asserting the Reset signal. The IUnit starts a sequence of actions as soon as Reset is true. The reset mechanism in the instruction unit is used to support several system level activities. For example, traps, page faults, and system power-up sequences use the IUnit reset feature.

The operation example, shown in Table 2-4, illustrates several other features supported by the IUnit during resets. First, a reset request from the EUnit does not invalidate the instructions cached in the IUnit. It does force the IUnit to ignore any pending fetches or prefetches. Secondly, this example demonstrates the sequence of internally generated instructions sent from the IUnit to the EUnit. During phi2 of cycle 1, the EUnit requests the IUnit to reset. In phi3 of the same

cycle, the IUnit sends a TRAP\_CALL instruction to the EUnit. The READ\_PC instruction is sent to the EUnit during phi3 of cycle n. The EUnit discontinued the reset on phi2 of this cycle. The final IUnit feature that this example illustrates is the prefetch-on-miss algorithm. Cycle n+1 was chosen to be an instruction Hit even though this is unlikely. The prefetcher remains idle until a miss, invalidation, or global suspension occurs. In most typical sequences, however, a miss will occur after a reset. Therefore, the prefetcher will resume its prefetching activities.

## Instruction Unit Inputs

## Instruction Unit Outputs

| Cycle 1                                 |      | state(FET_normal, PF_prefetch)                     |

|-----------------------------------------|------|----------------------------------------------------|

| EUnit requests ins_add[i] on the PC_bus | phi1 |                                                    |

| EUnit Resets IUnit                      | phi2 |                                                    |

|                                         | phi3 | IUnit sends ins[TRAP_CALL] to EUnit on the Ins_bus |

| IUnit ignores Data_bus                  | phi4 |                                                    |

| Cycle n                        |      | state(FET_reset, PF_reset)                       |

|--------------------------------|------|--------------------------------------------------|

| IUnit ignores the PC_bus       | phil |                                                  |

| EUnit discontinues IUnit Reset | phi2 |                                                  |

|                                | phi3 | IUnit sends ins[READ_PC] to EUnit on the Ins_bus |

| IUnit ignores Data_bus         | phi4 |                                                  |

| Cycle n+1                               |      | state(FET_normal, PF_idle)                                              |  |

|-----------------------------------------|------|-------------------------------------------------------------------------|--|

| EUnit requests ins_add[i] on the PC_bus | phil |                                                                         |  |

|                                         | phi2 | IUnit detects a Hit for ins_add[i]                                      |  |

|                                         | phi3 | IUnit sends ins[i] to EUnit on the Ins_bus                              |  |

| IUnit ignores Data_bus                  | phi4 | Prefetcher idle until a Miss,<br>Invalidate or Global Suspension occurs |  |

Table 2-4: IUnit Operation Example - Reset Followed by a Hit

IUnit Operation Example - Trap: The trap sequence, shown in Table 2-5 is quite similar to the the preceding reset example. The EUnit uses the reset mechanism to initiate the sequence of internally generated instructions: TRAP\_CALL and READ\_PC. In this example, the IUnit detects a miss after the READ\_PC instruction. This is a more realistic case since it is unlikely that the trap handler instructions would be cached by the IUnit.

## Instruction Unit Inputs

#### Instruction Unit Outputs

| Cycle 1                                 |      | state(FET_normal, PF_prefetch)                     |

|-----------------------------------------|------|----------------------------------------------------|

| EUnit requests ins_add[i] on the PC_bus | phil |                                                    |

| EUnit Resets IUnit                      | phi2 |                                                    |

|                                         | phi3 | IUnit sends ins[TRAP_CALL] to EUnit on the Ins_bus |

| IUnit ignores Data_bus                  | phi4 |                                                    |

| Cycle 2                        | state(FET_reset, PF_reset) |                                                 |  | state(FET_reset, PF_reset) |  |

|--------------------------------|----------------------------|-------------------------------------------------|--|----------------------------|--|

| IUnit ignores the PC_bus       | phi1                       |                                                 |  |                            |  |

| EUnit discontinues IUnit Reset | phi2                       |                                                 |  |                            |  |

|                                | phi3                       | IUnit send ins[READ_PC] to EUnit on the Ins_bus |  |                            |  |

| IUnit ignores Data_bus         | phi4                       |                                                 |  |                            |  |

| Cycle 3                                 |      | state(FET_normal, PF_idle)                      |

|-----------------------------------------|------|-------------------------------------------------|

| EUnit requests ins_add[i] on the PC_bus | phil |                                                 |

|                                         | phi2 | IUnit detects a Miss for ins_add[i]             |

| ECache is not Busy                      | phi3 | IUnit sends ins[MISS] to EUnit on the Ins_bus   |

| IUnit ignores Data_bus                  | phi4 | IUnit sends ins_add[i] to ECache on the Add_bus |

| Cycles 4 & 5 | Same as Cycles 2 & 3 in Ideal | Miss (Table 2-2) |

|--------------|-------------------------------|------------------|

Table 2-5: IUnit Operation Example - Trap

IUnit Operation Example - Global Pipeline Suspension The final IUnit operation example is shown in Table 2-6. This sequence illustrates the interaction between the EUnit and the IUnit during a global pipeline suspension. Cycle 1, which is an IUnit Hit, sends the requested instruction (ins[i]) to the EUnit on phi3. The IUnit latches this instruction internally on phi2. During phi1 of cycle 2, the EUnit signals a global pipeline suspension. The IUnit responds by repeatedly sending out the last instruction (ins[i]) to the EUnit on phi3. The prefetcher could remain active during a global pipeline suspension as shown in cycle 2. This is unlikely, however, because any other request for the external cache disables the prefetcher. In cycle n, after the pipeline suspension has ended, the IUnit resumes normal operation.

# Instruction Unit Inputs

# Instruction Unit Outputs

| Cycle 1                                 |      | state(FET_normal, PF_prefetch)                     |  |  |

|-----------------------------------------|------|----------------------------------------------------|--|--|

| EUnit requests ins_add[i] on the PC_bus | phi1 |                                                    |  |  |

|                                         | phi2 | IUnit detects a Hit for ins_add[i]                 |  |  |

| ECache is not Busy                      | phi3 | IUnit sends ins[i] to EUnit<br>on the Ins_bus      |  |  |

|                                         | phi4 | IUnit sends ins_add[i]+1 to ECache on the Data_bus |  |  |

| Cycle 2                                               |      | state(FET_normal, PF_prefetch)                    |  |  |

|-------------------------------------------------------|------|---------------------------------------------------|--|--|

| EUnit signals Global Pipeline Suspension              | phil |                                                   |  |  |

|                                                       | phi2 | Unit does not read a new instruction              |  |  |

| ECache data is valid                                  | phi3 | IUnit sends ins[i] to EUnit on the Ins_bus        |  |  |

| IUnit accepts ins[i]+1 from ECache<br>on the Data_bus | phi4 | IUnit sends ins_add[i]+2 to ECache on the Add_bus |  |  |

| Cycle n                                            |      | state(FET_normal, PF_prefetch)                    |  |  |

|----------------------------------------------------|------|---------------------------------------------------|--|--|

| EUnit requests ins_add[i]+1 on the PC_bus          | phi1 |                                                   |  |  |

| EUnit ends Global Pipeline Suspension              |      |                                                   |  |  |

|                                                    | phi2 | IUnit detects a Hit for ins_add[i]+1              |  |  |

| ECache Data is valid                               | phi3 | IUnit sends ins[i]+1 to EUnit<br>on the Ins_bus   |  |  |

| IUnit accepts ins[i]+2 from ECache on the Data_bus | phi4 | IUnit sends ins_add[i]+3 to ECache on the Add_bus |  |  |

Table 2-6: IUnit Operation Example - Global Pipeline Suspension

#### 3. THE SPUR INSTRUCTION UNIT IMPLEMENTATION

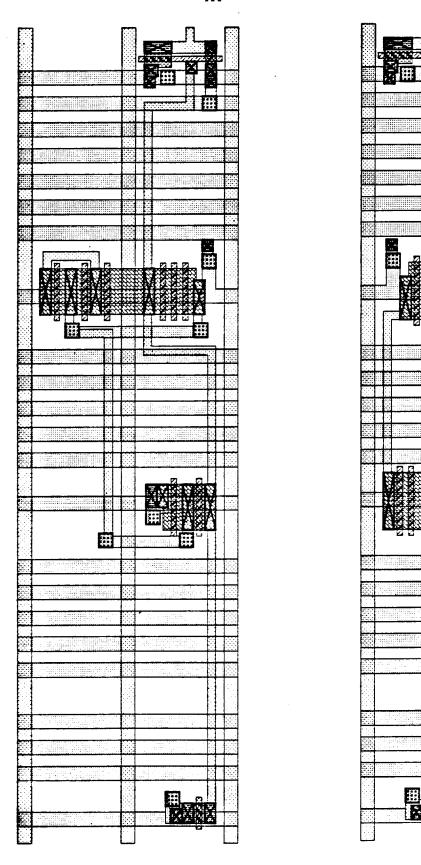

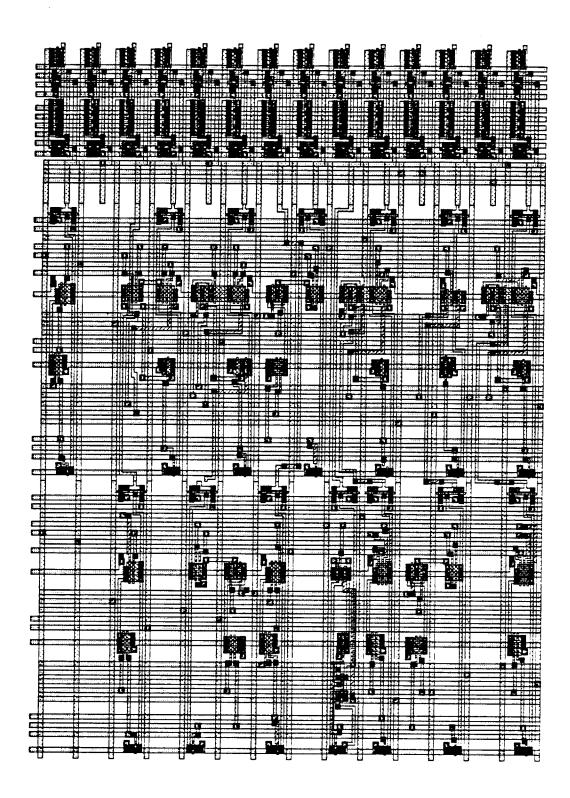

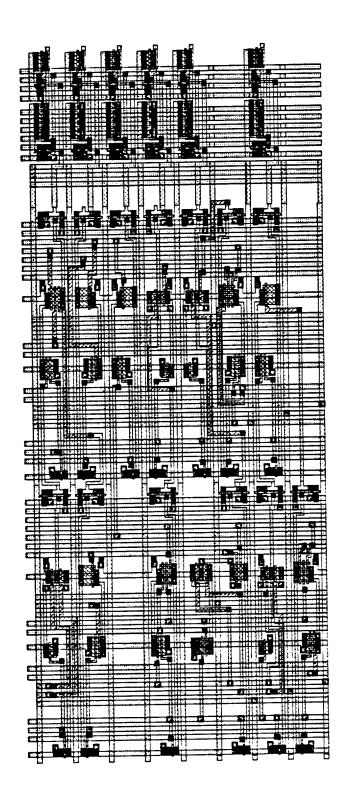

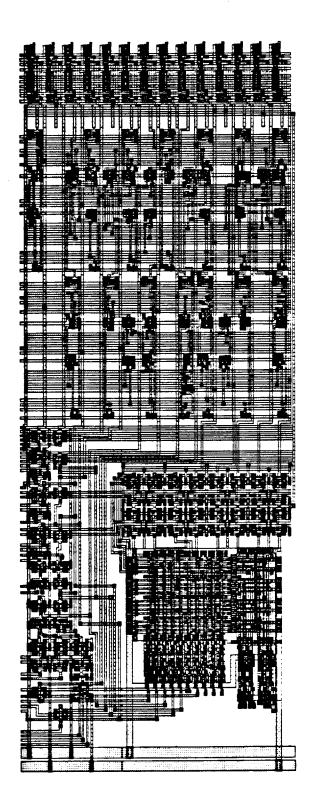

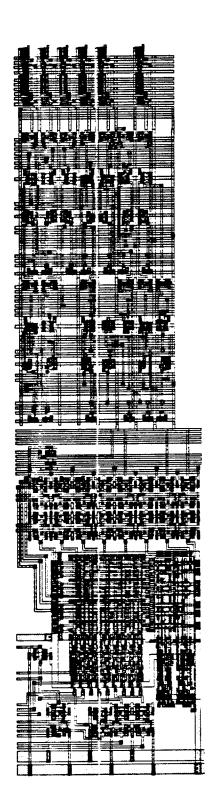

The architectural decisions described in the previous chapters take on different meanings when the implementation issues are also considered. The purpose of this chapter is to highlight the implementation of the SPUR CPU instruction unit. It serves as a benchmark for future instruction cache implementations. A layout plot of the IUnit is shown in Figure A-1 in Appendix A. The information in this chapter is arranged in a hierarchical fashion for the convenience of both casual readers and those hungry for details. First, a state machine description of the IUnit is provided to clarify its operation. The IUnit is then dissected into four parts: control, instruction buffer, tag comparison, and prefetcher.

#### 3.1 Instruction Unit State Description

Two finite state machines exist within the IUnit: the fetch finite state machine (Fetch\_FSM) and the prefetch finite state machine (Prefetch\_FSM). The input signals to these two finite state machines are shown in Table 3-1. The first seven input signals (Reset > Flush) are simple derivatives of the IUnit interface signals presented in section 2.3. The Miss signal is derived from two signals internal to the IUnit: Block\_Miss and Instruction\_Miss. These signals are discussed further in sections 3.4 and 3.5. The final signal, Starting\_Prefetch, is the only connection between the Fetch\_FSM and the Prefetch\_FSM. Starting\_Prefetch is used to implement the prefetch-on-miss algorithm. The Fetch\_FSM tells the Prefetch\_FSM that it can begin prefetching after a Miss, Flush, or a Global\_Suspension are true.

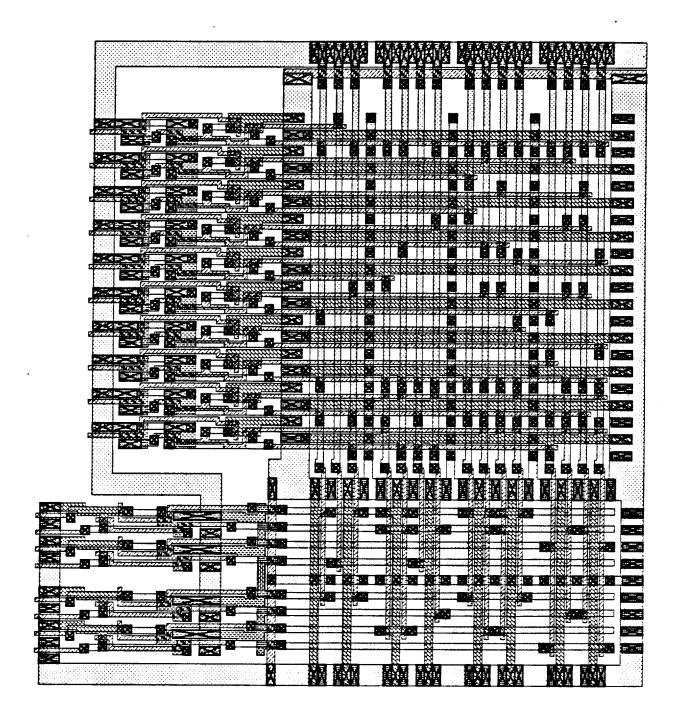

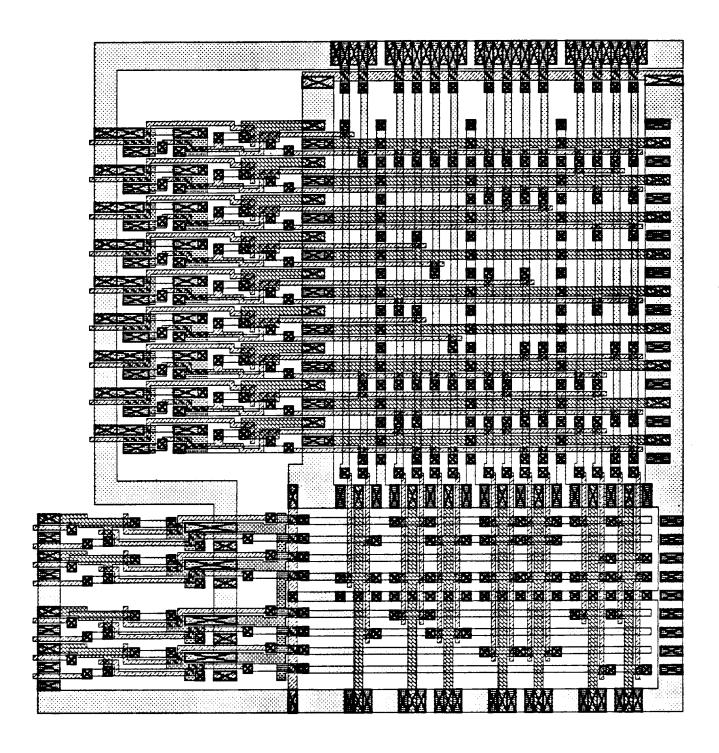

In both the Fetch\_FSM and Prefetch\_FSM, the next state is determined by the input signals in Table 3-1 and the previous state. A programmed logic array (PLA) determines the next state during phi4. A new state officially begins on every phi1. Two sets of dynamic latches are used in conjunction with the PLA's. The first set of latches captures the next state on phi4. The second set of latches, which hold the present state, are updated on phi1. The PLA's for the Fetch\_FSM and the Prefetch\_FSM are shown in Figures A-2 and A-3 respectively in Appendix A. The finite state machine descriptions for both PLA's are included in Appendix B.

| Signal Name       | Origin of Signal                                                                        |  |  |

|-------------------|-----------------------------------------------------------------------------------------|--|--|

| Reset             | Same as Reset_IUnit signal                                                              |  |  |

| IUnit_Enable      | Latched version of IUnit_KPSW_Set signal                                                |  |  |

| Prefetch_Enable   | Latched version of Prefetch_KPSW_Set signal                                             |  |  |

| Global_Suspension | Latched version of Pipeline_Not_Suspended                                               |  |  |

| Memory_Busy       | Cache_Busy AND NOT(Cache_Data_Valid) OR (Load_OPCode OR Store_OPCode OR lowTOup_OPCode) |  |  |

| Data_Valid        | Latched version of Cache_Data_Valid signal                                              |  |  |

| Flush             | Invalidate_OPCode OR Invalidate_Trap                                                    |  |  |

| Miss              | Block_Miss OR Instruction_Miss                                                          |  |  |

| Starting_Prefetch | Signal from the Fetch_FSM to the Prefetch_FSM                                           |  |  |

Table 3-1: Instruction Unit Control Input Signals

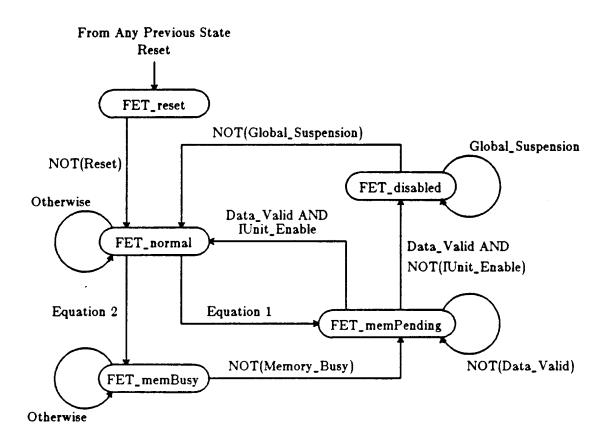

Fetch Finite State Machine: The Fetch\_FSM controls most of the activities in the instruction unit. The state of the Fetch\_FSM is combined with other inputs to determine whether the IUnit transfers instructions to the EUnit (Ins\_bus), fetches instructions from the external cache (Add\_bus), or accepts data from the external cache (Data\_bus). The Fetch\_FSM is controlled by seven of the input signals in Table 3-1: Reset, IUnit\_Enable, Global\_Suspension, Memory\_Busy, Data\_Valid, Flush, and Miss. The Fetch\_FSM consists of five states as shown in Figure 3-1. Each state is briefly described below.

FET\_reset: The Reset signal forces the Fetch\_FSM into the FET\_reset state from any previous state. It will remain in this state as long as Reset is true. The IUnit engages in the following activities while in the FET\_reset state:

- 1. The IUnit ignores the program counter from the EUnit (PC\_bus).

- 2. The IUnit does not read or write any instructions or address tags from its memory arrays. Previous fetches or prefetches from the ECache are ignored.

- 3. The IUnit sends out the READ\_PC internal instruction repeatedly to the EUnit (Ins\_bus) during phi3. The TRAP\_PC instruction has already been sent out on the previous cycle. In other words, the TRAP\_PC signal is generated after the Reset signal is true and before the IUnit moves into the FET\_reset state.

- 4. No Fetches are initiated by the IUnit.

- 5. The Fetch\_FSM keeps Starting\_Prefetch false so that the Prefetch\_FSM does not initiate any prefetches.

FET\_normal: The Fetch\_FSM moves to the FET\_normal state on the cycle after the Reset signal is false. Changes on the Reset, Global\_Suspension, Miss, or Flush signals move the Fetch\_FSM out of the FET\_normal state. The IUnit performs the following activities while

#### in the FET\_normal state:

- 1. The IUnit latches the program counter from the EUnit (PC\_bus). In effect, the IUnit has accepted an instruction request from the EUnit.

- 2. The IUnit may read and write instructions and address tags from its memory arrays. These actions are also dependent on other input signals. For example, the IUnit only writes information into the instruction memory array when Data\_Valid is true.

- 3. The IUnit passes one of three instructions to the EUnit while in the FET\_normal state. It passes the requested instruction to the EUnit (Ins\_bus) if it detects a hit. It sends a MISS instruction if a miss occurs or a TRAP\_PC instruction if the Reset signal is true.

- 4. The IUnit initiates fetches from the external cache (Add\_bus) if Miss or Flush are true and Memory\_Busy is false.

- 5. The Fetch\_FSM keeps Starting\_Prefetch false until Miss, Flush or Global\_Suspension are true.

Equation 1: NOT(Global\_Suspension) AND (Miss OR Flush)

AND Memory\_Busy

Equation 2: NOT(Global\_Suspension) AND (Miss OR Flush)

AND NOT(Memory\_Busy)

Figure 3-1: Fetch State Diagram

FET\_memBusy: The Fetch\_FSM moves to this state if Miss or Flush are true and the external cache is busy (Memory\_Busy=true). The IUnit activities while in this state are:

- 1. The IUnit ignores the program counter from the EUnit (PC\_bus).

- 2. The IUnit does not read or write any instructions or address tags from its memory arrays.

- 3. The IUnit passes the MISS instruction to the EUnit (Ins\_bus).

- 4. Fetches may be initiated by the IUnit during this state if the Memory\_Busy signal is false. For example, assume a Miss occurred in the IUnit during the previous cycle and Memory\_Busy was true. Therefore, the Fetch\_FSM moved into the FET\_memBusy state. The IUnit initiates a fetch as soon as Memory\_Busy is false.

FET\_memPending: The Fetch\_FSM moves to this state if Miss or Flush are true, and the external cache is not busy (Memory\_Busy=false). In this state, the IUnit is waiting for a fetch request from the external cache to be satisfied. The IUnit activities in the FET\_memPending state are:

- 1. The IUnit ignores the program counter from the EUnit (PC\_bus).

- 2. The IUnit does not read any instructions or address tags from its memory arrays. However, the IUnit may write into its instruction array if Data\_Valid is true.

- 3. The IUnit passes the MISS instruction to the EUnit (Ins\_bus).

- 4. No fetches may be initiated by the IUnit during this state. The IUnit is presently waiting for its last fetch to be satisfied.

- 5. The Fetch\_FSM signals the Prefetch\_FSM that it can start making sequential prefetches.

FET\_Disabled: The Fetch\_FSM moves to this state if the IUnit\_Enable signal is false. The FET\_disabled state permits the CPU to function without the IUnit. The only activity that the IUnit performs during this state is to pass instructions to the EUnit (Ins\_bus). No prefetches are initiated while the IUnit is in this state. The IUnit may pass either the last requested instruction, a MISS or a TRAP\_PC.

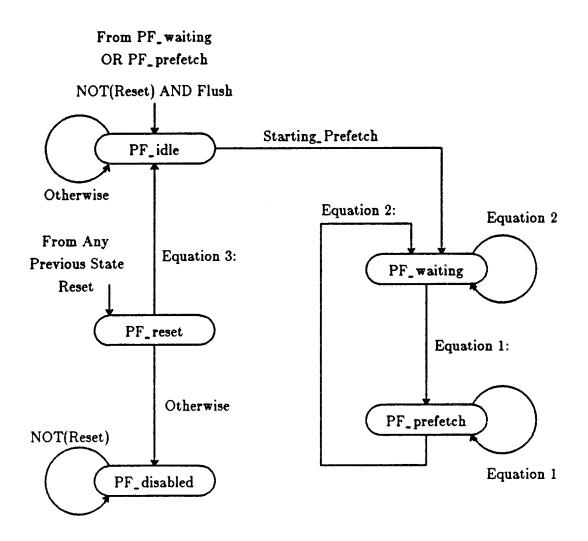

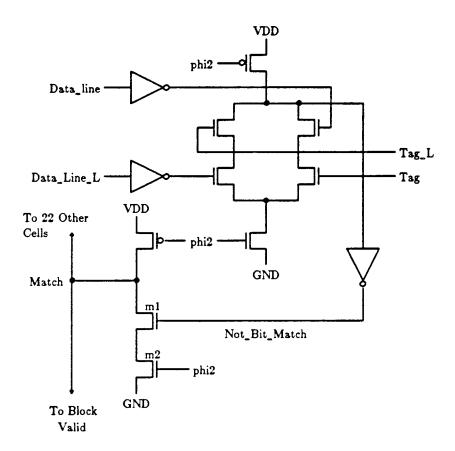

Prefetch Finite State Machine: The state of the Prefetch\_FSM determines whether any sequential prefetching will be done by the IUnit. The Prefetch\_FSM PLA has six inputs: Reset, IUnit\_Enable, Prefetch\_Enable, Memory\_Busy, Flush, and Starting\_Prefetch. The five states in the Prefetch\_FSM are shown in Figure 3-2.

PF\_reset & PF\_disabled: The Prefetch\_FSM is forced into the PF\_reset state from any other state when the Reset signal is true. The Prefetch\_FSM will move into the PF\_disables state

after a reset if IUnit\_Enable or Prefetch\_Enable is false. No Prefetching is initiated from either of these states.

PF\_idle: The idle state supports the prefetch-on-miss algorithm. The prefetcher will remain in this state until the Fetch\_FSM receives a Miss, Flush, or a Global\_suspension. While in the idle state, the Prefetch\_FSM repeatedly latches in the address of the last instruction that was fetched by the IUnit (Add\_bus). It increments this address so that it is prepared to prefetch the next sequential instruction if requested by the Fetch\_FSM (Starting\_Prefetch=true).

PF\_waiting & PF\_prefetch: The Prefetch\_FSM is attempting to prefetch sequential instructions while in either of these states. In both cases, the Prefetch\_FSM latches in the address of the last instruction that was either fetched or prefetched. It increments this address so that it may initiate a prefetch. The Prefetch\_FSM moves between these two states when either the Memory\_Busy signal and the Starting\_Prefetch signal change. A new prefetch is initiated on every cycle when both the Memory\_Busy and the Starting\_Prefetch signals are false. Prefetches are initiated by sending the next sequential instruction address to the external cache (Add\_bus) and asserting the Prefetch\_Request signal. The Prefetch\_FSM also writes incoming prefetched instructions into the instruction memory array when Data\_Valid is true. It will continue in this mode indefinitely until either Flush or Reset are true.

#### 3.2 Control Implementation Philosophy

Computer architects have often complained about the difficulties of control design in computers. A familiar adage states that the control design only occupies 10% of the computer hardware but requires 90% of the total design time. Fortunately, this has not been the case in the SPUR CPU design. Careful planning on the CPU functional level has helped segment the control blocks into manageable pieces [Kong86a], [Kong86b]. The IUnit control implementation occupies 8% of the total IUnit area and only required 50% of the total design time.

Equation 1: NOT(Starting\_Prefetch OR Memory\_Busy)

Equation 2: Starting\_Prefetch OR Memory\_Busy

Equation 3: NOT(Reset) AND IUnit\_Enable AND Prefetch\_Enable

Figure 3-2: Prefetch State Diagram

Design Constraints: The implementation philosophy that I pursued was shaped by several characteristics of the CPU design. The CPU floor plan was designed so that the upper and lower datapaths were approximately the same width. The height of the cells in each datapath were matched so that circuit designs could be shared. The height of the static memory cell used in both the register file and the IUnit also match the datapath cells. The area allocated for the IUnit was also an integral part of the CPU floor plan. The CPU upper and lower datapath layouts were

already complete, and fixed the IUnit width dimension. Therefore, I was forced to establish some tight pitches that influenced my approach. Secondly, there is a high probability that logic changes will be made in the IUnit control. Therefore, the layout was planned to support these changes. Finally, the IUnit control must issue low-level control signals during all four clock phases. This constraint limited the amount of logic that could be implemented in PLA's.

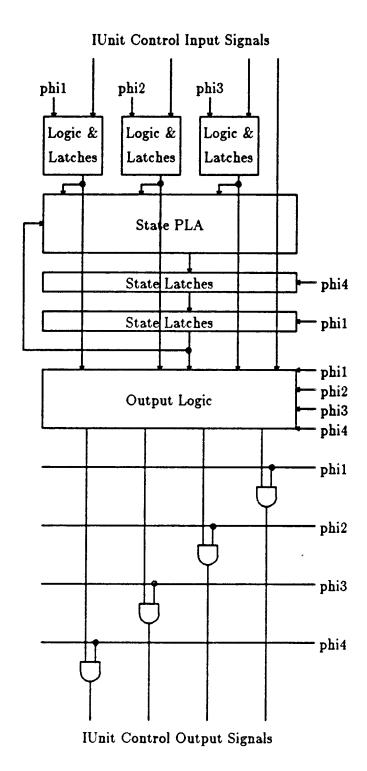

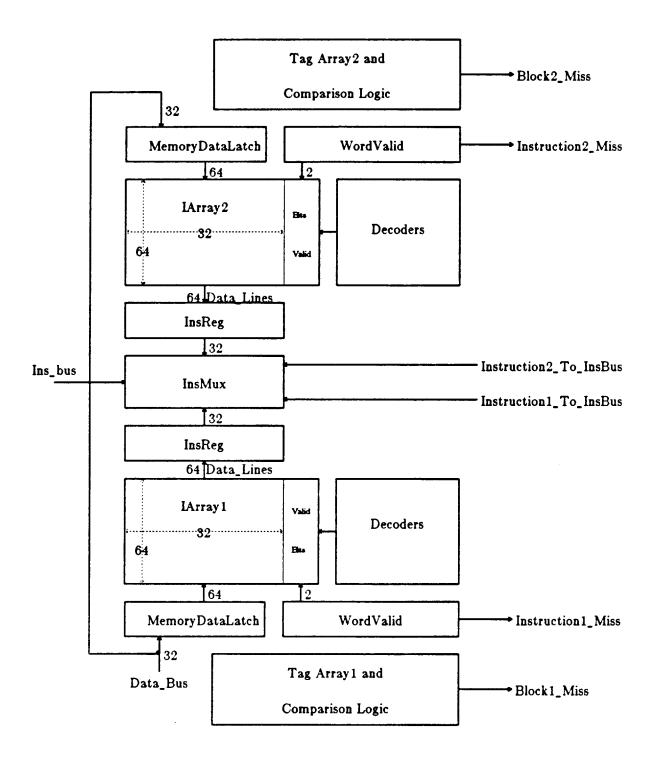

Generic IUnit Control Implementation: The two finite state machines PLA's within the IUnit are quite similar. This also holds true for the rest of their control functional blocks. Figure 3-3 shows a generic block diagram which illustrates either the Fetch\_FSM or the Prefetch\_FSM control functions [Kong86b]. The IUnit control inputs come from four sources: the EUnit, the instruction memory array, the tag comparison block, and the other finite state machine. Section 3.3 lists the input and output signals for both finite state machines. The Input Logic & Latches in Figure 3.3 are conventional static gates. The State PLA's were also simple to implement because generation tools and templates had already been developed [Scott86], [Jeon86]. Therefore, the output logic implementation is the focus of the remainder of this section.

Output Logic Constraints: The output logic block was the most challenging part of the IUnit control implementation. Several constraints complicated its design. First, a PLA could not be used to implement the output logic because the output signals are used during the same phase that they are evaluated. The targeted performance for this output logic was under 4 ns. Since the logic equations in this block are likely to change, I tried to implement a layout that was structured and general. I hoped to implement the output logic with standard logic cells that could be fit together in mosaics of all possible patterns. Ideally, changing one standard cell would not effect the layout of any other cell. I also hoped to bus all input signals into this standard cell mosaic so that any logic gate could be connected to any desired input. Unfortunately, the layout area required for this completely general approach was not practical. The output logic would be 2.5 times taller than my available height.

Output Logic Implementation: In my final implementation strategy I made tradeoffs between speed, area, and a completely general approach. The output logic equations vary widely

Figure 3-3: Generic IUnit Control Block Diagram

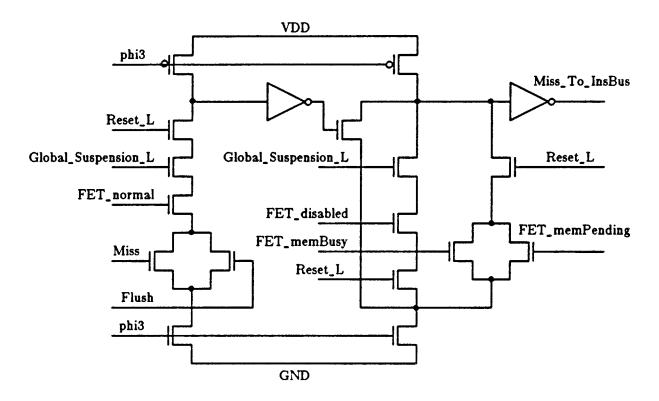

in complexity. The simplest equations are just a buffered version of the present state. The most complex output logic equation is shown below (MISS\_To\_InsBus). The 'FET\_...' inputs signals identify the present state of the Fetch\_FSM. Therefore, only one of the following signals are true:

FET\_normal, FET\_disabled, FET\_memBusy, or FET\_memPending. In the actual implementation, all signals proceeded by a NOT operator were inverted prior to the output logic gate.

MISS\_To\_InsBus= {FET\_normal AND NOT(Reset) AND NOT(Global\_Suspension)

AND (Miss OR Flush)}

OR {FET\_disabled AND NOT(Reset) AND Global\_Suspension}

OR {(FET\_memBusy OR FET\_memPending) AND NOT(Reset)}

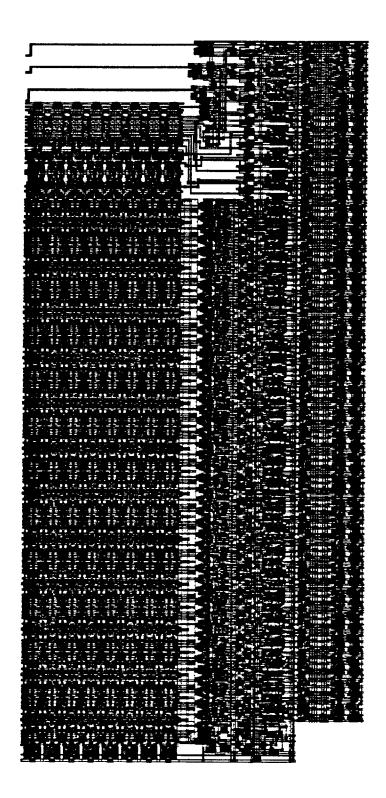

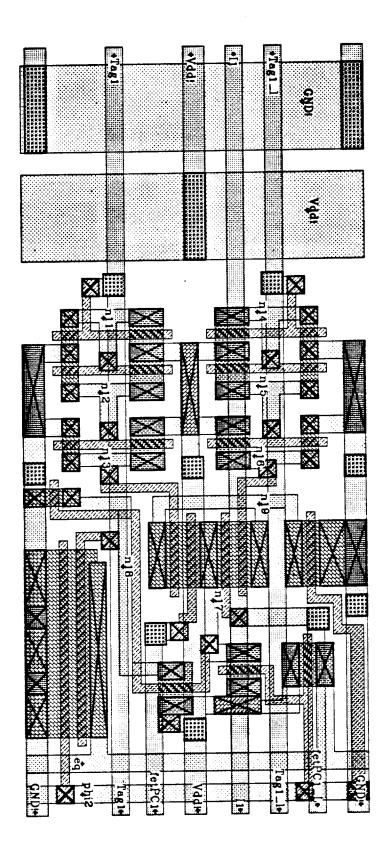

Domino Logic Standard Cells: This complex logic output equation emphasizes several important points. If a completely general implementation approach were adopted, the same amount of area should be reserved for all output logic equations. This approach consumed far too much area. A circuit implementation must be selected that minimizes both delay time and area. Domino logic gates were selected to best satisfy these criteria. Figure 3-4 shows a domino logic gate implementation for the MISS\_To\_InsBus output logic equation. Two AND\*OR domino logic gates were used in this implementation. All the output logic equations use at most two series domino logic gates to ensure adequate performance. No more than 5 NMOS devices are connected in series in any logic gates to avoid threshold voltage shifts due to an excessive backgate voltage. Layouts plots for two standard domino logic gates are shown in Figure A-4 in Appendix A: a 4 Input AND Gate and a 7 Input AND\*OR Gate.

Standard Cell Mosaic Implementation: I made several implementation tradeoffs in my domino standard cells to improve the layout density. I did not bus all input signals through the mosaic. Instead, I left several free routing channels to carry signals required at a later time. A typical output logic mosaic is shown in Figure 3-5. The input signals are bussed through the logic cells. This corresponds to the top and bottom of Figure 3-5. I shared area between outputs signals so that complex logic equations could use excess space from simple logic equations. This technique is illustrated in Figure 3-5. Each output is allocated enough room for two logic cells. For example, Output Signal 1 uses a 4 Input AND Gate and a 2 Input OR Gate. Output Signal 2 only requires one 3 Input AND Gate, therefore, one of its logic cells is free. The most complex

Figure 3-4: Domino Output Logic Gate

logic gate that can fit into a single cell height is a 4 Input AND. More complex AND\*OR gates can be implemented by using two single cell heights. Sharing area between output signals that have complex and simple logic equations is also demonstrated in Figure 3-5. For example, Output Signal 3 only uses one 3 Input AND Gate so it can contribute the space occupied by one logic cell to another output. In this case, Output Signal 4 has a more complex logic equation that requires one 6 Input AND\*OR Gate and one 4 Input AND Gate. Therefore, it uses the free space available from Output Signal 3. In the extreme case, an output logic equation requires two AND\*OR gates. Fortunately, there are some outputs that do not require any logic cells. Sharing area between output signals was effectively used to reduce the area of the output logic mosaic.

Limitations of the Output Logic Mosaic: There are several disadvantages with the output logic mosaic approach that I implemented. First, changing the logic equation for one output may effect other outputs. Hopefully, most logic changes will only require modifying the input

| Logic Cells      | Logic Cells      | Output Buffer   |

|------------------|------------------|-----------------|

| 4 Input AND Gate | 2 Input OR Gate  | Output Signal 1 |

| free cell        | 3 Input AND Gate | Output Signal 2 |

| 6 Input AND*OR   | 3 Input AND Gate | Output Signal 3 |

| Gate             | 4 Input AND Gate | Output Signal 4 |

| 7 Input AND*OR   | 5 Input AND*OR   | Output Signal 5 |

| Gate             | Gate             | Output Signal 6 |

Figure 3-5: Typical Output Logic Mosaic

connections. In addition, there would be little difficulty substituting a simpler output logic gate for a more complex gate. However, problems could arise if more complex logic gates are needed. In the worst case, a new custom logic gate could be packed into the available space. The general purpose logic cells that I designed keep most of the metal 1 routing channels open. This makes them easier to connect to any of the available inputs. If necessary, this routing area could be packed with additional transistors. The second limitation of this approach is that the logic gate inputs must be connected to the input signals by hand. This is an error prone and time consuming process. I'm confident that software tools could be developed to automate the output logic generation. Finally, it may be possible to redefine the control architecture to capture more of the problem into the state PLA's. The PLA's are quite area efficient in comparison to the output logic and are already supported by automatic generation tools. One possible approach is to use PLA's to perform all the output logic functions that can be evaluated one phase earlier than necessary. Domino output logic could then be reserved for only those parts of the output logic that must be evaluated during the final phase.

#### 3.3 Fetch and Prefetch Control Implementations

This section summarizes the implementation details of the Fetch\_FSM and the Prefetch\_FSM. The layout of the IUnit control occupies 8% of the total area in the IUnit and contains approximately 2300 transistors. The generic control block diagram, presented in the previous section, proved to be impractical in several cases. For example, the regularity of my output logic implementation had to be abandoned to achieve adequate performance margins for some output signals. This section is divided into three parts. First, a complete list of input and output signals for the Fetch\_FSM and Prefetch\_FSM is reviewed. The output logic mosaics implemented for both of these finite state machines is then presented. Finally, SPICE simulation results for the worst case speed path in the control block are discussed.

Fetch and Prefetch Input and Output Signals: A complete list of the input signals used by the Fetch\_FSM and Prefetch\_FSM are shown in Table 3-2. Input signals used by the IUnit control arrive during all four phases. However, input signals that arrive during phi4 are latched on the following phi1 to avoid race conditions between these signals and the PLA's. All of the input signals in Table 3-2 have been introduced in previous sections except the Write\_Fetch signal.

The Write\_Fetch signal connects the Fetch output logic to the Prefetch output logic.

Write\_Fetch is important because potentially it is the slowest signal path in the IUnit control design. The speed path is illustrated by the two following logic equations:

|                                         | Signal Timing Information |                                                  |                                                  |                |  |

|-----------------------------------------|---------------------------|--------------------------------------------------|--------------------------------------------------|----------------|--|

| Signal or Bus Name                      | phi1                      | phi2                                             | phi3                                             | phi4           |  |

| Filett and ECasha In-                   | 4- TII-14 C               |                                                  | 1- 0 1)                                          |                |  |

| EUnit and ECache Inp<br>Enable_KPSW_Set | des to l'Onit C           | Outrol (see 180                                  | ole z-1)                                         | *C1.           |  |

| Prefetch_KPSW_Set                       |                           | <del>-</del>                                     |                                                  | *Changes       |  |

| Pipeline_Not_Suspended                  |                           |                                                  |                                                  | *Changes       |  |

| Load_OPCode                             | Changes                   |                                                  |                                                  | *Changes       |  |

| Store_OPCode                            | Changes                   | <del>                                     </del> | <del>                                     </del> |                |  |

| lowTOup_OPCode                          | Changes                   |                                                  |                                                  |                |  |

| Invalidate_OPCode                       | Changes                   |                                                  |                                                  |                |  |

| Invalidate_Trap                         |                           | <del>                                     </del> | ļ                                                |                |  |

| Reset_IUnit                             | Changes                   | GI.                                              |                                                  | ļ              |  |

| Cache_Busy                              |                           | Changes                                          |                                                  |                |  |

|                                         |                           | Changes                                          | 1                                                |                |  |

| Cache_Data_Valid                        | ļ                         |                                                  | Valid                                            |                |  |

| PC_bus <30 bits>                        | EUnit                     |                                                  | Pre-Charge                                       |                |  |

| Address_bus <30 bits>                   | Pre-Charge                | EUnit                                            | Pre-Charge                                       | EUnit or IUnit |  |

| Data_bus <40 bits>                      | EUnit                     | Pre-Charge                                       | ECache                                           | Pre-Charge     |  |

| IUnit Derivatives of EU                 | Init and Ecach            | e Inpute (see 7                                  | *able 2-1\                                       |                |  |

| IUnit_Enable                            | Changes                   | e inputs (see 1                                  | able 3-1)                                        |                |  |

| Presetch_Enable                         | Changes                   |                                                  |                                                  |                |  |

| Global_Suspension                       | Changes                   |                                                  |                                                  |                |  |

| Reset                                   | 3                         | Changes                                          |                                                  |                |  |

| Flush                                   |                           | Changes                                          |                                                  |                |  |

| Memory_Busy                             |                           | Changes                                          |                                                  |                |  |

| Data_Valid                              |                           |                                                  | Changes                                          |                |  |

|                                         |                           |                                                  | 1 onenges                                        | 1              |  |

| IUnit DataPath Inputs                   | to IUnit Contr            | ol                                               |                                                  |                |  |

| Block_Miss                              |                           | Valid                                            |                                                  |                |  |

| Instruction_Miss                        |                           | Valid                                            |                                                  |                |  |

| Fetch_FSM Outputs to                    | Prefetch FSM              | Inputs                                           |                                                  | ·              |  |

|                                         |                           | <u>.</u>                                         | Valid                                            |                |  |

| Starting_Prefetch                       | I.                        | 1                                                | i valid                                          |                |  |

<sup>\*</sup>Signals arrive on phi4 but are not used until the following phi1.

Change- indicates that the signal is always asserted. It only changes during the designated phase.

Table 3-2: Fetch and Prefetch Input Signals

Valid - indicates that the signal may only be asserted true during the designated phase. Signal is false during all other phases.

The Write\_Fetch signal would normally be evaluated during phi4 because the Data\_Valid signal does not change until phi3. When using domino logic gates, it is essential that none of the inputs make a high to low transition during the evaluation period. My standard domino gates avoid this problem by always evaluating the logic function on the phase after the last signal changes. The slow signal path arises because the Write\_Instruction signal must wait for the Write\_Fetch signal. Therefore, this speed path essentially suffers from two delays through the output logic: one for the Fetch\_FSM and the second for the Prefetch\_FSM.

This signal delay path was removed by using a static logic gate for the Write\_Fetch signal. This technique works because the Data\_Valid signal is valid midway through phi3. The Write\_Fetch signal has enough time (15 ns) to propagate through the 3 input static gate and settle at the input of the Write\_Instruction output logic gate before the beginning of phi4.

The Fetch\_FSM and Prefetch\_FSM output signals, listed in Table 3-3, provide direct control of the instruction memory array, tag comparison logic, and prefetcher. These output signals are described in subsequent sections of this chapter.

|                                          | Signal Timing Information |       |              |                |

|------------------------------------------|---------------------------|-------|--------------|----------------|

| Signal or Bus Name                       | phi1                      | phi2  | phi3         | phi4           |

| Instruction Memory Array                 | Control Signa             | ls    |              |                |

| Invalidate_Block                         |                           | Valid |              | 1              |

| Enable_Block                             |                           | Valid |              |                |

| Read_Instruction                         |                           | Valid |              |                |

| Instruction_To_InsBus                    |                           |       | Valid        |                |

| MISS_To_InsBus                           |                           |       | Valid        |                |

| TRAPCALL_To_InsBus                       |                           |       | Valid        |                |

| READPC_To_InsBus                         |                           |       | Valid        |                |

| Ins_bus <32 bits>                        |                           |       | <b>IUnit</b> |                |

| Read_MemLatch                            |                           |       |              | Valid          |

| Write_Instruction                        |                           |       |              | Valid          |

| Tag Comparison Logic Con<br>Load_FetchPC | Valid                     | Valid |              |                |

| Invalidate_Tag                           |                           | Valid |              |                |

| Bypass_Tag_Decoder                       |                           | Valid |              |                |

| Write_Tag                                |                           |       |              | Valid          |

| Add_bus <30 bits>                        | Pre-Charge                | EUnit | Pre-Charge   | EUnit or IUnit |

| Prefetcher Control Signals               |                           |       |              |                |

| FetchPC_To_AddBus                        |                           | T     | 1            | Valid          |

| IncrementedPC_To_AddBus                  |                           |       |              | Valid          |

| Load_ReferencePC                         |                           |       |              | Valid          |

| Fetch_FSM Outputs to Pre                 | efetch_FSM Inp            | uts   |              |                |

| Starting_Prefetch                        | T                         |       | Valid        |                |

| Write_Fetch                              |                           |       |              | Valid          |

| Outputs to the Execution I               | Jnit .                    |       |              |                |

| Fetch_Request                            | T                         |       | Valid        |                |

| Prefetch_Request                         |                           |       | Valid        |                |

Valid - indicates that the signal may only be asserted true during the designated phase. Signal is false during all other phases.

Table 3-3: Fetch and Prefetch Output Signals

Fetch and Prefetch Output Logic Mosaics: The output logic implementation followed the structured standard cell approach whenever possible. Actually, only the Write\_Fetch signal needed to use a static output gate. However, several other output signals had potential race

problems. For example, the Fetch\_Request and Prefetch\_Request output signals are evaluated during phi3. Both these signals are derived from the Memory\_Busy signal. This signal does not become valid until late in the phi2 cycle. Extra attention had to be given to this delay path to ensure that Memory\_Busy was valid before the beginning of phi3.

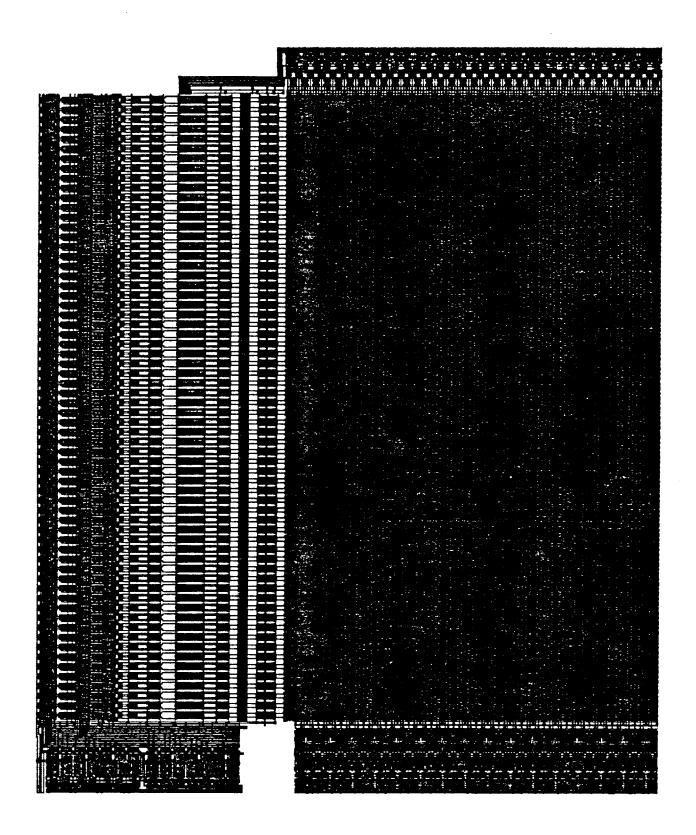

The output logic mosaics for the Fetch and Prefetch finite state machines are shown in Figure 3-5 and Figure 3-6 respectively. The Fetch output logic supports 14 output signals in the same number of standard cell rows. The Prefetch output logic contains six output signals in eight logic cell rows. The area consumed by the Fetch output logic mosaic set the critical dimension of the IUnit control block. Figures A-5 and A-6 in Appendix A show the layout plots of the Fetch and the Prefetch output logic mosaics respectively. Layout plots for the entire Fetch\_FSM and Prefetch\_FSM blocks are shown in Figures A-7 and A-8. The output logic consumes about 50% of the total control area in both of these plots.

| Logic Cells         | Logic Cells             | Output Buffer         |

|---------------------|-------------------------|-----------------------|

| 4 Input AND Gate    | 6 Input AND*OR  Gate    | Fetch_Request         |

| fet_free Cell       | (d4AND2OR)              | Load_FetchPC          |

| 5 Input AND*OR Gate | 3 AND*OR Gate           | Starting_Prefetch     |

| (d4AND1OR)          | fet_free Cell           | READPC_To_InsBus      |

| 4 Input AND Gate    | 6 Input AND*OR          | FetchPC_To_AddBus     |

| 2 Input OR Gate     | Gate<br>(d4AND2OR)      | TRAPCALL_To_InsBus    |

| fet_free Cell       | 5 Input AND*OR  Gate    | Write_Tag             |

| 4 Input AND Gate    | (d4AND1OR)              | Read_MemLatch         |

| 5 Input AND*OR      | 7 Input AND*OR          | MISS_To_InsBus        |

| Gate<br>(d4AND1OR)  | Gate<br>(d3AND4OR)      | Invalidate_Block      |

| fet_free Cell       | 6 Input AND*OR          | Instruction_To_InsBus |

| 3 Input AND Gate    | Gate<br>(d5AND1OR)      | Read_Instruction      |

| fet_free Cell       | fet_free Cell           | Enable_Block          |