Copyright © 1987, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# LOW-COST HIGH-SPEED GENERAL SERVICE FIBER OPTIC NETWORKS

by

Ming-Kang Liu

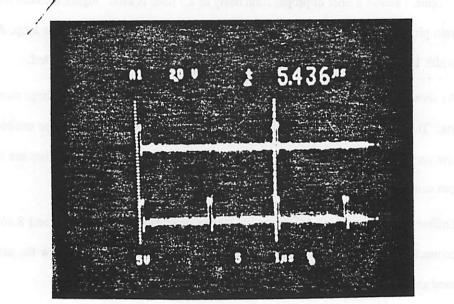

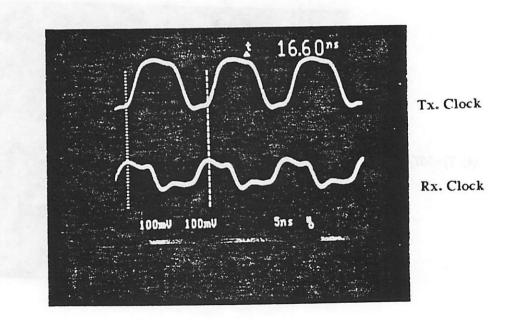

Memorandum No. UCB/ERL M87/26

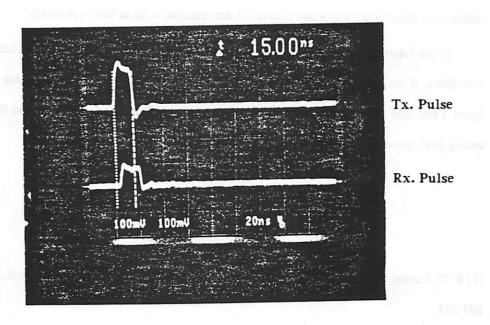

20 April 1987

# LOW-COST HIGH-SPEED GENERAL SERVICE FIBER OPTIC NETWORKS

by

Ming-Kang Liu

Memorandum No. UCB/ERL M87/26

20 April 1987

# K **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# LOW-COST HIGH-SPEED GENERAL SERVICE FIBER OPTIC NETWORKS

by

Ming-Kang Liu

Memorandum No. UCB/ERL M87/26

20 April 1987

# ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

# Low-Cost High-Speed General Service Fiber Optic Networks

#### Ming-Kang Liu

#### **ABSTRACT:**

Fiber optics is an emerging low cost technology for high speed communications, and the information age has been characterized as a time of exploding communication demands of all kinds. In this thesis, system solutions to low cost but high performance implementation of fiber optic communication networks for general services are proposed.

A fiber optic network distinguishes itself from other networks by its large transmission bandwidth. As a result, it is electronics that limits the available bandwidth for the information exchange. Also, a general service network has the capability to support all video, voice, and data traffic. With quite different traffic characteristics, a general service network should be designed so that all messages are handled efficiently and satisfactorily. In the thesis, system solutions which (1) minimize the speed mismatch between optics and electronics and (2) optimize the service for different traffic are considered.

These solutions include: (1) a circuit switching approach called Time Slot Switching (TSS), (2) an integration of TSS and Carrier Sense Multiple Access (CSMA), (3) an integration of TSS and slotted-ring, (4) and a simple high speed timing recovery method suited for fiber optics. Circuit switching provides multiple simultaneous links; therefore, the throughput can be much larger than with packet broadcasting such as CSMA or token-passing. Its fixed transmission delay is also desirable for voice or video. Compared with packet switching, circuit switching avoids much of the high speed packet processing; consequently, the speed constraint from electronics is mitigated.

The integration of TSS with CSMA or slotted-ring provides better services for data traffic and for networks covering larger geographical areas. We show that this integration is attractive for better performance and simple implementation.

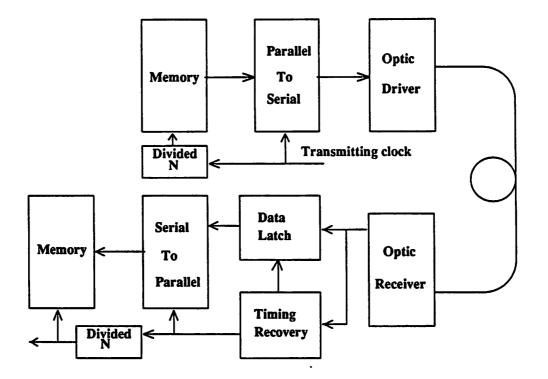

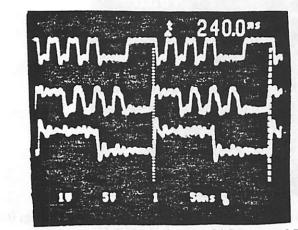

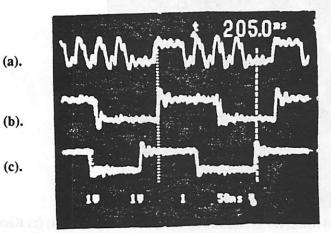

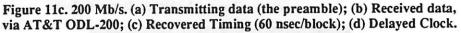

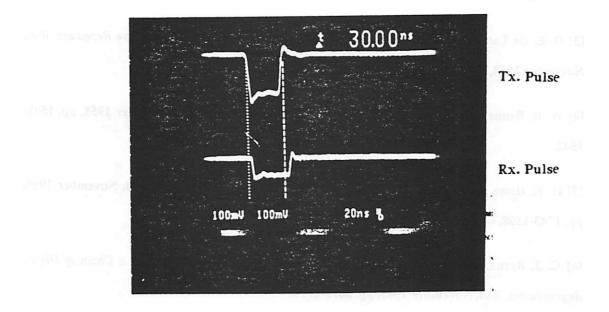

The new timing recovery approach for high speed fiber optic communications avoids the use of PLL or SAW filters. The basic idea is to use a code with special properties which dramatically simplify the timing recovery process. This has been experimentally verified at 200 Mb/s using ECL logic. This suggests that Gb/s speeds can be achieved in bipolar integrated circuits or a few hundred Mb/s in CMOS.

These results contribute to achieving high speed fiber optic networks with low cost and high performance.

aird GMessischants

David G. Messerschmitt Committee Chairman

"The fear of the Lord is the beginning of knowledge, but fools despise wisdom and discipline."

•

.

.

Proverbs 1:7

.

.

To My Parents, Yee-Tang and Pei-Yu Liu,

for Their Endless Love

¥.,

## ACKNOWLEDGEMENTS

I am deeply indebted to my research advisor, Professor David G. Messerschmitt, for his intelligent guidance and persistent support throughout my study. I wish to express my gratitude to Professor David A. Hodges, who initiated the project and provided me with valuable technical knowledge and experimental environment. I would also like to extend my appreciation to my committee members: Professors Finbarr O'Sullivan, Jean Walrand, and Michael Lieberman.

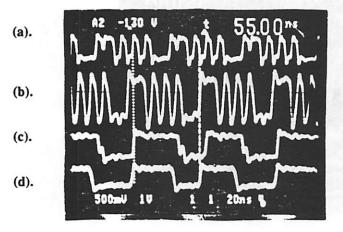

Many other people made themselves available during my researches: Mr. Hyun J. Shin gave me very strong support with the high speed circuit switch he designed and implemented; Miss Janet M. Cooper in Bell Communications Research contributed important experimental work; Professor Robert G. Meyer and Mr. Mehmet Soyuer provided very valuable technical discussions; and Dr. Harry Mussman in AT&T Bell Laboratories offered indispensable optical fibers, transceivers, and wiring tools. The work cannot be completed without their help.

I would also like to thank my friendly colleagues: Graham Brand, Teresa Meng, Tom Chen, Biswa Ghosh, Vijay Madisetti, Keshab Parhi, Ilovich Mordechay, and etc., who constantly support me and give many suggestions. In particular, I should thank Tom Chen for carefully reading and commenting my draft.

This work was supported by grants from Advanced Micro Devices, Fairchild Semiconductor, Harris Semiconductor, National Semiconductor, Intel Corporation, and Bell Communications Research, with a matching grant from the University of California MICRO program.

I should finally express my deep appreciation to my wife, Ai-Ching, who carefully arranges my life and accompanies me over countless nights.

# **Table of Contents**

| Chapter 1: Introduction                       | 1  |

|-----------------------------------------------|----|

| Chapter 1: Introduction<br>1.1 Introduction   | 1  |

| 1.2 The Objective                             | 1  |

| 1.3 Network Classifications                   | 2  |

| 1.3.1 Transmission Medium                     | 3  |

| 1.3.2 Network Size                            | 4  |

| 1 3 3 Network Bandwidth                       | 5  |

| 1.3.4 Network Topology                        | 5  |

| 1.3.5 Traffic Types                           | 6  |

| 1.3.6 Medium Access Protocols                 | 6  |

| 1.4 Traffic Characteristics                   | 7  |

| 1.4.1 Voice                                   | 7  |

| 1.4.2 Data                                    | 8  |

| 1.4.3 Video                                   | 8  |

| 1.5 Local Area and Metropolitan Area Networks | 8  |

| 1.6 Fiber Optics and Integrated Electronics   | 9  |

| 1.7 The Approaches                            | 10 |

| REFERENCE                                     | 12 |

# Part I: Asynchronous Time Division Networks

| Chapter 2: Time Slot Switching (TSS)                   | 16 |

|--------------------------------------------------------|----|

| 2.1 Introduction                                       | 16 |

| 2.2 Homogeneous TSS Networks                           | 16 |

| 2.2.1 Network Topology and Architecture                | 17 |

| 2.2.2 Basic Operations                                 | 19 |

| 2.2.3 Some Remarks on TSS                              | 22 |

| 2.3 Switching Management                               | 24 |

| 2.3.1 Frame and Slot Timing                            | 24 |

| 2.3.2 Circuit Connection Setup                         | 25 |

| 2.3.3 The Control Traffic                              | 26 |

| 2.4 Performance Analysis of Homogeneous TSS            | 27 |

| 2.4.1 Guard Time Analysis                              | 28 |

| 2.4.2 Network Circuits and Blocking Probability        | 31 |

| 2.4.3 Compression Delay                                | 35 |

| 2.4.4 Network Utilization vs. Compression Delay        | 37 |

| 2.5 Heterogeneous TSS                                  | 40 |

| 2.6 Conclusion                                         | 43 |

| Appendix A. Blocking Probability Analysis: Single Star | 45 |

| Appendix B. Blocking Probability Analysis: Double Star | 45 |

| REFERENCE                                              | 46 |

| Chapter 3: Integration of TSS and CSMA/CD              | 47 |

.

| 3.1 Introduction                                                                                  | 47   |

|---------------------------------------------------------------------------------------------------|------|

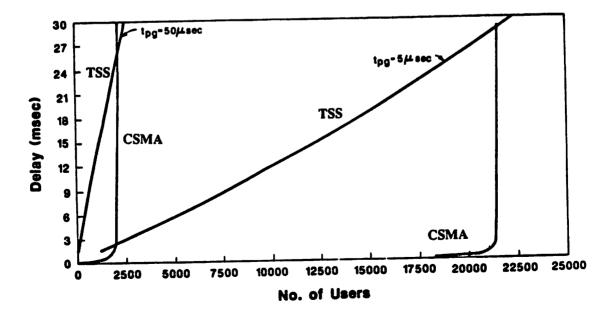

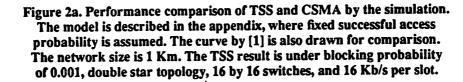

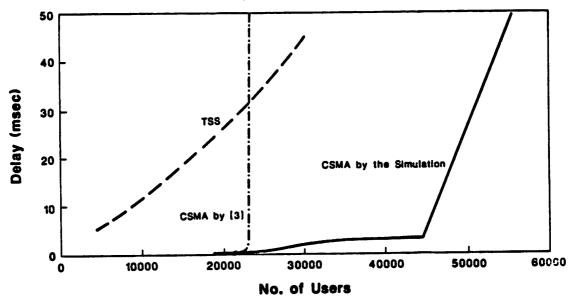

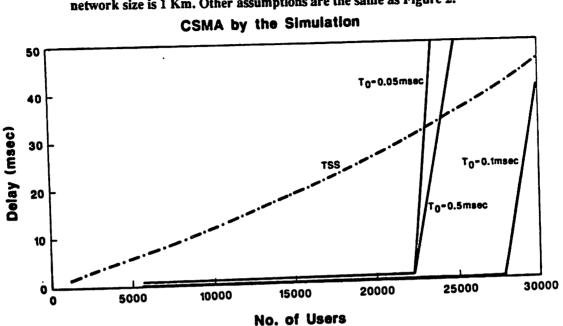

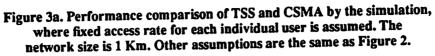

| 3.2 A Performance Comparison between TSS and CSMA                                                 | 47   |

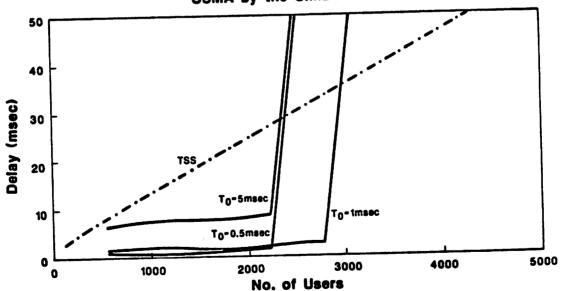

| 3.3 Medium Access Protocol for Integration of TSS and CSMA                                        | 51   |

| 3.3 Medium Access Protocol for Thegration of 105 and 05.22 million and 3.4 Further Considerations | 53   |

| 3.4 Further Considerations                                                                        |      |

| 3.4.1 Hardware Architecture                                                                       |      |

| ' 3.4.2 Traffic Priority                                                                          |      |

| 3.4.3 Traffic Performance                                                                         | . 59 |

| 3.5 Conclusion                                                                                    | , 01 |

| Appendix. Simulation Model for Interactive Data Traffic by CSMA/CD                                | . 63 |

| REFERENCE                                                                                         | . 67 |

| Chapter 4: Skew TSS and Slotted-Ring in a Metropolitan Area Network                               | . 70 |

| 4.1 Introduction                                                                                  | . 70 |

| 4.2 Skew Time Slot Switching                                                                      |      |

| 4.2 Skew Time Slot Switching                                                                      | . 72 |

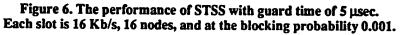

| 4.2.1 Basic Concepts                                                                              | . 74 |

| 4.2.2 Practical Implementation                                                                    | . 78 |

| 4.2.2 Fractical Implementation                                                                    | . 80 |

| 4.4 The Integration of Skew TSS and Slotted-Ring                                                  | . 00 |

| 4.5 Conclusion                                                                                    | . 84 |

| Appendix. Analysis for the Slotted-Ring                                                           | . 86 |

| Appendix. Analysis for the Slotted-Ring                                                           | 90   |

# Part II: High Speed Network Implementation

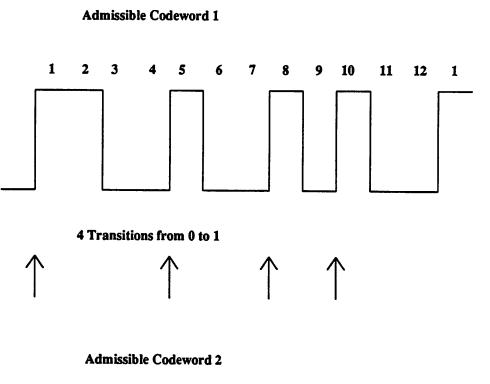

| Chapter 5: A Fixed Transition Coding for High Speed Timing Recovery | 92  |

|---------------------------------------------------------------------|-----|

| 5.1 Introduction                                                    | 92  |

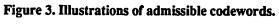

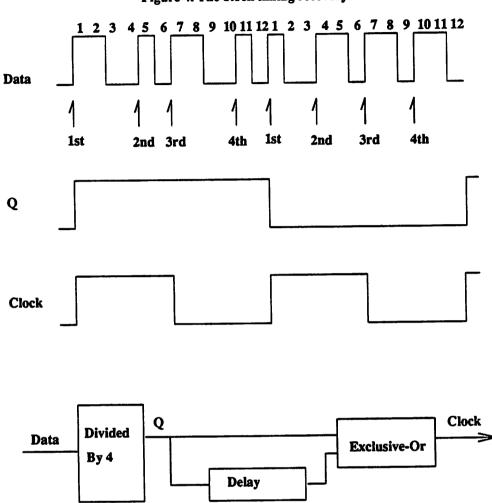

| 5.2 The Block Timing Recovery                                       | 96  |

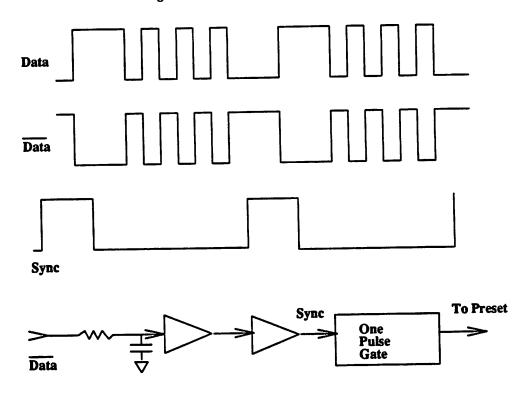

| 5.2.1 A Fixed Transition Block Code                                 | 96  |

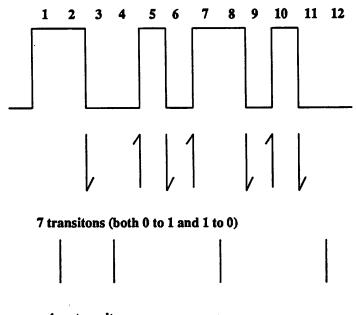

| 5.2.2 Timing Recovery                                               | 96  |

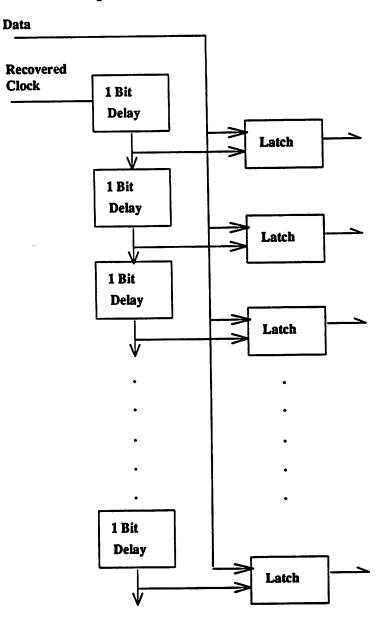

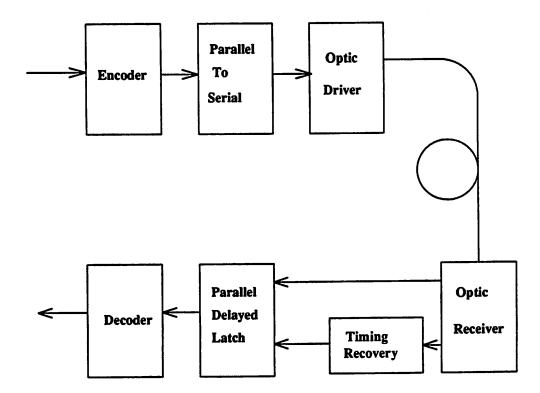

| 5.2.3 Parallel Delay Latching                                       | 99  |

| 5.3 The Technical Issues                                            | 101 |

| 5.3.1 The Block Synchronization and Transition Errors               | 101 |

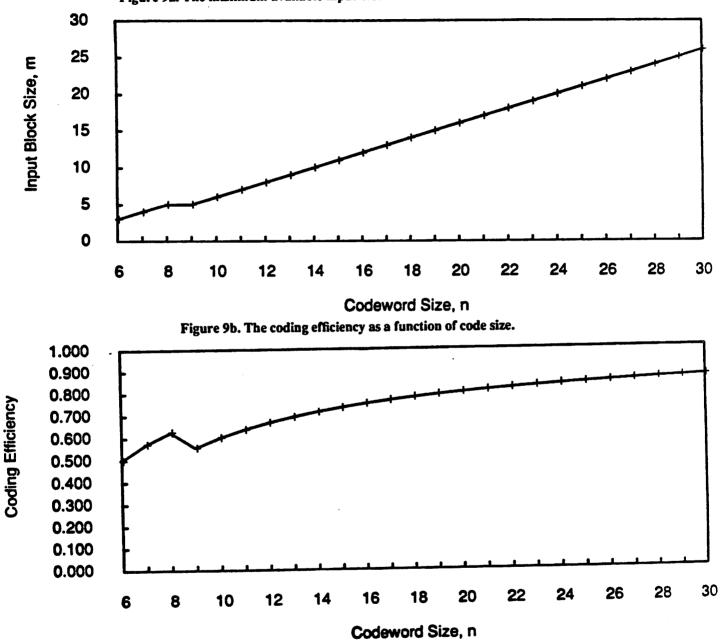

| 5.3.2 Coding Efficiency and Complexity                              | 102 |

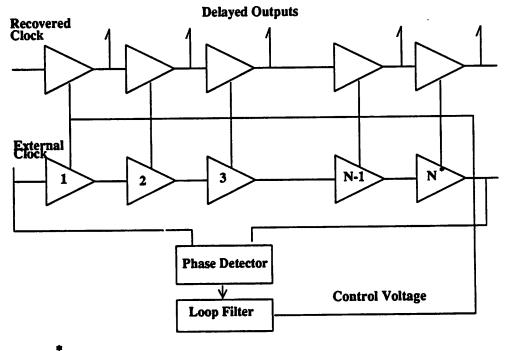

| 5.3.3 The Precise Delay Line                                        | 103 |

| 5.4 An Experimental Example                                         | 106 |

| 5.5 Conclusion                                                      | 106 |

| Appendix, Algorithms for Encoding and Decoding                      | 109 |

| REFERENCE                                                           | 113 |

| Chapter 6: The Cascading Effect of Circuit Switches                 | 115 |

| 6.1 Introduction                                                    | 115 |

| 6.2 Timing Jitter Model                                             | 115 |

| 6.3 Experimental Setup                                              | 116 |

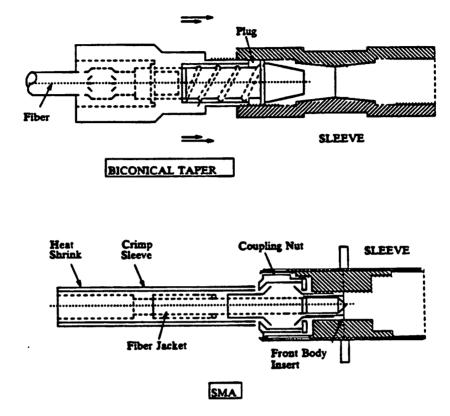

| 6.3.1 Optical Link Components                                       | 117 |

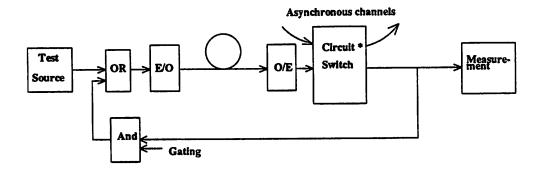

| 6.3.2 Feedback Loop Setup                                           | 119 |

| 6.4 Test Results                                                    | 121 |

| 6.4.1 ODL-50                                                        | 123 |

٠

| 6.4.2 ODL-200                                           | 123 |

|---------------------------------------------------------|-----|

| 6.5 Future Extensions                                   | 128 |

| REFERENCE                                               | 128 |

| Chapter 7: Future Work                                  | 130 |

| 7.1 Introduction                                        | 130 |

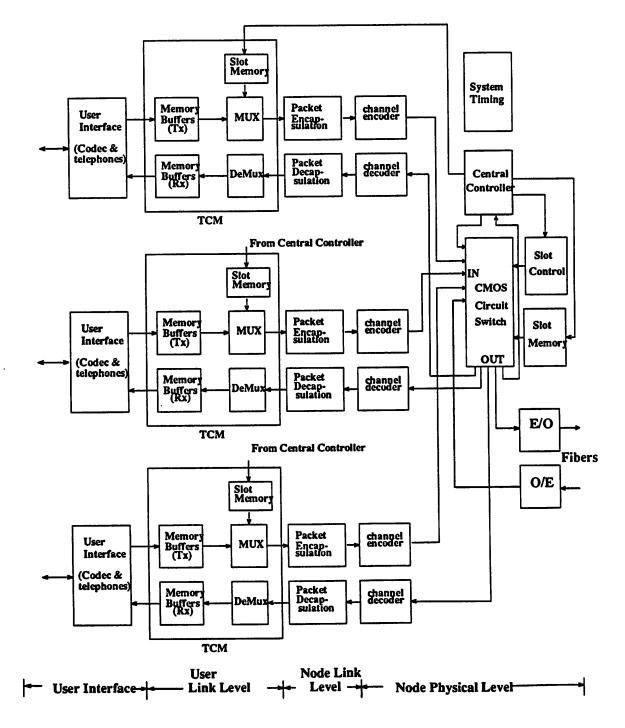

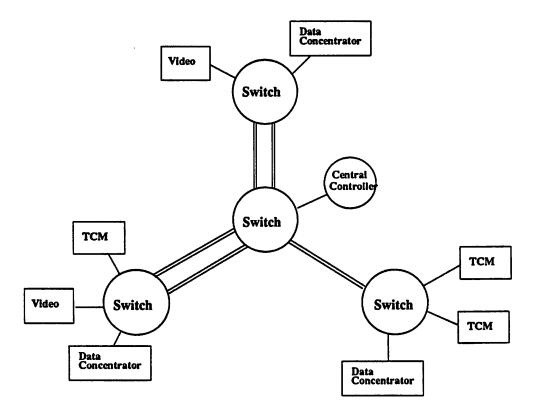

| 7.2 A Prototype TSS Network                             | 132 |

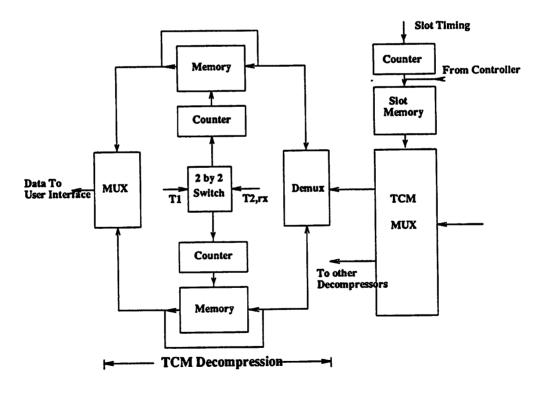

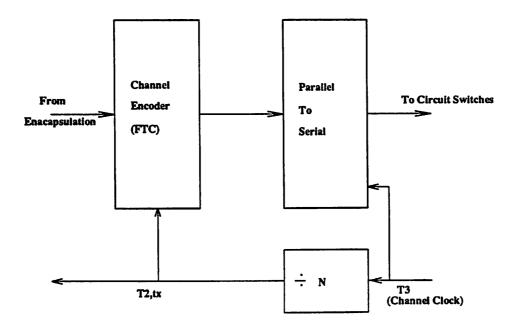

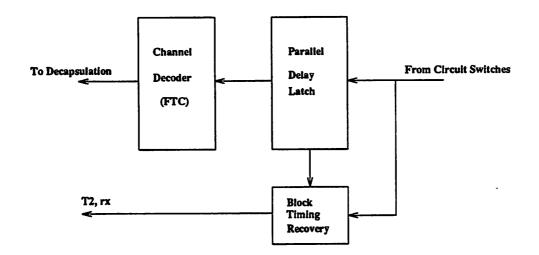

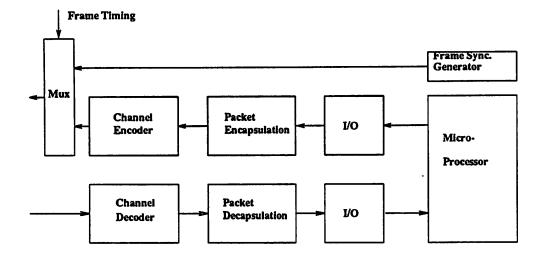

| 7.2.1 The TCM                                           | 132 |

| 7.2.2 The User Interface                                | 132 |

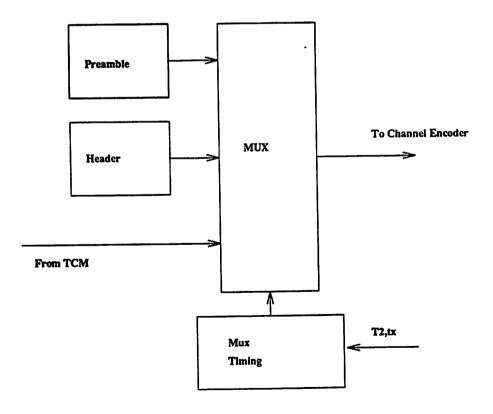

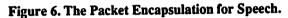

| 7.2.3 The Packet Encapsulation and Decapsulation        | 136 |

| 7.2.4 The Channel Encoder and Decoder                   | 138 |

| 7.2.5 The System Timing                                 | 138 |

| 7.2.6 The Central Controller and Control Traffic        | 139 |

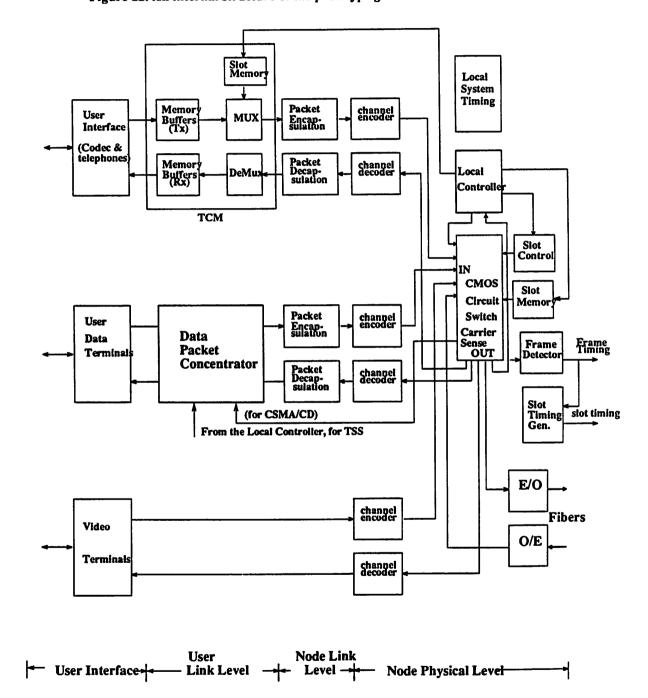

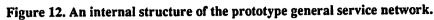

| 7.3 Modified Prototype Networks                         | 140 |

| 7.3.1 A LAN for General Service: Voice, Data, and Video | 141 |

| 7.3.2 A MAN with Skew TSS and Slot-Ring Service         | 141 |

| 7.4 Conclusion                                          | 144 |

· · ·

•

-

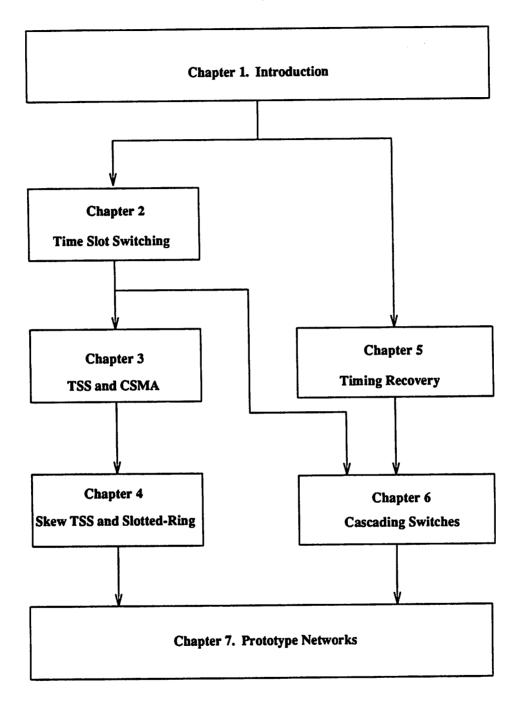

The Relationship of the Chapters

### **CHAPTER 1**

#### Introduction

#### **1.1. Introduction**

A communication network consists of nodes interconnected through some transmission medium by which a large number of users communicate with each other. A network can use radio, coaxial cable, pair wire, or fiber optics as its transmission medium, and it can span over a campus, a city, or even a whole nation. It can serve different functions: voice, data, video information, or some combination. In this thesis, a fiber optics network to serve various types of traffic will be studied. The network's range can span a local area to a larger metropolitan area.

This chapter explains the objective of this thesis, fundamental backgrounds, and a brief introduction to the approach. Detailed discussion will follow in the remaining chapters.

#### 1.2. The Objective

Fiber optics provides low cost and high immunity to noise, and has become a good choice for the transmission medium in local area and metropolitan area networks [1-7]. Also, technologies of integrated electronics, especially high performance CMOS circuits, have improved significantly in both switching speeds and function complexity during last decades [8-10]. With these advanced optics and electronics, communication bandwidth has been greatly increased.

The "Information Age" has been characterized as a time of exploding communications demands of all kinds. These new demands, for example to provide a general service for all voice, data and video, create great challenges for system engineers. Our current communications technologies have been designed around specific applications and these different applications impose different constraints on the network (e.g., allowable transmission delay). The telephone network, cable networks, and data packet switching networks (e.g. the ARPA Net) are examples.

#### Chapter 1: Introduction

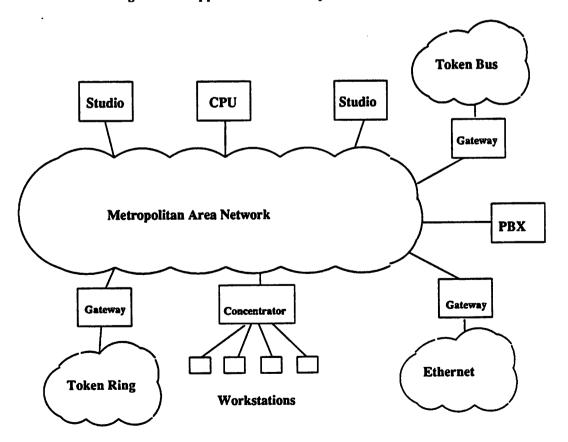

Interestingly, minicomputers, workstations and personal computers have gradually replaced the roles of main frames for data processing and computation. In response to this change, small area networks such as local area networks (LAN) have emerged to provide the intercommunications between these small computers [11]. Ethernet, Token-ring, and Slot-ring are successful examples of such networks [12-15]. In more recent years, information exchanges between LANs, PBXs, and main frames have also been needed. This resulted in the Metropolitan Area Network (MAN) concept [16-19].

In summary, a general purpose local and metro area network is getting more and more important, and as a result, the objective is to take advantage of well developed and low cost electronics and optics technologies to serve voice, data, and video traffic in local or metropolitan areas. There are three major problems to be solved:

(1) Traffic congestion in a network.

- (2) Integrating the different service requirements of voice, data, and video traffic.

- (3) The speed mismatch between electronics and optics.

These will be elaborated in the following sections.

Foundations to the approaches to solving these problems -- classifications of networks, characteristics of traffic, special features of LANs and MANs, and properties of fiber optics and integrated electronics -- are discussed first. Brief descriptions of the approaches will also be given before detailed discussion in the remaining chapters.

#### **1.3. Network Classifications**

A network can be classified by its: (1) transmission medium, (2) size, (3) traffic types, (4) bandwidth, (5) topology, and (6) medium access protocol.

#### 1.3.1. Transmission Medium

Electrical signals can pass through various kinds of media, with variations in attenuation, noise interference, and channel bandwidth. Examples are twisted pair in telephone subscriber loops, coaxial

cables in cable TVs, free space for radios, and fiber optics for high bandwidth applications.

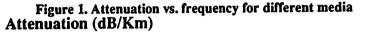

A good communication channel is characterized by low signal attenuation, low noise interference level, and large signal bandwidth. If analog transmission is used, linearity will also be important. A comparison of the attenuation as a function of carrier frequency among twisted pairs, coaxial cables, waveguides, and optical fibers is shown in Figure 1, [20]. In general, the bandwidth is proportional to the carrier frequency; as a result, optical fiber is the best medium for transmission in terms of the attenuation and bandwidth. Another important feature of optical fibers is its very low noise interference. Radio interference, multiple path effect, cross talk, and even strong signal jamming would have very little effect

to the signals in fibers. This makes fiber optics more attractive than other media in many important respects.

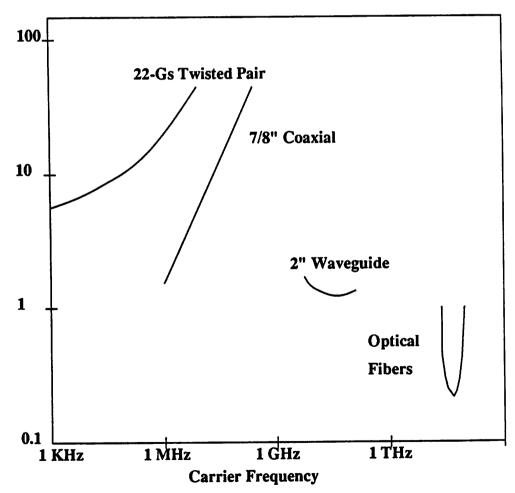

#### 1.3.2. Network Size

Not only the transmission medium but also the network size affects the quality of a communication channel. A larger size requires longer transmission lines and therefore a higher noise level, larger signal attenuation, and smaller bandwidth due to the dispersive effect. These facts make bandwidth over a long distance very expensive, and we can see in Figure 2 [21] that there is a tradeoff in the network size and bandwidth for the existing networks.

The network size also has a very important influence from the system point of view. A fundamental limitation is that the propagation delay is linearly proportional to the network size, and the larger the propa-

gation delay, the more difficult to synchronize all the users sharing a common medium [22]. For small area networks such as LANs, the propagation delay and signal distortion are both small. These leads simplicity in network designs possible. Section 4 will study this in detail and it will be clearer as we go thoroughly in next three chapters.

#### 1.3.3. Network Bandwidth

The available network bandwidth strongly depends on the transmission medium and the network size, as just explained. Larger bandwidth networks can provide more general service (e.g. video and data) and lower queuing delay.

#### 1.3.4. Network Topology

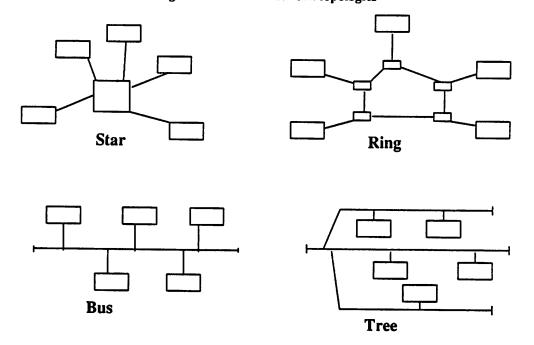

The network topology is the geometrical relationship of communication nodes in a network. The topology has strong correlations with its transmission medium, medium access protocol, system reliability and flexibility, and traffic throughput. Figure 3 shows some typical network topologies: star, ring, bus, and tree.

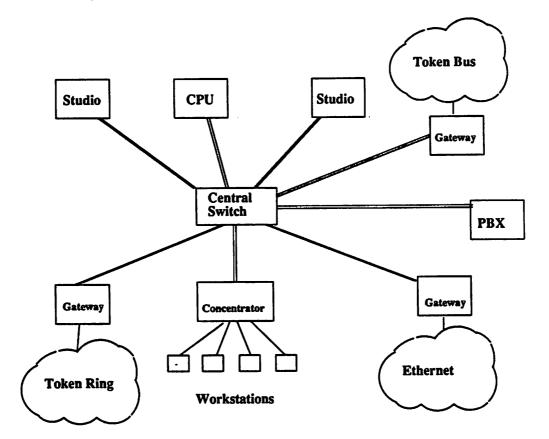

Generally speaking, the bus or ring has a linear structure and therefore traffic flow can be more regular; as a result, they are potentially more efficient in resolving access conflicts, especially when the network size is large. Token ring or token bus is an example. On the other hand, since the traffic has to go in one direction and through all the links, the total throughput is limited by the link bandwidth [22]. In addition, they have lower reliability because any node's failure may partition the network. The star provides more flexibility in traffic flow by using a circuit switch inside the central star. In addition, in fiber optics networks, the optical interface to the network prefers the star topology [7]. The disadvantage is that a central controller is required to manage the switching.

#### 1.3.5. Traffic Types

Voice, data, and video have quite different characteristics in arrival statistics, bandwidth, delay tolerance, and error tolerance, and a medium access protocol should satisfy all their needs. Detailed discussion will be given in the next section.

Figure 3. Different network topologies

#### 1.3.6. Medium Access Protocol

A medium access protocol defines the rules for users to share the common medium; in other words, it specifies how different traffics are multiplexed in a network. The first choice of multiplexing is in time or frequency domain. In this thesis, only time domain multiplexing will be considered, in which there is another choice: broadcasting or switching. Discussion of these two categories follows.

Broadcasting network techniques including token-ring, slot-ring, and carrier-sensing have been used to time-share a single physical channel among many stations for LANs. The IEEE 802 standard has established well defined protocols for LANs. The 802.3 specification is for Carrier-Sense Multiple-Access with Collision Detection (CSMA/CD) on a bus, while standards 802.4 and 802.5 are for token-passing on a bus and a ring, respectively [23-24]. The advantages of this approach are simple processing (no routing, no central controller, for examples) and low cost (no switching hardware and software required). But broadcasting has the disadvantage that total network throughput is limited by the bandwidth of a single communication link.

Switching allows multiple transmissions at the same time and therefore provides a higher throughput. There are two switching methods: packet or circuit. In packet switching, X.25 recommended by CCITT [25], for example, data is divided into packets, and involves packet capsulation and decapsulation, routing, sequencing, acknowledgement, and error recovery. For a fiber optics environment, these require high speed processors matched with the high transmission rate of optical links. On the other hand, circuit switching used in telephone networks, provides a dedicated link by prior call request, and therefore involves no complicated real-time processings. However, protocols involving circuit switching at high speed and using fiber optics have received less attention, in part because of the unavailability of wideband optical or electronic circuit switches.

#### **1.4. Traffic Characteristics**

A general communication network should accommodate all kinds of data, voice, and video traffic. Traffic characteristics which can be described by its arrival process, bandwidth, delay tolerance, and error tolerance are examined below.

#### 1.4.1. Voice

Voice traffic in most cases is interactive and requires real-time transmission. This limits the transmission delay to be within tens of milliseconds. Longer delays will make listeners uncomfortable and even noisy. On the other hand, speech is less susceptible to interference, conversation echoes, lost packets, than data.

The standard PCM digital speech requires a bit rate of 64Kb/s. During a conversation, statistically an average of 40 to 50% of time is active in each direction [26]. There are many time compression and interpolation techniques [27-30] to increase the bandwidth efficiency, but inevitably they introduce extra hardware and degraded quality. Since fiber optics in LANs and MANs provides abundant bandwidth, standard PCM voice will be simpler to use and will probably result in a lower overall cost.

#### 1.4.2. Data

Data traffic can be either interactive or send-and-wait. Interactive data (e.g. RS232) has similar characteristics to voice except that the active time percentage in each direction could be much lower. Send-and-wait data has a collection of bits to transmit, such as E-mails or file transfers. In general it is non-interactive and allows a large variation of transmission delay.

Both these types of data all require a low error rate. Messages in error generally have to be retransmitted. Their arrival process compared to speech is very bursty. These characteristics make packet switching is more favorable than circuit switching.

#### 1.4.3. Video

Video traffic in most cases requires real time transmission, and is not interactive. Compared to voice, it has much larger bandwidth (50 to 140 Mb/s) and 100% bandwidth usage. As a result, circuit switching seems to be most promising for video.

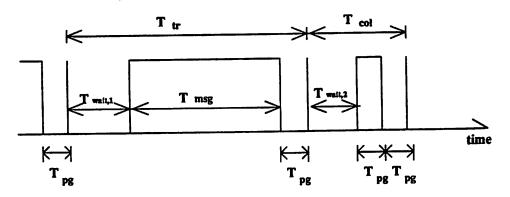

## 1.5. Local Area and Metropolitan Area Networks

Local area networks (LANs) were developed first for data communication among workstations or minicomputers [11,12], and have short propagation delay and small signal distortion. These features provide extra opportunities in the protocol design. For example, CSMA and ALOHA [31-32] both bear the same concept of random access, but only CSMA has collision detection (CD) capability to abort a collided transmission immediately. In general, the larger the propagation delay, the higher the "asynchronousness" between users. This asynchronousness reveals itself in different forms in different networks. For CSMA/CD, it is the time to detect a collision; for token-ring, it is the time to pass the token; and for TDMA (Time Division Multiple Access) [33], it is the guard time between adjacent time slots. Fortunately, when a LAN is concerned, this asynchronousness is negligible and can be traded for simpler protocols or implementations.

Low signal distortion offers an additional opportunity in implementation. If a packet passes a few nodes which are not the destination, timing recovery would be unnecessary because timing distortion is not

## Chapter 1: Introduction

significant. For fiber optics with low noise, small dispersion, and little attenuation, no timing recovery is necessary, thereby reducing the cost in implementation.

Metropolitan area networks (MANs) have a larger network size (about 50 Km); therefore, the propagation delay becomes more significant than in LANs. Techniques in LANs consequently can not be applied directly and need at least some modifications. For example, CSMA/CD would be unfeasible in MANs because the overhead in collision time is very significant, and IEEE 802.6 [18] is modified from the slot-ring protocol to fit MAN applications.

On the other hand, if MAN is used for the intercommunication between LANs, PBXs, and main frames, the structure of a network for this purpose could be simpler than that of LANs. This has an analogy that wire connections of central offices in telephone networks are much simpler than those of local user distributions. This important property will be utilized in the protocol studied in chapter 4.

# 1.6. Fiber Optics and Integrated Electronics

Over the past 15 years, successful efforts have been made to increase the bandwidth and reduce the energy attenuation in fibers. Now inexpensive optical fiber media capable of several Gb/s data rates over point-to-point links of several kilometers are available. It has become very attractive to use optical fiber as the transmission media for LANs or MANs.

To produce economical fiber optic systems, the electronic functions required in transmitters, receivers, multiplexors, circuit switches, buffers, etc. must be eventually integrated as VLSI components. Unfortunately, neither silicon nor gallium arsenide technology can provide VLSI implementations capable of operating at rates higher than a few hundred Mb/s. While this is adequate for integrated voice, data, and video services to a single station, it is not high enough to meet the needs in a broadcast network of tens or hundreds of stations.

An additional impetus for introducing switching into a fiber optic network is that many years of research on optical devices have failed to produce practical three-way optical couplers that would be needed for networks based on a shared optical bus [7]. The reason is optical couplers have insertion loss

-9-

which limits the total number of taps on a bus. Active couplers are subject to failure unreliability and high cost. In addition, practical optical switches that could be the basis for a switched optical network are not available. However, recent work has demonstrated the feasibility of economical electronic circuit switches in CMOS VLSI, operating at up to 200 Mb/s data rates per channel [34,35]. Assuming the availability of economical switching techniques, a network based on this requires an opto-electronic transceiver pair for every link at each switching node. However, avoiding the costly timing recovery function at the switching node(s) can significantly reduce costs. Provided that crosstalk and timing jitter in a fiber-optic local area network can be adequately controlled, we will describe an approach which avoids the need for timing recovery in the switching nodes.

#### **1.7. The Approaches**

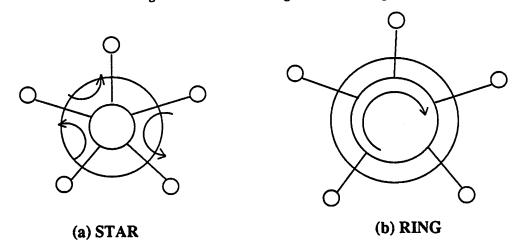

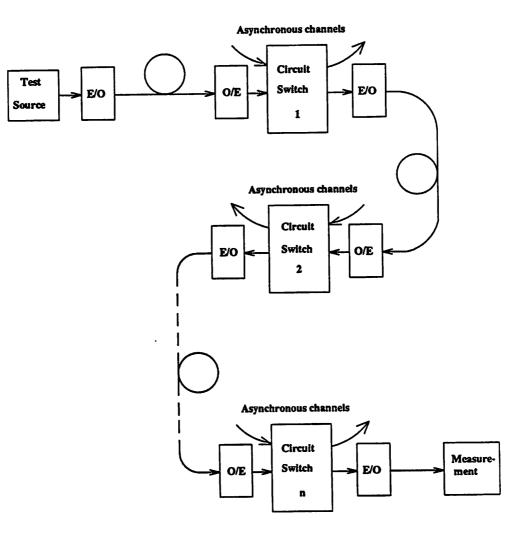

Instead of going to more exotic and costly technologies to achieve a higher rate network utilizing a broadcast protocol such as CSMA or a token-ring, our approach will be to incorporate switching in the network, in order to gain almost unlimited bandwidth capability while at the same time running each link in the network at the highest speed consistent with low-cost technologies. A comparison between circuit switching and broadcasting architectures is illustrated in Fig. (4a) and (4b). Switching allows multiple transmission paths to coexist simultaneously, resulting in greater network throughput for a given link bandwidth. This approach offers in addition the ability to add network capacity incrementally, and it is inherently more reliable since failures result in incremental loss of capacity.

In considering switching, we have chosen circuit switching primarily because it allows a switching fabric that does not actually examine or process the bit streams passing through (as just explained in section 1.2.6), with the result that the bit rate can be considerably greater for a given low-cost technology. This greater speed can more than make up for the inefficiency in circuit switching data traffic with fluctuating bit rates, particularly in view of that fact that packet switching data networks can easily be overlaid on the circuit network using lower speed circuits as packet links. Furthermore, the modest efficiencies gained in packet switching voice and video do not appear to be justified in a small-area network where bandwidth is plentiful.

Figure 4. Circuit switching vs. broadcasting

There has been previous work on LANs using circuit switching at 1 Mb/s [36] and 380 Mb/s [37]. With circuit switching, low speed traffic, like 64 Kb/s voice channels, needs to be multiplexed into high speed media. This can result in timing recovery and multiplexing functions which reduce the achievable bit rate. An additional problem with circuit switching is that when the number of switchable links is small, significant blocking will occur at a low level of network utilization.

These problems with circuit switching lead us to propose a variant which we call time slot switching (TSS). TSS can be described as a time-divided space-division switch in a particular form well-suited to LANs based on fiber optics. A detailed description of TSS is in chapter 2.

The electronic switch can not only be operated to switch different traffics, but can also be configured in a broadcasting way. This provides the flexibility in combining TSS with other broadcasting protocols for better serving some data traffic. Chapter 3 considers the integration of TSS and CSMA, and chapter 4 evaluates the combination of TSS and Slot-Ring. Their performance in LANs and MANs will also be studied in these chapters.

In chapter 5, an approach leading to the simplification of timing recovery is also considered. High speed timing recovery is essential but difficult to implement in digital communications. A fixed coding technique is proposed and tested. Finally, chapter 6 discusses tests of the effects of no timing recovery but just amplification when bit streams pass through many circuit switches connected by fiber optics by TSS as

proposed in chapter 2.

#### **REFERENCE:**

[1] Morton I. Schwartz, Optical Fiber Transmission - From Conception to Prominence in 20 Years, IEEE Communication Magazine, May 1984, pp. 38-48.

[2] Eric G. Rawson, Application of Fiber Optics to Local Networks Proceedings of the LACN Symposium, May 1979.

[3] A. Husain and S. D. Cook, Impact of Fiber Optics on Local Area Networking SPIE Vol. 355, 1982, pp. 120-126.

[4] Tadashi Akiba, Akihiro Okada, Shun Suzuki and Osamu Takahashi, Optical Bus Network Using Ethernet and Higher Level Protocol LSIs Proceeding of ICC, 1984, pp. 1335-1339.

[5] S. D. Personick, A Review of Alternative Fiber Optic Distributed Access Network Designs, - And The Problems They May Solve Proceeding of ICC, 1984, pp. 898-902.

[6] Ronald V. Schmidt and Eric G. Rawson, Fibernet II: a Fiber Optic Local Area Network with Data Collision Sensing, SPIE Vol. 355, 1982, pp. 127-131.

[7] Marion R. Finley Jr., Optical Fibers in Local Area Network, IEEE Communication Magazine, Aug. 1984, pp. 22-35.

[8] J. A. Becker and J. N. Shive The Transistor - A New Semiconductor Amplifier Electrical Engineering, March 1949, pp. 215-221 and reprinted in Proceedings of the IEEE, Dec. 1984, pp. 1696-1703.

[9] Rick D. Davies The Case for CMOS, IEEE Spectrum, October 1983, pp. 26-32.

[10] Edward T. Lewis Design and Performance of "1.25-um" CMOS for Digital Applications

[11] V. David Tsao, A LAN Architecture Overview, IEEE Communication Magazine, August 1984, pp.

7-11.

[12] Robert M. Metcalfe and David R. Boggs, Distributed Packet Switching for Local Computer Networks, Communications of ACM, July 1976, pp. 395-404.

[13] J. D. Markov and N. C. Strole, *Token-Ring Local Area Networks: A Perspective*, Proceedings of COMPCON F82, pp. 606-614.

[14] D. W. Andrews and G. D. Schultz, A Token-Ring Architecture for Local Area Networks: An Update, ibid, pp. 615-624.

[15] J. H. Saltzer, D. D. Clark, and K. T. Pogran, *Why a Ring?* Proceedings of the Seventh Data communications Symposium, 1981, pp. 211-217.

[16] Robert W. Klessig, Overview of Metropolitan Area Networks, IEEE Communications Magazine, January 1986, pp. 9-15.

[17] Floyd E. Ross, FDDI - A Tutorial, IEEE Communications Magazine, May 1986, pp. 10-17.

[18] Draft of Proposed IEEE 802.6 Standard, Metropolitan Area Network (MAN) Media Access Control, August 1985, Revision D.

[19] Daniel T. W. Sze, A Metropolitan Area Network IEEE Journal on Selected Areas In Communications, November 1985, pp. 815-824.

[20] Paul S. Henry, Introduction to Lightwave Transmission, IEEE Communications Magazine, May 1985, pp. 12-16.

[21] William Stallings, Local Networks, An Introduction, ISBN 0-02-415460-1, 1984, Chapter 1.

[22] C. Petitpierre, Influence of the Network Topology Upon the Throughput Limitations, Proceedings of ICC 1984, pp. 428-433.

[23] IEEE Project 802, Local Area Network Traffic Handling Characteristics Committee Report, working draft, January 1982.

[24] IEEE 802.3, IEEE 802.4, and IEEE 802.5, ANSI/IEEE Standards, Draft International Standard, IEEE Inc., 1985.

[25] CCITT Recommendations X.1, X.2, X.25, X.92, and X.96 *Public Data Networks*, CCITT Orange Book, Vol. VIII.2, Geneva, Switzerland: ITU, 1977

[26] Paul T. Brady, A Statistical Analysis of On-Off Patterns in 16 Conversations, The Bell System Technical Journal, January 1968, pp. 73-91.

[27] K. Bullington and J. M. Fraser, Engineering Aspects of TASI ibid, March 1959, pp. 353-364.

[28] J. M. Fraser, D. B. Bullock, and N. G. Long, Over-All Characteristics of a TASI System, ibid, July 1962, pp. 1439-1454.

[29] H. Miedema and M. G. Schachtman, TASI Quality - Effect of Speech Detectors and Interpolation, ibid, July 1962, pp. 1455-1473.

[30] Richard V. Cox and Ronald E. Crochiere, Multiple User Variable Rate Coding for TASI and Packet Transmission Systems IEEE Transactions on Communications, March 1980, pp. 334-344.

[31] N. Abramson, The ALOHA System - Another Alternative for Computer Communications, AFIPS Conference Proceedings, Vol. 37, 1970, pp. 281-285.

[32] R. Binder, et. al., ALOHA Packet Broadcasting - A Retrospect, AFIPS Conference Proceedings, Vol. 44, 1975, pp. 201-215.

[33] Kemilo Feher, Digital Communications, Satellite/Earth Station Engineering, Prentice Hall Press, 1981.

[34] Gary A. Hayward, A. M. Gottlieb, D. G. Boyer, and J. E. Berthold, *High-Speed 16x16 CMOS Crosspoint Switch, Electronics Letters, Vol. 21*, No. 20, 1985, pp. 923-925.

[35] H. J. Shin and D. A. Hodges, CMOS Switch for 200 Mb/s Fiber Optic Networks, to be published.

[36] B. Hailpern, A. Heller, L. W. Hoevel, and Y. J. Thefaine, ALAN: A (Circuit-Switched) Local Area Network, IEEE Jr. on Selected Areas in Communications, May 1985, pp. 427-430.

[37] Ulrich Killat and Johann Kruger, System Aspects and Realization of Wide-Band Switching in the Local Area, ibid, March 1985, pp. 330-335.

# Part I.

**Asynchronous Time Division Networks**

## **CHAPTER 2**

## Time Slot Switching

#### 2.1. Introduction

A new medium access protocol called *Time Slot Switching* (TSS) for use in fiber optics LAN is explained in this chapter. This protocol incorporates features of time division, space division, and time compression for users to share a common medium. With these features, data, voice, and video traffic can all be served in a single local area network. In addition to fiber optics used for transmission, VLSI CMOS electrical crosspoints are used to switch traffic within individual time slots. Based on these techniques, high network traffic capacity and low implementation costs can be achieved.

Although TSS can serve various kinds of traffic, operation of TSS for a specific type of traffic with one constant rate (homogeneous TSS) is first described in section 2. CMOS circuit switches in TSS in general are distributed in a network and controlled by a central controller which assigns time slots and crosspoints for requesting traffic. This traffic control management will be explained in section 3. To examine the performance, an analysis is presented in section 4 to show the trade-offs among traffic capacity, frame guard times, blocking probability for new circuit requests, and transmission delay. The analysis is done for 64 and 16 Kb/s channels, and the results show that TSS is more attractive than broadcast protocols for voice traffic or constant rate data traffic. In section 5, TSS is generalized for serving voice, data, and video traffic.

## 2.2. Homogeneous TSS Networks

By a "homogeneous" TSS network, we mean one which supports a multiplicity of circuits, all at the same constant rate (e.g., 64 Kb/s PCM voice channel); this homogeneous assumption will be relaxed in Section 5.

#### 2.2.1. Network Topology and Architecture

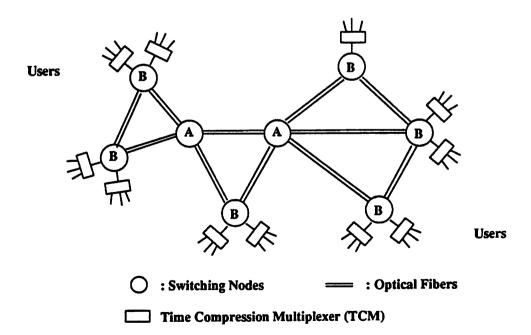

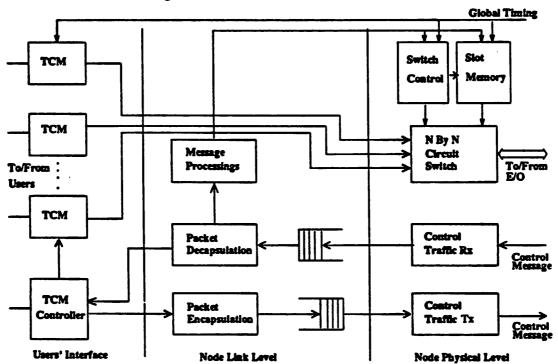

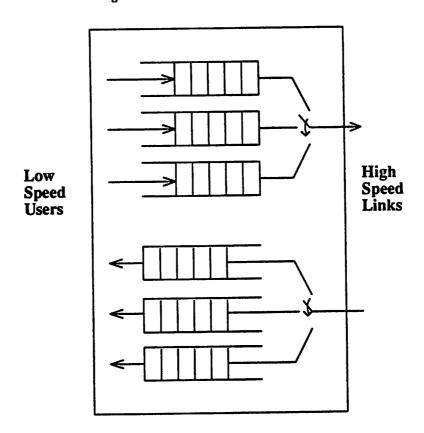

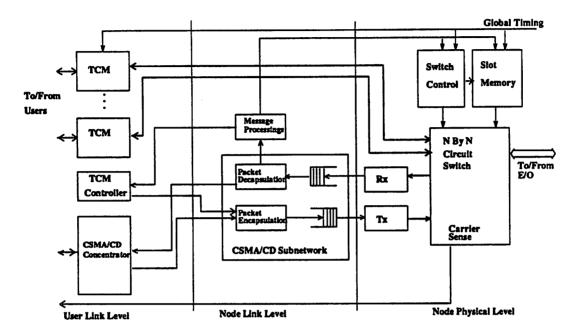

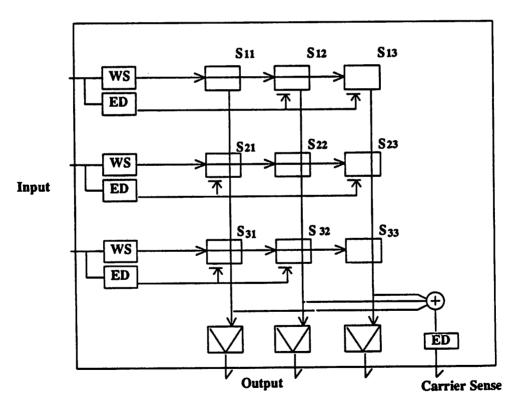

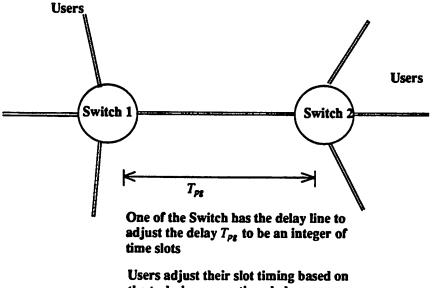

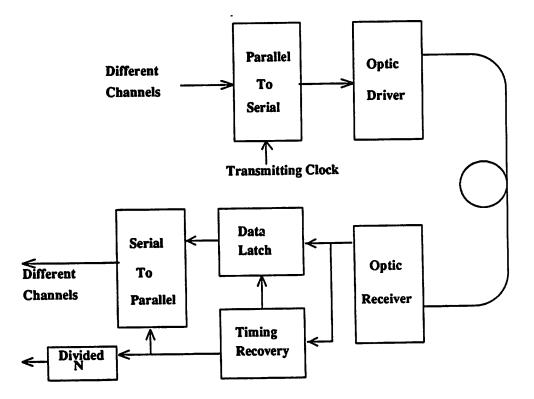

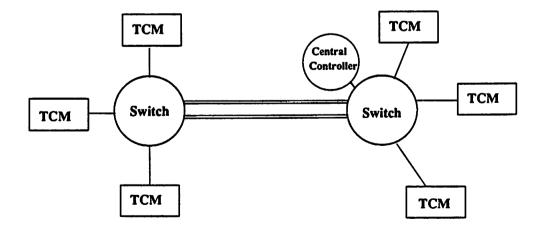

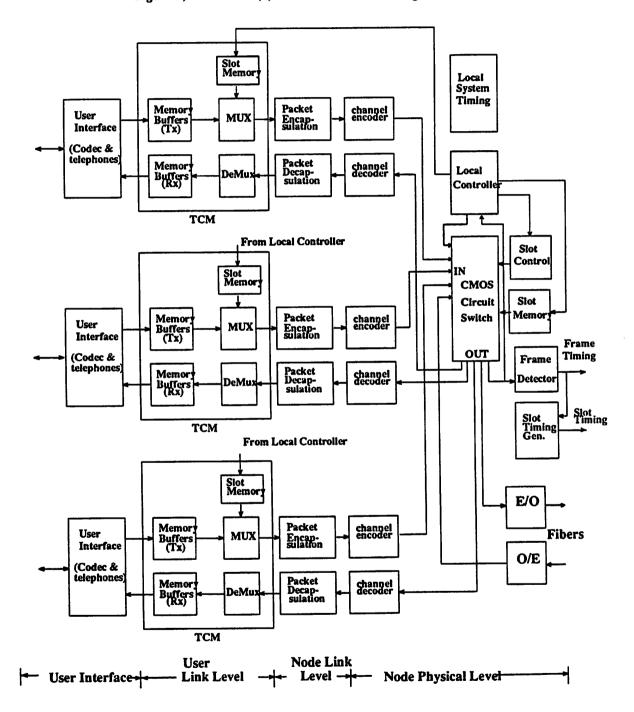

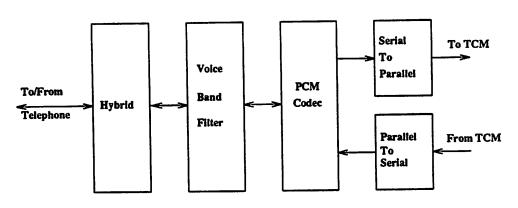

A TSS network generally consists of switching nodes connected by fiber optics. The switching nodes connect simultaneous circuits by their internal space-division switches. Users access the switching nodes through concentrators called time compression multiplexers (TCM), which multiplex user traffic in a time-division fashion, figures (1,2). Detailed operations of the switches and TCM will be addressed shortly.

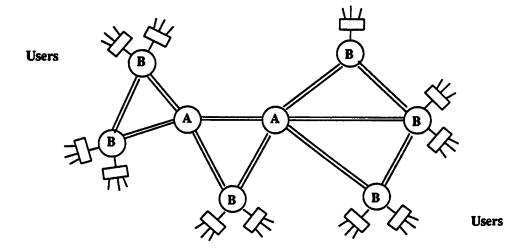

Figure (1a) illustrates a mesh network structure with two types of switching nodes. Type A switches are only connected with other switching nodes. Type B switches connect TCMs with Type A and/or other type B nodes.

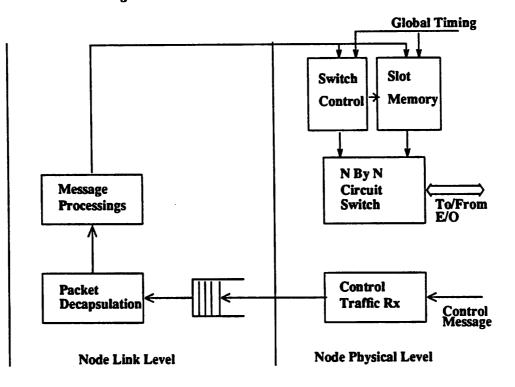

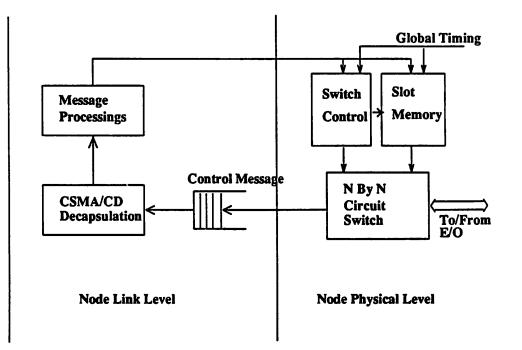

Figure (1b) shows a type A switching node, drawn to illustrate link level (control) and physical level (data path) elements. The circuit switches need connection information from the central controller to set up communication links; this information may be conveyed by a separate (lower speed) network, or by the TSS network itself where dedicated slots are reserved for this purpose (see section 3).

Figure 1a. TSS network topology and architecture

5

Figure 1b. Internal architecture of class A nodes

Figure (1c) shows a type B switching node, where it not only receives the connection information, but also transmits control messages like "circuit request" or "circuit finish" from the user terminals.

#### 2.2.2. Basic Operations

Time slot switching (TSS) can be described as a switched time-division multiple-access (TDMA) network [1]. TDMA is often used in satellite networks for the same reason it is used here; namely, it allows very simple hardware for running the network at the maximum speed for a given technology. TCMs are used in TSS to give users TDMA access. In addition to the TCMs, TSS incorporates circuit switches to increase traffic throughput; in other words, the configuration of all the space-division switches

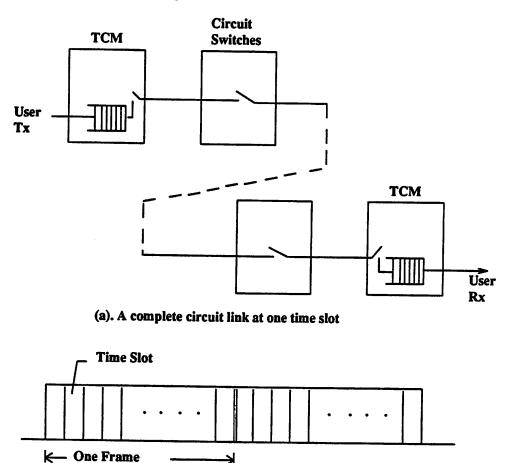

#### Figure 2. Basic circuit connections

(b). Time Division Multiple Access

┝

within the network changes for each time slot, thereby providing a multiplicity of circuits.

To set up a communication link, both the TCM and switches should operate synchronously in each time slot, figure (2); that is, a bit stream from a transmitting user is first multiplexed through a TCM to a circuit switch in a certain time slot, then arrives at the destination TCM through a correct connection of cross-points, and is finally demultiplexed to the receiving user at the same time slot. This synchronization between the TCM and switches is established by a pre-arrangement and will be discussed in section 3.

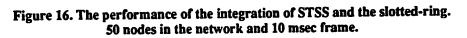

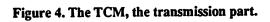

The TCM is an interface between low speed users and high speed circuit switches. The TCM performs two functions. One is to buffer a number of bits during one frame for lower speed users. Second, the TCM transmits or receives these bits within the appropriate time slot for which the desired connectivity has been pre-arranged through the space-division network. Each circuit for a particular user terminal will continue to access the same time slot in each frame for the duration of the circuit. Figure (3) shows the

Figure 3. Internal structure of a TCM

configuration of a TCM. Here we see the user data streams are first stored in the transmitting buffers of the TCM. Typically more than one circuit will be established within a given TCM, and each circuit has its own buffer. Then during the selected time slots, the data in the corresponding buffers is transmitted over the high speed link. Similarly, on the receiving side, data arriving on a high speed link within pre-selected time slots are stored in receiving buffers, and then transmitted at a continuous slower speed to the user terminals. To summarize, a lower speed circuit is *compressed* and transmitted over the higher speed channel in a specific time slot in the frame, and at the receiver the circuit is *decompressed* for that same time slot to the lower speed user terminal.

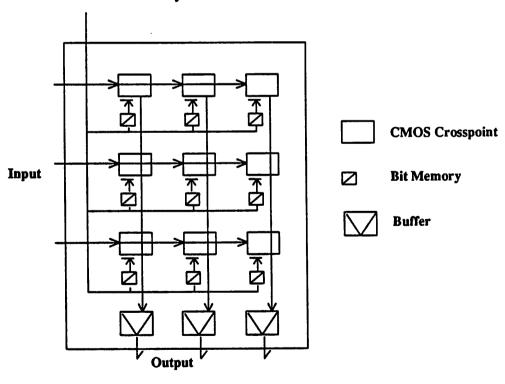

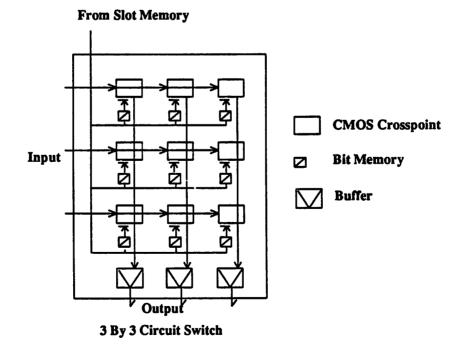

The Circuit Switches connect physical paths for different communication links. An internal architecture of a circuit switch consists of an electrical cross-point matrix, a bank of slot memory, and control

Figure 4. Internal structure of a circuit switch

From Slot Memory

circuitry, figure (4) [2]. The slot memory contains connection information used for changing the configuration of the cross-point matrix after each time slot. The control circuitry provides slot timing and updates the connection information. In each time slot, there are simultaneous circuits being transmitted by the switches, each at a very high speed (e.g 200 Mb/s) compared to that of users. These multiple links combine to a total traffic capacity much greater than that achieved by broadcasting protocols such as token passing or CSMA operating at the same link speed.

## 2.2.3. Some Remarks on TSS

For the foreseeable future, electronics rather than optics is the factor that limits the bandwidth of practical fiber optic networks. TSS is primarily motivated by the desire to minimize the impact of electronic limitations:

- 1. The traffic passes through the TSS network *asynchronously*; in other words, no examination or processing of bit streams is required except at the source and destination nodes, where the data can be handled in a parallel format up to the final parallel-to-serial conversion in the TCM. This minimizes high speed electronics constraints.

- 2. Because the asynchronousness of the traffic flow, different instantaneous bit rates can coexist within the same network. For example, the logically separate control network can operate at a slower speed within a dedicated time slot, eliminating the necessity for using the same high speed electronics technology in the implementation of the control as compared to the switching function itself.

- 3. Timing recovery is required only once for each link, in the destination node (this is similar to broad-cast networks). High-speed timing recovery is a costly function in opto-electronic transceivers; this function would be needed for every channel through every switch if bit or byte synchronization were required. In contrast, the function of low-speed timing recovery for frame synchronization is needed only once per switch node (section 3).

- 4. Collisions are eliminated by the arbitration provided by a central controller.

5. Circuit switching results in a deterministic delay, which is desirable in voice traffic and some data communication.

TSS also has disadvantages of course:

- 1. Though the switching nodes receive the same global timing, they are distributed in the network. Timing skew among these switching nodes is inevitable. This, coupled with the propagation delay of signals through the network results in the need for guard times in each time slot, and a resultant reduction in traffic capacity. This is very similar to the situation of satellite communication by TDMA with distributed earth stations. The need for reasonable throughput efficiency limits the geographical size of the network, although this limitation can be circumvented by using gateways with internal buffering.

- Circuit switching results in blocking [3]. At a given traffic intensity, by increasing the total number of time slots in a frame, the blocking probability can be reduced, but at the expense of a larger frame size, which results in a larger transmission delay. The frame size can not be arbitrary large (see Eq. (9)); however, within its possible range, an achievable traffic intensity level can be estimated by specifying the blocking probability (e.g. 10<sup>-3</sup>), Eq. (7).

- 3. TSS results in a buffering delay, called the compression time, on the order of the time duration of one frame. This is due to the need in the TCM to store one frame of data for transmission at a higher link bandwidth. This presents a problem in voice and interactive applications. (The first three disadvantages are analyzed in detail in section 4.)

- 4. Intermediate space-division switches without retiming introduce timing jitter due to dispersion on the fiber and crosstalk within the switch. This will limit the number of intermediate switching nodes and hence the allowable network topologies. Experiments to quantify this limit has been carried (chapter 6), and the results showed that the timing jitter is not noticeable.

- 5. The basic circuit switching architecture suggests a central controller. This, in addition to the requirement for global time slot timing, introduce possible points of vulnerability to single-point failure. This can be overcome by careful design and redundancy in these functions.

#### 2.3. Switching Management

Because TSS has both time and space division switching, the TCM and switches need (1) frame timing, (2) slot timing, (3) cross-point connection information, and (4) TCM multiplexing information to set up correct communication links.

### 2.3.1. Frame and Slot Timing

The frame and slot timing are needed to change the TCM and switch configurations. These configurations are different in each time slot, and repeat each frame.

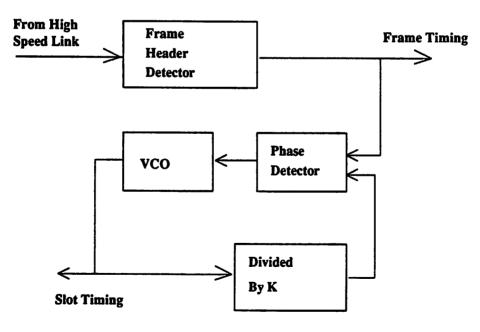

The frame timing can be obtained simply by generating a frame header of a special pattern and frequency from the central controller, just as in TDMA in satellite communications [1]. In TSS, this frame header can be put at the beginning of each frame; and by sensing this particular pattern, the frame timing can be extracted. Since both the frame and slot timing is at relatively low frequency (e.g. 20 Hz if each frame is of 50 msec, and 20 KHz if each slot is of 50  $\mu$ sec), a simple PLL and a frequency divider can gen-

Figure 5. Frame and slot timing recovery

(K is the no. of slots in a frame)

erate slot timing synchronized with respect to the frame timing, figure (5).

### 2.3.2. Circuit Connection Setup

The switches and TCM need connection information to set up circuits correctly in each time slot. Since the switching nodes are generally distributed in the network, this connection is determined and distributed by the central controller after the controller receives "call requests" or "call finishes" from users. This subsection describes an algorithm for the controller to set up circuits, and the next subsection suggests how to pass the connection information between the switches and controller.

First, the central controller has a cross-point allocation table for each circuit switch and each time slot. After receiving a circuit request from one switching node to another node, the controller linearly searches for the first available time slot from the beginning of the frame. Generally, the circuit path may not be unique for a call, switches and cross-points of the minimum distance path will be chosen if there is no particular reason. Other searching algorithms such as random search are also possible, but will not be covered in this chapter.

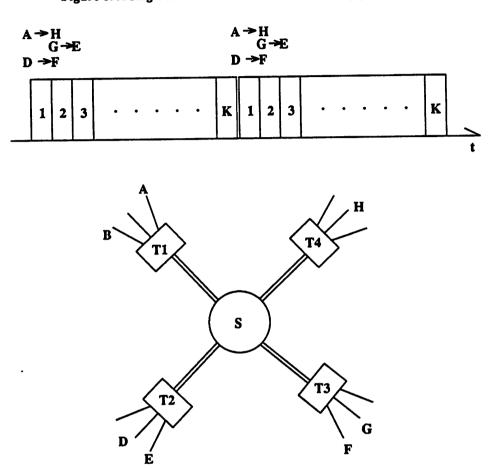

As an example illustrated in figure (6), user terminal A is currently transmitting to user H during time slot 1 of each frame. TCMs T1, T4 and the switch S are synchronized to provide this link. Now, user terminal D wants to transmit to user F. There is no other traffic through TCM T2 and T3, and the current link between A and H causes no conflict in using circuit switch S for this new request. Thus the central controller can assign any slot for this new request, and it chooses slot no. 1 by the algorithm There will be two independent circuits in the same time slot. A few moments later, user terminal G wants to communicate with user E and sends the request to the central controller. There is no conflict with the existing circuits in the central controller. There is no conflict with the existing circuits in the central controller will assign time slot 2 for this new request.

If there is neither an available time slot nor an available space-division path for a new requested circuit even the destination is idle, blocking occurs. The probability of blocking is estimated in the next section. Any circuit can be terminated by transmitting an appropriate "disconnect" message to the central controller, releasing the associated time slot for future use.

Figure 6. A single star network and its circuit setup procedures

### 2.3.3. The Control Traffic

A logically separate signaling network is needed to provide the connection information as mentioned above. This traffic demands can be estimated as follows: suppose there are 1000 users with active probability 50% (i.e. 50% of users are most likely using circuits at any time), and an average of circuit holding time is three minuntes such as in voice conversations, there will be only  $1000 \cdot \frac{0.5}{180}$ =2.8 calls/min. Suppose each circuit establishment requires 1 Kb/call (to send source and destination addresses to the controller, and to send the connection information to the switching nodes), then the total control traffic demand is only about 3 Kb/s.

As mentioned before, though this control traffic can be supported by a separate lower speed network, it can be supported by the same TSS network with the first few slots reserved. For example, in the network shown in figure (1), let the switching node of type A on the right be the central controller also, the connection information for all the switches and TCM can be broadcasted at the second time slot of each frame, and the call request and finish information from all the switching nodes of type B can be sent to the controller at the third and forth time slots (at least two slots needed since there is a circuit conflict of two type B switching nodes on the left). It is noted that the first slot is already assigned for the extraction of the frame timing.

### 2.4. Performance Analysis of Homogeneous TSS

In this section, we present a quantitative analysis of the behavior of the TSS network. For simplicity, we treat the homogeneous case in which all circuits have the same bit rate. In order to quantify the impact of the choice of the bit rate, we consider two cases: 16 and 64 Kb/s.

In the analysis of TSS, we must consider a number of dependent parameters: the number of time slots per frame, the length of a time slot, the blocking probability for new circuit connection requests, utilization, and the compression delay. In the remainder of this section, we determine the following:

- 1. The guard time, required to protect the data in adjacent slots. It will be shown to be proportional to the maximum propagation delay in the network.

- 2. The blocking probability, which is a function of the topology and available circuits. We approximate this probability for a single or double star network topology.

- 3. The compression delay, which depends on the total number of time slots per frame, the slot size, and hence the utilization.

- 4. The preceding allows us finally to study the tradeoff between network utilization and the compression delay for a fixed blocking probability and network topology.

Before proceeding with the analysis, some definitions are appropriate:

Network Circuits: The average number of circuits connected at one time. Using telephone terminology, this has the units of Erlangs, where one Erlang is equivalent to one circuit continuously connected.

Network Utilization: The ratio of average total network throughput (bits per second) to the capacity of one link. Since multiple links are utilized in TSS due to switching, the network utilization in general can be greater 100%. This definition of utilization enables us to compare the traffic capacity to that of a multiple access protocol using a single shared link with the same capacity.

Blocking Probability: The probability that a circuit initiation request will be denied due to the absence of an available circuit path for any time slot between source and destination.

**Compression Delay:** The delay introduced in the most efficient implementation of TSS is equal to the time duration of one frame, which we call the compression delay. The delay in a practical implementation is likely to be slightly larger than this, since the propagation delay will be comparably smaller.

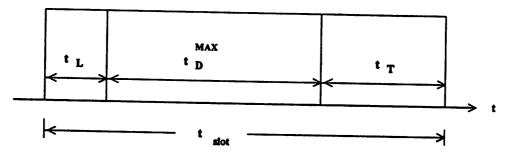

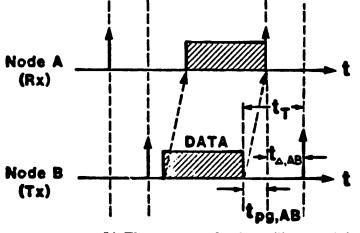

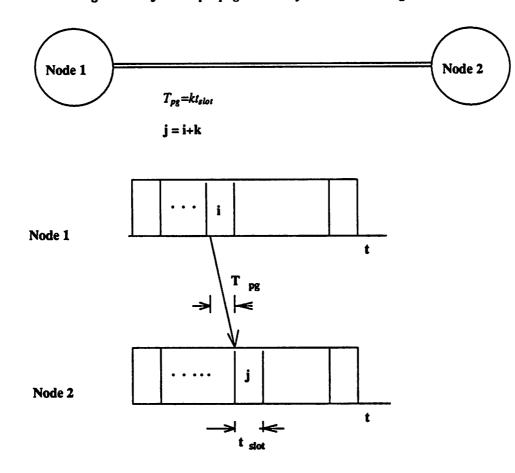

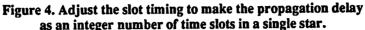

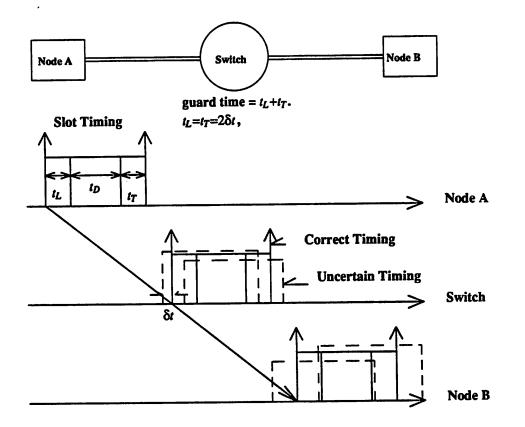

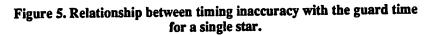

### 2.4.1. Guard Time Analysis

A time slot shown in figure (2.b) is shown in more detail in figure (7), where  $t_L$  is the leading guard time of a time slot,  $t_T$  is the trailing guard time of a time slot, and  $t_{B}^{MAX}$  is the interval of time available for actual data transmission. Then we have an expression for the interval of time corresponding to a time slot,

$$l_{slot} = l_L + l_D^{MAX} + l_T \equiv l_D^{MAX} + l_{idle}$$

(1)

The requirement for non-zero  $t_L$  and  $t_T$  derives from finite propagation delay and timing skew (due to distributed global timing propagation delay between the central clock and each switching node in the net-

## Figure 7. Internal structure of a time slot

work).

The slot utilization  $\eta_{slot}$ , defined as the fraction of the slot bandwidth actually used for data transmission, is

$$\eta_{slot} = \frac{t \beta^{fAX}}{t_{slot}}$$

(2)

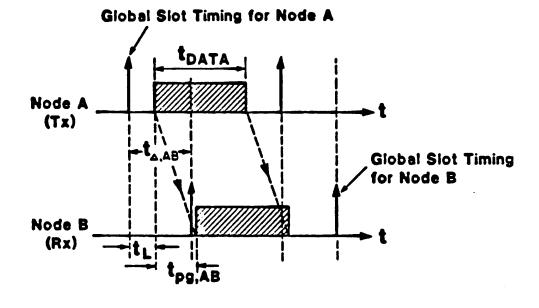

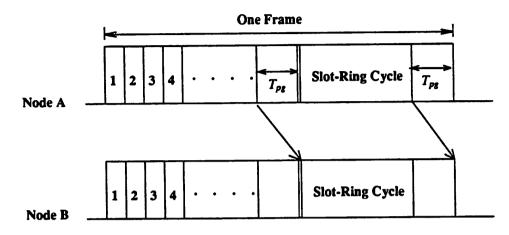

From Eq.(2), we want to minimize the guard times  $t_L$  and  $t_T$ . This minimal condition of  $t_L + t_T \equiv t_{idle}$  can be obtained as in figure (8). Starting with  $t_L$ , the purpose of the leading guard time is to insure that a packet does not arrive at a node prior to the start of a time slot. Suppose node A sends a packet to node B where the global time slot timing of Node A leads that of Node B, as shown in figure (8a). To ensure that the beginning of the packet from Node A does not arrive too early, we have

$$i_L + i_{pg,AB} \geq i_{\Delta,AB}$$

where  $t_{PR,AB}$  is the propagation delay between nodes A and B, and  $t_{\Delta,AB}$  is the timing skew for the time slot clock between nodes A and B.

Similarly, the purpose of the trailing guard time is to insure that the end of a packet from node B to node A occurs before the end of the time slot as shown in figure 8b. The requirement is that

The above conditions have to hold for any two switching nodes, so we have

$$t_{L} = \begin{cases} 0, & \text{if } t_{\Delta,\max} < t_{pg,\min} \\ t_{\Delta,\max} - t_{pg,\min} \\ \text{, otherwise.} \end{cases}$$

(3)

Also,

$$t_T \ge t_{\Delta,\max} + t_{pg,\max} \tag{4}$$

The worst case occurs when  $t_{pg,min} = 0$  and  $t_{\Delta,max} \approx t_{pg,max} = t_{pg}$ , in which case

$$l_L = l_{Pg}$$

$$l_T \approx 2 \, l_{Pg}$$

$$l_{idle} \equiv l_L + l_T \approx 3 l_{Pg}$$

(5)

Because  $t_{p_2}$ , the maximum propagation time throught the network, cannot be reduced without compromising the size of the network, the only way to minimize the guard time  $t_{idle}$  is to minimize the

Figure 8. Guard time analysis for the worst cases

### (a). The worst case for the leading guard time.

(b). The worst case for the trailing guard time.

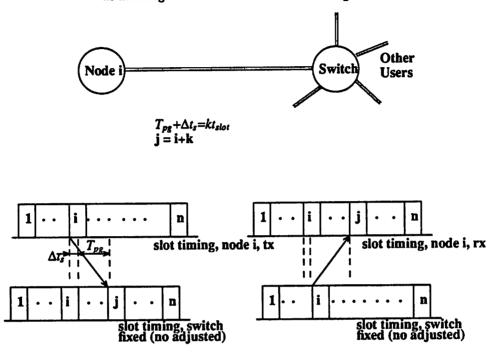

timing skew  $t_{\Delta,max}$ . If we borrow a technique from TDMA satellite communications, where guard time also exists because of distributed earth stations [1], the guard time can be reduced by estimating the distance between the earth station and the satellite in the initialization of the switching nodes. Similarly, the propagation delay between a switching node to the central controller in TSS can be estimated, and the frame timing can be offset by this amount. That is, the time skew effect in the guard time can be reduced to a minimum; in that case, by Eqs. (3-4),  $t_L$  will be 0 and  $t_T$  will be only one  $t_{pg}$ . The idle time could be reduced to

$$t_{idle} \approx t_{pg}$$

. (6)

In particular, if there is only one switching node in TSS, just like the case where many earth stations communicate to each other by only one satellite, the propagation effect in the trailing guard time (Eq. (4)) will also be zero, and the guard time can be made to approach to zero.

### 2.4.2. Network Circuits and Blocking Probability

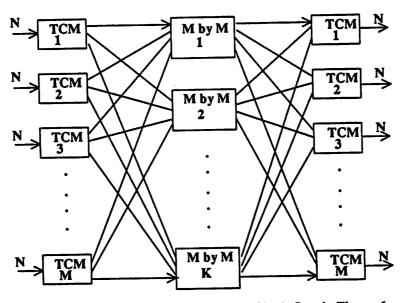

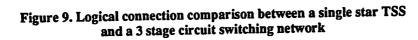

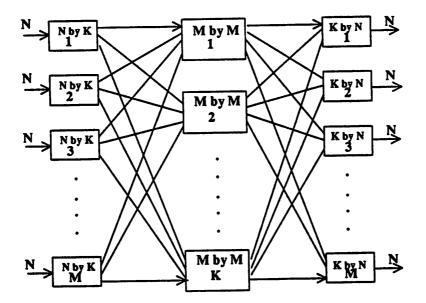

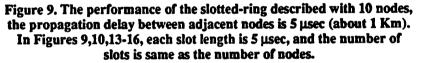

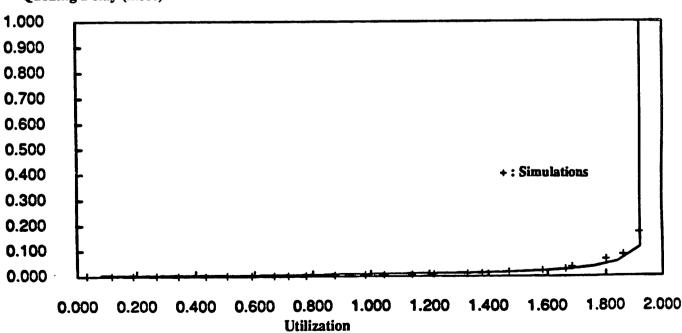

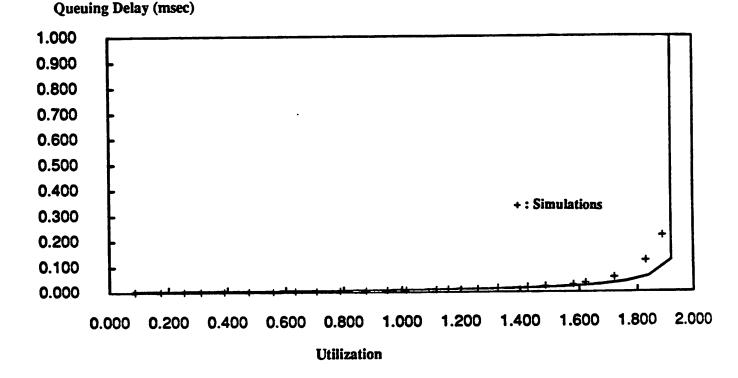

In this section, we calculate the relationship between the average number of active circuits and the blocking probability in TSS. For a given network topology, any TSS network can be transformed into a topologically equivalent space-division switching network for which the blocking probability can be estimated by the method of Lee [3]. To illustrate, a simple single star network in figure (6) is considered. There are M TCMs connected to the central M by M switch, K time slots in each frame of the TCM, and N < K user terminals connected to each TCM. As shown in figure (9), this switching network is equivalent to a space-division network with three stages. There are K (M by M) switches in the middle stage, one for each time slot, corresponding to the single physical time-divided space-division M by M switch. Each TCM allows the N user terminals to access one of K time slots, and hence is topologically equivalent to an N by K space-division switch.

In general, except for special designs [4], switching networks have a non-zero blocking probability. Given a circuit switch structure, Lee [3] developed an approximate method of evaluating the blocking probability. For a single-star network shown in figure (6), by Lee's method (see Appendix A), we have the following approximation to the blocking probability,

$$P_{bk} = [1 - (1 - p)^2]^{\kappa}$$

$$p = \frac{A}{MK},$$

where A is the total offered traffic in Erlangs.

(a). Switching Connections of the Single Star in Figure 6

(b). Equivalent Three Stage Space-Division Switching Network

,

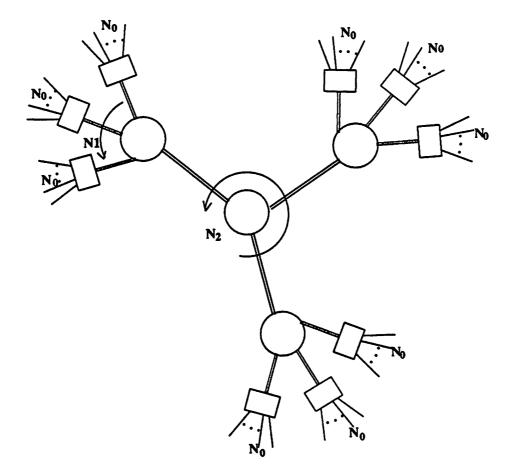

# Figure 10. A double star TSS network

A similar analysis for a a double-star network (Fig. (10), see Appendix B) gives

$$A = KN_{2} \left\{ 1 - \left(1 - P_{bx}^{\frac{1}{2}}\right)^{\frac{1}{2}} \right\}.$$

(7)

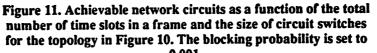

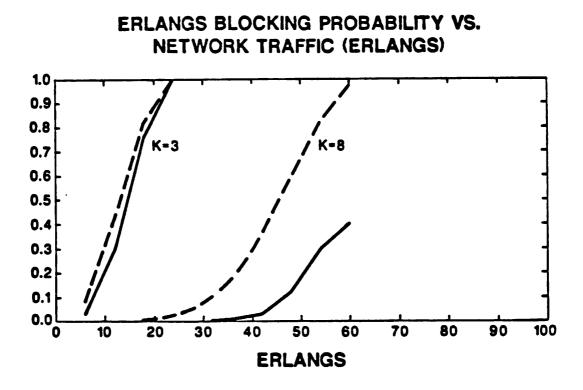

Figure (11) illustrates this relation numerically for a blocking probability of  $10^{-3}$ .

Our experience is that Lee's method gives a conservative estimate of blocking probability; that is, it estimates a blocking probability higher than the actual. This is substantiated by simulation, the results of which are compared to Eq.(7) in figures (12) and (13). Lee's method of Eq. (7) will be used in the following performance analysis.

Figure 12. Blocking probability comparisons between the simulation and

Lee's method, for the single star topology in Figure 6.

Figure 13. Blocking probability comparisons between the simulation and Lee's method, for the double topology in Figure 10.

SOLID LINE: SIMULATED ON A DOUBLE STAR OF 8 BY 8 EACH DOTTED LINE: ANALYSIS BY C.Y. LEE [BSTJ 1955, PP 1287-1315]

#### 2.4.3. Compression Delay

The compression delay in TSS is equal to the duration of one frame. Since there are K time slots in each frame, the compression delay is

$$D = Kt_{slot}.$$

(8)

Considering now one circuit corresponding to one time slot, the following relation insures that the input bit rate can be accommodated within the time slot time less the guard time,

$$R t_{D}^{MAX} \ge B D = R t_{D} \tag{9}$$

where R is the bandwidth on a link, B is the bit rate for one circuit,  $t_D$  is the time interval for information transmission. and D is the duration of a frame from Eq.(8). The left side of Eq.(9) equals the maximum available number of bits for transmission during one time slot, while the right side represents the number of

bits accepted for one circuit from the data terminal. Equality occurs when the whole  $t_{D}^{MAX}$  is used for transmission.

By simple manipulation of Eqs. (1,9),

$$t_{slot} = \frac{t_{idle} + \Delta t_D}{1 - \frac{KB}{R}}$$

(10)

where  $\Delta t_D = t_D^{MAX} - t_D$  and adding Eq. (8),

$$D = K \frac{t_{idle} + \Delta t_D}{1 - \frac{KB}{R}}.$$

(11)

Since larger K results in a larger number of circuits available at a given blocking probability (Eq. (7)), we see the promised tradeoff between throughput and delay, where as expected the delay increases as throughput increases. In addition, KB is the total available throughput passing through any cross-point and is limited by the link bandwidth R; as a result, K can not be arbitrary large and is bounded by  $\frac{R}{B}$ . Also,  $\Delta t_D$  can not be reduced to 0 in practice, since some preamble bits are necessary for the bit timing recovery at the receiver. But it is much smaller than  $t_{idle}$  and can be neglected.

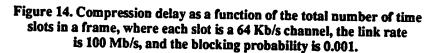

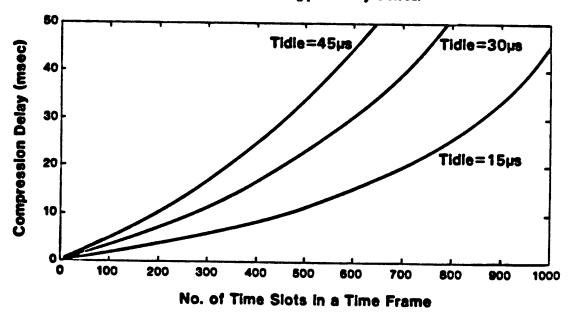

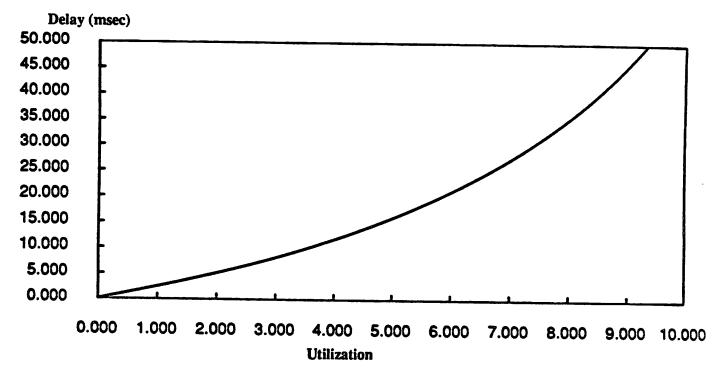

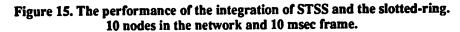

Figure 15. Same analysis as in Figure 14, but each slot is 16 Kb/s Channel.

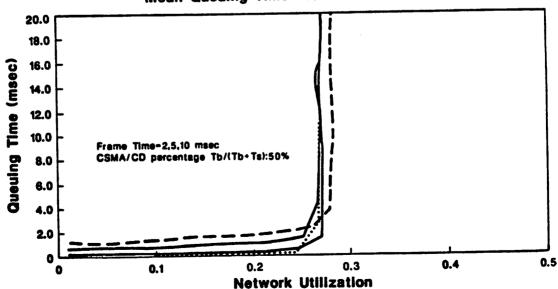

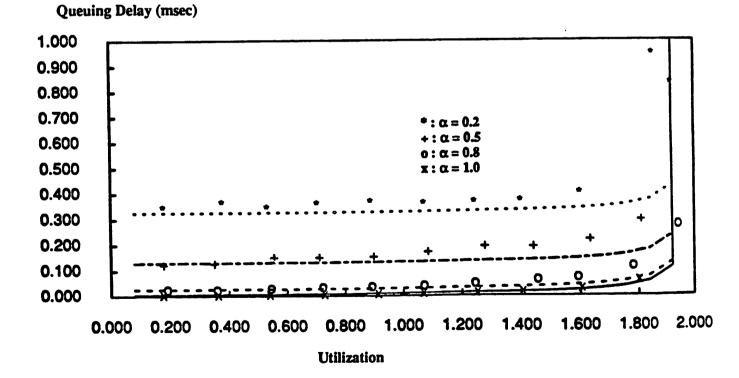

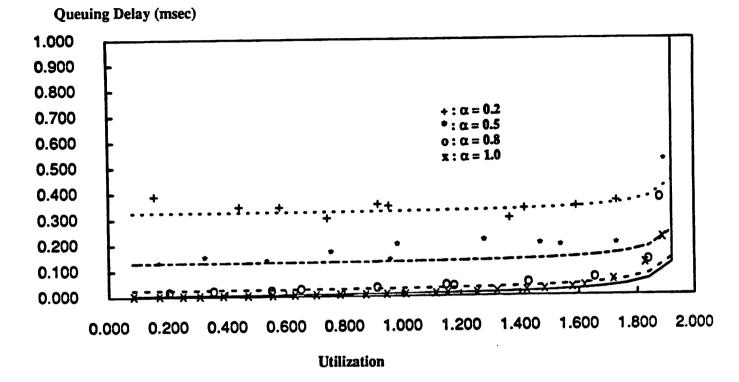

Figures (14,15) give numerical results describing these relations for B = 64 Kb/s and 16 Kb/s respectively. We expect that R = 200 Mb/s can be achieved using a low-cost CMOS technology for the switches [2,5], but to be conservative we use R = 100 Mb/s. In the figures,  $\Delta t_D$  is assumed 0 in Eq. (11). If a propagation velocity of  $2 \cdot 10^8 m/sec$  is assumed in the optical fiber and the worst case in Eq. (5) is assumed, then the *t<sub>idle</sub>* to network size ratio is 15 µsec/Km in figures (14,15). The three cases shown correspond, therefore, to a maximum network dimension of 1,2, and 3 km.

# 2.4.4. Network Utilization vs. Compression Delay

The previous results can be used to obtain the relationship between network utilization and compression delay if we combine the results for compression delay and blocking probability. In the following, assume that the full  $t_{D}^{MAX}$  in each time slot is used in transmission. For this case, by Eqs. (1), (2), and (10), we have:

$$\eta_{stor} = \frac{KB}{R} \tag{12}$$

Furthermore, total network utilization can be easily expressed in terms of A, the average offered traffic in Erlangs. Because there are A circuits on average, by definition of network utilization, we have:

$$\eta_{network} = \frac{AB}{R}.$$

$$= \frac{A}{K} \cdot \eta_{slot}$$

(13)

By Eq. (7), we have:

$$\eta_{network} \approx N_2 \left\{ 1 - (1 - P_{bk}^{\frac{1}{2}})^{1/2} \right\} \eta_{elot}$$

(14)

Eq. (14) gives very important physical insight into TSS networks. Total network utilization is naturally increased by the factor  $N_2$  due to the multiple transmission links, while it is subject to two degrading factors. One is the effect of the guard time expressed by  $\eta_{stot}$ , and the other is the blocking probability limitation in the brackets.

By combining Eq.(11) with Eqs. (12,14), an expression relating D and  $\eta_{network}$  can be obtained. Instead of writing this complicated expression, by observing:

$$\alpha = 1 - (1 - P_{bk}^{\frac{1}{k}})^{1/2}$$

is a weak function of K, simple manipulation of Eqs. (7,11,13) gives

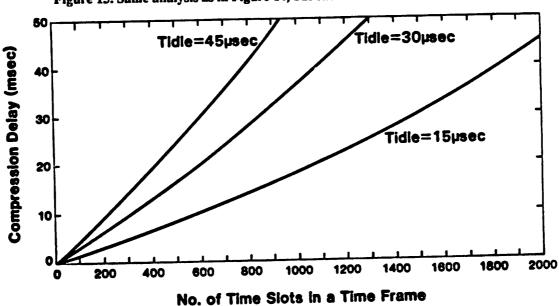

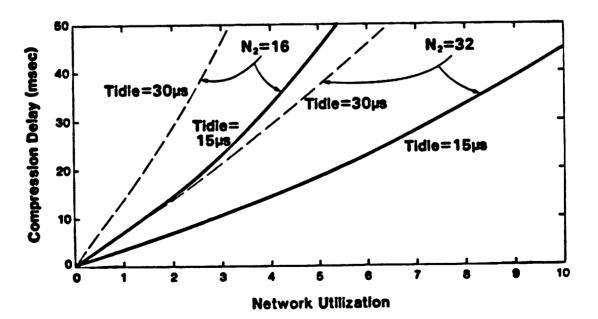

Figure 16. Trade-offs between compression delay and the network utilization, where each slot is 64 Kb/s, link rate is 100 Mb/s, and blocking probability is 0.001. Solid lines are for a network of 1 Km (15 µsec idle time), and dash lines correspond to 2 Km.

$$D = \frac{Rt_{idle}}{B} \frac{\frac{\eta_{network}}{N_2 \alpha}}{1 - \frac{\eta_{network}}{N_2 \alpha}}$$

(15)

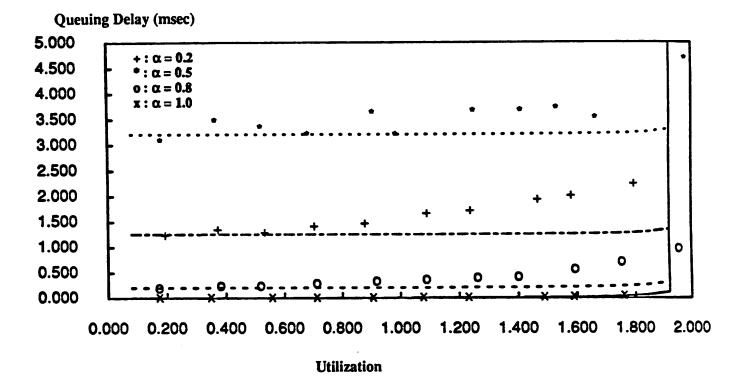

This expression is very similar to those in multiple access protocols, even though the underlying reasons are quite different. Figures (16,17) show that  $\eta_{network} > 1$  can be achieved at a reasonable delay; that is, the total utilization can be much larger than the bandwidth of one link that would be characteristic of a multiaccess protocol. For example, at a 50 msec compression delay (which would be acceptable for a voice network), 100Mb/s network bandwidth, 10<sup>-3</sup> blocking probability, and a 16 by 16 switch in the central star of a double star network,  $\eta_{network} \approx 10$  is easily achieved for 64 Kbps/slot. This corresponds to a 1000 Mbs total network throughput in comparison to a 100 Mbs for each link. Thus, for these parameters the increased capacity from multiple links dominates over the diminished capacity due to guard times and blocking probability.

The effect of the link bandwidth on the delay-utilization characteristic can be also observed from Eq. (15). With a given network utilization and fixed idle time, the delay is proportional to the link bandwidth. Intuitively, to keep the same utilization, the time interval in each time slot for transmission must be same,

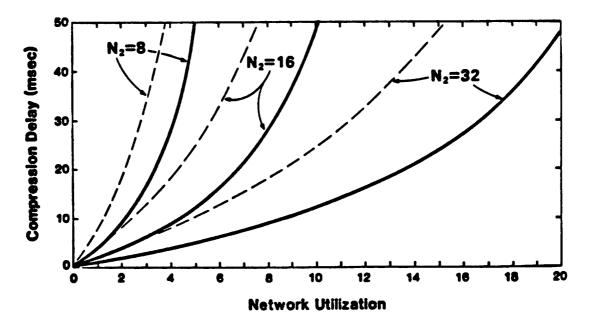

Figure 17. Same analysis as in Figure 16, but 16 Kb/s channel per slot is assumed.

and the total bits transmitted in each slot is proportional to the link bandwidth, but the compression delay will also linearly increase. From Eq. (15), the effect of increasing link bandwidth is the same as decreasing the idle time by the same proportion. As a result, smaller idle time (smaller network) can be used to counterbalance the increase in delay because of increase in link bandwidth.

### 2.5. Heterogeneous TSS

In section 4, the homogeneous case where all circuits had the same bandwidth was considered. However, in practice we seek to integrate data, voice and video traffic within TSS.

First, we can have the following assignment:

- 1. Each time slot is equivalent to a 16 Kb/s channel.

- 2. Voice traffic uses a fixed 64 Kb/s bit rate, and each channel is assigned 4 time slots.

- 3. Interactive data traffic has a fixed rate, e.g. 16 Kb/s, 32 Kb/s, etc.; a multiple number of slots are assigned depending on its bit rate; that is, one slot for 16 Kb/s, and so on.

- 4. Video has no standard rate and is in the order of 20 Mb/s to 200 Mb/s. For simplicity, a whole frame circuit will be assigned for this large bandwidth traffic. Because the circuit switches are distributed and provide multiple circuits, this assignment will not significantly affect other traffic transmission.

- 5 Fixed length data such as file transfer can be assigned a certain number of slots based on its length. This will be explained in more detail in the remaining section.

Several characteristics of this approach should be mentioned:

- If it can be arranged for these slots to be contiguous, then there is a potential saving in guard time. In the extreme case of a high bandwidth full-motion video signal, one entire link or most of a link could be dedicated to one circuit. The overall utilization would then increase considerably above that estimated in the previous section.

- 2. For the heterogeneous case, the compression delay remains equal to one frame interval.

- 3. When the blocking probability for one circuit is small, say 10<sup>-3</sup>, the blocking probability for a higher rate circuit made up of lower rate circuits is approximately multiplied by the number of time slots assigned in a frame.

- 4. For file transfer, we simply want the maximum bandwidth available to minimize the time to transfer the file. If there is only one file transfer request, and the file can be transmitted within one frame by available time slots, the number of time slots assigned can be variable depending on the size of the file, and the blocking probability is not a meaningful concept. However, if there is more than one request for file transfer, or the file transfer cannot be finished in one frame, the maximum use of available bandwidth will possibly block others' requests. Thus, we should be conservative in assigning bandwidth for file transfer.

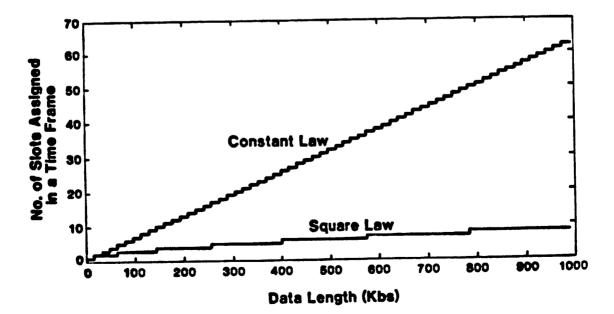

For the last point relating to file transfer, we can suggest two approaches to assigning bandwidth. The first rule, the constant law,

$$n = \left\lceil \frac{L_D}{t_0 16Kb/s} \right\rceil \tag{16}$$

Figure 18. Number of time slots assigned as a function of the file length for file transfer.

assigns a bandwidth proportional to the file length (resulting in a constant file transfer time). The second, the square root law, assigns a smaller bandwidth,

$$\boldsymbol{n} = \left[ \left( \frac{L_D}{L_0} \right)^{\nu_a} \frac{L_0}{\iota_0 16Kb/s} \right], \tag{17}$$

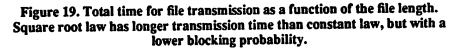

where *n* is the number of time slots assigned which will be the same for each succeeding frames until the file is exhausted,  $L_D$  is the data size of the file,  $t_0$  is a time parameter that is equal to the total transmission delay for the constant law, and  $L_0$  is a length parameter. Transmission delay is equal to  $mt_0$  when  $L_D = m^2 L_0$  at square root law, and m is an integer. The resulting time for file transmission is,

Transmission Delay

$$\approx \begin{cases} t_0, \text{ constant law} \\ (\frac{L_D}{L_0})^{\nu_0} t_0, \text{ square root law} \end{cases}$$

(18)

Numerical results are shown in figures (18,19). The constant law promises smaller transmission delay (Eq. 18) at the expense of larger blocking probability for other requests (by assigning more free time slots). The square root law has less effect on other users.

The performance and hardware cost are attractive for voice and video traffic in this heterogeneous TSS since they are well suited to circuit switching. The same can be said for file transfer activity as long as the file length is long enough that the circuit connection time is insignificant. For interactive data traffic, however, there are significant disadvantages:

- 1. For very small data packets, the overhead in establishing a circuit is too large.

- 2. Interactive data traffic at a fixed rate is idle most of the time. The slots reserved are wasted during idle periods. This reduces the effective network utilization below our earlier estimates.

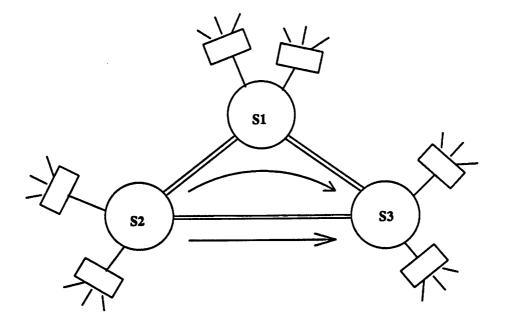

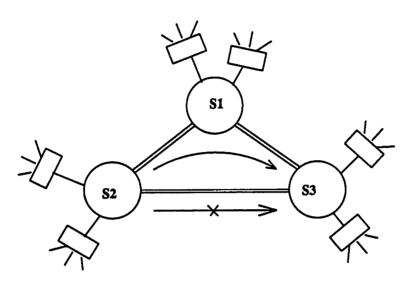

If these disadvantages are dominant, as in a network where interactive data represents a significant fraction of the total offered traffic, it is possible to overlay packet data networks on top of TSS. For example, we can establish a packet network operating at lower speeds where the implementation costs are reasonable by establishing semi-permanent circuit links through the TSS network. For example, a token ring can easily be established. TSS is very flexible in its ability to reconfigure and reassign capacity to various services such as packet data networks on a demand basis. It is also possible to combine TSS with a CSMA/CD data network in a portion of the frame [6,7]. These extensions of TSS to combine CSMA/CD or slotted-ring will be considered in Chapters 3 and 4. In fact, the presence of the active switches considerably simplifies the detection of collisions in such a network. This extension of TSS will be explained in chapter 3. We should emphasize again that due to the asynchronous nature of the switches, overlaid data networks can also use arbitrary bit rates as long as they adhere to the maximum rate imposed by the switch.

### 2.6. Conclusion

In this chapter, we describe a new protocol for local-area networks: time slot switching or TSS. Since electronics is the factor limiting the bandwidth of practical fiber optical networks, TSS is very attractive by minimizing electronics in switching nodes. It uses circuit switching, which appears more appropriate for very high speeds and is quite compatible with voice and video traffic, but does not preclude overlaid packet networks for interactive data traffic operating at more moderate speeds. The network is compatible with fiber optics technology, since it utilizes only point-to-point links at speeds that are quite modest by fiber standards. It is quite compatible with integrated traffic, and can easily provide different effective speeds for different services. Its greatest strength is the ability to incrementally add capacity and the ability to reach quite impressive total throughputs without exotic technologies. Its greatest weakness is its limitation in geographical size to the order of one to two kilometers. This latter limitation can be overcome by the standard technique of adding gateways with buffering at the expense of additional delay.

TSS can be described as a wideband distributed PBX, and is perhaps a closer relative to today's PBX products than it is to traditional LAN approaches. Since technologies springing from both LAN and PBX products show promise in providing an integrated solution to local communications, it will be interesting to see which approach becomes dominant.

# Appendix A. Blocking Probability Analysis: Single Star

In this appendix, the blocking probability is estimated based on Lee's method [3] for a single star network as shown in figure (6).

Assume that p, the probability of any one time slot on any one link being already used, is known, and that the events of different time slots on the same link or different links being used are independent. Now, suppose we want to form a new connection between two TCMs in any particular time slot. The probability of success is  $(1-p)^2$ . Therefore the blocking probability for the connection in any particular time slots is  $1 - (1-p)^2$ . Because there are K time slots can be chosen for the connection, the probability that they are all blocked is

$$P_{bk} = \left\{ 1 - (1 - p)^2 \right\}^K$$

(A.1)

It remains to determine the probability p. Assume there are A time slots in use on average, then the active probability for user terminals is  $p_0 = A / NM$ , since there are total NM users. Assuming the traffic is uniformly distributed in all time slots and there are N user terminals in each TCM,

$$p = p_0 \frac{N}{K} = \frac{A}{MK} \tag{A.2}$$

## Appendix B. Blocking Analysis: Double Star

The blocking probability for the double star in figure (10) is estimated in this appendix. It is assumed here that a circuit connection follows the same hierarchy principle as in telephone networks. That is, if a circuit can be locally connected through the local switching star, no connection will be required in the central switching star. Therefore, a blocking probability is larger if a circuit needs to go through the central switching star. To obtain a conservative estimate, this latter probability will be used.

By Lee's method and using the same technique as in Appendix A, the blocking probability is

$$P_{bk} = \left\{ 1 - (1 - p_1)^2 (1 - p_2)^2 \right\}^{\kappa}$$

(B.1)

Chapter 2: Time Slot Switching

where

$$p_1 = \frac{A}{K(N_1+1)N_2}$$

is the probability of use for the time slots around local switches, and

$$p_2 = \frac{A}{KN_2}$$

is that probability for the time slots around central switches.

Since  $p_1$  is in general much smaller than  $p_2$ , the factor  $(1 - p_1)^2$  in Eq. (B.1) can be neglected. Network throughput may therefore be expressed as:

$$A = KN_{2} \left\{ 1 - (1 - P_{bk}^{\frac{1}{k}})^{1/2} \right\}$$

(B.2)

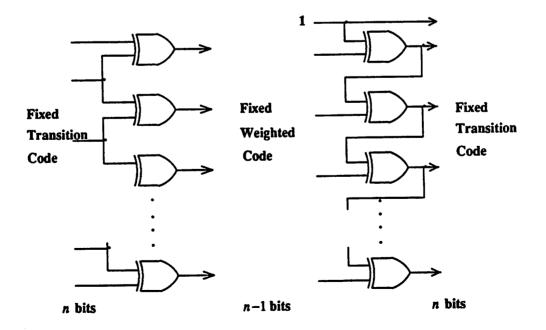

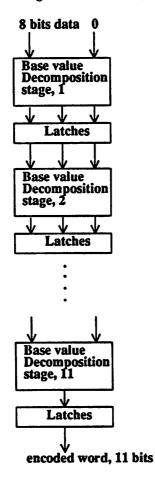

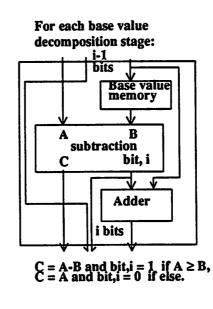

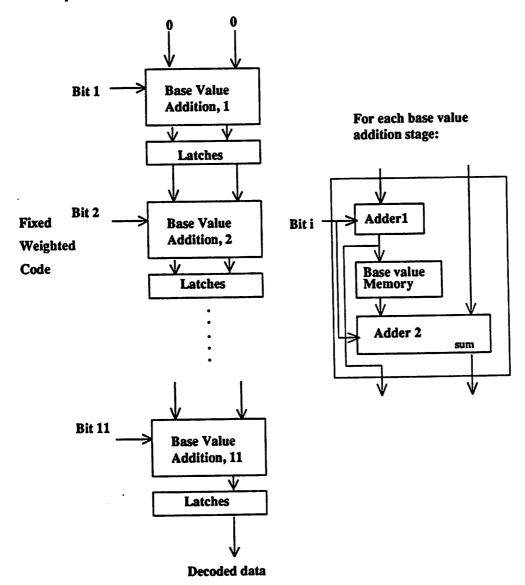

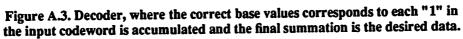

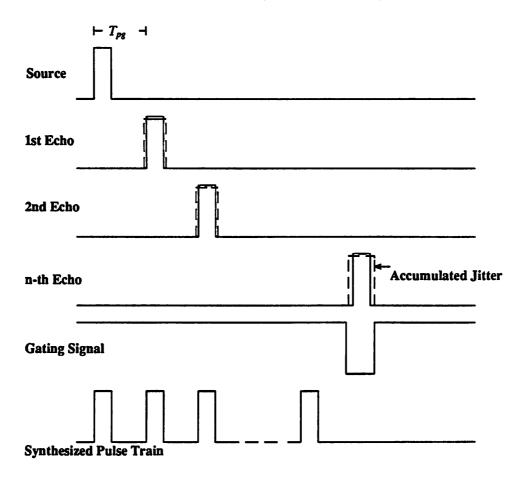

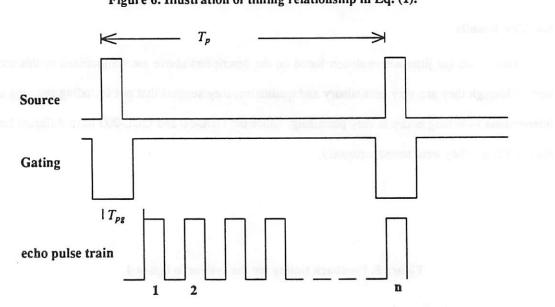

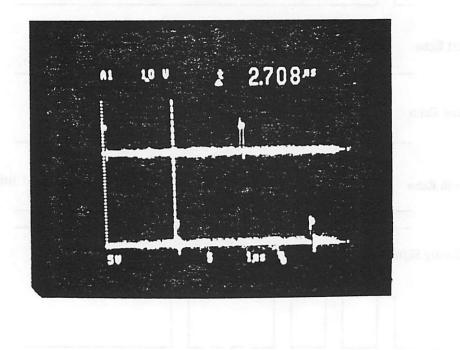

### **REFERENCE:**