# Mocha Chip: A Graphical Programming System for IC Module Assembly

Robert Nelson Mayo

December 14, 1987

Computer Science Division (EECS)

University of California

Berkeley, California 94720

Submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Computer Science.

## Mocha Chip: A Graphical Programming System for IC Module Assembly

Copyright © 1987 by Robert N. Mayo

All rights reserved.

## Mocha Chip: A Graphical Programming System for IC Module Assembly

#### Robert Nelson Mayo

#### **ABSTRACT**

Mocha Chip is a system for designing module generators. There are two unique aspects to this system: diagrams are used to represent the structure of a module generator, and assembly primitives ensure that the generated layout obeys geometrical design rules and is properly connected.

Module generators are created using hierarchical diagrams rather than programs. The idea is to draw diagrams describing the topology of a class of modules, and to parameterize the diagrams to indicate how the individual modules differ. Parameterization is done using Lisp and special built-in cells that provide graphical representations of iteration and conditional selection. The diagrams may be considered to be a graphical programming language tailored to IC design. Diagrams can invoke either other diagrams or cells of mask geometry drawn by the user.

Describing module generators with graphics rather than text adds flexibility to the module generator. Textual languages, such as programming languages, tend to obscure the geometrical relationships. Mocha Chip separates out the module structure and represents it graphically, resulting in module generators that are easier to design and modify. Openness and ease of modification are important since users need to tailor module generators to produce specialized modules.

Layout for a module is produced using two pairwise assembly operators that take pieces of layout and combine them to form a larger pieces. The tile-packing operator aligns user-specified rectangles. The river-route-space operator uses two phases. The routing phase connects ports that do not line up exactly, and the cell spacing phase places the cells and routing as close together as rules allow.

The assembly process guarantees that no geometrical design rules will be violated and that the proper connections will be made. In other tile-based module generation systems, the user must manually check to make sure that all possible combinations of tiles will fit together properly. This is impractical for module generators that have a large number of tiles and options. The connection operator automatically ensures that the proper connections will be made and that no geometrical design rules will be violated.

#### Acknowledgments

Many thanks go to John Ousterhout, whose drive and ambition serves as a model for all. I've enjoyed working with him immensely.

I'd like to acknowledge a number of other colleagues for their help and technical insights. All the members of the Magic team deserve special thanks: Gordon Hamachi, Walter Scott, George Taylor, and of course John Ousterhout. Randy Katz and Charles Woodson, as members of my qualifying exam committee, reviewed my work at various stages and provided useful guidance. The previous tool builders at Berkeley made life much easier for me, and helped point me in the right direction. The past and present occupants of 508-7 Evans Hall deserve a special round of applause for the interesting discussions: Michael Arnold, Gordon Hamachi, John Hartman, Paul Heckbert, Mike Hohmeyer, Barry Roitblat, Ken Shirriff, George Taylor, Steve Viavant, and Tara Weber. There are many other people in the EECS department at Berkeley that made it a great place. I'd like to thank them all.

Finally, I would like to express my gratitude to several people for their personal support and encouragement. Many thanks go to my parents for their guidance, and to my brothers and sisters. Thanks are also due to Gordon Hamachi, Herb Ko, and Paula Peters for their lasting friendship.

This research was funded, in part, by the Defense Advanced Research Projects Agency under contracts N00039-83-C-0107 and N00039-87-C-0182. I'd like to thank IBM Corporation for their Graduate Fellowship for two of my years at Berkeley.

### **Table of Contents**

| CHAPTER | 1 Introduction                   | 1  |

|---------|----------------------------------|----|

| 1.1     | IC DESIGN                        | 1  |

| 1.2     | MOCHA CHIP OVERVIEW              | 3  |

| 1.3     | COMPONENTS OF A MODULE GENERATOR | 5  |

| 1.4     | THESIS ORGANIZATION              | 8  |

| 1.5     | REFERENCES                       | 10 |

| CHAPTER | 2 Generator Specification        | 11 |

| 2.1     | INTRODUCTION                     | 11 |

| 2.2     | TILES                            | 12 |

| 2.3     | PARAMETERIZATION OF TILES        | 15 |

| 2.4     | ASSEMBLY DIAGRAMS                | 17 |

| 2.5     | PARAMETERIZATION OF DIAGRAMS     | 22 |

| 2.6     | SUMMARY                          | 28 |

| 2.7     | REFERENCES                       | 29 |

| СНАРТЕ  | R 3 Related Work                 | 30 |

| 3.1     | INTRODUCTION                     | 30 |

| 3.2     | PROGRAMMING                      | 31 |

| 3 3     | GRAPHICAL SYSTEMS                | 34 |

|      | 3.4  | TILING                         | 36 |

|------|------|--------------------------------|----|

|      | 3.5  | REGULAR-STRUCTURE GENERATOR    | 38 |

|      | 3.6  | ARRAY-STRUCTURE TEMPLATES      | 41 |

|      | 3.7  | DISCUSSION                     | 42 |

|      | 3.8  | REFERENCES                     | 44 |

| СНАР | PTER | 4 System Overview              | 47 |

|      | 4.1  | SYSTEM STRUCTURE               | 47 |

|      | 4.2  | MOCHA DRAW                     | 51 |

|      | 4.3  | COMMUNICATION WITH LISP        | 54 |

|      | 4.4  | MOCHA EVAL                     | 55 |

|      | 4.5  | MOCHA ASSEM                    | 57 |

|      | 4.6  | SUMMARY                        | 58 |

|      | 4.7  | REFERENCES                     | 59 |

| CHAI | PTER | 5 Pairwise Assembly            | 60 |

|      | 5.1  | INTRODUCTION                   | 60 |

|      | 5.2  | THE TILE PACKING OPERATOR      | 62 |

|      | 5.3  | THE RIVER-ROUTE-SPACE OPERATOR | 63 |

|      | 5.4  | MAGIC'S DESIGN RULES           | 64 |

|      | 5.5  | RIVER ROUTER                   | 69 |

|      | 5.6  | SPACER                         | 70 |

|      | 5.7  | CONCLUSIONS                    | 73 |

|      | 5.8  | REFERENCES                     | 73 |

| CHAP | TER | 6 An Example PLA Generator | 75             |

|------|-----|----------------------------|----------------|

| ,    | 6.1 | INTRODUCTION               | 75             |

|      | 6.2 | COMPONENTS OF MCPLA        | 80             |

|      | 6.3 | HOW MCPLA WORKS            | 81             |

|      | 6.4 | MPLA                       | 92             |

|      | 6.5 | DISCUSSION AND LIMITATIONS | 94             |

|      | 6.6 | REFERENCES                 | 97             |

| СНАР | TER | 7 Future Work              | 98             |

|      | 7.1 | INTRODUCTION               | 98             |

|      | 7.2 | GENERATOR COMPILATION      | <del>9</del> 9 |

|      | 7.3 | PITCH-MATCHING             | 99             |

|      | 7.4 | GENERAL ROUTING            | 100            |

|      | 7.5 | PARAMETERIZED NETLISTS     | 101            |

|      | 7.6 | FLEXIBLE PARAMETER PASSING | 103            |

|      | 7.7 | SUMMARY                    | 104            |

|      | 7.8 | REFERENCES                 | 105            |

| СНАР | TER | 8 Pitch Matching           | 106            |

|      | 8.1 | INTRODUCTION               | 106            |

|      | 8.2 | STRETCH GRAPHS             | 107            |

|      | 8.3 | SOLVING THE GRAPHS         | 112            |

|      | 8.4 | DISCUSSION                 | 118            |

|      | 8.5 | REFERENCES                 | 119            |

| CHAPTER 9 Discussion                            | 120   |

|-------------------------------------------------|-------|

| 9.1 DISCUSSION                                  | 120   |

| APPENDIX A Manual Pages                         | 123   |

| A.1 ARRAY BUILT-IN CELL                         | 124   |

| A.2 CASE BUILT-IN CELL                          | 126   |

| A.3 MCPLA PLA GENERATOR                         | 128   |

| A.4 MOCHA CHIP                                  | 131   |

| APPENDIX B Tutorials                            | 140   |

| B.1 USING A MOCHA CHIP MODULE GENERATOR         | 141   |

| B.1.1 INTRODUCTION                              | 141   |

| B.1.2 HOW TO GET HELP AND REPORT PROBLEMS       | 142   |

| B.1.3 STARTING UP MOCHA CHIP                    | 142   |

| B.1.4 A PLA EXAMPLE                             | 143   |

| B.1.5 CONCLUDING REMARKS                        | 147   |

| B.2 DESIGNING MODULE GENERATORS WITH MOCHA CHIP | 148   |

| B.2.1 INTRODUCTION                              | 148   |

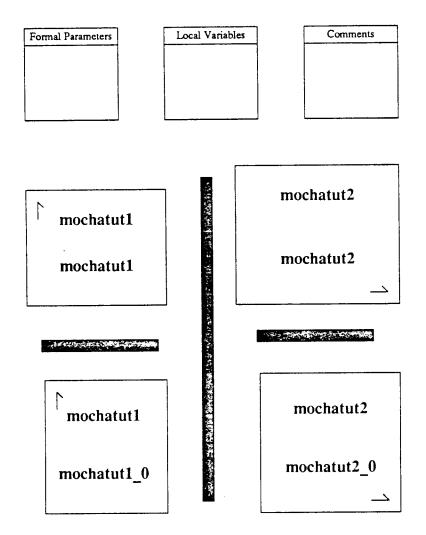

| B.2.2 AN EXAMPLE DIAGRAM                        | 149   |

| B.2.3 CREATING MOCHA CHIP DIAGRAMS              | 152   |

| B.2.4 THE ARRAY AND CASE CELLS                  | . 155 |

| B.2.5 ADDING PARAMETERIZATION                   | . 157 |

| B.2.6 SUMMARY                                   | . 159 |

1

## **INTRODUCTION**

#### 1.1. IC DESIGN

Integrated circuits (*ICs*) are electronic circuits etched onto silicon wafers using patterns of material on several different layers, called *mask layers* because a photographic mask is used to manufacture them. The design of the patterns is called *layout design*, and is usually a time-consuming manual task. The layout designer implements the circuit by choosing patterns for the mask layers, following *electrical design rules* that ensure the proper functioning of the circuit. In addition to implementing an electrically correct circuit, the pattern of mask layers must obey another set of rules, called

geometrical design rules, that ensure that the resulting patterns can be reliably fabricated.

Geometrical design rules specify which patterns can be reliably fabricated, and which patterns cannot be. A typical rule specifies the minimum spacing between pieces of material, to prevent accidental shorts, or the minimum width of a wire, to prevent accidental gaps. Additional rules describe the proper construction of transistors and contacts, in terms of required overlaps and separations.

Layout designers often employ programs called *module generators* to help them design their ICs. Module generators generate standard building blocks from a set of parameters, freeing the designer to concentrate on the unique aspects of the design. Like layout design, the design of a new module generator is also a time-consuming manual task.

Module generators consist of two phases: a phase called behavioral processing that maps the behavioral specification into a structural description showing the approximate position of components, and a phase called layout generation that maps the structural description into a set of mask patterns. Both phases have traditionally been implemented with textual programs. For the latter phase, this is an error-prone method, since textual languages are not well-suited to the specification of topological information. Mocha Chip addresses this phase using a more intuitive scheme: an extensible graphical programming language to specify topology and special operators to assemble layout using the geometrical design rules.

#### 1.2. MOCHA CHIP OVERVIEW

There are two key ideas of this research: a graphical specification language for module generators, and interconnection operators for creating larger structures out of smaller components. This combination allows the structure of the module to be specified graphically, and ensures that the resulting module will obey geometrical design rules. The approach solves many of the problems associated with the layout-generation phase of a module generator.

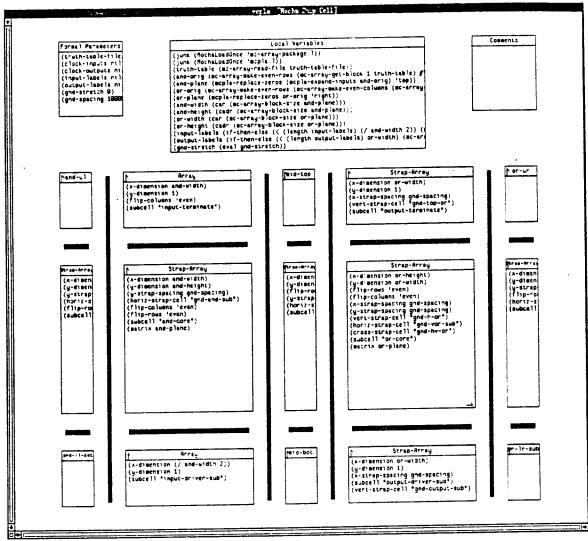

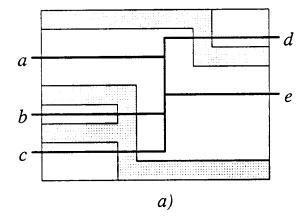

Mocha Chip encourages a style where module generators are designed with diagrams rather than programs (Figure 1.1). Each diagram shows the organization of a class of modules, and parameters specify the differences between individual modules. The parameterization is done using Lisp and special built-in cells that provide two-dimensional analogues of iteration and conditional selection. The diagrams constitute a graphical programming language tailored to IC design.

By separating out the module structure and representing it graphically, module generators are easier to design and modify. This is important since module generators are currently designed by programmers rather than the IC designers, often resulting in generators that don't produce exactly what the IC designer needs in a given situation. With Mocha Chip, IC designers can tailor module generators to fit their particular needs, and can also design their own simple generators from scratch.

In addition to diagrams, Mocha Chip provides pairwise assembly operators that create layout by pairing together two smaller pieces of layout, such as basic tiles, to form larger pieces. The pairing is done in a way that ensures that no geometrical

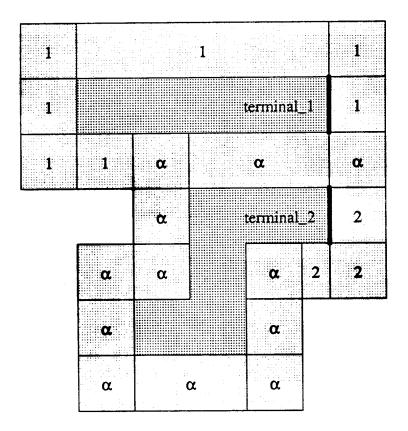

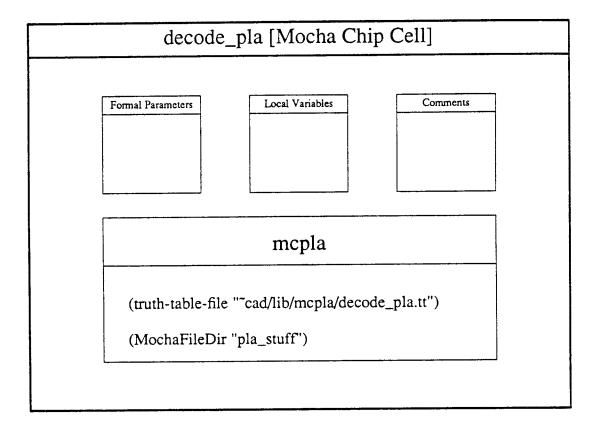

Figure 1.1. Mocha Chip's diagrams represent module generators. This figure shows the top-level diagram for a PLA generator. The generator consists of two core arrays, surrounded by arrays of precharge transistors and input and output drivers. The three blocks at the top of the diagram describe the parameters expected by the generator and the computations done on those parameters.

design rules are violated. This ensures that all modules created will obey the geometrical rules, and frees the module generator's designer from those considerations. The designer is still free to hand-tune cells so that particular ones fit together tightly, and the system will ensure that all combinations of cells will fit together without geometrical design rule violations. Ensuring the design-rule correctness of all modules generated was, in the past, a very difficult task. Mocha Chip eliminates this time-

consuming phase, making it easier for module generators to be designed by IC designers.

#### 1.3. COMPONENTS OF A MODULE GENERATOR

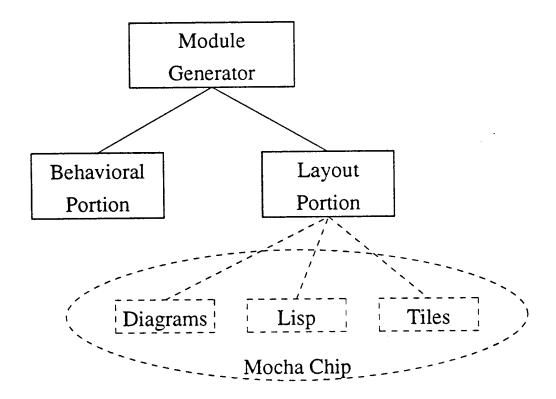

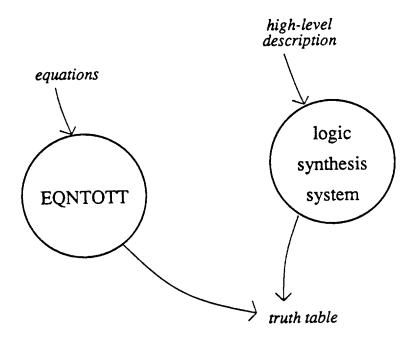

Module generators generally consist of two parts (Figure 1.2): a part that maps a specification of the module's behavior into structural information (called *behavioral processing*), and a part that maps the structural information into actual mask geometries (called *layout generation*). The first part is problem-specific and involves manipulations of symbolic, algebraic information rather than spatial information. It is best handled by a general-purpose programming language. The second part, however, involves spatial operations that are common to all module generators. It is in this area that Mocha Chip seeks to improve the design process. Traditional techniques use a programming language for this part, while Mocha Chip makes use of graphics.

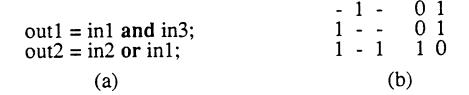

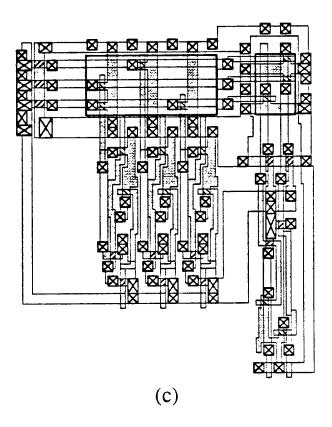

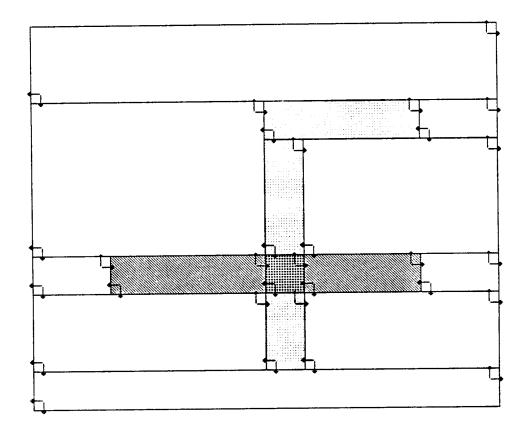

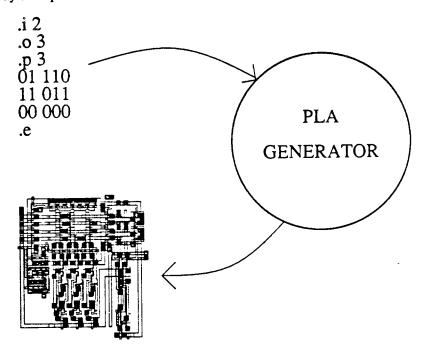

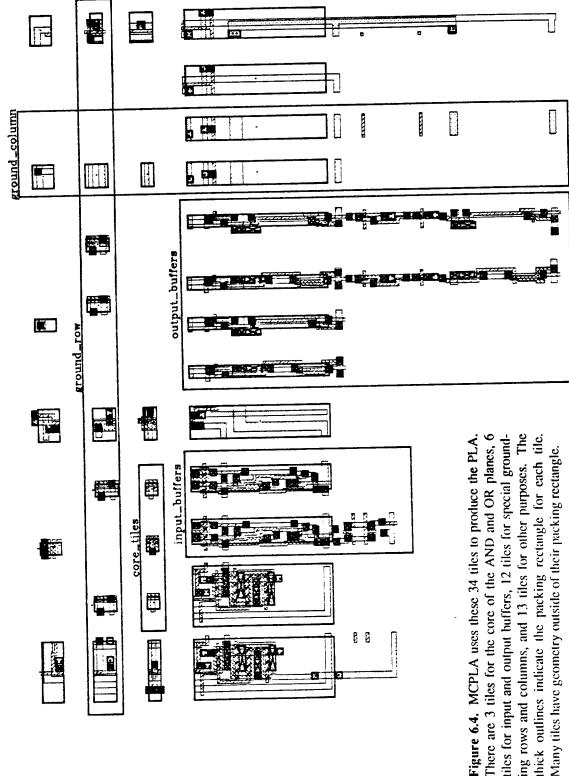

An example will be used to illustrate the distinction between the two parts. The example chosen is a Programmable Logic Array (PLA) generator. A PLA is a combinatorial circuit that takes a set of boolean input variables and produces as output a function of those variables. The input to a PLA generator is a set of equations (Figure 1.3a) which specify the behavior of the PLA. The output of the generator is layout (Figure 1.3c) that implements the function using a PLA.

The behavioral-processing part of the PLA generator takes the input equations and decides on a structure for the module. PLAs implement a two-level *and-or* structure, so the generator takes the equations and produces such a structure. The details of

Figure 1.2. A module generator typically is composed of two parts: one that creates a structural description from a specification of the desired behavior, and one that creates mask layout from the structural description. Mocha Chip makes the design of the second part easier, breaking it down into three parts: diagrams, which represent the structure of a class of modules; Lisp code, which specifies how the individual instances differ; and tiles of mask layout, which form the basic building blocks of the module.

this structure are not important for this discussion; the important idea is that the new structure is close to the structure of the final layout. For example, if we represent the structure as a table, as in Figure 1.3b, each position in the table might correspond to a particular cell or combination of cells in the final layout. The final layout will probably also contain many cells of a housekeeping nature — ones that aren't a direct consequence of the input specification but are rather part of the electrical design of the structure. This mapping of behavior to structure is problem-specific, and is best handled with a general-purpose programming language.

Figure 1.3. The equations in Figure 1.3a specify the desired behavior, and are translated into the table shown in Figure 1.3b. The table represents the structure of a module, and is a close match to the actual layout in Figure 1.3c. The layout consists of two small core areas (outlined by thick lines) which are programmed according to the table, and the surrounding buffers, precharge transistors, and power busses, which are provided automatically by the generator.

After deciding on the structure, the module generator produces layout. In the past, the popular methods of producing layout from a structural description were to use a general-purpose programming language or to use *tiles* (small cells) of mask layout combined with a programming language. In Mocha Chip, the layout-generation phase is implemented with three items: tiles of mask layout that form the basic components

to be assembled, diagrams showing the structure of the modules to be generated, and Lisp code which parameterizes the diagrams.

This method eliminates many of the problems of past approaches. The tiles of mask layout are the basic building blocks of the module, and are drawn graphically by the module generator designer. The pairwise assembly operators built into the system automate much of the error-prone task of assembling the tiles. The diagrams, called assembly diagrams, specify graphically the overall structure of the class of modules to be generated, and are clearer and more visually expressive than textual programs. The diagrams are parameterized by Lisp code that specifies how the individual modules differ. Calls to arbitrary user-defined Lisp functions may be used, giving a convenient way to implement the behavioral-processing phase.

#### 1.4. THESIS ORGANIZATION

The next chapter describes the graphical language used by Mocha Chip and how it is evaluated, or executed, to produce an instantiated module. As mentioned previously, the graphical language makes modules generators easier to design and modify, and is Mocha Chip's main contribution.

Chapter 3 reviews previous module generator design techniques, discussing their pitfalls and how each new technique improves upon the previous techniques. I'll compare Mocha Chip with these techniques and show why it is an improvement.

Chapter 4 describes how the system is organized and implemented. The system is implemented in three parts: a front end built into the Magic[1] IC layout system, an

evaluation system written in Lisp[2], and a layout assembly system also built into Magic.

Chapter 5 describes the two interconnection operators and their implementation. The packing operator, a simple operator that does not guarantee design-rule correctness, is described, as is the river-route-space operator, which does guarantee design rule correctness. Both operators are useful in specific situations, but it appears that pitch-matching needs to be added in order for the river-route-space operator to have general applicability.

Chapter 6 reports on an example PLA generator built with Mocha Chip. This chapter demonstrates that non-trivial module generators can be built using the graphical constructs present in Mocha Chip. The chapter concludes by comparing the generator with similar generators built without Mocha Chip. The comparisons are based on the number of lines of code written by the generator designer, the number of diagrams drawn, and the number of tiles drawn.

Chapter 7 presents some ideas for future work. The ideas fall into three categories: usability improvements, to make the system faster and easier to use; interconnection operators, to increase the flexibility of the layout process; and language improvements, to extend the class of modules that can be easily described with Mocha Chip.

Chapter 8 presents some thoughts on the pitch-matching problem. Pitch-matching fits well into the Mocha Chip framework, since Mocha Chip was designed with it in mind. However, due to time limitations the pitch-matcher wasn't

implemented. This chapter gives some ideas on how it could be done.

Finally, Chapter 9 presents concluding remarks about the system, both advantages and disadvantages. The main disadvantages are that Mocha Chip runs more slowly than some other systems, and that pitch-matching seems to be required in many situations. The main advantage is that Mocha Chip's graphical diagrams work well for regular modules such as PLAs, ROMs, and datapaths, although they are less useful for more irregular modules. The example PLA generator compares favorably with existing PLA generators, proving that Mocha Chip's extensible graphical programming language is sufficient to specify real-world module generators. In addition, the idea of using assembly operators provides a means of assuring design-rule correctness; this is something that previous module generator systems have had problems with.

#### 1.5. REFERENCES

- J. K. Ousterhout, G. T. Hamachi, R. N. Mayo, W. S. Scott and G. S. Taylor, The Magic VLSI Layout System, *IEEE Design & Test of Computers*, February, 1985.

- 2. G. L. Steele, Jr., Common Lisp, The Language, Digital Press, 1984.

# 2 GENERATOR SPECIFICATION

#### 2.1. INTRODUCTION

A module generator is specified in Mocha Chip with three parts: tiles of layout that are the basic building blocks of the module, assembly diagrams that show the overall structure of the class of modules to be generated, and Lisp code that parameterizes the diagrams and tiles to indicate how the individual modules differ. This Lisp code may include calls to user-defined Lisp functions, giving a convenient way to incorporate the behavioral-processing part of the module generator.

This chapter will present each of the three parts in detail. It will begin with tiles, then present Lisp parameterization, and conclude with a discussion of assembly diagrams.

#### 2.2. TILES

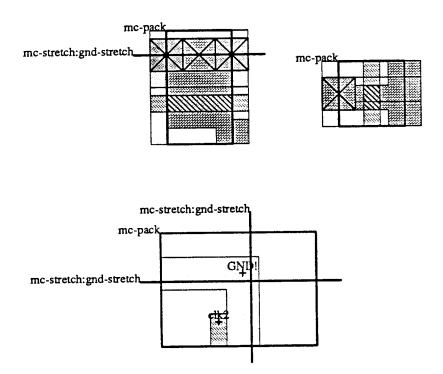

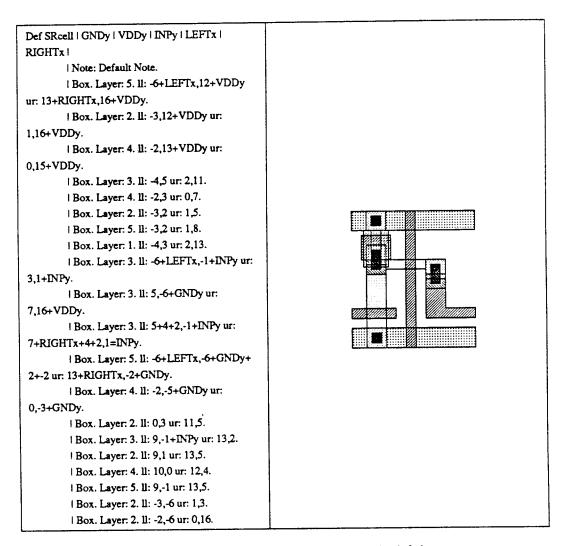

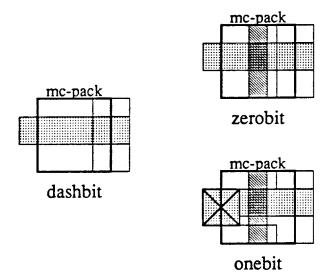

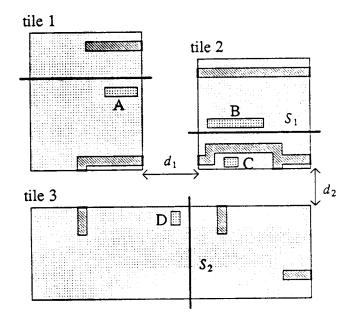

Figure 2.1. This figure shows three tiles from a PLA generator built with Mocha Chip. Tiles form the basic building blocks out of which modules are built. The tiles consist of mask layout as well as annotations to control the assembly process. Annotations are labels beginning with the characters "mc-".

Tiles (Figure 2.1) are small pieces of mask layout created using an interactive graphical editor, such as Magic[1]. The tiles form the building blocks that will be assembled according to the instructions contained in the assembly diagrams. A typical tile would contain structures such as an input buffer, a RAM cell, or a basic element in a shift register. Each tile is treated as an indivisible entity out of which larger

Figure 2.2. Labels in tiles can be parameterized. In this case, the tile references the parameter "var", which contains the string "input-A". The tile could be used with other values of "var", resulting in different labels for different instances of the tile.

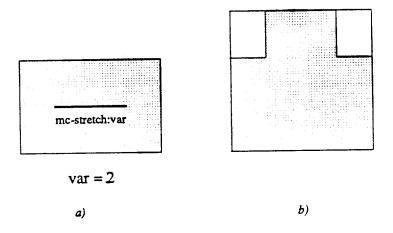

Figure 2.3. This example shows a horizontal stretch line that references the parameter "var", which has a value of 2. Part a shows the tile before the stretch, and part b shows the tile after the stretch. Horizontal lines cause material to move upwards, while vertical lines cause material to be moved to the right. In practice, a sequence of lines usually spans the width of the tile in order to avoid skewing.

structures are built. As a result, most tiles tend to be small. There is no built-in limitation, however, as to the size of tiles.

Three types of annotations are permitted in tiles: packing rectangles, parameterized labels, and parameterized stretch lines. *Packing rectangles* are user-specified boxes used by one of the pairwise assembly operators, as will be discussed later. They take the form of a rectangular label denoted "mc-pack" (Figure 2.1). *Parameterized*

Chapter 2

labels are labels of the form "mc-label:text". The text after the colon names a parameter that contains the text to be used as the label (Figure 2.2). Tiles can be invoked with different values for this parameter, resulting in several different versions of the same tile, each containing a different label. One example of how this can be used is to label the inputs to a structure, where each input consists of the same tile but the labels on the input terminals differ.

Figure 2.4. Stretch lines normally extend across the width and height of the tile, in order to avoid dislocations. In this example, three stretch lines are used to increase the width of three segments of a wire.

Parameterized *stretch lines* allow tiles to be stretched. They are used to widen power and ground lines and contacts in order to follow electrical design rules, and to resize transistors in order to adjust the performance of the circuit. Parameterized stretch lines are lines drawn over the tile that have the label "mc-stretch:*text*" attached. The text after the colon names a parameter that contains the amount of stretch desired (Figures 2.1a and 2.1b). If the line is horizontal, all material directly above the line is moved upwards by this amount (Figure 2.3). If the line is vertical, material directly to

Chapter 2

the right of the line is moved to the right by this amount. Care must be taken that the lines don't skew or distort the material in undesired ways. A simple guideline, applied to horizontal lines, is to ensure that each vertical slice through the tile crosses the same number of horizontal stretch lines. A similar rule can be applied to vertical lines. Figure 2.4 shows an example of a tile with stretch lines that follow these guidelines.

The parameter mechanisms allow tiles to be parameterized, but I have not yet discussed how parameters are computed. The next section covers this aspect.

#### 2.3. PARAMETERIZATION OF TILES

Lisp code[2] is used to parameterize tiles, and is also used in assembly diagrams. Lisp code consists of data items and expressions. The basic data types used in Mocha Chip are integers, strings, atoms, and lists of items. Expressions are lists that are evaluated to produce a data item as a result. In Lisp, a data item must be preceded by a quote mark, otherwise Lisp assumes that the item is an expression to be evaluated. Integers and character strings always evaluate to themselves, so quote marks are usually omitted when referring to these data types. Figure 2.5 shows some example data items and expressions. Integers are represented in the normal manner. Strings are surrounded by double quotes. Individual characters are represented by the character proceeded with the "#\" characters. Atoms are unique tokens used to represent a value, such as red, green, or blue. They are similar to enumerated types in Pascal and some uses of #define in C. Atoms are normally proceeded by a quote mark, since they represent values rather than expressions to be evaluated. Variables, when evaluated,

| Data Type  | Example                                 |

|------------|-----------------------------------------|

| integer    | 492                                     |

| string     | "hello world"                           |

| character  | <b>'</b> #                              |

| atom       | 'blue                                   |

| variable   | foo                                     |

| list       | '(234 round 98 "bear") '(3 5 6 (8 9 0)) |

| expression | (multiply 3 4)<br>(concat "one" "word") |

Figure 2.5. These are the Lisp data types that are commonly used in Mocha Chip. The table shows each data type along with an example of the syntax. Lists may contain any number of items, of any data type. The second list is an example of a list that contains another list. Expressions are lists where the first item is the name of a function. The remaining elements in the list form the arguments to the function. For example, the "multiply" expression evaluates to 12 and the "concat" expression evaluates to "oneword".

| Parameter Form    | Example                                                 |

|-------------------|---------------------------------------------------------|

|                   | (gnd-stretch 3)                                         |

| (name expression) | (gnd-stretch (+ 3 5))                                   |

|                   | (output-name (concat "out" (num2string output-number))) |

Figure 2.6. A Mocha Chip parameter is a two-element list, with the first element being the name of the parameter and the second element being an expression to compute the value of the parameter.

return the value they contain.

Mocha Chip specifies a parameter using a two-element list. The first element in the list is the parameter's name, and the second element is an expression to be evaluated (Figure 2.6). Parameters may take on any value, such as integers, strings, or even lists. For example, the syntax for the parameter in Figure 2.2 would be:

#### (var "input-A")

while the syntax for the parameter in Figure 2.3 would be

(var 2).

Of course, the values could be computed rather than being constants. A similar mechanism is used with assembly diagrams to provide parameterization.

As we will see later, Mocha Chip provides a way to execute expressions that are not direct computations of parameters. These expressions can be used as a general-purpose mechanism to escape to Lisp code. For example, an expression such as:

#### (result (load "myfunc.l"))

can be used to load in a file of Lisp code. These newly provided functions can then be used to compute parameters. This mechanism is typically used to write the behavioral-processing portion of the module generator.

#### 2.4. ASSEMBLY DIAGRAMS

Mocha Chip uses diagrams, called assembly diagrams, to specify the structure of the modules to be produced. These diagrams are drawn by the designer of the module generator, and replace much of the code that is traditionally written for the structural assembly portion of a module generator. The diagrams constitute a graphical programming language tailored to IC design. They are drawn using a special-purpose interactive editor built into the Magic IC layout editor.

Assembly diagrams show the relative positions and orientations of subcells. Each subcell is either another assembly diagram or a tile. Subcells, either assembly diagrams or tiles, may take parameters in order to alter the layout.

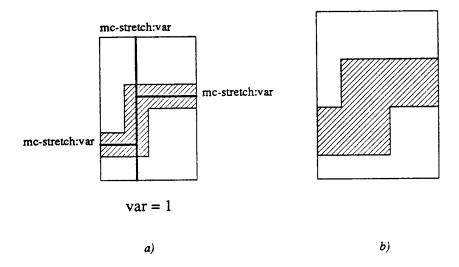

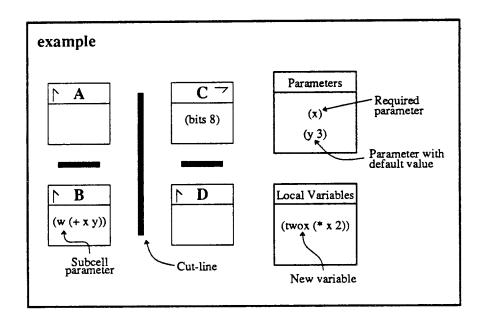

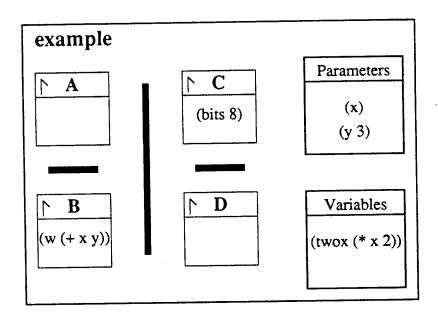

Figure 2.7. The four blocks on the left side of this assembly diagram are parameterized subcells, and may be either diagrams or cells of mask layout. The orientation of each block is indicated by the small arrow. Cut-lines describe the relative positions of the cells, and are used in constructing the module. The two blocks on the right contain parameters and local variables, and their location is of no consequence. The diagram is named "example", as indicated in the upper-left corner.

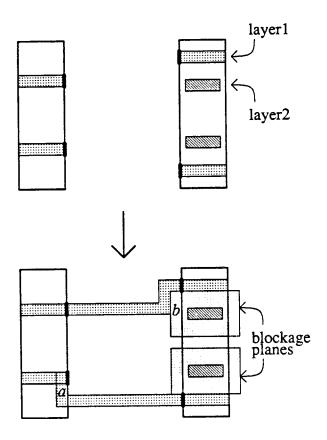

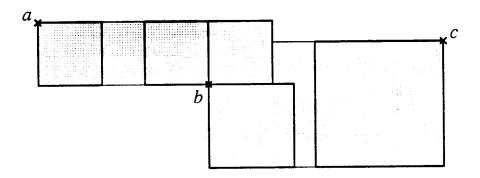

Figure 2.7 shows a simple assembly diagram that contains four subcells. The small arrows show the orientation of the cells. The bold *cut-lines* specify which cells (or groups of cells) are to be positioned relative to which other cells (or groups of cells). For example, cut-lines in Figure 2.7 specify that cell A is to be positioned above cell B, and that the A-B pair is to be positioned to the left of the C-D pair. Mocha Chip produces these lines automatically, but the user can draw them directly if desired.

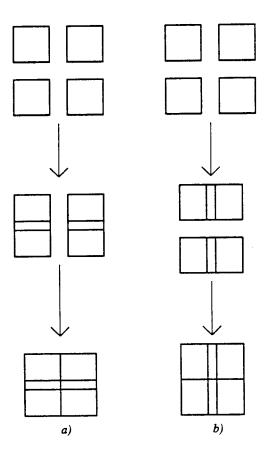

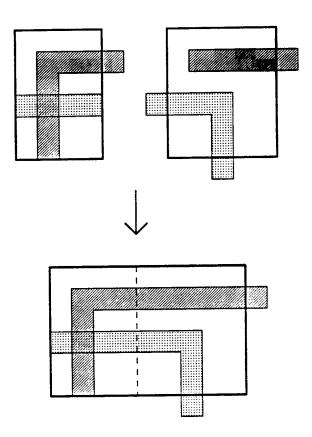

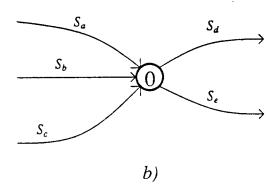

Figure 2.8. The assembly order chosen can change the end result. With the river-route-space operator, cells are joined as tightly as design rules allow. Part a shows the case where the vertical joins were performed first, as specified in Figure 2.7. In this case the horizontal joins were able to overlap cells, but they precluded a tight join in the vertical direction, possibly because of design rules. Part b shows a similar case with different cut lines that caused the vertical joins to be performed first.

The lines also specify a partial ordering for the assembly process. In the current example, both the A-B join and the C-D join must be performed before the AB-CD join. Depending upon the assembly operator used, a different collection of cut-lines may produce different results (Figure 2.8). For example, if the diagram were redrawn with the long line horizontal, this would specify that the A-C join and the B-D join should be performed before the final AC-BD join. The result might be different than in the first case. It is the responsibility of the diagram designer to ensure that the lines

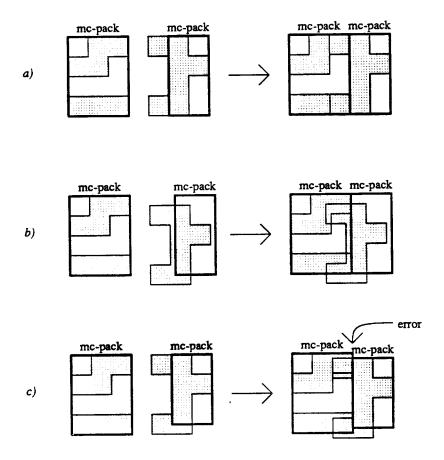

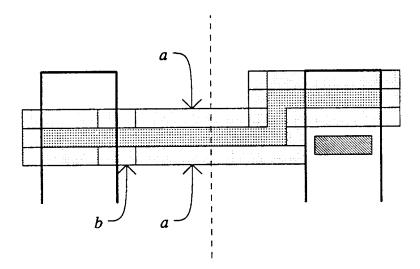

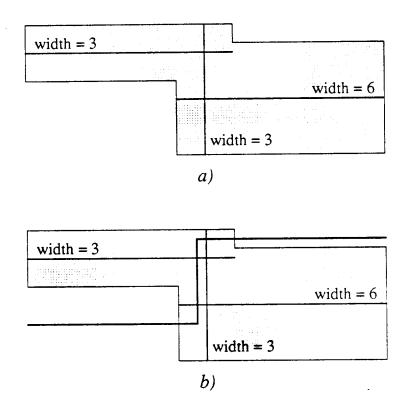

Figure 2.9. The packing operator assembles tiles by abutting their user-specified packing rectangles, denoted by the "mc-pack" label (part a). The operator ignores design rules and connectivity constraints, as shown in part b. This gives added flexibility, but may result in errors. The sides of the packing rectangles to be abutted must be of the same length, or an error is reported (part c).

chosen will work correctly with the assembly operator chosen.

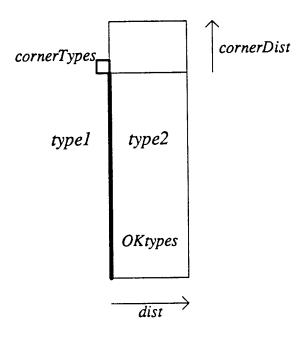

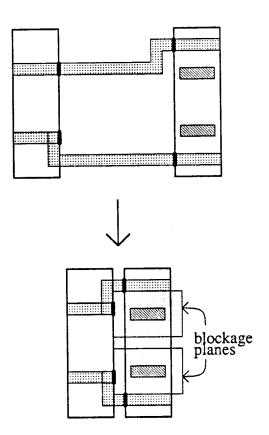

Assembly operators are chosen by tagging each cut-line with the name of the operator. Currently three tags are recognized: pack, river, and default. The pack operator (Figure 2.9) combines tiles by packing together their user-specified packing rectangles, ignoring connectivity and design-rule violations. Tiles are usually designed so that they pack together correctly irrespective of the assembly order. If an error occurs due to incorrect packing rectangles, it is likely that the end result is dependent

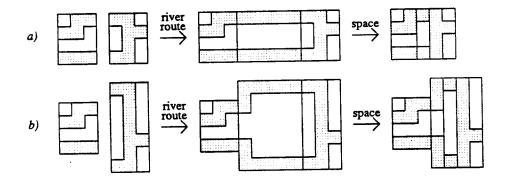

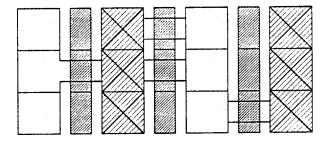

Figure 2.10. The river operator joins tiles together in two phases: river routing and spacing. The river routing phase ensures that the proper connectivity is created, while the spacing phase compacts the result according to geometrical design rules. The operator will eliminate routing entirely if the terminals align properly and design rules allow connection by overlap or abuttment.

on the assembly order since the system makes a "best guess" at the alignment and proceeds. The location of the error in the layout is tagged with a special marker that is easy to find. The river operator joins tiles by river routing and spacing, ensuring that design rules are met (Figure 2.10). If spacing rules allow, the operator may eliminate the routing and make the entire join using abuttment or overlap. This operator is dependent upon the assembly order, since it attempts to squeeze out as much space as possible during each join. It is the responsibility of the diagram designer to chose an order that produces the desired result. The default tag instructs Mocha Chip to inspect a global variable in order to pick an assembly operator. This variable will contain either the tag pack or the tag river. Using the default tag makes it possible to delay the choice of an assembly operator until after the diagrams are designed. For example, a module generator could be built with many of the cut-lines tagged with default. The user of the generator could set the default variable to either pack or river in order to experiment with different layouts of the module.

#### 2.5. PARAMETERIZATION OF DIAGRAMS

Assembly diagrams also take parameters, to control the layout of the module. The parameters and variables are put into the diagrams by pointing to a block or subcell in the diagram and invoking a text editor. These parameters could be as complex as a truth table, in the case of a PLA generator, or as simple as the size for an inverter. Assembly diagrams can also compute local variables and pass new values down to subcells.

Figure 2.7 shows how parameters are declared, local variables computed, and new values passed to subcells. The "Parameters" block specifies two parameters: x and y. The x parameter has no default value, so it must be defined at some higher level. The y parameter has a default value of 3, which is used if y is not defined when the diagram is invoked.

Subcells may also access parameters and variables defined at higher levels of the hierarchy, using Lisp's dynamic scoping rules. When a diagram is evaluated, the parameters block is evaluated first, followed by the variables block and then the parameters for each individual subcell. The parameters block simply checks to make sure that the parameters are currently defined at some higher level in the hierarchy or have values supplied by defaults. If defaults are used, a new nested scope is created that contains those values. A new scope is then created for the variables block, which is evaluated. Lastly, each subcell in the diagram is then evaluated one at a time, in a scope that includes its parameters.

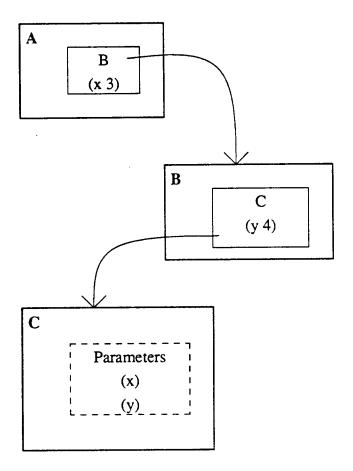

Figure 2.11. In this example, diagram A invokes diagram B with the parameter x set to the value 3. This binding holds over the entire area of the invocation of B, and includes an invocation of C. When C is finally invoked, both x and y are defined. This satisfies the parameters block in diagram C, which checks that both x and y are defined. If default values were supplied in the parameters block, they would be used if the parameter was undefined.

Figure 2.11 illustrates the scoping rules. When a parameter is declared for a subcell, that parameter value holds for all subcells used further down in the hierarchy unless superceded by a new binding for the parameter. A diagram's parameters do not have to be defined by the direct caller, since they may be inherited from some higher level. This can be considered a form of topological scoping, in that the scope of a parameter is an area rather than a temporal calling sequence. The scoping rules map directly into Lisp's dynamic scoping rules.

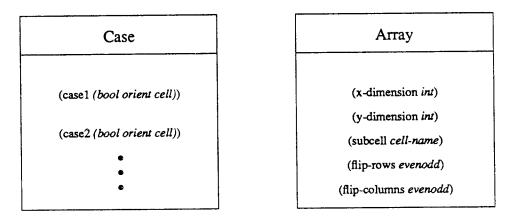

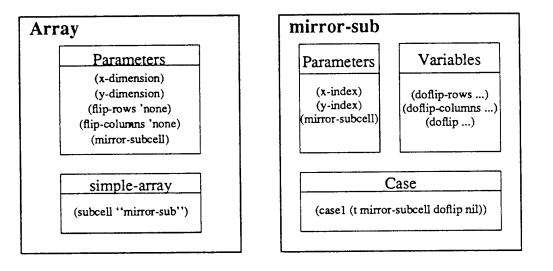

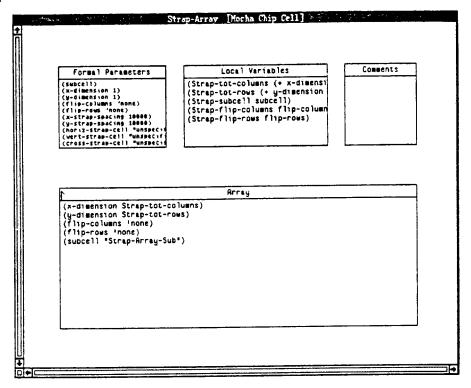

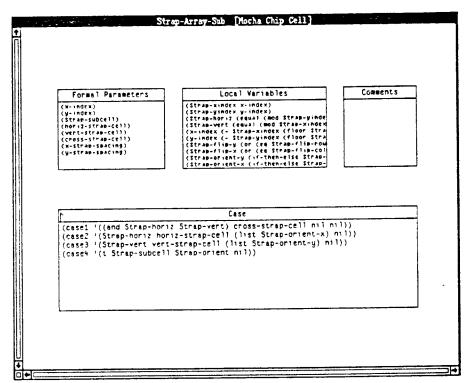

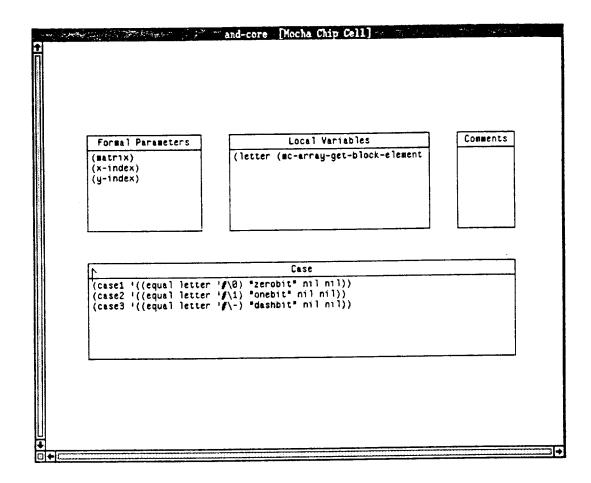

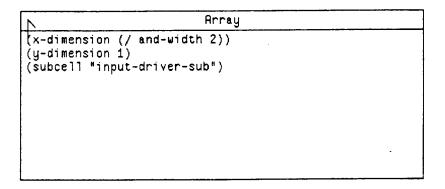

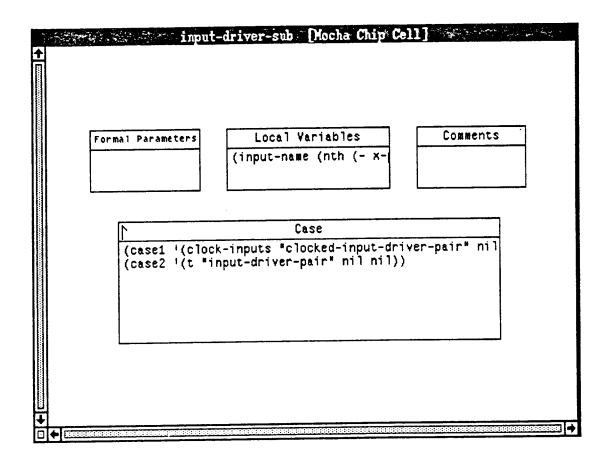

Mocha Chip provides simple graphical programming constructs that make use of these parameters, in the form of two special cells: *case* and *array*. The case cell provides a form of conditional selection, and the array cell provides a form of two-dimensional iteration. These two building blocks can be combined to form more complex control constructs, in the same way that programmers combine loops and conditionals.

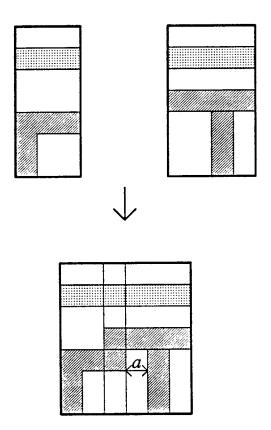

Figure 2.12. The case cell provides a form of conditional selection, and the array cell provides a form of two-dimensional iteration. These two cells can be combined in much the same way that a programmer combines loops and conditionals. The operation of the cells is controlled by parameters. The expected types of the parameters are shown in this figure with italics.

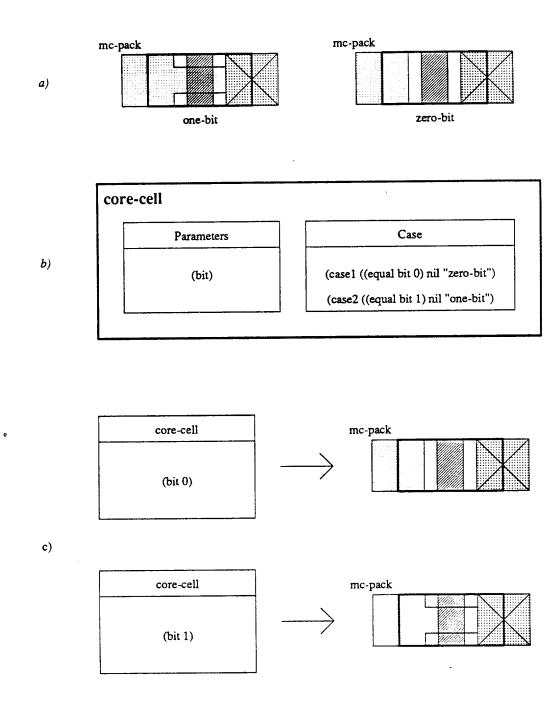

The case cell (Figure 2.12) takes a sequence of parameters, each containing three items: a Boolean expression, a cell, and an orientation. The case cell finds the first true boolean expression and uses the corresponding cell in the specified orientation. If no true expression is found, then an error is signaled. As an example, Figure 2.13 shows how a case cell can be used to choose between two tiles of layout. The example is a simplified version of part of a PLA generator.

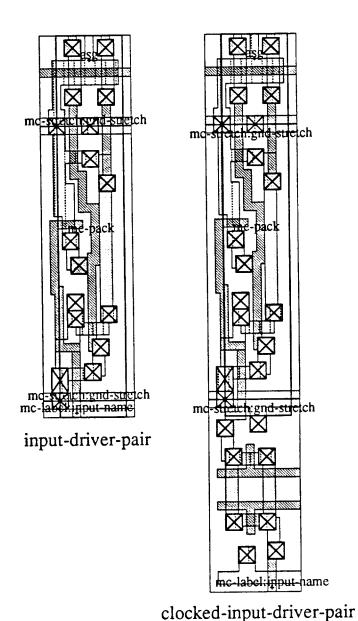

Figure 2.13. Part a of this figure shows two tiles from a PLA generator. Part of the job of the generator is to choose between these tiles at each location in an array. Part b shows a new assembly diagram, called core-cell, that takes a parameter called bit and uses the one-bit tile if the parameter is a 1, and the zero-bit tile if the parameter is a 0. This gives us a new parameterized cell, called core-cell, that chooses between the tiles. Part c of this figure shows the core-cell invoked with different parameter values.

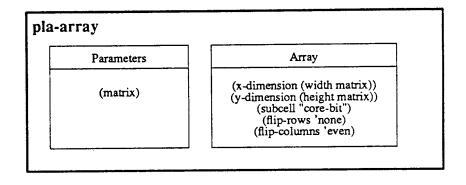

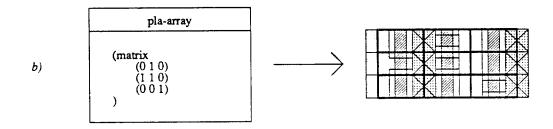

Figure 2.14. The array cell creates a two-dimensional array, invoking either a tile or an assembly diagram at each point. In this example, the diagram pla-array takes a parameter called matrix and creates an array of the diagram core-bit. This diagram uses its own indices to reference a position in the matrix, and passes this value to core-cell to select a tile.

The array cell (Figure 2.12) takes parameters that specify its dimensions, the subcell to invoke at each position, and the orientation of the rows and columns. The subcell may be either a cell of mask geometry or another diagram that contains subcells

27

— including, perhaps, array and case cells. Subcells may determine their structure using the current x and y index (provided to them by the array cell) as well as additional parameters defined by the caller of the array cell. The orientation of rows and columns are controlled by two flags, each of which takes on one of four values: none, even, odd, all. The flag allows even or odd rows (or columns) to be flipped upsidedown (or sideways). Figure 2.14 gives an example of an array cell.

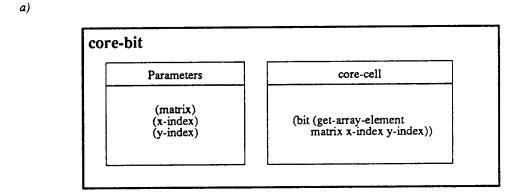

Figure 2.15. Two diagrams can implement our array cell using only a simpler array cell and a case cell. To do this, a diagram called array is drawn, and the appropriate parameters are declared. The simpler array cell is used to provide iteration, and the case cell is used to select the orientation of the cell at each position in the array. The actual computation of orientation is done using Lisp code in the variables block. The code has been eliminated from this figure due to lack of space, but it is easy to see how it would work. For example, the code for dofliprows needs only to inspect the current y coordinate y-index and the parameter flip-rows to see if there is a match. A similar computation is done for the columns. The two are combined to form an overall orientation that is stored in doflip. The Case cell selects among the alternatives, but in this instance the alternatives are chosen by using variables instead of multiple branches with constant expressions.

The case and array cells are general-purpose control constructs, and can be combined to build new control constructs in the same way that loops and conditionals may be combined. This can be demonstrated by synthesizing the flipping capability of the array cell using only the case cell and a non-flipping version of the array cell. Figure 2.15 shows how this could be done using two assembly diagrams containing the case cell and a hypothetical simple-array cell. The flipping capability in Mocha Chip's array cell ability is only an optimization to speed up the assembly process.

#### 2.6. SUMMARY

Mocha Chip's assembly diagrams provide a means of graphically representing the structure of a module. The diagrams replace the code that is traditionally written for this purpose. The parameter scoping mechanism is similar to dynamic scoping in Lisp, and can best be thought of as a form of topological scoping. The case and array cells provide what may be thought of as two-dimensional control constructs. These cells may be composed to form new constructs, in the same way that programmers combine loops and conditionals. The end result is that parameterized diagrams may be composed to form more complex diagrams that generate the modules we see in VLSI chips.

## 2.7. REFERENCES

- J. K. Ousterhout, G. T. Hamachi, R. N. Mayo, W. S. Scott and G. S. Taylor, The Magic VLSI Layout System, *IEEE Design & Test of Computers*, February, 1985.

- 2. G. L. Steele, Jr., Common Lisp, The Language, Digital Press, 1984.

## 3 RELATED WORK

#### 3.1. INTRODUCTION

In the past, several techniques have been developed for the design of module generators. The ideal system would provide visually intuitive mechanisms for expressing geometrical relationships, and allow for flexible parameterization of the structures. Graphics works well for describing geometrical relationships, but is hard to parameterize. Textual programming languages express parameterization well, but make the structure hard to visualize. This interplay of text and graphics is at the heart of the development of module-generator systems. The following sections survey the

Chapter 3

development of the field in a roughly chronological order.

#### 3.2. PROGRAMMING

Initial module generator systems were based upon general-purpose programming languages, such as DPL[1] (written in Lisp) and Chisel[2] (written in C). These systems provided library routines for generating low-level primitives such as rectangles of material. A typical line in a module generator built using one of these systems looks like:

## rect(x, y, 3, 5, METAL1);

This places a metal rectangle of width 3 and height 5 at the coordinates specified by x and y. Since these are calls in a general programming language, the full power of the language can be used to compute the layout of the module. Layout generation then becomes a programming task. For example, constructs such as loops and procedures (Figure 3.2) could be combined to produce the structure shown in Figure 3.1.

Figure 3.1. Some layout produced by part of a simple PLA generator.

While the programming approach provides the ultimate in flexibility, it is difficult to use in practice. Computing the location of rectangles involves many simple, but

32

```

procedure pla_array(matrix)

for i = 0 to width_of(matrix)

{

for j = 0 to height_of(matrix)

if (odd(i))

core_bit_odd(i * 8, j * 4, matrix[i, j]);

core bit even(i * 8, j * 4, matrix[i, j]);

}

}

}

procedure core_bit_odd(x, y, bit)

rect(x, y, 4, 4, M1 CONTACT);

rect(x + 5, y, 2, 4, POLY);

rect(x + 8, y, 4, 4, N_DIFF);

if (bit == 1)

rect(x + 4, y + 1, 4, 2, N_DIFF);

}

procedure core_bit_even(x, y, bit)

rect(x, y, 4, 4, N_DIFF);

rect(x + 5, y, 2, 4, POLY);

rect(x + 8, y, 4, 4, M1\_CONTACT);

if (bit == 1)

rect(x + 4, y + 1, 4, 2, N_DIFF);

}

```

Figure 3.2. Some code to produce the layout in Figure 3.1. In a system like this, all the features of a general-purpose programming language can be applied to layout generation. The disadvantage is that the code is textual and makes it hard to visualize the geometry.

error-prone, computations, since it is hard to visualize the layout by looking at the text. These module generators are debugged by editing the program, compiling it, and plotting the output. Many iterations are required in order to debug a module generator. In addition, most module generators have many options which exacerbate the problem. Erroneous output is often produced when a module generator built using this technique is supplied with combinations of input parameters that have not been previously tested. More information about the programming technique and its limitations may be found

Chapter 3

in Chapter 6 of Steve Trimberger's book[3] and Chapter 8 of Steve Rubin's book[4].

One approach to improving the programming technique is to automate some of the placement of geometry. This is done by handling connections and design rules automatically. The programmer specifies the relative positions of the rectangles and what is to be connected. The system then picks absolute coordinates for the rectangles creating a design-rule correct layout. The best know examples of this technique are i[5] and allende[6]. In i, symbols (transistors, contacts, etc.) are placed relative to other features, such as other symbols or wires. Wires are attached to terminals (called connectors) on the symbols. It is possible to specify relative distances, such as the placement of one symbol 3 units above another. The design style is similar to symbolic layout[7, 8], but is programmed rather than being drawn. In Allende (Figure 3.3), the user abuts cells to form new ones, but the abutment specifies connections and relative positions, not absolute coordinates. Coordinates are determined by solving a set of constraints between rectangles that capture the designer's specification. The basic cells are either provided externally to the system or built out of primitive components such as transistors and rectangles.

These approaches help, but they still suffer from the problem that text is an awkward way to specify geometry. Additional problems are also created. Solving the constraints takes more time than more direct approaches. For example, Allende takes 9.5 minutes to produce a 16-bit ALU when running on a VAX 11/750. The designs produced are not always as small as hand designs, since the systems give up some flexibility in order to guarantee the correctness of the constraints. On the whole, though,

```

procedure pla_array(matrix)

begincell('pla_array');

for i = 0 to width_of(matrix)

begincell(' ');

for j = 0 to height_of(matrix)

if (odd(i))

place(FLIPPED0);

if (matrix[i, j] == 1)

extcell('onebit');

else

extcell('zerobit');

if (j != height of(matrix)) place(ABOVE);

}

endcell(' ');

if (i != width_of(matrix)) place(RIGHT);

endcell(' ');

}

```

Figure 3.3. This figure presents Allende code that is equivalent to the previous example. Allende generates a set of constraints on rectangles that, when solved, will implement this specification.

constraint-based layout seems to be an improvement over the direct programming of actual coordinates, in that design-rule errors are eliminated.

#### 3.3. GRAPHICAL SYSTEMS

Graphical systems such as Caesar[9], Chipmonk[10], and Magic[11] were first developed as an intuitive means of specifying non-parameterized geometry. The layout is simply drawn rather than programmed. This provides a better user interface, since what the designer sees on the screen is identical to the conceptual image in the designer's head. The problem, of course, is that these graphics systems don't provide programmability. Without programmability, we cannot create module generators and all layout must be drawn manually.

Chapter 3 35

Some graphical systems have features to partially compensate for their lack of programmability. In some systems, such as Chipmonk[10] and Electric[4], wires are attached to other pieces of material and move around when the attached pieces move, to maintain connectivity. Symbolic layout systems such as Mulga[7] and Vivid[8] take this one step further, providing a graphical version of the design style we encountered with constraint-generating programming languages. In the symbolic layout style, circuit elements and wires are drawn in their relative positions and the system solves constraints to determine the absolute coordinates.

Two systems, SAM[12] and Daedalus[13], combine a graphical display with a textual programming language. In SAM, the two displays are simply two views of a single data structure (Figure 3.4). This greatly aids the writing of programs for layout generation, providing something that is best thought of as instant plotting with the ability to make small graphical changes. The user can edit either of the views, and the corresponding changes appear in the other view. The graphical display only shows one instance of the module to be generated, in effect instantiating the program with a fixed set of parameters. When the graphical layout corresponding to parameterized text is edited, there in ambiguity in how the text should be updated, since several parameterized texts can generate a single graphical layout. The users of these systems must use and understand two different but linked representations. While this works well for the layout of low-level cells, it does not greatly aid the higher-level parameterization of a module generator.

Figure 3.4. In SAM, the display shows two windows. On the left is parameterized text, and on the right is an instance of the cell. Either window may be modified, and the other is updated. The two windows are in fact two views of a single internal data structure. This diagram is copied from a paper on SAM[12].

#### 3.4. TILING

Tiling attempts to combine the good features of a programming language with the visual power of a graphical editor[14]. With tiling, a graphical editor is used to prepare pieces of geometry called tiles. The tiles can contain any amount of geometry, but usually contain components similar in size to input buffers, gates, and registers. The tiles are assembled by a program, providing a parameterized way of assembling the

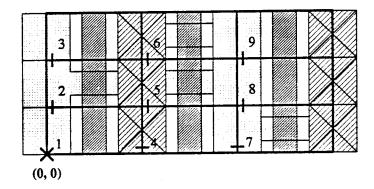

```

procedure pla_array(matrix)

width = WIDTH OF("onebit");

height = HEIGHT_OF("onebit");

for i = 0 to width_of(matrix)

if (odd(i))

orient = SIDEWAYS;

else

orient = NORMAL;

for j = 0 to height_of(matrix)

if (matrix[i, j] == 0)

name = "zerobit";

else

name = "onebit";

place_tile(i * width, j * height, name, orient);

}

}

```

Figure 3.5. In the tiling approach, a graphical editor is used to prepare tiles of layout, which are then assembled using a program. The program in this figure places tiles at absolute coordinates. More advanced systems placed tiles by aligning their corners or by packing them together using user-specified packing rectangles.

building blocks (Figure 3.5).

This approach eliminates the difficulties encountered when placing individual rectangles with a program, instead replacing it with the similar, but smaller, problem of placing tiles of geometry. Errors can occur between tiles, but are less frequent than when individual rectangles are placed.

Several schemes were developed for placing the tiles. The earliest scheme placed tiles at absolute positions (Figure 3.5). Correct alignment was difficult with this scheme. A more popular method placed tiles by aligning their user-specified packing rectangles. For example, the code could specify that a tile was to be placed above some previously placed tile. The system would then compute a location for the new tile that caused its packing rectangle to exactly abut the packing rectangle of the

previously placed tile.

TPACK[14], my Master's Project, developed a more powerful scheme. In TPACK, tiles are aligned by their corners. This is more general, since special empty spacing tiles can be defined whose corners are used to control the alignment of other tiles (Figure 3.6). This allows placement of a new tile at an arbitrary offset from some previously placed tile, something that is not possible with the packing rectangle approach. However, there is a price paid for this additional flexibility. The information about which corners are used for alignment is contained in the program code. This means that the tile designer must either look at the program code when designing spacing tiles, or read documentation that describes the code's behavior. With the packing-rectangle approach, there is no variation in the assembly method, resulting in a simpler interface for the tile designer. My experience over the past few years indicates that the additional flexibility provided by TPACK is not worth the added complexity for the tile designer.

## 3.5. REGULAR-STRUCTURE GENERATOR

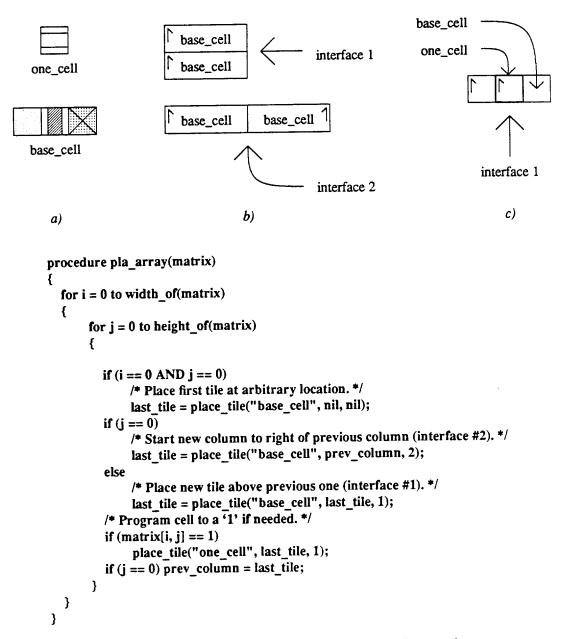

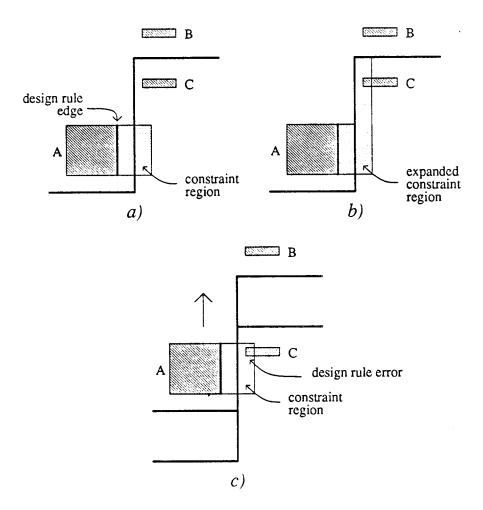

Bamji's Regular-Structure Generator[15] attempts to solve the problem of assembling tiles. Bamji defines an interface, which is a legal relative position for two tiles. The set of interfaces is defined by the user by placing examples in a diagram and numbering them (Figure 3.7). The system ensures that when tiles are placed only prespecified interfaces are used. This allows the user to verify the interfaces in advance, in turn ensuring that the resulting layout only contains verified interfaces.

```

procedure pla_array(matrix)

for i = 0 to width_of(matrix) {

if (odd(i)) {

zero_tile = "zerobit-flipped";

one tile = "onebit-flipped";

} else {

zero tile = "zerobit";

one_tile = "onebit";

for j = 0 to height_of(matrix) {

if (matrix[i, j] == 0)

new tile = zero_tile;

else

new tile = one tile;

if (i == 0 \text{ AND } j == 0) /* Place first tile at (0, 0). */

last tile = place_tile(new_tile, ORIGIN);

if (j == 0) /* Start new column to right of previous column. */

last tile = place_tile(new_tile,

align(lower_left(new_tile), lower_right(prev_column)));

/* Place new tile above previous one. */

last tile = place tile(name,

align(lower_left(new_tile), upper_left(last_tile)));

if (j == 0) prev_column = last_tile;

}

}

}

```

Figure 3.6. TPACK uses corner alignment to place tiles. Each new tile has a corner aligned with a previously placed tile, as is indicated by heavy bars in this this figure. The bars are numbered sequentially in the order that the tiles where placed. Spacing tiles could be used to provide arbitrary offsets, but this is not needed for this example. The tile-packing method recognizes this, and uses packing rectangles instead of specifying corners in the code. The result is much the same, but simplifies both the code and the design of tiles, since the tile designer never needs to know which corners are used for alignment. Some flexibility is lost, however, since arbitrary offsets cannot be provided through the use of spacing tiles.

Figure 3.7. In the Regular-Structure Generator (RSG), tiles are drawn and example arrangements given. The arrangements define *interfaces*, which are then used by a program to specify the connectivity of the tiles. The actual positions and orientations are determined by the relative positions and orientations drawn in the example arrangements. A given pair of tile types may have more than one possible configuration, leading to multiple interfaces (as in part b of this figure). Interfaces are numbered and referred to in the code. RSG uses a Lisp-like language, but this example has been coded in a C-like language for consistency with the other examples in this chapter.

The technique does not work well for generators that have a large number of optional tiles for a certain location, as is common in practice. An interface must be defined for each possible combination of tiles, leading to an exponential rise in the number of interfaces to be defined and checked. This problem is partially, but not completely, overcome by allowing tiles to be stacked on top of each other, allowing a single tile to be "programmed" by the presence of other tiles on top.

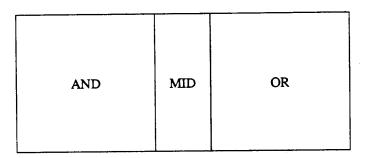

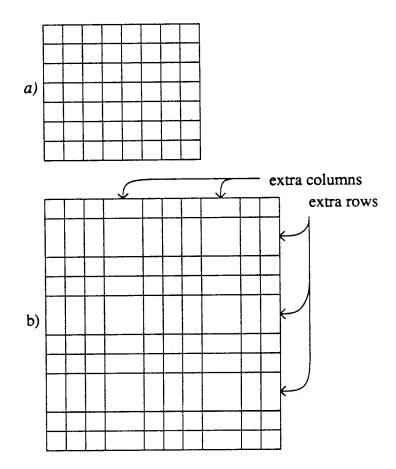

## 3.6. ARRAY-STRUCTURE TEMPLATES

SDA's Structure Compiler uses array-structure templates[16] to specify graphically the global structure of a module. The user can draw arrays whose contents are determined by personality matrices and pieces of code (Figure 3.8). The system has no graphical representation of conditional selection, and doesn't allow arrays to be nested. These features would be needed in order to make the system complete, in the sense of allowing arbitrary structures to be built graphically and re-used as if they were primitive components.

Module assembly proceeds in three steps. In the first step, each block is processed, creating a map of symbols based upon a personality matrix and rules attached to the block. The second step executes user-supplied code that manipulates the map. In the final step, each block is assembled by translating the symbols into tiles, packing the tiles together (using user-specified packing rectangles), and joining the resulting blocks as specified by the array-structure template.

Array properties for the AND plane:

```

map: 1 \rightarrow TN; 0 \rightarrow NT; - \rightarrow NN; tiles: N \rightarrow "zerobit"; T \rightarrow "onebit"; orientation: flip-odd-rows; flip-odd-columns; procedure: "pla_code.l";

```

Figure 3.8. SDA's Structure Compiler uses a diagram to show the overall structure of a module that consists of arrays. Our simple example would contain only one array, but this figure shows a module with three arrays to give a feel for the sort of diagrams that are drawn. Each array is tagged with array properties that control how a personality matrix is mapped into an array of tiles. In this example, a "1" symbol in the input is expanded to the two symbols "TN". After this expansion, the procedure pla\_code.l is invoked. This procedure may inspect the array and change symbols, add new rows and columns, and do other manipulations to produce a new array. For our simple example, no such procedure would be required. After the procedure is run, the symbols in the array are translated into tiles using the tiles array property, and packed together using user-specified packing rectangles. The orientation property controls the positioning of the tiles. The syntax of array properties has been changed for this example in order to increase readability.

#### 3.7. DISCUSSION

Several techniques have been developed for the design of module generators. The key theme is the tradeoff and integration of visually-expressive graphics with parameterization. There are two main problems that concern this tradeoff: the representation of the structure of a module, and the correct placement of tiles so that they obey geometrical design rules.

Most current systems use graphics to draw tiles that are then assembled by a programming language. Only the Regular-Structure-Generator specifically addresses the

problem of correctly placing tiles. It, however, requires the legal interfaces to be drawn by the user, which can be impractical if a large number of tiles can fill a given position, resulting in an exponentially large number of interfaces. Mocha Chip takes a different approach: tiles are assembled by assembly operators rather than directly placed. The simplest of these operators, the packing-rectangle operator, provides no help with the correct placement of tiles. The river-route-space operator, however, places tiles so that they obey geometrical design rules and connectivity rules. As a result, placement is guaranteed to be correct without forcing the module generator designer to verify an exponentially large set of tile interfaces.

The other main concern is the representation of the overall structure of a module. Both array-structure templates and Mocha Chip provide a means of using graphics to specify this structure. Array-structure templates are limited to the specification of the top-level array structure of a module. Mocha Chip, however, is an extensible programming system that has graphical representations of both conditional selection and iteration. In addition, Mocha Chip diagrams can be used in other diagrams in the same way that tiles are, resulting in a system that can express hierarchical module generators using graphics. Thus, Mocha Chip diagrams are used to specify the structure of all levels of a module, not just the top-level overall structure.

Mocha Chip is an advance in both areas addressed by previous systems: the representation of the module's structure and the placement of individual tiles. A new graphical programming language is used to represent the structure of a module. The language is complete in the sense that it provides graphical representations of iteration.

and conditional selection that can be combined to form new control constructs. Mocha Chip's assembly operators represent a new approach to the second problem: the placement of tiles. In Mocha Chip, the river-route-space assembly operator guarantees proper connectivity and ensures that geometrical design rules are not violated. This automatic placement of tiles frees the module generator designer from having to manually verify that all possible tile interfaces are valid. The end result is a powerful module generation system that eases the module design process.

#### 3.8. REFERENCES

- J. Batali and A. Hartheimer, The Design Procedure Language, VLSI Memo 80-31, MIT, September, 1980.

- 2. K. Karplus, CHISEL: An Extension to the Programming Language C for VLSI Layout, Report No. STAN-CS-82-959, PhD Thesis, Stanford University, 1983.

- 3. S. M. Trimberger, An Introdution to CAD for VLSI, Kluwer Academic Publishers, 1987.

- 4. S. M. Rubin, Computer Aids for VLSI Design, Addison-Wesley, 1987.

- 5. S. Johnson and S. Browning, The LSI Design Language i, Technical memorandum 1980-1273-10, Bell Laboratories, November 18, 1980.

- 6. J. M. Mata, A Methodology for VLSI Design and a Contraint-Based Layout Language, PhD Thesis, Princeton University, October, 1984.

- 7. N. Weste and B. Ackland, A Pragmatic Approach to Topological Symbolic IC Design, in *VLSI* '81, Academic Press, 1981, pp. 117-129.

- 8. J. Rosenberg, D. Boyer, J. Dallen, S. Daniel, C. Poirier, J. Poulton, D. Rogers and N. Weste, A Vertically Integrated VLSI Design Environment, *Proc. 20th Design Automation Conference*, 1983, pp. 31-38.

- 9. J. K. Ousterhout, The User Interface and Implementation of an IC Layout Editor,

IEEE Transactions on Computer-Aided Design CAD-3, 3 (July, 1984).

- 10. P. Petit, Chipmonk: An Interactive VLSI Layout Tool, Digest of Papers, Compcon 82, 1982, pp. 302-304.

- J. K. Ousterhout, G. T. Hamachi, R. N. Mayo, W. S. Scott and G. S. Taylor, The Magic VLSI Layout System, *IEEE Design & Test of Computers*, February, 1985.

- 12. S. Trimberger, Combining Graphics and a Layout Language in a Single Interative System, *Proc. 18th Design Automation Conference*, 1981, pp. 234-239.

- 13. J. Batali, N. Mayle, H. Shrobe, G. Sussman and D. Weise, The DPL/Daedalus Design Environment, in *VLSI* '81, Academic Press, 1981, pp. 183-192.

- 14. R. Mayo and J. Ousterhout, Pictures with Parentheses: Combining Graphics and Procedures in a VLSI Layout Tool, *Proc. 20th Design Automation Conference*, 1983, pp. 270-276.

- 15. C. Bamji, C. Hauck and J. Allen, A Design by Example Regular Structure Generator, *Proc. 22nd Design Automation Conference*, 1985, pp. 16-22.

- 16. H. Law and J. Mosby, An Intelligent Composition Tool for Regular and Semi-Regular VLSI Structures, IEEE International Conference on Computer Aided Design, 1985, pp. 169-171.

# 4 SYSTEM OVERVIEW

#### 4.1. SYSTEM STRUCTURE

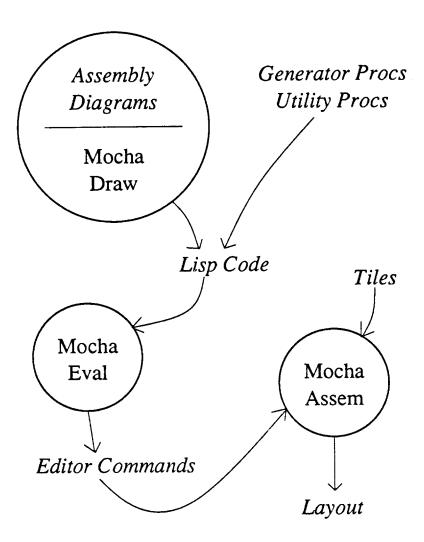

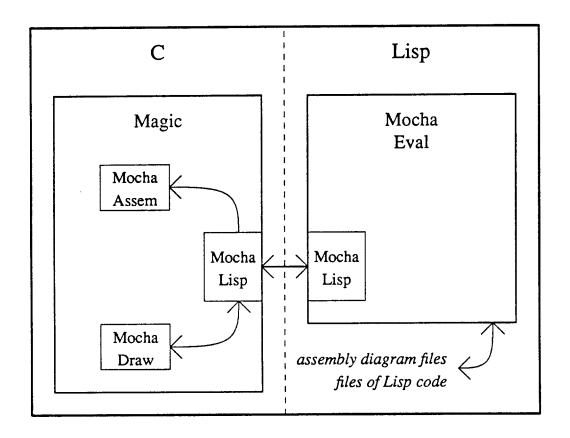

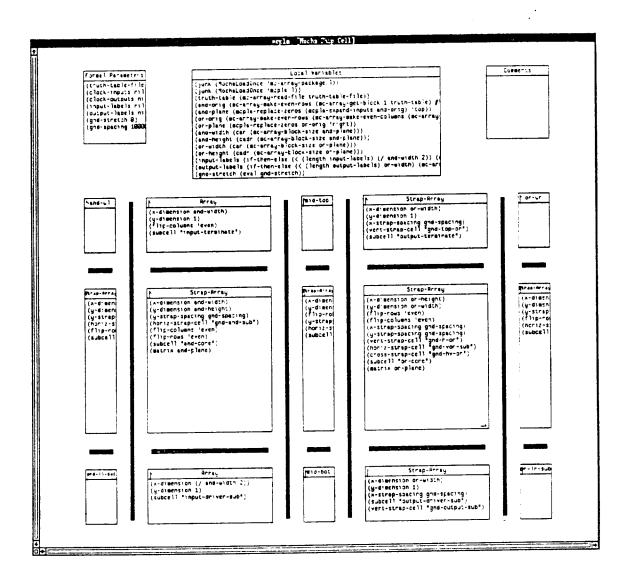

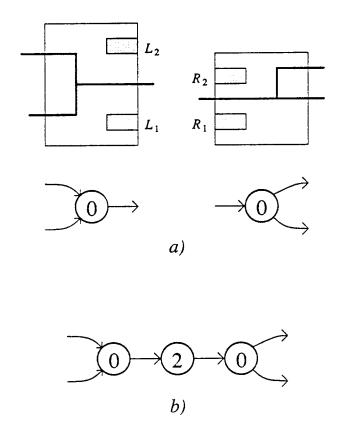

The Mocha Chip implementation contains four components (Figure 4.1). Three of the components correspond to three issues that Mocha Chip addresses: the use of graphics to draw parameterized diagrams, the evaluation of those diagrams to produce an instantiated module, and the assembly of mask layout for that module. Graphics are handled by the Mocha Draw module, instantiation by the Mocha Eval module, and assembly by the Mocha Assem module. The fourth module, Mocha Lisp, provides a communication mechanism between C and Lisp, as will be discussed later.

Figure 4.1. Mocha Chip is divided into four components. Mocha Draw handles editing of the assembly diagrams and produces Lisp code that represents them. Mocha Eval evaluates the code to produce an instance of a module, also represented as Lisp code. The instantiated Lisp code is used to produce a file of editor commands that control Mocha Assem's assembly of mask layout. Mocha Lisp, not shown in this diagram, is a module that allows C code to communicate with Lisp code, and will be discussed later.

During use, data flows from Mocha Draw into Mocha Eval and then on to Mocha Assem. Mocha Draw takes input from the user and creates assembly diagrams. These diagrams are converted into files of Lisp code. This parameterized Lisp code is combined with other Lisp code and given to Mocha Eval, which evaluates it to produce a single instance of the module. The instance is represented as a binary tree of pairwise

assembly operations, and is communicated to the Mocha Draw module via a file of special-purpose editor commands. These commands, along with a set of tiles of mask geometry, are used by the Mocha Assem module to produce the final layout.

Figure 4.2. Mocha Chip is written in both C and Lisp. The C portion consists of the Mocha Draw module and the Mocha Assem module, both of which are integrated into Magic. The Lisp portion consists of Mocha Eval. The Mocha Lisp module implements a special purpose RPC (remote procedure call) mechanism that allows the two parts to communicate. Part of Mocha Lisp is written in C, and part in Lisp.

Mocha Chip is integrated with the Magic VLSI layout editor [1], as shown in Figure 4.2. Mocha Draw is a special window type in Magic that draws assembly diagrams. It consists of about 12,000 lines of C code. Mocha Assem is also written in C, and makes heavy use of Magic's corner-stitched database. It consists of about 10,000 lines of code. Mocha Eval is a Lisp system, run as a subprocess to Magic. It is written in

about 8,000 lines of Lisp code, and communicates with Magic via a special-purpose RPC (remote procedure call) as well as with files. The RPC mechanism is written in both C and Lisp, and is contained in the Mocha Lisp module.

Mocha Chip was written in two languages to facilitate the integration with Magic and the interpretation of code written interactively. The latter requirement comes from the fact that diagrams are drawn and parameterized interactively, and then need to be evaluated. Lisp was chosen as a common and easily understandable language for interactive interpretation of expressions. C was chosen for the rest of the system, so that Mocha Chip could make use of Magic's graphics routines and Magic's cornerstitched layout database.

Mocha Chip is an open system in the sense that the user may elect to use only part of it. I expect that users will draw assembly diagrams in order to specify modules, but it is possible to write the Lisp code directly. This provides a means of determining if the assembly diagrams are really a convenient specification. If not, I would expect to see users writing Lisp code instead of drawing assembly diagrams. It is also possible to generate the file of editor commands directly, bypassing the Lisp system entirely. This retains the use of the pairwise assembly operator, but allows for the development of different front ends for module specification.

The next sections discuss the implementation of the modules.

#### 4.2. MOCHA DRAW

Figure 4.3. This is an example of an assembly diagram drawn with Mocha Draw. Commands are used to place the blocks and control their orientation. The editor provides a mechanism for editing the text that is contained within each block. Cut-lines may be inserted automatically, although the editor allows the user to modify them.

Mocha Draw is the graphical editor for drawing assembly diagrams. Figure 4.3 shows a simple assembly diagram drawn with the editor. Mocha Draw is implemented as a special window type in the Magic VLSI layout editor. There are commands to read and write assembly diagrams, to place a subcell, and to perform transformations such as rotation and mirroring. For the most part, the syntax of these commands is similar to the corresponding Magic commands for IC layout. Mocha Draw also provides special commands for editing the text inside of a cell as well as commands for dealing with cut-lines. Text is edited by selecting a cell in the diagram and opening up a new window with a text-editor containing the contents of the cell.

Chapter 4 52

Mocha Draw can automatically draw cut-lines, although the user is free to put them in manually. Mocha Draw's automatic procedure is very simple. First, it attempts to find a clear path through the diagram. If such a path is found, a cut-line is drawn through that path and the procedure repeats on the areas on each side of the cut-line. If no path is found, a side of the diagram is chosen and all the cells that touch that side are moved outwards enough to open up a clear path. The procedure then repeats. Eventually the procedure will encounter a single cell, at which point it terminates.

Once a diagram is created, Mocha Draw stores the diagram as Lisp code (Figure 4.4). This Lisp code can be read back into the editor for further graphical editing of the diagram. Each graphical construct has a corresponding Lisp function. Each of these will be described.

The setup for an assembly diagram is handled by the MochaChipCell, Parameters, and Variables functions. MochaChipCell takes a cell name and an expression to evaluate. This expression is usually a call to the Parameters function, which contains a list of parameters to be set up and a function to evaluate in the new referencing environment. The Variables function has a similar effect. Figure 4.4 shows the use of these functions in a small example.

The main body of the diagram is handled by the Invoke function, the pairing functions HorizontalPair and VerticalPair, and the orienting functions Clockwise, Sideways, and UpsideDown. Invoke takes a cell name, an instance name, and some arguments for the cell. The result is the cell evaluated with the given arguments. This

```

(MochaChipCell "sample"

(Parameters ( (a) (b 3) )

(Variables ( (var (* b 2)) )

(VerticalPair "pack"

(HorizontalPair "pack"

(Invoke "A" ( (sub var) ) ...)

(Invoke "A" ( (sub (+ a b)) ) ...)

...)

(HorizontalPair "pack"

(Invoke "B" nil ...)

(UpsideDown (Invoke "C" nil ...))

...)

...)

...)

```

Figure 4.4. Assembly diagrams are stored as Lisp procedures. The translation is a simple one — each graphical construct has a corresponding Lisp function. Each Lisp function has a place for the editor to store uninterpreted data (indicated by ...). This data suggests coordinates for the corresponding graphical object, so that diagrams retain their appearance across editing operations.

cell may be transformed using the Clockwise, Sideways, and UpsideDown functions. Clockwise rotates by a multiple of 90 degrees, while Sideways and UpsideDown provide mirroring operations. Each cut-line in the diagram corresponds to a call to either HorizontalPair or VerticalPair. The first argument to these functions is the text associated with the cut-line, and specifies which pairwise assembly operator to use.

Additional information, indicated in Figure 4.4 by ellipses, is provided by the graphical editor. This information contains suggestions about the size and placement of components on the screen. It is used to ensure that diagrams don't change in appearance across editing sessions. If the information is omitted or inconsistent, Mocha Draw provides reasonable values.

Assembly diagrams are read into Mocha Draw by executing them in a special Lisp environment. The procedures in this environment invoke procedures in Mocha Draw via a special-purpose RPC mechanism. These procedures construct and place the corresponding graphical objects to create the assembly diagram represented by the Lisp code.

## 4.3. COMMUNICATION WITH LISP

A text-based and line-oriented RPC mechanism is used to communicate between the C and Lisp portions of Mocha Chip. For a call to Lisp, C sends a line to Lisp. Lisp sends back lines containing messages to be printed, a return value, and a then a prompt. The line immediately before the prompt line is assumed to be the return value. Errors are recognized by the special prompt that Lisp prints out after an error.

For a call to C from Lisp, Lisp prints out a special message line that is recognized by the C part of the system. The line contains a special prefix followed by the name of the function to invoke and textual arguments. C looks this up in a table and calls the appropriate routine. The return value of the routine is sent to Lisp as a text string which sets a Lisp variable. The calls may be nested, so Lisp can call C and vice-versa to any depth.

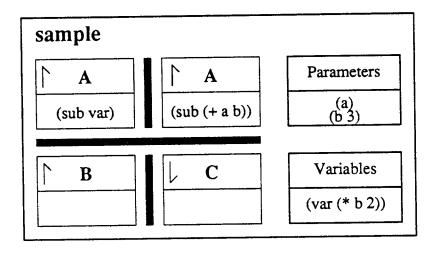

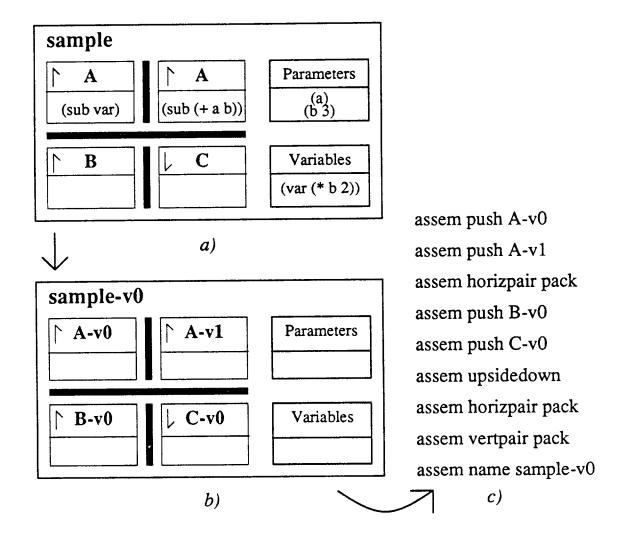

#### 4.4. MOCHA EVAL

Mocha Eval's task is to take the code produced by Mocha Draw and produce an instantiated module. This is done by executing (or in Lisp terminology, "evaluating") the code in a special Lisp execution environment. Two phases are used. The output of the first phase is a tree of diagrams. These diagrams correspond to the assembly diagrams drawn by the user (Figure 4.5a), except that parameters have been eliminated and unique names have been assigned to the resulting versions of the diagrams (Figure 4.5b). In the second phase, this tree of diagrams is translated into commands to control the assembly process (Figure 4.5c).

The Mocha Eval code is written in Common Lisp, which is readily portable. The user may, however, parameterize assembly diagrams with Lisp code that is not portable. It is important that the user avoid non-portable code if the generator is to be portable.

If a Lisp error occurs during evaluation (e. g. because of improper code specified by the user), information about the error is passed to the user along with the name of

Figure 4.5. Mocha Eval takes a set of parameterized diagrams and produces a file of Magic commands. This proceeds in two phases. In the first phase, parameters and variables are evaluated to produce an instantiated tree of diagrams. Next, the tree of diagrams is translated into a file of special-purpose commands.

the cell that was being evaluated when the error occurred. The user can also elect to interact directly with Lisp when an error occurs. In this mode, Magic and Mocha Lisp just act as intermediaries, passing lines back and forth between the user and the Lisp subprocess.

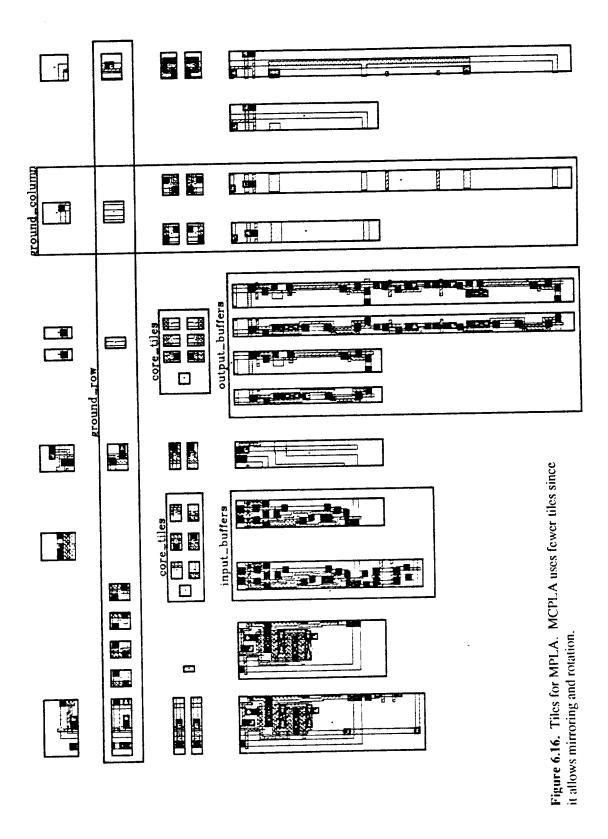

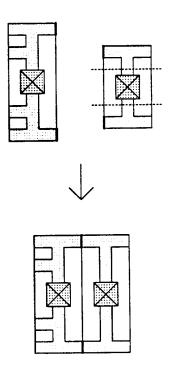

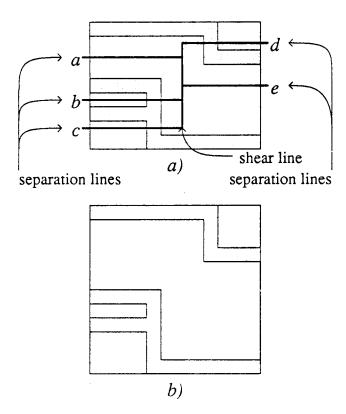

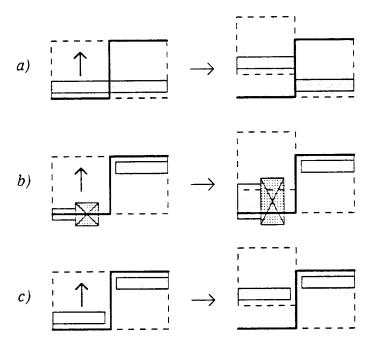

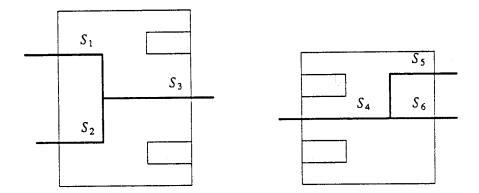

In the first phase, Mocha Eval starts with the name of the topmost cell of the module. The procedure with this name (corresponding to an assembly diagram) is executed, and the procedure may explicitly load in files of Lisp code containing user-specified functions. When subcells are invoked, Mocha Eval finds the corresponding file of code and loads it. The subcells are then executed, and the process recurses. The result (function return value) of the execution of a cell is another cell that has all the parameters and variables instantiated (Figure 4.4b). This new cell may contain fully instantiated subcells, also produced by the cell evaluation process.