## A New Interface Specification Methodology and its Application to Transducer Synthesis

Gaetano Borriello

Computer Science Division

Department of Electrical Engineering and Computer Sciences

University of California, Berkeley

Copyright © 1988, Gaetano Borriello.

All rights reserved.

### A New Interface Specification Methodology and its Application to Transducer Synthesis

by

Gaetano Borriello

B.S. (Polytechnic Institute of New York) 1979

M.S. (Stanford University) 1981

#### DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

# DOCTOR OF PHILOSOPHY in COMPUTER SCIENCE

in the

# GRADUATE DIVISION OF THE UNIVERSITY OF CALIFORNIA, BERKELEY

Approved: Randy H. Katz (Chairman) May 26, 1988

Carlo H. Sequin May 25, 1988

Alice M. Agogino May 24, 1988

Filed: May 26, 1988

Research supported by the University of California under a Microelectronics Fellowship and the Defense Advanced Research Projects Agency under Contract No. N00039-83-C-0107.

## A New Interface Specification Methodology and its Application to Transducer Synthesis

#### ABSTRACT

In this dissertation, I present a new methodology for the abstract specification of digital circuit interfaces. An interface is the collection of signal wires that cross a circuit boundary and the constraints on the events on those wires. The specification methodology is based on a formalization of the timing diagrams commonly used by digital circuit designers. This mostly graphical method is not only familiar to its intended users but is also concise in its description. An interactive editor, called *Waves*, has been implemented to support this methodology and used to describe a wide range of circuit interfaces ranging from static memories, to microprocessors, to system busses.

Interface specification has a wide range of uses during the design and evaluation of a circuit. Waves diagrams and the constraints they capture form the basis for an entire new set of CAD tools that reason about interface design, synthesis, evaluation, and testing. One of these applications, the automatic synthesis of interface transducers, is highlighted in this dissertation.

An interface transducer is the collection of logic circuitry that connects two compatible circuit interfaces. In general, it includes both synchronous and asynchronous components and must satisfy the timing constraints of both interfaces. Interface transducers are required whenever a custom chip is integrated into a computer system or in general, whenever two circuit blocks need to be connected. Their automatic design can greatly reduce the time required to assemble systems or integrate new components into existing systems.

Janus uses a novel approach, based on a small set of templates, to synthesize mixed asynchronous and synchronous control logic. The synthesis algorithm, called Suture, first constructs a skeletal circuit and then locally modifies the design to meet interface timing constraints and eliminate internal race conditions. Optimizations of the resulting sequential logic yield transducers that are comparable in both size and performance to those generated by experienced designers. Three practical examples are used to demonstrate this result.

A mio padre

#### **ACKNOWLEDGEMENTS**

First and foremost I must thank my advisor, Randy Katz, for taking a chance on me when I first came to Berkeley and helping me get over the rough spots of the last four years. Many thanks also go to the remainder of my dissertation committee Alice Agogino, Alberto Sangiovanni-Vincentelli, Carlo Sequin, and Mark Stefik for their superb guidance and advice.

A special acknowledgement to my friends from my days at the Xerox Palo Alto Research Center: Lynn Conway, Mary Hausladen, Richard Lyon, Alan Paeth, and Mark Stefik. They continuously expanded my horizons and made PARC an incredibly enlightening and exciting place.

The work presented in this dissertation benefitted greatly from many discussions with my friends and colleagues. Among these I must especially thank David Wood, Richard Rudell, David Gedye, and Fred Obermeier for letting me sound them out on many half-baked ideas. To me, my writing still leaves much to be desired. Without the help of David Gedye, Randy Katz, Robert Mayo, and Melissa Westbrook, it may never have become presentable.

My time at Berkeley was made enjoyable and memorable by great friends. They are too numerous for me to include them all, but I must mention Margaret Butler, Gregg Foster, Susan Eggers, David Gedye, Garth Gibson, Mark Hill, James Larus, Robert Mayo, Fred Obermeier, Stuart Sechrest, and David Wood.

My parents, Rosa and Cristoforo, are the best anyone can ever hope to have. They have constantly supported and encouraged me in all my efforts, helping me through my life with their inexhaustable love and affection. I only hope that I may be half as selfless with my own children.

No thanks are enough for my wife, Melissa. Her companionship, love, and support made finishing this work easier and more pleasant than I could have hoped.

And lastly, a special thanks to my son, Cristoforo Samuel, who arrived in time to catch the final moments and put this effort in proper perspective.

#### CONTENTS

| 1. Introduction                                       | 1  |

|-------------------------------------------------------|----|

| 1.1. Circuit Interfaces and their Specification       | 2  |

| 1.1.1. Interface Specification                        | 3  |

| 1.1.2. Applications of the Specifications             | 4  |

| 1.2. Interface Transducer Synthesis                   |    |

| 1.2.1. A Brief Example                                | 5  |

| 1.2.2. Summary of Results                             | 8  |

| 1.3. Organization of this Dissertation                | 9  |

| — PART I —                                            |    |

| 2. Interface Specification                            | 13 |

| 2.1. Circuit Interfaces as Collections of Constraints |    |

| 2.1.1 Logical Constraints                             |    |

| 2.1.2 Timing Constraints                              |    |

| 2.2. Requirements for Interface Specification         |    |

| 2.2.1. Specification of Event Sequences               |    |

| 2.2.2. Co-routine Model for Combination               |    |

| 2.2.3. Expressibility of HDLs                         |    |

| 2.3. Related Specification Work                       |    |

| 2.3.1 Hardware Description Languages                  |    |

| 2.3.2 State Graphs and Petri Nets                     |    |

| 2.3.3 Temporal Logic                                  |    |

| 2.4. Formalized Timing Diagrams — A New Approach      |    |

| 3. Waves                                              | 33 |

| 3.1. A Formalized Timing Diagram Editor               |    |

| 3.2. The Basic Waves Diagram                          |    |

| 3.2.1. The Signal Name Window                         |    |

| 3.2.2. The Trace Window                               |    |

| 3.2.3. The Time Line Window                           |    |

| 3.2.4. The Feedback Window                            |    |

| 3.2.5. The Title Window                               |    |

| 3.2.6. The Waves Icon                                 |    |

| 3.3. Extensions for Interface Specification           |    |

| 3.3.1. Representation of Arbitrary Logic Circuitry    |    |

| 3.3.2. Conditional and Looping Event Sequences        |    |

| 3 3 3 Combination of Diagrams                         |    |

| 3.4. Applications of Waves                           | 49  |

|------------------------------------------------------|-----|

| 3.4.1. Interface Documentation                       | 49  |

| 3.4.2. Interface Design                              |     |

| 3.4.3. Simulation and Testing                        |     |

| 3.4.4. Synthesis of Interface Circuitry              |     |

| — PART II —                                          |     |

|                                                      |     |

| 4. Transducer Synthesis                              |     |

| 4.1. Interface Transducers                           |     |

| 4.1.1. Interface Operations                          | 58  |

| 4.1.2. Specification of Transducer Behavior          |     |

| 4.1.3. Automatic Synthesis of Transducers            | 60  |

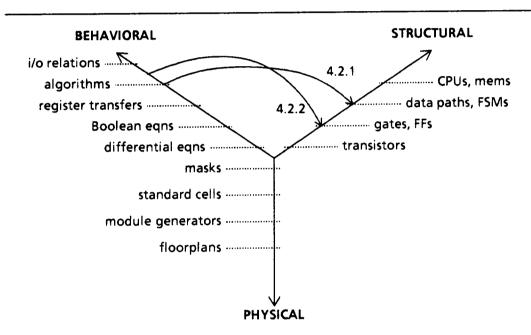

| 4.2. Related Synthesis Work                          | 62  |

| 4.2.1. Synthesis from Algorithmic Specifications     |     |

| 4.2.2. Synthesis from Input/Ouput Specifications     | 68  |

| 4.3. Suture — A New Synthesis Method                 |     |

| 4.3.1. Overview of the Method                        |     |

| 4.3.2. Examples of its Application                   | 77  |

| 5. Janus                                             | 87  |

| 5.1. A Synthesis Tool for Interface Transducers      |     |

| 5.1.1. Specification Using Waves Diagrams            | 89  |

| 5.1.2. Limitations of the Implementation             | 90  |

| 5.2. Generation of the Event Graphs                  | 92  |

| 5.2.1. Merge Points                                  | 93  |

| 5.2.2. Intervals of Occurance                        | 93  |

| 5.2.3. Interconnection of Operation Graphs           |     |

| 5.2.4. Timing Constraint Translations                | 97  |

| 5.2.5. Compression of Synchronous Events             |     |

| 5.2.6. Splitting of Signals                          |     |

| 5.2.7. Extraneous Events                             |     |

| 5.3. Synthesis of the Data Path Circuitry            |     |

| 5.3.1. Data Transfers Through the Transducer         |     |

|                                                      |     |

| 5.3.2. Multiplexed Data Transfer Paths               |     |

| 5.4. Synthesis of the Control Circuitry              |     |

| 5.4.1. Synthesis of the Skeletal Circuit             |     |

| 5.4.2. Local Corrections for Constraint Satisfaction |     |

| 5.4.3. Local Corrections for Race Elimination        |     |

| 5.5. Extensions for Conditionals and Loops           |     |

| 5.6. Logic Optimization                              |     |

| 5.6.1. Merging Across Operations                     |     |

| 5.6.2. Sequential Logic Optimizations                | 111 |

#### - CONCLUSION -

| 6. Conclusions and Contributions               | 115 |

|------------------------------------------------|-----|

| 6.1. Summary of Contributions                  | 116 |

| 6.1.1. Interface Specification                 | 116 |

| 6.1.2. Transducer Synthesis                    | 117 |

| 6.2. Directions for Future Research            | 119 |

| 6.2.1. Interface Specification                 | 119 |

| 6.2.2. Application of Interface Specifications | 120 |

| 6.2.3. Transducer Synthesis                    | 120 |

| 6.2.4. Summary                                 |     |

| 6.3. Closing Comments                          | 123 |

| - APPENDICES -                                 |     |

| A. Waves Implementation                        | 127 |

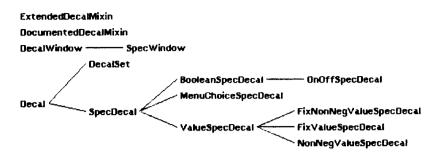

| A.1. Implementation Medium                     | 128 |

| A.2. Decal Windows                             |     |

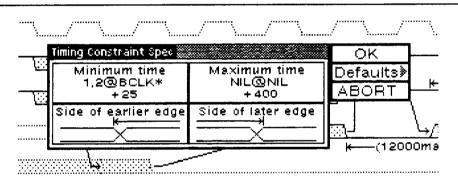

| A.3. Specification Dialog Windows              | 132 |

| A.4. Constraint Checking                       | 135 |

| A.5. Diagram Editing Support                   | 137 |

| A.6. Diagram Regions                           | 139 |

| A.7. Waves Object Classes                      |     |

| A.8. Portability Issues                        | 143 |

| B. Waves Specification Examples                | 145 |

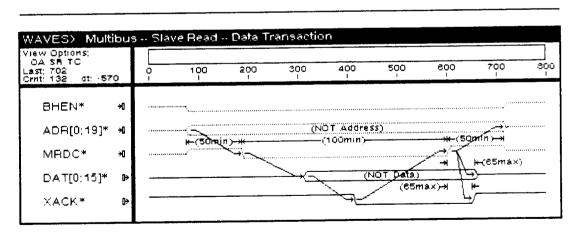

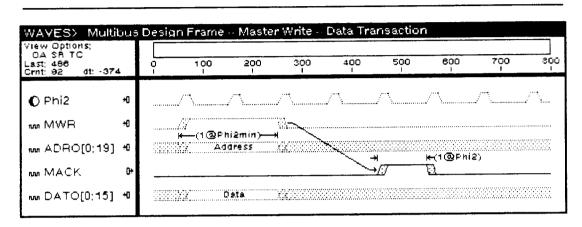

| B.1. The Intel Multibus                        | 146 |

| B.1.1. Slave Read                              | 146 |

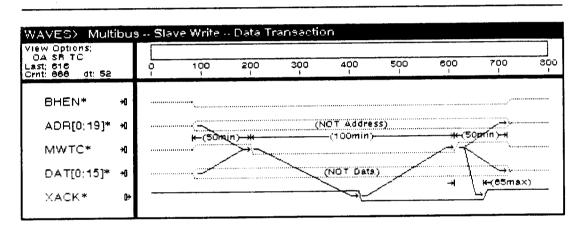

| B.1.2. Slave Write                             | 147 |

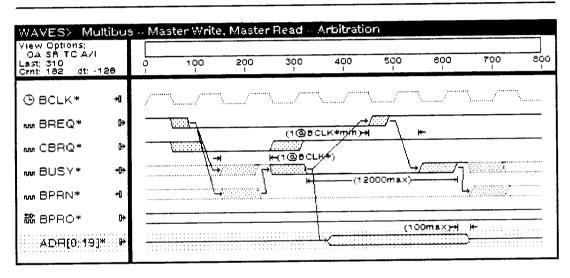

| B.1.3. Arbitration                             | 148 |

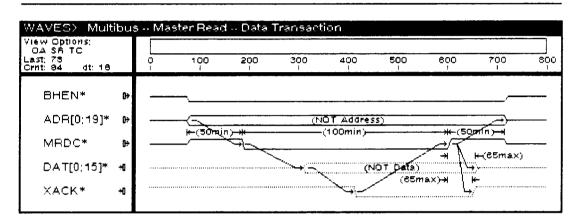

| B.1.4. Master Read                             | 149 |

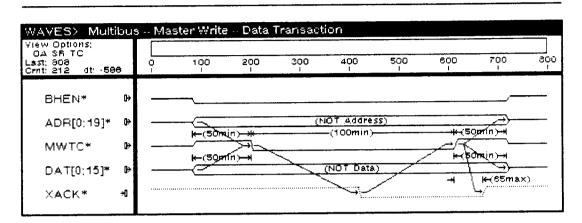

| B.1.5. Master Write                            | 150 |

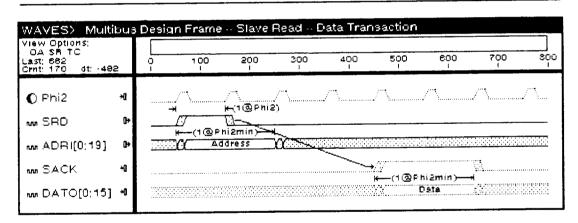

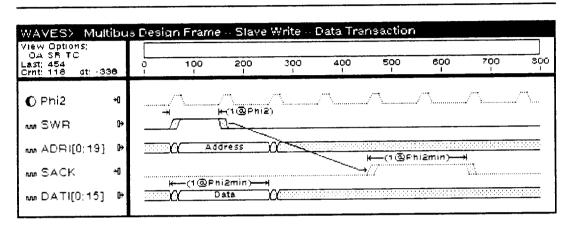

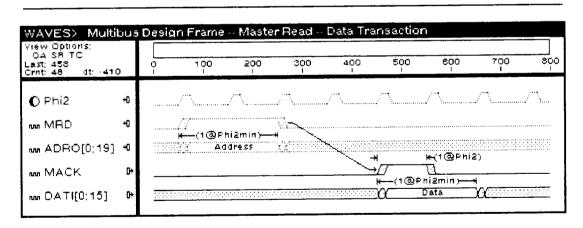

| B.2. The Multibus Design Frame                 | 151 |

| B.2.1. Slave Read                              | 151 |

| B.2.2. Slave Write                             | 152 |

| B.2.3. Master Read                             |     |

| B.2.4. Master Write                            |     |

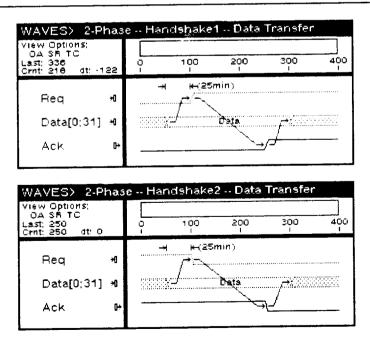

| B.3. 2-Phase and 4-Phase Protocols             |     |

| B.3.1. 2-Phase Protocol                        |     |

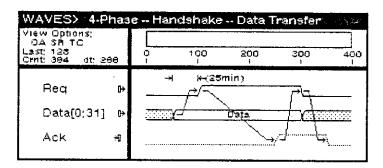

| B.3.2. 4-Phase Protocol                        | 155 |

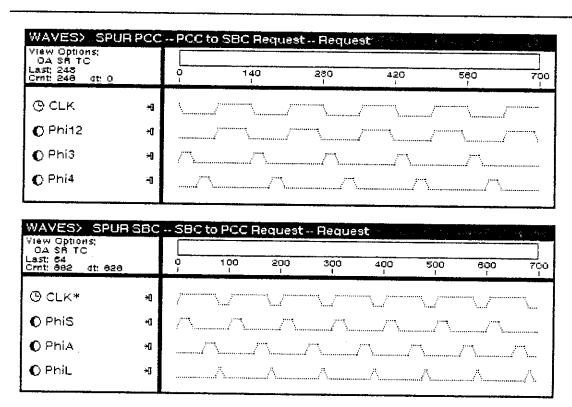

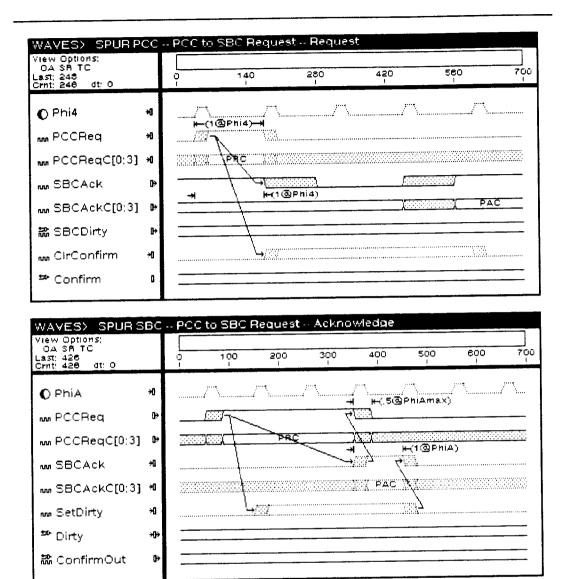

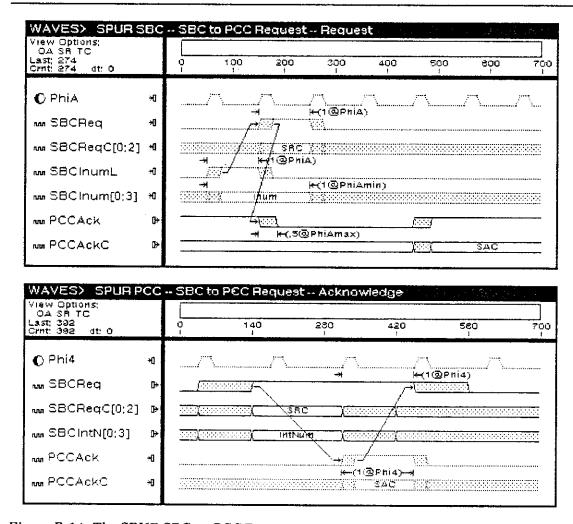

| B.4. SPUR PCC-SBC Interface                                                | 156 |

|----------------------------------------------------------------------------|-----|

| B.4.1. Clock Signals                                                       |     |

| B.4.2. PCC to SBC Request                                                  | 157 |

| B.4.3. SBC to PCC Request                                                  | 159 |

| B.4.4. Cache Handshaking                                                   | 160 |

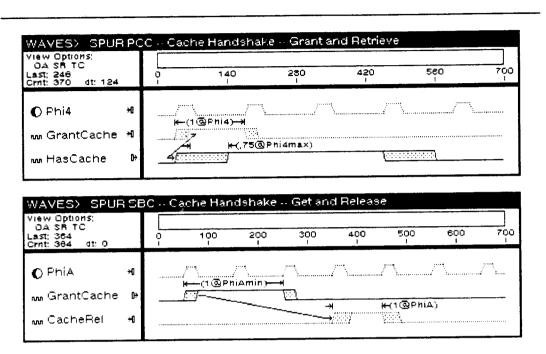

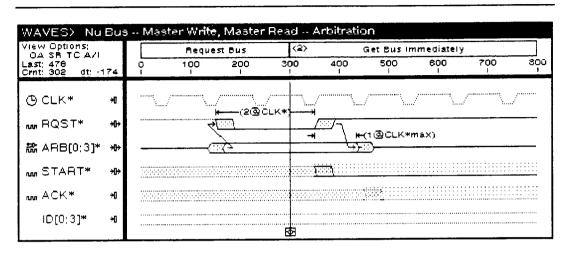

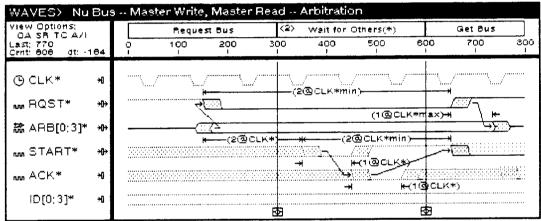

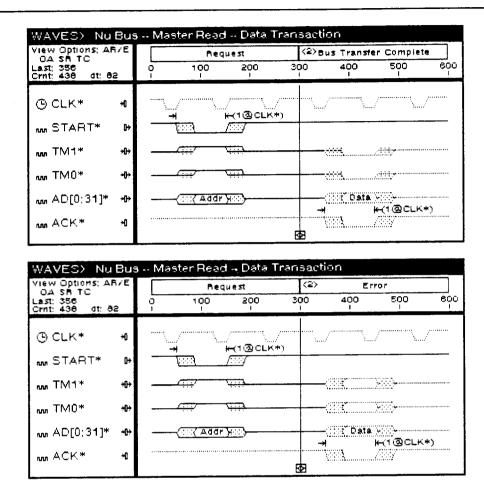

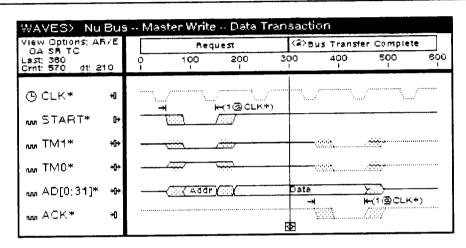

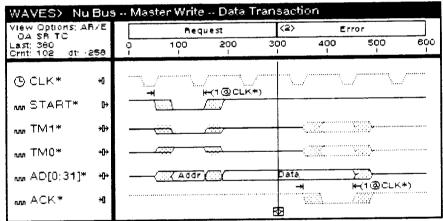

| B.5. The Texas Instruments NuBus                                           | 161 |

| B.5.1. Arbitration                                                         |     |

| B.5.2. Master Read                                                         | 162 |

| B.5.3. Master Write                                                        |     |

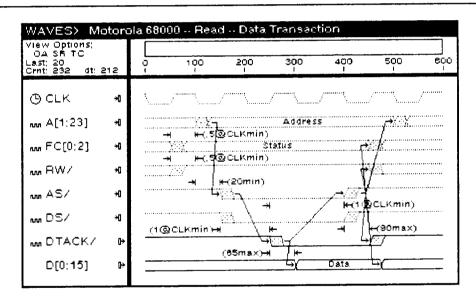

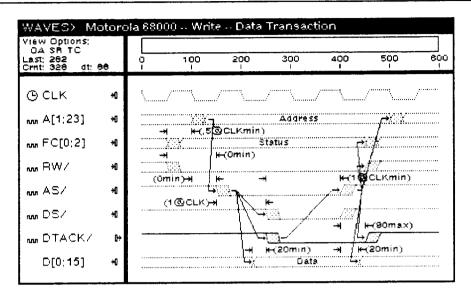

| B.6. The Motorola 68000                                                    |     |

| B.6.1. Read                                                                | 165 |

| B.6.2. Write                                                               | 166 |

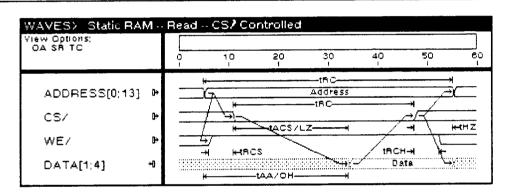

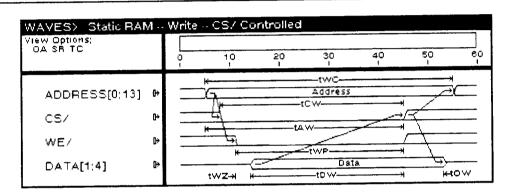

| B.7. Static RAM                                                            |     |

| B.7.1. Read                                                                |     |

| B.7.2. Write                                                               |     |

| C. Janus Implementation                                                    | 169 |

| C.1. Janus Object Classes                                                  |     |

| C.2. Validation of Input Specifications                                    | 172 |

| C.3. Event Graph Browser                                                   | 173 |

| C.4. Representation of the Circuit Library                                 | 175 |

| C.5. Simulation and Validation                                             | 177 |

| C.6. Portability Issues                                                    | 178 |

| D. Janus Synthesis Examples                                                | 179 |

|                                                                            |     |

| D.1. The Multibus Design Frame                                             | 180 |

| D.1.1. Event Graphs                                                        |     |

| D.1.2. Janus and Designer Generated Circuits                               |     |

| D.1.3. Summary and Comparison                                              |     |

| D.2. 2-Phase to 4-Phase Protocol Adapter                                   | 103 |

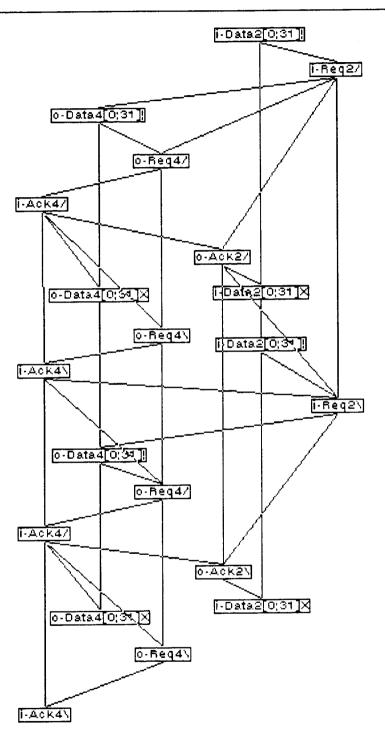

| D.2.1. Event Graph                                                         |     |

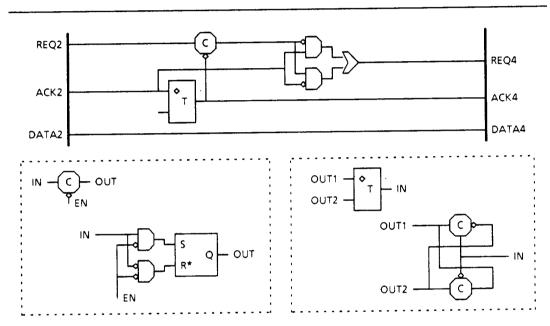

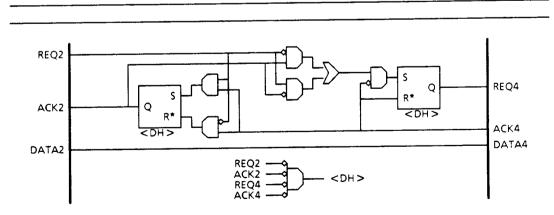

| D.2.2. Janus and Designer Generated Circuits                               |     |

| D.2.3. Summary and Comparison                                              |     |

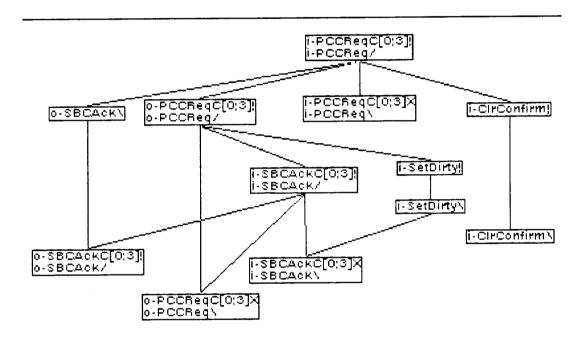

| D.3. SPUR PCC-SBC Interface                                                |     |

| D.3.1. Event Graphs                                                        | 109 |

| D.3.2. Janus and Designer Generated Circuits D.3.3. Summary and Comparison |     |

|                                                                            |     |

| References                                                                 |     |

| Part I                                                                     |     |

| Part II                                                                    | 204 |

| Ammandiaaa                                                                 | ZUC |

#### **FIGURES**

| 1.1.                  | An Example Waves Specification                          | 6  |

|-----------------------|---------------------------------------------------------|----|

| 1.2.                  | An Example Synthesized Transducer                       | 7  |

| 2.1.                  | Excerpts from the Intel Multibus Specification          |    |

| 2.2.                  | SLIDE Multibus Master Read Specification                | 22 |

| 2.3.                  | BSI/ISPS Multibus Master Read Specification             |    |

| 2.4.                  | ADAM Multibus Master Read Specification                 |    |

| 2.5.                  | I-net Multibus Master Read Specification                |    |

| 2.6.                  | CCS Multibus Master Read Specification                  | 27 |

| 2.7.                  | Temporal Logic Multibus Master Read Specification       |    |

| 2.8.                  | Regural Expression Multibus Master Read Specification   |    |

| 2.9.                  | Formalized Timing Diagram Specification                 | 32 |

| 3.1.                  | A Sample Waves Diagram                                  |    |

| <b>3</b> . <b>2</b> . | A Signal Name Window                                    |    |

| 3.3.                  | A Trace Window                                          |    |

| 3.4.                  | A Time Line Window                                      |    |

| 3.5.                  | A Feedback Window                                       |    |

| 3.6.                  | A Title Window                                          |    |

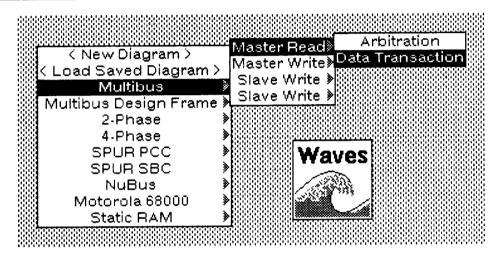

| 3.7.                  | The Waves Icon and Diagram Menu                         |    |

| 3.8.                  | A Diagram with a Computed Signal                        |    |

| 3.9.                  | The Waves Boolean Expression Menu                       |    |

| 3.10.                 | A Diagram with Looping and Conditional Segments         |    |

| 3.11.                 | A Time Line Window with Nested Segments                 |    |

| 3.12.                 | An Example of Diagram Combination                       |    |

| 3.13.                 | Compatibility of Synchronous Waveforms                  | 51 |

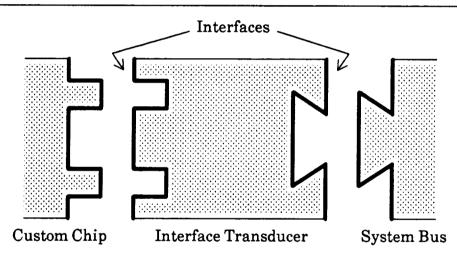

| 4.1.                  | An Interface Transducer                                 |    |

| 4.2.                  | A Y-Chart for Transducer Synthesis                      |    |

| 4.3.                  | BSI/ISPS Specification for an Example Transducer        |    |

| 4.4.                  | Scheduled VT-bodies for the Specification of Figure 4.3 |    |

| 4.5.                  | Synthesized Circuit for the Example of Figure 4.3       |    |

| 4.6.                  | STG Specification for an Example Control Circuit        |    |

| 4.7.                  | Synthesized Circuit for the Example of Figure 4.6       |    |

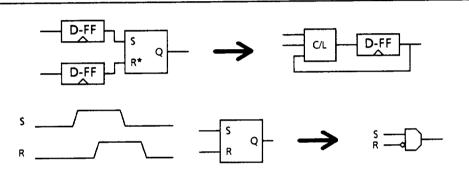

| 4.8.                  | Circuit Templates Used by the Suture Method             |    |

| 4.9.                  | Examples of Sequential Logic Transformations            |    |

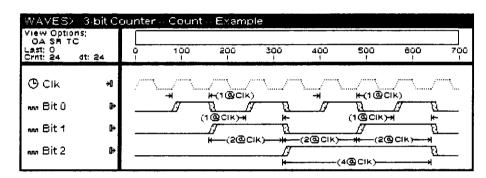

| 4.10.                 | Waves Specification for a Three-Bit Counter             |    |

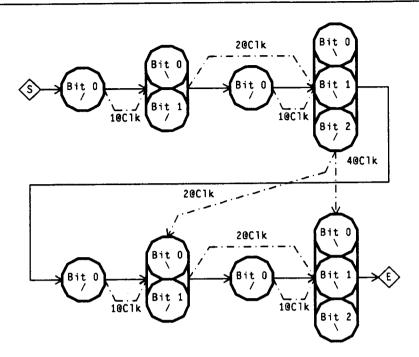

| 4.11.                 | Event Graph for the Counter of Figure 4.9               |    |

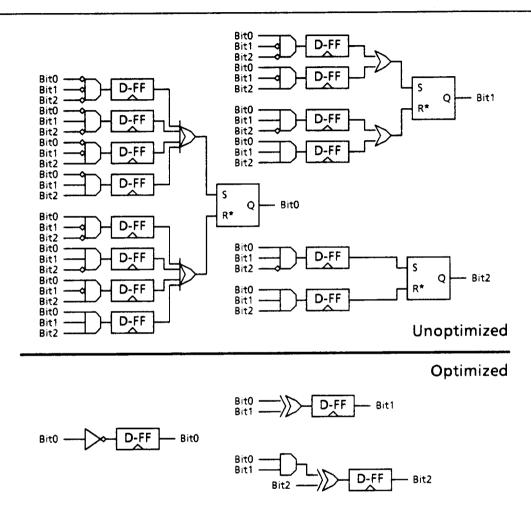

| 4.12.                 | Circuit Synthesized by Suture from Graph of Figure 4.9  |    |

| 4.13.                 | Waves Specification of the Example of Figure 4.6        | 80 |

| 4.14.        | Event Graph for the Example of Figure 4.13              | 80  |

|--------------|---------------------------------------------------------|-----|

| 4.15.        | Circuit Synthesized by Suture from Graph of Figure 4.14 | 81  |

| 4.16.        | Waves Specification of the Transducer of Figure 4.3     | 82  |

| 4.17.        | Event Graph for the Example of Figure 4.16              | 83  |

| 4.18.        | Circuit Synthesized by Suture from Graph of Figure 4.17 | 84  |

| 5.1.         | A Y-chart for Janus                                     |     |

| <b>5.2</b> . | The Janus Icon and Menu                                 |     |

| 5.3.         | A Janus Interface Transducer Icon                       |     |

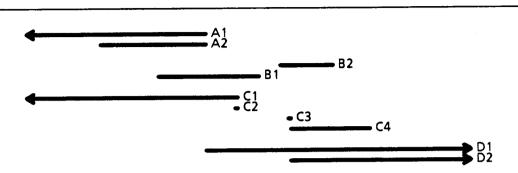

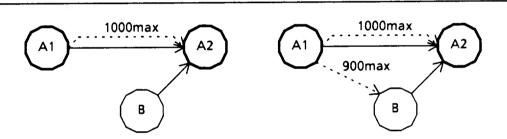

| <b>5.4</b> . | Example of Intervals of Occurrence                      |     |

| 5.5.         | Interconnection of Event Graphs                         |     |

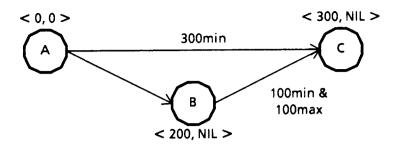

| 5.6.         | Example of Timing Constraint Translation                |     |

| 5.7.         | A Specification of Compressible Synchronous Events      |     |

| 5.8.         | Template Changes for Compressible Events                |     |

| 5.9.         | Splitting of a Tri-statable Signal                      |     |

| 5.10.        | A Multiplexed Data Transfer Path                        |     |

| 5.11.        | The Implementation of an Output Signal Latch            |     |

| 5.12.        | Addition of Timing Constraint to Improve Checking       | 106 |

| A.1.         | The Decal Window Object Class Inheritance Lattice       |     |

| A.2.         | A Specification Dialog Window                           |     |

| A.3.         | Examples of Constraint Violations                       |     |

| A.4.         | Waves Diagram Scrolling                                 |     |

| A.5.         | Waves Diagram Regions                                   |     |

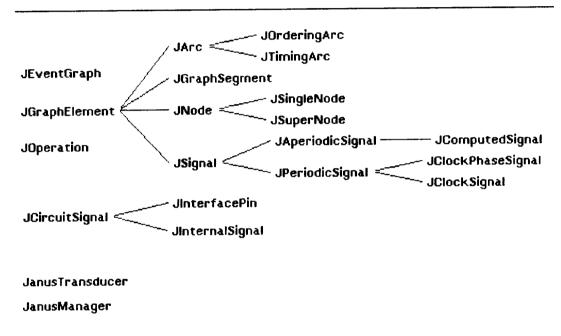

| A.6.         | Waves Object Class Inheritance Lattice                  | 141 |

| B.1.         | The Multibus Slave Read Operation                       |     |

| B.2.         | The Multibus Slave Write Operation                      |     |

| B.3.         | The Multibus Arbitration Sequence                       |     |

| <b>B</b> .4. | The Multibus Master Read Operation                      |     |

| B.5.         | The Multibus Master Write Operation                     |     |

| B.6.         | The Multibus Design Frame Slave Read Operation          |     |

| B.7.         | The Multibus Design Frame Slave Write Operation         |     |

| B.8.         | The Multibus Design Frame Master Read Operation         |     |

| B.9.         | The Multibus Design Frame Master Write Operation        |     |

| B.10.        | The 2-Phase Protocol                                    |     |

| B.11.        | The 4-Phase Protocol                                    |     |

| B.12.        | The SPUR PCC and SBC Clock Signals                      |     |

| B.13.        | The SPUR PCC-to-SBC Request Operation                   |     |

| B.14.        | The SPUR SBC-to-PCC Request Operation                   |     |

| B.15.        | The SPUR PCC-SBC Cache Handshaking Operation            |     |

| B.16.        | The NuBus Arbitration Sequence                          |     |

| B.17.        | The NuBus Master Read Operation                         | 163 |

| B.18. | The NuBus Master Write Operation                     | 164 |

|-------|------------------------------------------------------|-----|

| B.19. | The Motorola 68000 Read Operation                    | 165 |

| B.20. | The Motorola 68000 Write Operation                   | 166 |

| B.21. | The Lattice Logic SR64K4-35 Read Operation           | 167 |

| B.22. | The Lattice Logic SR64K4-35 Write Operation          | 168 |

| C.1.  | Janus Object Class Inheritance Lattice               | 170 |

| C.2.  | Janus Event Graph Browser                            | 174 |

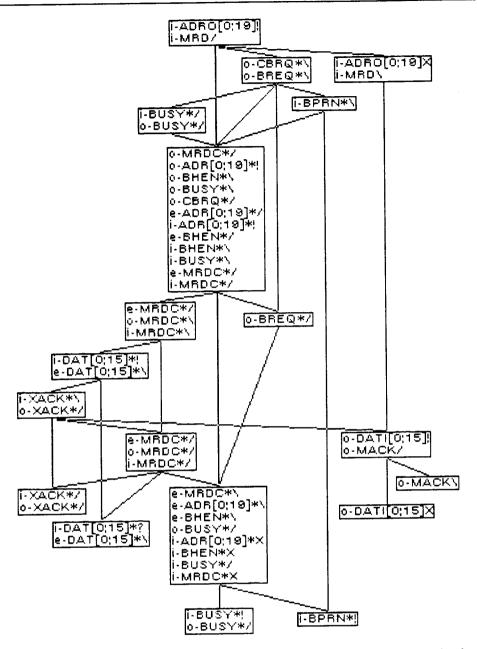

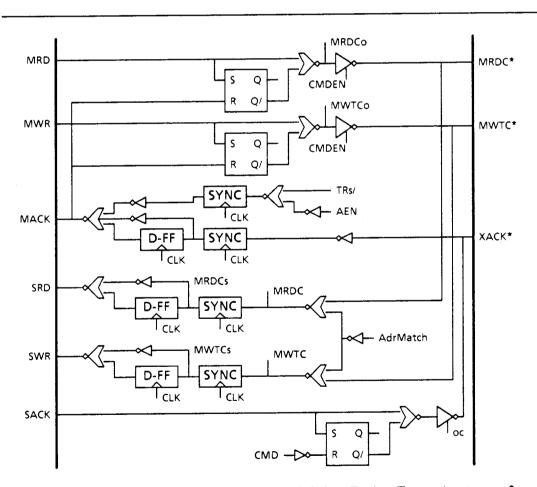

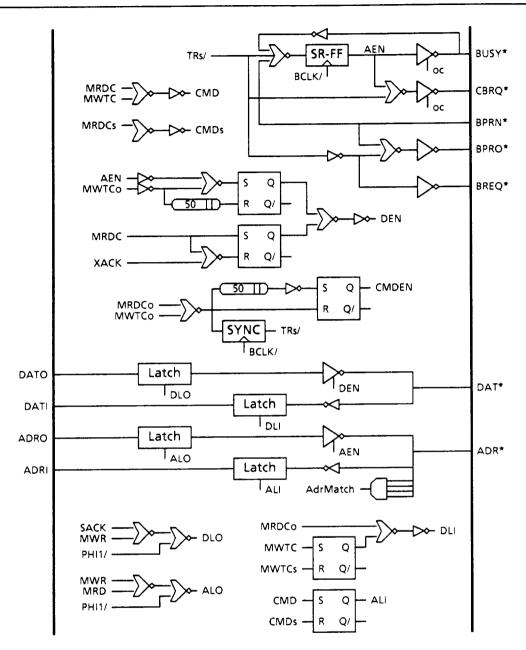

| D.1.  | Event Graph for the Slave Read Operation of MDF      |     |

| D.2.  | Event Graph for the Slave Write Operation of MDF     |     |

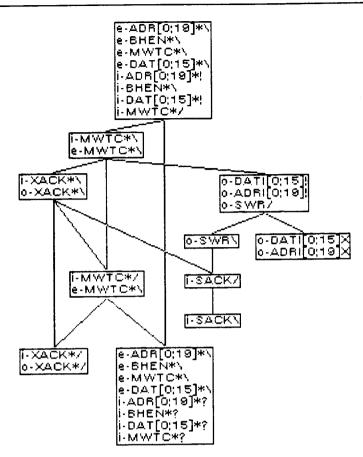

| D.3.  | Event Graph for the Master Read Operation of MDF     |     |

| D.4.  | Event Graph for the Master Write Operation of MDF    |     |

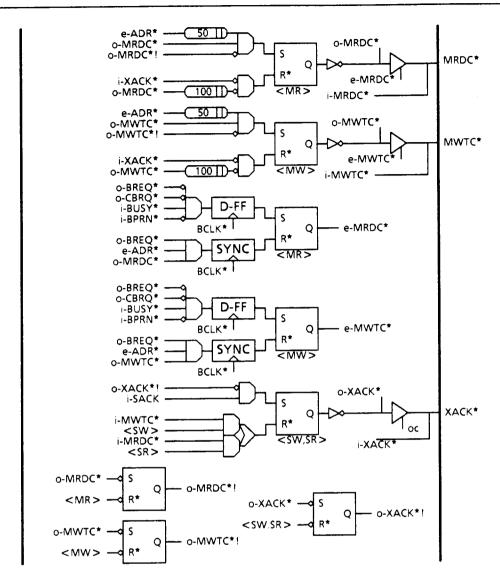

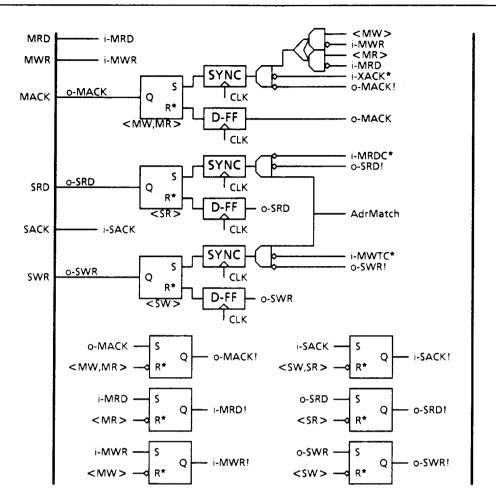

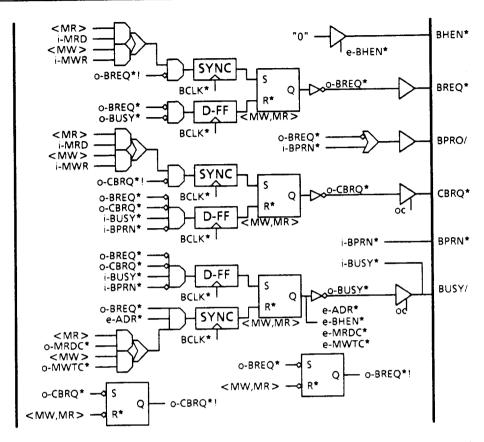

| D.5.  | Manually Designed Circuit for MDF (Part I)           |     |

| D.6.  | Manually Designed Circuit for MDF (Part II)          |     |

| D.7.  | Janus Designed Circuit for MDF (Part I)              |     |

| D.8.  | Janus Designed Circuit for MDF (Part II)             |     |

| D.9.  | Janus Designed Circuit for MDF (Part III)            |     |

| D.10. | Janus Designed Circuit for MDF (Part IV)             | 189 |

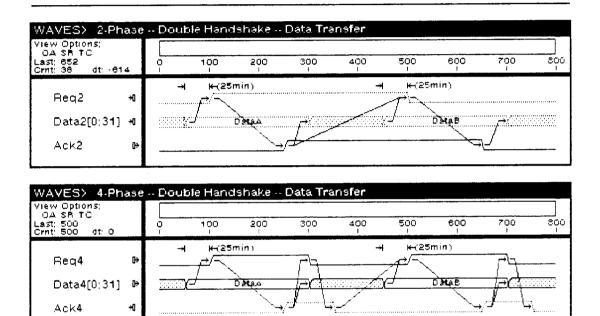

| D.11. | Waves Diagrams for Double Handshake Operation        |     |

| D.12. | Event Graph for the Double Handshake Operation       | 193 |

| D.13. | Manually Designed Circuit for Protocol Adapter       | 194 |

| D.14. | Janus Designed Circuit for Protocol Adapter          | 194 |

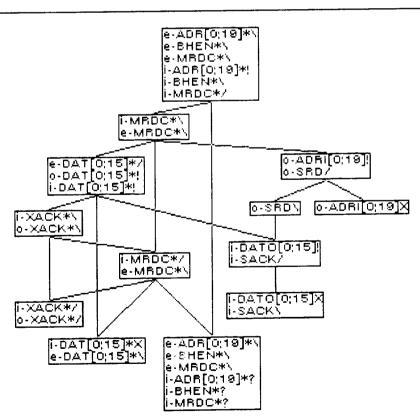

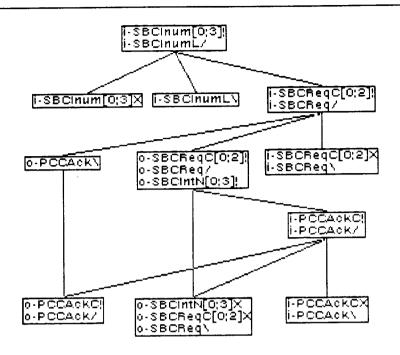

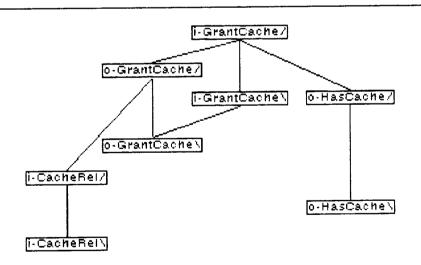

| D.15. | Event Graph for the PCC-to-SBC Request Operation     |     |

| D.16. | Event Graph for the SBC-to-PCC Request Operation     | 197 |

| D.17. | Event Graph for the Cache Handshaking Operation      | 197 |

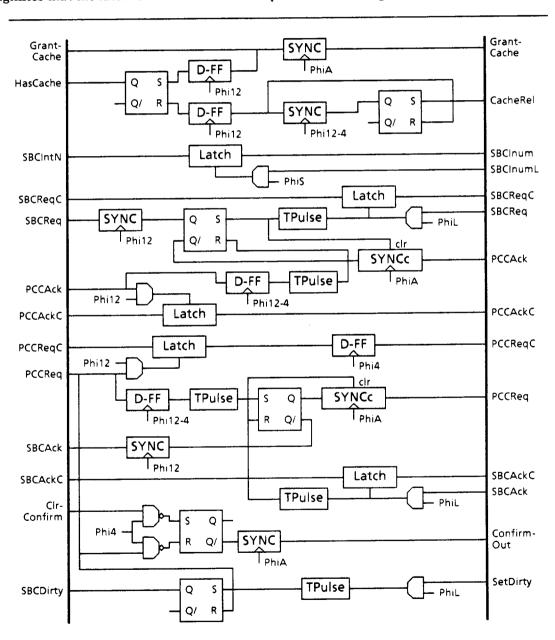

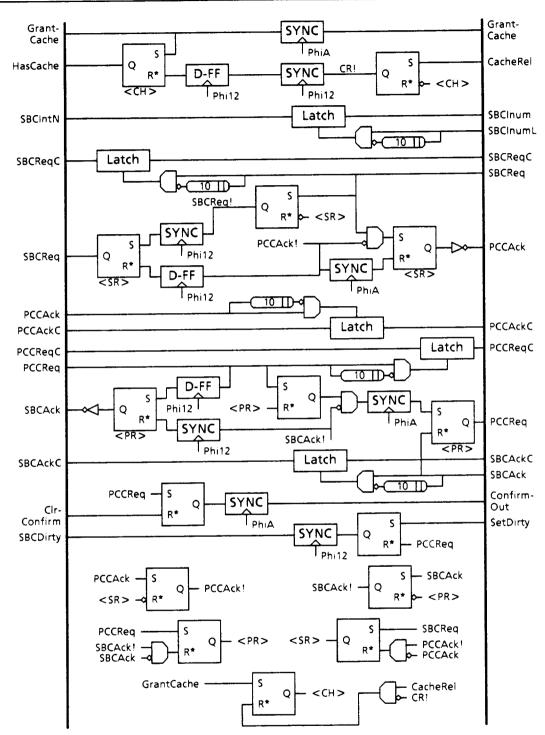

| D.18. | Manually Designed Circuit for SPUR PCC-SBC Interface | 198 |

| D.19. | Janus Designed Circuit for SPUR PCC-SBC Interface    | 199 |

|       | TABLES                                               |     |

| 1.1.  | Comparison of Janus and Experienced Designers        | 8   |

| 2.1.  | Classification of Timing Constraints                 | 16  |

| 5.1.  | Time Interval Update for Neighboring Nodes           | 95  |

| D.1.  | Comparison of Circuits for Multibus Design Frame     |     |

| D.2.  | Comparison of Circuits for Protocol Adapter          | 195 |

| D.3.  | Comparison of Circuits for SPUR PCC-SBC Interface    | 200 |

Introduction 1

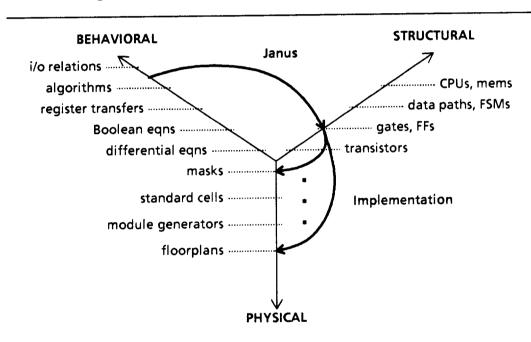

Circuit interfaces are an important design abstraction. However, although they are critical to both circuit function and performance, there has been little work by the computer-aided design (CAD) community that directly addresses issues of circuit interface specification and design. An appropriate specification methodology can elevate circuit interfaces to first-class design objects alongside circuit logic and serve as the foundation for an entirely new class of CAD tools for interface design. In this dissertation, I develop an interface specification methodology and demonstrate its utility by automating the logic design of interface transducers, the glue logic that connect two interfaces together. The automatic generation of these circuits required the development of new synthesis algorithms that handle both synchronous and asynchronous circuits and timing constraints on their operation.

This chapter is divided into three sections. In the first section, I will introduce the special nature of circuit interfaces and discuss why a specification method that emphasizes the properties of circuit interfaces is needed. The section makes a case for a specification method that emphasizes the properties of circuit interfaces and describes the of use of the specifications in interface CAD tools. The second section outlines one of these applications, the automatic synthesis of interface transducers. It highlights the novel features of the synthesis algorithms developed for this class of circuits and uses a small transducer example to illustrate the form of the initial specification and the resulting logic circuit. A table of results on larger examples shows that the synthesized circuits are comparable in both size and performance to those generated by experienced designers. The third section concludes the chapter with some notes on the organization of the remainder of this dissertation.

A circuit logic block is typically defined by its internal hardware, the logic gates and storage elements that determine the circuit's function. However, this *internal* view is only part of a complete definition. The other, complementary part, is how the circuit is viewed by surrounding circuitry through its *interface*, the signal wires that cross the boundary of the logic block. This *external* view of the circuit is a collection of *constraints* on these signal wires.

No formal or generally accepted definition of a circuit interface exists. In the context of this dissertation, a circuit interface is simply a collection of sets of constraints on the signal wires that cross the periphery of a logic block. Each set corresponds to an interface operation, a semantic entity that consists of a sequence of events, the changes in logic level, that represents the exchange of information (i.e., communication) with the circuit's environment. The interface is not concerned with the semantic meaning of the operations but only with the events that must occur and the data that must be transferred. It is also independent of the interface circuitry, the internal logic that may use the signals as inputs or generate them as outputs.

The design of circuit interfaces and interface circuitry is as important as the design of internal circuit logic. A circuit interface can be viewed as a contract between a circuit and its environment. If the contract is not met, then the circuit will not be able to communicate with its surroundings and will be useless. If the contract is not met well, then communication might not proceed fast enough to be practical.

The interface designer must try to define an interface contract, embodied by the interface constraints, that can be met easily and efficiently, with a minimum amount of overhead on the size and complexity of the internal circuitry. Since for a given interface there can be many possible internal implementations that meet the constraints, the interface circuitry designer must try to find an implementation of the interface circuitry that is efficient in both the technology used to realize the logic and in the way it complies with the interface contract. Communication across the interface may proceed faster or slower depending on how the constraints are met.

Therefore, interface specification is the description of the constraints on the interface signals. These constraints take many forms that range from the behavioral level — focusing on the sequencing of events — to the details of electrical requirements and proper physical packaging and connections. Traditional hardware description languages are inadequate for interface specification. They emphasize the description of logic circuits and their physical realization in hardware and usually do not provide mechanisms for the specification of abstract constraints.

Circuit interfaces actually have more general applicability than circuit logic. By definition every logic circuit has an interface, however, a circuit interface can exist independently of any logic blocks. Bus structures are a common example of a system component with an interface

but no associated circuitry. A bus specification is solely a collection of constraints and there may not be any associated logic circuitry.

#### **Interface Specification**

1.1.1

Interface specifications provide information that is complementary to circuit specification. The interface description of a logic block can be used to generate stimulus vectors for simulators and testers, to verify that two blocks to be connected are compatible, to automatically generate interface circuitry, and to document a design.

Although interface specification is clearly important and many useful tools could be developed to help designers deal with interface issues, there has been little work in the area of interface specification. Most attempts have fallen into one of three categories: extensions to existing hardware description languages (HDLs), the adaptation of Petri nets and other state graphs, and temporal logic specifications.

Each category has its own disadvantages. Because HDLs concentrate on circuit function many interface constraints can become embedded in the logic description. If interface details are not explicitly factored out, it is difficult, if not impossible, to exploit the interface specification for design. Specialized languages have been developed for asynchronous interfaces, an aspect missing from many HDLs, but these languages are usually awkward for synchronous interfaces. Petri nets have also been used to specify asynchronous behavior and sequencing of events but usually ignoring timing constraints. Temporal logic offers a more formal methodology that unfortunately becomes extremely cumbersome when timing constraints are introduced. A problem common to all the categories is the unfamiliarity of designers with the specification language and its idiosyncracies. These approaches are described in more detail in section 2.3.

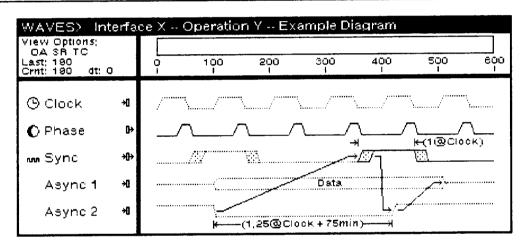

What is needed is a specification method that covers both synchronous and asynchronous circuits, can handle timing information, is natural and concise for designers to use and, most importantly, stresses the specification of interface constraints over the specification of logic circuitry. In this dissertation, I describe such a method based on timing diagrams.

Timing diagrams are a familiar form of specification for logic designers. The major components of timing diagrams — the shapes of the waveforms and the timing constraints between the changes in logic level — properly emphasize the most important aspects of circuit interfaces. If the diagrams can be formalized to include all the information necessary for interface specifications, then they can provide just the specification method required.

The Waves timing diagram editor provides this formalization. It is an interactive editor that directly supports the many types of timing constraints encountered in interface specifications. The editor informs the user of any constraint violations in the drawn waveforms and has application in interface design and documentation as well as specification.

Circuit interface specifications form a foundation upon which tools that reason about interface issues can be built. The classes of tools range from documentation and exploratory design aids to automatic interface design and synthesis tools and are useful through all stages of the design process from initial evaluation through integration and testing.

Waves diagrams are an excellent medium for communicating with interface CAD tools. The diagrams are not only familiar to designers, they also provide dialogue and error reporting capabilities between the user and the tools. Signal events and constraints can be highlighted on the diagrams rather than directing the designer to the object of interest through textual cues in an HDL. The two dimensional nature of the diagrams is also a better match for expressing the constraints between signal waveforms than a linear HDL program.

In the early stages of design, Waves diagrams are a spreadsheet-like tool for experimenting with prototypes of the interface specification. An initial sketch of the desired waveforms can be drawn and timing constraints attached to events. Then the designer can vary the positions of some events and see if any timing constraints are violated. The period (or duty cycle) of a clock can be changed to view the effect of different system timing schemes. This is especially helpful when there are interactions with asynchronous signals to consider.

If an interface specification is associated with all system components, then whenever two blocks are to be connected their interfaces can be checked for compatibility. This is an important capability when members of a large design team are simultaneously working on different parts of the design. Slight inconsistencies in circuit connections are a common cause of design bugs.

This leads to a set of tools that can handle incompatibilities and modify or add circuitry to correct the problem. One such tool is an interface transducer synthesizer. An interface transducer is the glue logic that connects two circuit blocks. Glue logic is common in most systems and especially in those with many components at high levels of integration. Automatic synthesis of interface transducer logic can greatly reduce the design effort in integrating a new custom chip into an existing environment. This enables the rapid prototyping of system components, their evaluation in-situ, and their faster introduction into the marketplace.

Finally, tools that deal with simulation and testing issues are made possible. Today, when a chip is tested or a simulation performed the collected output vectors are compared to a sequence of expected vectors. However, this is not the real objective of the test. Rather, we test to determine whether the changes in logic level on the output vectors meet the ordering and timing constraints on the events of the interface, not whether they precisely match one of many possible sequences of acceptable expected outputs. Timing diagrams can be used to directly generate input vectors and then verify that the output vectors do actually meet the constraints.

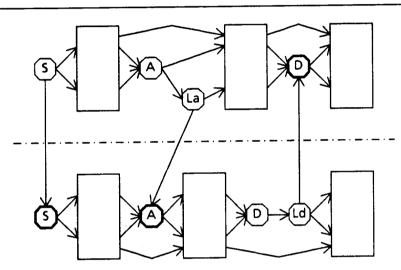

The application of circuit interface specifications highlighted in this dissertation is the automatic synthesis of interface transducers. Transducers require synthesis methods that differ in two important ways from current methods. First, they need to be able to handle the design of both synchronous and asynchronous components. And second, the synthesized circuits must respect interface timing constraints.

The tool I implemented to perform this task is called Janus. Two interface specifications, in the form of collections of Waves diagrams, are provided as input to Janus. It then generates a specification of the sequential logic that will implement the connection between the two interfaces. Future tools to be integrated with Janus, will use Waves diagrams to interact with the user during the synthesis process and to compose simulator commands to validate the generated circuitry.

The control logic synthesis algorithm in Janus is called Suture and it differs from classical synthesis algorithms in several ways. First, in the early states of synthesis, synchronous and asynchronous signals are treated in exactly the same fashion. Second, rather than attempting to generate a correct circuit directly, the Suture algorithm constructs a skeletal circuit that may have timing constraint violations and race conditions. Later passes over the circuit correct these problems. Lastly, there is no attempt to generate a dense circuit in the early stages of the algorithm, rather, local transformations are used to reduce the size of the sequential logic once a correct circuit has been generated.

Janus prepares the input to Suture. An event graph is derived from the Waves diagrams of the interface specifications. Janus interconnects the graphs, based on data transfer through the transducer, and calles the Suture algorithm as a subroutine. The transducer is designed piecemeal, a complete logic block is separately generated for each interface operation. Janus then combines and optimizes the resulting circuitry into a single circuit.

### A Brief Example 1.2.1

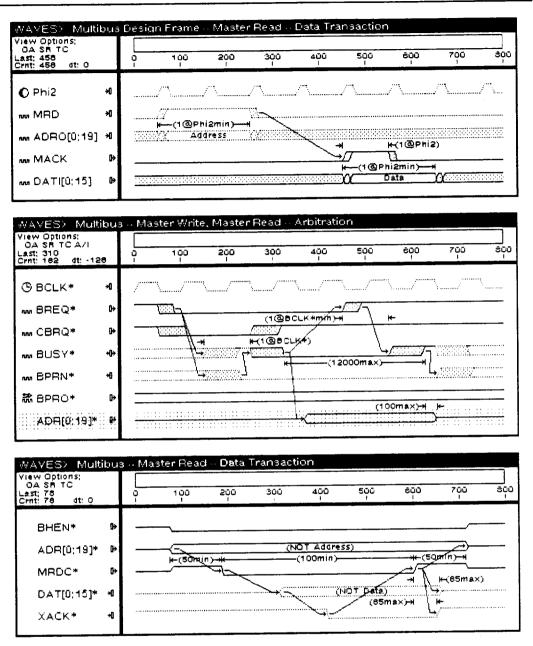

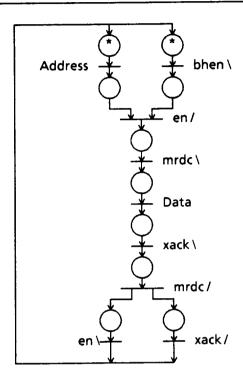

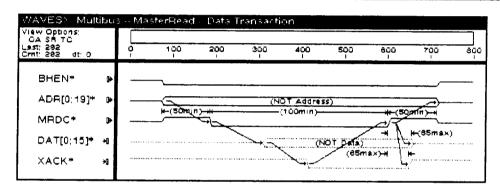

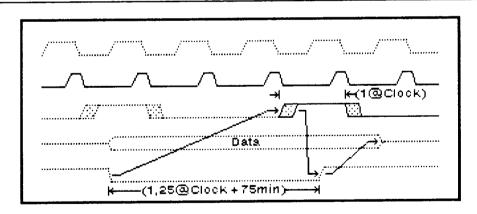

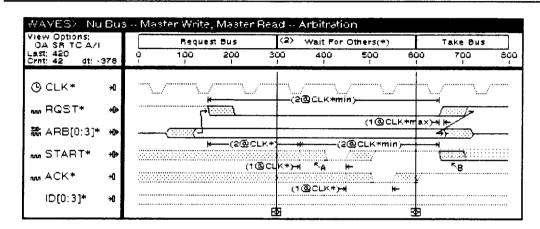

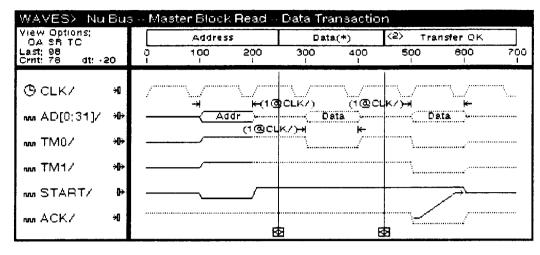

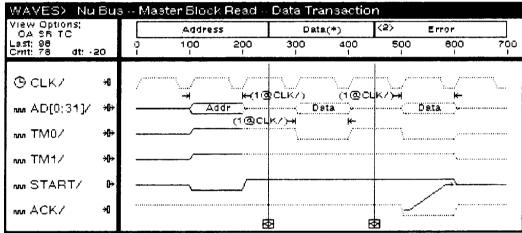

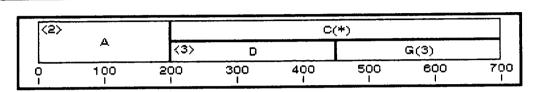

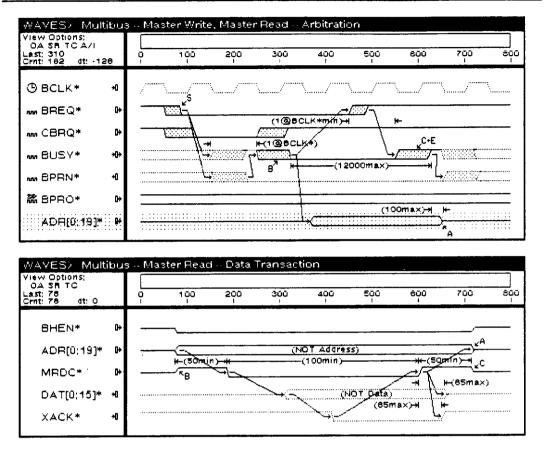

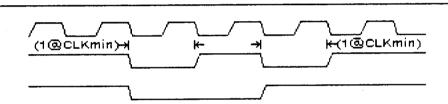

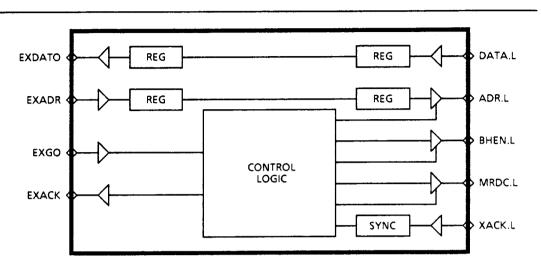

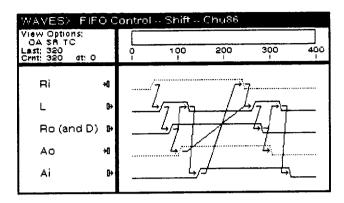

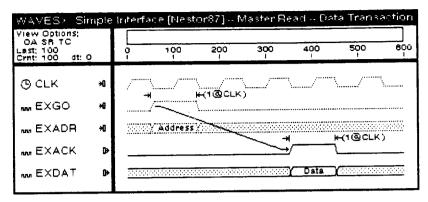

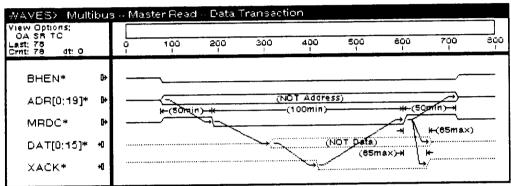

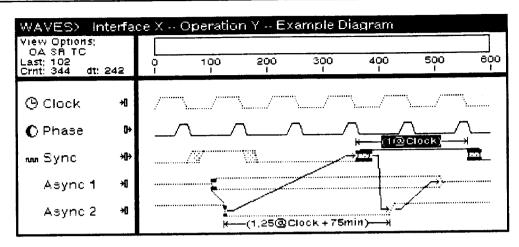

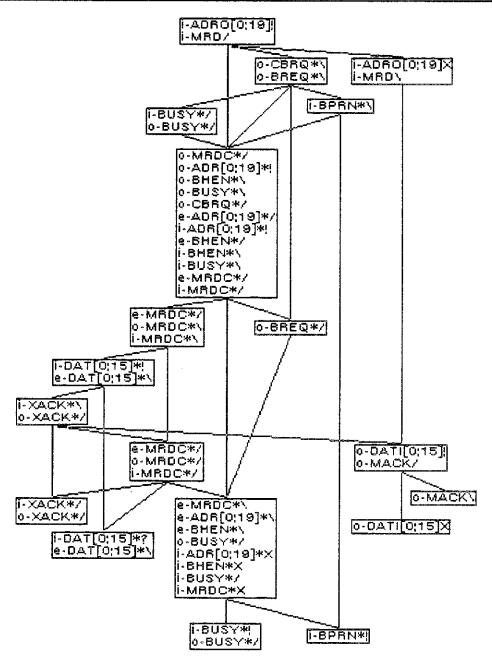

An example of the use of Waves and Janus is the problem of connecting a synchronous microprocessor to an asynchronous system bus. Figure 1.1 shows three Waves diagrams that are part of the transducer specification. The first diagram describes the read operation as it is seen at the the interface of the microprocessor. The other two diagrams show the details of arbitrating for the system bus — a synchronous process — and the specification for the read operation as seen on the bus, an asynchronous process.

Figure 1.1 Waves diagrams corresponding to the master read operation of the Multibus Design Frame [Borriello85]. The top diagram is the operation as seen by one side of the transducer, a custom synchronous microprocessor. The other two represent the master read operation as seen on the Intel Multibus [Intel82]. One describes arbitration for the bus and the other the details of the data transfer.

These three diagrams are the input to Janus and correspond to only one of the many operations performed across this interface. Janus requires corresponding diagrams for both interfaces for each operation that the transducer is to support. Not all of the specification is

visible in the diagrams and many constraints are not displayed but entered and modified through the graphical cues on the diagram.

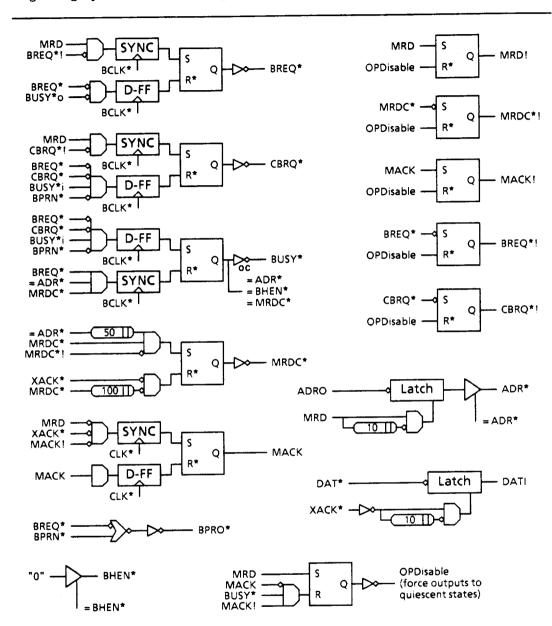

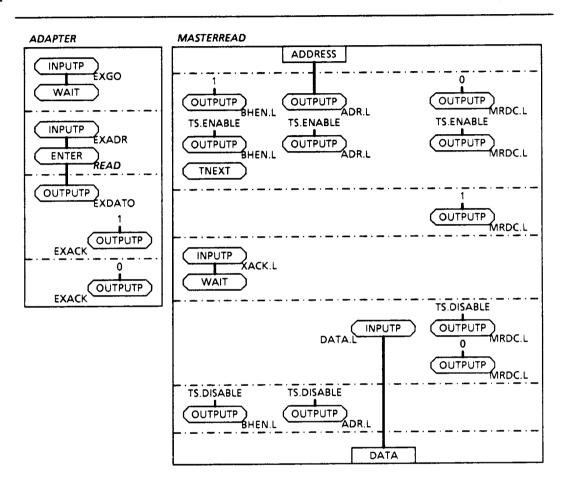

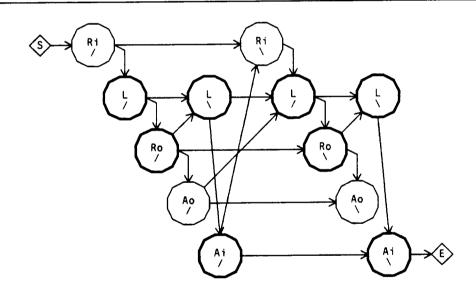

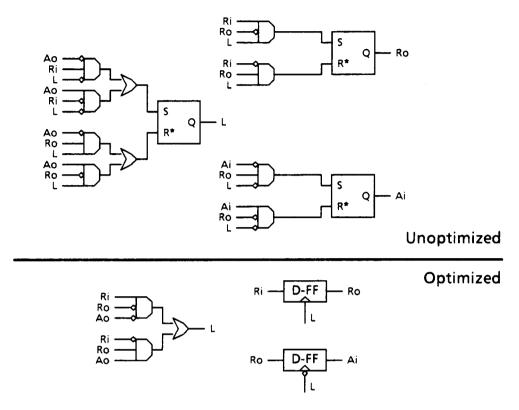

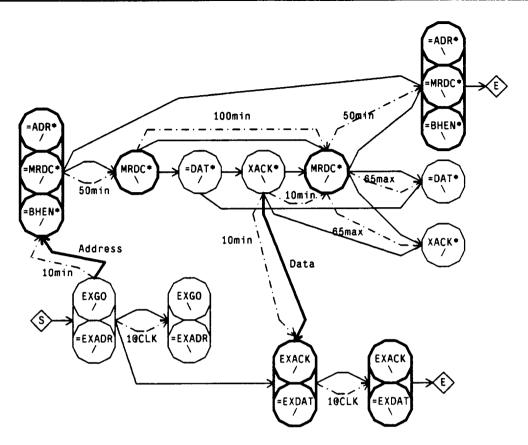

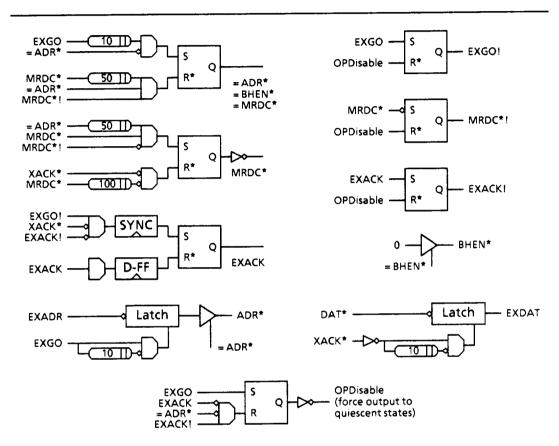

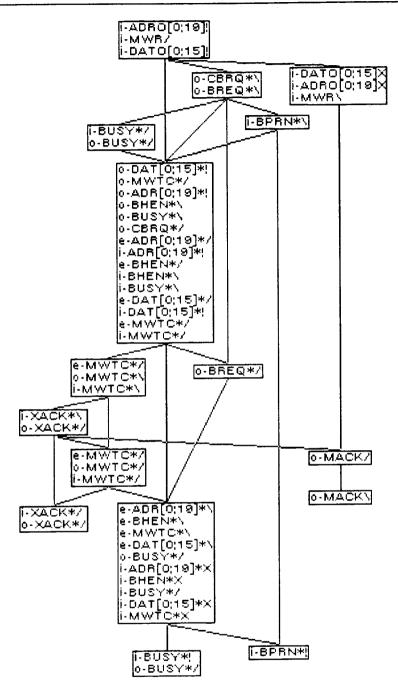

Figure 1.2 Circuitry synthesized by Janus from the Waves diagram specifications of Figure 1.1. The circuitry is shown before any optimizations. Appendix D provides more details for this and other examples.

The circuitry synthesized by Janus is shown in Figure 1.2. As is typical with interface transducers, the circuitry is not particularly large. However, it is complex in its interconnections and in the timing constraints that are enforced by this particular arrangement. The large number of constraints and interactions is what makes interface

transducer design complex and error-prone. Janus is meant to relieve the designer of the concerns associated with this myriad of details by using the constraints to synthesize the circuit automatically.

In this example, Janus generates circuitry that is only 11% larger than that generated by an experienced human designer. But more importantly, the performance of this interface transducer, obtained by measuring the elapsed time for the transaction, is 9% better than the human-generated design. This can be traced to a simplification made by the designer that greatly reduces the amount of parallelism in the circuit (and the number of interactions). In fact, 40% of the extra circuitry is generated by Janus to handle this parallelism.

#### **Summary of Results**

1.2.2

Janus emphasizes performance, the most important aspect of a circuit interface. The performance of an interface transducer is determined by its communication bandwidth. A good transducer maximizes the bandwidth by allowing the events to occur as fast as the interface constraints will permit. As can be seen in Table 1.1, the performance of the Janus-generated circuitry is at least as good or better as the human-generated circuitry for each of three practical examples. In regard to circuit size, Janus is within 20% of the implementations realized by experienced designers. It is important to note that although circuit size is always important, it is less so for interface transducers than other parts of a design. Transducers are not replicated as are many other components, therefore, a slightly larger circuit is usually tolerable. The specifications and resulting circuits for each of the examples of Table 1.1 are described in detail in Appendices B and D.

| Example                             | Performance | Size |

|-------------------------------------|-------------|------|

| Multibus Design Frame               | 1.09        | 1.11 |

| 2-Phase to 4-Phase Protocol Adapter | 1.00        | 0.61 |

| SPUR PCC-SBC Interface Unit         | 1.00        | 0.89 |

Table 1.1 Comparison of the results of Janus and experienced designers for three examples (ratioes are Janus/Designer). Performance is in terms of maximum throughput (shortest duration for the interface operations). Size is in terms of total number of logic gates. The examples are described in detail in Appendix D.

This dissertation is organized into two principal parts bracketed by this introduction and a summary. Interface specification is the subject of Part I, which consists of the next two chapters. Chapter 2 presents a set of requirements for a circuit interface specification method, describes previous work in this area, outlines a method based on timing diagrams that meets the requirements, and lists the many CAD tools that can be developed based on the substrate of a complete interface specification methodology. Chapter 3 discusses the *Waves* editor and how it formalizes timing diagrams so that a designer can specify circuit interfaces as described in Chapter 2.

Transducer synthesis is the subject of Part II. This part of the dissertation has a similar organization to Part I and is also composed of two chapters. Chapter 4 presents the problems associated with transducer synthesis and explains how previous approaches are inadequate for the task. It then introduces Suture, a new synthesis method that can automatically synthesize the control logic of interface transducers. Chapter 5 is a detailed description of Janus, the interface transducer synthesizer I have implemented. Janus uses the Suture method as a subroutine: generating the input to Suture from the collection of Waves diagrams that specify the transducer and optimizing the sequential and combinational logic output by the synthesis method. The details of the graph algorithms used in Suture are also presented in this chapter.

The dissertation concludes with Chapter 6 which describes the contributions of this work and how it builds on previous efforts. The chapter also outlines some avenues for future research into both the application of interface specifications and extensions to the circuit synthesis and optimization techniques developed in Janus. A set of appendices provide supplementary information on the implementation of both Waves and Janus. They include collections of practical examples of interface specification and transducer synthesis that can be used in evaluating this work.

<This page intentionally left blank.>

## PART I

< This page intentionally left blank. >

Interface specifications complement circuit specifications. While a circuit specification emphasizes the internal function of a circuit block, an interface specification focuses on the interactions between the circuit and its environment. Circuit logic specifications are collections of Boolean logic equations and memory requirements. Circuit interface specifications are collections of constraints on signal wires in the physical, electrical, logical, and timing domains. Formalized timing diagrams can be used to graphically represent the logical and behavioral constraints of a circuit interface, namely, the timing and sequencing behavior.

This chapter is composed of four sections. In the first section, I describe my taxonomy for the types of constraints that appear in interface specifications. The next section outlines the requirements for a general interface specification methodology. Previous work in this area is surveyed in the third section. The concluding section presents a new approach to interface specification based on formalized timing diagrams.

A digital circuit interface can be viewed as a group of signal wires with constraints. I classify the constraints into four domains: physical, electrical, logical, and timing. For example, physical constraints include the formfactor of circuit boards, and the positioning and size restrictions of chip packages and signal traces on a circuit board. Logic levels, current requirements, and input/output capacitances are examples of the electrical concerns. In this dissertation, I will concentrate on the logical and timing constraints. The logical constraints specify the logic levels along the signal waveforms and the timing constraints indicate the proper separation in time of the changes in logic level.

Interface constraints can be collected into sets that correspond to the basic communication operations supported by the interface. An interface operation is an indivisible sequence of events generated by two circuit blocks that constitutes communication between the two circuits. It may be as simple as a two-phase handshake or as complex as a multi-word data-transfer over a shared bus. Different operations may use the same or different signal wires.

Interfaces typically support many operations and each imposes a large number of constraints on the design of the interface circuitry — the circuitry that interacts directly with the signal wires of the interface. These constraints can have many idiosyncratic details. Constraints in one domain are derived from concerns on many different levels of design ranging from physical to behavioral. For example, electrical requirements determine signal rise and fall times that will lead to a timing constraint in the form of a setup time requirement on data to be latched. Considerable design effort is expended in ensuring that all the constraints are satisfied and in achieving good performance across the interface (i.e., that communication proceeds as fast as the constraints permit).

#### **Logical Constraints**

2.1.1

Logical constraints determine the shape of a signal waveform by specifying the logic level to be carried on a signal wire over a specified period of time. The boundaries between levels, or events, are transitions in logic value or changes in direction, and determine the time interval to which the logical constraints apply. Rise and fall times determine the duration of these transitions. Two orthogonal sets of constraints can be applied to the wire during a time interval: the logic level to be carried (a logic 0, a logic 1, or a high-impedance state) and the direction of the wire (input, output).

Five different level constraints can constrain the logic level carried on a digital signal. These are logic 0, logic 1, valid, high-impedance (tri-state), or don't care. A logic 0 or 1 constraint is

self-explanatory; that level must be present on the signal wire during the particular time interval. A valid level means that either a logic 0 or 1 is permitted but the precise value will only be known during each specific use of the interface operation. For example, in the transfer of data it is not known what the logic values of the data will be until the data is actually transferred. A high-impedance or tri-state level means that neither a logic 0 nor logic 1 should be asserted on the signal wire. This constraint is specified when a signal shares a common wire and must defer its use of it to one of the other connected signals. The don't care level signifies that any of the three basic levels (logic 0, logic 1, or tri-state) is acceptable. Although this set of five constraints does not cover all possible combinations of the three basic levels, it does include all the logical constraints used by interface designers.

Logic levels can also be constrained to be a Boolean function of other logic levels. In this case, the logic 0 and logic 1 constraints are never used since the level is determined by the Boolean relationship. However, whether a wire actually carries the level or is in a high-impedance state cannot be expressed by the Boolean function. Valid, tri-state, and don't care constraints still need to be specified for the wire.

Periodic waveforms have a fixed set of level constraints. The signal can consist solely of alternating intervals of logic 0 and logic 1. The position of the events delineating the time intervals is derived from the period and duty-cycle of the waveform.

Specifying that a signal wire is pre-charged or open-collector are examples of electrical, not logical, constraints. An open-collector signal is simply one for which logic 1 and high-impedance logical constraints are equivalent. A pre-charged signal is one that is constrained to be in a high-impedance state during each pre-charge phase. Correct logical constraint specification can be attained with the set of constraints described above. Therefore, whether a signal wire is pre-charged or open-collector is not considered at the logical domain, but rather in the domain of electrical constraints.

#### **Timing Constraints**

2.1.2

Logical constraints determine the overall shape of a signal waveform. Timing constraints specify how events are separated in time both for events on the same signal wire and across signal wires. A timing constraint specifies a minimum and maximum time between two events. The events must be separated by no less than the minimum time and no more than the maximum time. In the general case, the minimum and maximum times may be negative as well as positive.

There are more restrictive, but more familiar, forms of timing constraints. These include ordering, simultaneity, and synchronicity constraints. An ordering constraint is simply a restriction that one event occurs after another event. The corresponding general timing constraint with a zero minimum time and an infinite maximum time. A simultaneity constraint specifies that a set of events occur at the same time, within some tolerance. This corresponds to a set of general timing constraints between each pair of simultaneous events

that have a maximum time equal to the tolerance. and a minimum time that is the negative of the maximum, making it symmetric. A synchronicity constraint corresponds to setup and hold times for a synchronous signal. It applies to all events on a signal wire and specifies a timing constraint between the events and the closest edge of the synchronizing signal. In this case, one constraint applies to all events on a signal wire. Table 2.1 is a summary of all these forms of timing constraints and their special characteristics.

| Constraint    | Minimum      | Maximum     | Events     |  |

|---------------|--------------|-------------|------------|--|

| general       | + /- time    | + /- time   | one pair   |  |

| ordering      | 0            | + infinity  | one pair   |  |

| simultaneity  | – infinity   | + tolerance | many       |  |

| synchronicity | – setup time | + hold time | many pairs |  |

Table 2.1. The four types of timing constraints and their restrictions. Each type is an abbreviation for a collection of general timing constraints. The ordering constraint is minimum constraint with a value of 0. The simultaneity constraint is a set of maximum constraints between all pairs of events to which it applies. The synchronicity constraint applies to many pairs, constraining each event on a signal to the nearest event on the synchronous periodic signal. This classification is similar to that found in [Granacki86b].

The last type of timing constraint defines the timing relationships of periodic waveforms and is not a variation of the general timing constrant. A periodic waveform is composed of an alternating sequence of logic 0 and logic 1 levels that repeat every period with the duration of the logic 1 level defined by the duty-cycle of the periodic signal. Therefore, the periodic timing constraint is composed of two values: the period and the duty-cycle. The duty-cycle is often expressed as a fraction of the period.

What distinguishes interface specification languages from functional specification languages is the *emphasis* on constraints. However, there are other aspects of interface behavior that cannot be represented as constraints. To be able to call an interface specification method complete, it must be capable of describing arbitrary circuit behavior. Furthermore, a usable description language requires many of the features common to all computer languages. These include composing a more complex specification from simpler pieces in a hierarchical or non-hierarchical fashion and the ability to specify conditional and looping sequences of events. These are constructs familiar to all programmers, though there are some important differences when these ideas are applied to interfaces. In this section, I will outline the necessary requirements for a complete and general interface specification language. The Waves editor described in Chapter 3 is an example of a specification methodology that meets these requirements.

#### Specification of Event Sequences

2.2.1

The ability to express timing constraints distinguishes interface specification languages from traditional hardware description languages. It must be possible to specify a general timing constraint between two events. The prerequisites for this are the ability to specify the shape of the signal waveforms and to uniquely identify events so that they can be connected by one of the constraints outlined above (see Table 2.1).

A specification language must be capable of describing more than just a simple linear sequence of events. It must have the capability of expressing conditional and looping sequences as well. In specifying conditional sequences the differences between interface specification and computer languages is substantial. Each conditional sequence is enabled by a specific event. However, the enabling event may not be just the change in logic levels that defines the event, but also that the event occurred within a specific time interval. This is markedly different from the simple *if-then-else* statement. It includes time as a discriminant as well as values. For example, it should be possible to specify that if an event occurs later than a certain time then a different sequence of events should be followed.

Looping sequences are specified almost exactly as they would be in software computer languages. In fact, it is necessary to also support while statements, where an event sequence may be repeated until some terminating event occurs, as well as simple deterministic iterations. The terminating condition for a while loop takes the same form as that for conditional sequences. An example of the use of such a loop is in arbitrating for a bus where bus grant lines are repeatedly polled until the bus is granted to the requestor.

The procedure or subroutine is the most commonly used method of composing larger programs from smaller ones. However, this is not a sufficient construct for interface specification. A more appropriate model is that of communicating sequential processes or co-routines.

Hardware, by its very nature, has a high degree of parallelism. It must be possible to describe communicating processes that proceed through event sequences in parallel. Synchronization points determine when the event sequences must interlock. Events may occur in parallel before or after the synchronization points. This is quite different from sequential procedure calls where a sequence is simply inserted between two events in another sequence.

#### Expressibility of HDLs

2.2.3

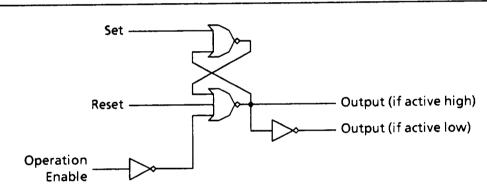

The last requirement for an interface specification language is that it have the expressibility of a general hardware description language. Many interfaces include a description of finite automata that control aspects of the interface or preserve state across interface operations. Typically, this logic is identical in all implementations of the interface circuitry. One example is the bus arbitration or request daisy-chain logic of many busses. Another example is the state information that needs to be preserved across operations in a packet-switched bus to match acknowledge packets with outstanding requests. It should be possible to directly specify these combinational or sequential logic components.

To make this specification possible, three hardware description language features are required in interface specification languages as well: Boolean expressions, latching conditions, and delay elements. Boolean expressions require no explanation. Latching conditions are necessary for interfaces that have state, and together with Boolean expressions, permit the description of arbitrary finite state machines by providing a means of specifying state. Delay elements are necessary for modeling real hardware elements and especially asynchronous components where the delay of components is sometimes critical to the proper function of the circuit. For example, if a signal logic level is a Boolean function of other signals then it should be possible to specify that a change in the logic level of one of the inputs will not be seen at the output signal for a certain period of time. For the purposes of this dissertation, these three features are the minimum required to describe arbitrary digital circuits. Of course, higher-level abstractions based on these primitives, as used in hardware description languages, are extremely useful. For example, an ALU that is part of the interface (e.g., for address computation) should be specified as such and not by the large number of logic equations that would be required.

Interface specification has attracted limited attention from the CAD community. There have been only a handful of attempts at developing interface specification methodologies. These can be classified into three main categories: (1) hardware description languages, (2) state graphs and Petri nets, and (3) temporal logic. The three categories correspond to three specification needs encountered by different communities of researchers. The languages work arose in response to the problems of system specification and hardware synthesis. The state graph approaches derive from work on self-timed circuit design and the specification of communication protocols. Temporal logic specifications were attempted so that formal verification of digital circuits would also include verification of interface constraints.

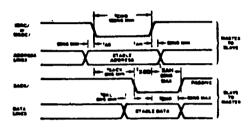

In this section, I will describe each of the approaches and how they meet some, but not all, of the requirements for an interface specification language presented in the previous section. To make the approaches easier to compare and evaluate, I will specify one of the operations of the Intel Multibus, the master memory read, in each of the methods. This is an asynchronous data transaction and is only one of the many operations supported by the Multibus interface. However, its description raises many of the special issues associated with interface specification. Figure 2.1 contains excerpts from the Multibus specification describing this operation. Timing diagrams and accompanying text are used to outline the sequence of events and describe timing constraints.

## Hardware Description Languages

2.3.1

The earliest work in the specification of interface details naturally began in the hardware description language community. This work was motivated by: (1) the complete specification of digital systems including their interfaces, and (2) the synthesis of digital hardware with interface constraints taken into account. A good history of the early work in interface specification languages is given by Parker [Parker85].

2.2.2.5 MULTIBUS COMMANDS. In this section, we will discuss the command lines and how they work in conjunction with the lines explained in the previous sections to accomplish a read or a write operation.

There are four MULTIBUS command lines.

Memory Read Command - MRDC/ I/O Read Command - IORC/ Memory Write Command - MWTC/ I/O Write Command - IOWC/

The command lines, which are driven by three state drivers on the bus master, indicate to the bus slave the action that is being requested.

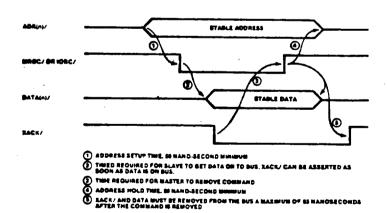

Read Operations. The two read commands (MRDC/ and IORC/) initiate the same basic type of operation. The only difference being that MRDC/ indicates that a memory address is valid on the MULTIBUS address lines, and IORC/ indicates that there is an I/O port address on the MULTIBUS address lines. This address (memory or L/O port) must be valid on the bus 50ns prior to the read command being generated. When the read command is generated, the slave module (memory or I/O port) puts the data on the MULTIBUS data lines and returns a Transfer Acknowledge (XACK/), indicating that the data has been placed on the bus. When the bus master receives the acknowledge, it strobes in the data and removes the command (MRDC/ or IORC/) from the MULTIBUS interface. The slave address (memory or 1/O port) is removed from the bus a minimum of 50ns after the read command is removed. XACK/must be removed from the MULTIBUS interface within 65nsec after the command is removed, to allow for the next bus cycle. Figure 2-8 shows the timing for the Memory Read or I/O Read command.

#### 3.2.1 READ OPERATIONS (I/O AND MEMORY)

A Read operation transfers data from memory or from I/O to the master that is controlling the bus. For detailed functional descriptions refer to Section 2.2. The lines involved and timing specifications for a Read Operation are as follows (figure 3-3):

Figure 3-3. Read AC Timing

See Section 5.1 for guidelines and examples. See also the special inhibit operation in Section 3.2.3. For system anomalies with respect to read commands see Section 6.5.

Figure 2-8. Memory or I/O Read Timing

Figure 2.1. Excerpts from the Intel Multibus Specification describing the Multibus master read operation [Intel82]. The excerpts only describe the data transaction part of the operation. The bus arbitration part is not shown for the purpose of brevity. The description includes two timing diagrams and some text to describe the logical and timing constraints. Four signals are used in the operation and a fifth, not shown (BHEN\*) to signal a 16-bit wide data transfer. Electrical and physical constraints are described elsewhere in the specification document. Reprinted by permission of Intel Corporation.

Initially, HDL support for interfaces took the form of simple declarative specification of input and output ports to a circuit block, outlining their special electrical and logical characteristics (e.g., output, open collector, active low). This early work was eventually incorporated into the ISPL hardware description language [Barbacci76]. Parallel work at IBM with AHPL, an HDL based on APL, also added some simple timing constructs to represent delay, especially useful for describing asynchronous systems where there is no clock to advance time [Vissers76]. However, timing constraints are not represented explicitly, but are embedded in the circuit description. For example, if the circuit is to wait for a transition on an input signal that is to occur within some time interval, a loop construct is used as the specification of this timing constraint. The signal is continuously polled, for a maximum number of iterations derived from the timing constraint, to determine if the transition had occurred. The situation is worse with timing constraints on output signals. The transition is set to occur at a convenient time to meet the constraint but there is no explicit representation of the timing constraint. Therefore, the description includes only one of the many possible correct behaviors for the interface.

The first real example of an interface specification language is SLIDE [Parker81]. SLIDE was originally developed as a programming language that could accurately simulate system interconnect. Since system interconnect (i.e., system busses and backplanes) is primarily a circuit interface, SLIDE directly addresses many of the issues of interface specification.

There are three interesting innovations in SLIDE. The first is the model of interfaces as a collection of communicating sequential processes. Synchronized co-routines are an accurate model of the highly parallel and asynchronous hardware that makes up a computer system and they make it straightforward to implement simulators for system interconnect [Altman80]. The second is the ability to use signal and wait constructs, similar to those in concurrent programming languages. This allows an explicit representation of timing constraints rather than the polling loop construct discussed above. And lastly, SLIDE emphasizes signal transitions rather than logic levels so that asynchronous systems can be more easily modeled.

Figure 2.2 is a SLIDE description of the Multibus master read operation of Figure 1.1. Here we can see all three of the major features of SLIDE. The interface operation is represented as a separate process that can be started by a *call* from another part of the description or by a WHEN clause. A WHEN clause specifies a set of conditions that, when met, initiate the

process. The wait construct is represented in SLIDE by the DELAY UNTIL statement that specifies that the process should remain in its current state until a condition is met. SLIDE also allows for a timeout period on the wait. And lastly, as can be seen in the description, there is equal support for transitions and levels on signal wires.

#### PROCESS masterread;

**BEGIN**

mrdc ← 1; bhen ← 0; adr ← Address;

bhen.en ← 1; adr.en ← 1; cmd.en ← 1 NEXT

DELAY 50 NEXT

mrdc ← \ NEXT

DELAY UNTIL xack EQL \ NEXT

Data ← dat NEXT

mrdc ← / NEXT

DELAY 50 NEXT

bhen.en ← 0; adr.en ← 0; cmd.en ← 0 NEXT

END;

Figure 2.2. SLIDE description of the Multibus master read operation. The signals can be assigned levels (1 or 0) and transitions (falling (\) or rising (/)). The Address and Data variables represent bit vectors. Signals with the .en suffix are used as tri-state control for the signal with the same name. The NEXT keyword enforced a sequence on the statements. Statements between two NEXTs can occur in any order.

There are some major difficulties with SLIDE, however. Its emphasis on asynchronous behavior makes it cumbersome to express synchronous behavior. To do so requires that all transitions be described relative to a fine-grain clock, typically with a 1 or 2 nanosecond period. This is necessary for modelling both asynchronous and synchronous behavior in the same program. It is also difficult to express constraints across statements that do not follow each other in the program sequence.

Another approach to interface specification comes from problems in high-level synthesis [Thomas83]. These synthesis systems enable designers to synthesize circuits directly from high-level specifications to actual hardware. However, designers are then faced with the problems of system integration (i.e., the satisfaction of interface constraints so two circuit blocks can communicate).

ISPS is a familiar HDL used in high-level synthesis [Barbacci81]. The Behavioral Synthesis with Interfaces (BSI) extensions to ISPS add constructs for describing circuit interfaces [Nestor86]. Three features of BSI/ISPS are particularly interesting. The first extends the input and output port semantics to include specifications such as active low and tristatability. The second makes explicit use of ordering statements to enforce the proper order on interface event sequences. Since the synthesis process attempts to optimize circuit size by rescheduling

the order of events in the description, it is necessary to specify explicit ordering constraints to override this rearrangement. This ordering is expressed using the TNEXT() construct as shown in Figure 2.3. Finally, general timing constraints can also be expressed. Rather than using a delay statement as in SLIDE, BSI/ISPS uses labels on statements of the description to identify interesting events. Timing constraints are then declared to exist between these labels and are not restricted to be in the program sequence, as in SLIDE (see Figure 2.2).

```

MasterRead( Address < 23:0 > ) < 15:0 > : = begin

OUTPUTP(bhen.i, TS.ENABLE) {L:mr0e};

OUTPUTP(adr.l, TS.ENABLE) {L:mr1e};

OUTPUTP( mrdc.l, TS.ENABLE) NEXT

OUTPUTP(bhen.l, 1) {L:mr0};

OUTPUTP(adr.I, Address) {L:mr1} NEXT

OUTPUTP( mrdc.l, 1 ) {L:mr2} NEXT TNEXT() NEXT

WAIT(INPUTP(xack.l)) NEXT

MasterRead = INPUTP(data.l) NEXT

OUTPUTP( mrdc.l, 0 ) {L:mr3} NEXT

OUTPUTP( adr.l, TS.DISABLE) {L:mr4} NEXT

OUTPUTP(bhen.I, TS.DISABLE) {L:mr5} NEXT

OUTPUTP( mrdc.l, TS.DISABLE) {L:mr6} NEXT

end

mrTenb:

time( mr0e, mr0 ) GEQ 0ns;

time( mr1e, mr1 ) GEQ 0ns;

mrTena:

time(mr0, mr2) GEQ 50ns;

mrTbs:

mrTas:

time(mr1, mr2) GEQ 50ns;

time(mr3, mr4) GEQ 50ns;

mrTbh:

mrTah:

time( mr3, mr5 ) GEQ 50ns;

mrTdis:

time(mr3, mr6) GEQ 50ns;

time(mr2, mr3) GEQ 100ns;

mrTcmd:

```

Figure 2.3. BSI/ISPS description of the Multibus master read operation (adapted from [Nestor87a]). The procedure takes the address as an argument and returns the data value. Signals with the .l suffix represent lines that are active low, that is, when a logic 1 is assigned to these lines it actually appears a low electrical level. The output statements take two arguments: the name of the signal and the value. The value can be a logic 0, logic 1, or a string to signify that the signal should be driven or high-impedance. The labels used by the timing constraint declarations are within curly brackets ({}).

Two timing constraints of the interface cannot be expressed with BSI/ISPS. These are the 65ns maximum constraints that exist between the event that deasserts the command line (labeled mr3 in Figure 2.3) and the deassertion of the acknowledge and data lines by the slave

device. To express this constraint it is necessary to use a WAIT statement for the acknowledge input and then add a constraint between that statement and the statement that deasserts the command. However, this is not done in ISPS because the semantics are such that the synthesis procedures would then synthesize circuitry to check that the acknowledge signal was deasserted. This is not the true intent of the specification. It is simply to state that the circuitry can be designed to assume that the signal will be deasserted within 65ns, not that circuitry should be added to actually check for this event. The similar constraint on the data lines cannot even be expressed because the data lines carry unknown logic values and it is not possible to use a WAIT statement because standard digital logic cannot determine when a wire is in a high-impedance state. This is due to the fact that BSI/ISPS was not designed to be an interface specification language. Rather it is intended to be a means of introducing interface constraints into a functional description.

Furthermore, timing constraints are interspersed with functional details. Although the sequence of events on the interface signals and their timing constraints can be separated into their own procedure, as in Figure 2.3, this is not a viable alternative because it leads to inefficiencies in the synthesized circuitry. Unless the procedure is expanded in-line and merged with the procedures that call it, the synthesized interface circuitry will execute sequentially and not in parallel with the circuit internals. The in-line expansion is very difficult because it is not obvious how events should be ordered across procedures. Therefore, timing constraints are typically embedded in the functional description much in the same way as the precursors to SLIDE described above. The separation of interface constraints from circuit function is one of the principal advantages derived from SLIDE's co-routine model that is absent in ISPS.

The Timing Design System (TDS) uses a similar approach to constraint specification as BSI/ISPS [Kara86]. The events are simply a list of changes between two logic levels on a signal wire. Constraints are expressed as a minimum and maximum tme between two events. Unfortunately, TDS can only express constraints within a fixed sequence of events and lacks the higher-level constructs of HDLs such as conditionals and loops.

A problem common to all these languages is the difficulty of describing event sequences within a linear program. The one-dimensional nature of a programming language is not a good match for the two dimensions of timing constraints. The implicit time axis used to represent the linear sequence of events is the only dimension visually present. The second dimension is used to represent constraints between different signals and is not available in the linear program. This makes the interrelationships between signals difficult to discern. This has led to attempts to make machine-readable interface specification more like the methods employed by designers. One approach has been to describe the interface as well as the circuit in natural language text (see Figure 2.4) [Granacki86a].

Although English is easily readable, it is still difficult to quickly grasp the relationships between the pieces of information described. The use of English only partially alleviates the requirement of learning a new language for specification. It is simply a new and restricted style of a more familiar natural language rather than a familiar computer language.

A 16 bit word of data is read over the dat lines.

A 24 bit address is transferred over the adr lines.

All command lines are active low.

There is an asynchronous four-cycle handshake that takes place across the mrdc and xack lines.

The adr and bhen signals have a 50ns setup time before mrdc is asserted.

The adr and bhen signals have a 50ns hold time after mrdc is deasserted.

The mrdc line must be asserted for a minimum of 100ns.

The data and xack lines will be deasserted within 65ns of mrdc being deasserted.

To read the data the master asserts the mrdc line and then waits for xack to be asserted by the slave.

The data is available while the xack line is asserted.

Figure 2.4. PHRAN-SPAN natual language specification of the Multibus master read operation. To make the natural language system practical the English is restricted to some simple templates of declarative sentences.

My approach is to use the complementary part of interface documentation for formal specification, the timing diagrams. Timing diagrams are ubiquitous in interface specification documents and are familiar to all digital circuit designers. Interestingly, the constraints in TDS are used to derive a timing diagram for the user. In section 2.4, and in more detail in Chapter 3, I will demonstrate how timing diagrams can be used for interface specification, but first, I will describe the other two classes of approaches to interface specification.

# State Graphs and Petri Nets

2.3.2

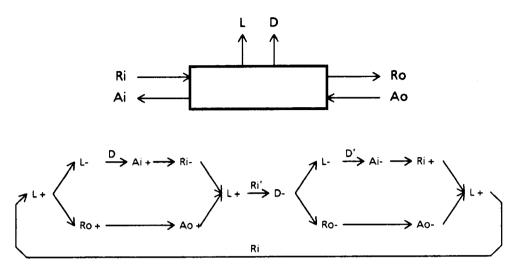

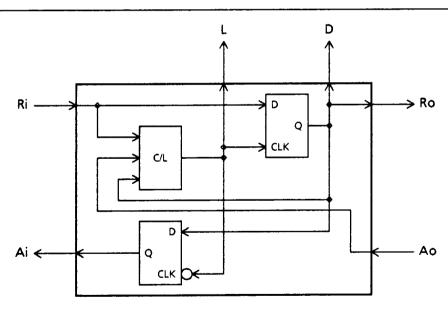

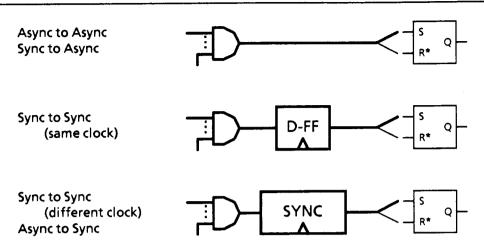

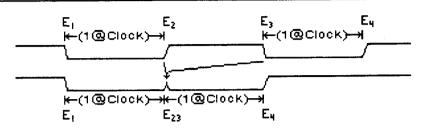

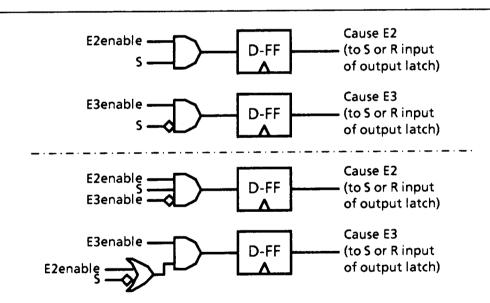

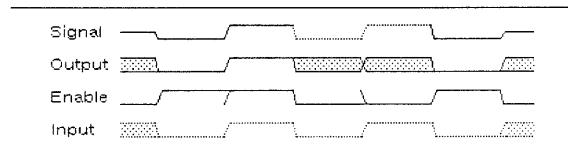

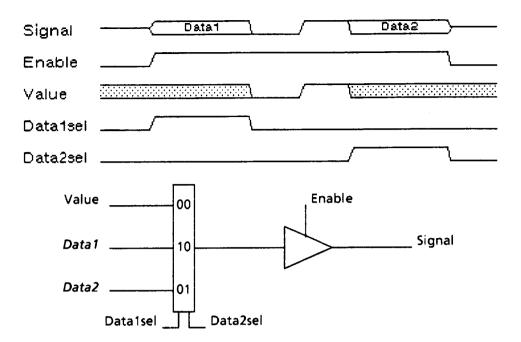

Petri net theory forms the basis of the state graph approaches to interface specification [Petri62]. Petri nets are an abstract graph model for describing event sequencing and have been adapted to describe many sequential processes including interface protocols. Petri nets are bi-partite graphs composed of two types of nodes called places and transitions [Agerwala79]. Places symbolize computation and transitions are synchronization points for different paths through the graphs. Arcs connect places to transitions and transitions to places. They can fan-out or fan-in arbitrarily.