# VLSI Design Techniques for Floating-Point Computation

By

## Bidyut Kumar Bose

B.Tech. (Indian Institute of Technology) 1977 M.S. (Carnegie-Mellon University) 1979

## DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

in

# ENGINEERING ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

in the

## **GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA at BERKELEY

| Approved: | D. A. Pattorson | 11/18/88     |

|-----------|-----------------|--------------|

|           | Dand a Hodges   | 11/16 Date 8 |

|           |                 |              |

\*\*\*\*\*\*\*\*\*\*\*

|   |  |  | æ' |

|---|--|--|----|

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

|   |  |  |    |

| l |  |  |    |

1

VLSI Design Techniques for Floating-Point Computation

Bidyut Kumar Bose

Abstract

This thesis presents design techniques for floating-point computation in

VLSI. A basis for area-time design decisions for arithmetic and memory

operations is formulated from a study of computationally intensive programs.

Tradeoffs in the design and implementation of an efficient coprocessor inter-

face are studied, together with the implications of hardware support for the

IEEE Floating-Point Standard. Algorithm area-time tradeoffs for basic arith-

metic functions are analyzed in light of changing technology. Details of a

single-chip floating-point unit designed in two micron CMOS for SPUR are

described, including special design considerations for very wide datapaths.

The pervasive effects of scaling technology on different levels of design are

explored, from devices and circuits, through logic and micro-architecture, to

algorithms and systems.

David A. Patterson

(Committee Chairman)

|  |  | ** <b>•</b> |

|--|--|-------------|

|  |  |             |

|  |  |             |

|  |  |             |

|  |  |             |

|  |  |             |

|  |  |             |

|  |  | ÷           |

|  |  |             |

|  |  |             |

| Dedicated with love to  |  |

|-------------------------|--|

| Baba Ma Joya Didi Tutul |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

#### Acknowledgement

This work would not have been completed without the constant, selfless love and gentle encouragement of my parents, my *best-buddy* Joya, and my sisters Krishna and Devjani. Dave Patterson, my research advisor, has been invaluable with his guidance, advice and support, and Dave Hodges and Bob Goldman kindly served on my dissertation committee. A project of this scope would have been impossible without the essential contributions of many colleagues, including the completion and testing of the FPU functional simulator by Corinna Lee, the coprocessor interface specification by Paul Hansen, and layout, circuit, and timing simulation of portions of the FPU datapath and control by Tim Hu and Debby Jensen. Principal funding for the project was by DARPA under contract N00039-85-C-0269.

# **Table of Contents**

| CHAPTER 1. Introduction                                              | . 1 |

|----------------------------------------------------------------------|-----|

| 1.1. Motivation                                                      |     |

| 1.2. Thesis Outline                                                  |     |

| 1.3. References                                                      | . 9 |

| CHAPTER 2. Floating-point Computation Characteristics & Accelerators | 10  |

| 2.1. Characteristics of Floating-point Computation                   | 11  |

| 2.1.1. Frequently Used Functions                                     | 11  |

| 2.1.2. Two Benchmarks, Linpack and Livermore Loops                   | 13  |

| 2.1.3. Dynamic Data From Two Real Programs                           |     |

| 2.2. Comparison of Floating-point Processors                         |     |

| 2.2.1. Comprehensive Floating-point Processors                       | 21  |

| 2.2.2. Basic Floating-point Processors                               |     |

| 2.2.3. Floating-point Performance Comparison                         |     |

| 2.3. Summary                                                         |     |

| 2.4. References                                                      | 29  |

| CHAPTER 3. Design Tradeoffs for VLSI Floating-Point Units            | 30  |

| 3.1. Coprocessor Interface Design                                    | 32  |

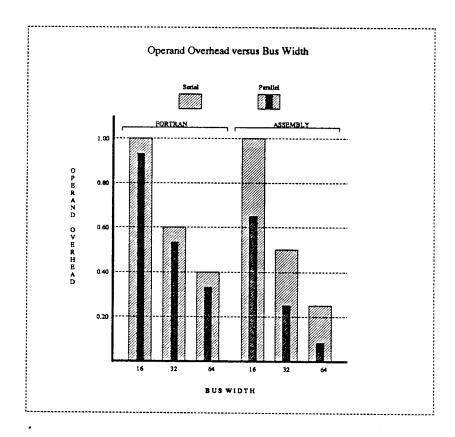

| 3.1.1. Communication Overhead in Floating-Point Coprocessors         |     |

| 3.1.2. Communication Overhead and Total Loop Execution Time          |     |

| 3.1.3. Parallel Execution Between CPU and FPU                        | 39  |

| 3.2. Implementing the IEEE Floating-Point Standard                   |     |

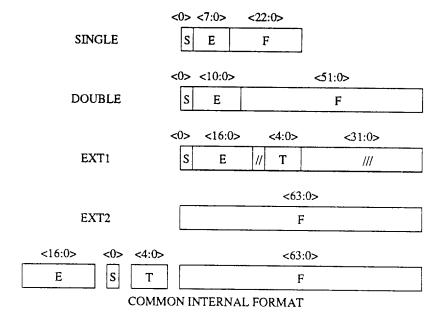

| 3.2.1. Data Formats                                                  |     |

| 3.2.2. Memory and Arithmetic Operations                              |     |

| 3.2.3. Exception Detection and Handling                              |     |

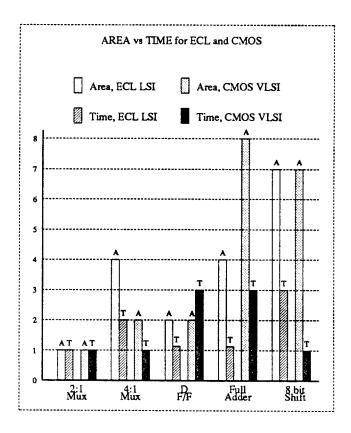

| 3.3. Arithmetic Algorithms and Implementation Technology             |     |

| 3.3.1. Add/Subtract Design Issues                                    |     |

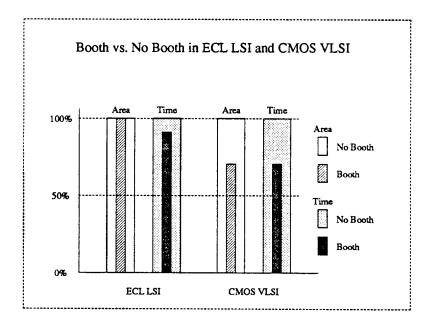

| 3.3.2. Multiply Design Issues                                        |     |

| 3.3.3. Divide Design Issues                                          |     |

| 3.4. Summary                                                         |     |

| 3.5. References                                                      | 59  |

| CHAI | PTER 4. Add/Subtract Datapath Design Considerations | 61  |

|------|-----------------------------------------------------|-----|

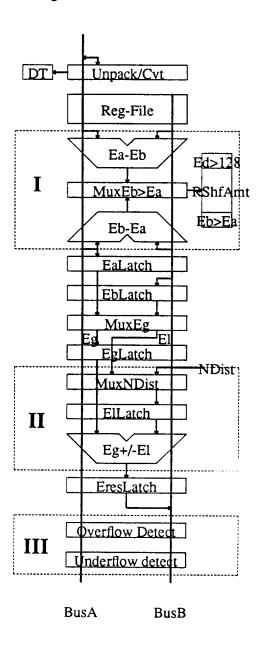

|      | 4.1. Implementation Considerations                  | 62  |

|      | 4.2. The Exponent & Fraction Front-Ends             |     |

|      | 4.2.1. Unpacking and Packing Data                   |     |

|      | 4.2.2. Handling Special Operands                    |     |

|      | 4.2.3. Conversion to Single and Double Precision    |     |

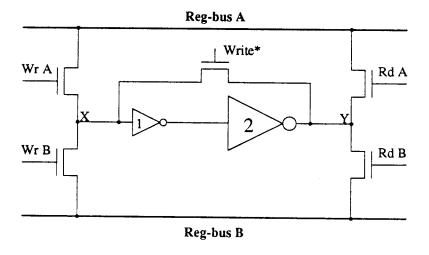

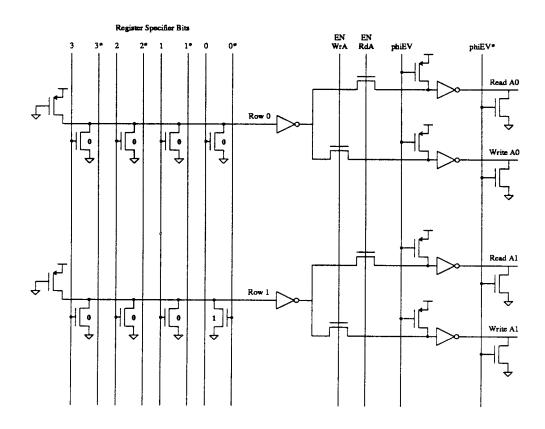

|      | 4.2.4. The Register File                            |     |

|      | 4.3. The Exponent Datapath                          |     |

|      | 4.3.1. The Exponent Difference Unit                 |     |

|      | 4.3.1.1. A Fast Adder/Subtractor                    |     |

|      | 4.3.2. Overflow and Underflow Detection             |     |

|      | 4.4. The Fraction Datapath                          |     |

|      | 4.4.1. The Shifter                                  |     |

|      | 4.4.1.1. The Shifter Array                          |     |

|      | 4.4.1.2. The Sticky Logic                           |     |

|      | 4.4.1.3. The Shifter Decoder                        |     |

|      | 4.4.2. The Leading One's Detector                   |     |

|      | 4.5. Rounding                                       |     |

|      | 4.6. Summary                                        |     |

|      | 4.7. References                                     |     |

|      | 5.1. Implementation Considerations                  | 95  |

|      | 5.2. The Multiplier                                 |     |

|      | 5.2.1. The Algorithm                                |     |

|      | 5.2.2. The Multiply Inner Loop                      |     |

|      | 5.2.3. Rounding                                     |     |

|      | 5.3. The Divider                                    |     |

|      | 5.3.1. The Algorithm                                |     |

|      | 5.3.2. The Divide Inner Loop                        |     |

|      | 5.3.3. Quotient Selection                           |     |

|      | 5.3.4. Rounding                                     |     |

|      | 5.4. Summary                                        |     |

|      | 5.5. References                                     | 13  |

|      |                                                     |     |

| СНАР | PTER 6. Control Design Considerations               | .14 |

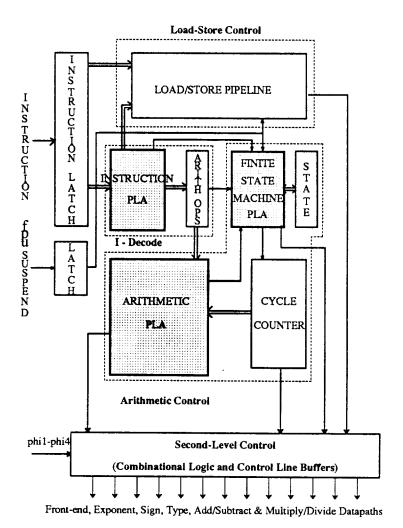

|      | 6.1. FPU Control Unit Overview                      | 15  |

|      | 6.2. The Instruction Decoder                        | 16  |

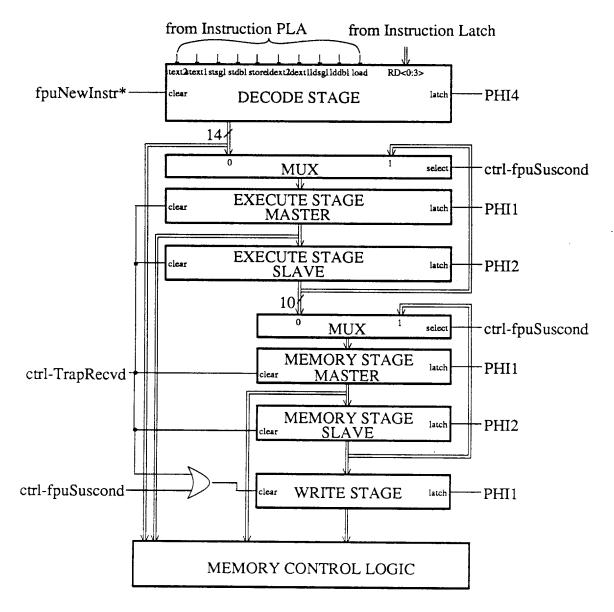

|      | 6.3. Load-Store Control                             | 18  |

|      | 6.4. Arithmetic Control                             | 20  |

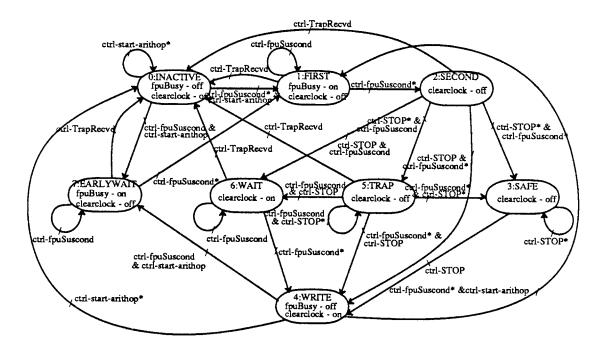

|      | 6.4.1. The State Machine                            | 21  |

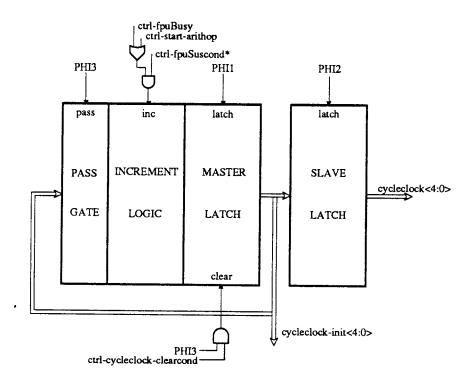

| 6.4.2. The Cycle Counter                             | 123 |

|------------------------------------------------------|-----|

| 6.4.3. PLA Partitioning                              |     |

| 6.5. Clock Generation, Distribution and Skew         |     |

| 6.6. Summary                                         |     |

| 6.7. References                                      |     |

|                                                      | 10, |

| CHAPTER 7. Implications of Scaling Technology        | 138 |

|                                                      |     |

| 7.1. Scaling at the Device/Circuit Level             |     |

| 7.2. Scaling at the Logic/Micro-architectural Level  |     |

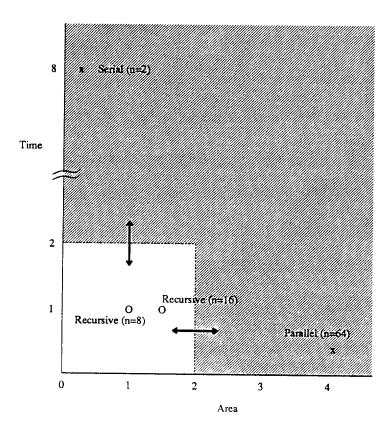

| 7.3. Scaling and Arithmetic Algorithms               |     |

| 7.4. Scaling and Multiple Function Units             |     |

| 7.5. Scaling at the Architectural Level              | 151 |

| 7.6. Summary                                         | 154 |

| 7.7. References                                      | 156 |

|                                                      |     |

| CHAPTER 8. Conclusions                               | 158 |

|                                                      |     |

| 8.1. Summary                                         |     |

| 8.2. Future Work                                     |     |

| 8.3. References                                      | 164 |

|                                                      |     |

| APPENDICES                                           | 167 |

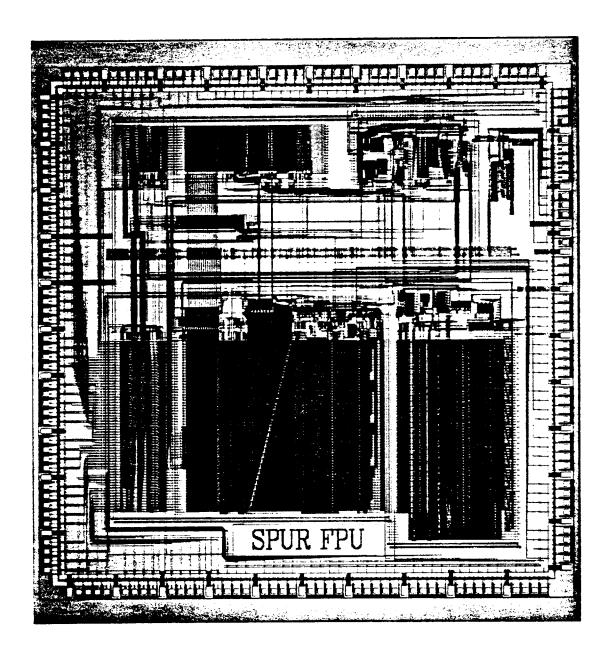

| Appendix 1. SPUR FPU die photograph                  | 168 |

| Appendix 2. SPUR FPU Instruction Set and Cycle Times |     |

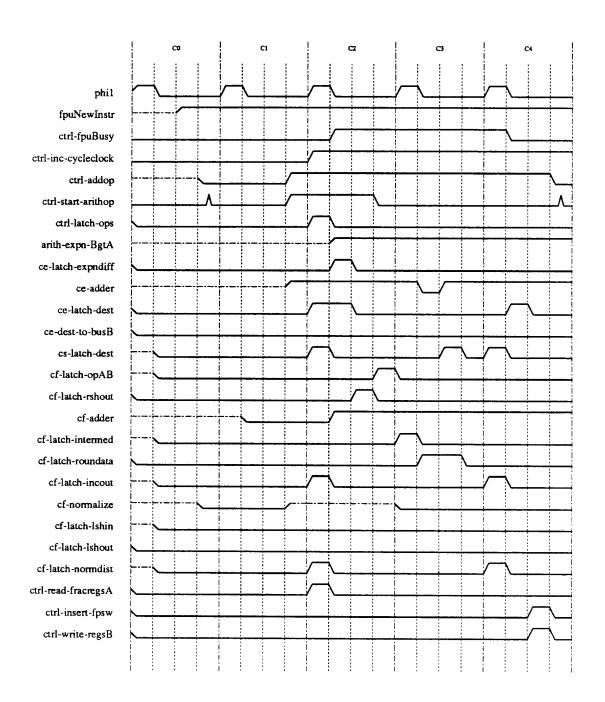

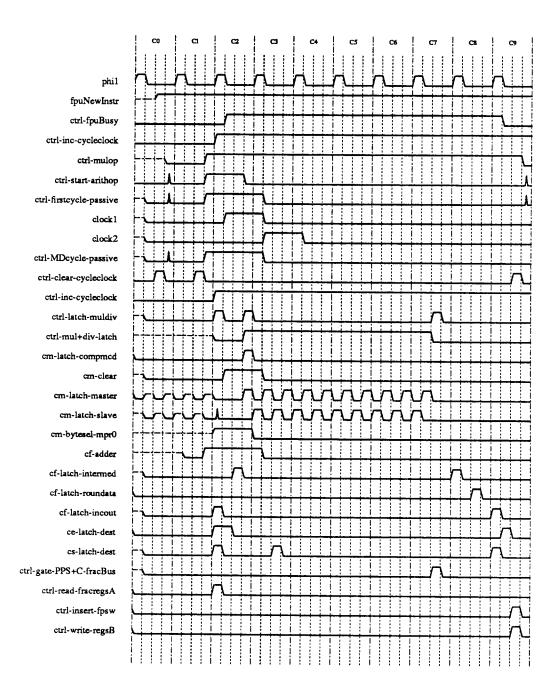

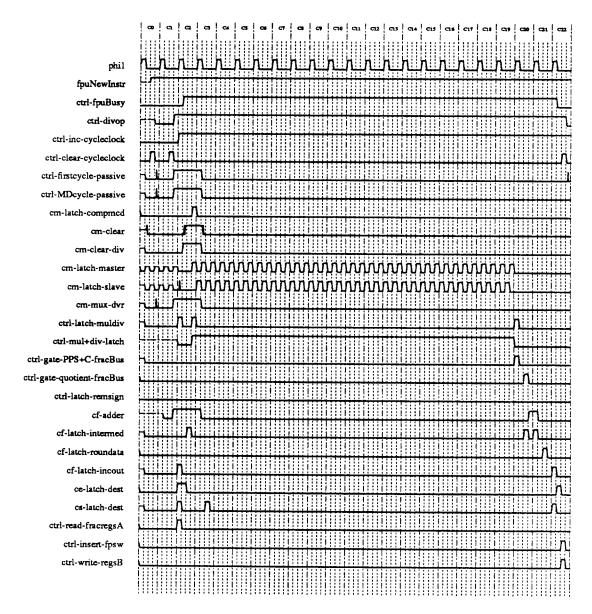

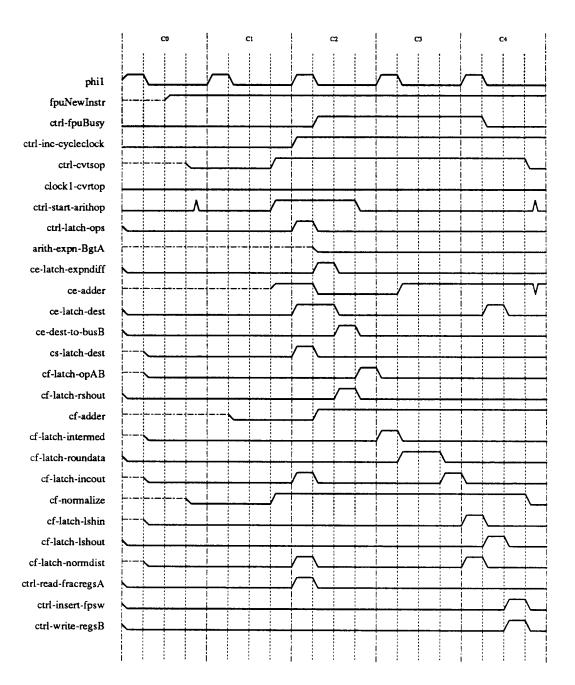

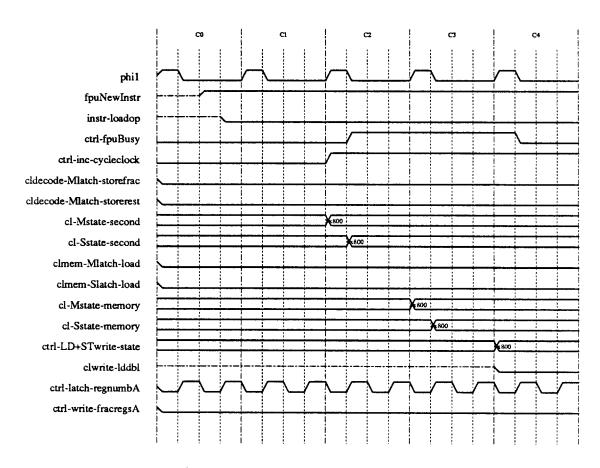

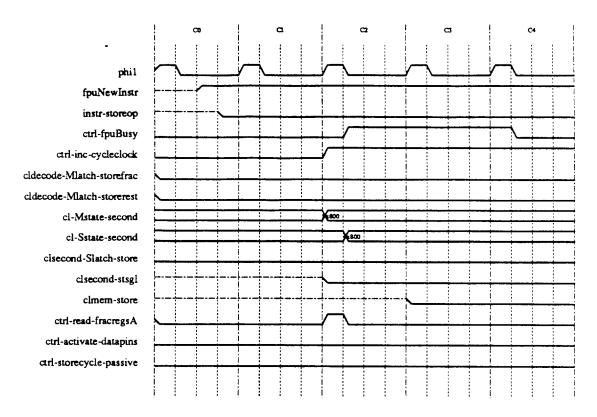

| Appendix 3. SPUR FPU Timing Waveforms                |     |

|  |  | ,  |

|--|--|----|

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  | u: |

|  |  |    |

# 1

# Introduction

From their very inception, computers have been driven by the forcing function of scientific computation towards ever higher performance. Since scientific and engineering computations are dominated by floating-point calculations, these have had to be speeded up to sustain the drive for higher performance. The evolution of VLSI technology towards finer geometries has been another dominant factor in performance improvement. This in turn has precipitated a need for the evolution of design techniques for efficient implementation of floating-point arithmetic in VLSI. This thesis develops design techniques for fast floating-point computation in VLSI.

Computationally intensive programs are studied to formulate a basis for area-time design decisions, emphasizing memory and arithmetic operations. Design tradeoffs for single-chip floating-point units are investigated at the algorithmic and architectural level. Logic, circuit and layout design considerations for VLSI datapath and control units are studied, leading to design projections considering the implications of scaling technology.

As a case study, a floating-point unit (FPU) is designed in CMOS VLSI as part of the SPUR project [Hill86], which supports extended-precision arithmetic and uses hardwired control, while implementing the IEEE floating-point standard [Cody84]. Even though the design is specific to floating-point processors and CMOS technology, most of the ideas presented here, and especially the design method and analysis of design tradeoffs, extrapolate to general-purpose processor design and to VLSI technology in general. For example, key components in CPU and FPU datapaths are very similar, and tradeoffs in control PLA partitioning apply to all processor designs in any VLSI technology.

This chapter provides motivation for the research undertaken and reported here, and proceeds to outline the remainder of this thesis.

#### 1.1. Motivation

High speed floating-point computation is essential for a large class of problems, like computer modeling and simulation, computer graphics, image processing, meteorology, hydrodynamics, and computer-aided design/computer-aided manufacturing. Fundamental to the analysis of a physical system is a need to solve systems of simultaneous partial differential equations, which are approximated with an array of

discretely placed points in the space-time continuum. The greater the number of points, the smaller are the truncation errors introduced by representing continuous independent variables as discrete points, which are in turn evaluated using finite difference or finite element grid-based simulation techniques. Floating-point arithmetic has generally been used for these applications, since integer arithmetic lacks the range and precision for computation of most of these real-world needs.

Traditionally, floating point arithmetic has been slow in software. Even basic arithmetic operations like addition require long shifts for fraction alignment, and rounding, evaluation of normalizing distance, and overflow/underflow detection can involve many cycles of bit-manipulation. Even with some hardware support, scientific computation can be expensive to implement in software. For example, it is much more efficient to compute special functions if the internal working precision of a machine allows extra range and precision. If the operand (x) and result of lnx (natural logarithm of  $\{x\}$ ), say, are in double precision (64 bits), but it is possible to compute intermediate results in extended precision (80 bits), the code for this transcendental function gets much simpler, cleaner, and faster [Kaha85].

Floating-point arithmetic has traditionally been expensive in hardware. Mainframe computers invest significantly in logic, boards, power dissipation and design time to provide floating-point support. Only recently is VLSI technology making it possible to have fast, inexpensive floating point arithmetic [Fand85]. In less than eight years, more than a dozen such processors have been designed, and the trend continues at an even accelerated pace.

One of the primary reasons for this resurgence is the evolution of VLSI technology to finer geometries. At present levels of integration, it is possible to build single chips with more than 100,000 transistors, allowing designers a choice of algorithms for arithmetic functions. CMOS technology, with its many advantages including low static power dissipation and high noise immunity, is considered to be the technology of choice for present-day processors [Myer86].

By their very nature, floating-point accelerators require very wide datapaths (64-bit fractions in extended precision), and improvements in interconnect have made it possible to build fast, wide datapaths. In particular, multiple layers of metal interconnect have greatly reduced interconnect delays that would otherwise have been present with more resistive control lines. For example, a polysilicon control line driving 2pF across half a chip,  $(5000\mu$  at  $2\mu$  pitch, i.e. 2500 squares, at 50 ohms per square) would have a distributed RC delay (.68RC) of around 200ns! Contrast this with attempts to achieve processor cycle times under 100ns.

Another factor in the resurgence of floating-point processors is the emergence of the IEEE Floating-point Standard 754 [Cody84] as an industry-wide standard for floating-point computation. Features of this standard include the specification of formats of operands and results for several arithmetic operations, conversions between numbers of different formats, and exception detection and handling. Supporting the standard ensures the accuracy, predictability and portability of numerical software.

Design techniques need to be developed to take full advantage of the evolving technology and the emerging IEEE standard, and that is the subject of this dissertation. The thesis ranges from a study of the characteristics of scientific computation, through

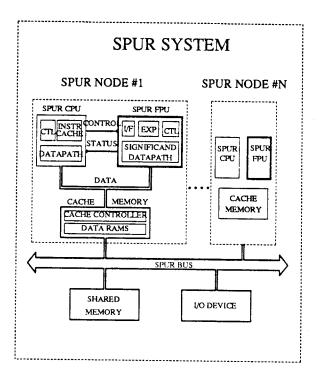

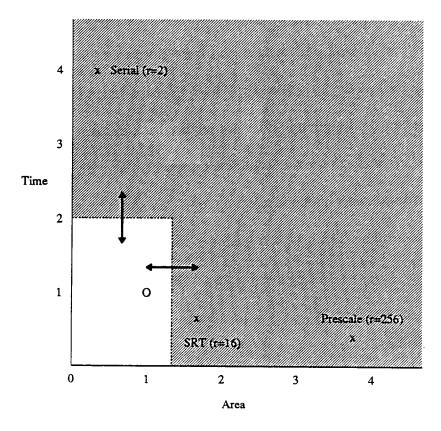

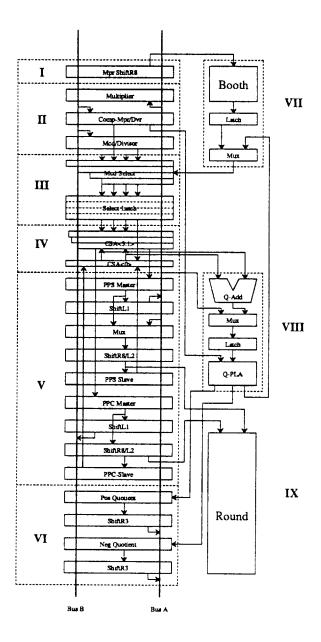

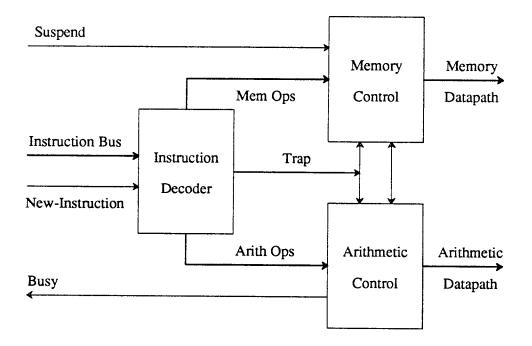

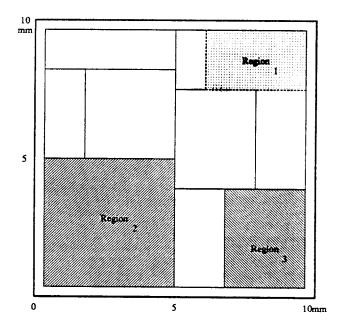

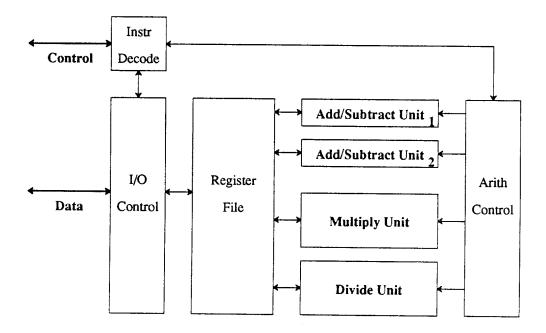

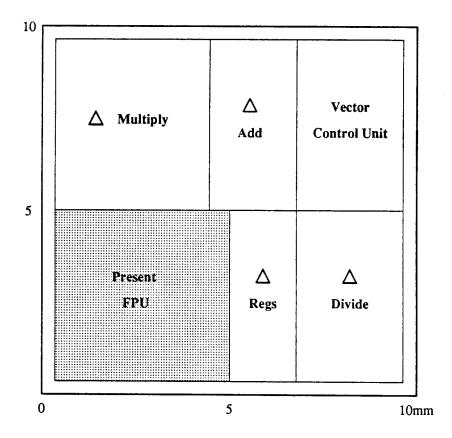

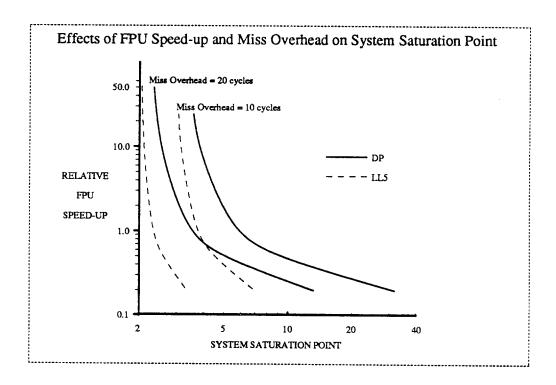

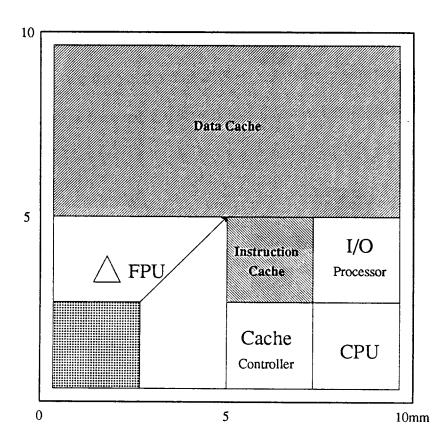

architectural and micro-architectural issues, to the details of logic and circuit design and the impact of scaling technology. A single-chip floating-point unit is also implemented, to better appreciate the tradeoffs through actual design. This FPU is one of three custom chips built as part of the SPUR project. SPUR, a multiprocessor workstation being developed at the University of California at Berkeley, is a research vehicle for studying symbolic and scientific computation in parallel processors. Research is being conducted in several areas: integrated circuits and technology, computer architecture, operating systems, and programming languages, and the system configuration is shown in Figure 1.

Figure 1.1. A SPUR Multiprocessor workstation system. The system includes as many as 12 processor nodes, each with its own central processor (CPU), floating-point unit FPU, and cache memory. The main components of the CPU are an on-chip instruction cache, a 32-bit datapath and control, and the FPU consists of exponent and fraction datapaths, together with separate control for arithmetic and memory operations. The shared global memory is accessed through a modified TI NuBus.

Salient features of the system include:

- architectural support for the Common Lisp programming language and the IEEE Standard for binary floating-point arithmetic,

- 6 to 12 high-performance processors per workstation with a modified NuBus backplane to memory and I/O devices,

- a common memory accessible by all nodes for sharing between cooperating processes,

- a 128-Kbyte direct-mapped cache between each CPU and common memory that significantly reduces bus traffic and effective memory access time,

- caching of virtual addresses, eliminating address translation on cache hits, and

- a hardware *snooping* mechanism that guarantees data shared between two or more processes is always consistent.

#### 1.2. Thesis Outline

The main body of the thesis consists of six chapters, beginning with a review of floating-point computation in Chapter 2, and continuing through design and implementation considerations of floating-point units, to the implications of scaling technology in Chapter 7. The final chapter concludes this thesis with a recapitulation of the issues addressed, emphasizing contributions in analysis and design, and finishing with suggestions and directions for future work.

To provide good support for scientific computation, we should understand what it is that computationally-intensive programs do. Chapter 2 begins by presenting a picture of the nature of scientific computation. Program measurements from the literature are collected, and critical, time-consuming loops of some representative programs are studied. The chapter concludes with a review of existing floating-point accelerators implemented in silicon. The architecture, instruction set design and performance of some of these processors are studied to better evaluate design and implementation

considerations. Even though some multi-chip implementations are considered, the emphasis is on single-chip implementations, since the tradeoffs are quite different for the two cases.

As floating-point units are getting faster, the problem of supplying them operands from memory is getting more severe. Chapter 3 identifies components of interface overhead, comparing the interfaces of two popular floating-point units with the coprocessor interface for SPUR, and outlining means of reducing overhead. The implications of implementing the IEEE Standard with a combination of hardware and software are presented, considering available VLSI technology. Of particular interest is support for extended precision arithmetic in a fast, non-microcoded machine. Chapter 3 also examines area-time tradeoffs in matching appropriate algorithms to available technology. Algorithms for all the basic arithmetic operations -- add, subtract, multiply and divide -- are considered, and their VLSI implementation implications presented.

Chapters 4 and 5 present datapath design considerations for performing data manipulations on memory operations and arithmetic functions. Among the arithmetic operations, add and subtract functions are discussed in Chapter 4, while Chapter 5 concentrates on multiplication and division. Area-time tradeoffs that went into the logic, circuit and layout design decisions of the key building blocks of the SPUR floating-point unit are presented.

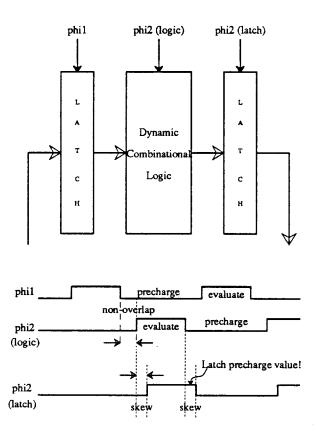

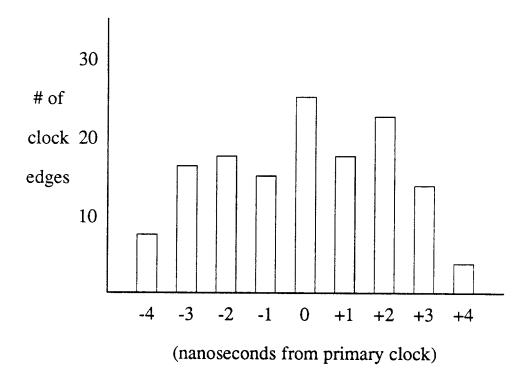

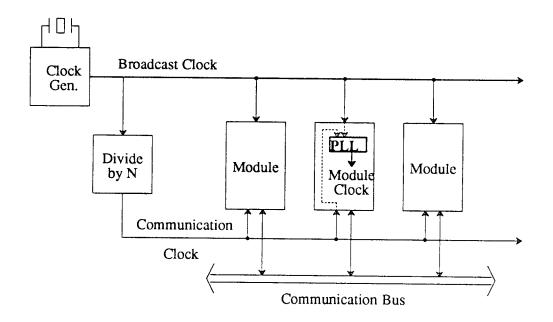

Design considerations for the control of memory and arithmetic operations in the SPUR FPU are presented in Chapter 6. The control of the FPU interface with the rest of the system is also described. Different components of the control unit are discussed, including the load-store pipeline, the state machine, and sequencer. Issues involving

clock generation, distribution and skew are also considered, especially in light of dynamic design techniques.

The effects of technology scaling on scientific computation are discussed in Chapter 7. The effects of scaling are pervasive across all levels of processor design, and all of these levels are inspected in turn, beginning with devices and circuits, through logic and micro-architecture, to algorithms and system architecture.

The appendices include design details specific to our case study, the SPUR FPU. A die photo of the SPUR FPU is shown in Appendix 1. The FPU instruction set and performance specifications of these instructions are presented in Appendix 2. Appendix 3 contains timing waveforms for various operations of the SPUR FPU, including memory and arithmetic operations.

#### 1.3. References

[Cody84] W. J. Cody, J. T. Coonen, D. M. Gay, K. Hansen, D. Hough, W. Kahan, R. Karpinski, J. Palmer, F. N. Ris and D.Stevenson, A Proposed Radix- and Word-length-independent Standard for Floating-point Arithmetic, *IEEE Micro*, Vol. 4, No. 4 (August 1984).

- [Fand85] J. Fandrianto and B. Y. Woo, VLSI Floating-point Processors, *Proc. Seventh IEEE Int' l. Symposium on Computer Arithmetic* (May 1985), pp. 93-100.

- [Hill86] M. D. Hill, S. J. Eggers, J. R. Larus, G. S. Taylor, G. Adams, B. K. Bose, G. A. Gibson, P. M. Hansen, J. Keller, S. I. Kong, C. G. Lee, D. Lee, J. M. Pendleton, S. A. Ritchie, D. A. Wood, B. G. Zorn, P. N. Hilfinger, D. Hodges, R. H. Katz, J. Ousterhout and D. A. Patterson, Design Decisions in SPUR, IEEE Computer, Vol. 19, No. 11 (November 1986).

- [Kaha85] W. Kahan, personal communication (April 1985).

- [Myer86] G. J. Myers, A. Y. C. Yu and D. L. House, Microprocessor Technology Trends, *Proceedings of the IEEE*, Vol. 74, No. 12 (December 1986), pp. 1605-1622.

# 2

# Floating-point Computation Characteristics and Accelerators

The first part of this chapter presents a picture of the nature of scientific computation, in an attempt to understand the behavior of numeric programs. Program measurements from the literature are collected, and critical, time-consuming loops of some representative programs are studied. This should provide insight into features that a floating-point unit should have, to enable it to execute such programs efficiently. This information will be used in successive chapters during the detailed discussions on design and implementation issues for VLSI floating-point processors.

The second part of this chapter reviews existing floating-point accelerators implemented in silicon. Rapid advances in integrated circuit technology are enabling significant developments in VLSI floating-point processor design. More than a dozen

processors have been designed in the last eight years, and the frequency of new designs is increasing. The instruction set features, interface characteristics and performance of several implementations will be compared, and their design considerations evaluated. The emphasis will be on single-chip VLSI implementations, even though a few multi-

chip designs will be included for comparison.

2.1. Characteristics of Floating-point Computation

Measurement of the important characteristics of scientific programs is essential for an understanding of the nature of floating-point computation. The kinds of operations performed, the nature of operands used, and the control sequences are studied here. The relative frequency of operations like add, subtract, and multiply should indicate design emphasis on required functional units, while the type, size, structure, and access frequency of operands used, should determine the memory organization. Studying the patterns of control transfer should provide insight into the nature and amount of extractable parallelism.

2.1.1. Frequently Used Functions

As a starting point, we begin by presenting three well-known functions [Kaha85] which form the core of many floating-point intensive applications:

Gaussian Elimination (GE) for i = 1 to n do X[i] := X[i] + (K \* Y[i])

Dot Product (DP) for i = 1 to n do P := P + (X[i] \* Y[i])

Polynomial Evaluation (PE) for

$$i = 1$$

to  $n$  do

$P := (P * K) + C[i]$

or as a continued fraction,

for  $i = 1$  to  $n$  do

$P := D[i]/P + C[i] + K$

Some common characteristics are evident from inspection of these simple equations. The operands are constants or array elements which are accessed in a regular arithmetic progression. The step size is one and the arrays are one-dimensional. The floating-point operations involve simple operators, with add and multiply being most frequent. The number of operations is of the order of the number of memory references, and while computation proceeds on current array elements, subsequent array elements can be loaded from memory simultaneously. A number of integer operations are needed to control the loop and are independent of the floating-point operations, allowing possible parallelism. Characteristics of floating-point operations for these loops is summarized in Table 2.1.

|       | Table 2.1: Characteristics of three loops - GE, DP, PE. |       |      |      |       |               |  |  |  |  |

|-------|---------------------------------------------------------|-------|------|------|-------|---------------|--|--|--|--|

| Loop  | Add                                                     | Mult- | Div- | Mem  | Mem   | FP operations |  |  |  |  |

| No.   | & Sub                                                   | iply  | ide  | Read | Write | per mem. ref. |  |  |  |  |

| GE    | 1                                                       | 1     | -    | 2    | 1     | 0.67          |  |  |  |  |

| DP    | 1                                                       | 1     | -    | 2    | -     | 1.00          |  |  |  |  |

| PE1   | 1                                                       | 1     | -    | 1    | -     | 2.00          |  |  |  |  |

| PE2   | 2                                                       | -     | 1    | 2    | -     | 1.50          |  |  |  |  |

| Total | 5                                                       | 3     | 1    | 7    | 1     | 9/8           |  |  |  |  |

| Mean  | 1.25                                                    | 0.75  | 0.25 | 1.75 | 0.25  | 1.13          |  |  |  |  |

This table indicates that operand reads occur about seven times as often as operand writes, and there are about eight memory references for every nine floating-point operations. Add and subtract operations occur almost twice as often as multiply, and divides occur about a third as often.

How representative is this set of equations? To answer this question, we look at several inner loops of programs written for scientific applications in the next sub-section.

### 2.1.2. Two Benchmarks, Linpack and Livermore Loops

Linpack [Dong79] is a set of programs for solving sets of linear equations; key routines perform LU decomposition and Gaussian elimination. The core of the subroutine performing matrix LU decomposition is shown below:

```

DO 60 K = N, 1, -1

XK = X(K)

DO 50 I = 1, K-1

X(I) = X(I) + A(I,K)*XK

50 CONTINUE

60 CONTINUE

```

As we can see, this is quite similar to the loop (GE) above, the only difference being the replacement of one one-dimensional array reference by a two-dimensional array reference.

The single and double precision Gaussian elimination routines in Linpack, sgefa and dgefa, do Gaussian elimination and backward substitution by calling subroutines saxpy and daxpy and functions sdot and ddot, whose cores are shown below:

```

I. DO 50 I = MP1,N,4

DY(I) = DY(I) + DA*DX(I)

DY(I+1) = DY(I+1) + DA*DX(I+1)

DY(I+2) = DY(I+2) + DA*DX(I+2)

DY(I+3) = DY(I+3) + DA*DX(I+3)

50 CONTINUE

II. DO 10 I = 1,N

DTEMP = DTEMP + DX(IX)*DY(IY)

DDOTCOUNT = DDOTCOUNT + 1

IX = IX + INCX

IY = IY + INCY

10 CONTINUE

```

Once again, the first loop consists of multiple applications of (GE) above, for four pairs of elements of arrays DX and DY, and the second loop is simply a dot product (DP) above.

The Livermore Loops [McMa86] are a set of 24 program kernels, taken from a wide range of numerically intensive application programs ranging from hydrodynamics through two-dimensional transport to Planckian distributions. Kernels 3, 5, and 21 involve simple operations on matrices, including inner product, tri-diagonal elimination and matrix product. Kernel 3 is the same as loop (DP), and kernels 5 and 21 are shown below:

We see two-dimensional arrays in kernel 21, but the form of both kernel calculations is similar to (GE) above, with the constant replaced by another array element. Kernels 4, 6, and 19 involve sets of linear equations, and these exhibit a form very similar to the examples above.

Kernel 9, called *Integrate Predictors*, is representative of several physical applications kernels, like kernels 7, 8 10, 13, 14, 18, and 23. These represent one and two-dimensional particles in cells, transport of discrete ordinates, two-dimensional hydrodynamics, and so on. Below is kernel 9:

```

DO 9 I = 1,N

PX( 1,I)= DM28*PX(13,I) + DM27*PX(12,I) + DM26*PX(11,I) +

DM25*PX(10,I) + DM24*PX( 9,I) + DM23*PX( 8,I) +

DM22*PX( 7,I) + C0*(PX( 5,I) + PX( 6,I))+ PX( 3,I)

9 CONTINUE

```

Several elements of array PX are multiplied by constants DM, and a sum of products evaluated; in some kernels, DM is also an array. Even though there is a lot more computation in this equation, the ratio of floating-point operations to memory references

is close to unity, and the loop control is still related to the array index and not on the array data, as in the first three examples.

Kernels 11 and 12 are a simple sum and difference of the elements of a vector.

Kernel 1 contains an inner loop from a hydrodynamics fragment simulator, and conforms to previous examples.

Kernels 15, 16, 17, 20, 22 and 24 contain all the floating-point *compare* instructions in the 24 loops. They all involve accessing arrays in a regular manner, but control sequencing depends on the actual data accessed. An example code segment from kernel 20 is shown below. The frequency of *compare* instructions is small compared to arithmetic instructions.

```

DO 20 L= 1,LOOP

DO 20 K= 1,N

DI= Y(K)-G(K)/( XX(K)+DK)

DN= 0.2

IF( DI .NE. 0.0) DN= MAX( 0.1,MIN( Z(K)/DI, 0.2))

X(K)= ((W(K)+V(K)*DN)* XX(K)+U(K))/(VX(K)+V(K)*DN)

XX(K+1)= (X(K)- XX(K))*DN+ XX(K)

20 CONTINUE

```

Table 2.2 summarizes the characteristics of the 24 Livermore Loops. The frequency distribution of arithmetic operations and conditionals is shown, as well as unique memory accesses for read and write. The ratio of floating-point operations to memory references is noted in the last column.

Note the similarity in the trends represented in Tables 2.1 and 2.2. The relative frequency of individual operations is similar in both cases, and so is the ratio of memory reads to memory writes and floating-point operations to memory references.

| Table 2.2: Characteristics of the 24 Livermore Loops. |       |       |      |        |        |             |       |               |

|-------------------------------------------------------|-------|-------|------|--------|--------|-------------|-------|---------------|

| Loop                                                  | Add   | Mult- | Div- | Square | Com-   | Mem         | Mem   | FP operations |

| No.                                                   | & Sub | iply  | ide  | Root   | pare   | Read        | Write | per mem. ref. |

| 1                                                     | 2     | 3     | -    | -      | -      | 3           | 1     | 1.25          |

| 2                                                     | 2     | 2     | -    | -      | -      | 5           | 1     | 0.67          |

| 3                                                     | 1     | 1     | -    | _      | -      | 5<br>2<br>4 | -     | 1.00          |

| 4                                                     | 1     | 2     | -    | -      | -      |             | 2     | 0.50          |

| 5                                                     | 1     | 1     | -    | -      | -      | 3           | 1     | 0.50          |

| 6                                                     | 1     | 1     | -    | -      | -      | 3           | 1     | 0.50          |

| 7                                                     | 8     | 8     | -    | -      | -      | 9           | 1     | 1.60          |

| 8                                                     | 20    | 12    | -    | -      | -      | 27          | 6     | 0.97          |

| 9                                                     | 9     | 8     | -    | -      | -      | 10          | 1     | 1.55          |

| 10                                                    | 9     | -     | -    | -      | -      | 10          | 10    | 0.45          |

| 11                                                    | 1     | -     | -    | •      | -      | 2           | 1     | 0.33          |

| 12                                                    | 1     | -     | -    | -      | -      | 2           | 1     | 0.33          |

| 13                                                    | 9     | -     | -    | -      | -      | 19          | 7     | 0.35          |

| 14                                                    | 10    | 1     | -    | -      | -      | 21          | 12    | 0.33          |

| 15                                                    | 2     | 6     | 2    | 2      | 7      | 20          | 4     | 0.79          |

| 16                                                    | 5     | 4     | -    | -      | 5<br>2 | 11          | -     | 1.27          |

| 17                                                    | 6     | 2     | -    | -      | 2      | 5           | 5     | 1.00          |

| 18                                                    | 26    | 14    | 2    | -      | -      | 46          | 6     | 0.81          |

| 19                                                    | 4     | 2     | -    | -      | -      | 6           | 2     | 0.75          |

| 20                                                    | 6     | 4     | 2    | -      | 2      | 13          | 2     | 0.93          |

| 21                                                    | 1     | 1     | -    | -      | -      | 3           | 1     | 0.50          |

| 22                                                    | -     | 3     | 2    | -      | 1      | 6           | 3     | 0.67          |

| 23                                                    | 6     | 5     | -    | -      | -      | 11          | 1     | 0.92          |

| 24                                                    | -     | -     | -    | -      | 1      | 2           | -     | 0.50          |

| Total                                                 | 131   | 80    | 8    | 2      | 18     | 243         | 69    | 239/312       |

| Mean                                                  | 5.5   | 3.3   | 0.3  | 0.1    | 0.8    | 10.1        | 2.9   | 0.77          |

This table indicates that operand reads occur about three times as often as operand writes, and there are about four memory references for every three floating-point operations. Add and subtract operations occur almost twice as often as multiply, and divides occur about a tenth as often. Compares occur about a fourth as often as multiply, while a special function, square root, occurs a third as often as divide.

Note also the scope for parallelism in the above examples at various levels. When long expressions are computed, with no control transfers in between, several floating-point operations can be executed in parallel if multiple function units are available. For example, independent sub-expressions involving additions and multiplications can be evaluated simultaneously if there are independent add and multiply units. Again, integer or loop counter calculations can be computed in parallel with floating-point computation. Finally, address calculation and memory references can also proceed in parallel with

floating-point computation. This is especially important because of the relatively high ratio of memory accesses to floating-point operations, and the problem is compounded when memory accesses involve the transfer of 64-bit words.

#### 2.1.3. Dynamic Data From Two Real Programs

So far, we have been looking at the static distribution of operands and operations in a variety of inner loops of numeric software. To see if and how the picture changes with the dynamic behavior of large scientific programs, let us now look at profiles gathered by Lin and Leung [Leun86] by running two real programs, *SPICE* [Nage73] and *Lattice* [Brod86], both developed at Berkeley. *SPICE* is a circuit simulator and *Lattice* simulates different lattice filter structures. Analog and digital circuits in different technologies are used as inputs to *SPICE*, to minimize sensitivity to input data, and the analytical (Level 2) device models are used. Instruction frequency is measured for different types of analyses: DC, AC, and transient. Similarly, speech and other data, including random, are used as inputs to *Lattice*. Table 2.3 shows the measured frequency of floating-point operations for these two programs, totaled over all the different inputs.

Lattice does not make any calls to special functions like transcendentals, while SPICE makes some references, especially when performing transient analysis. Table 2.4 shows the frequency of basic floating-point operations with calls to special functions decomposed into the basic functions.

Table 2.5 shows the percentage increase in frequency of each basic function after the special functions are decomposed. It is critical not to ignore some special functions just because they occur infrequently. Examining a profile of the *SPICE* run, for example,

| Table 2.3       | Table 2.3: Frequency of Floating-point Operations for Two Real Programs. |         |         |           |           |       |  |  |

|-----------------|--------------------------------------------------------------------------|---------|---------|-----------|-----------|-------|--|--|

| Operations      | Lattice                                                                  | SPICE   | SPICE   | SPICE     | SPICE     | SPICE |  |  |

| (Dbl Precision) | Filter                                                                   | DC      | AC      | Transient | Total     | Ratio |  |  |

| Add             | 3,186,800                                                                | 317,058 | 168,643 | 1,337,381 | 1,823,082 | 0.54  |  |  |

| Subtract        | 3,980,400                                                                | 399,668 | 238,970 | 1,818,824 | 2,457,462 | 0.72  |  |  |

| Multiply        | 9,548,000                                                                | 495,528 | 358,680 | 2,544,974 | 3,399,182 | 1.00  |  |  |

| Divide          | 793,600                                                                  | 177,312 | 52,726  | 917,469   | 1,147,507 | 0.34  |  |  |

| Compare         | 1,587,200                                                                | 259,534 | 56,681  | 1,124,872 | 1,441,087 | 0.42  |  |  |

| Sq. Root        | -                                                                        | 24,581  | 2,465   | 126,162   | 153,208   | 0.05  |  |  |

| Sine            | -                                                                        | 5       | 79      | 5         | 89        | 0.00  |  |  |

| Cosine          | -                                                                        | 942     | 153     | 5,139     | 6,234     | 0.00  |  |  |

| Arc Tangent     | -                                                                        | 937     | 74      | 5,133     | 6,144     | 0.00  |  |  |

| Exp             | -                                                                        | 3,593   | 465     | 44,708    | 48,766    | 0.01  |  |  |

| Log             | -                                                                        | 3,558   | 382     | 49,882    | 53,822    | 0.02  |  |  |

| Log10           | -                                                                        | 2       | 170     | 2         | 174       | 0.00  |  |  |

Other special functions, such as arc sin, were also monitored, but did not register any occurrence for the set of inputs. *Lattice* shows more multiply operations than add and subtract combined, while *SPICE* shows a ratio similar to the static distribution of the Livermore Loops. *Lattice* also shows relatively fewer Compare operations compared to *SPICE*.

| Table 2.4: Increased basic operations with special functions decomposed. |         |         |           |           |       |  |

|--------------------------------------------------------------------------|---------|---------|-----------|-----------|-------|--|

| Operation (Dbl Precision)                                                | SPICE   | SPICE   | SPICE     | SPICE     | SPICE |  |

|                                                                          | DC      | AC      | Transient | Total     | Ratio |  |

| Add                                                                      | 533,206 | 195,009 | 2,876,128 | 3,604,343 | 0.66  |  |

| Subtract                                                                 | 411,890 | 240,525 | 1,961,520 | 2,613,935 | 0.48  |  |

| Multiply                                                                 | 752,910 | 389,319 | 4,313,842 | 5,456,071 | 1.00  |  |

| Divide                                                                   | 314,179 | 67,171  | 1,711,441 | 2,092,791 | 0.38  |  |

| Compare                                                                  | 314,257 | 62,272  | 1,426,741 | 1,803,270 | 0.33  |  |

The last column shows the ratio of basic operations normalized to multiply. This ratio has not changed significantly even after all special function calls have been reduced to a sequence of basic operations.

| Table 2.5: Percentage increase in basic operations |        |        |               |           |  |  |

|----------------------------------------------------|--------|--------|---------------|-----------|--|--|

| Operation                                          | SPICE  | SPICE  | SPICE         | SPICE     |  |  |

| (Dbl Precision)                                    | DC (%) | AC (%) | Transient (%) | Total (%) |  |  |

| Add                                                | 68.1   | 15.6   | 115.1         | 97.7      |  |  |

| Subtract                                           | 3.1    | 0.7    | 7.8           | 6.4       |  |  |

| Multiply                                           | 51.9   | 8.5    | 69.5          | 60.5      |  |  |

| Divide                                             | 77.2   | 27.4   | 86.5          | 82.3      |  |  |

| Compare                                            | 21.1   | 9.9    | 26.8          | 25.1      |  |  |

It is interesting to note that even though the absolute frequencies of the special functions like square root and exponential seem to be a small percentage of the total operations, once decomposed the special functions add a significant percentage to the frequency of the basic operations.

on a SUN 3/160 with a Motorola 68881 floating-point unit, we measured that transcendental functions account for 16.1% of the total execution time. If transcendental functions are a factor of 10 slower, their evaluation would account for 10\*16/(84+10\*16) or 71% of the time. And if transcendentals evaluate 100 times slower, they could account for 100\*16/(84+100\*16) or 95% of the time! Since transcendental function evaluation is frequently reduced to a sequence of basic operations, it is critical that these basic operations evaluate as fast as possible.

There have been several studies of various programs and benchmarks that show the relative frequency of these basic operations. We summarize results from Berkeley with those of Knuth [Knut71] and Gibson [Gibs70] in Table 2.6. We see that add/subtract operations occur from 1.5 to 2.5 times more frequently than multiply operations, which in turn are 2 to 3 times as frequent as divide operations. The Lattice Filter seems to be an exception in that divisions occur much less often than in the others, and additions occur less frequently than multiplications.

Table 2.6 suggests chip resource allocation for a balanced design, where the proportion of hardware for add vs. multiply vs. divide should be close to the ratio of operation frequency. For example, a large chip area invested in an array multiplier may not be cost-effective without a proportionately fast adder and divider. If the product of operation frequency and operation delay for all the basic operations is almost equal, then the designers of software algorithms will not be tempted to devise devious means to achieve performance, which they would resort to if this product is very different for the distinct basic functions.

| Table 2.6: Relative Frequencies of Floating Point Operations |                      |          |        |  |  |

|--------------------------------------------------------------|----------------------|----------|--------|--|--|

| Source                                                       | Add,Subtract,Compare | Multiply | Divide |  |  |

| Knuth                                                        | 2.30                 | 1.00     | 0.38   |  |  |

| Gibson Mix                                                   | 1.80                 | 1.00     | 0.39   |  |  |

| Lattice Filter                                               | 0.75                 | 1.00     | 0.08   |  |  |

| SPICE                                                        | 1.45                 | 1.00     | 0.35   |  |  |

Operation frequencies are normalized to Multiply. Divides occur about a third as often, and Adds occur between 1.5 and 2.5 times as often as Multiplies.

Now that we have a picture of the nature of scientific computation, let us see if current designs of floating-point accelerators reflect this view, and what features enable efficient execution of numeric software.

### 2.2. Comparison of Floating-point Processors

Advances in integrated circuit technology are largely responsible for the relatively recent appearance of floating-point accelerators in VLSI. For example, the earliest floating-point units -- the Intel 8087 and the Motorola 68881 -- appeared in 1980 and 1983 respectively, and several floating-point units have been released in the last couple of years. Current VLSI floating-point processors fall into two main categories, comprehensive and basic, based on their functionality [Fand85]. The comprehensive floating-point processors usually have a rich repertoire of functions, on-chip storage and control store. They rely on built-in microcode routines to execute the basic arithmetic operations as well as many of the special operations like square root and logarithm. The basic floating-point units, on the other hand, tend to provide a small, basic set of functions, using dedicated hardware to optimize the performance of specific arithmetic functions. While the comprehensive processors provide generality and versatility with moderate performance, the basic processors can provide higher performance because of

their specificity.

## 2.2.1. Comprehensive Floating-point Processors

Examples of comprehensive floating-point processors include the Intel 8087/80287, National 32081, Motorola 68881, Zilog 8070, AMD 9511A/9512 and Fairchild F9450 [Nave80] [Gavr86] [Shah84] [Heni83]. Table 2.7 summarizes the instruction set features for four of these processors, including the year they were released.

| Table 2.7: Instruction set features of four comprehensive FPUs. |          |          |          |          |  |

|-----------------------------------------------------------------|----------|----------|----------|----------|--|

| Instruction                                                     | Intel    | Motorola | National | Zilog    |  |

| Set Design                                                      | 8087     | 68881    | 32081    | 8070     |  |

| Year sampled                                                    | 1980     | 1983     | 1983     | 1985     |  |

| IEEE Std.#754 coverage                                          | complete | complete | subset   | complete |  |

| Instruction length                                              | 16-32    | 32-48    | 8-24     | 16-32    |  |

| Number of formats                                               | 2        | 6        | 2        | 2        |  |

| Number of data types                                            | 7        | 7        | 5        | 7        |  |

| Max. # operands/instr.                                          | 2        | 2        | 2        | 6        |  |

| F.P. Instructions                                               |          |          |          |          |  |

| +,-,×,+, compare                                                | •        | •        | •        | •        |  |

| Square root                                                     | •        | •        |          | •        |  |

| Data transfer                                                   | •        | •        | •        | •        |  |

| Data conversion                                                 |          |          | •        |          |  |

| Integer operations                                              | •        |          | •        |          |  |

| Transcendentals                                                 | •        | •        |          | •        |  |

Most comprehensive FPUs cover the IEEE Floating-point standard, and provide instructions for special functions like square root and transcendentals. In particular, the Intel and Motorola FPUs are full-function processors. They do not need data conversion instructions because results are computed in any one of three desired precisions.

These processors tend to display rather different interface characteristics, and these are summarized in Table 2.8. The implementation technologies are also quite different, leading primarily to a wide range of clock frequencies. All of them allow parallel execution between floating-point and integer execution units, even though some of these systems are more tightly coupled than others.

Chapter 2 22

| Table 2.8: Interface characteristics of four comprehensive FPUs. |               |                   |                   |               |  |  |

|------------------------------------------------------------------|---------------|-------------------|-------------------|---------------|--|--|

| Interface<br>Characteristics                                     | Intel<br>8087 | Motorola<br>68881 | National<br>32081 | Zilog<br>8070 |  |  |

| Data bus width                                                   | 16            | 8,16,32           | 16                | 32            |  |  |

| # of operand regs                                                | 8             | 8                 | 8                 | 10            |  |  |

| Register width                                                   | 80            | 80                | 32                | 80            |  |  |

| Clock Frequency                                                  | 5MHz          | 16.7MHz           | 10MHz             | 10MHz         |  |  |

| Technology                                                       | 3μ HMOS       | 2.25µ HCMOS       | 3μ XMOS           | 2μ XMOS       |  |  |

| Control implementation                                           | microcode     | microcode         | hardwired         | microcode     |  |  |

| Extended Precision                                               | yes           | yes               | no                | yes           |  |  |

| Exception detection                                              | hardware      | hardware          | hw/software       | hw/software   |  |  |

| Exception handling                                               | hardware      | hardware          | software          | hw/software   |  |  |

Most of these *comprehensive* FPUs have microcoded control and provide support for extended (80-bit) precision arithmetic. Exception detection is mostly done in hardware, and exception handling is also done by hardware in several cases.

#### 2.2.2. Basic Floating-point Processors

Examples of basic floating-point processors include the Weitek 1164/65 chip set, AMD 29325, Fairchild Clipper, Analog Devices ADSP 3210/3220 chip set, Western Electric WE32106 and MIPS R3010 [Fand85] [Trou86] [Neff86] [Rowe88]. Table 2.9 summarizes the instruction set features for four of these processors, including the year they were released. Weitek splits floating-point operations among two chips, one for Multiply and the other for Add, Subtract and Divide. Even though the algorithmic tradeoffs are quite different going from one-chip to multi-chip design, it is included here as a comparison. The Fairchild Clipper, on the other hand, integrates the integer and floating-point units on a single chip. Even with severe die size constraints, it achieves fairly high floating-point performance by virtue of its high clock rate, as we shall see later in Table 2.11.

Table 2.10 shows the interface characteristics of these *basic* floating-point processors. While exception detection is usually done by these processors in hardware, most exception handling is normally left for software. One common exception is

| Table 2.9: Ins         | Table 2.9: Instruction set features of four basic FPUs. |           |               |        |  |  |  |

|------------------------|---------------------------------------------------------|-----------|---------------|--------|--|--|--|

| Instruction            | Weitek                                                  | Fairchild | Western Elec. | MIPS   |  |  |  |

| Set Design             | 1164/1165                                               | Clipper   | 32106         | R3010  |  |  |  |

| Year sampled           | 1985                                                    | 1986      | 1987          | 1988   |  |  |  |

| IEEE Std.#754 coverage | subset                                                  | subset    | complete      | subset |  |  |  |

| Instruction length     | 3,4,6                                                   | 16-64     | 32            | 32     |  |  |  |

| Number of formats      | 5                                                       | 11        | 1             | 3      |  |  |  |

| Number of data types   | 3                                                       | 10        | 5             | 2      |  |  |  |

| Max. # operands/instr. | 2                                                       | 2         | 3             | 3      |  |  |  |

| F.P. Instructions      |                                                         |           |               |        |  |  |  |

| +,-,×,+, compare       | •                                                       | •         | •             | •      |  |  |  |

| Square root            |                                                         |           | •             |        |  |  |  |

| Data transfer          | •                                                       | •         | •             | •      |  |  |  |

| Data conversion        | •                                                       |           | •             | •      |  |  |  |

| Integer operations     |                                                         |           |               |        |  |  |  |

| Transcendentals        |                                                         |           |               |        |  |  |  |

In contrast with the *comprehensive* FPUs, most of these *basic* processors are newer, provide only a subset of the IEEE standard, and provide only instructions for basic functions, data transfer and data conversion.

*inexact*, implying that rounding was performed on the result. It is usually handled by the hardware.

| Table 2.10: Interface characteristics of four basic FPUs. |           |           |               |           |  |  |

|-----------------------------------------------------------|-----------|-----------|---------------|-----------|--|--|

| Interface                                                 | Weitek    | Fairchild | Western Elec. | MIPS      |  |  |

| Characteristics                                           | 1164/1165 | Clipper   | 32106         | R3010     |  |  |

| Data bus width                                            | 64        | 32        | 32            | 32        |  |  |

| # of operand regs                                         | 2         | 8         | 4             | 16        |  |  |

| Register width                                            | 64        | 64        | 80            | 64        |  |  |

| Clock Frequency                                           | 20MHz     | 33.3MHz   | 17.8MHz       | 25MHz     |  |  |

| Technology                                                | 2.5µ NMOS | 2μ CMOS   | 1.75μ CMOS    | 1.6µ CMOS |  |  |

| Control implementation                                    | hardwired | hardwired | hardwired     | hardwired |  |  |

| Extended Precision                                        | no        | по        | yes           | no        |  |  |

| Exception detection                                       | hardware  | hardware  | hardware      | hardware  |  |  |

| Exception handling                                        | software  | software  | software      | software  |  |  |

Clock frequencies are increasing with improving technology, and few provide support for more than single and double precision. Control is hardwired, and the handling of exceptions is left up to software trap handlers.

## 2.2.3. Floating-point Performance Comparison

The performance of eight comprehensive and basic floating-point units in computing basic arithmetic operations are compared in Table 2.11. The table is in three parts, representing three different precisions of arithmetic with register operands.

| Table 2.11a: Single Precision Floating-Point Performance Comparison. |          |               |             |  |  |

|----------------------------------------------------------------------|----------|---------------|-------------|--|--|

| Implementation                                                       | Add (μs) | Multiply (µs) | Divide (µs) |  |  |

| Intel 8087                                                           | 8.50     | 9.70          | 19.80       |  |  |

| Motorola 68881                                                       | 2.88     | 4.20          | 6.12        |  |  |

| National 32081                                                       | 7.40     | 4.80          | 8.90        |  |  |

| Zilog 8070                                                           | 1.80     | 2.80          | 2.90        |  |  |

| Weitek 1164/1165                                                     | 0.15     | 0.15          | 1.25        |  |  |

| Fairchild Clipper                                                    | 0.36     | 0.72          | 2.82        |  |  |

| Western Elec. 32106                                                  | 2.80     | 2.80          | 16.80       |  |  |

| MIPS R3010                                                           | 0.08     | 0.16          | 0.48        |  |  |

| Table 2.11b: Double Precision Floating-Point Performance Comparison. |          |                                  |       |  |  |  |

|----------------------------------------------------------------------|----------|----------------------------------|-------|--|--|--|

| Implementation                                                       | Add (µs) | Add (μs) Multiply (μs) Divide (μ |       |  |  |  |

| Intel 8087                                                           | 8.50     | 13.80                            | 19.80 |  |  |  |

| Motorola 68881                                                       | 2.88     | 4.20                             | 6.12  |  |  |  |

| National 32081                                                       | 7.40     | 6.20                             | 11.90 |  |  |  |

| Zilog 8070                                                           | 1.80     | 4.20                             | 4.30  |  |  |  |

| Weitek 1164/1165                                                     | 0.15     | 0.25                             | 2.70  |  |  |  |

| Fairchild Clipper                                                    | 0.42     | 2.07                             | 5.46  |  |  |  |

| Western Elec. 32106                                                  | 2.80     | 2.80                             | 16.80 |  |  |  |

| MIPS R3010                                                           | 0.08     | 0.20                             | 0.76  |  |  |  |

| Table 2.11c: Extended P. | recision Floating | g-Point Performance | e Comparison. |

|--------------------------|-------------------|---------------------|---------------|

| Implementation           | Add (µs)          | Multiply (µs)       | Divide (µs)   |

| Intel 8087               | 8.50              | 13.80               | 19.80         |

| Motorola 68881           | 1.80              | 3.12                | 5.04          |

| National 32081           | -                 | -                   | -             |

| Zilog 8070               | 1.80              | 4.80                | 4.90          |

| Weitek 1164/1165         | -                 | -                   | -             |

| Fairchild Clipper        | -                 | -                   | -             |

| Western Elec. 32106      | 2.80              | 2.80                | 16.80         |

| MIPS R3010               | -                 | -                   | -             |

The basic processors generally have significantly less latency for the basic arithmetic functions, although they provide less functionality. Versatility and performance are inversely correlated, with the silicon area devoted to versatility being converted to speeding up basic functions.

Since the implementation technology varies significantly for these processors, and so do their cycle times or clock frequencies, Table 2.12 compares floating-point performance using the number of cycles needed to complete these basic arithmetic operations.

| Table 2.12a: Single Precision Floating-Point Performance Comparison. |                                |    |                 |  |  |

|----------------------------------------------------------------------|--------------------------------|----|-----------------|--|--|

| Implementation                                                       | Add (cycles) Multiply (cycles) |    | Divide (cycles) |  |  |

| Intel 8087                                                           | 85                             | 97 | 198             |  |  |

| Motorola 68881                                                       | 48                             | 70 | 102             |  |  |

| National 32081                                                       | 74                             | 48 | 89              |  |  |

| Zilog 8070                                                           | 18                             | 28 | 29              |  |  |

| Weitek 1164/1165                                                     | 3                              | 3  | 28              |  |  |

| Fairchild Clipper                                                    | 12                             | 24 | 94              |  |  |

| Western Elec. 32106                                                  | 50                             | 50 | 300             |  |  |

| MIPS R3010                                                           | 2                              | 4  | 12              |  |  |

| Table 2.12b: Double Precision Floating-Point Performance Comparison. |              |                   |                 |  |  |

|----------------------------------------------------------------------|--------------|-------------------|-----------------|--|--|

| Implementation                                                       | Add (cycles) | Multiply (cycles) | Divide (cycles) |  |  |

| Intel 8087                                                           | 85           | 138               | 198             |  |  |

| Motorola 68881                                                       | 48           | 70                | 102             |  |  |

| National 32081                                                       | 74           | 62                | 119             |  |  |

| Zilog 8070                                                           | 18           | 42                | 43              |  |  |

| Weitek 1164/1165                                                     | 3            | 5                 | 57              |  |  |

| Fairchild Clipper                                                    | 14           | 69                | 182             |  |  |

| Western Elec. 32106                                                  | 50           | 50                | 300             |  |  |

| MIPS R3010                                                           | 2            | 5                 | 19              |  |  |

| Table 2.12c: Extended Precision Floating-Point Performance Comparison. |              |                   |                 |  |  |

|------------------------------------------------------------------------|--------------|-------------------|-----------------|--|--|

| Implementation                                                         | Add (cycles) | Multiply (cycles) | Divide (cycles) |  |  |

| Intel 8087                                                             | 85           | 138               | 198             |  |  |

| Motorola 68881                                                         | 30           | 52                | 84              |  |  |

| National 32081                                                         | -            | -                 | +               |  |  |

| Zilog 8070                                                             | 18           | 48                | 49              |  |  |

| Weitek 1164/1165                                                       | -            | -                 | _               |  |  |

| Fairchild Clipper                                                      | -            | <u>-</u>          | -               |  |  |

| Western Elec. 32106                                                    | 50           | 50                | 300             |  |  |

| MIPS R3010                                                             | -            | •                 | -               |  |  |

With better technology, it is possible for the newer processors to implement more aggressive algorithms, leading to a significant decrease in the number of cycles to perform the basic functions.

Chapter 2 26

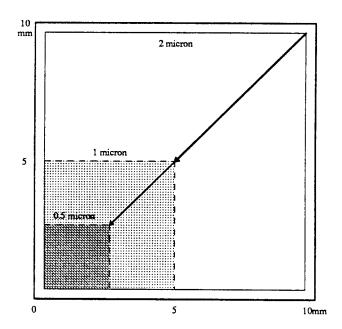

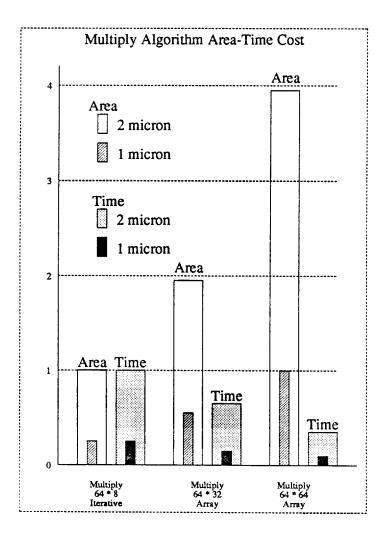

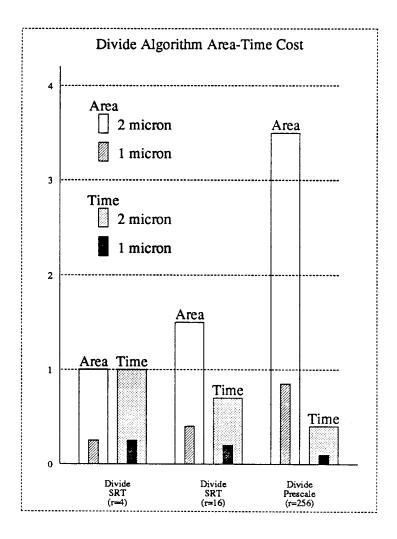

As clock frequencies increase with improving technology, the absolute times per function will decrease, but for the same algorithm, the number of cycles stays invariant. The comparison is complicated by the fact that, in practice, scaling technology directly affects the choice of algorithms implemented. For example, an iterative multiplier was feasible in 3 $\mu$  HMOS, but an array multiplier is practicable in 1.5 $\mu$  CMOS (see Chapter 7). The array multiplier should require fewer cycles than the iterative multiplier, and the cycle time in 1.5 $\mu$  CMOS is also less than 3 $\mu$  HMOS, thus leading to further speed-up than implied by classical scaling considerations.

Table 2.13 shows the ratio of operation speeds normalized to multiply, for each of these floating-point units for double precision. Variations in technology, architecture and algorithms, lead to variations in the speeds of individual operations by as much as a factor of 40, but it is interesting to see the disparity narrow as we compare relative operation speeds within each processor.

| Table 2.13: Relative speed of basic operations normalized to Multiply |      |          |        |  |  |

|-----------------------------------------------------------------------|------|----------|--------|--|--|

| Implementation                                                        | Add  | Multiply | Divide |  |  |

| Intel 8087                                                            | 1.62 | 1.00     | 0.70   |  |  |

| Motorola 68881                                                        | 1.46 | 1.00     | 0.69   |  |  |

| National 32081                                                        | 0.84 | 1.00     | 0.52   |  |  |

| Zilog 8070                                                            | 2.33 | 1.00     | 0.98   |  |  |

| Weitek 1164/1165                                                      | 1.67 | 1.00     | 0.09   |  |  |

| Fairchild Clipper                                                     | 4.93 | 1.00     | 0.38   |  |  |

| Western Elec. 32106                                                   | 1.00 | 1.00     | 0.17   |  |  |

| MIPS R3010                                                            | 2.50 | 1.00     | 0.26   |  |  |

The above performance numbers are for double precision operations. From Table 2.6 we find that, normalized to multiply, the relative frequencies of add/subtract are 1.5 to 2.3, and divide are 0.25 to 0.5 for several programs. Based on these relative frequencies, it appears that National 32081 and Western Electric 32106 addition units and the Weitek 1164/1165 divide unit are disproportionately slow, while the Zilog 8070 divide unit and the Fairchild Clipper addition unit are disproportionately fast.

#### 2.3. Summary

Several programs were studied to provide insight into the nature of scientific computation. Three simple loops, computing Gaussian elimination (GE), dot product (DP), and polynomial evaluation (PE) seem to be representative of a wide range of floating-point applications. Common characteristics that emerge from static and dynamic measurements are:

- operands are mostly array elements, accessed in a regular arithmetic progression;

- most arithmetic operations are simple, with add/subtract, multiply and divide instructions occurring most often;

- add/subtract operations occur almost twice as often as multiply, while divide occurs about a third as often as multiply;

- memory reads occur almost three times as often as memory writes, and the ratio of floating-point operations to memory references falls in a small range close to unity;

- there is scope for parallelism in floating-point computation at various levels, including overlap with integer computations, memory accesses, and simultaneous evaluation of sub-expressions.

Floating-point units were compared with respect to instruction set, interface and performance. FPUs fall broadly into two categories based on functionality, and increased functionality comes at the price of reduction in basic operation speeds. As technology improves, clock rates increase and more aggressive arithmetic algorithms can be implemented, leading to greater speed-ups than expected simply by classical scaling.

Several factors need to be considered when considering any of these floating-point processors in an actual system. Just as important as the algorithms and implementation are the interface of the floating-point unit to the rest of the system. It is not enough to merely have a fast floating-point unit; we need to meet the demand for operands from memory as well. An efficient interface is essential for obtaining any significant system

Chapter 2 28

speed-up, and this will be discussed in the next chapter, together with tradeoffs for fast algorithms and efficient implementations.

#### 2.4. References

- [Brod86] R. W. Brodersen and H. Murviet, An Integrated Circuit Based Speech Recognition System, *IEEE Trans. Accoustics, Speech and Signal Processing*, Vol. ASSP-34, No. 6 (December 1986), pp. 1465-1472.

- [Dong79] J. J. Dongarra, J. R. Bunch, C. B. Moler and G. W. Stewart, LINPACK Users' Guide, SIAM Publications (1979).

- [Fand85] J. Fandrianto and B. Y. Woo, VLSI Floating-point Processors, *Proc. Seventh IEEE Int' l. Symposium on Computer Arithmetic* (May 1985), pp. 93-100.

- [Gavr86] M. Gavrielov and L. Epstein, The NS32081 Floating-Point Unit, *IEEE Micro*(April 1986), pp. 6-12.

- [Gibs70] J. C. Gibson, The Gibson Mix, IBM Systems Development Division Tech. Report(June 1970).

- [Heni83] A. Heninger, The Zilog Z8070 Floating-Point Processor, Mini-Micro West (1983).

- [Kaha85] W. Kahan, personal communication (April 1985).

- [Knut71] D. Knuth, An Empirical Study of Fortran Programs, Software Practice and Experience, Vol. 1, No. 2 (1971), pp. 105-133.

- [Leun86] B. Leung and Y. M. Lin, Statistics on Floating-point Arithmetic, CS 252 Class Project(May 1986).

- [McMa86] F. H. McMahon, The Livermore Fortran Kernels: A Computer Test of the Numerical Performance Range, UCRL-53745, Lawrence Livermore National Laboratory (December 1986).

- [Nage73] L. Nagel and D. Pederson, Simulation Program with Integrated Circuit Emphasis (SPICE), 16th Midwest Symposium on Circuit Theory, Waterloo, Ontario (April 12, 1973).

- [Nave80] R. Nave and J. Palmer, A Numeric Data Processor, *Proc. Intl. Solid-State Circuits Conference*(February 1980), pp. 108-109.

- [Neff86] L. Neff, Clipper Microprocessor Architecture Overview, *Proceedings of Spring COMPCON*(March 4-6 1986), pp. 191-195.

- [Rowe88] C. Rowen, The MIPS R3010 Floating-point Coprocessor, *IEEE Micro*(June 1988), pp. 53-62.

- [Shah84] V. Shahan, The MC68881: The IEEE Floating Point Standard Reduced to One VLSI Chip, *Proc. IEEE Computer Conference*(March 1984), pp. 172-176.

- [Trou86] W. W. Troutman, Design of a Standard Floating-Point Chip, *IEEE J. of Solid-State Circuits*, Vol. SC-21, No.3(June 1986), pp. 396-399.

# 3

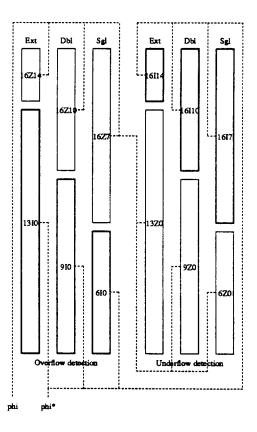

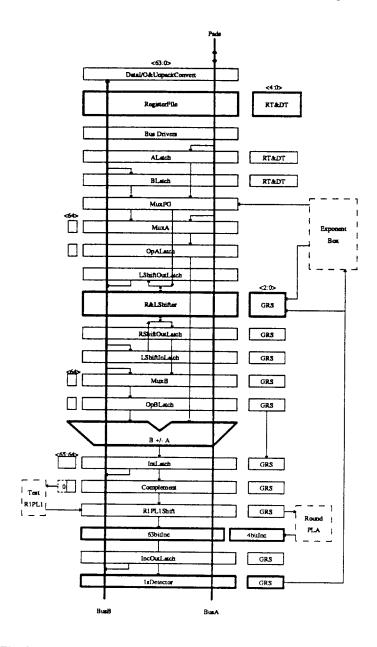

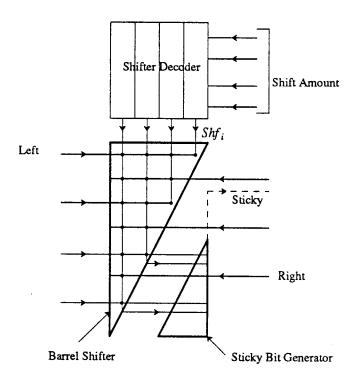

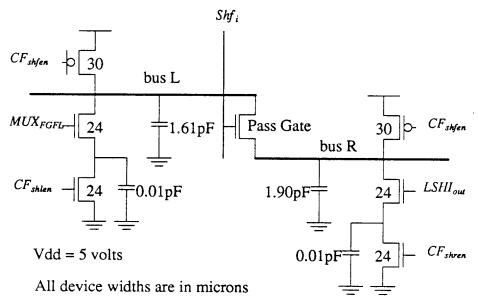

# Design Tradeoffs for VLSI Floating-Point Units