Copyright © 1988, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# AN INTEGRATED CAD SYSTEM FOR ALGORITHM-SPECIFIC IC DESIGN

by

Chuen-Shen Shung

Memorandum No. UCB/ERL M88/44

14 June 1988

# AN INTEGRATED CAD SYSTEM FOR ALGORITHM-SPECIFIC IC DESIGN

by

Chuen-Shen Shung

Memorandum No. UCB/ERL M88/44

14 June 1988

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# AN INTEGRATED CAD SYSTEM FOR ALGORITHM-SPECIFIC IC DESIGN

by

Chuen-Shen Shung

Memorandum No. UCB/ERL M88/44

14 June 1988

•

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# An Integrated CAD System for Algorithm-Specific IC Design

Ph.D.

Chuen-Shen Shung

**EECS** Department

## ABSTRACT

LagerIII, an integrated CAD system for algorithm-specific IC design is described. In particular, applications such as speech processing, image processing, telecommunication, and robot control are targeted. Designing such circuits usually requires the collaboration of algorithm developers, architecture designers, and circuit designers. LagerIII provides the user interface at behavioral, structural, and physical levels to facilitate this collaboration. It also provides an interface for integrating new CAD tools.

Because direct synthesis from a behavioral description has yet to produce efficient results in a wide range of applications, our approach requires the user to specify a behavior and a parameterizable datapath. The silicon compilation subsystem translates the behavioral description into datapath instructions and parameter values, which, together with the datapath specification, make up the structural description. The silicon assembly subsystem in turn translates the structural description into a physical layout. With the aid of simulation tools, the user can fine-tune the datapath by iterating this process.

The silicon compiler provides two kinds of behavioral languages: an applicative language called Silage, and an "extended subset" of C called RL. Two external programs, the Silage translator that translates Silage into RL and the RL compiler that translates the program into datapath instructions, have been linked into the system to allow silicon compilation.

The silicon assembler can be used independently of the silicon compiler for high-samplerate applications such as image processing. It consists of a structural interface, a database manager, module generation tools and a functional simulator. The structural interface processes the parameterized structural description and enters it into the database, for use by the simulator and by the module generation tools that generate the layout. The database is based on *Flavors*, an object-oriented programming system, to facilitate the integration of new CAD tools. The silicon assembler uses an open cell library consisting of parameterizable modules and leaf-cell layouts and functional models.

LagerIII has been applied to a number of algorithm-specific IC designs. Two examples, a frame buffer controller chip and a pitch tracker chip, are described in this thesis.

Brodeson

**Committee Chairman**

# TABLE OF CONTENTS

.

| 1. Algorithm-specific ICs 1                                           |

|-----------------------------------------------------------------------|

| 1.1 Commodity, Application-specific and Algorithm-specific ICs        |

| 1.2 Dedicated and Programmable Architectures                          |

| 2. The LagerIII CAD System                                            |

| 2.1 The Challenge                                                     |

| 2.2 The Philosophy                                                    |

| 2.3 System Overview                                                   |

| 2.4 Related Work                                                      |

| 3. The Silicon Assembly Subsystem                                     |

| 3.1 Internal Design Database                                          |

| 3.1.1 Integration Policy                                              |

| 3.1.2 Object-oriented System                                          |

| 3.1.3 Design Database Implementation                                  |

| 3.1.4 An Example                                                      |

| 3.1.5 Comparison with the OCT Database                                |

| 3.2 The Design Manager                                                |

| 3.2.1 Structural Description Language                                 |

| 3.2.2 An Example                                                      |

| 3.2.3 The Implementation of the Design Manager                        |

| 3.3 The Layout Generator                                              |

| 3.3.1 The Layout Generation Tools                                     |

| 3.3.2 Implementation of the Layout Generator                          |

| 3.4 The Design Simulator                                              |

| 3.4.1 Simulator Overview                                              |

| 3.4.2 Functional Model                                                |

| 3.4.3 Implementation of the Design Simulator                          |

| 3.4.4 Input/Output of Design Simulator                                |

| 3.4.5 Remarks on Simulator Performance                                |

| 4. Frame Buffer Controller Chip                                       |

| 4.1 Frame Buffers                                                     |

| 4.2 Image Signal                                                      |

| 4.3 Chip Architecture                                                 |

| 4.4 Layout Generation                                                 |

| 4.5 Simulation and Testing Results                                    |

| 5. The Silicon Compilation Subsystem                                  |

| 5.1 The KAPPA architecture                                            |

| 5.2 The Relationship Between the Instruction Set and the Architecture |

| 5.3 Silage Translator                                                 |

| 5.4 RL Compiler                                                       |

| 5.5 Control Generator                           | 92  |

|-------------------------------------------------|-----|

| 5.6 Summary                                     | 96  |

| 6. Pitch Tracker Chip                           | 98  |

| 6.1 Pitch Tracking Algorithm                    | 98  |

| 6.2 Chip Implementation                         | 100 |

| 7. Conclusions and Remarks                      | 104 |

| 7.1 Major Accomplishments                       | 104 |

| 7.2 Remarks on Future Improvements              | 105 |

| 7.3 Applications of LagerIII                    | 107 |

| Reference                                       | 108 |

| APPENDIX A: (part of) LagerIII User Manuals     | 112 |

| APPENDIX B: Frame Buffer Controller input files | 126 |

| APPENDIX C: The KAPPA Sadl file                 | 135 |

| APPENDIX D: Pitch Tracker Inputs                | 145 |

•

.

۲

- -

## ACKNOWLEDGEMENTS

I would like to thank my research adviser, Prof. Robert W. Brodersen, for his encouragement, guidance and support throughout the course of this thesis work.

The discussion with Dr. R. Jain in the early phase of the LAGER project was very fruitful. K. Rimey, E. Wang, M. Srivastava, E. Lettang, Dr. R. Jain, Prof. J. Rabaey and Prof. R. Brodersen contributed a great deal to the software development of the LAGER system. K. Azim used the LAGER system in its early stage of development and provided valuable feedback.

I also want to thank P. Schrupp, B. Richards, C. Lee and W. Baringer for sharing with me their knowledge on image frame buffers and hardware design.

The research project is funded by DARPA under grant N00039-87-C-0182. The Ministry of Education of the Republic of China supported me for my first two years of graduate study.

I am indebted to C. Lee who patiently read most of the thesis manuscript and corrected my numerous writing errors.

Finally, I want to thank my wife, Debbie, and my family for their constant care, support and love.

# **CHAPTER 1**

# Algorithm-specific ICs

# 1.1. Commodity, Application-specific and Algorithm-specific ICs

Most of the integrated circuits (ICs) designed today can be categorized into two groups: *commodity* ICs and *application-specific* ICs (ASICs). Examples of commodity ICs include memory chips, TTL MSI and LSI gates and microprocessor chips. The commodity chips are usually produced in large volume with fully custom design. Because they are standard products, *price* is the only figure of merits. The companies that produce commodity chips have to constantly improve the price-performance of their commodity IC products, usually by more advanced circuit design, and manufacturing processing technology, in order to be competitive.

The ASICs, as the name suggests, are small-volume products and hence often cannot afford the fully custom design approach. Examples of ASICs include computer peripheral chips and digital signal processing ICs. The turn-around time of ASICs is often more important than the area (cost), which also brings about the need for computer-aided design (CAD) tools. The ASICs achieve higher performance through architecture innovations. Due to their application-specific nature, each design can exploit the special conditions in the particular application to create an efficient architecture.

In the past several years we have seen a steady growth in the ASIC market, and it is predicted that by 1990 the commodity ICs and ASICs will each occupy 50% of the IC market. It is due to the following reasons that many believe the trend of the increasing importance of the ASICs will remain after 1990. First, in commodity ICs while scale down the technology has been fruitful over the past 10 years, significant investment is required. Second, many new systems and new architectures have been proposed which were implemented with ASICs as the key components. Even though the cost of an ASIC is higher than that of a

commodity IC with similar complexity and technology, the overall system had lower overall cost due to a more efficient system architecture.

Another reason of the increasing ASIC designs is the maturity of CAD tools. It is not until recently that high-quality module generators, silicon compilers and integrated CAD environments were available. The main products of the CAD industry have changed from layout editor, switch or circuit simulator (which were used by commodity IC designers) to higher level front-end tools like the schematic entry tools and functional simulators, and automatic layout generators. The latter played an important role in the design process of ASICs. In the future we expect to see additional CAD tools developed for ASIC design.

Finally, there is the issue of *fast prototyping* of design ideas. The system designer often wants to quickly evaluate the price/performance of hardware implementation of an application. It is often the case that the designer has the choice of a board with commodity chips or an ASIC to implement his idea. What has made the ASIC a more attractive choice is because there are much more tools available at the chip level than at the board level. The advantage of ASIC design is that there are a number of cell design styles (gate-array, standard-cell, semi-custom, etc.) with different turn-around times and performances. Once the design idea is verified, the performance can be improved with a different cell design style.

One main disadvantage of ASICs is the extra fabrication time as compared to off-the-shelf commodity ICs. However, the fabrication time has been reported to be as short as two weeks with some gate array design systems. Moreover, from our experience the design time is still much longer than the fabrication time. Therefore, to reduce the design time has a larger impact on the overall turn-around time.

The focus of this thesis research is on a subset of ASICs in which some computational algorithms are implemented. I will call them the *algorithm-specific* ICs. From the experiences of several algorithm-specific IC designs<sup>1,2,3</sup>, we found that even though the algorithms in various applications are very different, they however can all be implemented with a limited set of hardware modules (e.g. ram, data path). By reusing hardware modules, many of the design difficulties of most ASICs are alleviated. Specifically, this can be done by (1) selecting hardware modules to be used in a particular algorithm and (2) creating

new hardware modules if necessary in such a way that they are reuseable.

On the other hand, by restricting the design domain to algorithm-specific ICs, the CAD system design becomes simpler. First, it is possible to develop some special-purpose module generators for commonly-used hardware modules. Second, one of the tasks of the CAD system is to translate higher level design representations to layout, which is almost untractable unless we restrict the design domain.

Typical application areas of algorithm-specific ICs include speech processing, image processing, robot control, computer vision, digital audio and telecommunications. For example, inverse kinematics, adaptive equalizers for digital cellular telephones, fingerprint recognition, frame buffer controller, channel emulator for computer network protocols, image processing based on projection-transformed data, milling machine overseer and robot controller are a number of active research projects which involve algorithm-specific IC designs, which are underway in our research group.

#### **1.2. Dedicated and Programmable Architectures**

To achieve higher performance in algorithm-specific ICs, efficient architectures have larger impact than efficient layout just as in the case with ASICs. In general, the most efficient architecture is one that is *dedicated* to the particular algorithm. A dedicated architecture is often obtained by studying the data flow operations in the algorithm and allocating a dedicated hardware module for each operation, for example, an adder for an *add* operation. This way the logical data flow in the algorithm is implemented by the physical interconnection of the hardware modules. The control unit of the hardware modules is simple since in general there is no time-multiplexing of hardware modules, even though the data path may be very complicated. The speed of the implementation depends on the slowest hardware module in the design.

The drawback of dedicated architectures is that they have to be redesigned for new algorithms. Therefore, another type of architectures is often used in low sampling rate applications which consists of a number of most commonly used hardware modules, which are time-multiplexed (by microcode control) according to the algorithm. We call this type of architectures the *programmable* architectures. The control unit in a programmable architecture is complicated in order to control the time-multiplexing of hardware modules. The speed of the implementation depends on the total number of microcode cycles to realize the algorithm. A programmable architecture is applicable only if

# total number of cycles $\leq \frac{\text{sample period}}{\text{circuit cycle time}}$

For example, if the circuit runs at 5 MHz, and the sample frequency is 5 kHz, then the maximum number of cycles of an algorithm is 1000.

It is interesting to compare the differences and similarities of an algorithm-specific IC in programmable architecture, and an off-the-shelf microprocessor. Both of them offer some programmability. However, a microprocessor is *software programmable* in the sense that software programs can be compiled and stored in its program memory for execution. On the other hand, an algorithm-specific IC in programmable architecture is *hardware programmable*. Not only can different algorithms be compiled and stored, but the architecture itself can be tailored for the algorithms. Examples of typical parameters of a programmable architecture are the word length of the data path, and the depth of the stack, etc. Contrast to software programmable chips that are programmed after the chips are fabricated, the hardware programmable chips are programmed before the chips are fabricated, i.e. at the design phase of the chip. However, the fact that the programmable architecture is subject to customization of the particular algorithm makes the compiler design more challenging.

In summary, for low sampling rate applications, the programmable architecture is a good choice because not only the hardware modules but the architecture are reused to reduce design difficulties. On the other hand, dedicated architectures are necessary for high sampling rate applications because only dedicated hardware modules can provide the speed required. In the next chapter, a description of the CAD system which supports both types of architectures will be given.

# **CHAPTER 2**

## The LagerIII CAD System

## 2.1. The Challenge

The design representation of algorithm-specific ICs can be divided into three categories (by abstraction level): algorithm, architecture and layout. At the algorithm level, the design can be represented by an application program, or graphically by a signal flow graph. Because this representation describes only the behavior that the chip should implement without specifying what hardware modules to use, it is also called a behavioral level representation. At the architecture level, the design can be represented by interconnections of hardware modules. It can also be called a *structural* level representation. At the layout level, the design is represented by physical IC mask layout. It is the most detailed design representation a designer has to deal with. The hardware modules specified at the structure level are further refined such that their physical implementation with leaf cells is specified. The layout level representation can also be called the *physical* level.

A good CAD system should allow the user to specify the designs of algorithm-specific ICs at high levels (behavioral and structural) and generate the physical layout automatically. The productivity of the designer increases when s/he can use high level representations to describe the designs, an experience we learned from high-level programming languages.

The design of algorithm-specific ICs requires collaboration of people with expertise in various areas. Signal processing algorithm developers, VLSI architects and circuit designers is one typical combination. A CAD system should be easy to use for people of all levels of expertise such that (1) they can try out ideas easily and (2) they can work together. The CAD system should provide a means through which the architectures designed by the architects can be used by the algorithm developers. An algorithm developer can simply design and simulate the algorithm in a high-level language, and *choose* an architecture that is designed to realize the algorithm. The architecture has to be *parametrizable* such that it can be tailored according to the algorithm. For example, the round-off error characteristics of an algorithm may dictate the word length of the data path. The CAD system should also provide a means through which the hardware cells designed by the circuit designers can be used by the architects. All the architect needs to do is to determine how and what cells to use in the architecture. Basic cells (e.g. adder) and functional blocks (e.g. control unit) can be described in a parametrized form to encourage re-use and sharing of the leaf cells and functional blocks, and to facilitate the design of new architectures.

A set of layout generation and simulation tools is needed for quickly evaluating the area and performance of the architecture. In order to reduce the effort of integrating new design tools in the future, the CAD system must have a *policy* to deal with how the tools are integrated.

As the design gets increasingly complicated, design representation and documentation become more important. Because the CAD system can carry out the design from either the algorithm or architecture level, the input descriptions the user specified at those levels are the best design documentations. The design can be reproduced by giving the same high-level description and the choices of architectures and circuits.

In summary, the CAD system should be designed based on four considerations: (1) By providing high-level interfaces such that it can be used by users of different expertise. (2) It facilitates the sharing and re-using of leaf cells and functional blocks through parameterization. (3) New design tools can be integrated easily. (4) It should help fast prototyping the user's designs through automatic layout generation. Therefore, in the CAD system described in this thesis four user interfaces are provided: (1) a *behavioral* interface for entering algorithms, (2) a *structure* interface for entering architectures, (3) a *cell* interface for entering leaf cells and (4) a *tool* interface for entering new design tools.

Whether or not to automate the leaf cell design is also an issue to the CAD system design. The automatic approach is less vulnerable to the design-rule changes, and can produce shorter circuit delays if timing optimization is performed. It is however less efficient in terms of area and run-time. The automatic approach often introduces constraints to the leaf cells and the design tools. In our CAD system, the leaf cells are manually designed.

#### 2.2. The Philosophy

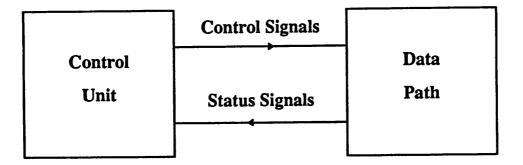

In this section I will discuss the approaches and their rationales that are taken in LagerIII. I will define the *silicon compilation* process as the process of translating behavioral level information to structural level information, and *silicon assembly* process as the process of translating structural level information to physical layout.

The *data path synthesis* approach<sup>4</sup> is often adopted in the silicon compilation process. It tries to mimic while automate the human designer's design methodology. It investigates the algorithm and finds out the minimal data path necessary to implement the algorithm. Then it proceeds to schedule the algorithm onto the data path and thereby produces the microcode. Some constraints on the number of hardware modules of each type may be imposed in some systems, which make the scheduling a bit more difficult.

However, the data path synthesis approach is not yet able to produce very efficient (in terms of area and performance) data path architectures for a wide range of applications. The main reason is that there are simply too many possibilities in architecture design to be captured in one software program. In most systems, some high-level decisions such as the bus structure, pipelined or parallel, lumped ALU or distributed functional modules, are pre-determined, which reduce the architecture design domain, and make the problem tractable. Researchers have used rule-based implementations<sup>5</sup> for the data path synthesizer but it was found that a set of rules was only applicable to a limited number of applications.

In some high performance applications special i/o considerations have significant impact on the overall performance of the architecture<sup>6</sup>, which are not addressed in most behavioral level descriptions.

The data path synthesis approach suffers from the fact that it can only generate data paths that are similar to what have been designed. It is not yet able to *invent* new data paths for exotic applications.

In LagerIII, we use a *data path mapping* approach where the data path is manually designed first and the silicon compilation system *maps* the behavioral level description onto the pre-defined data path. This approach results in more efficient data paths. This approach is made feasible by providing a dedicated data path module generator that allows easy generation and modification of data paths. For algorithms that have relatively similar sampling rate and contain the same set of primitive functions (and therefore can exploit the same data path implementation), the data path mapping approach eliminates the data path synthesis step. On the other hand, for algorithms that need very different data path designs, this data path mapping approach allows human designers to invent new data paths.

The implementation of data path mapping calls for a compiler that *compiles* the high-level behavioral description into microcode. The challenge of this compiler is that it has to be able to generate corresponding microcode for each manually designed data path. This is done through the input of a *code generation table* which essentially describes how each primitive functions in the behavioral description is implemented by a sequence of microcode of each data path. Each data path has one corresponding code generation table. The code generation table in this approach is effectively the same as the rules in a rule-based data path synthesizer; both describe the data path in an abstract way and allow the behavioral description to translate into structural level information.

The data path mapping approach is applied in the following way. First, each pre-designed data path is picked in turn, and the corresponding microcode will be generated by the compiler with the code generation table of the chosen data path. If none is satisfactory, new data path has to be designed and its code generation table written, and send to the silicon compilation system to generate the microcode. Usually, it is easy to find out how to modify an old data path to increase the performance for a particular algorithm.

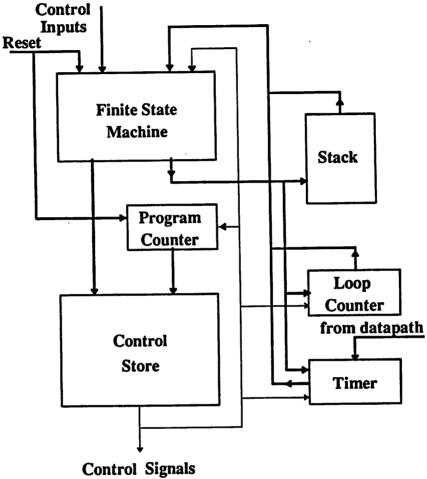

Even though the above discussion concentrates on the data path design, the same argument applies to the control unit design as well. In LagerIII, instead of trying to synthesize the control unit structure, we map the control flow operation (e.g. branch, if-then-else) in the algorithm into pre-defined control unit structures. For example, the contents of FSM and ROM in the control unit design<sup>7</sup> can be customized with the behavioral description in the silicon compilation system in LagerIII.

In summary, the silicon compilation system in LagerIII maps the behavioral level descriptions to pre-defined structural designs. This approach leaves room for the user to enter new manually designed data path and control unit architectures. This approach is the most feasible one under today's situation where the direct synthesis approach can not produce efficient architectures. It is a necessary first step toward direct synthesis to get more experiences in architectural design through manually design practice.

In the silicon assembly process, there is another issue: whether to let the CAD system or the user choose the hardware modules and cells in the design. In general, there is more than one cell in the cell library with the same functionality, each differing from another in, say, driving capability and layout area. The CAD system can choose the cells based on timing optimization and/or area optimization criteria. However, the drawback of this approach is that the CAD system needs to be re-compiled whenever a new cell or hardware module is integrated, which increases the maintenance cost of the cell library. New versions of the old cells and hardware modules create the same problem.

In LagerIII, we let the user specify all hardware modules and cells in the whole design hierarchy. The cell specification includes the cell name and the directory path name. Different versions of the same cell are stored in different directories.

#### 2.3. System Overview

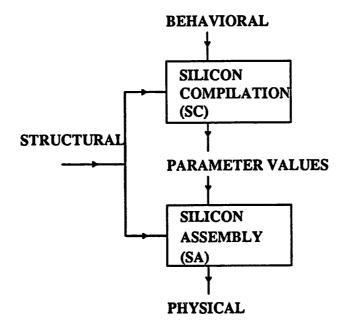

The relationship between the silicon compilation subsystem and the silicon assembly subsystem is shown in Figure 2.1. To facilitate the reuse of the hardware modules, the structural level description is parametrized. Therefore, the silicon assembly subsystem requires both the structural description and the parameter values in order to generate the layout. Typical parameters include the word length of the data path, the content of the ROM, etc. The silicon compilation subsystem maps the behavioral description of the algorithm onto the pre-defined structural design by generating the appropriate set of parameter values. The architecture designer can use the silicon assembly subsystem to generate layout, and the algorithm developer can use both subsystems to generate layout from an algorithm given the structural design.

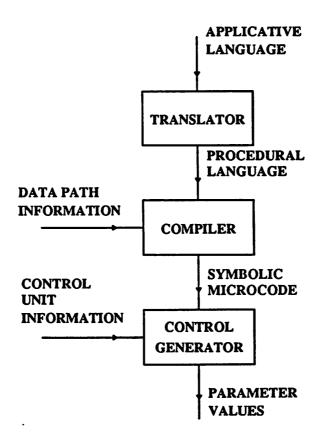

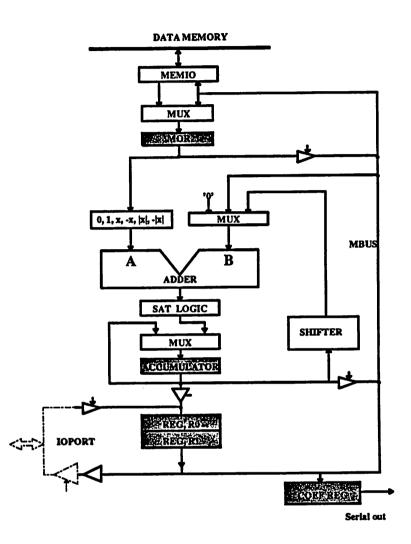

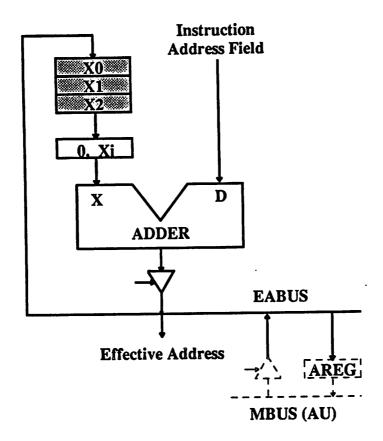

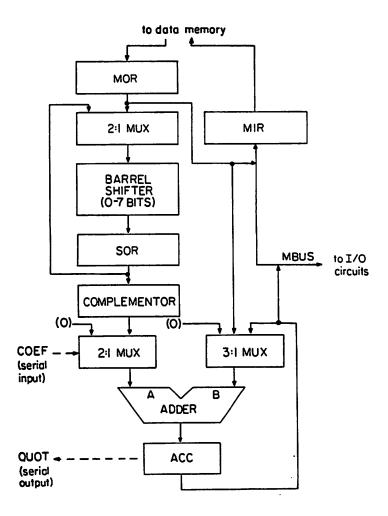

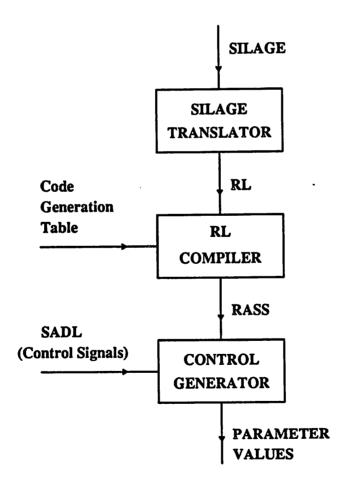

Figure 2.2 shows the block diagram of the silicon compilation subsystem. The behavioral level description language used in LagerIII is *Silage*<sup>8</sup>. Silage is an *applicative* language designed for describing the signal flow diagrams easily. A Translator translates the Silage program into a *procedural* language similar to C, in which control flow operations are put in. A *Compiler* compiles the procedural language into the symbolic microcode based on a code generation table that describes a pre-defined data path. The symbolic microcode has very general control flow primitives, which can be implemented in a lot of control units. A *Control Generator* generates the parameter values for a particular control unit. Note that the structural level information, in the form of a code generation table and control unit information, contributes to and affects the silicon compilation subsystem.

Figure 2.1 LagerIII system overview

The silicon compilation subsystem will be described in more details in Chapter 5.

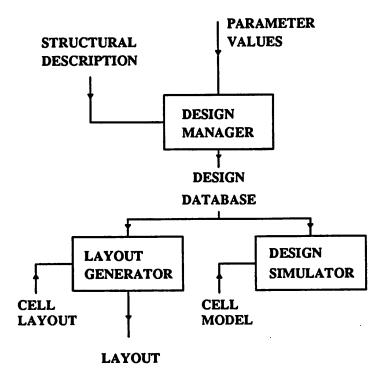

Figure 2.3 shows the block diagram of the silicon assembly subsystem. It consists of three software components (the *Design Manager*, the *Layout Generator* and the *Design Simulator*) and a cell library. The Design Manager translates the parametrized structural description and the parameter values to an internal database. The Layout Generator integrates a set of module generators. The Layout Generator accesses the design information from the internal database, and the leaf cell information from the cell library. The Design Simulator is an event-driven, functional/switch level simulator that allows the user to simulate the structural description. The Design Simulator accesses the design information from the cell library. It is very important to let the Layout Generator and the Design

Figure 2.2 The silicon compilation subsystem overview

Simulator take the same design information input, which eliminates the need of verifying that the two inputs are the same.

The silicon assembly subsystem will be described in more details in Chapter 3.

In previous chapter, it is said that there are two types of architectures, dedicated and programmable, for implementing algorithm-specific ICs. Both types of architectures are supported in LagerIII, but in different ways. The silicon compilation subsystem is designed to be used for programmable architecture and the silicon assembly subsystem is designed to be used for both programmable and dedicated architectures. This is because (1) The silicon compilation subsystem maps the algorithms onto reuseable pre-defined architectures, but the dedicated architectures is very hard to reuse. (2) Once the dedicated architecture is described by the structural description, the parameter values are often easy to obtain. (3) The programmable architecture, because of its nature of simple data path and complicated control, needs the silicon

Figure 2.3 The silicon assembly subsystem overview

compilation subsystem to help generate the control unit. The dedicated architecture has simple control and hence the silicon compilation subsystem is not critical.

#### 2.4. Related Work

The discussion in this section is organized by a taxonomy of *silicon compilation languages* (SCL), which are the input languages to silicon compilation systems.<sup>9</sup> Silicon compilation languages can be divided into two major categories: *structural* and *functional*. A structural SCL specifies how a circuit is constructed. A functional SCL specifies the input/output mapping of a circuit. A functional SCL can be subdivided into two groups: *architectural* and *behavioral*. A functional SCL is called architectural if it has predictable structural semantics; otherwise it is a behavioral SCL.

There are quite a few general purpose silicon assembly systems developed recently in the CAD industry. LSI Logic's *silicon integrator*, VLSI Technology Inc.'s VTItools, Silicon Compiler Systems's Genesil and Seattle Silicon Technology's Concorde are best known examples. The users of these systems usually specify the designs using a schematic entry, which can be viewed as a graphical structural description. Without the capability of taking behavioral level description as input, these systems cannot help the users in translating an algorithm to a structural design.

The CAD tools in these systems are often developed independently. Therefore, as the number of CAD tools increases, the tool integration becomes a problem. This issue has recently attracted much attention and research and development efforts in the CAD industry. Moreover, the fact that the cell library is not parameterizable makes it difficult to maintain the cell library and to share cell modules among designs.

A few special purpose silicon assembly systems have been reported that work on *architectural* level descriptions. These systems usually have restricted target architectures and application domains. The GE silicon compiler<sup>10</sup>, for example, is based on a *bit-serial* architecture. The MacPitts silicon compiler<sup>11</sup> is based on an architecture that contains a bit-sliced data path and a PLA control unit. Furthermore, the input languages to these systems do not support control flow operations very well. The MacPitts uses an

embedded Lisp language as input, and the only control flow construct is the Lisp cond function.

The silicon compilation started with a behavioral level description has been a hot research area for a number of years. A number of systems were proposed, each with different behavioral description language. The behavioral specifications are divided into three groups in the following discussion:

(1) frequency-domain specification. This behavioral specification describes the frequency-domain behavior desired in the chip. Typical parameters include the passband ripple, stopband ripple, stopband attenuation, etc. Based on these specification, a filter is synthesized and its coefficients are optimized for hardware realization. The Cathedral-I system was reported<sup>12</sup> in which a fixed bit-serial architecture has to be used to make the architecture mapping and optimization tractable.

(2) machine specification. One important example of this kind of behavioral specification is the ISPS<sup>13</sup> language, on which the CMU-DA<sup>4</sup> system is based. The ISPS language describes the instruction set of an architecture and the machine behavior in executing each instruction. The CMU-DA system synthesizes the data path that implements the instruction set. Both a iterative algorithmic approach (*EMUCS*) and a knowledge-based approach (*DAA*) have been tried in the CMU-DA system, both neither has yet been able to come close to the human designed data paths. Furthermore, the scope of CMU-DA is limited in generating the architecture of the data path, without actually generating the layout of the data path.

(3) algorithm specification. In this kind of the behavioral description, a particular algorithm is specified. It is *lower* than the *frequency-domain specification* because the implementation in terms of algorithm has been fixed. However, a frequency-domain specification usually is only applicable for a limited range of applications (e.g. filters). An algorithm specification is different from a *machine specification* because the architecture can be tailored by the particular algorithm, which is, however, a very difficult task. For example, the LagerI system<sup>14</sup> used an assembly level *design file* as input and the Cathedral-II system<sup>5</sup> used the Silage language. For simplicity, they all assume a fixed architecture onto which the behavioral description will be mapped.

In summary, even though a lot of silicon assembly and compilation systems have been reported, none was able to cover the entire design spectrum from behavioral description to layout. Silicon assembly

systems are more mature than silicon compilation systems. However, considerable effort is being devoted to make the silicon assembly system *open* to new CAD tools and cells. Silicon compilation systems have shown promising progress in the past few years, but significant breakthroughs are still required before the most efficient architecture can be generated given an algorithm specification. The LagerIII system attempts to do this by providing a structural input and a behavioral input. Because it is developed to support the design of algorithm-specific ICs, the LagerIII uses an algorithm specification (Silage) as behavioral description. A unique feature that separate LagerIII silicon compilation subsystem from LagerI and Cathedral-II is the structural input, with which the user can modify the target architecture. Finally, the LagerIII silicon assembly system is implemented in an object-oriented environment which makes it easy for new CAD tools and cells to be integrated.

## **CHAPTER 3**

## The Silicon Assembly Subsystem

The LagerIII silicon assembly subsystem is composed of four parts: an internal design database (section 3.1), a structural interface called the Design Manager (section 3.2), a Layout Generator that integrates a set of module generation tools (section 3.3) and an event-driven, functional level simulator called the Design Simulator (section 3.4).

#### **3.1. Internal Design Database**

The importance of a consistent internal database in a silicon assembly system will be discussed first in section 3.1.1. Second, in section 3.1.2 the object-oriented programming paradigm will be described, which is shown to be a suitable tool for implementing the database. The organization and actual implementation of the design database using Flavors and Lisp will be described in section 3.1.3. The Lisp interpreter provides a nice interactive environment in which the user can send queries to access the database. In section 3.1.4, a *sorter* example is used to show the internal organization of the database by using the Lisp interpreter. Finally, in section 3.1.5 some comparisons are made between the design database with the OCT database.

## **3.1.1. Integration Policy**

The *integration policy* defines how the design information is stored in the internal design database. In traditional CAD program implementations, each program has its private data structures and the communication is through reading and writing files. The integration policy is the *common data structure* that is shared by all CAD programs, and hence eliminates the file transfer overhead in program communications. A well-thought integration policy also makes the integration of new CAD programs easier because the interface problem is confined between the new CAD program and the internal design database.

Each CAD program has its own optimal data structures. However, since the integration policy is shared by all CAD programs, it is difficult to satisfy them all. If the common data structure were to be constructed to be the union of all private optimal data structures, then the overall database will be inefficient due to its enormous size. The integration policy has to compromise and be optimized for the overall performance. Therefore, it often depends on the CAD programs involved.

After the integration policy is defined, the CAD programs can be written as a sequence of *queries* to the design database to access, process and finally store the information. The productivity of the CAD tool designer increases when they can implement the CAD programs with high-level queries. The implementation detail of the database is encapsulated and can be modified without affecting the CAD programs.

In LagerIII, an *object-oriented* programming system ( $Flavors^{15, 16}$ ) is used to implement the design database. The object-oriented programming system provides a way of implementing highly modular systems and *generic operations*, which allows the high-level queries to be easily implemented.

#### 3.1.2. Object-oriented System

A *flavor* is the fundamental entity in the Flavors system, which designates a class of objects that have common characteristics. A flavor consists of *local state* and a set of operations (called *methods*) that can be performed on it. An *instance* is created by *instantiating* a flavor. The elements of local state are called *instance variables*. The values of the instance variables are different from instance to instance, though their number and names are the same for all instance of a flavor.

An instance is asked to perform an operation by specifying the generic name of the operation and by specifying arguments to that operation (a value may be returned). This is also called *sending a message*. Associated with each instance is a means by which a piece of code (*method*) can be found from the name of an operation. When a message is sent to an instance, the instance finds the appropriate method and runs

it, giving it the supplied arguments.

This paradigm permits the implementation of generic operations. A set of messages is defined, which specifies what the external behavior must be if an instance is to implement the message. The message does not define how the operation is implemented in the instance. This feature allows the implementation detail to be hidden in the instance. A good analogy of the messages is the computer network protocols, where the hardware, software and firmware implementations of the protocols is hidden from other computers in the network.

The terminologies used in Flavors are slightly different from other object-oriented systems. For example, in Smalltalk<sup>17</sup>, a flavor is called a *class* and an instance is called an *object*. Flavors is supported in a number of Lisp dialects. In the following, only the Franz Lisp Flavors is described. Several functions are included here for completeness and ease of discussion, and a detailed description is available<sup>15</sup>.

A flavor is defined by the special form

(defflavor flavor-name

- ( (var1 [init-var1]) (var2 [init-var2]) ...)

- (flav1 flav2 ...)

- (option1 option2 ...))

where *flavor-name* is a symbol which is the name of the flavor. *var1*, *var2*, ... are the names of instance variables and *init-var1*, *init-var2*, ... are their initial values. An initialization is not required but is useful for assigning default values to the instance variables. *option1*, *option2*, ... are option's to the defflavor form. *flav1*, *flav2*, ... are the names of the *component flavors* which the *flavor-name* flavor *inherits*. The instance variables and methods of the component flavors are inherited by the *flavor-name* flavor. The inheritance mechanism is one of the major differences between Flavors and other object-oriented programming systems. In Smalltalk, for instance, a class can only inherit from one parent class (called *superclass*). Therefore, the only possible ways to modify an existing class are by adding additional instance variables, by adding additional methods, or by *shadowing* (replacing) existing methods. Because of the strict hierarchy

among classes, this scheme cannot handle *orthogonal attributes* in a modular form. When there are several features that need to be combined in a pick-and-choose fashion, the single-superclass scheme becomes hard to use.

In Flavors, any flavor can inherit more than one component flavors, whose *order* is important in determining which method to inherit if there are more than one defined in the component flavors. The following flavor organization conventions are recommended. A *base* flavor is a flavor that defines a whole family of related flavors, all of which have that base flavor as a component. A *mix-in* flavor is a flavor that defines one particular feature of an object. A mix-in flavor cannot be instantiated, because it is not a complete description. A usable flavor can be constructed by choosing the mix-ins for the desired characteristics and combining them, along with the appropriate base flavor.

An instance can be instantiated by the special form

(make-instance 'flavor-name [init-option value] ...)

A method is defined by the special form

(defmethod (flavor-name message-name) argument-list

form1 form2 ...)

where *flavor-name* is the name of the flavor in which the message is defined. The name of the message is specified by the symbol *message-name*. The message-name has to be a Lisp *keyword* (which starts with a ":"). *argument-list* is a list of auxiliary variables used by the method. *form1*, *form2*, ... are the method body.

A message is sent to an instance by the special form

(send instance message-name argument-list)

where *instance* is the receiving instance to which the message *message-name* and the *argument-list* are sent. A message can be handled by the instance only if the appropriate method has been defined for the instance by a defmethod, otherwise it results in an error.

#### 3.1.3. Design Database Implementation

In an IC design system, we find that the most important objects are terminals, nets and cells, which are defined to be the base flavors in the design database. Their *instance variables* are defined in Table 3.1 to 3.3. Some instance variables used by the Design Simulator will be discussed later. A cell x is said to be the *sub-cell* of a cell X if X contains x. X is called the *parent-cell* of x. The notions of the parent-cell and the sub-cell are useful in a hierarchical design system, which allows us to focus the discussion on one level.

The generic-parameter-list stores a list of parameter names by which the cell is parametrized. The *instance-parameter-list* stores a list of parameter name and value pairs, which is obtained by combining the parameter names with the input parameter values through a parameter passing mechanism (see section 3.2). For example, suppose a cell is parametrized by two parameters, **a** and **b**, then the generic-parameter-list of

| instance variable         | brief description                    |

|---------------------------|--------------------------------------|

| generic-name              | flavor name                          |

| instance-name             | instance name                        |

| layout-generator          | type of layout generator used        |

| sub-cell-list             | sub-cells described in sdl           |

| instance-sub-cell-list    | list of instantiated sub-cells       |

| generic-parameter-list    | list of parameter declarations       |

| instance-parameter-list   | list of parameter definitions        |

| generic-terminal-list     | list of formal terminals             |

| instance-terminal-list    | list of instantiated terminals       |

| VGC-terminal-list         | list of Vdd, GND and clock terminals |

| net-list                  | net-list described in sdl            |

| instance-net-list         | list of instantiated nets            |

| generic-equivalent-list   | list of lists of equiv terminals     |

| generic-feed-thru-list    | list of lists of feed-thru terminals |

| xbot                      | minimum x coordinate                 |

| ybot                      | minimum y coordinate                 |

| xtop                      | maximum x coordinate                 |

| ytop                      | maximum y coordinate                 |

| cell-number               | cell enumeration                     |

| sim-list                  | simulation model in a list           |

| sim-level                 | simulation level                     |

| geometric-constraint-list | list of geometric constraints        |

Table 3.1 Instance variables of the cell flavor

a cell instance is (a b) while the instance-parameter-list is ((a 2) (b 5)).

The three most important instance variables of the cell flavor are (1) *instance-sub-cell-list* which contains a list of sub-cell instances, (2) *instance-net-list* which contains a list of net instances and (3) *instance-terminal-list* which contains a list of terminal instances. This information can be used to traverse the whole design hierarchy. The instance variable instance-terminal-list contains only the terminals that are defined in the structural descriptions. The special terminals like Vdd, GND and clock terminals are not defined in the structural descriptions. Instead, they are created as a result of the layout generation. The special terminals are stored in *VGC-terminal-list*.

| instance variable | brief description                               |

|-------------------|-------------------------------------------------|

| side              | side which terminal is on                       |

| name              | terminal name                                   |

| index             | bit number in a bus                             |

| coord             | terminal coordinate                             |

| layer             | layer which terminal is on                      |

| net-number        | number of net which terminal is on              |

| net-name          | name of net which terminal is on                |

| inward-net-name   | name of net in lower level which terminal is on |

| cell-name         | name of cell which terminal is in               |

| function          | function definition for simulation              |

Table 3.2 Instance variables of the terminal flavor

| instance variable | brief description                    |

|-------------------|--------------------------------------|

| name              | net name                             |

| number            | net number                           |

| connect-list      | list of (cell terminal)'s on the net |

| fanin-list        | list of fan-in nets for simulation   |

| fanout-list       | list of fan-out nets for simulation  |

| state             | Forced, HZ, Weak for simulation      |

| value             | 1,0,X value for simulation           |

| driven-cell-list  | list of driven cells for simulation  |

| driving-cell-list | list of driving cells for simulation |

Table 3.3 Instance variables of the net flavor

From the terminal instance t, the net instance that t is on can be readily obtained by the *net-name* instance variable of t. From the net instance n, in order to find out whether or not a particular terminal instance is on n, the *connect-list* instance variable of n can be searched. The information can sometimes be retrieved in more than one approach for efficiency. For example, if we want to find out all the terminals in the sub-cells that are connected to a particular terminal t in the parent-cell p, we can either start from the instance-net-list of p to search all terminals of the sub-cells that are in the same *connect-list* that t is in, or we can start with the instance-sub-cell-list of p to get all the terminals in each sub-cell, which have the same *net-number* as t.

The integration policy is essentially how the structural information is organized using the *cell*, *termi*nal and net flavors. Each CAD tool designer needs only to understand the relationship among them to be able to access the structural information efficiently. In the next section, a small example is given to illustrate the design database.

#### 3.1.4. An Example

A typical design may consist of tens or hundreds of instances (of cell, terminal or net flavors). Therefore, it is crucial to get the correct instance efficiently. Due to the hierarchical organization of these instances it is possible to reach every instance in the hierarchy by traversing up and down the hierarchy and by exploiting the integration policy. However, this is not efficient because it involves considerable list searching.

Another approach is to give every instance a unique name. Since a name can be used as a pointer to the instance in Lisp, we can get to any instance by its unique name. The naming convention is to concatenate the instance names of the parent-cell of an instance with the instance name of the cell, net or terminal instance. To increase readability, special characters are inserted between every two instance names. The character "-" is used to concatenate a cell; the character "." is used to concatenate a terminal; the character "@" is used to concatenate a net; the characters "[" and "]" are used to delimit an index number. For exam-

ples,

sorter-pr-mux

refers to the mux cell of the pr cell of the sorter cell. Sorter is the root cell in the structural hierarchy.

sorter@ctrlnet

refers to the ctrinet net of the root cell.

sorter-pr.in[0]

refers to the *in* terminal (bit 0 in the bus) of the *pr* cell of the root cell. Note that the terminals and the nets can only appear at the end; they cannot be the ancestors of any instances.

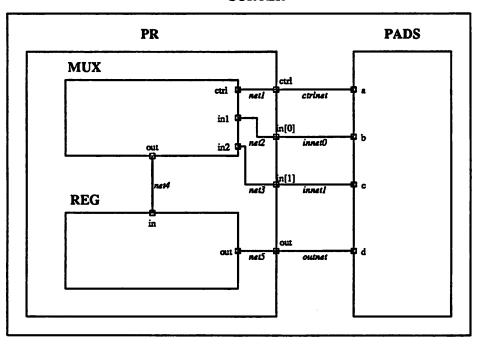

Now let us consider the example depicted in Figure 3.1, where the cell names are shown with boldface, net names with Italic and terminal names with Roman fonts. The root of the design hierarchy is

#### SORTER

sorter, which contains two sub-cells, sorter-pr and sorter-pads. Sorter-pr has two sub-cells, sorter-pr-mux and sorter-pr-reg. After the design database is created with the Design Manager by translating the structural description, the following Lisp queries can be used to access the information. The "=>" is the Franz Lisp prompt sign. The queries are shown in bold-face. The returned values (returned by evaluating the queries) are found next to the queries. An instance in Flavors is identified by its flavor name and a unique ID (e.g. #rt152884>).

=> (send sorter :instance-sub-cell-list)

```

(#<pads 1153436> #<pr 1152884>)

```

=> (send sorter :instance-net-list)

(#<net 1153900> #<net 1154140> #<net 1154192> #<net 1154244>)

=> (send sorter :instance-terminal-list)

nil

The values of the instance variables can be accessed externally by sending messages to the instance. In this case, the message name is the same as the instance variable name with the character ":" as the prefix . This effectively shields the instance variables from the external world. If the instance variables are changed later, the CAD programs remain unaffected if there are new methods defined for the messages. For example, if the instance variables *xtop*, *xbot*, *ytop* and *ybot* are changed to *xdim*, *xbot*, *ydim* and *ybot*, then the messages :xtop and :ytop can still be handled by the following methods

(defmethod (cell :xtop) () (+ xbot xdim))

(defmethod (cell :ytop) () (+ ybot ydim))

and the CAD programs are unaffected. Within the method body, an instance variable can be accessed simply by providing the name. Sometimes the notion of *self* is handy, which allows an instance to refer to itself. For instance, the above methods can also be written as

(defmethod (cell :xtop) () (+ (send-self :xbot) (send-self :xdim)))

(defmethod (cell :ytop) () (+ (send-self :ybot) (send-self :ydim)))

Note that the *instance-net-list* of *sorter* contains the nets between *sorter-pr* and *sorter-pads*. The *instance-terminal-list* contains the terminals on the perimeter which, for the case of *sorter*, is null. The *instance-sub-cell-list* shows that there are two instances in the list, and if we *evaluate* the cells *sorter-pr* and *sorter-pads* as

=> sorter-pr

#<pr 1152884>

=> sorter-pads

#<pads 1153436>

we can verify that they are indeed the sub-cells of *sorter* by comparing the id's. For readability, queries can be designed such that they produce names (as defined by the naming convention) instead of instances. However, creating new queries in the form of *methods* will dictate the recompilation of the database software. An alternative is for the user to create his own Lisp functions on top of the primitive set of queries. For example, the printIcell function defined as

(defun printIcell (cell)

(dolist (a (send cell :instance-sub-cell-list))

(format t "~a~%" (send a :instance-name))))

can be used to return the names of the sub-cells giving the parent-cell. For example,

=> (printIcell sorter) sorter-pads sorter-pr nil

Now suppose we start from the terminal instance sorter-pr.in[0] and would like to find out what terminals it connects to in its parent-cell and in it sub-cells. We can get the external connection information by the net-name with

=> (send sorter-pr.in\[0\] :net-name)

sorter@innet0

Since "[" and "]" are special characters in Franz Lisp, a back-slash escape character is used in front of them. We can find out the terminal instances on the *sorter@innet0* net by accessing its *connect-list* instance variable as

=> (send sorter@innet0 :connect-list)

((#<pads 1153436> #<terminal 1154764>) &)

or by using the user-defined printIconn function to get the names of the cell instances and terminal instances, as

=> (printIconn sorter@innet0)

(sorter-pads b)

(sorter-pr in[0])

```

nil

```

which shows that the *in[0]* terminal on *sorter-pr* is connected to the *b* terminal on *sorter-pads*. However, if we insert the (send sorter-pr.in[0] :net-name) query into the (send sorter@innet0 :connect-list) query directly, we will get an error.

=> (send (send sorter-pr.in\[0\] :net-name) :connect-list)

Error: funcall: Bad function sorter@innet0

Form: (send (send lsorter-pr.in[0] :net-name) :connect-list)

c{1}

This is because (send sorter-pr.in\[0\] :net-name) returns the *name* instead of the flavor instance that is required for the query. The fix is to insert an additional *evaluation* step as

=> (send (eval (send sorter-pr.in[0] :net-name)) :connect-list)

((#<pads 1153436> #<terminal 1154764>) &)

The function symbol-value can also be used in place of eval.

The *internal* net that sorter-pr.in[0] connects to can be found by the *inward-net-name* instance variable of sorter-pr.in[0]. Using the printIconn function, it is shown that the in1 terminal of the sorter-pr-mux cell is connected with sorter-pr.in[0].

=> (printIconn (symbol-value (send sorter-pr.in[0] :inward-net-name)))

(sorter-pr in[0])

(sorter-pr-mux in1)

nil

Another Lisp query that often comes handy is the describe function, which takes an instance as argument and returns the values of all the instance variables. For a list of generic Lisp query functions, the reader is referred to the Franz Lisp manual.<sup>15</sup>

All the queries above are used to *access* the information in the design database. The queries to *store* information can be formed by concatenating the string ":set-" to the instance variable names. For example, the following query store 0 to the *xbot* instance variable of *sorter*. Note that this query has an argument.

```

=> (send sorter :xbot)

```

nil

```

=> (send sorter :set-xbot 0)

```

0

=> (send sorter :xbot)

0

This example shows that design information can be accessed and stored by issuing Lisp queries in the form of message passing. This mechanism allows easy access to the design database while keeping the implementation detail of the design database independent of the CAD programs.

## 3.1.5. Comparison with the OCT Database

The design database was developed in parallel with the OCT database  $project^{18}$ . In this section, some comparisons between them are presented.

First, the instantiation scheme of the two systems are different. In LagerIII, an instance is instantiated with all of its parameter expressions evaluated. Instances of the same flavor description can be different due to different parametrizations. In OCT, the *masters* (the counterpart of flavors) are not parametrized. All instances of the same master are the same except the id's. Therefore, a 3x3 PLA is a different master from a 4x4 PLA in OCT, while in LagerIII they are two instances of the same PLA flavor with different parameter values. It is a trade-off between run-time and storage space. The LagerIII scheme consumes more run-time for evaluating the parameter expressions during instantiation; however, it allows more economic cell library and design database.

The integration policy in LagerIII corresponds to the *symbolic* policy in the OCT database. In LagerIII, the physical layout is stored in Magic<sup>19</sup> format and hence no *physical* policy is developed. The structural description language can be thought of as the textual form of a schematic policy. For the symbolic policy, there are noticeable differences between LagerIII and OCT. For example, In LagerIII a net name can be readily obtained from the terminal instance with the *:net-name* message. In OCT, a *generator* has to be used to search the net name given a terminal instance. In OCT, the *actual* terminals (terminals on the sub-cells) need not to be instantiated explicitly, whereas they do in LagerIII because of the possible variations from instance to instance. Nevertheless, a link has been implemented to generate an OCT database with symbolic viewtype from the design database of LagerIII, which makes it possible to exploit the CAD tools attached to OCT.

Other differences are listed below. In LagerIII, the *layout generator* information is stored as an instance variable of the cell flavor in order to perform the layout generation automatically. In OCT, a shell script is usually needed to *manage* the layout generation process. OCT treats Supply and Ground terminals the same way as other signal terminals. Therefore Supply and Ground are also considered as formal terminals, which means that the user has to specify the clustering of the Supply and Ground nets. In LagerIII, the Supply and Ground terminals are defined after the layout generation and hence they are not defined in the structural descriptions. OCT has the advantage that the database is non-volatile. The design database in LagerIII is only in the main memory without having a back-up image in the secondary memory, which makes it impossible to recover if the program crashes. OCT also has a powerful *property* set which provides an easy way to introduce new attributes. OCT uses full path names and LagerIII uses a special path search mechanism to direct the searching of remote files.

## 3.2. The Design Manager

The Design Manager is responsible for translating the structural descriptions to the design database, which was described in section 3.1. In this section, the syntax and the semantics of the structural description language are described first, which is followed by the description of the implementation of the Design Manager.

## **3.2.1.** Structural Description Language

A structural description language (sdl) file is used to describe the structure (cell hierarchy, interconnection, etc.) of a cell. Sdl files are inputs to the Design Manager, the structural interface program of LagerIII. The cell-name.sdl file specifies the relationship between the cell cell-name and its sub-cells, which are described by other sdl files. To implement an architecture, a set of sdl files is required. The Design Manager provides a path mechanism that allows using user-specified sdl files along with library sdl files. Sdl files can be parameterized to facilitate the re-use of library sdl files. A sdl file includes 7 sections, the order of which is not critical. Each section is recognized by a keyword. Layout-generator, parent-cell, sub-cells, net, geometric-constraint-list, sim-list and lispfunction are the keywords for the 7 sections. The sdl file is written in a lisp-like format; each section is composed of one or more *lists*. A *list* has zero or more elements, each of which can be a *lists* itself, enclosed by a pair of parentheses. The first element of the list in each section is the corresponding keyword of the section.

#### 1. Layout-generator section

The layout-generator section is a list with two elements. The first element is the keyword layoutgenerator and the second element is the name of the layout generator. At this moment, six layout generators (TimLager, dpc, Flint, Padroute, stdcell and mosaico) can be used.

Example:

(layout-generator TimLager)

## 2. Parent-cell section

The *parent-cell* section has one list of 3 elements. The second element is the name of the parent cell, which has to be the same as *cell-name* (the name of the *sdl* file). The third element is a list whose first element is the keyword **parameters**, and the rest of the list is a number of parameter declarations that parameterize the parent cell.

## Example:

#### (parent-cell rom (parameters row column))

## 3. Sub-cells section

The sub-cells section is one list of the keyword sub-cells, followed by n sub-cell definitions where n is the number of sub-cells in the parent cell. Each sub-cell definition is a list of 4 elements: its generic name, its instance name, a list of parameter definitions and an optional flag-expression. The generic name specifies the name of the sdl file where the sub-cell is defined. The instance name is used to refer to the

sub-cell in the *sdl* file. If more than one instance of the same generic sub-cell are used, then their *instance* names can be used to distinguish them.

The first element in the parameter definition list is the keyword *parameters*, with each following element of the form (*parameter expression*). The result of evaluating the *expression* defines the value of the *parameter*. The *expression* is a Lisp expression constructed by primitive Lisp functions and/or userdefined Lisp functions (see *lisp-function* section), which returns an integer, a literal symbol or an array of strings (in this case the *parameter* is a truth table). The *flag-expression* is used to decide whether to include the specific instance in the sub-cell list of the parent-cell. If *flag-expression* is evaluated into a non-zero value (default), then the instance is included; otherwise it is removed. If the instance is removed then all associated nets and terminals are removed as well.

For example, an instance *dec1* of the generic *rom-decoder* cell being a sub-cell of the parent cell *rom* can be represented by

#### (sub-cells

(rom-decoder dec1 (parameters (row row) (column (/ column 2))))

... (other sub-cells) )

From the example, we see that the *rom-decoder* has two parameters *row* and *column*, (which are defined in *rom-decoder*.sdl). In the instance of *dec1*, the value of **row** is the same as the value of *row* in the parent cell (*rom*), and the value of column is the value of *column* in the parent cell divided by 2. The combination of parameter declaration (in the parent-cell section) and parameter definition (in the sub-cell section) provide a mechanism for parametrizing the design with very few parameters. Note that since there is no *flag-expression* field in the definition the sub-cell *dec1* is included.

#### 4. Net section

The net section consists of one or more lists, each of which contains 3 or 4 elements. The first element in the list is the keyword net. The second element is the net name. The third element is an optional bus-expression which, if present, evaluates into the width of the net (or, the number of nets); otherwise one net is included. If the width is zero, the net is removed. The last element of the net definition is a connectivity list that is used to specify the connectivity. Each element in the connectivity list is a terminal definition. Each terminal definition defines a terminal on the net.

A terminal definition can be used to refer to one or more terminals, depending on the width of the net. The terminal definition is a list of 2, 3 or 4 elements. The first element is the *instance* name of the cell where the terminal is on, or the keyword parent if the terminal is on the parent cell. The second element is the name of the terminal. The third element is an optional *starting index* and the fourth element is an optional *increment*. The *starting index* and *increment* are useful when the *terminal definition* is to define the connection of a bus. The *increment* element can be present only if the width of the net is greater than 1. The *increment* is 1 by default, and the default value of *starting index* is 0 if the width of the net is greater than 1. If the width of the net is 1, then the terminal is not indexed. Note that the *increment* and the *starting index* can, in general, be Lisp expressions.

For examples,

(net net1 ((parent x) (dec1 out) (dec1 in 3)))

shows that the *out* terminal and the in[3] terminal of the sub-cell decl connect to the x terminal of the parent cell on the net *netl*; The width of *netl* is 1 since there is no bus-expression.

(net net2 row ((dec1 in1 (- row 1) -1) (other out)))

shows the *in1* bus of the sub-cell *dec1* connects to the *out* bus of the sub-cell *other* in bit-reversed order. The *width* of *net2* is equal to the parameter value of *row*. *Net2* can be viewed as a shorthand of the following set of net definitions:

(net net2[0] ((dec1 in1 (- row 1)) (other out 0)))

(net net2[1] ((dec1 in1 (- row 2)) (other out 1)))

•••

(net net[row-1] ((dec1 in 0) (other out (- row 1))))

A special syntax is created for describing the connection of buses to a single terminal. The third element in this case is the keyword mergeNet. The fourth element in the net definition is again the list of *terminal definitions* except that the first *terminal definition* defines only 1 terminal (i.e. no *increment* field) and the rest have a mandatory third and fourth elements for *starting index* and *ending index* respectively.

For example,

#### (net net3 mergeNet ((dec1 cin) (other cin 0 6 2)))

connects the cin terminal of the sub-cell decl and the cin[0], cin[2], cin[4] and cin[6] terminals of the sub-cell other on net3.

The generic terminals (the terminals on the boundary) of the parent cell are implicitly defined in the net section through the *parent* keyword. For completeness, *feed-through* terminals and *equivalent* terminals can be defined by the net constructs also. If more than one *generic* terminal with no *instance* terminal (the terminals of the sub-cell instances) appear in the *connectivity list*, the *generic* terminals in the list constitute a feed-through. If more than one *generic* terminal with at least one *instance* terminal appear in the *connectivity list*, the *generic* terminal appear in the list are said to be *equivalent*.

#### 5. Geometric-constraint-list section

Strictly speaking, geometric constraints, which are properties in the layout aspect of the parent cell, should not be considered as part of the *structures* of the parent cell. They are put together in the same sdl file for convenience. The geometric constraint definition is a list whose first element is the keyword geometric-constraint-list. Each following element deals with one aspect of geometric constraints. At this moment only the *side* information of the *generic* terminals can be specified. Others like the *aspect ratio* and the *placement* information are under consideration.

The *terminal* aspect of the geometric constraints is specified by a list whose first element is the keyword **terminal**. Each following element is in turn a list of 2 elements: the first being the name of the terminal; the second being a list whose first element is the keyword side, followed by the *side specification* (top, bottom, right or left, or a Lisp expression that returns one of the four side names), and a real number between 0 and 1 which specifies the *location* of the terminals.

For example,

(geometric-constraint-list (terminal (in (side top 0.65)) (out (side right 0.2)) ))

At this moment there is no construct to specify the side information of a bus except to list them one at a time.

## 6. Sim-list section

Sim-list is used to describe the simulation model of the parent cell, which is used by the Design Simulator. Sim-list is a list of at most 5 elements. The first element is the keyword sim-list. The second element is a list of the keyword in-term and all the input terminals/buses. A bus is specified by a list of *name* and *expression* that evaluates to the *width* of the bus. The third element in the *sim-list* is a list of the keyword **out-term** followed by all the output terminals/buses. The fourth element is a list of the keyword local and all the local states. If there are no input terminals/buses or local states, then the corresponding element can be absent. The fifth and last element is a list of the keyword function followed by a number of *function definitions*.

Each output terminal/bus and local state should have a *function definition*. Each function definition is a list of the name of the output terminal/bus or the local state, and a Lisp expression which evaluates to the simulation result of the corresponding output or local state. In the Lisp expression, one can use the names of the input terminals/buses and local states and output terminals/buses to refer to the values *carried* by those terminals/buses/local states, and the parameter name to refer to the parameter values. For example, let us create a sim-list of an inverter,

```

(sim-list

(in-term in)

(out-term out)

(function

(out (Xlognot in))

))

```

where *Xlognot* is a built-in function in the Design Manager which implements 1's complement. Note that the Design Simulator works on strings instead of integers.

7. Lisp-function section

Often a Lisp expression is used more than once in a sdl file, in which case a *lisp-function* definition can be used to avoid entering the Lisp expression over and over again. The lisp-function section consists of one or more lists, each of which starts with the keyword **lisp-function** and is followed by a Lisp function definition (e.g. defun).

For example,

(lisp-function (defun add2 (n)

(add n 2)))

3.2.2. An Example

The set of sdl files for the sorter example in previous section is shown in Figure 3.2 to 3.6.

The way the Design Manager is invoked is illustrated in figure 3.7. The user manual of the Design Manager is listed in Appendix A. Note that only the *root* sdl file name is required because the rest can be inferred recursively from the *generic* names of the sub-cells.

(layout-generator Flint)

(parent-cell sorter (parameter a))

(sub-cells

(pr pr (parameter (b (+ a 2)))) (pads pads))

(net ctrlnet ((pads a) (pr ctrl))) (net innet0 ((pads b) (pr in 0))) (net innet1 ((pads c) (pr in 1))) (net outnet ((pads d) (pr out)))

Figure 3.2 sorter.sdl

(layout-generator Flint)

(parent-cell pr (parameter b))

(sub-cells

(mux mux) (reg reg))

(net net1 ((parent ctrl) (mux ctrl))) (net net2 ((parent in 0) (mux in1))) (net net3 ((parent in 1) (mux in2))) (net net4 ((mux out) (reg in))) (net net5 ((reg out) (parent out)))

Figure 3.3 pr.sdl

(layout-generator leafcell)

(parent-cell pads)

(net a ((parent a))) (net b ((parent b))) (net c ((parent c))) (net d ((parent d)))

Figure 3.4 pads.sdl

(layout-generator leafcell)

(parent-cell mux)

(net ctrl ((parent ctrl))) (net in1 ((parent in1))) (net in2 ((parent in2))) (net out ((parent out)))

Figure 3.5 mux.sdl

(layout-generator leafcell)

(parent-cell reg)

(net in ((parent in))) (net out ((parent out)))

Figure 3.6 reg.sdl

yosemite 8>> DM\_new -I => (DM) Please enter root type (generic name) : sorter Please enter root name (instance name) : sorter

Please enter parameter file name (if none enter N) : N Please enter parameter value of a in cell sorter (root) : 4 Parameter values incorporated in file sorter.par. start creating structures

Now if you want to continue with layout generation Type (LG) to the coming prompt Or type (DSIM) to continue with event-driven simulation nil =>

#### Figure 3.7 Invoking the Design Manager

The -I option specifies the interactive mode. The parameter values can be entered one by one interactively or through a file. In this example, there is only one parameter value to be entered. In *sorter.sdl*, the parameter b of the sub-cell pr is defined to be (a + 2). Therefore, when the user enters 4 as the value of the parameter a of *sorter*, the parameter value of b in *sorter-pr* will be 6. In general, the user only needs to enter the parameter values of the root cell, and the parameter values of all parameters in the design hierarchy will be evaluated accordingly. After the Design Manager finishes and new Lisp prompt

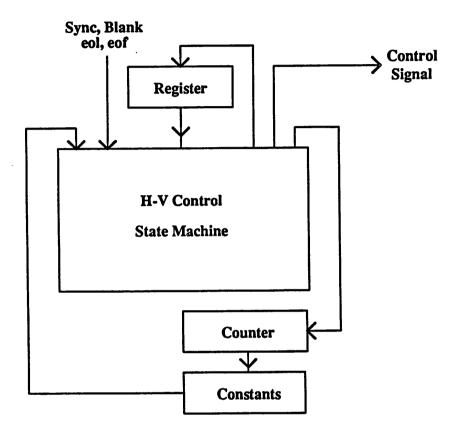

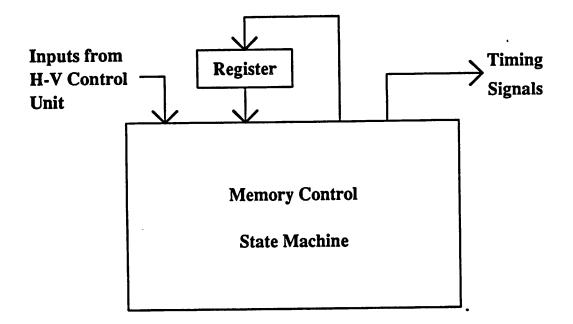

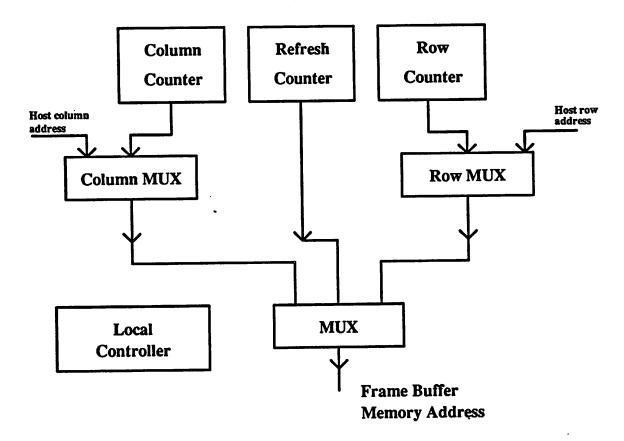

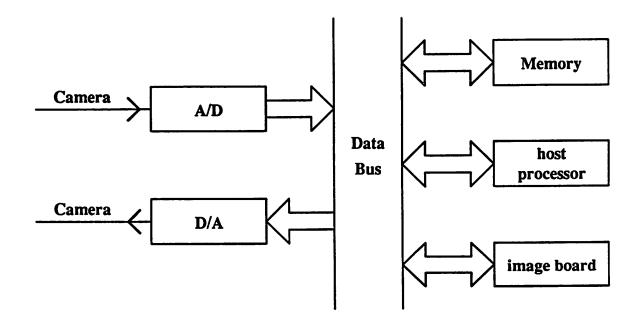

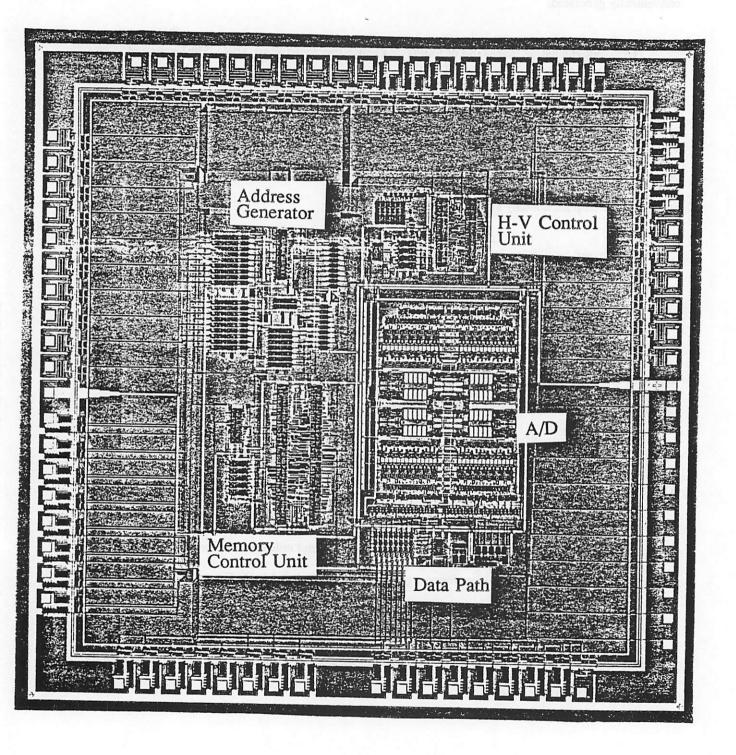

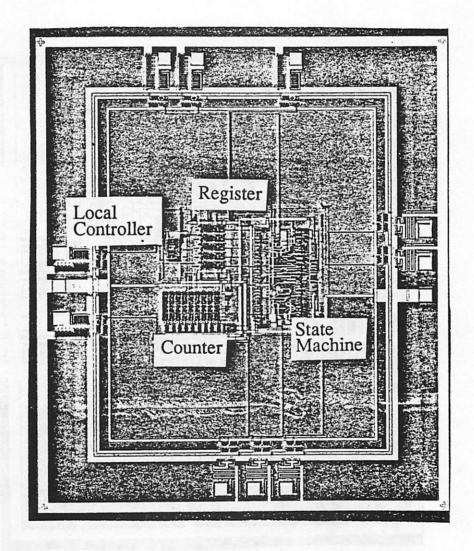

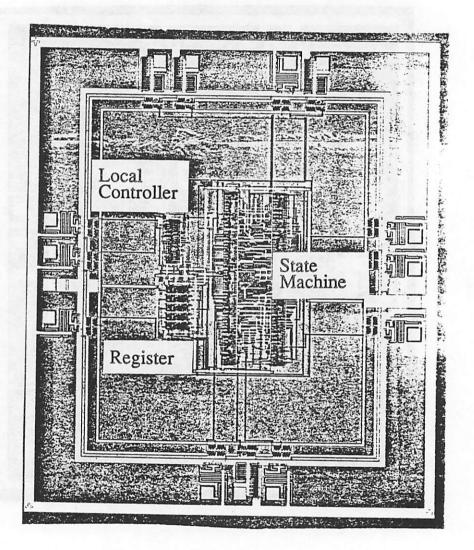

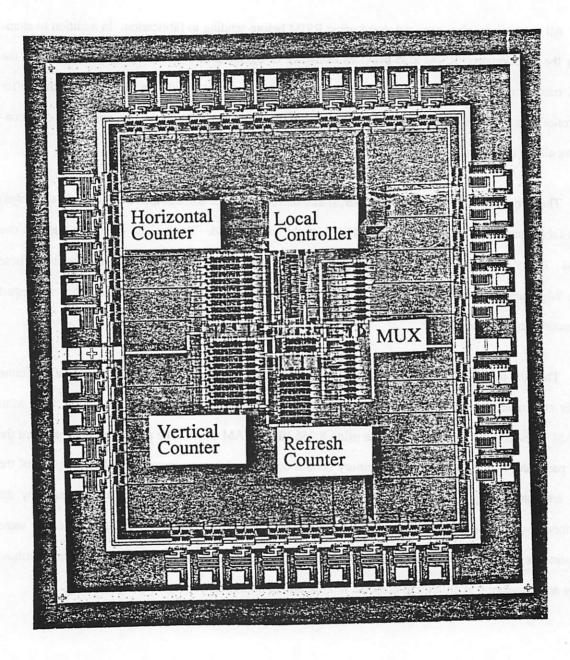

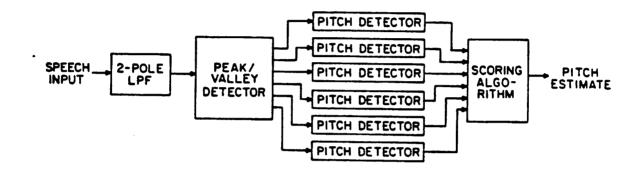

(=>) appears, the design database is created. The user can access the design database with the queries discussed in previous section, or proceed to perform layout generation or simulation. A log file with the name *root*-dm.log is created which contains verbose information about the status of the Design Manager operation. All the error and warning messages detected in the sdl files are also reported in the log file.