Hybrid Memory Management for Parallel Execution of Prolog on Shared Memory Multiprocessors Copyright © 1990 by Tam Minh Nguyen

This research is sponsored by the Defense Advanced Research Projects Agency (DARPA) (monitored by the Office of Naval Research under Contract No. N00014-88-K-0579), the NCR Corporation in Dayton, Ohio, and the National Science Foundation.

# Hybrid Memory Management for Parallel Execution of Prolog on Shared Memory Multiprocessors

#### Tam Minh Nguyen

#### PH.D. DISSERTATION

CS DIVISION (EECS)

#### ABSTRACT

Shared memory multiprocessors can provide high processing power at relatively low cost. In contrast to message passing systems, shared memory multiprocessors allow for efficient data sharing, and thus are more suitable for execution models that exploit medium grain parallelism. This dissertation investigates the problem of memory management for a globally shared space in a parallel execution environment. An AND/OR parallel execution model of Prolog is chosen for our work due to its medium grain parallelism and its intensive memory usage characteristics. With respect to space, we propose a hybrid heap-stack (called ELPS) which is dynamically allocated for more efficient space sharing and interference-free parallel execution. With respect to time, we present a two-tier memory architecture (called the Aquarius-II) with separate synchronization and high-bandwidth memory spaces.

A multiprocessor simulation system has been developed to evaluate the performance of ELPS and the Aquarius-II. ELPS incurs an average of 2% overhead (11% without hardware support), while satisfying the memory requirement to keep up with the speedup potential of the parallel execution model. Compared to the single bus multiprocessor architecture, the Aquarius-II provides higher performance by reducing contention on the synchronization bus and by providing a higher memory bandwidth with a crossbar. A simple broadcast for invalidation scheme is sufficient to keep the crossbar caches consistent while maintaining good cache performance.

Alvin M. Despain

Committee Co-Chair

Vason P. Srini

Vasar P. Sni

Committee Co-Chair

#### ACKNOWLEDGEMENT

This dissertation is the culmination of my graduate school "career." Through the years, I have received a great deal of support from many people who helped make this monumental task an achievable reality. First of all, I would like to express my deepest gratitude for my research co-advisors: Professor Alvin Despain, whose continual support and multi-faceted interest in science have fueled my enthusiasm for research; and Professor Vason Srini, who is always there for me to discuss the latest computer architectural concept as well as to complain about various aspects of graduate student life. Secondly, I would like thank my other two readers: Professor Chittoor Ramamoorthy and Professor Terence Speed. Their time and effort are greatly appreciated. Thirdly, I would like to thank: Mike Carlton, for his development of the cache simulation modules; Chien Chen (my officemate) for his cooperative effort in the development of the NuSim simulator; Bruce Holmer, for the words of encouragement in the late hours of the night; Peter Van Roy, for the insightful feedbacks to my work; and Jim Wilson and Edward Wang, for being my living encyclopedias of Unix, X-windows, Lisp, and LATEX. I would also like to thank my other dear friends and colleagues in the Aquarius group and the C.S. Division at U.C. Berkeley, with whom I have shared many enlightening discussions. They include: Glenn Adams, Philip Bitar, Gino Cheng, Ralph Haygood, Kinson Ho, Ken Rimey, Ashok Singhal, Danielle Smith, Jerric Tam, Hervé Touati, and Benjamin Zorn.

Outside of the C.S. division, I am grateful to a number of close friends that I have made over the years. They have provided me with the friendship that I needed to continue my pursuit of a graduate degree. Among them are: Ann Greyson, Merilee Lau, Nhât Nguyêñ, Arthur Sato, Roger Sit, and Lịch Trân. Although my friends in the Vietnamese Student Association at U.C. Berkeley are too many to list, they have individually and collectively made a positive impact on my outlook for the future.

I am indebted to my late grandmother for the weekly letters of encouragement that kept me afloat in my first two years at Berkeley; to my parents for their unbounded love and support, and for the constant reminder of the best measures of success: good health and happiness; and last but not least, to Quê Lam, my "best friend" and companion, for lifting me high above the hurdles in the final lap.

# Contents

| Li | st of | Tables  |                                                    | vii  |

|----|-------|---------|----------------------------------------------------|------|

| Li | st of | Figure  | es s                                               | viii |

| 1  | Intr  | oducti  | on                                                 | 1    |

| •  | 1.1   |         | tion: The Memory Management Problem                | 1    |

|    | 1.2   | The Tl  | hesis                                              | 3    |

|    | 1.3   |         | ch Direction                                       |      |

|    | 1.4   |         | butions                                            | 5    |

|    | 1.5   |         | cation Outline                                     | 6    |

| 2  | Mu    | ltiproc | essors and Parallel Execution                      | 7    |

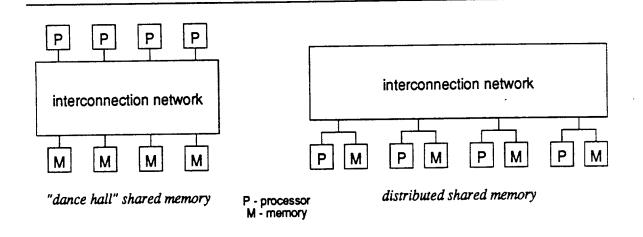

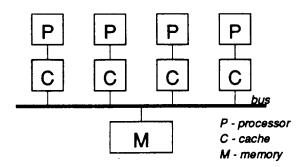

|    | 2.1   | Multip  | le Processor Systems                               | 7    |

|    |       | 2.1.1   | Message-Based Multicomputers                       | 7    |

|    |       | 2.1.2   |                                                    | 8    |

|    | 2.2   | Paralle | el Execution on Multiprocessors                    | 11   |

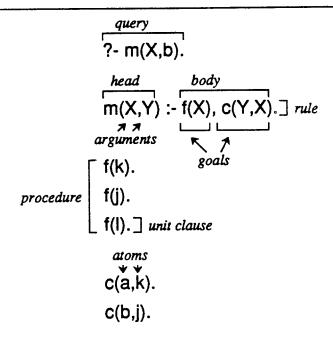

|    | 2.3   | Prolog  | and Its Applications                               | 12   |

|    |       | 2.3.1   |                                                    |      |

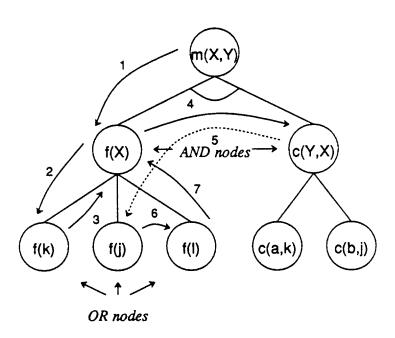

|    | 2.4   | Paralle | elism in Prolog                                    |      |

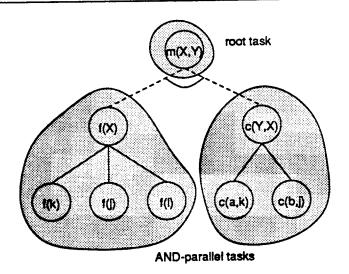

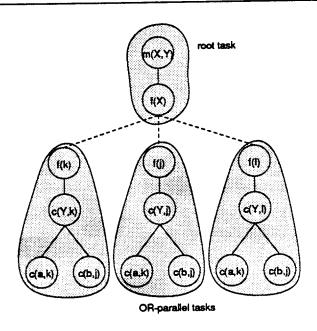

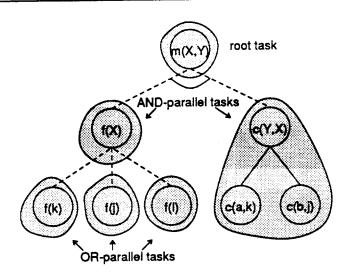

|    |       | 2.4.1   | AND-Parallelism                                    |      |

|    |       | 2.4.2   | OR-Parallelism                                     | 18   |

|    |       | 2.4.3   | Other Types of Parallelism                         | 20   |

|    | 2.5   | Proces  | ses and Tasks                                      |      |

|    | 2.6   | Chapte  | er Summary                                         | 22   |

| 3  | Me    | mory N  | Management: Issues and Past Solutions              | 23   |

|    | 3.1   | Issues  | in Memory Management                               |      |

|    | 3.2   | Memo    | ry Management Techniques: A Historical Perspective |      |

|    |       | 3.2.1   | Virtual Memory                                     |      |

|    |       | 3.2.2   | Allocation Strategies                              | 25   |

|    |       | 3.2.3   | Data Organization and Memory Access Policies       | . 27 |

|    | 3.3   | Seque   | ntial Execution of Prolog                          |      |

|    |       | 3.3.1   | Understanding Prolog Memory Requirements           |      |

|    |       | 3.3.2   | The WAM Stack Model                                | . 29 |

|   | 3.4 | Parallel Execution of Prolog                 | 31         |

|---|-----|----------------------------------------------|------------|

|   | 0.1 | 3.4.1 Memory Requirements                    | 31         |

|   |     | 3.4.2 Scheduling Effects on Memory Behavior  | 33         |

|   |     | 3.4.3 Message-Based Models                   | 33         |

|   |     | 3.4.4 Shared Memory Models                   | 35         |

|   |     | 3.4.5 Or-Parallel Binding Environments       | 37         |

|   | 3.5 | Static Partitioning of Globally Shared Space | 42         |

|   | 3.6 | Solving the Problems of Static Partitioning  | 42         |

|   | 3.0 | 3.6.1 Virtual Memory                         | 42         |

|   |     | 3.6.2 Garbage Collection                     | 43         |

|   |     | 3.6.3 Copy When Overflow                     | 44         |

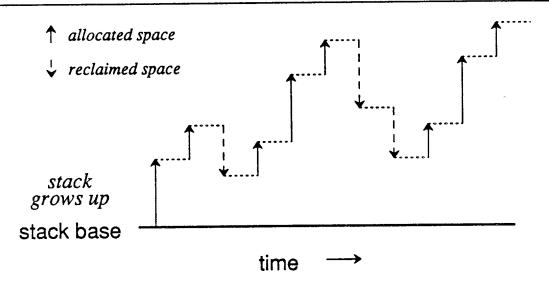

|   |     | 3.6.4 Dynamic Allocation                     | 44         |

|   | 27  | Chapter Summary                              | 44         |

|   | 3.7 | Chapter Summary                              |            |

| 4 | ELI | PS: The Explicitly Linked Paging Stack       | 46         |

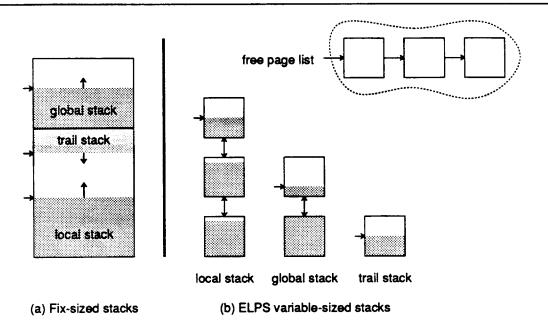

| - | 4.1 | General Model                                | 46         |

|   |     | 4.1.1 Page Partitioning                      | 46         |

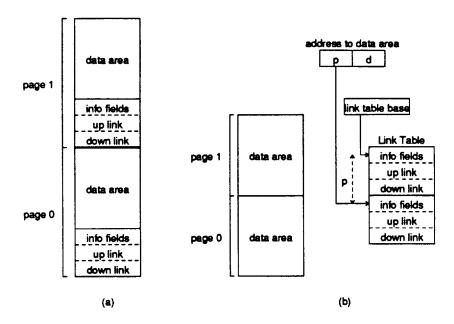

|   |     | 4.1.2 Link Management                        | 47         |

|   | 4.2 | Possible Implementations                     | 48         |

|   | *   | 4.2.1 Overflow and Underflow Detection       | 48         |

|   |     | 4.2.2 Overflow and Underflow Handling        | 50         |

|   |     | 4.2.3 Data Access                            | 50         |

|   |     | 4.2.4 Address Comparison                     | <b>5</b> 0 |

|   | 4.3 | Qualitative Evaluation                       | 51         |

|   |     | 4.3.1 Advantages                             | 51         |

|   |     | 4.3.2 Challenges                             | 51         |

|   |     | 4.3.3 Elimination of Address Comparison      | 52         |

|   | 4.4 | Chapter Summary                              | 54         |

|   |     |                                              |            |

| 5 | Nu  | Sim: A Multiprocessor System Simulator       | 55         |

|   | 5.1 | Introduction                                 | 55         |

|   | 5.2 | Simulator Design Goals                       | 56         |

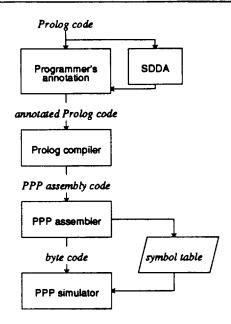

|   | 5.3 | Simulation System Overview                   | 57         |

|   |     | 5.3.1 Program Transformation                 | 57         |

|   |     | 5.3.2 Design Considerations                  | 59         |

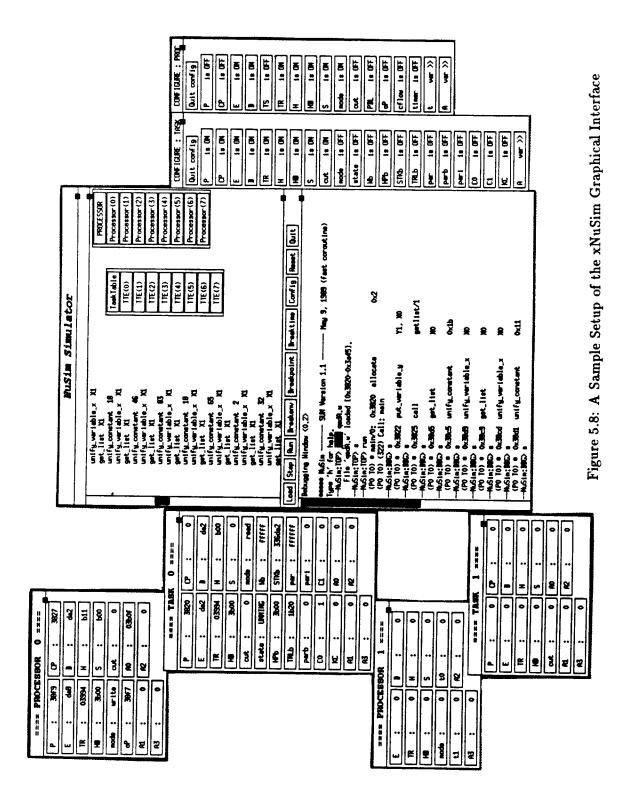

|   | 5.4 |                                              | 60         |

|   |     | 5.4.1 Assembler/Loader                       | 60         |

|   |     | 5.4.2 Command Interface                      | 61         |

|   |     | 5.4.3 Graphical Interface                    | 61         |

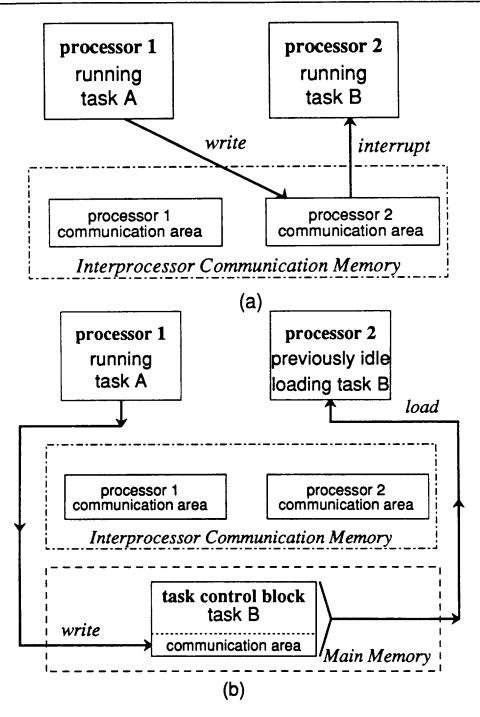

|   |     | 5.4.4 Main Simulation Engine                 | 61         |

|   |     | 5.4.5 Memory System                          | 64         |

|   | 5.5 | Instrumentation                              | 65         |

|   | 5.6 | Multi-level Debugging Facility               | 67         |

|   | 5.7 |                                              | 7          |

|   | 5.8 | Compatibility and Extendability              | 73         |

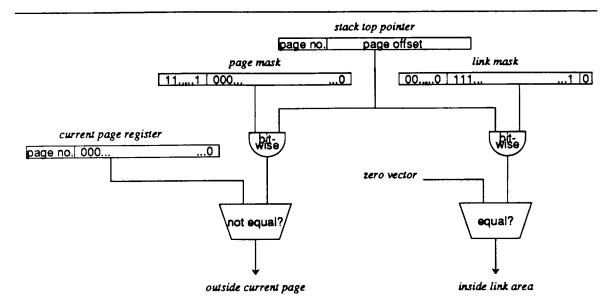

|   | 5.9         | Implementation of ELPS on the Simulated Multiprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74  |

|---|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |             | 5.9.1 Software Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74  |

|   |             | 5.9.2 Hardware Support for Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75  |

|   | 5.10        | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76  |

| 6 | Sim         | ulator Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 78  |

| • | 6.1         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78  |

|   | 6.2         | Validation Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 78  |

|   | 6.3         | Simulator Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80  |

|   | 0.5         | 6.3.1 VPsim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 80  |

|   |             | 6.3.2 Simulator Differences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81  |

|   | c 4         | The Validation of NuSim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82  |

|   | 6.4         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83  |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83  |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84  |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87  |

|   |             | 6.4.4 Operation Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 88  |

|   |             | 6.4.5 Memory Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 90  |

|   | 6.5         | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90  |

| 7 | ELF         | S Simulation Experiments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 91  |

|   | 7.1         | Sequential Execution Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91  |

|   |             | 7.1.1 Split Environment and Choice Point Stacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 91  |

|   |             | 7.1.2 Always Trail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 95  |

|   |             | 7.1.3 Put Permanent Variables on Heap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97  |

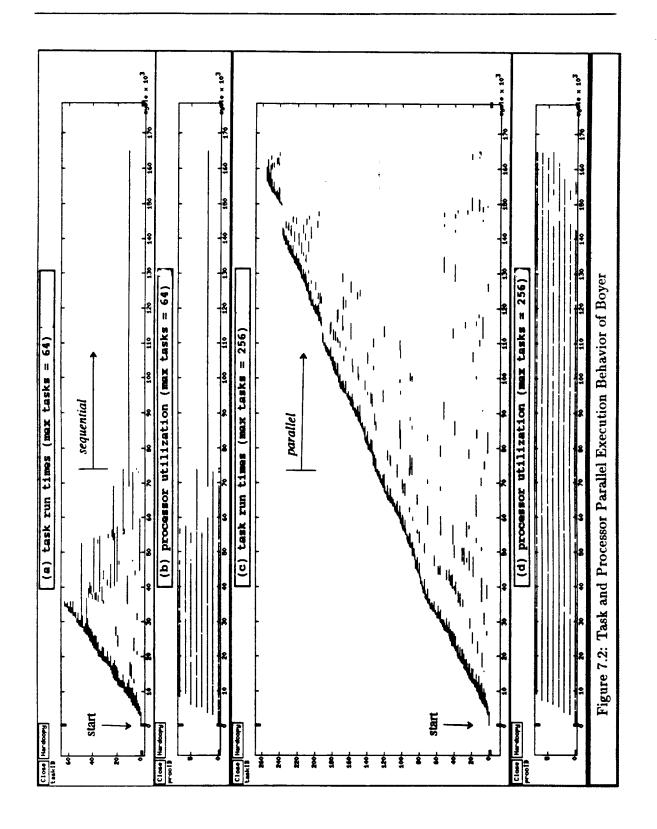

|   | 7.2         | Parallel Execution and ELPS Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100 |

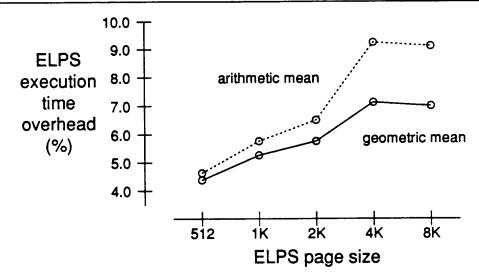

|   |             | 7.2.1 Execution Time Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100 |

|   |             | 7.2.2 Parallelism Gained                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 103 |

|   |             | 7.2.3 Effect of Page Size on Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105 |

|   |             | 7.2.4 Allocation and Deallocation Strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 109 |

|   | 7.3         | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 109 |

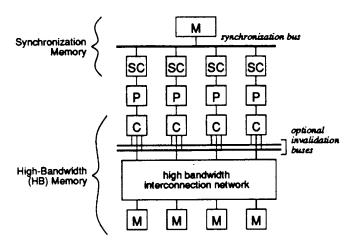

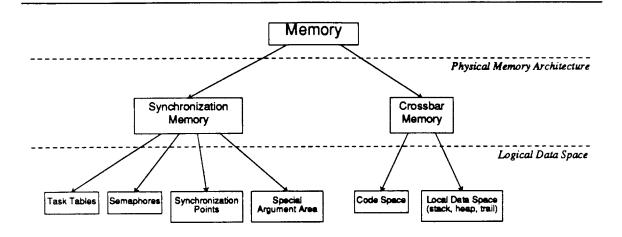

| 8 | <b>A</b> αι | arius-II: A Two-Tier Memory Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 112 |

| • | 8.1         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 112 |

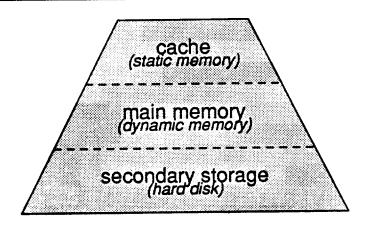

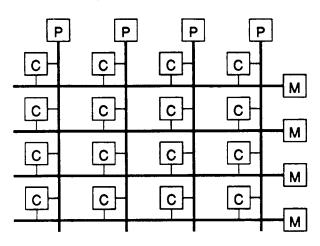

|   | 8.2         | High Performance Memory Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 113 |