Copyright © 1990, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# BERT - CIRCUIT ELECTROMIGRATION SIMULATOR

by

B. K. Liew, P. Fang, N. W. Cheung, and C. Hu

Memorandum No. UCB/ERL M90/3

8 January 1990

# BERT - CIRCUIT ELECTROMIGRATION SIMULATOR

•

by

B. K. Liew, P. Fang, N. W. Cheung, and C. Hu

Memorandum No. UCB/ERL M90/3

.

.

8 January 1990

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# **BERT - CIRCUIT ELECTROMIGRATION SIMULATOR**

# B. K. Liew, P. Fang, N. W. Cheung, and C. Hu Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, California 94720

# Abstract

Models for predicting interconnect and intermetallic contact reliability under arbitrary current waveforms have been developed [1-3]. These models are incorporated in the Circuit Electromigration Simulator module in BErkeley Reliability Tool (BERT). The simulator can (1) generate layout advisory for width and length of each interconnect, the safety factor of each contact and via in a circuit to meet user-specified reliability requirements and (2) estimate the overall circuit electromigration failure rate and/or cumulative failure percent of a layout design.

This work was partially supported by ISTO/SDIO administered through ONR under Contract N00019-85-K-0603.

# **Table of Contents**

| I. Overview of the Simulator                        | 1  |

|-----------------------------------------------------|----|

| 1.1 Introduction                                    | 1  |

| 1.2 Overview of the simulator                       | 1  |

| II. Electromigration Reliability Model              | 3  |

| 2.1 Introduction                                    | 3  |

| 2.2 Dependence on current density                   | 3  |

| 2.3 Dependence on geometry                          | 3  |

| 2.4 Dependence on statistical distribution          | 4  |

| III. Operation of the Simulator                     | 5  |

| 3.1 Installing the simulator                        | 5  |

| 3.2 Notational conventions                          | 5  |

| 3.3 Simulator commands in SPICE input deck          | 5  |

| 3.4 Setting up reliability parameters               | 6  |

| 3.5 Logical parameters in the rule file             | 6  |

| 3.6 Numerical parameters in the rule file           | 7  |

| 3.7 Parameters needed by the simulator              | 9  |

| 3.8 Example of EM design rule file                  | 10 |

| 3.9 Invoking the simulator                          | 11 |

| IV. Operation of the Layout Extractor               | 12 |

| 4.1 Introduction                                    | 12 |

| 4.2 Manhattan circuit extractor for VLSI simulation | 12 |

| 4.3 Modifications in mextra                         | 12 |

| 4.4 Limitations of the layout extractor             | 12 |

| 4.5 Converting .sim format to SPICE input format    | 13 |

| 4.6 Plotting cif layout                             | 13 |

| V. Setting up Geometry File by Hand                 | 15 |

| 5.1 Introduction                                    | 15 |

| 5.2 The format of user-entered geometry file        | 15 |

| 5.3 "Stacked" metal connections                     | 16 |

| VI. Output from the Simulator                       | 17 |

| 6.1 Introduction                                    | 17 |

| 6.2 Current Table                                   | 17 |

| 6.3 Layout advisory tables                          | 17 |

| 6.4 Failure rate statistics                         | 18 |

| VII. Examples of Simulation                         | 19 |

| 7.1 Introduction                                    | 19 |

| 7.2 The design rule and reliability parameters      | 19 |

| 7.3 CMOS EPROM sense amplifier                                         | 20 |

|------------------------------------------------------------------------|----|

| 7.4 21-Stage BiCMOS inverter chain                                     | 25 |

| 7.5 CMOS logic circuit using inverters, NOR and NAND gates             | 28 |

| 7.6 CMOS fulladder circuit                                             | 34 |

| 7.7 Configuration of our system                                        | 34 |

| VIII. Credits and Acknowledgement                                      | 36 |

| IX. References                                                         | 37 |

| Appendix A. Lognormal Distribution and Length Dependence Model         | 38 |

| Appendix B. Width Dependence Parameters                                | 40 |

| Appendix C. Default Values in EM Simulator                             | 42 |

| Appendix D. CIF Layer Names in the Layout Extractor                    | 43 |

| Appendix E. Setting up Alternative Technology for the Layout Extractor | 44 |

| Appendix F: EM Simulator Error Messages                                | 46 |

| Appendix G: Manual Pages for mextra, sim2spice and cif2ps              | 48 |

# L Overview of the Simulator

## **1.1 Introduction**

In the effort to assure reliable design in VLSI system, it is imperative that the reliability guidelines and potential reliability hazards are known during the design stage of a circuit. In this respect, circuit reliability simulator becomes an indispensable tool for circuit designers. The BErkerley Reliability Tool (BERT) is developed with the aim to assist circuit designer in implementing design for reliability. Presently, BERT has three modules: Circuit Aging Simulator (CAS) [4] for hot-electron degradation, Circuit Oxide Reliability Simulator (CORS) [5] for MOS oxide breakdown and Circuit Electromigration Simulator for interconnect and contact electromigration failures. This report describes the Circuit Electromigration Simulator.

#### 1.2 Overview of the Simulator

To use the EM simulator, the circuit designer prepares the SPICE input deck the usual way or uses the layout extractor to produce the SPICE input deck. But before invoking SPICE to perform circuit analysis, the EM simulator pre-processor is called. The pre-processor adds a dummy voltage source in the original SPICE input deck for every terminal of the circuit element and requests SPICE to printout the current in all the dummy voltage sources (this is necessary because SPICE can only print current flowing in voltage sources). In addition, a database of the dummy voltage sources and their associated circuit elements are generated by the pre-processor. This information will be passed automatically to the post-processor. The modified input deck can now be sent to SPICE simulator.

Output from SPICE simulation is filtered by the post-processor which reads the current waveforms and performs the required calculations. At the same time, the post-processor will remove from the SPICE output the voltage sources and printout lines added by the pre-processor. In this manner, the operation of the simulator is transparent to the user.

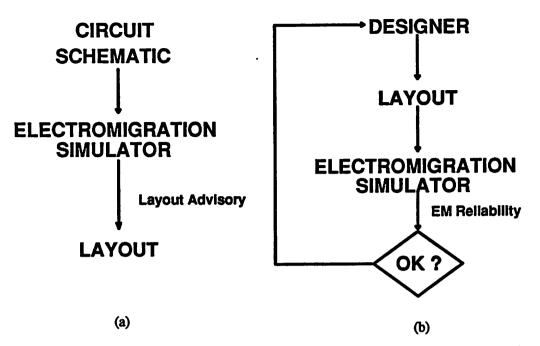

There are two modes of operation for the simulator, either one or both can be selected. In the first mode (Fig. 1(a)), the simulator is used as as a layout advisor. The user inputs the desired reliability specification in failure rate after a specified device operating hours. The simulator will generate layout guidelines for width and length of each interconnect (up to three layers of interconnect are supported), and safety factor for each contact or via in a circuit to meet user-specified reliability requirement.

In the second mode of operation (Fig. 1(b)), the simulator calculates the failure rate and/or the cumulative percent failure of a circuit layout. The user can supply the layout geometry of all the interconnects, contacts and vias for the layout by hand or more conveniently use the layout extractor which is available with our simulator. The layout extractor reads in the Caltech Intermediate Format (CIF) layout description file, extracts the circuit elements, and generates the SPICE input deck for the circuit. At the same time, it also fractures the interconnect patterns into segments and produces a geometry description file containing the length and width of each segment. Area of metal-to-metal vias and metal-to-silicon contacts are also identified. The geometry information is added to the database produced by the pre-processor and will be used by the postprocessor to calculate overall circuit electromigration reliability.

Fig.1. The electromigration simulator can be used in two ways: (a) to generate layout advisory, (b) to compute circuit failure rate and cumulative percent failure.

#### **II.** Electromigration Reliability Model

#### **2.1 Introduction**

This section briefly describes the physical and statistical models implemented in the simulator.

#### 2.2 Dependence on current density

The electromigration time-to-failure (TTF) under arbitrary current waveforms (which is valid for frequencies of waveforms greater than 1kHz) is given by [2]:

$$TTF = \frac{A_{DC}(T)}{\overline{|J|^{m-1}} \overline{J} \left[ 1 + \frac{A_{DC}}{A_{AC}} \overline{(\overline{|J|} - \overline{J})} \right]}$$

(1)

where  $\overline{J}$  is the average current density,  $\overline{|J|}$  is the average of the absolute current density.  $m, A_{DC}$  and  $A_{AC}$  are experimentally determined constants which need to be supplied to the simulator by the user.  $A_{AC}(T)$  and  $A_{DC}(T)$  have Arrhenius dependence on temperature with the same activation energy  $E_a$ .

#### 2.3 Dependence on geometry

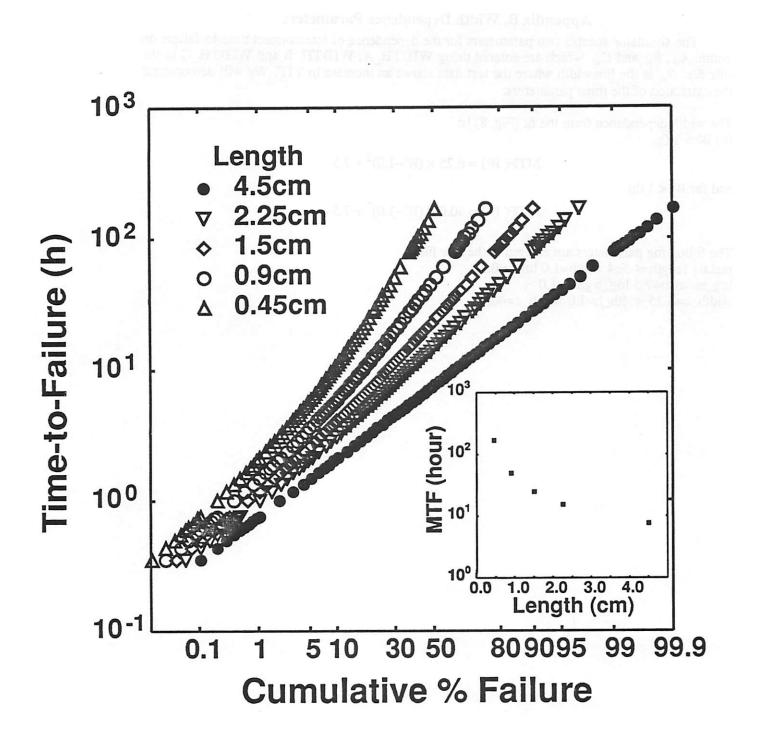

The simulator uses the independent element analysis for length dependence described in Ref[6]. The user is requested to input one time-to-failure result for long interconnect (longer than the longest interconnect in the circuit). Failure statistics are calculated for shorter lines by the following assumption: long interconnect is modeled by a series of shorter segments (see Appendix A) and its TTF is determined by the weakest segment. Therefore, the failure rate of a long metal line is the sum of the failure rates of shorter segments. For example, if the user inputs a MTF of 7.5 hours for 4.5 cm long interconnect. From this data, the simulator can construct the failure distribution for a line half the length of the original test line (with failure probability of F(t)). Because the 4.5 cm long line will fail if either or both of the two segments fail, the failure probability of a 2.25 cm line  $G_2(t)$  is:

$$[1 - G_2(t)]^2 = [1 - F(t)]$$

$$G_2(t) = 1 - [1 - F(t)]^{\frac{1}{2}}$$

The first equation states that the probability that the long line will not fail is the product of the probability of the two shorter segments are good. Thus, at time t = 7.5, the failure probability for the 2.25 cm long line is 0.29. In general, for a line that is 1/x of the long test line,  $G_x(t)$  is:

$$G_x(t) = 1 - [1 - F(t)]^{\frac{1}{x}}$$

(2)

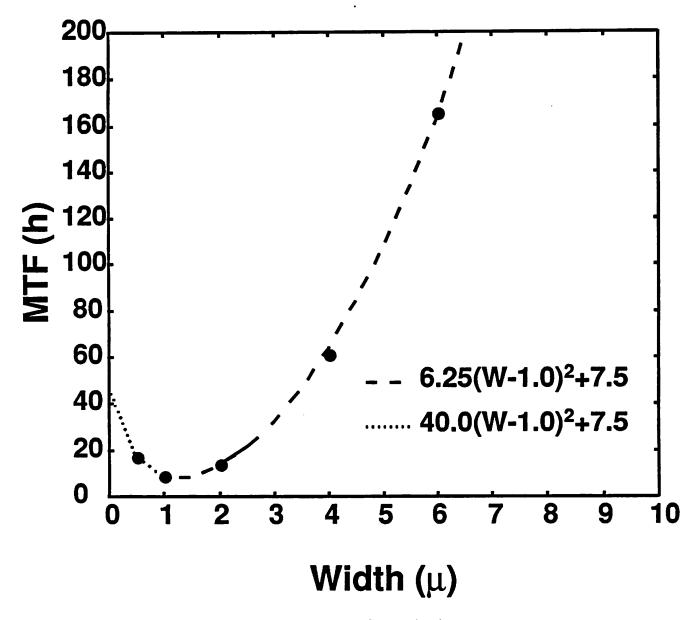

The width dependence of TTF is obtained from empirical fit of TTF versus linewidth data using piecewise fit of two second order polynomial functions (see Appendix B), which would allow an increase in TTF as linewidth is decreased below the average grain size [7]. The width dependence is specified by four parameters,  $A_w$ ,  $B_w$ ,  $C_w$  and  $D_w$  which are defined by the following equations:

for  $W \ge B_w$ :

$$TTF(W) = A_w \times (W - B_w)^2 + D_w$$

(3a)

for  $W < B_w$ :

$$TTF(W) = C_w \times (W - B_w)^2 + D_w$$

(3b)

$B_w$  is the linewidth at the minimum of TTF. It is approximately equal to the average grain size in the interconnect.

The failure probability for one contact/via opening is similarly calculated from the test data of a chain of contacts/vias.

# 2.4 Dependence on statistical distribution

.

The user is given the choice of using either lognormal or Weibull distribution function to calculate failure rate and cumulative percent failure. The user is advised to choose the appropriate distribution function that best describes experimental time-to-failure data. Ref[8] has an excellent discussion on the statistical failure distributions.

Although lognormal distribution function is commonly used to represent the experimental time-to-failure data, there is no physical foundation to expect that the electromigration failures should be lognormally distributed. If lognormal distribution is chosen, the length dependence model adopted in the simulator will results in distributions for shorter lines that are not lognormal. This inconsistency is illustrated in Appendix A. If Weibull distribution is chosen, the inconsistency is removed, i.e. failure distributions for all lines are Weibull.

# **III.** Operation of the Simulator

### 3.1 Installing the simulator

The makefile in the BERT distribution tape will automatically compile all modules and create the BERT executable codes prebert and postbert. Simply type make in UNIX. In addition, make will create the executable codes for the layout extractor mextra, sim2spice and also the code for a cif plotting program cif2ps. A "standalone" version of the electromigration simulator can be created (stripped off hot electron circuit aging and time-dependent oxide breakdown modules) by typing make emonly in the BERT/EM directory.

## **3.2 Notational conventions**

The following notations will be used to indicate how the command should be entered:

• Keywords shown in **bold** must be entered exactly as shown. However, they can consist of any combination of uppercase and lowercase letters.

• The items in lowercase *italic* must be supplied. For example, the name of the file should be entered when *filename* is shown in the format.

• Items enclosed in square brackets ([]) are optional. If optional information is to be included, the information is entered without the brackets.

• Items enclosed in braces ({}) are to appear together. Information is not complete if one of the items is not specified.

• Either one of the two items (or groups of items in braces) separated by a bar (1) can be specified but not both together.

• An ellipsis (...) indicates that an item can be repeated as many times as needed but the item(s) must stay in one line.

# 3.3 Simulator commands in SPICE input deck

The following commands are inserted in the SPICE input deck to request EM analysis. Only one command can appear in each line.

# (1) .EMMODEL filename

Example:

.EMMODEL emrulefile This command tells the simulator that reliability parameters are in emrulefile.

# (2) .EMSTAT filename hour [hour...]

Example:

.EMSTAT bicmos.int 100.0 1.0e3 2e4

This command specifies the failure rates are to be calculated at times: 100 hours, 1000 hours and 20000 hours. The geometry file which contains the length and width of interconnects, number of contact and via openings that the user set up (by hand) is *bicmos.int*.

(3) .EMSTATX filename hour [hour...]

Example:

#### .EMSTATX fulladder.geo 200.0

This command specifies the failure rates are to be calculated at times: 200 hours. The geometry file extracted from the layout by the extractor is *fulladder.geo*.

Either one of .EMSTAT or .EMSTATX, but not both is needed if user requests failure rate calculation for a circuit layout.

#### 3.4 Setting up reliability parameters

The simulator needs as input the necessary reliability parameters to perform electromigration analysis. The parameters are given in a file (which will be referred to as the EM design rule file). There are two types of parameters: numerical and logical. The parameter name must be typed in full. However, it can contain a combination of lowercase and uppercase letters. There is no requirement on the order the parameters are entered in the file. User is allowed to enter more than one parameters on a single line. Default parameters are given in Appendix C.

• Logical parameters are entered without assignment. It is set true as it appears.

Example:

#### PRINTCURRENT

• Numerical parameters are assigned values by following the name of the parameter immediately by an equal sign, and the value. The value must also immediately follow the equal sign. There can be no blank space in between.

Example:

LENGTH=1.2e4

• Comments can be entered by entering \* in the first column of the comment line. Entries in that \_\_ line will not be read by the simulator.

Example:

\*This is a comment line

#### 3.5 Logical parameters in the rule file

The list of logical parameters are:

(1) **PRINTCURRENT**

Request simulator to print out the current in each connection.

(2) SKIPLAYOUTCUR

Normally, the simulator generates the layout advisory table containing the width and length of interconnect, the safety factor of contacts and vias in a design for a number of specified current values to meet the reliability specification. This option requests the simulator not to generate this table.

#### (3) SKIPLAYOUTGEO

Normally, the simulator generates the layout advisory table containing width and length of each interconnect in the circuit, the safety factor of contacts and vias in every connection of the circuit to meet the reliability specification. This option requests the simulator not to generate this table.

## (4) SKIPFAILRATE

(5) SKIPFAILPERCENT

The simulator will not print out the cumulative percent failure table (if SKIPFAILPER-CENT is specified) or the failure rate table (if SKIPFAILRATE is specified). The default is both tables will be printed if either .EMSTAT or .EMSTATX card is found in the SPICE input deck.

(4) METAL1

The reliability parameters that follow are for metal-one.

(5) METAL2

The reliability parameters that follow are for metal-two.

- (6) METAL3 The reliability parameters that follow are for metal-three.

- (7) CONTACT The reliability parameters that follow are for metal-one contact to diffusion.

- (8) VIA

The reliability parameters that follow are for metal-to-metal vias.

# 3.6 Numerical parameters in the rule file

The list of numerical parameters are:

- (1) NCURRENT=ncurrent current1 current2 ... currentn

- Example:

NCURRENT=4 1.0e-4 2.0e-4 1.0e-3 2.0e-3

*ncurrent* is the number of current values the simulator uses to generate the current layout advisory table. *current1..currentn* are given in Amperes. There must be exactly *ncurrent* fields following *ncurrent* and they must all be in one line.

- (2) AC\_DEFINE=ac\_define

- Example:

Ξ,

# AC\_DEFINE=0.1

*ac\_define* is used as a criterion for pure AC waveforms. The simulator will treat a current waveform as pure AC if the average current is less than or equal to *ac\_define* × the average of the absolute current. This parameter is important because quite often the transient analysis in SPICE does not result in pure AC waveform for charging and discharging of a capacitor node. This is because the time duration requested in the .TRAN card might not cover one period under steady state operation. Usually a value of 0.1-0.2 is reasonable. To obtain steady state waveforms, user is advised to set up SPICE to run for more than one cycle of the waveform.

(3) MINJCURRENT=minJcurrent Example: MINJCURRENT=1.0e3

In order to save computation time, when the current density in the interconnect, contact or via is below minJcurrent (in  $A/cm^2$ ), the simulator will skip failure calculation and prints J <MinJ in the output.

(4) WORSTLIST=WorstList Example: WORSTLIST=0.5

The simulator will print out worst *WorstList* fraction of the connections in the failure rate/cumulative percent failure tables. In the example, half (50%) of the worst connections will be printed.

(5) NWIDTH=nwidth width1 width2 ... widthn Example: NWIDTH=3 0.8 1.2 2.0

*nwidth* is the number of widths the simulator will use to generate the layout advisory table for interconnect. *width1..widthn* are given in  $\mu$ m. There must be exactly *nwidth* fields following *nwidth* and they must all be in one line.

(6) NCV=*ncv* N1 N2 ... Nn Example: NCV=4 1.0 2.0 3.0 4.0

> ncv tells the the simulator that user wishes a layout advisory table for contacts and vias containing ncv columns for N1..Nn openings. In each column a safety factor is generated for the number of contact or via openings (in parallel) at that connection. There must be exactly ncv fields following ncv and they must all be in one line. The example shown above will request simulator to calculate safety factor for connections having: one contact/via, two contact/via, three contact/via and four contact/via openings.

(7) **SPEC\_TIME**=spec\_time

Example:

SPEC\_TIME=1.0e6

*spec\_time* is the device operating hours when failure rate is *spec\_failrate* in the user's reliability specification. *spec\_time* is in hours. The simulator will generate layout advisory to meet this spec.

(8) SPEC\_FAILRATE=spec\_failrate

Example:

SPEC\_FAILRATE=1.0e-3

spec\_failrate (in 1/hour) is the failure rate at spec\_time (hours) in the user's reliability specification. Note that 1 FIT = 0.1% percent ( $10^{-3}$ ) failures per million ( $10^{6}$ ) device hours is equal to a SPEC\_FAILRATE of  $10^{-9}$ . The simulator will generate layout advisory to meet this spec.

(9) **TOP**=*T*<sub>op</sub>

Example:

TOP=25

The circuit operates at temperature  $T_{op}$  (in °C). The accelerated testing data entered by the user will be extrapolated to this temperature.

The following parameters apply to metal-one, metal-two, metal-three, metal-one to diffusion contact and metal-to-metal via. To associate the parameters to one of the connection types, one of the logical parameters: METAL1, METAL2, METAL3, CONTACT and VIA must be set before any of the following appears. Items (1) to (14) must be given to complete the parameter set for each connection type. The simulator will skip any connection type with incomplete parameter set.

- (1)  $ADC = A_{DC}$

- (2)  $AAC=A_{AC}$

- (3) M=m

- (4) **TDATA=** $T_{data}$

- (5)  $EA = E_a$

Above are the parameters in Eq.(1). Note that, the user will have to enter the experimental determined values of  $A_{DC}$  and  $A_{AC}$  (both are in units of hours  $\times (A/cm^2)^2$ ). These values are obtained from experiment at temperature  $T_{data}$  (in °C).  $E_a$  is the activation energy for  $A_{DC}$

and  $A_{AC}$ .

- (6) THICK=thickness

- (7) WIDTH=width

- (8) LENGTH=length

These specify the *thickness*, width and length (all in  $\mu$ m) of interconnect used in electromigration lifetime experiment to extract  $A_{DC}$ ,  $A_{AC}$  and m.

- (9) AREA=area

- (10) NCHAIN=nchain

This specifies the *area* (in  $\mu$ m<sup>2</sup>) of each contact or via in the chain test structure used in lifetime experiment to extract  $A_{DC}$ ,  $A_{AC}$  and m. *nchain* is the number of contacts or vias in series in the test structure.

- (11) LOGMEDIAN=MTF

- (12) LOGSIGMA= $\sigma$

Select lognormal distribution with median MTF (in hours) and the lognormal standard deviation  $\sigma$ . The MTF is the experimental median-time-to-failure at temperature  $T_{data}$ .

- (13) WEIBULL\_A= $\alpha$

- (14) WEIBULL  $B=\beta$

Select Weibull distribution and specify the parameters  $\alpha$  and  $\beta$ . The failure data are collected at temperature  $T_{data}$ . The Weibull cumulative distribution function is described by:

$$F(t) = 1 - \exp(-\frac{1}{\alpha} t^{\beta})$$

(4)

where t is in hours.

- (15) WIDTH\_A= $A_w$

- (16) WIDTH\_B= $B_{w}$

- (17) WIDTH  $C=C_w$

Specify the width dependence of time-to-failure for interconnect (see Appendix B for an example). The parameters  $A_w$ ,  $B_w$ ,  $C_w$  are defined by Eqs.3(a) and 3(b) which are repeated below:

for  $W \ge B_w$ :

$$TTF(W) = A_w \times (W - B_w)^2 + D_w$$

(3a)

for  $W < B_w$ :

$$\Gamma TF(W) = C_w \times (W - B_w)^2 + D_w \tag{3b}$$

$D_w$  is found using the previously entered experimental time-to-failure and width. W is in  $\mu m$ . Note that by setting,  $A_w = C_w = 0$ , TTF will be a constant independent of width.

#### 3.7 Parameters needed by the simulator

One set of physical and statistical parameters are needed for each layer of interconnect, contact and via. The parameters are entered by the user in the EM design rule file which will be read by the post-processor.

The user is required to enter the parameters in Eq.(1) for long interconnect:  $A_{DC}$ ,  $A_{AC}$ , m and  $E_a$ . These parameters can be extracted from the TTF versus current density plot and the Arrhenius plot of TTF versus temperature. In addition, the length, width and thickness of the test

structures are input to the simulator. The user also selects either lognormal or Weibull distribution to represent the TTF data. If TTF is required to be a function of width (the simulator defaults to constant width dependence), the width parameters (Eqs.(3a) and (3b)) have to be extracted from additional experiments using the same long line but with a number of widths.

The parameter sets for contact and via are set up similarly. The test data for contact or via electromigration are obtained from contact/via chain test structures. User enters the  $A_{DC}$ ,  $A_{AC}$ , m,  $E_a$  as well as the area and the total number of contacts/vias in the chain.

# 3.8 Example of EM design rule file:

The following is an example of the rule file:

| * Reliability parameters for electromigration simulator                         |

|---------------------------------------------------------------------------------|

| PrintCurrent                                                                    |

| * print the current in each connection in the circuit                           |

| ncurrent=3 0.50e-3 1.00e-3 2.00e-3                                              |

| * requests simulator to generate current layout guidelines for 3 current values |

| SkipFailpercent                                                                 |

| * Do not print cumulative percent failure table, only failure rate table will   |

| * be printed                                                                    |

| <br>WorstList=0.5                                                               |

| * print half (50%) of the worst connections in failure rate/cumulative percent  |

| * failure table.                                                                |

| AC_define=0.2                                                                   |

| * Definition of Pure AC current                                                 |

| MinJcurrent=1e2                                                                 |

| * ignore anything with current density less than 1e2 A/cm2                      |

| spec_time=1.0e+4 spec_failrate=1.0e-9                                           |

| * this is the reliability specifications                                        |

| nwidth=2 1.0 2.0                                                                |

| * Generate layout guidelines for two widths of interconnect                     |

| ncv=3 1.0 2.0 4.0                                                               |

| * Generate layout guidelines for three contacts/vias openings: 1, 2 and 4       |

| * at a connection                                                               |

| * The following set for metal-one                                               |

| metal1 length=4.5e+4 width=1.0 thick=0.1                                        |

| Tdata=25.0 Ea=0.5                                                               |

| width_a=0.0 width_b=1.0<br>m=2.0 Adc=1.0e+16 Aac=1.0e+20                        |

|                                                                                 |

| Lognormal logsigma=1.0 logmedian=7.52                                           |

| * The following set for metal-two<br>metal2 length=4.5e+4 width=1.0 thick=0.1   |

| Tdata=25.0 Ea=0.5                                                               |

| width_a=0.0 width_b=1.0                                                         |

| m=2.0  Adc=1.0e+15  Aac=1.0e+19                                                 |

| Lognormal logsigma=1.0 logmedian=7.52                                           |

| * The following set for via                                                     |

| via area=1.0 nchain=10.0                                                        |

| * The test structure is a chain of 10 vias, each is $1\mu m^2$                  |

| Tdata=25.0 Ea=0.5                                                               |

| area_a=0.0 area_b=1.0                                                           |

| m=2.0  Adc=1.0e+16  Aac=1.0e+20                                                 |

| Lognormal logsigma=1.0 logmedian=7.52                                           |

|                                                                                 |

\* Because set for contact and metal-three are not given

\* Simulator will ignore them

#### 3.9 Invoking the simulator

The simulator can be invoked using the following command line:

prebert [-x] deckfile | spice | postbert [> outfile]

x is the version of *spice*, 2 for SPICE2, 3 for SPICE3B1 and 4 for SPICE3C1. The default (if no option is specified) is SPICE3C1. *spice* is the SPICE command used. Example:

vivante>prebert bicmos | spice3c1 | postbert > em.out

The command to invoke the "standalone" version of the pre-processor is:

preem [-G geometryfile] deckfile | spice > spiceoutfile

The pre-processor will generate the geometry file in *deckfile.geo* (or optionally named *geometryfile* with -G). If the SPICE input deck is not generated from the layout extractor, the pre-processor will add dummy voltages in the SPICE input deck. The dummy voltages have prefix VEM and the added node number will start from 5000. To prevent error in the simulator, the original SPICE input deck must not have voltage sources with prefix VEM and node number equal to or exceeding 5000. User can change the starting number of dummy nodes by defining new STARTNODE in the pre-processor header file empredef.h

The command to invoke the "standalone" version of the post-processor is:

postem [-S x] - Rrulefile - Ggeometryfile spiceoutfile [> outfile]

x is the version of *spice*, 2 for SPICE2, 3 for SPICE3B1 and 4 for SPICE3C1. The default (if no option is specified) is SPICE3C1. *rulefile* is the EM design rule file described previously and *geometryfile* is the geometry file from the pre-processor. *spiceoutfile* is the output file from SPICE simulation.

By using the "standalone" version of the pre- and post-processor, the user can save the SPICE output *spiceoutfile* (which can be quite a large file). This file can be post-processed again to generate layout guidelines and failure statistics if any of the parameters in the design rule file is changed. Thus user does not need to run SPICE analysis again.

# **IV.** Operation of the Layout Extractor

#### 4.1 Introduction

This section describes the procedures to extract SPICE input deck from CIF layout file. First, mextra is used to extract the connectivity of transistor, interconnect, contact and via. The extracted information is written to a file in sim format. sim2spice is called next to construct the SPICE input deck and also produce the layout geometry database from the sim file. A CIF to PostScript plotting program cif2ps is provided to plot the CIF file. cif2ps can also be used to locate input and power supply nodes in the SPICE deck and also to view any reliability hazards in interconnects, vias and contacts.

#### 4.2 Manhattan circuit extractor for VLSI simulation

The operation of the layout extractor: mextra is described in the accompanying manual page (see Appendix G). The technologies known to mextra are: nMOS ("nmos"), MOSIS P well CMOS/Bulk, also known as CBPM ("cmos-pw"), MOSIS Scalable CMOS/Bulk N-well, also known as SCN ("cmos-nw"), MOSIS Scalable CMOS/Bulk P-well, also known as SCP ("cmos-s"), and MOSIS Scalable CMOS/Bulk Generic, also known as SCG ("cmos-g"). The mask layer names for each technology are listed in Appendix D. If the CIF layers have different names than the ones listed in Appendix B, user can set up his/her own CIF layer names and use the -L option of mextra (explained in Appendix E). An example of the command line is:

vivante>mextra -t scmos circ.cif

which extracts the layout from circ.cif file. The technology is scmos.

#### 4.3 Modifications in mextra

Detailed description of the original version of mextra can be found in Ref[9]. Modifications have been made to the original version to extract interconnect width and length, metal-to-metal via and metal-to-silicon contact area. The additional layout information is appended to the *basename.sim* file. The line describing the via or contact geometry has the following format:

#### type nodel node2 area xloc yloc;

where type is either CONT or VIA (for metal-to-silicon contact or metal-to-metal via), nodel and node2 are the connection nodes, area is in square centi-microns (=0.0001  $\mu$ m<sup>2</sup>). The location of the via or contact is given by *xloc* and *yloc* in cif coordinates.

The line describing the metal-one or metal-two interconnect has the following format:

#### type nodel node2 width length xloc yloc;

where type is either M1 or M2, nodel and node2 are the connection nodes, width and length are in centi-micron (=0.01  $\mu$ ). The location of the interconnect is given by xloc and yloc in cif coordinates.

#### 4.4 Limitations of the layout extractor

The layout extractor has been tested for a number of circuit designs. Although it works well in most cases, the user has to be aware of its limitations:

- (1) mextra can only handle Manhattan type structure. Non-manhattan polygon will be ignored by the extractor.

- (2) mextra can only extract two layers of interconnects.

- (3) The extracted interconnect length and width are accurate for long metal lines. mextra tends to err at irregular corners and where many metal lines join together.

- (4) mextra, by default only recognizes the technologies listed in Appendix D. The user is advised to check the layer names in his/her CIF file with the layers listed in the table to

prevent unknow layers error. If necessary, user can set up alternate CIF layer names (see Appendix E).

#### 4.5 Converting .sim format to SPICE input format

The program sim2spice converts the basename.sim file produced by mextra to SPICE input deck and produces the layout geometry database in file basename.geo. Two files are needed for successful conversion: basename.sim which contains connectivity information and basename.nodes which contains node names and numbers. Both files are generated by mextra. sim2spice produces the spice input deck in basename.spice and the geometry information of metal interconnects, contacts and vias in basename.geo. In the SPICE deck, sim2spice will add for each interconnect and contact structure a dummy voltage source. For metal-to-silicon contact and metal-to-metal via a small series resistance (0.001  $\Omega$ ) will also be added in the SPICE deck. The name of the dummy voltage source has prefix VEM and the series resistor has prefix REM. The resistor is needed to prevent SPICE error when there is a closed loop consisting of voltage sources only.

The SPICE deck from sim2spice is incomplete. It does not have the input and power sources and it does not request any spice analysis. User is required to insert the voltages, set up the transient analysis card. The user will also have to insert the following two cards to request EM analysis (explained in Sec 3.3):

.EMMODEL rulefile .EMSTATX basename.geo 1.0e4 1.0e5

where *rulefile* is the EM design rule file and *basename.geo* is the extracted geometry file from sim2spice.

The user can locate the input, power and output nodes of the circuit by using the cif2ps program. This is described in Section 4.5.

The extracted SPICE deck may have a number of floating nodes where there is only one connection to the node. This will cause SPICE2G6 to abort simulation. Therefore, the user is advised to use SPICE3C1 or SPICE3B1 for the extracted SPICE input deck.

The geometry information of the layout in basename.geo has the following format:

node1 node2 VEMxxx type {width length} | area xloc yloc;

where nodel and node2 are the nodes in SPICE deck, VEMxxx is the dummy voltage source in SPICE deck, type is one of M1 (for metal-one), M2 (for metal-two), CO (for contact) or VI (for via), width and length are in  $\mu$ m (for interconnects) and area (for contacts and vias) is in  $\mu$ m<sup>2</sup>. The location of the connection is given in CIF coordinates xloc and yloc.

sim2spice also produces a file *basename.spcnode* containing node numbers in the SPICE deck and their locations in the layout. The list is written in CIF format. It can be read by cif2ps to make a plot showing the circuit with the named nodes superimposed.

An example of the command line is:

vivante>sim2spice circ.sim

which will read circ.sim, circ.nodes and produce circ.spice, circ.spcnode and circ.geo.

#### 4.6 Plotting CIF file

The program cif2ps converts CIF layout file to PostScript file which can be sent to a PostScript printer for printout. The operation of cif2ps is described in the accompanying manual page (see Appendix G). The following command line:

vivante>cif2ps -t scmos circ.cif | lpr

will plot circ.cif (which contains CIF layer names of scmos technology). cif2ps is technology

dependent: the layers known to cif2ps are listed in Appendix B. Appendix C describes the setting up of different CIF layer names for mextra and cif2ps.

The -m option of cif2ps can be used to superimpose CIF labels on CIF layout. This is useful in locating the SPICE node numbers assigned by sim2spice. Recall that sim2spice writes the locations of nodes in CIF format to *basename.spcnode* file. This file can be printed together with the original CIF layout file *basename.cif* using cif2ps -m. For example:

vivante>cif2ps -m -t scmos circ.cif circ.spcnode | lpr

will print the SPICE node numbers on the layout circ.cif.

The EM simulator produces a listing of metal structures that pose reliability hazards in CIF format. This listing can be printed on the CIF layout using the same procedure:

vivante>cif2ps -m -t scmos circ.cif circ.worst | lpr

circ.worst contains the listing of the worst metal structures.

# V. Setting up Geometry File by Hand

#### **5.1 Introduction**

The user can input the layout geometry by hand as an alternative to using the layout extractor. The use of the layout extractor might be cumbersome because it generates a lot of data and will consume considerable computation time in the SPICE simulation. For layout which uses a large number of standard cells, such as gate arrays and memory chips, user is advised to set up the geometry file by hand. Because of the repetition of standard cells and only the current waveforms in one cell are needed, user can set up subcircuit elements (using the SUBCKT card in SPICE) for all but one of the standard cells in the circuit. This implicitly instructs the EM simulator not to perform failure calculation for the metal connections in the subcircuit element. As a result, this will reduce the amount of cpu time used in the EM and SPICE analysis. The user can do this by the following procedures:

- (1) User enters the layout geometry of one cell by hand (or just have the layout extractor extract one cell).

- (2) User then sets up the subcircuit definition using the SUBCKT card in SPICE. All but one cell is replaced by subcircuit call. (using the Xzzz element in SPICE).

- (3) Layout geometry information is entered into the geometry file for that cell only. User is required to identify any "stacked" connections in the circuit. These are the connections that simultaneously feed current to a number of cells (for example: power, ground and clock lines). An example of "stacked" connection is explained in Sec.5.3.

#### 5.2 The format of user-entered geometry file

The pre-processor of the EM simulator reads the user-entered geometry file geometryfile that appears on the .EMSTAT card in the SPICE input deck. This file has a different format from the geometryfile produced by the extractor program. The format is such that user can easily enter and read the layout information in this file.

The format for capacitance, inductance, resistance, voltage and current (and other two-node) elements is:

#### element [ type {width length} | openings ] ...

type is one of MF, MS, MT, VI, CO which represents metal-one, metal-two, metal-three, via or contact. For interconnect, the user enters the width and length in  $\mu$ m. The number of contact or via openings is entered for contact and via (the area of the opening is taken to be the same as the area of contact/via opening entered in the Area= card for the test structure, see Sec. 3.6). There is no requirement on the order of appearance for the connection type (i.e. whether MF should be first, followed by VI and MS, etc.). But all information for one element must appear in one line only. For example, a capacitance element (labeled C10 in the SPICE deck) which has a first level metal connection  $4\mu$ m wide 100µm long connected to second level metal (2µm wide 20µm long) through via with 2 via openings can be specified as:

#### C10 MS 2.0 20.0 MF 4.0 100.0 VI 2.0

A single line with no type specified is treated by the simulator as a blank line, i.e. no failure statistics calculation will be performed for connection to this element. For example, simulator will ignore this line:

## C10

The format for transistor element and for subcircuit elements is:

element [ node nodenumber [ type {width length} | openings ] ... ]

type is one of MF, MS, MT, VI, CO which represents metal-one, metal-two, metal-three, via or contact. For interconnect, the user enters the width and length in  $\mu$ m. The number of contact or via openings is entered for contact and via (the area of the opening is taken to be the same as the

area of contact/via opening entered in the Area= card for the test structure, see Sec. 3.6). There is no requirement on the order of appearance for the connection type (i.e. whether MF should be first, followed by VI and MS, etc.). But all information for one element must appear in one line only. For example, a bipolar transistor (three terminal device) (labeled Q1 in the SPICE input deck) with the following metal connections:

- (1) Emitter (node number 1) contacting polysilicon,

- (2) Base (node number 2) has 1 contact opening to first level metal connection 2µm wide 5µm long.

- (3) Collector (node number 3) has 3 contact openings to first level metal connection 2.5μm wide 15μm long. The first level metal later connects to second level metal interconnect 5.0μm wide 100μm long through a via with 2 via openings

can entered in the geometry file as follows:

Q1 node 3 CO 3.0 MF 2.5 15.0 VI 2.0 MS 5.0 100.0 node 2 CO 1.0 MF 2.0 5.0 node 1

A node number not followed by the type, width and length or number of openings will be ignored by the pre-processor, as in last entry of the above example. The last node entry is redundant (but can be kept for better readability) and can be removed:

Q1 node 3 CO 3.0 MF 2.5 15.0 VI 2.0 MS 5.0 100.0 node 2 CO 1.0 MF 2.0 5.0

Comments can be inserted in the file but typing \* in the first column. For example:

\* This is a comment line

#### 5.3 "Stacked" metal connections

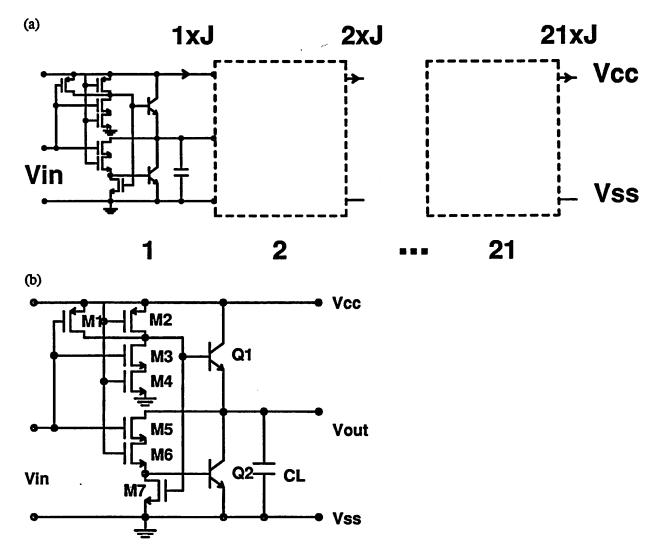

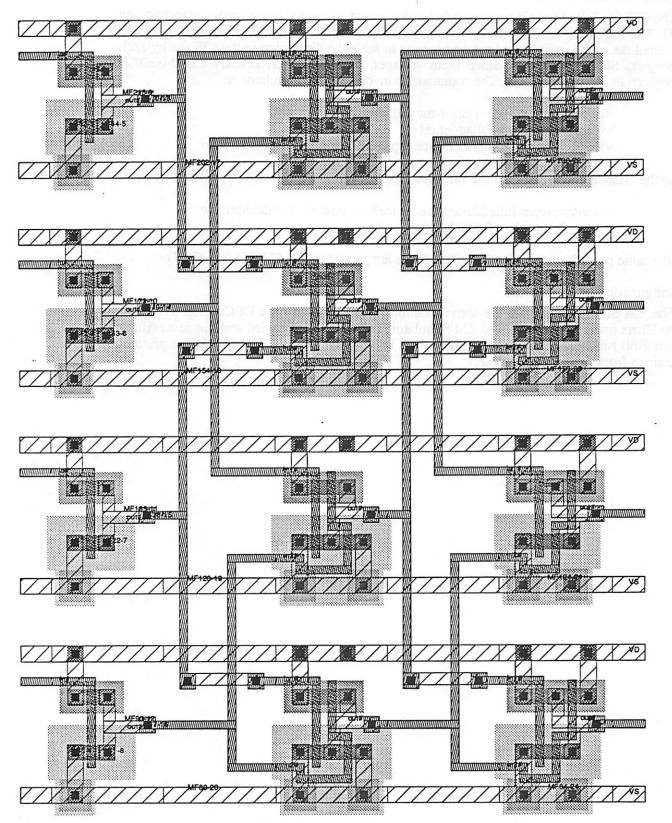

A "stacked" metal connection occurs when a power line (or signal line) successively connects to a number of identical cells (for example, see the 21-stage BiCMOS inverter chain in Fig. 3). The metal segments between two adjacent cells all have the same length and width. As a result, the average current density flowing in the metal segments "stacks" from the farthest cell (from the power or signal source) to the nearest cell. As noted earlier (in Sec.5.1), the user can set up subcircuit definition for the cell and repeat the subcircuits in the SPICE deck. But to account for the "stacked" connection, user have to set up a dummy resistor between two adjacent cells to attach geometry information. This can be quite troublesome if the number of cells is very large.

The simulator can be requested to treat "stacked" metal connection. The user can attach a suffix S after *type* followed by a "stacking" parameter *nSTACK* when entering the geometry information by hand. For example:

#### M1 node 2 MFS 21 10.0 30.0

is a "stacked" metal-one connection of 21 segments at node 2 of element M1. Each segment is 10  $\mu$ m wide 30.0  $\mu$ m long. In calculating the failure statistics, the simulator will sum the failure rate of first segment carrying current density J (from SPICE simulation), second segment carrying current density  $2 \times J$ , and so on, up to and including the *nStack*-th segment carrying current density *nStack*  $\times J$ .

# VI. Output from the Simulator

#### **6.1 Introduction**

The EM simulator can function in two modes: to provide layout guidelines or to predict failure rate or cumulative percent failure of a circuit. Both modes of operation can be requested simultaneously. In the first mode, it generates a layout advisory table listing maximum length allowed for each width of interconnect, the safety factor for number of contact and via openings given the reliability requirement. In the second mode, it calculates the electromigration failure rate and/or cumulative percent failure for each element in the circuit.

#### **6.2 Current Table**

Normally the current table is not printed, it is in the output if user request PrintCurrent in the rule file. It is printed in the first part of the output. The table lists average current and average absolute current (both in units of A) for each connection in the circuit. For some connections, where the average current  $< AC_DEFINE \times$  average absolute current, the simulator performs calculation assuming the current waveform is pure AC (by setting the internal average current to zero). Those connections are indicated by AC in the current table. It is a good idea to check this table to make sure that the assumptions for pure AC waveform are valid. This is particularly important for signal lines in MOS circuit where the gate current is supposed to be pure AC waveform. If a particular connection to a purely capacitive node is not indicated by AC in the output, the layout guideline and the failure rate calculated for this connection will be too pessimistic (assuming Aac > Adc in the rule file).

#### 6.3 Layout advisory tables

The second part of the output has two layout advisory tables. The first one is generated unless SKIPLAYOUTCUR is specified in the rule file. This table lists:

- (1) the maximum interconnect length L (in  $\mu$ m) for metal-one, metal-two or metal-three allowed for a given DC current (in A).

- (2) the safety factor S for contacts or vias (of different number of openings) for a given DC current (in A). If a number of less than 1.0 is printed, the number of contact/via openings carrying the given total DC current is not sufficient to guarantee the reliability spec and more contact/via openings are needed.

This table, although generated for a given DC current, can be used as a guideline for pulse DC current (if m in Eq.(1) is equal to 2). This is because for m=2 and under pulse DC current, the only current density dependence in Eq.(1) is J. Therefore, the designer can just read off the average current from the top of the table. For the case of pure AC current, if m is equal to 2, Eq.(1) will simplify to:

$$TTF = \frac{A_{AC}}{|J|^2}$$

or

$$=\frac{A_{\rm DC}}{\left[\sqrt{\frac{A_{\rm DC}}{A_{\rm AC}}}\,\overline{1J\,1}\right]^2}$$

To use the table for pure AC current waveforms, the current at the top of the table will have to be multiplied by  $\sqrt{\frac{A_{AC}}{A_{DC}}}$ . For example, Aac=1.0e20 and Adc=1.0e16, the table result for DC current of 0.1mA will be the same for AC current (the average of the absolute current) of 10.0mA.

The second layout advisory table gives a list of maximum interconnect length L (in  $\mu$ m) allowed and the safety factor S for contacts or vias (given the number of openings) in the circuit. The guideline is given for a number of specified widths of interconnects and number of openings of contacts and vias. The user can specified (by using NWIDTH and NCV in the rule file) widths of interconnects or the number of contact/via openings the simulator should consider.

The safety factor S for contacts and vias should be interpreted as follows: it is the maximum number of contacts/vias in a chain that is allowed along the path of the current flow. For example, if 3 is printed for 2 via openings, the number metal-to-metal vias in series (2 via openings in parallel at each terminal) along the current flow path can not exceed 3. A number of less than 1.0 for a particular number of contact/via openings indicates that the number of openings is not sufficient to guarantee the reliability spec.

If user enters the "stacked" parameter for a connection (See Sec.7.4), the guidelines generated are to be applied to one connection. (For example, the L printed for 21 "stacked" metal line segments should be the maximum length for one segment).

This table will not be printed if SKIPLAYOUTGEO is specified in the rule file. In this table, if the current density in a connection is smaller than *MinJCurrent* (specified using MINJCURRENT= in the rule file), the table entry is J < MinJ.

#### **6.4 Failure rate statistics**

The final part of the output contains the projected electromigration failure statistics of the design. This part is requested by EMSTAT (if user set up the geometry file by hand) or EMSTATX (if the geometry file comes from the layout extractor). In this table, the failure rate and/or cumulative percent failure for each connection are calculated at times specified in the EMSTAT or EMSTATX card. SKIPFAILPERCENT and/or SKIPFAILRATE can be specified in the rule file to instruct the simulator to skip either or both tables. The user can select to print out some of the worst connections by using the WorstList card in the rule file, otherwise all connections will be printed. The first column of the table is the name given by the simulator for the connection (useful for identifying trouble spots in CIF file) followed by the node connection in the SPICE input deck. At the bottom of the table the total failure rate/cumulative percent failure for the design is given. If EMSTATX is specified, the simulator will print out the location of of connections that pose electromigration hazards in CIF format. The listing consists of the connection names in descending order of failure rates and the ranking is attached to the name separated by a dash. User can then cut out the CIF format output and superimpose the names on the original CIF layout file for printout.

# VII. Examples of Simulation

#### 7.1 Introduction

In this section, we will demonstrate the operation of the EM simulator in four examples:

- (1) To design a CMOS EPROM sense amplifier circuit using the layout guideline from the simulator and make an estimation of the failure rate for the 512K × 8 EPROM.

- (2) To assess the failure rate of a 21-stage BiCMOS inverter chain. The layout information in entered by hand. The use of subcircuits to represent each inverter cell and "stacked" connection for the power supply line is demonstrated.

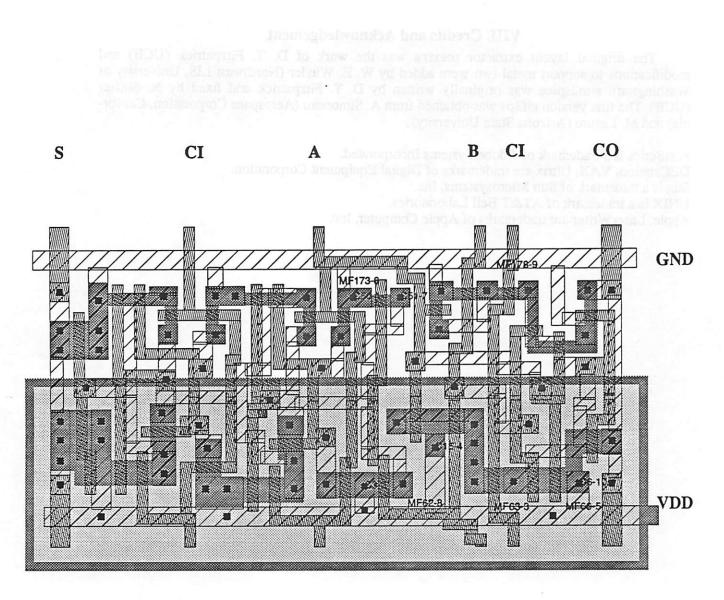

- (3) To project the reliability of a CMOS logic circuit designed using arrays of inverter, NOR and NAND gates. The SPICE input deck is extracted from the CIF layout file.

- (4) To project the reliability of a CMOS fulladder circuit. The SPICE input deck is extracted from the CIF layout file.

The SPICE input decks and CIF layout files are found in BERT/EM/examples in the distribution tape.

## 7.2 The design rule and reliability parameters

The EM design rule file for all the examples described below is **emrule**. The line: .EMMODEL emrule

is inserted in the SPICE input deck. The listing of *emrule* is given below:

\* Reliability parameters for electromigration simulator **PrintCurrent** ncurrent=3 1.00e-4 1.00e-3 5.00e-3 SkipFailpercent WorstList=0.5 AC define=0.2 MinJcurrent=1e2 \* this is the reliability specifications nwidth=4 1.0 2.0 4.0 10.0 ncv=3 1.0 2.0 4.0 \* The following set for metal-one interconnect metal1 length=4.5e+4 width=1.0 thick=0.5 Tdata=200.0 Ea=0.5 width a=6.25 width b=1.0 width c=40.0m=2.0 Adc=7.52e+12 Aac=7.52e+16 Lognormal logsigma=1.0 logmedian=7.52 \* The following set for metal-one to silicon contact contact area=1.0 Nchain=10.0 Tdata=200.0 Ea=0.5 m=2.0 Adc=1.0e+13 Aac=9.0e+14 Lognormal logsigma=1.0 logmedian=7.52 spec time=1.0e+4 spec failrate=1.0e-9

In the example, a listing of current in each connection is requested. For the layout advisory part, the simulator is instructed to generate guidelines for four interconnect widths:  $1\mu m$ ,  $2\mu m$ ,  $4\mu m$  and  $10\mu m$ , and three contact and via openings: 1, 2 and 4. It is also requested that layout guidelines are generated for three current values: 0.1 mA, 1.0 mA and 5.0 mA. Simulator will ignore any connections with current density less than 1e2 A/cm<sup>2</sup>. Pure AC waveform is defined if the

average current is less than 20% of the average absolute current. The width dependence is extracted from the example in Appendix B. The metal-one line used in electromigration lifetime experiment is 4.5 cm long, 2  $\mu$ m wide and 0.5  $\mu$ m thick.  $A_{DC}$ ,  $A_{AC}$  and *m* are obtained from accelerated testing at 200°C. Lognormal failure distribution is to be used. For example,  $\sigma = 1.0$  and MTF = 7.52 hours (using  $A_{DC}=7.52\times10^{12}$ , the DC stress current is 10<sup>6</sup> A/cm<sup>2</sup> at 200°C in the experiment). The contact chain structure used in the experiment has ten 1 $\mu$ m<sup>2</sup> contact openings in series. Finally, the reliability requirement for the circuit is failure rate of 1 FIT (10<sup>-9</sup> failure / device hour) at 10<sup>4</sup> hours (1.1 year).

The parameters for metal-two, metal-three and metal-to-metal vias are not given. The simulator will not perform analysis for these structures.

## 7.3 CMOS EPROM sense amplifier

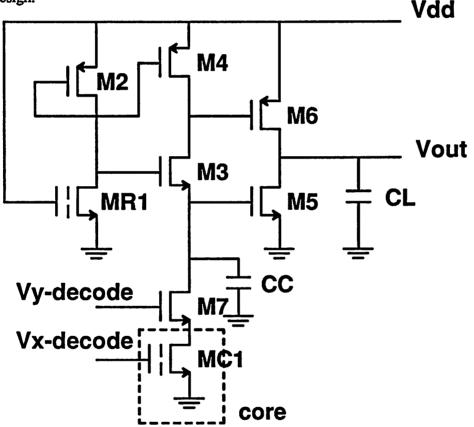

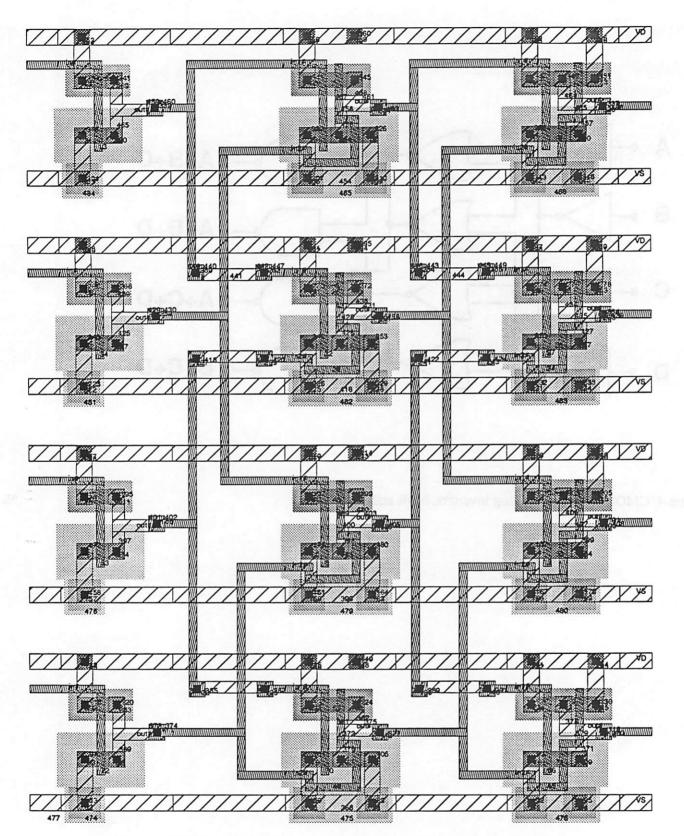

In this example, the designer wishes to generate a layout guideline for a CMOS EPROM sense amplifier circuit (see Fig.2) and later estimate the electromigration reliability of a 512K×8 EPROM design.

Figure 2. EPROM sense amplifier

The SPICE input deck (in file eprom) is set up as follows:

## CMOS EPROM SENSE AMPLIFIER

VDD 5 0 DC 5 VX 6 0 DC 0 PWL(0 0 5NS 5 55NS 5 60NS 0 150NS 0 155NS 5 205NS 5 + 210NS 0 300NS 0) VY 7 0 DC 0 PWL(0 0 5NS 5 55NS 5 60NS 0 150NS 0 155NS 5 205NS 5 + 210NS 0 300NS 0)

```

MR12500 EPROM L=2U W=3U

+ AD=20P AS=20P PD=14U PS=14U NRD=1.25 NRS=1.25

M2 2 2 5 5 MODP L=2U W=11U

+ AD=60P AD=60P PD=22U PS=22U NRD=0.42 NRS=0.42

M3 3 2 1 0 MODN L=2U W=39U

+ AD=200P AD=200P PD=50U PS=50U NRD=0.13 NRS=0.13

M4 3 2 5 5 MODP L=2U W=7U

+ AD=40P AD=40P PD=18U PS=18U NRD=0.63 NRS=0.63

M5 4 1 0 0 MODN L=2U W=49U

+ AD=250P AD=250P PD=60U PS=60U NRD=0.1 NRS=0.1

M6 4 3 5 5 MODP L=2U W=11U

+ AD=60P AD=60P PD=22U PS=22U NRD=0.42 NRS=0.42

M7 1 7 8 0 MODN L=2U W=49U

+ AD=250P AD=250P PD=60U PS=60U NRD=0.1 NRS=0.1

MC1 8 6 0 0 EPROM L=2U W=3U

+ AD=20P AS=20P PD=14U PS=14U NRD=1.25 NRS=1.25

```

CC 1 0 2P CL 4 0 0.3P

.MODEL MODN NMOS (LEVEL=2 VTO=0.9 KP=36U GAMMA=0.16 PHI=0.58 LAMBDA=0.04

+ CGSO=2.3E-10 CGDO=2.3E-10 CGBO=1.0E-10 RSH=30 CJ=1E-4 CJSW=3E-10

+ JS=3E-9 TOX=300E-10 NSUB=1E15 NFS=2E10 XJ=0.3E-6 LD=0.2E-6 UO=310

+ VMAX=6E4)

.MODEL MODP PMOS (LEVEL=2 VTO=-0.9 KP=17U GAMMA=0.27 PHI=0.63 LAMBDA=0.06 + CGSO=3.4E-10 CGDO=3.4E-10 CGBO=1.0E-10 RSH=120 CJ=1.7E-4 CJSW=6.7E-10 + JS=1E-9 TOX=300E-10 NSUB=3E15 NFS=2E10 XJ=0.4E-6 LD=0.4E-6 UO=150

+ VMAX=8E4)

#### .MODEL EPROM NMOS (LEVEL=2 VTO=2.0 KP=14U GAMMA=0.16 PHI=0.58 LAMBDA=0.04 + CGSO=2.3E-10 CGDO=2.3E-10 CGBO=1.0E-10 RSH=30 CJ=1E-4 CJSW=3E-10

- + JS=3E-9 TOX=300E-10 NSUB=1E15 NFS=2E10 XJ=0.3E-6 LD=0.2E-6 UO=310

- + VMAX=6E4)

.EMModel emrule .WIDTH OUT=80 .TRAN 1NS 300NS 150NS .OPTIONS NODE METHOD=GEAR VNTOL=0.001 ABSTOL=1.0E-8 .PLOT TRAN V(4) V(1) V(3) V(6) (0,5) .END

We have set up the input voltages and transient analysis card such that SPICE will simulate the circuit for two read cycle (each read cycle is 150 ns). Keep in mind that in the actual read cycle of the EPROM, only one out of many cells will be accessed. Since only layout guidelines are desired, we omit the **.EMSTAT** card in the SPICE deck. The command to call the simulator (using SPICE2G6) is:

vivante>prebert -2 eprom | spice2g6 | postbert > eprom.em

or using the "standalone" version of the EM simulator which saves the SPICE output:

vivante>preem eprom | spice2g6 > eprom.spcout vivante>postem -S2 -G eprom.geo -R emrule eprom.spcout > eprom.em

| <current table=""> Connection</current> | Avg Current(A)       | Avg Abs Cur(A) |    |

|-----------------------------------------|----------------------|----------------|----|

| VDD to 5                                | 2.56e-04             | 2.56e-04       |    |

| MR1 to 2                                | 1.12e-04             | 1.12e-04       |    |

| MR1 to 5                                | 1.49e-10             | 2.22e-09       | AC |

| MR1 to 0                                | 1.12e-04             | 1.12e-04       |    |

| M2 to 2                                 | 1.11e-04             | 1.11e-04       |    |

| M2 to 2                                 | 2.98e-09             | 4.47e-08       | AC |

| M2 to 5                                 | 1.11e-04             | 1.11e-04       |    |

| M5 to 4                                 | 1.09e-04             | 1.09e-04       |    |

| M5 to 1                                 | 4.80e-07             | 2.29e-06       |    |

| M5 to 0                                 | 1.09e-04             | 1.10e-04       |    |

| M6 to 4                                 | 1.07e-04             | 1.07e-04       |    |

| M6 to 3                                 | 3.48e-07             | 1.12e-06       |    |

| M6 to 5                                 | 1.06e-04             | 1.06e-04       |    |

| M7 to 1                                 | 2.98e-05             | 3.64e-05       |    |

| M7 to 7                                 | 2.19e-06             | 2.38e-05       | AC |

| M7 to 8                                 | 2.98e-05             | 3.03e-05       |    |

| MC1 to 8                                | 2.98e-05             | 3.03e-05       |    |

| MC1 to 6                                | 2.988-05<br>9.04e-08 | 1.72e-06       | AC |

| MC1 to 0                                | 2.98e-05             | 3.02e-05       |    |

A partial listing of the current table in eprom.em is given below:

The simulator indicates that the current in gate of MR1, gate of M2, gate of M7 and gate of MC1 is treated as pure AC current. But, note that this is not the case for the current in gate of M5 and gate of M6. SPICE simulation covering more cycles might thus be needed to obtain steady state current waveforms or AC Define can be set at a higher value.

The first layout advisory table gives the maximum allowable length for interconnect, and the safety factor for contacts and vias as a function of current:

| <layout advisory="" current="" for="" table=""><br/>Maximum Interconnect Length (in micron) or Safety Factor for Contacts or Vias t<br/>guarantee 1.00e-09(/h) failure rate at time 1.00e+04(h) for given Current(A)</layout> |         |         |         |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|--|--|

| DC Current(mA)                                                                                                                                                                                                                | 1.0e-04 | 1.0e-03 | 5.0e-03 |  |  |

| M1 W = 1.0                                                                                                                                                                                                                    | 2.2e+13 | 2.0e+02 | 5.6e-01 |  |  |

| M1 W = 2.0                                                                                                                                                                                                                    | 9.4e+20 | 8.9e+05 | 8.0e+00 |  |  |

| M1 W = 4.0                                                                                                                                                                                                                    | 1.9e+35 | 2.5e+14 | 1.9e+05 |  |  |

| M1 W = 10.0                                                                                                                                                                                                                   | 1.9e+60 | 3.8e+31 | 9.6e+16 |  |  |

| No.of CONT=1.0                                                                                                                                                                                                                | 9.5e+15 | 3.9e+01 | 9.7e-04 |  |  |

| No.of CONT=2.0                                                                                                                                                                                                                | 1.3e+22 | 9.0e+04 | 2.7e-02 |  |  |

| No.of CONT=4.0                                                                                                                                                                                                                | 1.2e+29 | 1.4e+09 | 4.9e+00 |  |  |

For example, the maximum length allowed for  $2\mu m$  wide metal-one interconnect carrying 5 mA current is  $8\mu m$  long. And the safety factor for 4 contact openings is 4.9 if 5 mA of current flows through the contact (each contact opening carries 1.25 mA).

The second table gives layout guideline for every connection in the circuit. The following is a partial listing (the least constraining guidelines have been omitted):

<Layout Advisory Table for all connections>

Maximum Interconnect Length (in micron) or Safety Factor for Contacts or Vias to guarantee 1.00e-09(/h) failure rate at time 1.00e+04(h) in each connection

| Metal: (Width) | Туре | 1.0e+00                                                                                                                 | 2.0e+00<br>2.0e+00                                                                      | 4.0e+00<br>4.0e+00                                      | 1.0e+01                 |

|----------------|------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------|

| Cont/Via:(#)   | Туре | 1.0e+00                                                                                                                 | 2.00+00                                                                                 | 4.00100                                                 |                         |

| VDD to 5       | MF   | 5.4e+07                                                                                                                 | 5.4e+13                                                                                 | 4.5e+25                                                 | 4.5e+30                 |

| VDD to 5       | CO   | 1.0e+09                                                                                                                 | 1.0e+14                                                                                 | 7.0e+19                                                 |                         |

| MR1 to 2       | MF   | 3.9e+12                                                                                                                 | 1.1e+20                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| MR1 to 2       | CO   | 1.2e+15                                                                                                                 | 1.2e+21                                                                                 | 1.0e+27                                                 |                         |

| MR1 to 5       | MF   | J <minj< td=""><td>J <minj< td=""><td>J <minj< td=""><td>J <minj< td=""></minj<></td></minj<></td></minj<></td></minj<> | J <minj< td=""><td>J <minj< td=""><td>J <minj< td=""></minj<></td></minj<></td></minj<> | J <minj< td=""><td>J <minj< td=""></minj<></td></minj<> | J <minj< td=""></minj<> |

| MR1 to 5       | CO   | J <minj< td=""><td>J <minj< td=""><td>J <minj< td=""><td></td></minj<></td></minj<></td></minj<>                        | J <minj< td=""><td>J <minj< td=""><td></td></minj<></td></minj<>                        | J <minj< td=""><td></td></minj<>                        |                         |

| MR1 to 0       | MF   | 3.9e+12                                                                                                                 | 1.1e+20                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| MR1 to 0       | CO   | 1.2e+15                                                                                                                 | 1.2e+21                                                                                 | 1.0e+27                                                 |                         |

| M2 to 2        | MF   | 4.2e+12                                                                                                                 | 1.1e+20                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| M2 to 2        | CO   | 1.2e+15                                                                                                                 | 1.3e+21                                                                                 | 1.0e+27                                                 |                         |

| M2 to 2        | MF   | J <minj< td=""><td>J <minj< td=""><td>J <minj< td=""><td>J <minj< td=""></minj<></td></minj<></td></minj<></td></minj<> | J <minj< td=""><td>J <minj< td=""><td>J <minj< td=""></minj<></td></minj<></td></minj<> | J <minj< td=""><td>J <minj< td=""></minj<></td></minj<> | J <minj< td=""></minj<> |

| M2 to 2        | CO   | J <minj< td=""><td>J <minj< td=""><td>J <minj< td=""><td></td></minj<></td></minj<></td></minj<>                        | J <minj< td=""><td>J <minj< td=""><td></td></minj<></td></minj<>                        | J <minj< td=""><td></td></minj<>                        |                         |

| M2 to 5        | MF   | 4.2e+12                                                                                                                 | 1.1e+20                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| M2 to 5        | CO   | 1.2e+15                                                                                                                 | 1.3e+21                                                                                 | 1.0e+27                                                 |                         |

| M5 to 4        | MF   | 6.1e+12                                                                                                                 | 1.9e+20                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| M5 to 4        | CO   | 2.0e+15                                                                                                                 | 2.2e+21                                                                                 | 1.0e+27                                                 |                         |

| M5 to 1        | MF   | 4.5e+30                                                                                                                 | 4.5e+30                                                                                 | 4.5e+30                                                 | J <minj< td=""></minj<> |

| M5 to 1        | CO   | 1.0e+27                                                                                                                 | 1.0e+27                                                                                 | J <minj< td=""><td></td></minj<>                        |                         |

| M5 to 0        | MF   | 5.4e+12                                                                                                                 | 1.6e+20                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| M5 to 0        | CO   | 1.7e+15                                                                                                                 | 1.8e+21                                                                                 | 1.0e+27                                                 |                         |

| M6 to 4        | MF   | 8.2e+12                                                                                                                 | 2.7e+20                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| M6 to 4        | CO   | 2.8e+15                                                                                                                 | 3.2e+21                                                                                 | 1.0e+27                                                 |                         |

| M6 to 3        | MF   | 4.5e+30                                                                                                                 | 4.5e+30                                                                                 | J <minj< td=""><td>J <minj< td=""></minj<></td></minj<> | J <minj< td=""></minj<> |

| M6 to 3        | CO   | 1.0e+27                                                                                                                 | J <minj< td=""><td>J <minj< td=""><td></td></minj<></td></minj<>                        | J <minj< td=""><td></td></minj<>                        |                         |

| M6 to 5        | MF   | 8.6e+12                                                                                                                 | 2.8e+20                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| M6 to 5        | CO   | 3.0e+15                                                                                                                 | 3.4e+21                                                                                 | 1.0e+27                                                 |                         |

| M7 to 1        | MF   | 9.1e+21                                                                                                                 | 4.5e+30                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| M7 to 1        | CO   | 1.6e+26                                                                                                                 | 1.0e+27                                                                                 | 1.0e+27                                                 |                         |

| M7 to 7        | MF   | 4.5e+30                                                                                                                 | 4.5e+30                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| M7 to 7        | CO   | 1.0e+27                                                                                                                 | 1.0e+27                                                                                 | 1.0e+27                                                 |                         |

| M7 to 8        | MF   | 5.8e+22                                                                                                                 | 4.5e+30                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| M7 to 8        | CO   | 1.0e+27                                                                                                                 | 1.0e+27                                                                                 | 1.0e+27                                                 |                         |

| MC1 to 8       | MF   | 5.8e+22                                                                                                                 | 4.5e+30                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| MC1 to 8       | CO   | 1.0e+27                                                                                                                 | 1.0e+27                                                                                 | 1.0e+27                                                 |                         |

| MC1 to 6       | MF   | 4.5e+30                                                                                                                 | 4.5e+30                                                                                 | J <minj< td=""><td>J <minj< td=""></minj<></td></minj<> | J <minj< td=""></minj<> |

| MC1 to 6       | CO   | 1.0e+27                                                                                                                 | J <minj< td=""><td>J <minj< td=""><td></td></minj<></td></minj<>                        | J <minj< td=""><td></td></minj<>                        |                         |

| MC1 to 0       | MF   | 6.2e+22                                                                                                                 | 4.5e+30                                                                                 | 4.5e+30                                                 | 4.5e+30                 |

| MC1 to 0 | CO | 1.0e+27 | 1.0e+27 | 1.0e+27 |

|----------|----|---------|---------|---------|

|          |    |         |         |         |

As pointed out earlier, because the gate current in M5 and M6 from SPICE output is not pure AC, the guideline calculated for the gate of M5 (M5 to 1) and gate of M6 (M6 to 3) is too pessimistic.

From the table above, the designer can layout the circuit and also estimate the failure rate of the layout using the table. The interconnect failure rate for the design at  $10^4$  hours is:

Designed FIT =

$$\frac{\text{Layout Length}}{L} \times 1 \text{ FIT}$$

where L is maximum length allowed from the layout advisory table. 1 FIT is used on the R.H.S. of the equation because the layout guidelines are generated for the spec of 1 FIT at  $10^4$  hours. The contact/via failure rate for the design is:

Designed FIT =

$$\frac{1}{S} \times 1$$

FIT

where S is the the safety factor from the layout advisory table.

We will calculate the failure rate at  $10^4$  hours of a 512K× 8 EPROM assuming the worst case scenario: the same 8 EPROM bits located furthest away from the sense amplifier are continuously accessed in each read cycle. The geometry of interconnects and contacts in the chip are:

All the transistors in the sense amplifier circuit (total of 8 sense amplifier circuits) have 20µm and 1µm wide metal-one lines connected to their source and drain. Failure rate for these: