# Integrated Placement and Routing for VLSI Layout Synthesis and Optimization

# by Ping-San Tzeng

#### **Abstract**

This dissertation investigates ways to integrate various VLSI layout algorithms via carefully designed integrated data structures. Such an integrated approach can achieve better overall results by iterating non-sequentially among the various algorithms in a demand-driven manner. The shared data structure which is modified incrementally by all the different algorithms serves as an efficient communication medium between them. This approach has resulted in several new prototype tools, including a new placement program that combines wire-length optimization with a new 2-D compaction algorithm, a new area-routing approach that employs hierarchical rip-up and reroute techniques in an integrated global and detailed routing environment, and also a system that integrates the area router with a placement adjustment algorithm. This integrated system can iterate automatically between area routing and placement adjustment phases to generate optimized results for macro-cell problems with over-the-cell routing.

| · |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

| , |  |  |  |

# Acknowledgements

I would like to thank my advisor, Prof. Carlo H. Séquin, for his constant support, guidance and inspiration. He not only gave me many technical advices, he also carefully reviewed this manuscript several times and helped me to improve the writing of this dissertation. Also, I would like to thank Prof. Richard Newton and Prof. David Donoho for reviewing this dissertation and giving me many useful comments. I am also indebted to Glenn Adams, Dr. Ren-Song Tsay, Dr. Han-Young Koh, and Naoto Ichihara, for many enlightening discussions and suggestions.

I am gratefully to Semiconductor Research Corporation for their support of this research project. I would also like to thank Cadence Design Systems, Inc. for giving me the opportunity to use their compactor to generate some of the final results.

Finally, I would like to thank my wife Yu-Ling, my father Po and my mother Shao-Shao for their support in my long graduate study. I dedicate this dissertation to them.

|   | , |  |

|---|---|--|

|   |   |  |

| • |   |  |

# **Table of Contents**

| Table of Contents                                           | iii |

|-------------------------------------------------------------|-----|

| List of Figures                                             | V   |

| List of Tables                                              | vii |

| Chapter 1 Introduction                                      | 1   |

| 1.1 The Placement and Routing Problem                       |     |

| 1.2 Dissertation Overview                                   |     |

|                                                             | 5   |

| Chapter 2 Placement Using Efficient 2-D Compaction          |     |

| 2.1 Placement Paradigm for Resolving Overlaps               |     |

| 2.2 Data Structure                                          |     |

| 2.2.1 Definitions                                           |     |

| 2.2.2 Building the RULD-Graph                               |     |

| 2.2.2.1 Building the Triangulation Graph                    |     |

| 2.2.2.2 Edge-direction Assignment                           |     |

| 2.2.3 Linear Constraints from RULD-graph                    |     |

| 2.2.4 Interpretations and Discussions                       |     |

| 2.3 Compaction Algorithms                                   |     |

| 2.3.1 1-D Compaction Algorithm                              |     |

| 2.3.2 2-D Compaction Algorithm                              |     |

| 2.3.2.1 An Alternative Control Strategy                     |     |

| 2.3.3 Evaluation of the Compaction Algorithm                |     |

| 2.4 Wire-Length Optimization Algorithms                     |     |

| 2.4.1 Simple Quadratic Formulation                          | 27  |

| 2.4.2 Quadratic Formulation using Exact Pin Positions       |     |

| 2.4.2.1 Cell-Shifting Algorithm                             | 30  |

| 2.4.2.2 Cell-Orienting Algorithm                            | 30  |

| 2.4.3 Half-perimeter Formulation                            | 33  |

| 2.5 Overall Placement Algorithm                             | 33  |

| 2.5.1 Initial Placement Phase                               | 33  |

| 2.5.2 First Refinement Phase - Quadratic Optimization       | 34  |

| 2.5.3 Second Refinement Phase - Half-perimeter Optimization |     |

| 2.5.4 Evaluation of the Optimization Phases                 | 36  |

| 2.6 Results                                                 | 37  |

| 2.7 Summary                                                 |     |

| Chapter 3 Area Routing with Hierarchical Rip-up and Reroute | 41  |

| 3.1 The Area Routing Problem                                |     |

| 3.2 Routing Hierarchy and Data Structure                    |     |

| 3.2.1 The Wiring Model                                      |     |

| 3.2.2 Partitioning Scheme                                   |     |

|                                                             |     |

| 3.2.3 Data Structure                                    | 18 |

|---------------------------------------------------------|----|

| 3.3 Routing Algorithms                                  |    |

| 3.3.1 Global Construction Algorithm                     |    |

| 3.3.2 Global Rerouting Algorithm                        |    |

| 3.3.3 Detailed Rerouting Algorithm                      |    |

| 3.3.4 Control Strategy and Congestion Data Structure    |    |

| 3.4 Results                                             |    |

| 3.5 Summary                                             |    |

| Chapter 4 Integrated Placement and Routing              | 66 |

| 4.1 Routing and Placement Adjustment                    | 66 |

| 4.2 Basic Idea                                          |    |

| 4.3 Area Routing                                        |    |

| 4.4 Placement Adjustment                                |    |

| 4.4.1 From Congestion to Space Requirement              |    |

| 4.4.2 Moving Cells.                                     |    |

| 4.4.2.1 Moving Wires                                    |    |

| 4.4.2.2 Stretching and Shrinking Wires                  |    |

| 4.5 Overall Algorithm.                                  |    |

| 4.6 Results                                             |    |

| 4.6.1 Comparison with Fixed Placement and Compaction    | 80 |

| 4.6.2 Macro-cell problems with Over-the-Cell Routing    |    |

| 4.6.3 Channel-based Macro-cell Problems                 |    |

| 4.7 Summary                                             | 88 |

| Chapter 5 Discussions and Conclusions                   | 89 |

| 5.1 Integrated Data Structure                           | 89 |

| 5.2 Iterative Optimization Using Cooperative Algorithms |    |

| 5.3 Conclusion                                          |    |

| References                                              | 93 |

|                                                         | -  |

# **List of Figures**

| Chapter | r 1 Introduction                                                            |    |

|---------|-----------------------------------------------------------------------------|----|

| 1.1     | Examples of row-based design styles                                         |    |

| 1.2     | Problems of using row structure in macro-cell designs                       | 3  |

| Chapter | 2 Placement Using Efficient 2-D Compaction                                  |    |

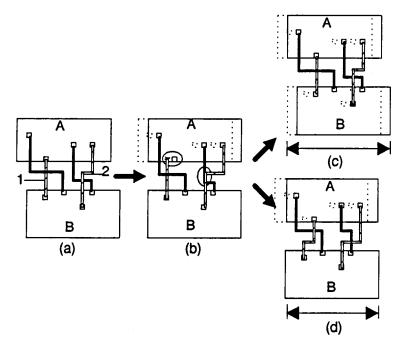

| 2.1     | Problems of using traditional 1-D compaction in placement                   | 7  |

| 2.2     | The Basic idea of using a compactor/spacer in placement                     |    |

| 2.3     | Triangulation graphs and edge-swapping operations                           |    |

| 2.4     | A legal RULD-graph and an illegal node                                      | 9  |

| 2.5     | The cut-paths in RULD-graph                                                 | 10 |

| 2.6     | A desired triangulation graph versus the Delaunay triangulation             | 10 |

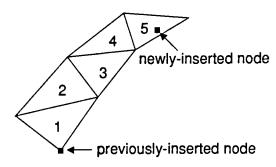

| 2.7     | A possible search sequence in finding the enclosing triangle on inserting a |    |

|         | new node                                                                    | 13 |

| 2.8     | Two ordering schemes in traversing a 2-D binary tree                        | 13 |

| 2.9     | The criterion for deciding the direction of edges in a RULD-graph           | 14 |

| 2.10    | Legalizing nodes in a RULD-graph                                            | 15 |

| 2.11    | The explicit constraints in a RULD-graph                                    | 16 |

| 2.12    | The three situations in Theorem 1                                           |    |

| 2.13    | Replacing the cut-path in Theorem 1                                         | 18 |

| 2.14    | Comparing a RULD-graph with a constraint graph                              | 18 |

| 2.15    | Comparing a RULD-graph with a rectangular-dual                              | 19 |

| 2.16    | Transforming projection constraints to spacing constraints                  | 20 |

| 2.17    | Changing a horizontal edge to a vertical edge in horizontal compaction      | 20 |

| 2.18    | Changing a vertical edge to horizontal edge during horizontal compaction    | 21 |

| 2.19    | Comparison of results from various compaction methods                       | 25 |

| 2.20    | The time-complexity analysis of 2-D compaction algorithms                   | 26 |

| 2.21    | The potential moves of a pin in the four orientation-change operations      | 31 |

| 2.22    | The changes of the wiring costs during two placement processes              | 36 |

| 2.23    | The placement result of the macro-cell benchmark AMI33                      | 38 |

| Chapter | 3 Area Routing with Hierarchical Rip-up and Reroute                         |    |

| 3.1     | The complexity of searching for a feasible rerouting sequence               | 42 |

| 3.2     | Comparison of gridless routing and grid-based routing                       | 44 |

| 3.3     | Four-way partitioning and two-way partitioning                              |    |

| 3.4     | The recursive partitioning scheme                                           |    |

| 3.5     | The two different methods in selecting the cuts in partitioning             | 47 |

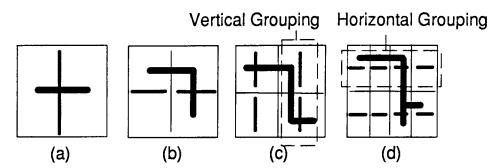

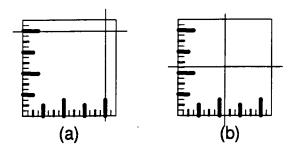

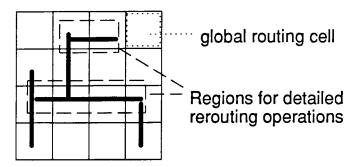

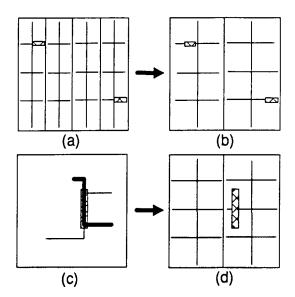

| 3.6     | Dynamic grouping for the detailed routing                                   |    |

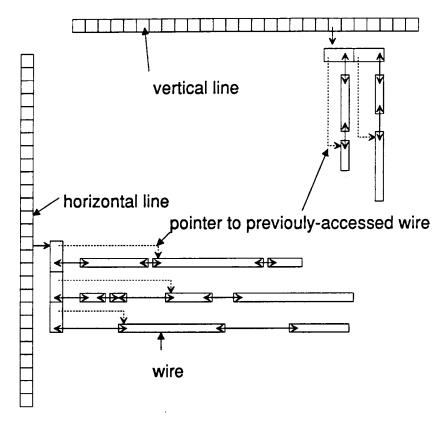

| 3.7     | The data structure for wires                                                |    |

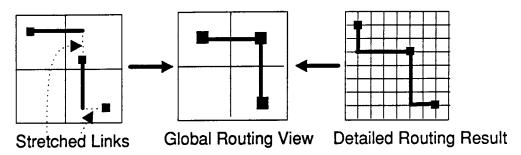

| 3.8     | The use of stretched links                                                  | 50 |

|         |                                                                             |    |

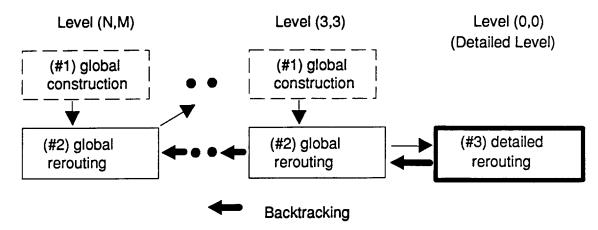

|    | 3.9    | The use of the three routing algorithms                                     | 51 |

|----|--------|-----------------------------------------------------------------------------|----|

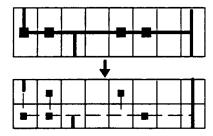

|    | 3.10   | Partitioning a horizontal $1 \times N$ strip into a $2 \times N$ strip      | 51 |

|    | 3.11   | The simple pattern router of the global construction algorithm              |    |

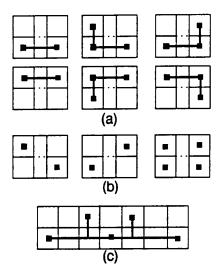

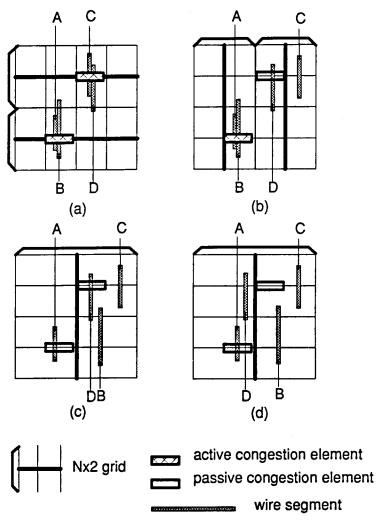

|    | 3.12   | The two basic rerouting operations in $2 \times N$ strips                   |    |

|    | 3.13   | The two rerouting primitives for detailed routing                           | 55 |

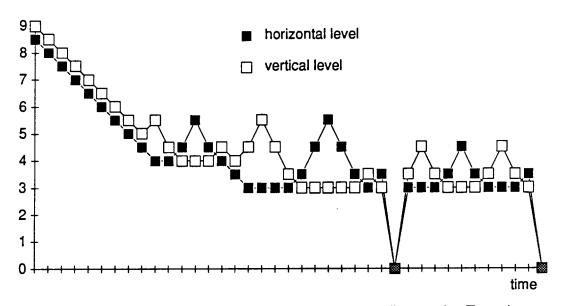

|    | 3.14   | The changes of the levels in routing a macro-cell example                   |    |

|    | 3.15   | Examples of the congestion elements                                         | 59 |

|    | 3.16   | The use of congestion elements in backtracking                              | 61 |

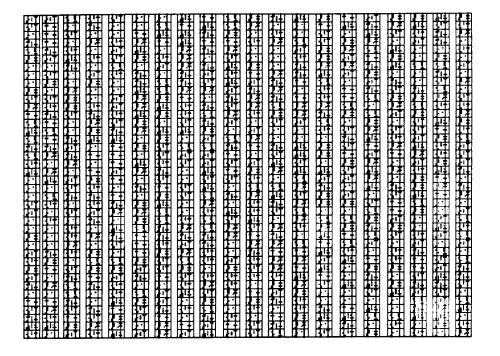

|    | 3.17   | An area routing example                                                     | 64 |

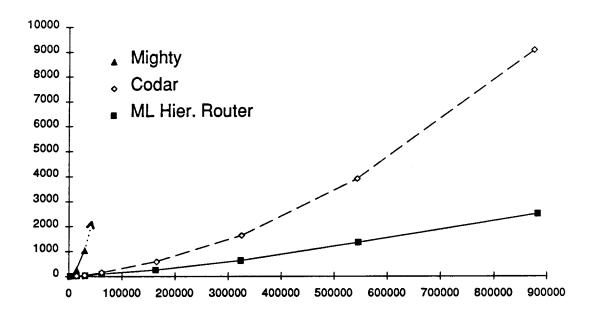

|    | 3.18   | The CPU-time v.s. the wire length for area routing problems                 | 65 |

| Cł | napter | 4 Integrated Placement and Routing                                          |    |

|    | 4.1    | Some routing results may be difficult to compact                            | 67 |

|    | 4.2    | Two different types of edges in the $2 \times N$ routing frame              | 70 |

|    | 4.3    | The area covered by an edge of a RULD-graph                                 | 71 |

|    | 4.4    | Congestion that cannot be resolved by increasing the spacing by the maxi-   |    |

|    |        | mum overload count                                                          |    |

|    | 4.5    | The two approaches to reconnecting broken nets after moving cells           | 73 |

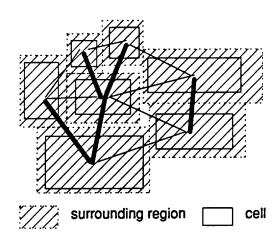

|    | 4.6    | The surrounding regions for the cells                                       | 75 |

|    | 4.7    | The use of the edge-covered region to fill the empty space                  | 76 |

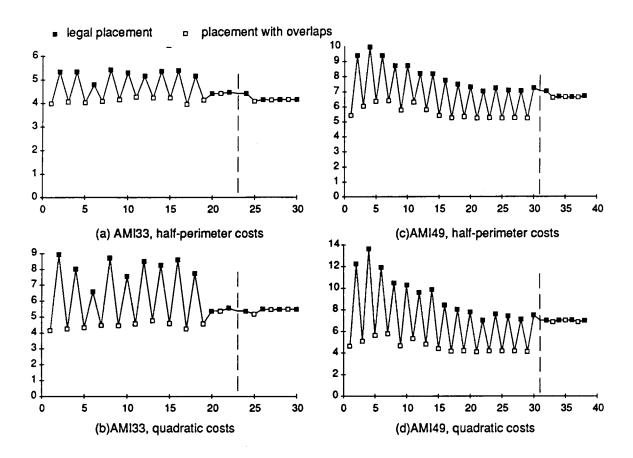

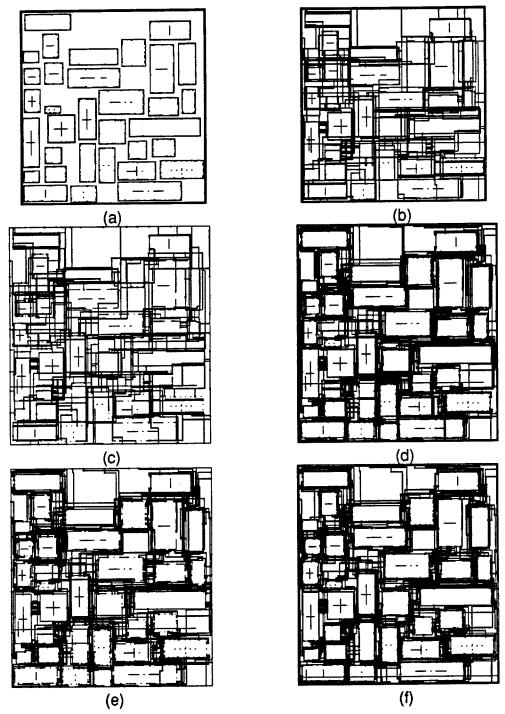

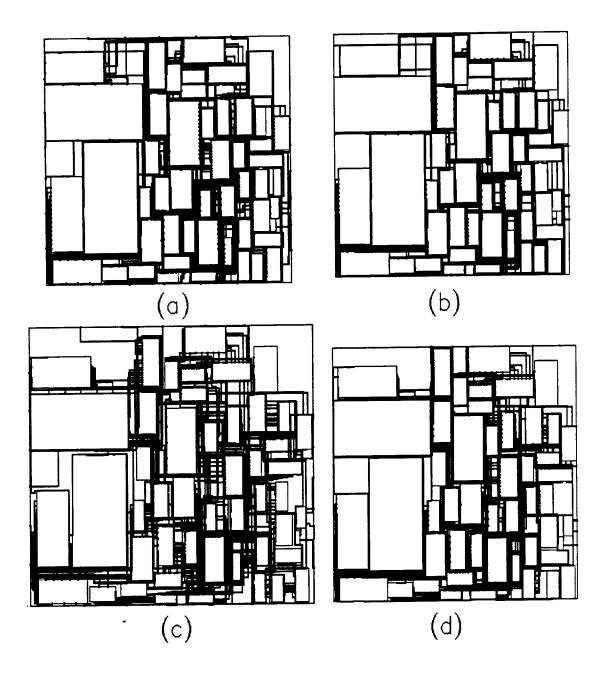

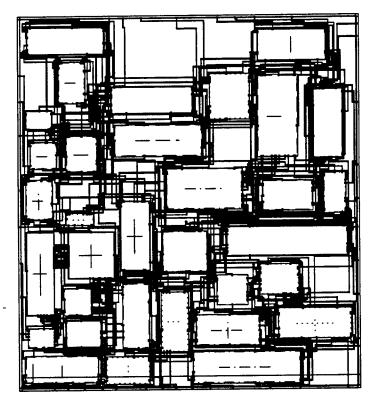

|    | 4.8    | The layouts in different stages of an actual placement and routing process. | 79 |

|    | 4.9    | Comparing the integrated placement and routing approach and the Place-      |    |

|    |        | Route-Compact approach on AMI33                                             | 82 |

|    | 4.10   | Comparing the integrated placement and routing approach and the Place-      |    |

|    |        | Route-Compact approach on AMI49                                             | 83 |

|    | 4.11   | An example of the randomly generated cells                                  | 84 |

|    | 4.12   | Results on AMI33otc with over-the-cell routing                              | 85 |

|    | 4.13   | Results on AMI49otc with over-the-cell routing                              |    |

|    | 4.14   | Resulting layout of AMI33                                                   | 87 |

|    |        |                                                                             |    |

# Chapter 5 Discussions and Conclusions

# **List of Tables**

| Chapter | 1 Introduction                                                                |

|---------|-------------------------------------------------------------------------------|

| Chapter | 2 Placement Using Efficient 2-D Compaction                                    |

| 2.1     | The number of the triangles tested when new nodes are inserted into a trian-  |

|         | gulation graph13                                                              |

| 2.2     | Comparison of two different compaction control strategies23                   |

| 2.3     | Comparison of the compaction results24                                        |

| 2.4     | Evaluation of the cell-orienting algorithm on initial placements of different |

|         | qualities32                                                                   |

| 2.5     | Placement results on MCNC macro-cell benchmarks                               |

| 2.6     | Placement results on MCNC standard-cell benchmarks                            |

| Chapter | 3 Area Routing with Hierarchical Rip-up and Reroute                           |

| 3.1     | Characteristics of the randomly generated area routing problems63             |

| 3.2     | Results on the randomly generated area-routing problems                       |

| Chapter | 4 Integrated Placement and Routing                                            |

| 4.1     | The effect of the placement adjustment algorithm on the number of stretched   |

|         | links and conflicts                                                           |

| 4.2     | Comparing the Place-Route-Compact approach and the integrated placement       |

|         | and routing approach81                                                        |

| 4.3     | Results of on macro-cell problems with over-the-cell routing84                |

| 4.4     | Results of on MCNC macro-cell benchmarks87                                    |

| 4.5     | Comparison of the results on MCNC macro-cell benchmarks                       |

| Chapter | 5 Discussions and Conclusions                                                 |

| • |  |  |

|---|--|--|

# Chapter 1 Introduction

# 1.1 The Placement and Routing Problem

Designing VLSI chips is a complex task comprising many steps, such as architecture/behavior design, logic design, physical design, and various verification steps. The task of physical design is to convert a circuit, usually consisting of a set of cells and a list of nets, into a layout that can be realized on a VLSI chip. In addition to cell design, the major task of physical design is to place all the cells and then route all the nets to connect the pins with proper wires and contacts. Normally, the goal of this placement and routing process is to generate realizable layouts in minimum area with minimum delay, which is related to the wire length.

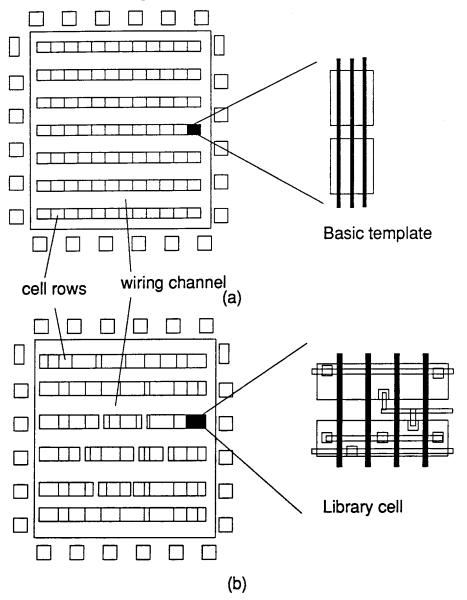

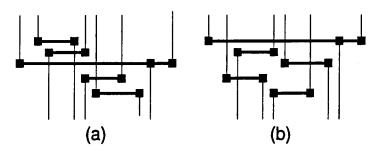

In principle, the placement and routing algorithms have to deal with two-dimensional objects in a two-dimensional space. Because true two-dimensional algorithms are normally quite complex, cells are usually organized into special structures such that the placement and routing problems can be reduced to pseudo-one-dimensional problems. The most common approach is to organize cells into parallel rows, as in *gate-array* and *standard-cell* designs (Fig. 1.1). With the row structure, the placement algorithms can compute legal positions for all the cells easily after moving cells around, optimizing the objective functions. In addition, the row structure partitions the routing region into independent routing channels, which can be routed with high efficiency [RF82] [RSVS85]. The combination of the row structure and the channel routing techniques have been very successful in carrying out the placement and routing task effectively.

#### 1.1 The Placement and Routing Problem

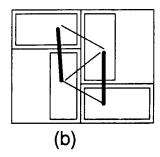

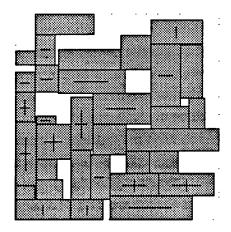

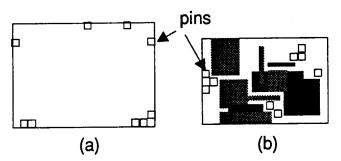

Fig. 1.1 (a) A possible structure of gate-array chips. In such a structure, a library cell may consist of one or several basic templates. (b) A possible cell placement of standard cell designs where the distance between rows can be adjusted based on actual wiring density.

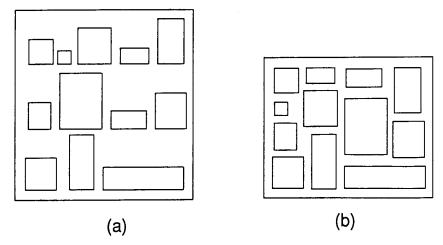

The combination of a row structure and of channel routing provides a satisfactory solution for many VLSI designs but it does not solve all the problems. In many cases, true 2-D placement and routing algorithms are required. First, many designs consist of complex logic functions such as ALUs, or of dense memory arrays, which have to be implemented with large macro-cells of varying sizes and aspect ratios. Usually, a lot of space is wasted when these macro-cells are forced into rows (Fig. 1.2).

Fig. 1.2 (a) Using row structure for macro-cells can cause a lot of wasted space. (b) Organize the cells in a true 2-D structure can generate a much smaller chip.

A true 2-D placement also requires true 2-D routing algorithms. The channel routing techniques are effective only when the routing region is divided into channels by cells that do not let wires pass through freely. As the manufacturing technology improves, more metal layers become available for routing, and wires at the higher layers can usually go freely over the cells. With these additional routing resources, the cells can be packed together closely and the router has to search for solutions in a true 2-D space instead of in the channels between cells. This kind of problem is usually referred to as over-the-cell routing or as the general area routing problem.

The *macro-cell placement* and *area routing* problems are difficult because of their 2-D nature. Even though some algorithms have been proposed for the macro-cell placement problem [SB87] [SS90] as well as the area routing problem [Shi87] [TS88], most algorithms have their drawbacks and cannot handle high-complexity VLSI designs efficiently and effectively. In addition to the issues arising when each problem is considered separately, an even more challenging problem is how to integrate the 2-D placement and routing algorithms so they can work together to generate optimized layouts. This interaction is necessary because the placement usually needs to be adjusted so proper space can be allocated between cells to accommodate all the wiring. In the row structure and channel routing scheme, the routing channels can be adjusted easily by moving whole rows vertically. However, in a true 2-D placement and routing problem, cells need to be moved in both horizontal and vertical directions. When there are no independent channels, these moves may render most of the routing results invalid and may require expensive rerouting processes. In most cases, a considerable amount of human intervention is required when the placement needs to be adjusted to complete the routing.

3

#### 1.2 Dissertation Overview

A possible approach to avoiding the expensive rerouting process and/or reducing the amount of human intervention is to use more precise congestion estimate to space cells before conducting the final routing. For gate-array or standard-cell problems, many hierarchical approaches have been proposed to integrate the placement and routing together [BHP83] [Sze86] [SK88] [KPS89] [Chr89]. These hierarchical approaches partition the problem recursively, conducting some form of global routing before proceeding to the next-level placement. With these global routing results, more precise wire-length and congestion estimates can be used to improve the placement and/or to space the cells. In addition to these top-down hierarchical approaches, a similar principle has also been employed in a bottom-up approach using a two-level hierarchy [SLS87]. However, all these hierarchical approaches work primarily on problems with large number (1000's to 100,000's) of small cells of about the same size. These partitioning approaches have not been very successful on macro-cell problems with less than a hundred cells of varying sizes.

In [IBSV89], a system integrating placement and area-routing is proposed to handle sea-of-gate layouts as problems with flexible, porous macro-cells. Using a simplified global router to estimate the routing requirement after the placement step, the system can adjust the placement to ease the routing task. Even though the system can iterate between the simplified global routing and the placement adjustment phases, the actual routing phase still works on a fixed placement. If the router fails due to some local congestion, there is still no automatic solution available.

#### 1.2 Dissertation Overview

Most of the "integrated" placement and routing approaches mentioned above mix placement and routing phases of different levels in a sequential process. The focus of this dissertation concerns the form of integration that iterates between the actual placement and routing tasks in an optimization loop. The primary application targets are the macro-cell problems with over-the-cell routing. The work includes new data structures and algorithms for both the macro-cell placement problem and for the general area routing problem. Based on these new data structures and algorithms, an integrated placement and routing scheme is developed to optimize the layout by iterating between the placement and routing processes.

This dissertation consists of five chapters. Chapter 2 presents the placement algorithm which relies on a *triangulation data structure* and on a 2-D compactor to resolve overlaps among cells while optimizing the objective function. Chapter 3 introduces the area router, which applies *rip-up and reroute* techniques *hierarchically* to complete the routing task efficiently. Chapter 4 then shows how the hierarchical router is integrated with a placement adjustment algorithm to complete the routing within a minimum amount of area. Chapter 5 presents some of the important lessons learned from this work.

# Chapter 2

# **Placement Using Efficient 2-D Compaction**

This chapter introduces a new placement algorithm that uses efficient 2-D compaction to resolve overlaps while optimizing the wire length. Section 2.1 first reviews previous approaches in resolving overlaps and then shows the basic idea of this new approach. Section 2.2 presents the definition and the construction algorithm of the new data structure, and Section 2.3 shows how the compaction algorithm works with this new data structure. Section 2.4 then introduces the wire length optimization algorithms that works with the compactor. Section 2.5 describes the overall placement algorithm, and Section 2.6 presents some placement results as well as a comparison with other placement tools.

# 2.1 Placement Paradigm for Resolving Overlaps

The objective of placement in VLSI layout synthesis is to place a given set of cells in a two-dimensional space such that a given net-list can be realized with minimum delay and area. Because it is difficult to minimize the delay and area directly, most placement programs try to optimize the wire length. By formulating the objective function as the sum of squared wire lengths, an optimal solution can be found very quickly with quadratic optimization techniques[TKH88]. However, the result is usually *illegal* because it has been obtained without considering overlapping blocks. To obtain a legal layout, additional constraints have to be introduced:

```

|x_i-x_j| \ge (sx_i+sx_j)/2 or |y_i-y_j| \ge (sy_i+sy_j)/2, for all i, j

where (x_iy_i) = \text{position of the center of cell } i

(sx_i,sy_i) = \text{size of cell } i

```

For N cells, there will be  $N^2$  constraints that are inherently *non-convex* functions, no matter how they are formulated. These non-convex constraints make it essentially impossible to find a global optimum in polynomial time, and various heuristics have been introduced to enforce these constraints. These heuristics for resolving overlaps usually are the critical element of any placement algorithm and strongly affect the overall performance.

Various approaches have been proposed to resolve overlaps while optimizing the objective function. Among them, there are two basic paradigms: (1) resolving overlaps gradually and (2) generating legal solutions repeatedly.

#### 2.1 Placement Paradigm for Resolving Overlaps

In the first paradigm, the placement algorithms work on *illegal placements* most of the time while *resolving overlaps gradually*. Only in the final stage of the placement, a legal solution can be generated. Based on this paradigm, a common approach is to formulate the no-overlap constraints as *penalty terms* in a new cost function:

$C = (wire length cost) + \lambda (overlap penalty function),$

where

$\lambda$  = an adjustable weighting factor

For such a cost function, non-linear optimization techniques [SB87] and simulated-annealing techniques [SS90] have been proposed to find a good solution. However, both approaches are very time-consuming yet still cannot always find the global optima. Furthermore, the value of  $\lambda$  strongly affects the quality of the solution and there is no single optimal value for all problems. Usually,  $\lambda$  is increased slowly based on the results from optimization theory [SB87] or based on a statistical analysis of benchmark examples [SS90].

Another placement approach that resolves overlaps gradually is to use partitioning [Bre77] [Lau79] [SK88] [TKH88] [KSJ88]. Typically, blocks are assigned to non-overlapping regions in a hierarchical, top-down manner until the partitions are comparable to the size of individual blocks. At this level, if the blocks cannot fit into the final partitions, overlaps may still occur and different heuristics have to be used to remove these overlaps.

This first general paradigm has a major drawback: the intermediate placement results are not legal, so their evaluations are based on estimations that are not really precise. In the second paradigm, placement algorithms generate legal solutions repeatedly for more precise evaluations. In row-based design styles, such as gate-array and standard-cell, legal solutions can be generated easily by assigning blocks to overlap-free rows or columns with linear ordering. However, this pseudo-one-dimensional approach is normally not applicable when blocks are of different sizes and shapes as in macro-block layout or in component placement on printed circuit boards.

For macro-block placement problems, some researchers have introduced creative new cost functions to redistribute blocks evenly from the initial placement. In [Joh87], new objective functions are created based on a planar triangulation derived from the initial placement. In [RJ89], cell area distributions are improved by optimizing the cell density projected on a rotating axis. However, while these approaches reduce the amount of overlap, they fail to produce legal and compact layouts quickly.

Compaction/Spacing is yet another method for resolving overlaps among cells of different sizes and shapes. Compaction has been widely used in enforcing layout rules when converting symbolic layout to mask geometry [HP79]. In placement, the use of compaction has been limited as a clean-up process to generate a legal solution and/or to optimize the total area after wiring optimization. Using compaction during the placement optimization process, so far, has been impractical because existing compaction algorithms either run too

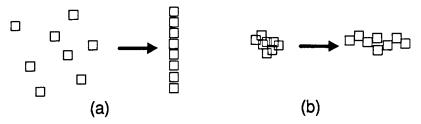

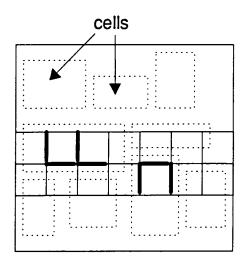

slowly or cannot generate satisfactory results. In general, graph-based 1-D compaction is fast enough but may not generate dense results for blocks of strongly varying sizes. Two-dimensional compactors [SLW83] [KW84] [Xio89] [SSVS86] can generate smaller results but have been too slow to be used repeatedly in the placement process. Furthermore, existing compaction algorithms may produce poor layouts with high wiring costs because they destroy important neighboring relations among blocks that were derived in previous wiring optimization steps. As shown in Fig. 2.1, compaction of very loose or highly clustered initial placements may result in layouts of unsatisfactory aspect ratios in which the original neighboring relations have been lost.

Fig. 2.1 Horizontal compaction of loose (a) or dense (b) initial placements.

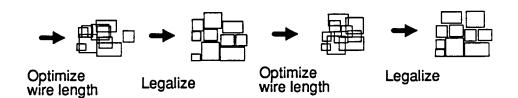

This chapter presents a new 2-D compaction algorithm for use in the placement process. Unlike typical layout compactors, the compaction algorithm is designed primarily for spacing and packing rectangular blocks without connecting wires. With a new data structure based on a planar triangulation graph, the compactor runs efficiently and is capable of maintaining the important neighboring relations among blocks. With such a 2-D compactor, the second paradigm that generates legal solutions repeatedly becomes feasible for the macro-cell placement problems. This can be achieved by alternating between wire-length optimization phases that may create overlaps, and legalization phases that use the 2-D compactor to generate dense legal placements quickly (Fig. 2.2). With such a paradigm, the placement tool can evaluate legal placements precisely and can choose the best solution.

Fig. 2.2 Basic idea of using a compactor/spacer in the placement process.

## 2.2 Data Structure

#### 2.2.1 Definitions

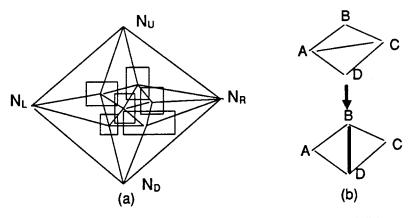

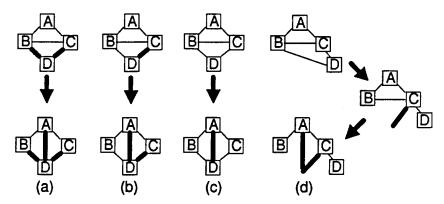

The basic data structure for the 2-D compactor is based on planar triangulation. As defined in [PS85], a graph is planar if it can be embedded (i.e. drawn) in a plane without crossings. The embedding of a planar graph determines a partition of the plane. This partition is a triangulation if all the bounded regions are triangles. Such an embedding of a planar graph will be referred to as a triangulation graph. For a given placement of blocks, a triangulation graph can be built with the centers of all blocks plus four additional boundary nodes,  $N_R$ ,  $N_U$ ,  $N_L$ , and  $N_D$  (Fig. 2.3(a)). For such a triangulation graph, every edge, except the four edges on the boundary of the graph, is enclosed by a quadrilateral. An edge-swapping operation on an edge (A,C) enclosed by quadrilateral ABCD is to replace edge (A,C) with (B,D) (Fig. 2.3(b)).

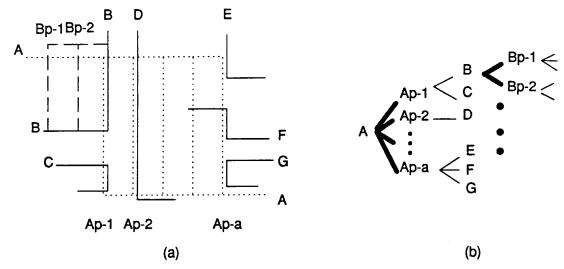

Fig. 2.3 (a) A triangulation graph from a given placement and (b) an edge-swapping operation on edge (A,C).

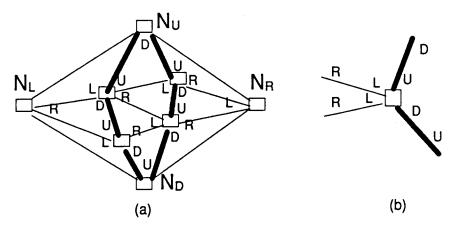

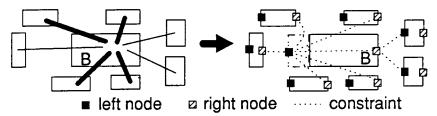

In [VKLS90], planar triangulation is used to represent topological constraints between elements for compacting layout in a two-dimensional manner. However, the proposed compaction algorithm is very slow because actual 2-D distances instead of manhattan distances are used in enforcing the constraints. To make use of the fast 1-D graph-based compaction algorithms, the triangulation graph is enhanced by marking each edge with an orientation, i.e. horizontal or vertical. Furthermore, each end of every edge is labeled with the direction viewed from the connected node. For a vertical edge, its upper end is marked as Down and its lower end as Up. For a horizontal edge, its right end is marked as Left and its left end as Right.

Fig. 2.4 (a) A RULD-graph with four legal nodes and the four boundary nodes. (b) An illegal node without any *Right* edge. *In most figures, bold lines represent vertical edges and thin lines represent horizontal edges*.

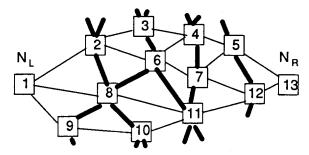

Because the triangulation graph is embedded in a plane, the edges connected to each node can be ordered counter-clockwise around the node. If the directions of the connecting ends of these edges form an ordered sequence containing all four types of directions: (Right..., Up..., Left..., Down...), the node will be called a legal node. If all the nodes in a triangulation graph except the four additional, special boundary nodes  $N_R$ ,  $N_U$ ,  $N_L$ , and  $N_D$  are legal, the graph will be called a Legal RULD-graph, or simply a RULD-graph (Fig. 2.4).

For a given RULD-graph, a horizontal (vertical) crack-path is a sequence of nodes,  $(n_1, n_2, ...., n_k)$ , such that there exist horizontal (vertical) edges  $e_j = (n_j, n_{j+1})$ , with  $1 \le j \le k-1$  and the directions of  $e_j$  at  $n_j$  are all the same. A cut-path is a crack-path from one boundary node to the opposite boundary node, e.g.  $N_R$  to  $N_L$ . A horizontal (vertical) crack-path  $B = (b_1, b_2, ...., b_n)$  is a branch of the horizontal (vertical) crack-path  $A = (a_1, a_2, ...., a_m)$  if the following conditions hold:

- (1)  $b_1=a_s$ ,  $b_n=a_e$ , for some s and e such that  $1 \le s < e \le m$ ;

- (2) Every edge  $(b_i,a_j)$ , 1 < i < n and s < j < e, is vertical (horizontal).

Fig. 2.5 shows examples of crack-paths and branches.

Fig. 2.5 A portion of a RULD-graph. Node 1 and 13 are boundary nodes. For example, (2,6,7) is a horizontal crack-path and (1,8,11,12,13) is a horizontal cut-path. Crack-path (6,4,5) is a branch of the crack-path (1,2,6,7,5,13) but the path (2,3,4,5) is not.

#### 2.2.2 Building the RULD-Graph

Given an initial placement of blocks, a corresponding RULD-graph can be built in two steps. First, a *triangulation graph* is constructed using the center points of all blocks; then proper orientations are assigned to every edge of the graph to create a legal RULD-graph.

#### 2.2.2.1 Building the Triangulation Graph

For a given placement of blocks, many possible triangulation graphs can be built by treating every block as a point at its center. The best-known is the **Delaunay triangulation**, which can be built in  $O(n \log(n))$  time for n points [PS85]. However, to allow the compactor to maintain the neighboring relations between blocks, the triangulation graph should have proper edges to connect adjacent nodes. When blocks can be of different sizes and may overlap, a Delaunay triangulation based on the centers of the blocks does not record these relations very well (Fig. 2.6).

Fig. 2.6 (a) is a Delaunay triangulation while (b) is a more desirable one.

A more suitable triangulation for our purpose is a minimum-weight triangulation [PS85] with a weight function based on an "effective" distance that takes the sizes of blocks into account. By assuming the value of 1.0 if two blocks just touch in the orientation of interest, the weight function, Weight(i,j) for edge (i,j), is defined as:

$$Weight (i,j) = X_{adj}^{2}(i,j) + Y_{adj}^{2}(i,j)$$

$$X_{adj}(i,j) = X_{dist}(i,j)/X_{size\_sum}(i,j) \qquad \text{if } X_{dist}(i,j) \le X_{size\_sum}(i,j)$$

$$= X_{dist}(i,j)-X_{size\_sum}(i,j)+1.0 \qquad \text{if } X_{dist}(i,j) > X_{size\_sum}(i,j)$$

where:

$X_{dist}(i,j)$  = the x-distance between the center of block i and j;  $X_{size\ sum}(i,j)$  = half the sum of the x-sizes of blocks i and j.

Unfortunately, there is no known polynomial-time algorithm for building a minimum-weight triangulation. Therefore, a greedy edge-swapping routine is used to improve the total weight of a given triangulation. This routine works on one node at a time. For a node m surrounded by edges  $(m, n_i)$ ,  $1 \le i \le k$ , the greedy algorithm tries to swap all surrounding edges  $(n_i, n_{i+1})$   $1 \le i < k$ , and edge  $(n_k, n_1)$ . The edge is swapped if the surrounding quadrilateral is convex and if the new edge has lower weight than the original one. This routine is repeated on the same node until there are no more edge-swapping operations that improve the total weight.

Such a triangulation graph is built incrementally. For a given block placement, the four boundary nodes  $N_R$ ,  $N_U$ ,  $N_L$ , and  $N_D$  are first placed with five edges  $(N_R N_U)$ ,  $(N_U N_L)$ ,  $(N_L N_D)$ ,  $(N_D N_R)$ , and  $(N_R N_L)$ , to make a triangulation graph that encloses all the block centers. Then the nodes are inserted one at a time. For every node N to be inserted, the enclosing triangle ABC is found and three new edges (A,N), (B,N), and (C,N) are created. Then the greedy edge-swapping routine is tried on node N. After all the nodes have been inserted, each one is tried once again in random order to improve the total weight of the triangulation. A reasonable local optimum can be achieved by this method. The overall algorithm can be described as the following C-like pseudo-code:

```

build_triangulation_graph()

G = build_initial_graph_with_four_boundary_node();

for(;;) {

n = sel node();

if ( n == NULL ) break;

insert_node_to_graph(G, n);

improve_node_by_greedy_edge_swapping(n);

for all node (n) {

mark_node(n);

do {

change = 0;

for all node (n) {

if ( node_is_marked ) {

improve_node_by_greedy_edge_swapping(n);

if ( some_edge_is_swapped ) {

mark neighbors(n);

change = change + 1;

} else {

unmark_node(n);

} while ( change > 0 );

}

```

In this process, all the basic routines can be accomplished in constant time except the operation to insert a new node into the graph because it needs to find an enclosing triangle first. If the nodes are inserted randomly, the average time complexity to find the triangle around the n-th node can be as high as O(n). To speed up this search process, the nodes are sorted based on their positions such that the next node to be inserted is close to the previous one. Under such a situation, the search can start from the node just inserted and choose one of its attached triangles. If the new point is not inside this triangle, an adjacent triangle closer to the point is selected until the enclosing triangle is found (Fig. 2.7).

Fig. 2.7 A possible search sequence in finding the enclosing triangle for the new node.

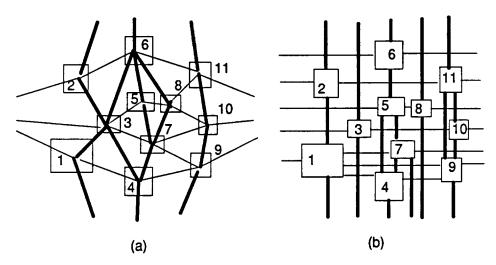

To insert nodes in a proper order, the block centers are sorted into a 2-D binary tree with alternating X and Y cuts such that each leaf node contains at most eight points which can be inserted in random order. Such a tree can be traversed in a depth-first order. If the traversal of the nodes is carefully arranged into Hilbert order [Kah89], it can be assured that the inserted node is close to the previous one (Fig. 2.8(a)). But even with a simple fixed ordering (Fig. 2.8(b)), on average, only three to four triangles need to be tested on every insertion. Table 2.1 shows that this number holds even for large problems with thousands of points.

| _   | 9          | 13   | 14 |  |  |

|-----|------------|------|----|--|--|

| 8   | 10         | 1112 | 15 |  |  |

| 7   | 2 3<br>1 4 | 19   | 16 |  |  |

| 6   | 5          | 18   | 17 |  |  |

| (a) |            |      |    |  |  |

|     | 10                          | 17    | 19 |  |  |

|-----|-----------------------------|-------|----|--|--|

| 8   | 9                           | 15 16 | 18 |  |  |

| 2   | $\frac{ 6 }{4} \frac{7}{5}$ | 12    | 14 |  |  |

| 1   | 3                           | 11    | 13 |  |  |

| (b) |                             |       |    |  |  |

Fig. 2.8 Traversing a 2-D binary tree in (a) Hilbert order and (b) simple fixed ordering.

|         | # Triangles tested |         |  |  |

|---------|--------------------|---------|--|--|

| # nodes | maximum            | average |  |  |

| 100     | 10                 | 3.57    |  |  |

| 400     | 34                 | 3.61    |  |  |

| 900     | 46                 | 3.76    |  |  |

| 1600    | 76                 | 3.81    |  |  |

| 2500    | 75                 | 3.95    |  |  |

**Table 2.1** The maximum and average number of triangles tested when new nodes are inserted into a triangulation graph. In each example, the N nodes are arranged into a 2-D array with  $\sqrt{N}$  rows and  $\sqrt{N}$  columns.

#### 2.2.2.2 Edge-direction Assignment

After building the triangulation graph, initial orientations are assigned to all the edges in the graph. Edges with slopes in the range of (-1.0,1.0) are initially classified as horizontal, with the directions of their left ends marked as Right and their right ends marked as Left. All other edges are vertical with their lower ends marked as Up and upper ends as Down. This initial assignment cannot guarantee that all nodes are legal; some nodes may miss an edge in a certain direction. However, such an assignment has two important properties:

- (1) The edges are ordered in a counterclockwise traversal around a node as (R..., U..., L..., D...). There may be missing directions but no out-of-order cases.

- (2) A node can't miss edges in two consecutive directions (e.g. Right and Up) because any internal angle of a triangle must be less than 180 degrees.

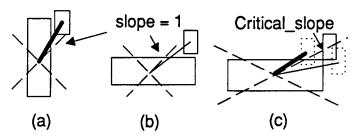

This initial assignment is simple but it doesn't capture the neighboring relations between blocks very well when the aspect ratios of blocks differs strongly from 1.0 (Fig. 2.9). Therefore, an improvement phase is conducted to get a better orientation assignment based on the following formula for a *desired* direction for all edges:

```

Edge (i,j) is horizontal if Edge\_slope(i,j) < Critical\_slope(i,j) vertical otherwise.

```

where

Edge\_slope(i,j) =  $|Y_{dist}(i,j) / X_{dist}(i,j)|$ Critical\_slope(i,j) =  $|Y_{size\_sum}(i,j) / X_{size\_sum}(i,j)|$   $X_{dist}(i,j)$  = the x-distance between the centers of block i and j  $X_{size\_sum}(i,j)$  = half the sum of the x-sizes of block i and j.

In this formula, the *Critical\_slope* is defined as the slope of the edge when the corners of two blocks touch as in Fig. 2.9(c).

Fig. 2.9 (a) An edge that should be horizontal but with slope greater than 1. (b) An edge that should be vertical but with slope smaller than 1. (c) The interpretation of the Critical\_slope in deciding the direction of edges.

In the improvement phase, the desired orientation is computed for every edge. The desired orientation will be assigned to the edge if the two important properties mentioned

above won't be destroyed on the direction change. This is necessary since the legalization process works only when the two properties hold.

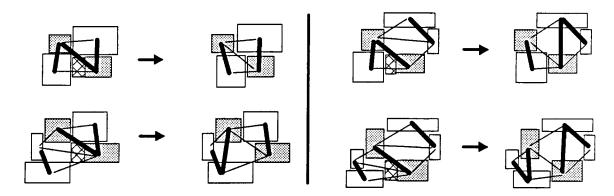

After the initial classification and the improvement phase based on block size, a legalization process is conducted with edge-swapping operations. Because of the two properties mentioned above, illegal nodes that miss edges in a certain direction will have edges in the two adjacent directions. For a triangle ABC where node A does not have any, say, Down edge, edge (A,B) and (A,C) must be both horizontal. Furthermore, edge (B,C) must be horizontal too or the two properties cannot hold on either node B or C. With the edge (B,C) being horizontal, the edges (B,D) and (C,D) of the adjacent triangle have to be in one of the following four cases (Fig. 2.10):

- (a) both are vertical;

- (b) one is horizontal and the other is vertical;

- (c) both are horizontal and their directions at D are different;

- (d) both are horizontal and their directions at D are the same.

Fig. 2.10 Legalizing node A by introducing a *Down* edge.

For the first three cases, node A can be legalized easily by replacing edge (B,C) with a vertical edge (A,D). In case (d), either B or C (C in Fig. 2.10(d)) is illegal and needs to be legalized first before edge (B,C) can be swapped to legalize A. This algorithm can always legalize all the nodes in the graph. Even though case (d) requires a recursive call of the legalization routine, this process always terminates because eventually, a boundary node will be encountered where case (d) cannot occur. Normally, this recursive process will terminate after just two or three steps.

# 2.2.3 Linear Constraints from RULD-graph

Like most layout compactors, linear constraints[HP79] are used to space the blocks properly. With enough linear constraints, a legal placement without overlaps can be obtained with the longest path algorithm[HP79]. Two kinds of constraints are derived from a RULD-graph: explicit constraints and implicit constraints. Each edge in the RULD-graph represents an explicit constraint. A vertical (horizontal) edge represents a vertical

#### 2.2 Data Structure

(horizontal) spacing constraint between the two connected nodes. These constraints work just like those used in traditional layout compactors. However, as shown in Fig. 2.11, these constraints alone cannot prevent all overlaps. Rather than adding new edges and destroying the planarity of the graph, such constraints are calculated dynamically whenever a corresponding block constellation is encountered. This leads to the notion of *implicit constraints*.

Explicit constraints fail to prevent overlaps when a vertical edge connects two blocks whose projection on the x-axis don't overlap, such as block B and C in Fig. 2.11. In the traditional 1-D compaction, vertical constraints are generated only when the block's projections on the x-axis overlap. It turns out that all illegal overlaps can be prevented if blocks with vertical constraints between them have overlapping projections on the x-axis. This notion is captured in the RULD-graph representation with a horizontal implicit constraint:

$$X_{R}^{left} \leq X_{C}^{right}$$

and  $X_{R}^{right} \geq X_{C}^{left}$ ,

where

$X_B^{left/right}$ : the x position of left/right edge of block B.

Similarly, blocks connected with a horizontal edge are assigned vertical implicit constraints for their y-coordinates. In some situations, a block may not be big enough to satisfy all such constraints simultaneously (Fig. 2.11). In this case, block B is provided with a virtual extension so that  $X_B^{right} \ge X_C^{left}$  and  $X_B^{left} \le X_F^{right}$ .

Fig. 2.11 (a) The explicit constraints in the RULD-graph do not prevent all overlaps (A and E). (b) Block B is extended with the shadowed region to satisfy all implicit constraints.

By enforcing explicit and implicit constraints, a legal placement without overlaps can always be obtained based on the following theorems:

Theorem 1: Blocks won't overlap if the *explicit* and the *implicit* constraints are enforced in both, horizontal and vertical, directions.

Proof: For any two blocks, exactly one of the three possible cases below can be true:

- (1) both are on the same vertical cut-path;

- (2) one is on a vertical cut-path and the other is on a branch of the cut-path; and

- (3) there is at least one vertical cut-path between them.

In case (1), the two blocks will be separated by the explicit constraints derived from the edges on the cut-path.

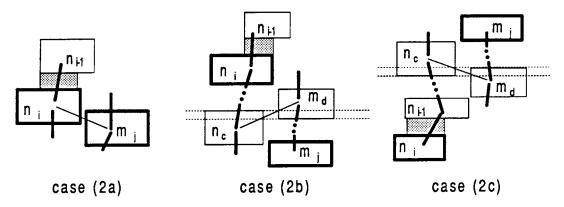

In case (2), the cut-path is assumed to be  $(n_1, n_2, ...., n_k)$  and the branch is  $(m_1, m_2, ...., m_l)$  and  $m_1=n_b, m_l=n_e$ . For any block  $n_i$  and  $m_j$ , only one of the three possible cases can happen (Fig. 2.12):

- (2a) they are connected by a horizontal edge  $(n_i, m_j)$ ;

- (2b) there is a horizontal edge  $(n_c, m_d)$  such that c > i and d < j; or

- (2c) there is a horizontal edge  $(n_c, m_d)$  such that c < i and d > j.

For case (2a), the two blocks won't overlap because of the constraints from edge  $(n_i, m_j)$ . For case (2b), block  $n_c$  and  $m_d$  will have overlaps in their projections on the y-axis (the dotted lines in Fig. 2.12). Therefore,  $n_i$  and  $m_j$  will be separated by this overlapping part because  $n_i$  is higher than  $n_c$  while  $m_j$  is lower than  $m_d$ . The same argument applies for case (2c).

Fig. 2.12 The three situations in case (2). The shadowed regions are the filler rectangles to form the *isolation zone* for the cut-path in case (3).

For case (3), it can be shown that a sequence of rectilinear isolation zones can be created for all the cut-paths between the two nodes that separate the two blocks. For each cut-path, its corresponding rectilinear isolation zone covers the blocks on the cut-path and filler rectangles drawn between subsequent blocks  $n_i$  and  $n_{i-1}$  with the width equal to the overlaps of their horizontal projection (Fig. 2.12). These rectangles can be of zero width or height. Based on the same argument used in the proof for case (2), no block on the branch of the cut-path can overlap with these rectangles either.

For the two blocks in case (3), a sequence of cut-paths can be formed from left to right by replacing the old cut-path,  $(n_1, n_2, ...., n_k)$ , with nodes from one of its branches on the right side  $(m_1, m_2, ...., m_l)$  to obtain a new cut-path,  $(n_1, ..., n_b, m_2, ..., m_{l-1}, n_e, ... n_k)$  (Fig. 2.13). For such a sequence of cut-paths, a sequence of isolation zones can be formed from left to right. Therefore, the two blocks will be separated by these isolation zones.

Fig. 2.13 For the cut-path (1,7,9,10,11,3), the rectilinear isolation zone is formed by adding the shadowed filler rectangles between the blocks. By replacing (10, 11, 3) with the branch (10, 12, 3), a new cut-path (1,7,9,10,12,3) can be formed.

## 2.2.4 Interpretations and Discussions

The RULD-graph replaces the horizontal and vertical constraint graphs used in the original 1-D compaction algorithm [HP79]. Our compaction algorithm also uses the vertical and horizontal edges to represent horizontal and vertical constraints respectively. However, the RULD-graph can easily capture diagonal adjacency relations that cannot be represented in the traditional constraint graph. Without this information, the relative positions between neighboring nodes can be destroyed easily during compaction.

Fig. 2.14 Comparison between (a) RULD-graph and (b) constraint graph. The edges, (1,3) (3,5) and (8,11) in the RULD-graph cannot be represented in the constraint graph.

Another data structure strongly related to the RULD-graph is the *rectangular-dual* for a triangulation graph [KK88] [TFKM91] that forms a partition of the rectangular layout space. For a given partition, a corresponding legal RULD-graph can always be built with all the explicit and implicit constraints satisfied. However, enforcing all the implicit and explicit constraints in a RULD-graph does not always create a rectangular-dual partition. As shown in Fig. 2.15, no rectangular partition can be found for the compaction results such that each block is covered by exactly one partition.

Fig. 2.15 (a) Compaction result for the given RULD-graph. (b) A possible rectangular-dual for the triangulation graph.

# 2.3 Compaction Algorithms

From a given RULD-graph, a legal placement without overlaps can be computed quickly using a 1-D compaction algorithm to enforce all the explicit and implicit constraints. The result is usually not dense enough, and a 2-D compaction algorithm that moves cells in both x- and y-directions simultaneously is needed to further reduce the total area. This section describes these compaction algorithms and presents the results of some experiments for evaluating them.

# 2.3.1 1-D Compaction Algorithm

The 1-D compaction algorithm generates results without any overlaps by enforcing all the explicit and implicit constraints. To build the complete constraint graph, implicit constraints are transformed into simple linear spacing constraints. While compacting to the right, a block B is represented with two point nodes B.left and B.right, whose x-coordinates represent  $X_B^{left}$  and  $X_B^{right}$ , respectively. Node B.right will have spacing constraints from the left nodes of all blocks on its right that have a horizontal edge to block B (Fig. 2.16). Node B.left will have spacing constraints from B.right (distance  $\geq$  width of the block) and from the right nodes of those blocks that have a vertical edge to block B (distance  $\geq$  0). Similarly, node B.left will have spacing constraints to all right nodes of the blocks with horizontal edges on the left side of block B.

#### 2.3 Compaction Algorithms

Fig. 2.16 Transforming projection constraints to spacing constraints.

In our actual implementation, this transformation is done in an implicit way. The implicit constraints are derived on the fly. This process, like traditional 1-D compaction, can be computed in O(n) time for n blocks.

### 2.3.2 2-D Compaction Algorithm

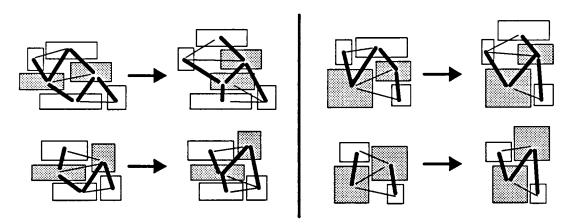

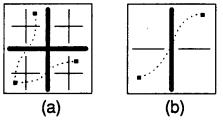

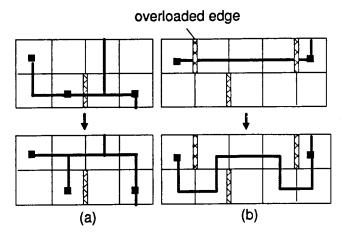

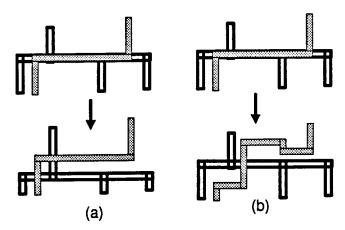

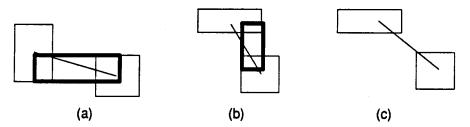

As demonstrated by 2-D compactors [SSVS86] [WMND88], layout density can be improved by moving selected blocks perpendicularly to the direction of compaction. However, such 2-D moves can be quite expensive if the constraint graph and the critical paths have to be recomputed after every move. In our compaction algorithm, these lateral moves are achieved by simply manipulating the edges in the RULD-graph. To shorten the horizontal critical path during the horizontal compaction, the compactor will try to change a horizontal edge into a vertical one. Fig. 2.17 shows four of the eight possible cases of changing a horizontal edge into a vertical edge when blocks are compacted to the *right*. The other four cases can be obtained by flipping these four cases vertically. In principle, there are 16 different possible quadrilaterals around an edge (four edges, two possible orientations), but seven of them are illegal in a RULD-graph. Only seven of the nine legal cases can be changed (two possible moves for one case). In the two remaining cases, the horizontal edge is caught between two other horizontal edges at one node and thus cannot be changed until one of the adjacent edges has been modified.

**Fig. 2.17** The four basic ways of changing a horizontal edge to a vertical edge while compacting to the *right*.

Sometimes, the critical path consists of implicit constraints as well as explicit constraints. During a horizontal compaction, the implicit constraints are derived from vertical edges so the compactor also tries to replace vertical edges with horizontal edges either to shorten the critical path or to convert them into explicit constraints. There are also eight possible cases of changing a vertical edge into a horizontal edge. Four of them are shown in (Fig. 2.18) and the other four also can be obtained by flipping these four cases vertically. The simple edge-reorientation may then be followed by some edge-swapping operations.

**Fig. 2.18** The four possible ways of changing a vertical edge that causes a horizontal implicit constraint on a horizontal critical path while compacting to the *right*.

Because the constraints are generated based on the RULD-graph instead of the absolute position of blocks, there is no need to recompute the constraints on every move. Therefore, these 2-D moves can be achieved much more efficiently than those of other 2-D compactors.

In addition to these moves, the critical path also can be shortened by rotating a block on the critical path by 90 degrees. Such a rotation won't modify any edges of the RULD-graph but it may change both horizontal and vertical critical paths. Because in some types of problem, the blocks cannot be rotated, this operation can be disallowed explicitly.

With this set of 2-D moves in the "toolbox", the remaining problem is to select a proper edge to switch direction. The move selection is based on the *supercompaction* proposed in [WMND88]. For a given placement problem, the compactor tries to generate a dense layout with the specified aspect ratio. The compactor works on one direction at a time trying to generate a smaller layout while keeping the aspect ratio close to the specified value. To compute the size of the resulting layout, the compactor maintains with every node in RULD-graph the values of the longest paths to the four boundary nodes. When the compactor tries to reduce the horizontal size, the compactor checks all the edges and nodes on the horizontal critical path and then selects the move that will cause the minimum increase of the vertical critical path can be computed from the longest paths of the involved nodes to the two vertical boundary nodes. After every

move, the longest paths for all nodes to the four boundary nodes are updated with an event-driven longest path algorithm. The overall control strategy can be summarized by the following C-like pseudo code:

```

2d_compact (desired_ratio_of_X_size_to_Y_size)

aspect ratio[horizontal] = desired_ratio_of_X_size_to_Y_size;

aspect_ratio[vertical] = 1 / aspect_ratio[horizontal];

best result = big_number;

ori = horizontal;

ori2 = vertical;

new_ratio = critical_path_length(ori) / critical_path_length(ori2);

if ( new_ratio < aspect_ratio[ori] ) {

exchange (&ori, &ori2);

for(;;) {

do {

mv = select_2d_move(ori);

make 2d_move(mv);

new_ratio2 = critical_path_length(ori2) / critical_path_length(ori);

} while ( new_ratio2 < aspect_ratio[ori2] * (1+ERR_RATIO) )</pre>

new_result = eval_placement();

if ( new_result >= best_result ) break;

best result = new result;

exchange (&ori, &ori2);

return (best_result);

}

```

In this algorithm, the compaction in one direction is terminated when further moves will cause too much increase of the critical path in the other direction. This is achieved by controlling the resulting aspect ratio to be close to the specified value. If the variable ERR\_RATIO is set to be 0.0, the generated layout will have almost the same aspect ratio as the specified value. However, to find a dense solution, the compactor usually has to shorten the critical path in the compaction direction by temporarily increasing the critical path in the other direction. Therefore, the variable ERR\_RATIO is normally set to be 0.15 to allow a 15% deviation of the resulting aspect ratio from the specified value so that the compactor won't get stuck prematurely.

When the compaction in one direction is terminated, the procedure eval\_placement evaluates the legal placement based on its area and on its estimated wire length, using weights supplied by the user. If no further improvement can be achieved, the compactor will quit and return the best solution.

#### 2.3.2.1 An Alternative Control Strategy

In [TS91b], a control strategy based on zone-refining [SSVS86] was proposed. This proposed zone-refining approach can run faster but it usually produces results with longer wire lengths.

This zone-refining approach runs faster because it minimizes the overhead for updating the critical paths. In the direction of compaction, the critical path is computed simply by adding the two critical paths from the two sides separated by the free zone. For the critical paths in the perpendicular direction, the projection constraints are replaced with quadrilateral constraints [TS91a] [TS91b], which are easier to compute.

There are several disadvantages to the use of the zone-refining control strategy. First, using the zone-refining control strategy normally causes more 2-D moves than using the supercompaction control strategy to achieve layouts with the same density. This is because the supercompaction approach selects the most promising 2-D move from the possible moves on the critical path, while the zone-refining approach can only move cells adjacent to the free zone. Although all the 2-D moves are local and preserve most of the neighboring relations among blocks, too many 2-D moves, especially when they are all in the same region, can destroy a lot of neighboring relations among blocks. These unnecessary 2-D moves usually increase the wire-lengths of the results.

The other disadvantage of the zone-refining control strategy is the requirement of an explicit size limit in the direction perpendicular to the compaction direction. If the limit is set too high during the compaction process, the compactor makes too many unnecessary 2-D moves and destroys a lot of neighboring relations. If the limit is too low, the compactor may not be able to reduce the critical path to generate a dense layout.

To compare these two control strategies, some illegal placements with overlaps were generated by sampling the intermediate results of actual placement processes on two MCNC macro-cell benchmarks, AMI33 and AMI49. These illegal layouts were then subject to the two different compaction algorithms. Table 2.2 summarizes and compares the results.

|         |        | Zone Refining |       |          | Sup     | ion   |          |

|---------|--------|---------------|-------|----------|---------|-------|----------|

|         |        | wire-l        | ength | CPU-time | wire l  | ength | CPU-time |

| Example | #Block | Average       | Min.  | Average  | Average | Min.  | Average  |

| AMI33   | 33     | 5.76          | 5.25  | 1.46     | 5.20    | 4.69  | 1.22     |

| AMI49   | 49     | 10.38         | 8.37  | 2.32     | 10.08   | 8.15  | 2.66     |

**Table 2.2** Comparison of the results from two different compaction control strategies. There are ten different placements tested for AMI33 and eleven for AMI49. The CPU-times are measured in seconds on a SUN SPARC-1.

#### 2.3 Compaction Algorithms

The supercompaction strategy can produce better results in terms of wire length and thus potentially result in chips with better performance. On the other hand, it is somewhat slower on larger layout problems. With typical macro-cell problems containing on the order of a hundred blocks, the speed penalty is not considered a serious problem. Therefore, the supercompaction control strategy has been adopted to achieve results with better wire length.

### 2.3.3 Evaluation of the Compaction Algorithm

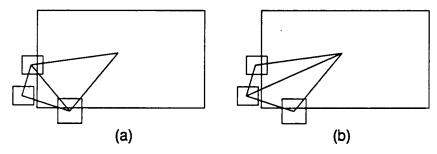

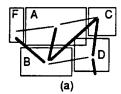

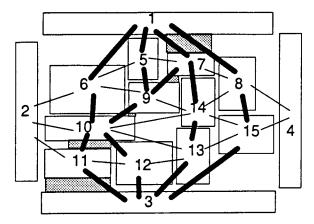

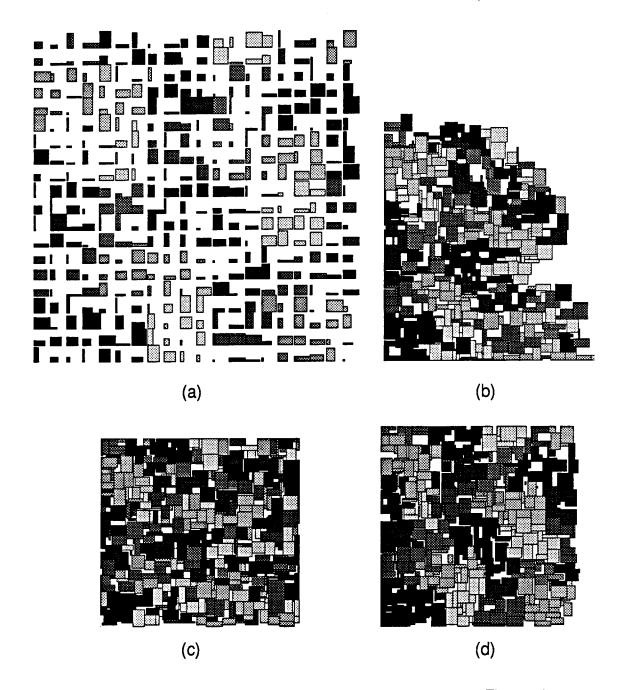

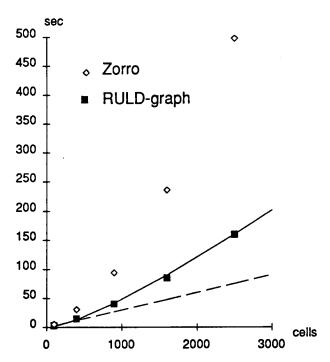

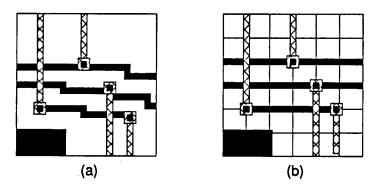

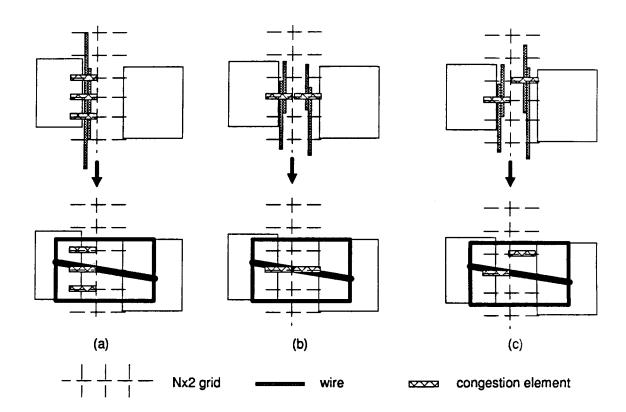

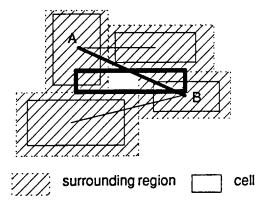

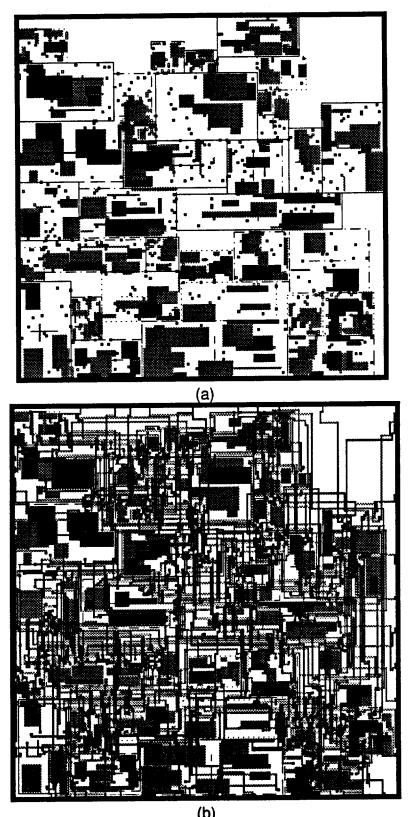

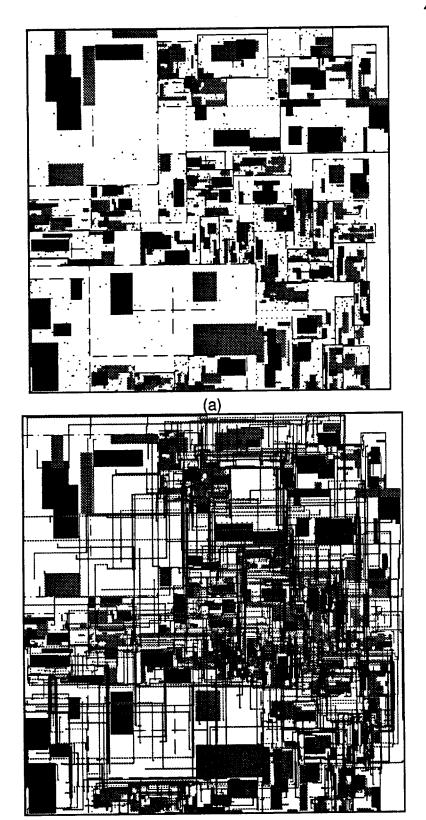

The compaction algorithm has been implemented in C in the UNIX environment. Because this compactor is designed for spacing and packing rectangular blocks without connecting wires, the well-known layout compaction benchmarks [Boy87a] [Boy87b] can not be used to test the compactor. To evaluate the compactor, a series of random examples were generated. In these examples, rectangles with random sizes are arranged into a two-dimensional array (Fig. 2.19(a)). Using these examples, we compare our RULD-graph compactor with a very simplistic implementation of traditional 1-D compactor and another 2-D compactor, Zorro[SSVS86]. Table 2.3 summarizes these results. In this table, our compaction results are obtained with four compaction passes, consisting of Left, Down, Right, and Up compactions, with the target aspect ratio set to be 1. The 1-D compaction results are generated using the pre-compactor of Zorro with four compaction passes, consisting of horizontal, vertical, horizontal, and vertical compactions. The Zorro's 2-D results are obtained with a horizontal 1-D pre-compaction, and then with four vertical 2-D compaction passes, consisting of Up, Down, Up, and Down compactions. Because the aspect ratio cannot be specified while compacting with Zorro, each example is given a target width that is equal to our compacted result. Fig. 2.19 shows the initial layout and the three compacted layouts on the example with 400 cells.

|       | 1-D Compaction |       | 2-D: Zorro |       |       | 2-D: RULD-graph |          |       |       |

|-------|----------------|-------|------------|-------|-------|-----------------|----------|-------|-------|

|       |                | void  |            | void  | CPU-  |                 |          | void  | CPU-  |

| #cell | Area           | space | Area       | space | time  | Area            | (/Zorro) | space | time  |

| 100   | 72x77          | 40.9% | 65x61      | 17.4% | 5.7   | 65x64           | (1.049)  | 21.5% | 3.0   |

| 400   | 135x149        | 39.4% | 122x113    | 11.6% | 30.3  | 122x120         | (1.062)  | 16.8% | 15.0  |

| 900   | 202x236        | 44.5% | 179x168    | 12.0% | 94.1  | 179x177         | (1.054)  | 16.5% | 40.5  |

| 1600  | 258x313        | 39.0% | 245x226    | 11.0% | 235.1 | 245x242         | (1.071)  | 16.9% | 84.6  |

| 2500  | 307x405        | 38.3% | 304x282    | 10.5% | 496.3 | 304x300         | (1.064)  | 15.9% | 158.5 |

**Table 2.3** Comparison of the compaction results. The "(/Zorro)" column shows the ratio between the areas generated by the RULD-graph compaction and by Zorro. The CPU-times are measured in seconds on a SUN SPARC-1.

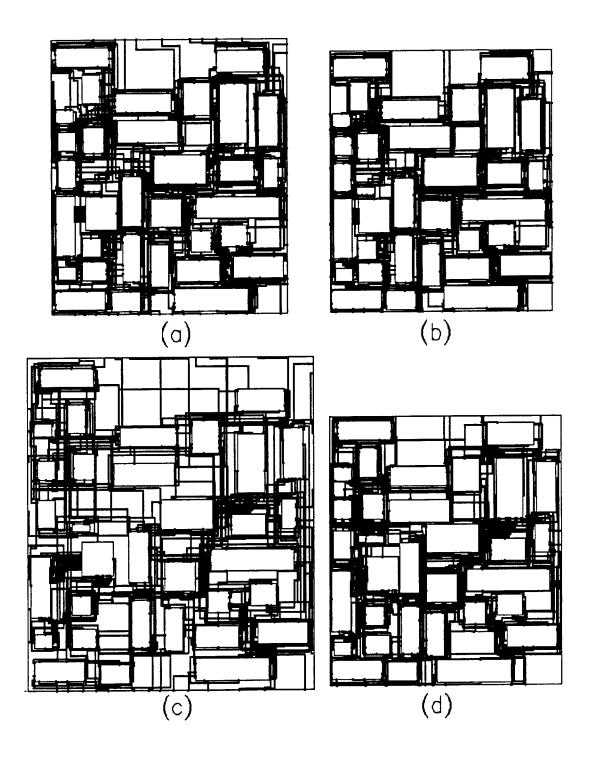

Fig. 2.19 (a) The initial layout. (b) The result of 1-D compaction. (c) The result of 2-D compaction by ZORRO. (d) The result of our 2-D compactor.

The results show that for simple cell-packing problem without wires, the RULD-graph compactor can achieve very compact layouts which are much smaller than the very simplistic 1-D compaction results produced by the Zorro pre-compactor. The results also show that the RULD-graph compactor is much faster than Zorro in 2-D compaction while generating layouts with areas fairly close to Zorro's results. Zorro can produce results that are about 6% smaller because it does not try to preserve the neighboring relations among cells. This

#### 2.4 Wire-Length Optimization Algorithms

is demonstrated by Fig. 2.19. In these figures, cells are filled with different patterns based on their initial locations. By comparing the pattern distributions of the compacted results with the initial layout, it is clear that our compactor maintains most of the neighboring relations of cells while the other two compaction methods destroy a lot of them.

To further analyze the complexity of our compactor, Fig. 2.20 shows the relation between the run-times and the number of the cells for Zorro and the RULD-graph compactor. It shows that complexity of our compactor is close to  $O(n\log n)$  for these cases, where n is the number of the cells.

Fig. 2.20 The CPU-time vs. the number of cells for Zorro and the RULD-graph compactor. The solid line comprises points with  $O(n \log n)$  complexity and the dashed line is for O(n) complexity.

# 2.4 Wire-Length Optimization Algorithms

Most placement algorithms optimize an objective function based on estimated total wire length. The most popular estimate used in comparing placement results is the *half-perimeter metric*[Oht85], which calculates the sum of the half-perimeter of the bounding boxes of all nets. This half-perimeter measure is essentially the lower-bound of realizable wire length and is usually a very good estimate of final routed results. However, this is not a continuous function that can be optimized easily and quickly. To make use of standard optimization

techniques, many placement tools formulate the cost function as the sum of the squared wire length, which is a quadratic function.

In comparing two different placements of the same problem of significantly different quality, the one with better quadratic cost normally has better half-perimeter cost, too. However, this correlation disappears when the quadratic costs of the two placements under comparison are roughly equal. To achieve the best result in the minimum amount of time, the quadratic cost function is used initially to obtain a good solution. Then simple greedy algorithms are used to further optimize the half-perimeter cost function.

In the following sections, the formulation of the quadratic functions and the corresponding optimization algorithms will be first presented. Then the simple greedy algorithm that optimizes the half-perimeter cost function will be introduced.

## 2.4.1 Simple Quadratic Formulation

By assuming that all the pins are in the center of the cells, a simple quadratic cost function F can then be formulated as:

$$F = \frac{1}{2} \sum_{i,j} c_{i,j} ((x_i - x_j)^2 + (y_i - y_j)^2)$$

where

$(x_i, y_i)$  = the position of the center of cell i $c_{ij}$  = the number of connections between cell i and j;

or in the matrix form:

$$F = \mathbf{x}^{T} \mathbf{B} \mathbf{x} + \mathbf{y}^{T} \mathbf{B} \mathbf{y}$$

$$= \sum_{ij} b_{ij} x_{i} x_{j} + \sum_{ij} b_{ij} y_{i} y_{j}$$

where

$$b_{ij} = -c_{ij}$$

if  $i \neq j$

=  $\sum_{k} c_{ik}$  if  $i = j$ .

In computing  $c_{ij}$ , a two-pin net between the cell i and j is counted as 1.0. For a net with more than two pins, it is assumed that every pair of cells connected by the net has the same amount of connection derived from the net, which is scaled to be much smaller than 1.0 so these multiple-pin nets won't dominate the wire length cost. This is computed by assuming the quadratic cost F for the net is always 1.0 disregarding the number of pins when the pins are put on a straight line with distance 1.0 between any two adjacent pins. Based on this

#### 2.4 Wire-Length Optimization Algorithms

assumption, there will be q-i pairs of pins with distance i, for i=1,...,q-1, for a net with q pins. The quadratic cost derived from these connections is:

$$\sum_{i=1}^{q} c (q-i) i^2,$$

where

c = amount of connection for each pin pair.

By setting this function to be 1, c will be equal to  $12/(q^2(q-1)(q+1))$ .

With the above quadratic cost function F, the optimal cost is zero when  $x_1=x_2=...=x_N$  and  $y_1=y_2=...=y_N$ , i.e. all the blocks are at the same position. However, when there are fixed pins, the x-part of the equation can be rewritten as:

$$F = \frac{1}{2} \sum_{ij} c_{ij} (x_i - x_j)^2 + \frac{1}{2} \sum_{ik} c_{ipk} (x_i - x_{pk})^2$$

where

$(x_{p_k}y_{p_k})$  = the position of pin k

$c_{ip_k}$  = number of connections between cell i and pin k.

To optimize such a quadratic cost function, the Gauss-Seidel formulation [GV83] is used, which is essentially a gradient-descent method to move each cell toward its optimal position gradually. The x-positions of the blocks can be computed with the following equations.

$$x_i^{(t+1)} = x_i^{(t)} + \frac{1}{b_i} \left( \sum_i c_{ij} (x_j^{(t)} - x_i^{(t)}) + \sum_k c_{ip_k} (x_{p_k} - x_i^{(t)}) \right)$$

where

$x_i^{(t)} = x$ -position of block i in iteration t,

$$b_i = \sum_j c_{ij} + \sum_k c_{ip_k}.$$

The time complexity for computing one move for N cells is O(cN), where c is the average number of cells with connection to each cell. In the worst case, c = N and the time complexity is  $O(N^2)$ . However, for large problems with many blocks, c is usually much smaller than N and the time complexity is almost linear.

## 2.4.2 Quadratic Formulation using Exact Pin Positions

The simple formulation introduced in the previous section assumes all pins are at the center of the cells. When the cells are small, such as in the standard-cell or gate-array design styles, the distances from the pins to the center of the cells are usually much shorter than the

average net length, so this simplified model is precise enough. However, for macro-cell problems, this simplified model is no longer a good approximation because the net length can be fairly close to the distance from the pins to the cell center. To estimate the wire length with the exact pin positions, the x-part of the quadratic cost function can be formulated as:

$$F_{x} = \frac{1}{2} \sum_{m} \sum_{i,j} w_{m} (x_{p_{i}} - x_{p_{j}})^{2}$$

$$= \frac{1}{2} \sum_{m} \sum_{i,j} w_{m} ((x_{c_{i}} + dx_{p_{i}}) - (x_{c_{j}} + dx_{p_{j}}))^{2}$$

where

$\sum_{m}$  : all nets;

$\sum_{i}$  : all pin pairs in net m;

$w_m$  = weight on each pair of pins for net m;

$x_{c_i} = x$ -position of the center of cell  $c_i$  which contains pin  $p_i$ ;

$x_{p_i}$  = absolute x-position of pin  $p_i$ ;

$dx_{p_i} = x_{p_i} - x_{c_i}$ , i.e. x-position of pin  $p_i$  relative to the center of cell  $c_i$ .

In most macro-cell placement problems, cells can be rotated or mirrored to one of the eight possible orientations. To allow rotational degrees of freedom, a continuous angle variable  $\theta$  can be introduced to represent the relative position of a pin to the cell center:

$$\begin{pmatrix} dx_{p_i} \\ dy_{p_i} \end{pmatrix} = \begin{pmatrix} \cos \theta & -\sin \theta \\ \sin \theta & \cos \theta \end{pmatrix} \begin{pmatrix} \Delta x_{p_i} \\ \Delta y_{p_i} \end{pmatrix}$$

where

$(\Delta x_{p_i}, \Delta y_{p_i})$  = relative position of the pin  $p_i$  to cell center without rotation.

In [SB87], such continuous angle variables are introduced to allow all blocks to rotate with arbitrary angles. However, with these continuous angle variables, the cost function is no longer quadratic, and general non-linear optimization routines have to be used. Furthermore, to bring the blocks to one of the eight legal final orientations, additional constraints are also required. To simplify the optimization task, heuristics are used to optimize the cost function in two steps. First, a *cell-orienting algorithm* tries to find near-optimal orientations of all the cells for the current placement. Then a *cell-shifting algorithm* moves cells with fixed orientations to their optimal positions. Because the cell-orienting algorithm is based on the concept of *force* introduced in the cell-shifting algorithm. The cell-shifting algorithm will be discussed first.

#### 2.4.2.1 Cell-Shifting Algorithm

In the cell-shifting phase, the orientations of the cells are assumed to be fixed, i.e. the relative position from each pin to the center of the cell,  $dx_{p_i}$ , is assumed to be constant. Based on the Guass-Seidel method or a gradient-descent method, the optimal solution can be obtained quickly by a sequence of moves:

$$x_h^{(t+1)} = x_h^{(t)} + \frac{1}{d_h} \sum_{m_h} \sum_{j} w_{m_h} \left( (x_{c_j}^{(t)} + dx_{p_j}) - (x_h^{(t)} + dx_{p_{m,h}}) \right)$$

where

$\sum$  : all nets with pins on cell h

$\sum_{i}$ : all pins in net  $m_h$  except pin  $p_{m,h}$

$p_{m,h}$  = the pin on cell h that belongs to net  $m_h$

$x_h^{(t)}$  = the x-position of the center of cell h in iteration t

$d_h = \sum_{m_h} \sum_j w_{m_h}$

Based on these equations, the nets are processed one at a time for calculating the effect of each net on all the cells with pins belonging to the net. After accumulating the effect from all the nets, all the cells are moved simultaneously. For a problem with N cells and M nets, the complexity of the algorithm is O(N+dM), where d is the average of the square of the number of pins for all nets. For macro-cell problems, M is usually greater than N, and this optimization process is slower than the simple quadratic formulation. Fortunately, d is normally a small constant, and the overall complexity is still close to linear.

## 2.4.2.2 Cell-Orienting Algorithm

In the cell-orienting phase, the cells are rotated or mirrored with their centers fixed. Instead of using the complex and time-consuming non-linear optimization routines as shown in [SB87], simple heuristics based on the concept of *force* are used.

Traditional force-directed relaxation methods [FCW67] [HWA73] use attraction forces derived from the nets to pull connected cells together to minimize the wire length. To fit into the concept of force, the equation for computing cell moves can be rewritten as:

$$x_h^{(t+1)} - x_h^{(t)} = \frac{1}{d_h} \sum_{m_h} \sum_j w_{m_h} \left( (x_{c_j}^{(t)} + dx_{p_j}) - (x_h^{(t)} + dx_{p_{m,h}}) \right)$$

$$= \frac{1}{d_h} \sum_{m_h} F_{x,pin} \left( p_{m,h} \right)$$

where

$$F_{x,pin}(p_{m,h}) = \sum_{j} w_{m_h} ((x_{c_j}^{(t)} + dx_{p_j}) - (x_h^{(t)} + dx_{p_{m,h}}))$$

$$= x\text{-component of the force on pin } p_{m,h}$$

$$\sum_{j} : \text{all pins in net } m_h \text{ except pin } p_{m,h}$$

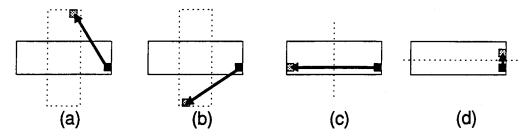

In this new equation, the desired move  $x_h^{(t+1)} - x_h^{(t)}$  is the average of the forces on all pins. These forces are just like the forces used in the traditional force-directed method [HWA73]. If each pin can be moved independently, the desired move of each pin would be the force on the pin. Based on this idea, we can evaluate the effect of four possible orientation change operations: rotate  $90^\circ$ , rotate  $-90^\circ$ , mirror-x, and mirror-y, by comparing the force on each pin to the potential move of the pin on each operation (Fig. 2.21).

Fig. 2.21 The potential moves of a pin on the four orientation-change operations: (a) rotate 90° (b) rotate -90° (c) mirror-x (d) mirror-y.

For a block with only one pin, the orientation change that would minimize the force on the pin would be advantageous. However, blocks normally have more than one pin and the effects on all the pins of a cell need to be accumulated. The overall effect of operation op on a cell h,  $E_{cell}$  (h, op), is evaluated based on the following equations:

$$E_{cell}(h, op) = \frac{1}{d_h} \sum_{i_h} E_{pin}(i_h, op)$$