# **Operating Systems Mechanisms For Continuous Media**

# Ramesh Govindan

Computer Science Division

Department of Electrical Engineering and Computer Sciences

University of California, Berkeley

Berkeley, CA 94709

Support for digital audio and video (*continuous media*) as part of the human/computer interface is an important direction for computer systems research. There are various ways to incorporate continuous media (CM) in computer systems; in the *integrated* approach, CM data is handled by user-level programs on general-purpose operating systems such as Unix or Mach.

Integrated CM applications handle data at high rates, with strict timing requirements and often in small "chunks". Conventional operating systems support for program execution and local communication may be non-optimal for such applications. In particular, conventional mechanisms for process scheduling and inter address space communication can add significant overhead for some CM programs. *User/kernel interactions*, by which user-level programs invoke system functions, are partly responsible for this overhead.

We describe new mechanisms for process scheduling and CM stream communication between virtual address spaces. These mechanisms, *split-level scheduling* and *memory-mapped streams*, reduce or eliminate user/kernel interactions by using user/kernel shared memory for exchanging scheduling and communication information. We demonstrate that, compared with conventional mechanisms for process scheduling and stream communication, these new mechanisms can reduce overhead by up to a factor of four.

# **ACKNOWLEDGEMENTS**

A number of people have been instrumental in shaping this dissertation and influencing the direction of my career.

To David Anderson, my thesis advisor, I am immeasurably grateful. He has instilled in me a research discipline that, left to myself, I might not have inculcated. His constant emphasis on effective communication has greatly improved my writing and verbal presentation skills. His patience with my sometimes monstrous stupidity and ineptness still continues to baffle me. Those competitive Friday afternoon tennis games helped sharpen my tennis game considerably. Thank you, Dave.

Prof. Domenico Ferrari was responsible for introducing me to the DASH group in my early days as a graduate student. He has been generous with his time whenever I needed advice. His patient and thorough reading of this dissertation also helped improve the quality of the presentation.

Prof. David Wessel has always maintained a great interest in my work with continuous media. His interest in Indian classical music provided a focal point for some interesting discussions.

A number of colleagues have contributed to my intellectual development, either directly with advice or help or indirectly as role models. Among them: Ramon Caceres, Riccardo Gusella, Srinivasan Keshav, Puneet Kumar, Steve Lucco, Mark Moran, Stuart Sechrest, Shin-Yuan Tzou, Dinesh Verma, Robert Wahbe, and Hui Zhang. Members of the ACME group have directly or indirectly contributed to this dissertation: Eric Barr, Pamela Chan, Cindy Hertzer, George Homsy, Yukkei Hui, Yoshi Osawa, and Kyoji Umemura.

I am very deeply indebted to my grandfather S. Lakshminarasimha Sastry and to my mother Indira for the gift of music. Music provided much needed solace during trying times and helped preserve my sanity in this sometimes difficult world.

A number of people have supported and guided me during these years as a graduate student. Ramach Gurumoorthy and Sekhar Raghavan have been kind and caring friends. Sekhar and Ramach, thanks for those long and animated discussions that brightened many an evening. I'll miss those wonderful Sunday evening music sessions with Ramach and Swaminathan Gopalswamy. M. T. Raghunath and I go a long way back; I shall long cherish his wacky sense of humor and his warm personality. Ravikumar Ramachandran and Sridhar Srinivasan, thanks for those great dinners and juicy gossip sessions. Shanthi, my wife of two months, thanks for those lovely letters and phone calls that kept me going for the last year.

Finally, I'd like to thank my parents and my brother whose incredible support from across the oceans kept me going for these years. Without them, this work would not exist.

# **TABLE OF CONTENTS**

| 1. | INTRODUCTION                                                           |

|----|------------------------------------------------------------------------|

|    | 1.1. Motivation                                                        |

|    | 1.2. Thesis Statement and Contributions                                |

|    | 1.3. Thesis Overview                                                   |

| 2. | INTEGRATED CONTINUOUS MEDIA                                            |

|    | 2.1. What is Integrated Continuous Media?                              |

|    | 2.1.1. Hardware and Software Framework                                 |

|    | 2.1.2. The Integrated Continuous Media Framework                       |

|    | 2.2. Requirements of Integrated CM Applications                        |

|    | 2.2.1. Example: The CM File Playback Application                       |

|    | 2.2.2. Example: Audio Teleconferencing                                 |

|    | 2.2.3. Delay and Throughput Requirements of Integrated CM Applications |

|    | 2.3. Survey of Integrated CM Systems                                   |

|    | 2.3.1. End-to-end scheduling                                           |

|    | 2.3.1.1. The CM-Resource Model                                         |

|    | 2.3.1.1.1 Describing CM Workload and Delay1                            |

|    | 2.3.1.1.2. Sessions and Compound Sessions 1                            |

|    | 2.3.1.2. The Producer/Consumer Paradigm1                               |

|    | 2.3.1.3. The Sun Approach1                                             |

|    | 2.3.2. CM Storage 1                                                    |

|    | 2.3.2.1. Structural Issues in CM File Storage1                         |

|    | 2.3.2.2. Real-time Storage and Retrieval of CM files1                  |

|    | 2.3.3. CM I/O                                                          |

|    | 2.3.4. Network Communication                                           |

| 3. | OPERATING SYSTEM SUPPORT FOR INTEGRATED CM APPLICATIONS                |

|    | 3.1. Reexamining OS Policies and Mechanisms                            |

|    | 3.2. Operating Systems Policies1                                       |

|    | 3.2.1. Deadline/Workahead Scheduling1                                  |

|    | 3.3. Operating Systems Mechanisms                                      |

|    | 3.3.1. Mechanisms For Process Scheduling and Stream Communication      |

|    | 3.3.1.1. CM Task Structure Examples1                                   |

|    | 3.3.1.2. Conventional Approaches for Process Scheduling and Message    |

|    | Transfers                                                              |

|    | 3.3.1.3. Domain Switches And Mapping Switches                          |

|    | 3.4. New Mechanisms for Process Scheduling and Stream Communication    |

| 4. | SPLIT-LEVEL SCHEDULING AND SYNCHRONIZATION                             |

|    | 4.1. Overview of Split-Level Scheduling                                |

|    | 4.2. Client Interface to the Split-Level Deadline/Workahead Scheduler | 22 |

|----|-----------------------------------------------------------------------|----|

|    | 4.2.1. LWP Creation and Deletion                                      | 22 |

|    | 4.2.2. LWP State Manipulation                                         | 23 |

|    | 4.2.3. LWP Synchronization                                            | 24 |

|    | 4.3. Implementation of the Split-level Deadline/Workahead Scheduler   | 24 |

|    | 4.3.1. Terminology and Notation                                       | 24 |

|    | 4.3.2. User/Kernel Interface                                          | 25 |

|    | 4.3.2.1. System calls                                                 | 25 |

|    | 4.3.2.2. User-interrupts                                              | 26 |

|    | 4.3.2.3. User/Kernel Shared Memory Interface                          | 27 |

|    | 4.3.3. ULS Implementation                                             | 27 |

|    | 4.3.4. KLS Implementation                                             | 28 |

|    | 4.3.5. Implementing Synchronization                                   | 30 |

|    | 4.3.6. Extensions to Split-Level Scheduling                           | 30 |

|    | 4.3.6.1. Different policy for workahead processes                     | 30 |

|    | 4.3.6.2. Adding support for non-real-time policies                    | 31 |

|    | 4.3.6.3. Different CPU scheduling policy                              | 31 |

|    |                                                                       | 31 |

|    | 4.3.7. UNIX Implementation of SLS                                     | 31 |

| _  | MEMORY-MAPPED STREAMS                                                 | 34 |

| Э. | 5.1. Motivation                                                       | 34 |

|    |                                                                       | 35 |

|    | 5.2. Interface to Memory-Mapped Streams                               |    |

|    | 5.3. Implementation of Memory-Mapped Streams                          | 37 |

|    | 5.3.1. User/Kernel Interface                                          |    |

|    | 5.3.1.1. User-kernel shared memory                                    | 37 |

|    | 5.3.1.2. System Calls and User-interrupts                             | 38 |

|    | 5.3.2. Library Implementation                                         | 39 |

|    | 5.3.3. Kernel Implementation                                          | 41 |

|    | 5.3.4. UNIX implementation of MMS                                     | 41 |

| 6  | SHARED MEMORY CONCURRENCY CONTROL                                     | 44 |

| v. | 6.1. User-mode Critical Section Violations                            | 44 |

|    | 6.2. Preventing User-interrupts During Process-level Execution        | 44 |

|    | 6.3. Concurrency Control Between User-mode and Kernel-mode Execution  | 47 |

|    | 6.3.1. Preemption Masking                                             | 47 |

|    | 6.3.2. Multi-word Reads                                               | 48 |

|    |                                                                       | 48 |

|    | 6.3.3. Multi-word Writes                                              | 49 |

|    | 6.3.4. Read Followed By Related Write                                 | 43 |

| 7. | PERFORMANCE OF SPLIT-LEVEL SCHEDULING AND MEMORY-MAPPED               |    |

| -  | STREAMS                                                               | 51 |

|    | 7.1. Scheduling Paths and Their Costs                                 | 51 |

|    | 7.1.1. Thread Scheduling Path Costs                                   | 52 |

|    | 7.1.2. LWP Scheduling Path Costs                                      | 52 |

|    | 7.1.3. SLS Scheduling Path Costs                                      | 53 |

|    | 7.1.4. Discussion                                                     | 53 |

|    | 7.2 I/O Paths and Their Costs                                         | 53 |

|    | 7.2.1. Read/Write System Call I/O Path Costs | 54 |

|----|----------------------------------------------|----|

|    | 7.2.2. Asynchronous I/O Path Costs           | 54 |

|    | 7.2.3. MMS Path Costs                        | 54 |

|    | 7.2.4. Discussion                            | 55 |

|    | 7.3. Performance Under Synthetic Workloads   | 55 |

|    | 7.3.1. Methodology                           | 56 |

|    | 7.3.2. Simulation Results                    | 56 |

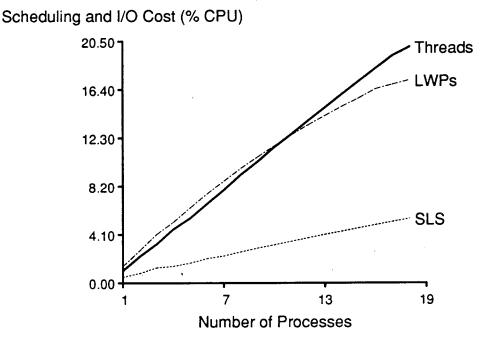

|    | 7.3.2.1. Varying the Number of Processes     | 56 |

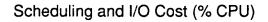

|    | 7.3.2.2. Varying the Message Rate            | 57 |

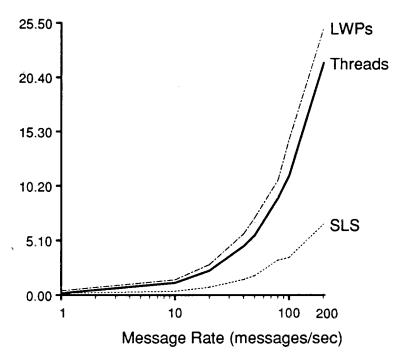

|    | 7.3.3. Varying Process Delay Bounds          | 57 |

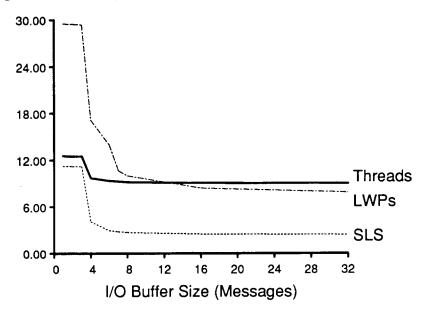

|    | 7.3.4. Varying I/O Buffer Sizes              | 59 |

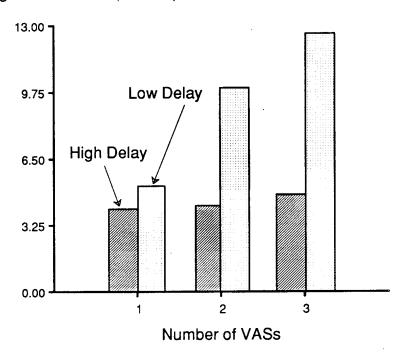

|    | 7.3.5. Varying the Number of VASs            | 60 |

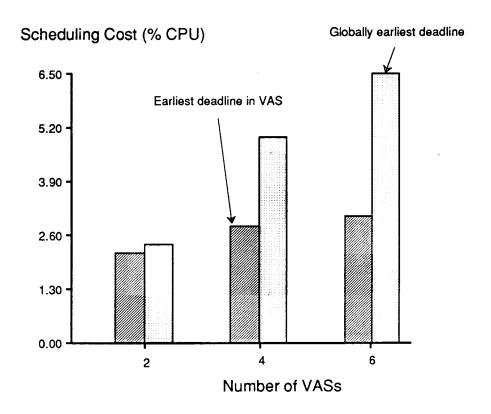

|    | 7.3.6. Varying workahead policy              | 61 |

| 8. | RELATED WORK                                 | 63 |

|    | 8.1. Efficient Process Scheduling            | 63 |

|    | 8.2. Efficient Stream Communication          | 64 |

|    | 8.3. OS Support for CM                       | 64 |

|    | 8.4. Related Trends in Operating Systems     | 65 |

| 9. | CONCLUDING REMARKS                           | 66 |

|    | 9.1. Thesis Contributions                    | 66 |

|    | 9.2. Summary of Results                      | 66 |

|    | 9.3 Future Work                              | 67 |

# **LIST OF FIGURES**

| 1.1. | An integrated CM application                  | 2  |

|------|-----------------------------------------------|----|

| 2.1. | The CM file playback application              | 6  |

| 2.2. | An audio teleconference                       | 8  |

| 2.3. | Different portions of an integrated CM system | 9  |

| 2.4. | Message arrival time and workahead            | 11 |

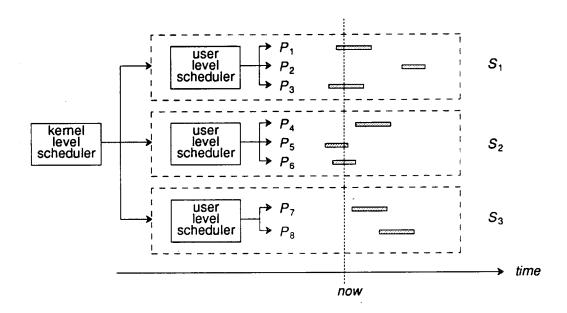

| 3.1. | Deadline/workahead scheduling                 | 17 |

| 3.2. | The ACME server task structure                | 18 |

| 3.3. | The mixer task structure                      | 19 |

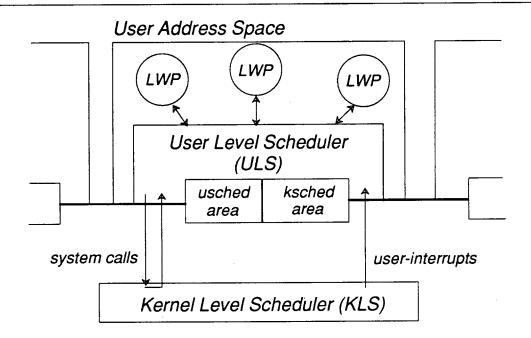

| 4.1. | Split-level scheduling                        | 23 |

| 4.2. | Two parts of a split-level scheduler          | 25 |

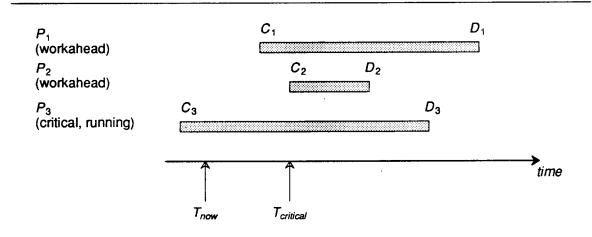

| 4.3. | Illustration for Claim 4.1                    | 28 |

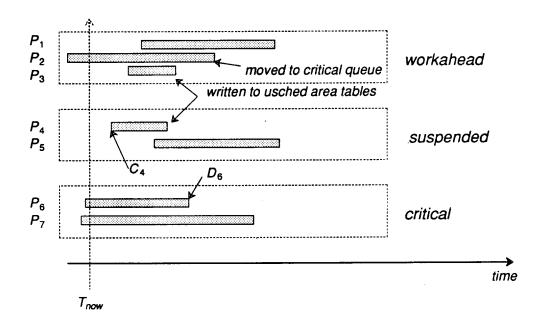

| 4.4. | Illustration for algorithm in Section 4.3.3   | 29 |

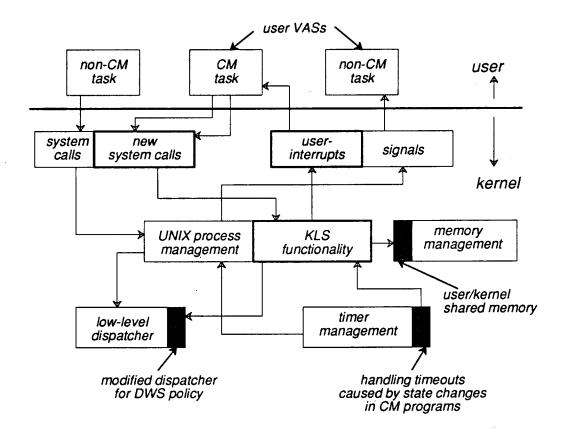

| 4.5. | UNIX implementation of SLS                    | 32 |

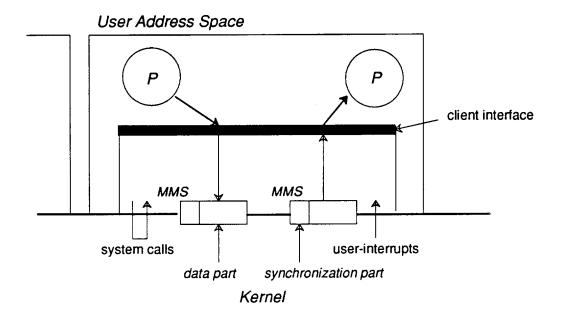

| 5.1. | Memory-mapped stream interfaces               | 35 |

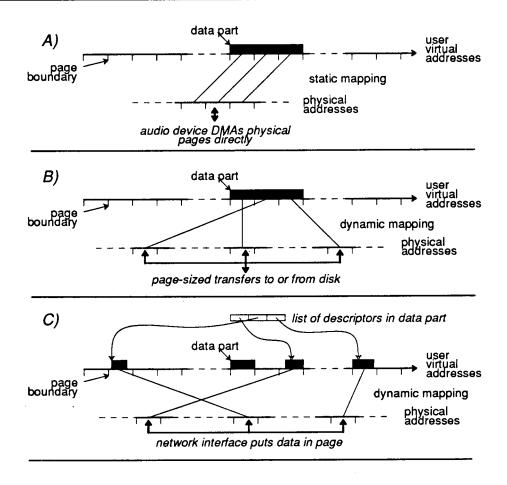

| 5.2. | The MMS data part                             | 39 |

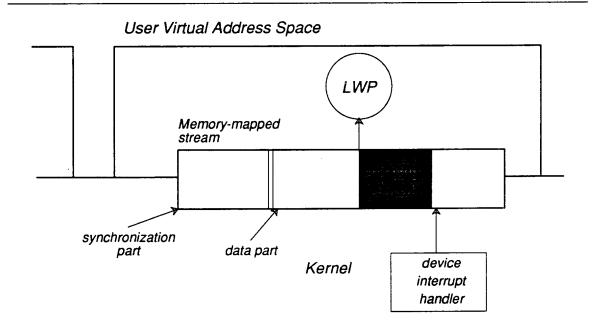

| 5.3. | Illustration of KU stream transfer            | 42 |

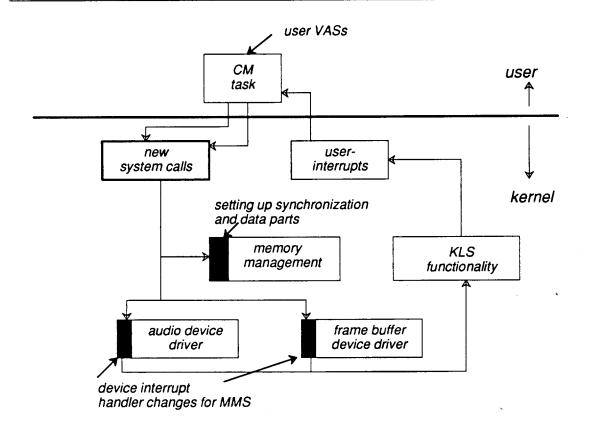

| 5.4. | UNIX Implementation of MMS                    | 43 |

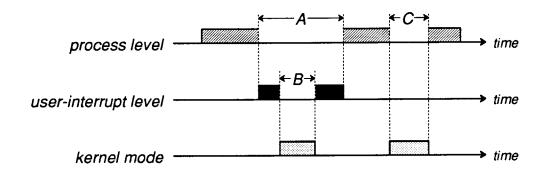

| 6.1. | User-mode critical section violations         | 45 |

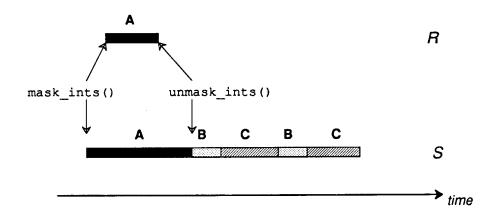

| 6.2. | Virtual user-interrupt masking                | 46 |

| 6.3. | Critical section                              | 47 |

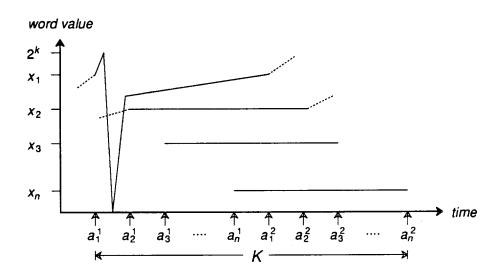

| 6.4. | Multi-word reads                              | 49 |

| 6.5. | Missed I/O notifications                      | 50 |

| 7.1. | Varying the number of processes               | 57 |

| 7.2. | Varying message rate                          | 58 |

| 7.3. | Varying process delay bounds                  | 59 |

| 7.4. | Varying I/O buffer sizes                      | 60 |

| 7.5. | Varying the number of VASs                    | 61 |

| 7.6. | Varying workahead policy                      | 62 |

|      |                                               |    |

# LIST OF TABLES

| 4.1. | Client interface to the split-level scheduler | 24 |

|------|-----------------------------------------------|----|

| 4.2. | User/kernel interface for SLS                 | 26 |

| 5.1. | Client interface to MMSs                      | 37 |

| 5.2. | The MMS user/kernel interface                 | 40 |

| 7.1. | Scheduling path costs                         | 54 |

|      | I/O path costs                                | 55 |

|   |   |   |   | • |   |

|---|---|---|---|---|---|

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   | 6 |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   | • |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

| Ŷ |   |   | • |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   | • |   |   |   |   |

|   |   |   |   |   |   |

|   | • |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   | • |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

# Chapter 1

# INTRODUCTION

The topic of this dissertation is operating systems mechanisms for digital audio and video (continuous media). We consider operating systems (OSs) that provide protected virtual address spaces for user program execution. We argue that mechanisms in these OSs may be non-optimal for user programs that handle CM data (CM programs). In particular, CM programs may incur high overhead when implemented using conventional approaches for process scheduling and CM data transfer between address spaces. We propose new mechanisms for process scheduling and CM data communication and show that they can reduce overhead significantly for CM programs, compared to conventional approaches.

The research area of this work is Operating Systems. It is also related to Multimedia Systems, an emerging discipline which discusses software and hardware issues in supporting diverse media types (still images, animation, digital audio, full-motion video and so on) in computer systems.

The first chapter briefly motivates the dissertation, states its thesis and its contributions, and gives an overview of its structure.

#### 1.1. Motivation

Historically, the addition of new elements to the human/computer interface has necessitated hardware and software changes in computer systems. For instance, the addition of pointer-based interaction required the development of workstations with a bitmapped display and a mouse. Significant additions were needed in terms of software: network-transparent window servers [2, 4] and application-side user-interface toolkits [3] evolved gradually and with considerable discussion. However, this software placed few new requirements on operating systems or networks; it could be layered on existing systems such as MS-DOS and UNIX [1].

The development of CM I/O devices (e.g., digital-to-analog convertors) and the trend towards faster processors and high-speed networks will soon make it feasible to incorporate CM into the human/computer interface in an integrated manner. In an integrated CM system, CM data is handled in the same hardware and software framework as discrete media (such as text and graphics). This framework is characterized by a computing environment distributed on an internetwork of LANs and WANs. Hosts on this internetwork run general-purpose operating systems (such as UNIX or Mach). Applications may communicate discrete media over the network; to support such applications, the software framework has elements like network file servers, network-transparent window systems and so on.

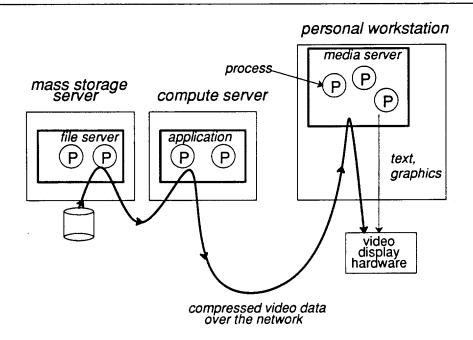

Integrated CM applications (like the video file playback application in Figure 1.1) have real-time requirements that are different from those of discrete media applications. For instance, an integrated CM application may need guaranteed minimum throughput, depending on the data rate of the CM stream that it handles. This requirement can range from tens of Kbps to tens of Mbps. The application may also need a bound on the end-to-end delay of the CM stream (in Figure 1.1, this is the time taken for a chunk of video data to be moved from the disk to the display). The required bound can range from a second down to tens of milliseconds.

While attempting to integrate CM into the human/computer interface, researchers have encountered the following questions. The answers to these questions have required (or will require) changes or additions to the existing discrete media framework.

Figure 1.1. An integrated CM application.

In this application, a video file is retrieved from a file server and transmitted on the network to a compute server. The compute server performs some processing on the video data and then sends it to the media server, which outputs the data on the local display.

- (1) What parametrization of user requirements is general enough (sufficient for a large range of applications) and accurate enough (gives adequate information so that resources can be used efficiently) for CM? Should an integrated CM system attempt to provide performance guarantees to CM applications (the hard real-time approach)? Or, should it only schedule resources intelligently and gracefully degrade when resource limits are reached (a soft real-time approach)? In Figure 1.1, the file traverses different hardware components (the disk, the file server CPU, the network etc.). How do these different components collaborate to ensure that application requirements are met end-to-end?

- (2) CM files are characterized by high display rates and large sizes. What are appropriate disk architectures for storing these large files? What file system data structures permit efficient manipulation (sharing, composition) of CM files? What are good file layout policies and disk head scheduling algorithms for reading CM files from disks at the display rate?

- (3) In the existing discrete media framework, window servers provide network-transparent, concurrent access to I/O devices. What are the appropriate abstractions for accessing CM I/O devices in a similar manner? How should such a media server (Figure 1.1) provide synchronization between different media (e.g., lip synch, video sub-titling)?

- (4) How can existing packet switched networks transport CM data in real time? What are the network issues (e.g., congestion control, routing) that arise in this new framework? What are appropriate transport-level protocols for CM data? How are such protocols efficiently implemented?

(5) In the integrated CM framework, user programs can handle CM data. How can operating systems satisfy the real-time processing requirements of such programs? Are conventional operating systems mechanisms still appropriate for CM programs?

Existing and ongoing work has attempted to answer some of the questions posed in items (1) through (4) (Chapter 2). This work attempts to answer some of the questions raised by item (5).

#### 1.2. Thesis Statement and Contributions

Some CM programs consist of multiple processes. A CM process may communicate CM data with a process in another address space or with the kernel (we call this *CM stream communication*). Our thesis is that conventional mechanisms for process scheduling and stream communication are inefficient for CM programs, and that new techniques can significantly improve performance.

The contribution of this thesis is a new set of efficient mechanisms for process scheduling and stream communication on general-purpose OSs. These new techniques arise from a reevaluation of conventional approaches in light of CM program requirements.

# Conventional approaches to process scheduling:

With conventional approaches, process scheduling is either implemented entirely in the OS kernel or at the user level. The former requires a kernel intervention (e.g., a system call) for each process switch. With the latter, it is not possible to prioritize a process in one address space relative to processes in other address spaces.

## New approach to process scheduling:

This approach splits the functionality of scheduling between user and kernel levels, to simultaneously achieve cheap process switches and global process prioritization. User-kernel shared memory conveys scheduling information between the two levels; this avoids kernel intervention whenever possible.

# Conventional approaches to stream communication:

Stream communication is implemented as a sequence of data transfers between user address spaces or between user and kernel address spaces. Conventional approaches require kernel intervention for each data transfer; that is, each data transfer operation incurs one or more system calls. The kernel interface allows both synchronous (relative to user programs) and asynchronous data transfers.

#### New approach to stream communication:

Stream communication is implemented at the user level using shared memory between the communicating address spaces. Communication is asynchronous relative to user programs and the use of shared memory reduces or eliminates system calls.

This dissertation explores these new approaches, validating the thesis by design, implementation and performance evaluation.

#### 1.3. Thesis Overview

Chapter 2 describes the integrated approach in greater detail. It surveys work in different aspects of designing an integrated framework for CM, sampling research projects to see how they answer some of the questions posed in Section 1.1.

Chapter 3 discusses operating system related issues for an integrated CM framework. It motivates the thesis stated in Section 1.2.

Chapter 4 and Chapter 5 describe the design and implementation of new mechanisms for process scheduling and stream communication respectively. Both these techniques use user/kernel shared memory to communicate information. Chapter 6 describes efficient user/kernel shared memory concurrency control mechanisms.

Chapter 7 presents the results of a series of simulations to study the performance of these mechanisms. It describes CM workload characterization and an experimental study of the effect of different factors on the scheduling and communication costs for CM workloads.

Finally, Chapter 8 presents related work in the area and Chapter 9 offers some concluding remarks.

# Chapter 2

# INTEGRATED CONTINUOUS MEDIA

In this chapter, we describe the *integrated* approach to incorporating CM into computer systems. In this approach, CM data is handled in the same hardware and software framework as other (discrete) data. Section 2.1 lists the properties of an integrated CM system. Section 2.2 discusses the requirements of integrated CM applications. These requirements differ from those of discrete media applications. This difference affects parts of the existing software framework such as network communication, operating systems, and so on. Section 2.3 surveys work on adding CM functionality to these parts.

#### 2.1. What is Integrated Continuous Media?

We first describe our model of the existing framework for handling discrete media data (*e.g.*, text and graphics). We then list desirable properties of an integrated CM framework and compare it with other approaches to incorporating CM.

#### 2.1.1. Hardware and Software Framework

In our model of the existing hardware framework, general-purpose computing is performed on a collection of personal workstations linked by an internetwork of LANs and WANs. The internetwork may also contain other hosts; file servers for storage, gateways for internetwork communication, compute servers for special-purpose processing and so on.

Each host runs a general-purpose operating system (OS) such as UNIX [RiT74] or Mach [ABB86]. In such systems, the OS kernel runs in privileged mode and provides multiple, protected virtual address spaces (VASs) for user program execution. A thread of control in a VAS is called a process. Each VAS may contain one or more processes. The term process does not imply a particular implementation technique; processes may be implemented entirely at the user level or by the kernel. Task denotes an instance of user program execution; a task consists of the VAS in which the program executes, the processes in that VAS and other resources (e.g., port IDs, file descriptors) allocated at runtime to the program.

In our model of the existing software framework, application tasks may reside on different nodes and communicate over the internetwork. A standard protocol suite is used for network communication (e.g., the Internet protocol suite [Tan81]). Network file servers (e.g., NFS [SGK85]) provide distributed data storage and retrieval. Network-transparent window systems (e.g. X11 [ScG86] or NeWS [SSS87]) manage the human/computer interface elements such as the display, the keyboard and the mouse.

# 2.1.2. The Integrated Continuous Media Framework

If the framework described in Section 2.1.1 has the following additional properties, we say that it supports *integrated continuous media*:

- (1) CM data is handled in hardware by primary memory, the I/O subsystem, and networks, and in software by the OS and user programs. DVI [Gre92] is an example of a system that provides this functionality.

- (2) Users can run multiple applications concurrently, with no adverse effects from contention for hardware resources.

- (3) Application tasks can communicate CM data across the network.

(4) The essential elements (e.g., network-transparent window systems, network file access) of the framework described in Section 2.1.1 are used for CM data storage, processing, communication and I/O as well.

Other approaches to incorporating audio and video in computer systems are possible. In one approach, audio and video data is in analog form. However, audio and video storage and communication are under computer control. Examples include VOX [ABL89] and IMAL [LuD87]. In another approach, CM data is in digital form and may be communicated over a digital communication network, but does not pass through the main memory of the computer. Examples include Pandora [Hop90] and the Xerox Etherphone [ZTS89].

In the integrated CM framework, CM data can be manipulated algorithmically in the same way as other data. Relative to these other approaches, an integrated CM system is therefore more flexible and general. Moreover, hardware may be simpler, since no separate disks or networks are required for CM data.

# 2.2. Requirements of Integrated CM Applications

Applications that handle digital audio and video may have stringent real-time requirements. For instance, CM data must be produced, processed, and consumed at fixed rates (up to 40 Mbps for uncompressed full-motion video). To understand the range of real-time requirements (Section 2.2.3) of integrated CM applications, we describe two such applications (Sections 2.2.1 and 2.2.2).

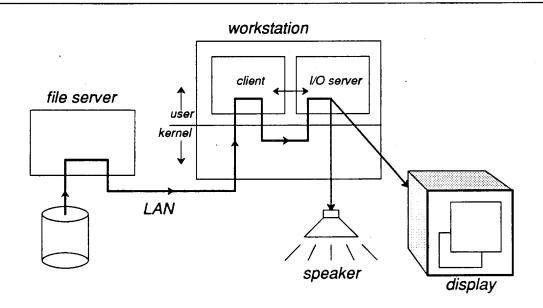

Figure 2.1. The CM file playback application.

This picture shows a program that implements playback of a file containing audio and video data. The program retrieves the file from a network file server, does some processing on the data, and sends the data to a I/O server. The latter outputs the video to the display device and the audio to the speaker.

#### 2.2.1. Example: The CM File Playback Application

Figure 2.1 illustrates an application playing back a file containing a video sequence and its associated audio. An I/O server provides network-transparent, concurrent access to CM output devices (speaker and video display) and to CM input devices (microphone and video camera, not shown). This functionality is similar to that provided by the X11 server for discrete media I/O devices such as the display, the keyboard and the mouse.

A network file server transmits the file as a CM *stream* (a sequence of bytes of CM data) across the LAN. A client of the I/O server may do some processing (*e.g.* audio volume scaling) on the stream. The client task sends the CM stream to the I/O server. The latter separates the audio and video data and sends each component to its respective output device (speaker, display). More generally, the client task may execute on a different workstation from the I/O server.

## 2.2.2. Example: Audio Teleconferencing

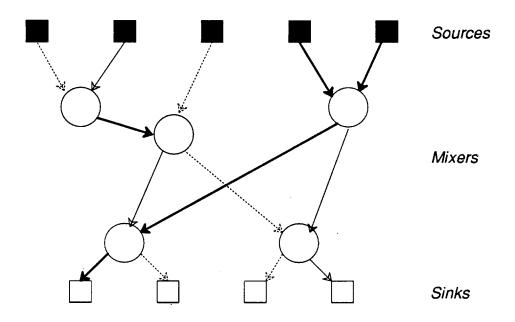

An important class of audio applications enabled by integrated CM is audio teleconferencing. Each participant in a teleconference must hear a sum of the inputs of other participants. The conference may also take input from one or more files; all participants hear file inputs. Similarly, a "transcript" of the conference might be recorded to a file.

In general, a conference has N audio sources and M audio sinks. Each sink receives a linear combination of the sources, with arbitrary volume coefficients. Some common examples of audio teleconferences are:

N = 2, M = 2: a telephone conversation between two people.

N = 1, M = large: a radio broadcast.

N ~ 10, M ~ 100: a panel discussion with an audience.

N~10, M~10: a chamber music rehearsal.

When an audio teleconference is implemented in the integrated CM framework, conference sources and sinks can be either I/O servers or file servers distributed across the network. Other hosts on the network may be used to run a third component of the teleconferencing application, "mixers". A mixer combines audio streams from conference sources or from other mixers and distributes the results to one or more sinks or mixers. Mixers, I/O servers and file servers exchange audio streams over network connections.

There are many digital formats for audio, ranging from telephone quality to hi-fi quality. Source and sinks may be able to generate or accept data in more than one format, and mixers may be able to convert between formats.

Given sources and sinks, the audio teleconferencing application computes a configuration of mixers that satisfies the requirements of the conference. Figure 2.2 shows one such configuration for some sources and sinks.

#### 2.2.3. Delay and Throughput Requirements of Integrated CM Applications

Integrated CM applications may require guaranteed minimum throughput. For example, the file playback application (Section 2.2.1) requires that data be read from the disk file and transferred to the DAC at a minimum average data rate. This rate is determined by the data representation.

The data rates for digital audio can vary from 64 Kbps (for telephone quality audio) to 1.4 Mbps (for 44 KHz stereo CD-quality audio) and 1.536 Mbps (for 48 KHz stereo DAT quality audio) [Wat88]. Uncompressed full-motion NTSC video requires a data rate of 40 Mbps. DVI edit-level video [Gre92] compresses this to about 1.2 Mbps. The MPEG standard [Fox91] for motion video compression achieves a maximum data rate of 1.5 Mbps for NTSC quality video and associated audio. However, analogous future technology for HDTV video may produce data rates in the tens of Mbps.

In the file playback example (Section 2.2.1), the CM stream traverses a number of devices from source to sink (disk, file server CPU, network, client CPU and display). At each of these, the CM stream may incur some queueing and processing delay. We call the cumulative delay from

Figure 2.2. An audio teleconference.

A particular configuration of mixers in an audio teleconference might look like this. Arrows represent network connections carrying audio data. A dashed arrow represents low-quality audio data, a thin arrow medium quality and a solid arrow high quality.

source to sink the end-to-end delay.

Integrated CM applications may also require bounds on the end-to-end delay of the CM stream. Delay requirements depend on the nature of the application. File playback may be able to tolerate delays in the range of 1-2 seconds. However, audio teleconferencing (Section 2.2.2) requires an end-to-end delay in the range of 100-200 milliseconds [Coh78]. For applications such as distributed music rehearsal (a special case of audio teleconferencing), the required delay may be 20 milliseconds or less [Loy85].

# 2.3. Survey of Integrated CM Systems

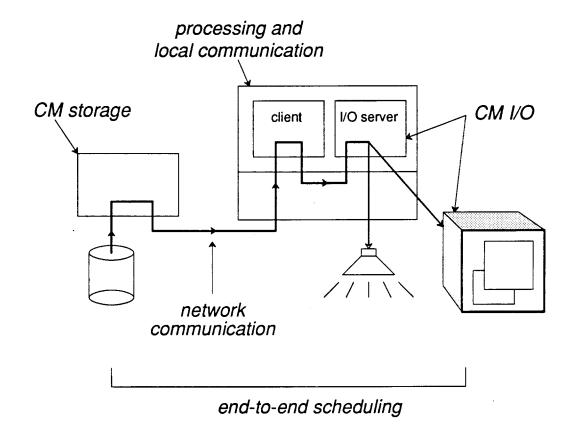

To realize an integrated CM framework, we need to satisfy the four properties described in Section 2.1.2 in the existing discrete media framework. Equivalently, we need to satisfy properties (1) and (4), and satisfy the delay and throughput requirements listed in Section 2.2.3. Figure 2.3 shows portions that should be added to or changed in the existing discrete media framework for this purpose. In this section, we survey existing and ongoing work on: end-to-end scheduling, CM storage, CM I/O, and network communication. The fifth portion, processing and local communication, is the subject of this dissertation and is discussed in subsequent chapters.

#### 2.3.1. End-to-end scheduling

We say that an integrated CM framework solves the *end-to-end scheduling* problem if it can satisfy the throughput and end-to-end delay requirements of integrated CM applications. There are two parts to the problem. The application's requirements must be conveyed to all devices (disks, networks, CPUs and so on) on the path of the CM stream from source to sink. Then, device schedulers must each satisfy the minimum throughput requirement and collectively satisfy the

Figure 2.3. Different portions of an integrated CM system.

Taking the file playback example, we highlight five different portions of the software framework described in Section 2.1.1 that are affected by the need to integrate CM.

end-to-end delay requirement.

One approach to this problem reserves device capacity and "guarantees" that an application's requirements will be met over its lifetime (Sections 2.3.1.1, 2.3.1.2). The approach described in Section 2.3.1.3 does not reserve device capacity, but detects and gracefully degrades from device capacity overload.

#### 2.3.1.1. The CM-Resource Model

To guarantee performance levels for the duration of an application's execution, the shared components, such as CPU, file system, and network, may support "reservations". An application specifies its workload and the component reserves part of its capacity to provide the application with a performance guarantee.

To formalize the reservation of component capacity, a model for expressing workload and processing is needed. In this section, we briefly describe the *CM-Resource model* [And]. In this model, the set of system components that handle CM data is decomposed into a set of *resources*. In general, a resource corresponds to a schedulable hardware device and its accompanying software driver. For example, a CPU and its scheduler might comprise a resource. Resources may also be more complex: a local area network (which includes multiple interface devices,

concurrent operation, and multiple scheduling mechanisms) might be treated as a single resource.

The CM-resource model assumes that work is assigned to resources in discrete units called *messages*, typically representing a segment of CM data. Each message has a well-defined *arrival time* at which it is available for handling by a resource and *completion time* at which the handling is finished.

The flow of CM data consists of linear simplex *streams* of messages that pass through one or more resources. Data is generated by a *source resource* (a disk, digitizer, or compression unit), then processed by a sequence of *handler resources* (networks, CPUs, etc.) and finally consumed by a *sink resource* (disk, decompression unit, etc.). A message's completion time in one resource is its arrival time at the next resource. Many of these simplex data streams may exist concurrently, even within a single application. Therefore this scheme encompasses many CM applications: file playback, audio teleconferencing.

# 2.3.1.1.1. Describing CM Workload and Delay

Each data stream flowing across an interface defines an *arrival process* into the downstream resource. To describe message arrival, the CM-resource model uses *linear bounded arrival processes* (LBAPs). An LBAP has the following parameters:

M = maximum message size (bytes)

R = maximum message rate (messages/second)

W = workahead limit (messages)

that, for all  $t_0 < t_1$ , satisfies  $N_I(t_0, t_1) \le R |t_1 - t_0| + W$ , where  $N_I(t_0, t_1)$  denotes the number of messages arriving at an interface I in the time interval  $[t_0, t_1)$ .

The long-term data rate of an LBAP is MR bytes per second. The parameter W allows short-term violations of this rate constraint, modeling programs and devices that generate "bursts" of messages that would otherwise exceed the constraint. These bursts consist of messages that have arrived "ahead of schedule"; they do *not* reflect burstiness in the underlying data stream. The extent to which arrivals are ahead of schedule is quantified by the *workahead* w(t) of an LBAP, defined as

$$w(t) = \max_{t_0 < t} \left\{ 0, N(t_0, t) - R|t - t_0| \right\}.$$

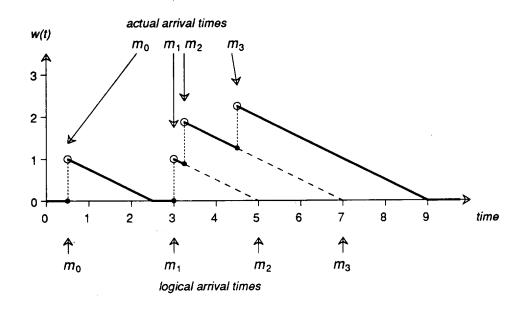

Intuitively, w(t) is the largest "message excess" (relative to R) during any time interval ending at t. More concretely, w(t) is a function that increases by 1 on each message arrival, decreases with slope -R otherwise, and remains nonnegative (see Figure 2.4).

To parameterize the delay between two interfaces in the system, we take workahead into account. For a given LBAP, let  $m_0 \cdots m_n$  denote the sequence of messages, and let  $a_0 \cdots a_n$  denote their arrival times. The *logical arrival time*  $l(m_i)$  of a message  $m_i$  is defined as  $l(m_i) = a_i + w(a_i)/R$  Intuitively, l(m) is the earliest time message m could have arrived if workahead were not allowed (see Figure 2.4; note that the logical arrival times of consecutive messages are separated by at least 1/R.)

We define the *logical delay* d(m) of a message m between two interfaces  $l_1$  and  $l_2$  to be the difference between the logical arrival times of m at those interfaces.

# 2.3.1.1.2. Sessions and Compound Sessions

Prior to using a resource, an application must create a *session* with the resource. Each message handled by a resource is associated with a particular session. A session has the following parameters:

Figure 2.4. Message arrival time and workahead.

The workahead function w(t) for an LBAP with R=0.5 and message arrivals at times 0.5, 3.0, 3.25, and 4.5. The corresponding logical arrival times are 0.5, 3.0, 5.0, and 7.0.

M = maximum message size (bytes)

R = maximum message rate (messages/second)

$W_{in}$  = input workahead limit (messages)

$W_{out}$  = output workahead limit (messages)

D = maximum logical delay (seconds)

A = minimum actual delay (seconds)

The application must ensure that the arrival process at the input interface obeys the LBAP parameters M, R and  $W_{in}$ . The resource must ensure that the arrival process at the output interface obeys the LBAP parameters M, R and  $W_{out}$ . D is an upper bound on the logical delay, between the input and output interfaces of the resource, of any message associated with the session. A is a lower bound on the actual delay.

A session is an agreement between the application and the resource. The resource guarantees that it will obey the delay bounds and the output workahead limit. The application guarantees that it will not exceed the workload parameters.

Each resource has an associated software module that exports three functions:  $\mathtt{reserve}()$ ,  $\mathtt{relax}()$  and  $\mathtt{free}()$ . To establish a session with a resource, the application first calls  $\mathtt{reserve}()$ , giving the session's message size and rate. If the session can be accepted,  $\mathtt{reserve}()$  returns the minimum possible logical delay bound  $D_{\min}$  for the session, and makes a resource reservation sufficient to provide this bound. The application then decides (see below) on a specific delay bound  $\overline{D} \geq D_{\min}$ . It calls  $\mathtt{relax}()$  to alter the existing reservation by changing the delay bound to  $\overline{D}$ . Free() deletes an existing session.

Consider a situation where CM data traverses a linear sequence of resources. For example, in the file playback application of Section 2.2.1, data originates from a disk, traverses a CPU, a network, and another CPU, and is then consumed by the display or the speaker. In the CM-

resource model, such a situation is represented as a "compound session" consisting of sessions with each of the resources involved. A *compound session* S is a sequence of sessions  $S_1 \cdots S_n$  in which the output interface of  $S_i$  is the input interface of  $S_{i+1}$ .

The CM-resource model defines a two-phase protocol for establishing compound sessions. In the first phase, the application calls reserve() at each resource  $S_i$ . Based on an economic approach to end-to-end delay allocation, the application then decides how to divide its target end-to-end delay among the resources  $S_i$ . In the second phase, the application calls relax() at each resource from  $S_n$  to  $S_1$ , giving each resource its share of the delay. Anderson [And] discusses this algorithm in greater detail.

#### 2.3.1.2. The Producer/Consumer Paradigm

Another approach to the end-to-end scheduling problem uses the *real-time* producer/consumer paradigm [JeS90]. A CM application may be modeled as a directed graph in which the vertices represent processes and the edges represent message communication channels. Each channel defines a producer/consumer relation between two processes. The application specifies the minimum rate of messages on the channel.

A pair of interconnected processes adheres to the real-time producer/consumer paradigm if a message produced on the connecting channel is consumed before the next message is sent. In other words, the emission of messages by the producer defines ticks of a discrete time clock; if the paradigm is obeyed, the consumer appears as fast as the producer. Jeffay [Jef] describes a decision procedure for determining whether, for a given set of processes and processing resources, all pairs of interconnecting processes are guaranteed to adhere to the paradigm. The input to the decision procedure includes the worst case message processing time on each channel (the actual delay in Section 2.3.1.1).

This approach has been used in the construction of a desktop audio and video conferencing system on top of a real-time operating system called YARTOS [JSS91]. The kernel provides two basic abstractions: tasks and resources. A task represents a thread of control; a task may need to access one or more resources during its execution. An application workload is specified as a set of tasks and resources. The kernel then guarantees, using the real-time producer/consumer paradigm, that the delay requirements of all tasks are met and that no shared resource is accessed simultaneously by more than one task.

#### 2.3.1.3. The Sun Approach

Sun Microsystems' HRV project [HBJ91] takes a different approach to the end-to-end scheduling problem. In their approach, an application specifies its delay and throughput requirements, but no attempt is made to reserve resources for the application's lifetime. Instead, their approach attempts to satisfy each application's requirements until device capacity overload is encountered. At that point, their resource schedulers negotiate with applications to arrange for graceful degradation from overload.

An application constructs an end-to-end schedulable entity using two abstractions: *transducers* and *conduits* [NoK91]. A transducer is similar to a source or sink resource in Section 2.3.1.1, while a conduit represents a handler resource. An application may compose conduits in serial and in parallel to obtain compound conduits (similar to compound sessions).

Applications specify their delay and throughput requirements in terms of a time interval (T) during which some number of samples (N) are to be transported from source to sink transducers. The operating system and network communication system then attempt to satisfy this requirement using software phase-locked loops. This is a mechanism for time-regulation of conduits which adjusts the rate of transport on the conduit based on an error signal. This signal is generated by comparing the actual number of samples transported in a time interval over the compound conduit with the desired number N.

# 2.3.2. CM Storage

The throughput requirements of integrated CM applications have two implications for CM storage system design. High data rates mean that CM files can occupy significant disk space. File system organization must permit efficient sharing of CM files. Section 2.3.2.1 discusses these structural issues. Moreover, applications may concurrently retrieve multiple files from disk. Section 2.3.2.2 surveys work in real-time storage and retrieval of CM data from disk.

# 2.3.2.1. Structural Issues in CM File Storage

Structural issues for CM files (sharing, parallel composition, annotations, etc.) have been addressed in the Xerox Etherphone system [TeS88], the Sun Multimedia File System [StL89], and the Northwestern Network Sound System [RKD85].

In the Etherphone system, a sequence of continuously recorded video frames or audio samples is called a *strand*. Editing applications may create *ropes*: a rope describes a collection of related strands and how they are synchronized relative to each other. Ropes permit serial or parallel temporal composition of strands. A rope can be implemented without duplicating the constituent strands. A browsing application may annotate a collection of strands; in the Sun Multimedia File System, annotations can be stored as part of a rope.

# 2.3.2.2. Real-time Storage and Retrieval of CM files

In the Continuous Media File System (CMFS) [AOGar], applications may store or retrieve CM files in "sessions". Each session has a guaranteed minimum data rate. Multiple sessions, perhaps with different data rates, may coexist. CMFS also handles non-real-time traffic concurrently with real-time sessions.

Consider a schedule of disk reads that cyclically reads a set of blocks for each session in progress. Such a schedule is *feasible* if the playback time of the blocks read for each session is greater than the worst case time to perform the schedule. The existence of a minimal such schedule that fits the available buffer space is used to test for session acceptance. After a session is accepted, CMFS guarantees an application a minimum data rate for reading the file.

If adequate buffer space is available, CMFS can work ahead (Section 2.3.1.1) on a session. If CMFS has worked ahead on all sessions, it has some "slack time" before which reads for sessions should restart (to avoid session starvation). This slack time is used to service non-real-time disk requests. In the absence of such requests, CMFS uses the available slack time to compute a feasible schedule that adds to session work ahead.

Other work has investigated more restricted versions of the problem. Abbott *et al.* [Abb84] and Park and English [PaE91] address performance issues without guaranteeing minimum data rates. Yu *et al.* [YS89] discuss the layout of interleaved data streams with different data rates on a compact disk for guaranteed-performance playback. Gemmell and Christodoulakis [GeC92] describe a file system supporting multiple audio channel playback with concurrent non-real-time traffic. The channels must have the same (constant) data rate and must start at the same time. Finally, Rangan and Vin [RaV91] describe a system that combines disk input and display-device output for multiple data streams. They study admission control under the assumption that sessions have equal data rates.

#### 2.3.3. CM I/O

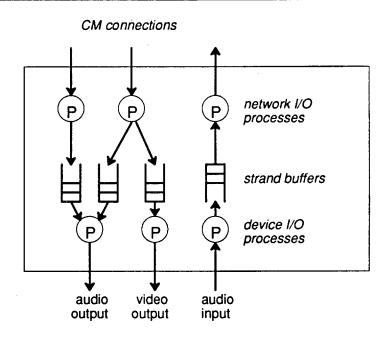

In the existing discrete media framework, window systems like X11 and NeWS provide network-transparent, concurrent access to discrete media I/O devices. Property (4) of the integrated CM framework (Section 2.1.2) implies that it is desirable to access CM I/O devices as well in a network-transparent, concurrent manner. Examples of work in this area include ACME [AGH91], the DEC Audio Server [AHL91], and MuX [RBK92].

The ACME client-server protocol is based on the following abstractions:

Ropes, Strands, and CM Connections: A strand is a stream of audio or video data encoded in a byte stream. Each strand has a type representing the encoding scheme. Multiple strands (say, an audio and a video stream) may be interleaved in a byte-stream rope

- (different from the rope described in Section 2.3.2); the interleaving scheme defines the type of the rope. A *CM connection* is network connection used to convey a strand or rope.

- Logical Devices: A logical device (LDev) is an abstract CM I/O device. There are four types of LDevs: VWins (video output), VCams (video input), listeners (audio input), and players (audio output). LDevs have various attributes according to their type; for example, a VWin has the attributes of a graphics window: position, size, and stacking order. Clients can map LDevs to physical I/O devices. Multiple LDevs may be mapped to a single physical device; in the case of players, the server is responsible for "mixing" the respective outputs. The LDevs associated with the strands of a rope are grouped into a compound logical device (CLDev).

- Logical Time Systems: LDevs and CLDevs can be associated with a logical time system (LTS). All strands in an LTS are played (or generated) in synchrony, even if they come from different sources. The ACME server ensures that the strands start playing at the same time and remain in lockstep. The client may also start, stop, or alter the speed of an LTS, affecting the component strands uniformly.

The DEC Audio Server defines abstractions similar to CM connections, LDevs and CLDevs. Synchronization is performed using command queues associated with the CLDev; a command specifies a particular operation on an LDev or CLDev. Queues allow for sequential processing of commands without client-server round-trip communication. The server also maintains a client-addressable name space of audio clips; it stores and retrieves these directly from the storage device.

MuX is an extension to the X11 window system to support network-transparent, concurrent CM I/O. In addition to strands, ropes, CM connections, logical devices and logical time systems, MuX also provides the *sequence* abstraction. A *sequence* is a time-line description that allows parallel and serial composition of CM and discrete media I/O activity.

#### 2.3.4. Network Communication

In the framework described in Section 2.1.1, applications communicate over the network using a standard protocol suite. Property (4) of an integrated CM framework implies that it is desirable to modify the Internet suite of protocols for CM data communication across networks. This section briefly reviews some work in this area.

SRP [AHS90] is a resource reservation protocol for guaranteed-performance communication on the Internet. Using the CM-resource model as the basis for reserving network resources (network interfaces, gateways etc.), SRP sets up a compound session associated with the connection of a particular IP-based protocol (e.g., a TCP connection). Data sent on this connection is then transmitted according to the throughput and delay requirements of the compound session.

The Tenet real-time protocol suite [BaM91] is a connection-oriented suite of network and transport protocols for real-time wide area communication. The Tenet approach provides for the establishment of *real-time channels* that guarantee minimum throughput and bounded network delay. The basis for resource reservation is similar to the CM-Resource Model; the traffic parametrization is different.

The Stream Protocol (ST) is an internet layer connection-oriented protocol for real-time conferencing applications. ST allows higher level protocols to set up *streams* [Top90]. A stream is a multi-way connection spanning all participants of a conference. Applications specify stream characteristics such as average and burst throughput, round-trip delay, delay variance and error rate. Gateways and networks select multicast routes and perform network resource allocation. Streams may be modified by addition or deletion of endpoints or by network failures.

# Chapter 3

# OPERATING SYSTEM SUPPORT FOR INTEGRATED CM APPLICATIONS

This chapter discusses how integrated CM affects the "processing and local communication" portion of the existing discrete media framework (Figure 2.3). Property (2) of an integrated CM framework requires that users be able to run multiple CM applications concurrently. Therefore, multiple CM tasks (tasks whose processes handle CM data) may execute concurrently on a workstation. For example, Figure 2.1 shows a client task and an I/O server task executing on the same workstation. These tasks may also communicate CM streams between user VASs or between user and kernel VASs. In Figure 2.1, the client task sends a CM stream to the I/O server and the latter writes two streams to the kernel.

Section 3.1 motivates reexamination of OS **policies** and **mechanisms** for integrated CM. Section 3.2 argues that CPU scheduling policies in general-purpose OSs may be non-optimal for scheduling CM tasks. It describes *deadline/workahead scheduling*, a CPU scheduling policy designed for CM. Section 3.3 argues that conventional mechanisms for process scheduling and inter-VAS stream communication can add significant overhead to CM task execution. This motivates the design of new process scheduling and stream communication mechanisms, the subject of this dissertation.

# 3.1. Reexamining OS Policies and Mechanisms

General-purpose operating systems incorporate design principles that are contrary to the needs of integrated CM application processing and communication:

- The request/reply paradigm (the basis of centralized systems as well as RPC-based and object-oriented distributed systems) may be non-optimal for stream-oriented CM communication.

- Assumptions about delay tolerance of data accesses leads to the use of buffering and large messages. These can add queueing or packetization delay to CM processing.

- Scheduling policies in current systems have the goals of fairness, maximum system throughput, and fast interactive response. CM applications have real-time requirements that may conflict with these goals.

- Communication protocols may provide reliable data transport. Some CM applications can tolerate unreliable delivery of CM data.

These principles impact the design of policies and mechanisms in these general-purpose OSs. These policies and mechanisms may need to be reexamined in light of the real-time requirements of integrated CM applications.

#### 3.2. Operating Systems Policies

Anderson's solution [And] to the end-to-end scheduling problem (Section 2.3.1.1) divides an application's end-to-end delay among the different system components that handle CM data. One such component is a CM task (e.g., the client task in Figure 2.1). Within a CM task, it is convenient to handle separate CM streams in separate processes; the CPU scheduler can then schedule each process according to its throughput and delay requirements.

Most CPU scheduling policies in general-purpose OSs do not allow applications to "reserve" CPU capacity. CPU overload may occur; such overload can violate the throughput requirements

of CM processes. Most OSs lack mechanisms for overload detection and graceful degradation.

Even if CPU capacity reservation were supported, CPU scheduling policies in general-purpose OSs could still be non-optimal for CM process scheduling. Most such policies use the following criteria: 1) fast response for interactive processes, 2) high throughput for background processes and 3) fairness. For instance, the round-robin policy is often used to satisfy fairness. Thus, the UNIX time-slicing policy [LMK89] assigns processes to one of many different priority levels; at a given level, processes are scheduled round robin.

One or more of the above criteria may be contrary to CM process delay requirements. Suppose we are given a set of CM processes, each with its delay and throughput requirements. Suppose further that there exists a scheduling policy which will satisfy these requirements (*i.e.*, the set of processes is *schedulable*). Results in real-time systems show that policies which use preemption on quantum expiration (*i.e.*, use round-robin scheduling) may reduce the schedulability of such a set of processes (*i.e.*, may not be able to satisfy its real-time requirements) [LiL73, TNR90].

#### 3.2.1. Deadline/Workahead Scheduling

The deadline/workahead CPU scheduling (DWS) policy is designed for CM tasks [And]. Each CM task has one or more processes. In DWS, processes are classified as either real-time or non-real-time. There are two classes of non-real-time processes: interactive (those requiring fast response) and background (those requiring high throughput).

CM tasks reserve sessions (Section 2.3.1.1) with the CPU scheduler's resource manager. We assume that for each session S there is a real-time process  $P_S$  that does all the work for S, and no other work.  $P_S$  handles a sequence of messages arriving asynchronously (say, on a network connection), and sleeps whenever no messages are available. The input interface for S is defined by message arrivals; in the case of a network connection, a message arrival occurs when the network interface requests a receive interrupt. Message completion occurs when  $P_S$  makes a call indicating that it has handled the packet; this call either changes the priority of  $P_S$  or puts it to sleep if there are no more messages.

The delay bound of a real-time process is the delay bound of its associated session. The deadline of a message is the sum of its logical arrival time (Section 2.3.1.1) and the delay bound of the process handling that message. At any instant, a real-time process may have one or more unprocessed messages. The critical time of a real-time process is the earliest logical arrival time among all unprocessed messages. The deadline of a real-time process is the earliest deadline among all unprocessed messages. At a given time t, a real-time process is called critical if it has an unprocessed message m with  $l(m) \le t$  (i.e., m's logical arrival time has passed). Real-time processes that have pending work but are not critical are called workahead processes. A workahead process becomes critical when its critical time equals the current time.

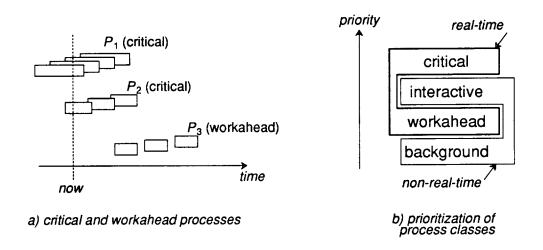

The DWS policy can be summarized as follows (Figure 3.1). Critical processes have priority over all others, and are preemptively scheduled according to earliest deadline. Interactive processes have priority over workahead processes, but are preempted when those processes become critical. Background processes have lowest priority.

Non-real-time processes are scheduled according to an unspecified policy, such as the UNIX time-slicing policy. This policy may also move a process between interactive and background. The policy for workahead processes is also unspecified. One possible policy chooses a workahead process P, perhaps with the earliest deadline or the most work available. P is then run for a full quantum (say, 100 times the system call plus context switch time) even if its deadline advances beyond that of another workahead process. Such a policy is designed to reduce context switch overhead.

The DWS policy is appropriate for CM process scheduling for a number of reasons. It supports CPU capacity reservation; this can prevent CPU overload and "guarantee" process throughput requirements. For any set of schedulable processes whose delay bound is equal to the message interarrival time, the earliest-deadline policy can meet each process' delay bound; DWS uses earliest-deadline scheduling as a heuristic to improve the schedulability of CM workloads. The DWS policy includes timeliness as a criterion for real-time processes; CM processes may express their throughput and delay requirements in terms of message deadlines. DWS also

Figure 3.1. Deadline/workahead scheduling.

In the deadline/workahead scheduling (DWS) policy, each real-time process has a queue of pending messages. In example a), each message is shown as a rectangle whose left edge is its *logical arrival time* and whose right edge is its *deadline*.  $P_1$  and  $P_2$  are *critical* because they have a pending message whose logical arrival time is in the past. Processes are prioritized as shown in b). Critical processes are executed earliest deadline first; policies for other classes are unspecified.

allows processing of messages that have arrived before their logical arrival time; CPU schedulers may efficiently schedule workahead processes (see the policy above), for example, to reduce context switch overhead.

# 3.3. Operating Systems Mechanisms

Section 3.1 suggests reexamining OS mechanisms for integrated CM applications. These mechanisms may add processing overhead to CM tasks. This can happen when functionality is inappropriately partitioned across protection domains. For instance, if process scheduling is implemented in the OS kernel, every process switch requires kernel intervention. Real-time processes in DWS change their deadlines at every message completion (Section 3.2.1); each such deadline change incurs kernel trap overhead.

Section 3.3.1 argues that process scheduling and inter-VAS CM stream communication mechanisms can add significant processing overhead to integrated CM. Recent work demonstrates that this overhead is not decreasing in proportion to increasing processor speeds.

# 3.3.1. Mechanisms For Process Scheduling and Stream Communication

In DWS (Section 3.2.1), each real-time process handles a sequence of CM messages. After handling a message, the process changes its deadline (a scheduling operation). CM tasks may communicate CM streams between user VASs or between a user VAS and a kernel VAS. Inter-VAS CM stream communication can be decomposed into a series of CM message transfer operations.

Section 3.3.1.1 describes the process structure of two CM tasks, and illustrates how these tasks may perform frequent process scheduling and message transfer operations. Section 3.3.1.2 lists two conventional approaches for process scheduling and message transfer. Section 3.3.1.3

argues that CM tasks may incur high overhead when implemented using these approaches.

## 3.3.1.1. CM Task Structure Examples

Figure 3.2 shows the real-time processes in a typical ACME (Section 2.3.3) server task. This task has two types of real-time processes: network I/O and device I/O processes. Network I/O processes perform I/O to and from CM connections. A network output process reads a block of messages from a CM connection and writes it to an internal strand buffer. Before writing the data it may process it in some way; for example, it may do volume scaling of audio streams or split a rope into its constituent strands. Device I/O processes perform I/O to and from CM devices. A device output process gathers data from one or more strand buffers, perhaps combines them (e.g., by summing audio samples), and writes them to the device. A device input process reads data from the device and writes a copy to the internal buffer, to be read later by a network input process.

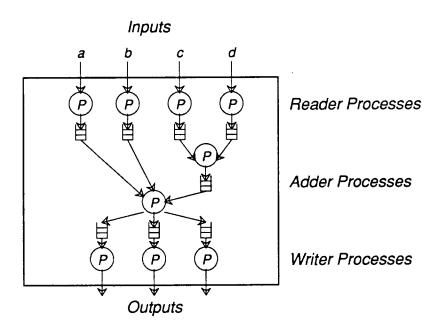

Figure 3.3 shows the real-time process structure of the mixer task (Section 2.2.2). Each mixer task has three kinds of real-time processes. *Reader* processes copy data from input network connections to memory buffers. They may do some processing (*e.g.*, type conversion) on the stream. *Adder* processes read data from one or more buffers, do the mixing, and write the results to other buffers. *Writer* processes copy data from buffers to the output CM connections. They may also perform some mixing or format conversion.

The rationale for the process structures of these tasks is as follows. Streams on different CM connections may tolerate different delays and different workahead limits; for instance, stream

Figure 3.2. The ACME server task structure.

The ACME server is structured as a set of LWPs. Network I/O processes perform message transfers from CM connections and may do some processing on the message. Device I/O processes perform message transfers to CM I/O devices.

c (Figure 3.3) may be an input from a file and stream b may be from a live participant. Assigning one process to each network connection (e.g., reader or writer processes in the mixer and network I/O processes in ACME) enables the CPU scheduler to differentiate between streams with different delay bounds and workahead limits. For a similar reason, each I/O device in ACME is assigned one process. A similar argument can be made for having multiple adder processes in the mixer task. Suppose streams c and d (Figure 3.3) are input from a file but a and b are input from live participants. The reader tasks of c and d can work ahead on their streams. If both reader tasks have worked ahead, then it is beneficial to work ahead on mixing those streams also. For that reason we assign an adder process to mixing c and d.

Each real-time process in ACME and the mixer performs at least one scheduling operation per CM message. A real-time process may also perform one inter-VAS message transfer per message. For example, the network output process does a kernel to user message transfer on message arrival and changes its deadline on message completion. A writer process does a user to kernel message transfer and a deadline change on message completion. An adder process does a deadline change on message completion.

If the number of processes is high (e.g., the number of concurrent CM streams is high), then the frequency of process scheduling and message transfer operations is high. This frequency is high for CM tasks handling low end-to-end delay CM streams. Such streams tend to have high message rates; one hundred messages/sec represents a packetization delay alone of 10 ms.

Figure 3.3. The mixer task structure.

Real-time processes in a mixer are of three types: reader, writer and adder. The reader and writer processes perform I/O from network connections to sources or sinks. The adder processes perform the intermediate steps of the mixing computation.

# 3.3.1.2. Conventional Approaches for Process Scheduling and Message Transfers

In existing general-purpose OSs, tasks use one of two conventional mechanisms for process scheduling and message transfer.

- Threads and read/write system calls: A thread is a kernel-implemented process. The kernel exports a system call interface for thread management and maintains thread execution state. Thread switching is done completely within the kernel. Threads perform message transfers using system calls. In Mach, for example, a thread calls send\_msg() for a user-to-user message transfer.

- Lightweight processes (LWPs) and asynchronous message transfer: LWPs are implemented entirely at the user level. A library implements LWP creation, deletion, state manipulation and switching. A blocking system call (e.g., on an I/O operation) by a LWP suspends all activity in the VAS. To avoid that, LWPs use a kernel interface that provides asynchronous, non-blocking message transfers. The QIO facility in the VMS operating system provides such an interface [LeE89]. With such an interface, a message transfer typically involves a system call to initiate the transfer followed by an asynchronous event (e.g., a UNIX signal [LMK89]) to signal transfer completion.

When implemented using these approaches, CM tasks may incur the overhead of user/kernel interactions (by which user programs access system functions for process scheduling and message transfer). User/kernel interactions are of two types: synchronous (with respect to user programs) user-to-kernel system calls and kernel-to-user asynchronous events. Each user/kernel interaction incurs one or more domain switches. A domain switch is defined as a crossing of the user/kernel protection boundary; a system call involves two domain switches and a UNIX signal three (one for a kernel upcall to user space to execute the signal handler and two for a signal return system call that resets signal masks). A user/kernel interaction may also incur a mapping switch between different user VASs.

With these conventional approaches, a single scheduling or message transfer operation may incur more than one user/kernel interaction. For example, an asynchronous kernel-to-user message transfer in UNIX may incur up to nine domain switches and two mapping switches. A non-blocking read() system call returns immediately if no messages are pending. A SIGIO signal is delivered when a message arrives. The select() system call chooses the file descriptor on which the message has arrived and another read() does the actual transfer.

## 3.3.1.3. Domain Switches And Mapping Switches

Domain switches are expensive relative to procedure calls. A null system call (which incurs two domain switches) takes about 34 µsecs on SunOS 4.1 for the SPARCstation 1+. There are two components to system call overhead: the kernel trap and preparing the processor to execute a procedure call to a higher-level language OS routine. This latter call preparation involves vectoring from trap entry point to the appropriate exception handler, managing machine state (e.g., machine registers and kernel stack pointers) and saving/restoring registers used during the call.

A system call has indirect costs as well. Because a system call involves a cross-domain interaction, the system call handler must copy and check parameters to guard against application errors. Moreover, inter-procedural optimizations (e.g., avoiding register saves/restores) are difficult for system calls [Kar89]. Finally, kernel execution during a system call may incur more cache and TLB misses than user-level execution. Agarwal et al. [AHH88] show that caches perform poorly for OS memory references for two reasons: 1) OS code and data structures are larger than user code and data structures; they occupy more cache space and bringing the working sets into the cache needs more cache misses and 2) OS code loops have fewer iterations than user code loops. Clark and Emer [CIE85] argue that TLBs perform poorly for similar reasons.

With architectural trends towards RISC processors, system call costs have not decreased in proportion to increasing processor speeds [ALB89]. RISC processors such as the Sun SPARC [CCC90] and the MIPS R2000 [Kan87] have more than 64 registers, so call preparation costs are greater. Moreover, RISC processors have added new features, such as the register windows in SPARC, that reduce kernel trap performance. In SPARC, the hardware ensures that one register window is available for the trap handler on exceptions. This handler has to ensure that another

window is available for the system call handler (to avoid recursive window overflow traps). This requires possibly saving (and later restoring) user register windows, and additional copying of system call parameters.

User VAS mapping switches are also expensive. In SunOS 4.1 for the SPARCstation 1+, the cost of suspending one UNIX process and switching to another is about 140 µsecs.

The direct cost of a mapping switch is the time taken to change the current processor memory map. However, a mapping switch has a significant indirect cost component. A mapping switch results in a change in program locality; the indirect cost is the cost of repopulating cache and TLB contents in this new locality. Depending on the cache parameters, this cost may be in the tens or hundreds of microseconds [MoB89].

The indirect costs of mapping switches are not decreasing in proportion to increasing processor speeds [MoB89]. Processor speeds are improving, but memory access times have not been increasing proportionately. Thus, cache-miss penalties are becoming relatively greater.

#### 3.4. New Mechanisms for Process Scheduling and Stream Communication

The previous section makes the following arguments:

- (1) Some CM tasks may perform frequent process scheduling and message transfer operations.

- (2) With conventional approaches, each process scheduling or message transfer operation may incur one or more user/kernel interactions. A user/kernel interaction requires at least one domain switch and possibly a mapping switch.

- (3) Domain switches and mapping switches are expensive. The cost of these components does not seem to be decreasing with increases in processor speeds.

This dissertation argues that new process scheduling and inter-VAS stream communication mechanisms can significantly reduce overhead (up to a factor of four) for some CM application workloads. These new mechanisms are:

- Split-level scheduling and synchronization. In this approach each user VAS contains multiple lightweight processes (LWPs). The scheduler is partitioned into user-level and kernel-level parts, which communicate via shared memory. The information in shared memory is used to correctly prioritize LWPs in different VASs and to minimize user/kernel interactions.