Copyright © 1993, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### AN APPLICATION OF A SYNCHRONOUS/REACTIVE SEMANTICS TO THE VHDL LANGUAGE

.

by

Wendell Craig Baker

Memorandum No. UCB/ERL M93/10

29 January 1993

### AN APPLICATION OF A SYNCHRONOUS/REACTIVE SEMANTICS TO THE VHDL LANGUAGE

by

Wendell Craig Baker

Memorandum No. UCB/ERL M93/10

29 January 1993

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### Acknowledgments

I am indebted to my research advisor, Professor Richard Newton, for his encouragement and support throughout the course of this work. I am also grateful to Professors Susan Graham and Bob Brayton and Kathy Yelick for the interest they have shown in this project.

This work is supported by the Semiconductor Research Corporation under contract 91-DC-008. Their support is gratefully acknowledged. Additional support was provided by Digital Equipment Corporation through their support of the CAD Group's DECstation-based computing environment.

I thank Cygnus Support Inc. for their work over the past two years maintaining the GNU C++ 2.0 compiler and debugger and porting that system to the DECstation. I also thank the Microelectronics and Computer Technology Corporation (MCC) for the use of their VHDL simulator during the course of this work. I also thank Gérard Berry of INRIA and Hervé Touati of DEC PRL for the use of the Esterel V.3 compiler system.

All of the members of the Berkeley CAD Group, past and present, have helped me in various ways during my tenure here; in particular Gregg Whitcomb, Paul Gutwin, and Dr. Rick McGeer. I thank Jim Rowson and David Ku of Redwood Design Automation for the many discussions that we have had.

Above all I would like to thank my wife, Mary Baker for her patience and support during this project.

#### Abstract

The goal of this project was to define and demonstrate a subset of the VHDL language [IEEE87] which is *consistent with the simulation semantics* and yet has an *interpretation as a specification*. The subset shown in this work incorporates as much of the language as is possible without compromising its interpretation as a specification of system behavior. There is no other subset of the VHDL language which can incorporate more of the semantics of the language, yet retain an interpretation as a specification.

To show why this is the larges subset of the VHDL language which has this property, a review of some of the many uses of VHDL is given along with an explanation of why the interpretation of the full VHDL language as a specification within this context is problematic at best. A definition of what it means to interpret an executable description as a specification is given in the form of an example of an existing class of languages, *the reactive languages*, which have this property: being executable yet having an interpretation as a specification. The question then is whether there is a useful subset of the VHDL language that can be shown to be reactive. In fact, within the wide range of uses of VHDL, there is a class of uses that can be interpreted as a reactive specification. The identification of this class of uses, and the restrictions on the language structure that accompany it form the basis of the subset definition.

Reactive systems, or equivalently synchronous systems, have the property that they respond to events from the environment in which they reside; nothing of interest outside these events and their responses occurs in these systems. The formulation of the definition of reactive systems in terms of events allows for a succinct description of their behaviors as *regular expressions*. Hence the implementation of a reactive system is naturally in terms of one of the many finite automata which recognizes the regular language that defines the system's behavior. The goal of the subset definition then is to identify the reactive portion of the VHDL language, independent of its language structures, so that the behavior of programs written in the subset may be interpreted as regular expressions, and implemented in terms of (communicating) finite automata.

The Synchronous VHDL subset presented here is derived through a restriction on the abstract simulator that defines the meaning of a VHDL program. The focus here is on restricting the simulator behavior and using that restriction to drive the definition of the VHDL subset, instead of the other way around as has been traditional in the definition of other VHDL language subsets. The result of this work is a description of the subset of the VHDL language that uses only finite-automata-like behavior; it thus has well-defined implementation as a network of communicating finite state machines.

In addition to the definition of Synchronous VHDL, a goal of this project was to demonstrate the subset in use. Thus, a major portion of this project was the implementation of a compiler front-end which is used to analyze VHDL source text, converting from the syntax of the language into a form suitable for compilation into a reactive language.

# Table Of Contents

.

| 1 | In  | troduction                                                                                                                                                                                                                   | 1                                   |

|---|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 2 | 2.1 | ne VHDL Problem<br>Policies of Use<br>The Breadth of VHDL Description<br>The Nature of Parallelism<br>2.3.1 Asynchronous Parallelism<br>2.3.2 Synchronous Parallelism<br>Language Interpreters versus Program Specifications | 5<br>6<br>9<br>19<br>20<br>20<br>21 |

| 3 | Sy  | 25                                                                                                                                                                                                                           |                                     |

|   | 3.1 | Overview of the Language                                                                                                                                                                                                     | 25                                  |

|   | 3.2 | Core Language Constructs                                                                                                                                                                                                     | . 26                                |

|   |     | 3.2.1 An Example - A Mouse Handler                                                                                                                                                                                           | 28                                  |

|   | 3.3 | Interpretation and Specification                                                                                                                                                                                             | 29                                  |

|   |     | 3.3.1 The Interpretation of Esterel                                                                                                                                                                                          | 29                                  |

|   | 21  | 3.3.2 The Compilation of Esterel                                                                                                                                                                                             | 30                                  |

|   | 3.4 | Implications for VHDL                                                                                                                                                                                                        | 31                                  |

| 4 | Th  | ne Synchronous VHDL Subset                                                                                                                                                                                                   | 35                                  |

|   |     | Implications of the Restrictions                                                                                                                                                                                             | 36                                  |

|   | 4.2 | Implications on the Syntax                                                                                                                                                                                                   | 37                                  |

|   |     | 4.2.1 Restriction 1 - Time Queues of Length One                                                                                                                                                                              | 37                                  |

|   |     | <ul><li>4.2.2 Restriction 2 - No Runtime Stack</li><li>4.2.3 Restriction 3 - No Heap Storage</li></ul>                                                                                                                       | 39<br>42                            |

|   |     | 4.2.3 Restriction 5 - No Heap Storage<br>4.2.4 Other Restrictions                                                                                                                                                            | 42                                  |

|   |     | 4.2.5 Summary                                                                                                                                                                                                                | 42                                  |

|   | 4.3 | VHDL to Esterel                                                                                                                                                                                                              | 43                                  |

|   |     | 4.3.1 Syntactic Correspondences                                                                                                                                                                                              | 44                                  |

| 5 | Α   | 49                                                                                                                                                                                                                           |                                     |

|   | 5.1 | Synchronous VHDL Simulator<br>Simulator Architecture                                                                                                                                                                         | 49                                  |

|   | 5.2 | Abstract Machine Architecture                                                                                                                                                                                                | 51                                  |

|   |     | 5.2.1 The Abstract Architecture                                                                                                                                                                                              | 51                                  |

|   |     | 5.2.2 Describing Systems                                                                                                                                                                                                     | 52                                  |

|   |     | 5.2.3 The NDAM Process                                                                                                                                                                                                       | 52                                  |

|   | 5.3 | Translation of Imperative Processes To Finite Automata                                                                                                                                                                       | 55                                  |

|   | 5.4 | Lessons Learned                                                                                                                                                                                                              | 57                                  |

|   |     | 5.4.1 VHDL Event versus VHDL Transaction<br>5.4.2 The Flat versus Nested Process Models                                                                                                                                      | 57<br>58                            |

|   |     | 2.7.2 IIV I ICL VISUS I WORK I I VUESS IVIUEIS                                                                                                                                                                               | 00                                  |

|            | 5.4.3 The Subtleties in the -Time Models | 58 |

|------------|------------------------------------------|----|

| 6          | Conclusions                              | 61 |

| References |                                          | 63 |

| Α          | The Key-Chain Example                    | 65 |

| B          | The Synchronous VHDL Subset              | 67 |

•

# **Chapter 1**

## Introduction

The 1980s saw the introduction of VHDL as a standard hardware description language for producing simulation models of existing hardware components. The original purpose of VHDL was to provide a standard language in which the behavior of electronic devices procured under U.S. Department of Defense programs could be encoded. The language designer's goal was allow the seller to transmit a description of the part to the purchaser along with the part so that a definite idea of its behavior would be imparted. In addition to describing behavior, the description was to act as a specification for the part so that another one could be built in the future; to build a second copy, one must know what the first copy did.

Coupled with other developments such as an increased use of logic-level synthesis, larger designs being attempted, and more complicated designs which require better testing, the use of VHDL changed from being purely a *descriptive* language to one which is now being applied in far more varied ways. These areas range across testing, specification, netlist representation and even into device-level simulation and analog simulation! For this project, the interest in VHDL is solely in the area of *specification*; system-level specification for use in high-level and sequential-level synthesis.

It would be tempting to ignore these other areas to concentrate on VHDL as specification but unfortunately these other application areas of VHDL impinge upon its use as a specification language. Both the simulator origins of the language and the subsequent reinterpretation of it to apply it to new uses impose difficulties for the sound definition of VHDL as a specification for computing hardware. A sound definition of specification is a precondition for defining a synthesis path from VHDL to sequential-level or logic-level synthesis.<sup>1</sup>

#### The Theses of This Work

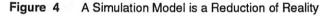

The thesis being investigated in this project is whether or not it is possible to define a subset of VHDL which is both consistent with the simulation semantics described in its 1987 definition [IEEE87] and which also has an interpretation as a specification of hardware. The interpretation as a specification is given by the restriction of the VHDL simulator behaviors to those behaviors allowable under the synchronous system hypothesis. The consistency of the subset with the full simulation semantics is guaranteed by defining the language subset based on a restriction of the simulator model and deriving the effects on the language.

The validity of this thesis implies that it is possible to define the meaning of a VHDL program in this subset in a rigorous way; the meaning is as a specification for a network of communicating finite state machines. The computations of this network, its states and its state transitions, will be exactly the same as those of any correct VHDL simulator. Thus this subset of VHDL can be used as an input for both sequential optimization and synthesis and also it can be checked for correctness by automata-theoretic or temporal-logic based verification tools such as such as COSPAN [HK90] and [CJLM91].

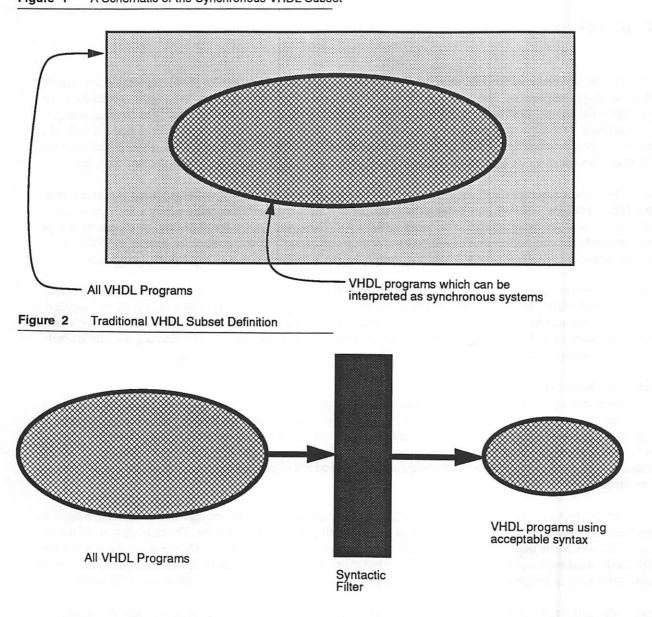

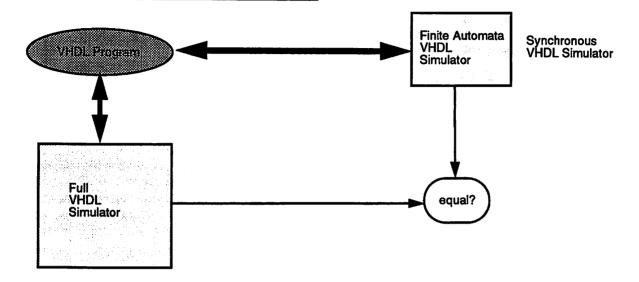

A schematic of the desired VHDL subset is shown in Figure 1. Depicted there, as a subset of all possible VHDL programs, is the synchronous subset. This subset is defined, not by the set of syntactic constructs allowable in the subset, but by the behavior of the simulator on those programs. The subset is defined by the behavior of the simulator, which implies restrictions on the syntax, not the other way around as has been traditionally done. Figure 2 and Figure 3 illustrate this distinction. A major point underpinning the synchronous subset is that this subset, while defined through the dynamic pro-

An Application of a Synchronous/Reactive Semantics to the VHDL Language

<sup>1.</sup> Exactly the same can be said for Cadence Design System's Verilog language [Ver91], save for its history and origins. As the capabilities of VHDL are a strict superset of those in Verilog, the work here applies equally to well to each language; Verilog will not be mentioned further.

cess of simulation, can actually be identified in a static analysis of program text; it is possible to determine whether a VHDL program obeys synchronous semantics at compile time. **Figure 1** A Schematic of the Synchronous VHDL Subset

#### Long- and Short-Range Goals

Ultimately the goal of this work is to define the synthesis semantics of VHDL in a rigorous way. That being done, the effect of such a rigorous definition will show up elsewhere in the chain of tools that consume design descriptions. In addition to synthesis applications there are also verification aspects to design which are current areas of research. Providing a standard front-end language to those tools is also a goal of this work. Further, though, a consistent semantics of VHDL as finite automata will have affects in the design of simulators for VHDL; surely a simulator which used a network of communicating finite state machines would be simpler to partition and parallelize than a simulator which was fashioned as prescribed in the definition of the VHDL language [IEEE87]<sup>2</sup> (*c.f.* [Vel90]).

Figure 3 Synchronous VHDL Subset Definition

Despite these far-reaching goals, the focus here is on a far more tractable problem: using the proposed synchronous semantics of VHDL to define a translation path from VHDL to an executable format (*e.g.* to C code). This translation path defines a simple simulator, thus forming a proof of concept both for the soundness of the synchronous subset of VHDL and for the idea of using reactive compilation to define the specification aspect of this subset of VHDL.

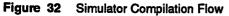

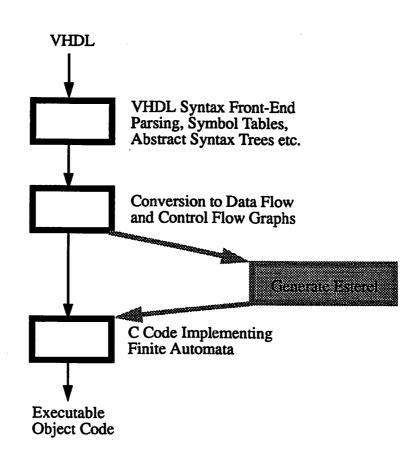

Attempting to produce a system that performs both the identification of the synchronous subset of VHDL and the translation to the final executable form required too great an effort for a simple proof of concept study such as this one. Instead, the approach taken for this work was to break that job up into two parts: the construction of a compiler front-end for the VHDL language, and the use of that front-end to convert VHDL source text into a form which can be conveniently compiled by a reactive language compiler. The reactive language used is Esterel [CIS88], and thus this report describes the design of a translation path from VHDL into Esterel and thus to a final executable form in  $C^3$ . The main body of the report describes the design and definition of Synchronous VHDL, leaving to the appendices the documentation of the salient facts about the C++ compiler front-end for VHDL that was developed to support this work.

#### Overview

The goal of this work is to demonstrate the feasibility of constructing the translation path. The description here is simply that of a proof of concept study. The simulator described here is in no sense yet a product, though the hope is that the technique described here for using reactive compilation to implement certain classes of simulation models is powerful enough that one day it may lead to a product-quality approach.

The ideas described in this report have been given form in the development of a toolkit of compiler algorithms, which have been written in C++. Because the construction of a complete VHDL simulator is a rather gargantuan task, it has not been possible to produce a full VHDL simulator implementation within the scope of this project. Instead, what this work represents is a study of the issues involved in developing such a simulator. Thus only those aspects of the simulator which are directly related to the use of the reactive semantics as an implementation method for simulator models has been imple-

An Application of a Synchronous/Reactive Semantics to the VHDL Language

<sup>2.</sup> The description of the required simulator event processing loop, as found in Chapter 12 of [IEEE87], is reproduced in Appendix B.

<sup>3.</sup> Again, it must be stressed that the use of the Esterel compiler in this work is merely a convenience; a stand-alone reactive compilation algorithm would allow for its replacement.

mented. A good portion of the implementation which is not germane to the use of reactive compilation has been forgone. The C++ compiler toolkit which was implemented for this study is described in the presentations of Chapter 4 and Chapter 5. The hope is that with this work as the basis, a more extensive investigation of the use of reactive compilation techniques can be attempted. Based on the investigation done here, those techniques hold the promise of enabling improvements in a number of application areas ranging from embedded software applications to discrete-event simulators as is the case here.

There are a number of problems involved in defining the translation path proposed here over and above the simple development of a relationship between a VHDL subset and Esterel. The first of these is to motivate why a sound definition of a translation path from VHDL to *any* other representation of computation is problematic; this is the subject of Chapter 2.<sup>4</sup> The properties of reactive/synchronous languages with emphasis on the Esterel language is described in Chapter 3. That chapter provides some background on Esterel's semantics - both the interpretation semantics and the compilation semantics. The synchronous subset of VHDL which is motivated by the translation of VHDL processes into Esterel is presented in Chapter 4. A simple VHDL simulator for the Synchronous VHDL subset which uses the reactive language compilation capability of the Esterel compiler as a code generator is presented in Chapter 5. Finally, a review of the conclusions which can be drawn from the project described in this report is given in Chapter 6.

<sup>4.</sup> For the purposes of this report it is assumed that the reader is familiar with VHDL. The overview presented in the next chapter is not a general presentation of the language, rather it focuses on the issues involved in interpreting VHDL models as synchronous specifications. Readers unfamiliar with VHDL may wish to see [LSU89], [IEEE87], [Coe89] or [ALG+91].

## Chapter 2

## **The VHDL Problem**

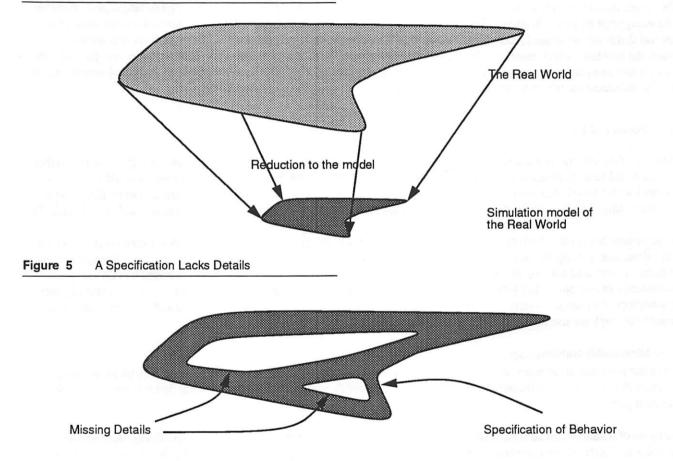

Expanding the interpretation of VHDL descriptions away from simulation is problematic because simulation models are *descriptive* and the reduction relationship from reality to the modeling domain is held largely in the mind of the observer. The differences between simulation models and specifications is shown schematically in Figure 4 and Figure 5. The purpose of this chapter is to motivate why attempting to find a sound definition of a VHDL subset that can be interpreted as a specification is hard.

The difficulties in subset definition fall into roughly four categories which can be summarized in the following way:

- A syntax-directed policy of use for the language is insufficient; this is addressed in Section 2.1.

- The *inexact focus* of the level of VHDL description makes interpretation at any *specific level* for specification problematic. This issue is addressed in Section 2.2.

An Application of a Synchronous/Reactive Semantics to the VHDL Language

- The asynchronous nature of parallelism in VHDL models is difficult to work with in simulation models and extremely difficult to interpret as a specification. This and the simplification to synchronous parallelism being used here are described further in Section 2.3.

- The VHDL simulator loop and the sequential code execution rules introduce an *interpreter bias* into the use of VHDL for specification. Interpreter bias, the problems that it causes and the use of the synchronous system paradigm as an attempt to solve them are described in Section 2.4.

Qualifying the difficulty of the problem is important so that the reader can better understand that all of the mechanism and formality introduced in the later sections are necessary to achieve these ends. This proposal is for a semantics-driven policy which defines a VHDL subset that achieves the end of an interpretation for specification that covers as much of the VHDL language as possible while still preserving the observable simulation behavior of the VHDL models.

This interpretation is not necessarily the easiest to implement nor is it the simplest subset policy ever devised<sup>5</sup>. The claim is however, that this policy is the most *complete* in the sense that it allows for as much of the VHDL language as possible to be interpreted as a specification of behavior. This is a very difficult claim to prove in the traditional formal sense of lemmas and theorems, so instead a convincing argument of this completeness is presented. The purpose of this section is to review the problems which must be solved to define the notion of VHDL as a specification. Thus, this section provides the basis for that convincing argument - that the synchronous interpretation of VHDL as described in Chapter 4 is both necessary and sufficient for use as a specification of behavior.

#### 2.1 Policies of Use

One of the first objections which arises in a semantics-modification proposal which is as invasive as is this one is whether or not it could have been achieved with fewer restrictions or whether a result which was *good enough* could have been achieved with a simple but mathematically inelegant set of restrictions on the language. In an attempt to head off those arguments, this section is devoted to a description of the options for a VHDL policy in the traditional style (*c.f.* Figure 2).

The argument here is that each of these possibilities save for one, the synchronous subset which is based on the behavior of the simulator directly, is insufficient or incomplete in some important way. It is important to remember throughout, that the purpose here is to investigate the possible ways that a most-general subset for specification might be derived. The insufficiency of any one of the following attempts on the problem does not indicate that it *cannot* be used; certainly there are a number of synthesis systems which use each one. The point is that there is a more general and more elegant solution available through the use of the Synchronous VHDL subset.

#### Using Identifiable Sublanguage

One of the more common restrictions to impose is that the VHDL description be restricted to use only an identifiable sublanguage. A common one is the dataflow portion of VHDL; another is a restriction to structural descriptions from a library of known parts.

Examples of dataflow and structural subsets of VHDL are shown in Figure 6 and Figure 7 respectively. Both of these examples are fairly straightforward as they are combinational examples; they contain no feedback and no internal state.<sup>6</sup>

<sup>5.</sup> A quick look through the relevant literature on VHDL-based high-level synthesis systems confirms this [CBH+91] [Che91] [HCD90] [LiGa89] [RoVe89] [UdVe89].

<sup>6.</sup> The processes in VHDL do have internal state in the signal drivers; that state is being ignored for these examples.

When the examples use data types which are more complex than  $Bit^7$  or when the flow dependencies in the models are not acyclic, then the interpretation of the meanings of the architectures as specifications becomes unclear.

Figure 6 An Example of the Dataflow Sublanguage of VHDL

```

entity Some_Function is

port(A, B, C, D: in Bit; Ol, O2: out Bit);

end Some_Function;

architecture Dataflow of Some_Function is

begin

O1 <= (A and B) or (C and D);

O2 <= (A nor B) nand (C nor D);

end Dataflow;

```

Figure 7 An Example of the Structural Sublanguage of VHDL

```

entity Some Other_Function is

port(A, B, C, D: in Bit; O1, O2: out Bit);

end Some Other Function;

use Lib.Specification Parts.all;

architecture Structural of Some Function is

signal Tmp1, Tmp2, Tmp3, Tmp4: Bit;

begin

Ul: and2

port map(I1 \Rightarrow A, I2 \Rightarrow B, O \Rightarrow Tmp1);

U2: and2

port map(I1 => C, I2 => D, O => Tmp2);

U3: or2

port map(I1 => Tmp1, I2 => Tmp2, 0 => 01);

U4: nor2

port map(I1 => A, I2 => B, O => Tmp3);

U5: nand2

port map(I1 => C, I2 => D, O => Tmp4);

U6: nand2

port map(I1 => Tmp1, I2 => Tmp2, 0 => 02);

end Structural;

```

Somehow it would be more satisfying if the interpretations of Figure 6 and Figure 7 as specifications were derived from the behavior of the simulator rather than an intuitive understanding of what is written in English. Such a specification would be more sound in general and could also trivially take into account the redefinition of the **and**, **or**, **nand** and **or**

.

<sup>7.</sup> The **Bit** data type is not predefined in VHDL; rather, it is a data type which is required to be available in the standard library by the declaration: type Bit is ('0', '1');

operators. It is rare for a user to redefine these operators on the **Bit** type, but quite common to do it for other data types. The mechanics of the treatment of a VHDL specification subset should be robust under such redefinitions.

#### **Using Structural Patterns**

Another treatment of VHDL for specification involves using a known structure of the syntax to imply a specification. For example, in Figure 8 a pattern of usage is indicated which will ultimately be interpreted as a clocked latch by the tool that interprets the specification - the synthesis system.<sup>8</sup>

Figure 8 An Example of a Pattern of Usage

```

entity A Latched Function is

port(A, B, C, D: in Bit;

CLK, RST: in Boolean;

O: out Bit);

end A_Latched Function;

architecture Pattern Match of Some Function is

signal Tmp_O: Bit bus;

begin

Reset:

block(RST = FALSE)

begin

Tmp 0 <= guarded `0';</pre>

end block Reset;

Func:

block(not Clock'stable and Clock = True and RST)

begin

Tmp_0 \leq guarded (A and B) or (C and D);

end block Func;

0 \le \text{Tmp } 0;

end Pattern Match;

```

It may take more than a moment of reflection to determine the behavior of the two guarded blocks operating in tandem driving a local signal of kind **bus** which is ultimately fed to the output. In fact, the simulator does quite a bit of work to simulate these three constructs, so it is not surprising that the pattern is hard to recognize as a clocked latch with a reset without some *gedanken* experiments on the abstract VHDL simulator.

This style of description is convenient, however complicated it may seem, for the tool writers for the "synthesis system" need only recognize the three patterns: two guarded blocks driving the same bus signal and a third concurrent assignment feeding the result out. This pattern can be used as a specification for a query into "the library" in which there will be just such a clocked latch. The right-hand side of the **Func** block is taken as the specification of the logic function to be computed and stored in the clocked latch.

The important point of this very structured use of VHDL is that it represents an extension to the language. The patterns which are recognized by the synthesis tools, though defined completely within the syntax of the language standard, repre-

8. This style of specification in VHDL is in daily use at a major electronics company.

sent idioms which are imbued with meanings defined outside of the language standard. Thus the use of a style or policy of use VHDL ultimately represents a change in the language to suit a specific tool implementation or design library. As this style of specification is so implementation-specific and depends so much on the modeler's interpretation of the meaning of the cooperation between the two blocks (**Reset** and **Func** in the figure) it will not be considered further here. It is introduced here because this style of specification with VHDL is in fact used and is considered acceptable *as a specification* to those who use it - it allows them to get designs done.

#### "... Well, Then We Won't Support That"

Finally, there is the common method building a VHDL policy for synthesis specification which is completely *ad hoc*. Essentially the procedure used is to start with a small subset of VHDL, such as the dataflow subset described above, and grow by iteratively adding one more construct to the subset until it becomes difficult or impossible to support the new addition. On the positive side, this method does tend to keep constructs out of the resulting subset which are obviously incongruous: pointers and files and the like.

The problem with this method, as with the other syntax-directed policies is that there is no unifying principle with which to accept or reject constructs from the subset language. The process of selection tends to devolve into attempting to map a VHDL statement's perceived meaning onto the target tool and if that cannot be done, then "... well, we won't support that."

#### **Restricting the Simulator**

Developing a policy for VHDL that can be interpreted as a specification which is based on restricting the syntax that will be supported sounds easy and attractive. Its appeal lies in the ability to use the grammatical structure of the language, as defined in Appendix A of [IEEE87], as an aid to the categorization and elimination of statements or constructs which are considered too difficult to use. This unfortunately has serious effects on both the breadth of the language which can be supported and the interpretation of that language after the allowed subset is identified.

After the allowed subset is identified from a review of the language definition there is no guarantee about *what* the review process generated in terms of a subset (how much of the language is supported). Further, there is no set of rules for determining the meaning of the constructs in the subset after selection and ensuring that the specification meaning is the same as the simulation meaning. This problem arises from the procedure used to accept or deny support for the various statements; it is based on what is known to be supported in some target tool.

What is being searched for in an interpretation of VHDL as a specification is exactly backwards from the syntax-directed case: there is no tool yet, so the goal is to find a subset of VHDL that specifies computing structures *such that* a tool can be built which will derive an implementation for that specification. The presentation of that subset and the identification of a tool, a VHDL-to-Esterel translator and its use as a simulator generator is the subject of Chapter 4 and Chapter 5.

#### 2.2 The Breadth of VHDL Description

VHDL is a large language as many have noted. It is surprising just how large it is however when one considers not only the languages structures involved, but also the various interpretations or policies with which its users mold the language to suit various needs. These needs are outlined in the following sections; they range from describing test benches to black box models to pure netlists and on into more exotic areas where VHDL was never intended to be applied.

In this section is exhibited the breadth of use to which VHDL can be put in order to frame the uses to which the specification interpretation of VHDL will be made. These areas are not the areas to which VHDL is *best* put to use necessarily, but they are areas where it can be demonstrated that VHDL *is currently being* put to use. It is important to understand this breadth in order to provide the proper context for the presentation of the very constrained usages required of the synchronous subset of VHDL. The desire is to motivate here is that the range of uses of VHDL are driven by needs for design description and management which are outside the scope of this project. They are driven by a need for a language-driven design framework which uses a common language across all levels of design ranging from high-level specification to testing to low-level modeling of semiconductor behaviors. This goal may or may not be a desirable one to achieve. It is however being actively pursued and as will be shown in the following sections, it has a large effect on how well and how much of VHDL can be interpreted as a specification.

The important point of this section is that from a specification viewpoint, there is no way to tell these various uses apart: a test bench in VHDL looks remarkably like a switch-level model of a CMOS circuit - from the perspective of an automated tool which consumes VHDL specifications. Typically it is only the identifier names used in the models which distinguish them (*i.e.* names like **test\_bench** or **and3** or **nfet**). An automated tool cannot be expected to extract and comprehend this intended use. It is thus critical that the user be able to identify these uses and disallow their submission as specifications in the first place; this is a "well we just won't let users do that" situation. A taxonomy of VHDL is provided in this sectoin so that when users are told that they can't use a certain class of VHDL as a specification, then they can have a name for that class and a reason for the claimed inappropriateness as a specification.

#### **Test Bench Construction**

The test bench is where the full power of the VHDL language is most useful. In most design situations, it is up to the designer of the model to provide a rig to test out the device model. Instead of letting that task be provided in an implementation-dependent manner, the VHDL language designers have allowed VHDL itself to serve that function. In fact, there are standards for test benches written in VHDL such as the WAVES standard [WAV90] and the BSDL on-board test structures [PO90]. These test bench standards describe test structures ranging among the vector formats in files, the procedures to apply test patterns, files that they will read and write and the in-device test structures required for the methodology.

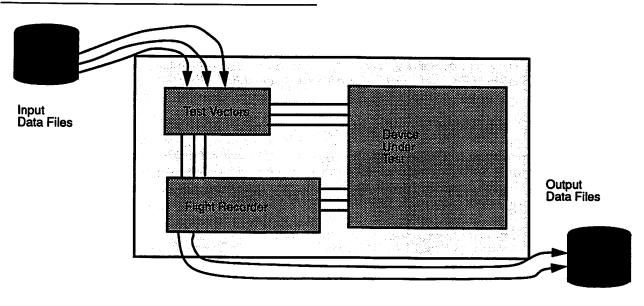

The test bench is simply a VHDL entity and architecture which instantiates the *device under test* (DUT) and applies test vectors and records the results. A schematic of this is shown in Figure 9. Some simulators provide this facility directly for simple models; however for complex models like processors or controllers, it is typically advisable to build a flight recorder and test vector application unit. This way the full power of VHDL can be used to filter the events being input to and emanating from the DUT and record only the interesting ones.

A test bench for the traffic light controller is shown in Figure 10.9 Although this test bench does not contain all of the parts which are shown in Figure 9, it does contain the essential aspects which are: the test bench is autonomous, it does not have any ports connecting *it* to anything, the test bench instantiates some component, and it applies test vectors to that component and records the results of those tests. In Chapter 3 these conditions are shown to imply that a test bench is not a reactive component and cannot not have an interpretation as a specification.

Figure 10 A Test Bench for the Traffic Light Controller

```

entity TLC Test is

end TLC Test;

use Work.Traffic Package.all;

architecture Test of TLC_Test is

signal Car On Farm Road: Boolean := FALSE;

signal Highway: Color := Green;

signal Farmroad: Color := Red;

component TLC

generic(Long Time: Time; Short Time: Time);

port (Car On Farmroad: Boolean in Boolean;

Highway: Light: out Color;

Farmroad: Light: out Color);

end component;

begin

Controller: TLC

generic map (5 ns, 2 ns)

port map(Car_On_Farm_Road, Highway, Farmroad);

Car on Farm Road <= FALSE,

TRUE after 1 ns,

FALSE after 3 ns,

TRUE after 10 ns,

FALSE after 20 ns;

end Test;

use Work.all;

configuration spec of TLC_TEST is

for Test

for Controller: TLC

use entity Work.Traffic_Light_Controller(Specification);

end for;

end for;

end spec;

```

#### **Black-Box Modeling**

The essential idea behind a black box model is that it doesn't matter how the part is described so long as it simulates the correct responses. In fact, there is a retail market for models of processor blocks, controllers and other large blocks. These

<sup>9.</sup> This example is taken from [LSU89], pages 186-188.

models are used *in* other models such as models of boards or backplanes to ensure that the complete design works correctly with the part.

What is considered to be behavioral or black-box modeling is shown in Figure 11.<sup>10</sup> The idea is that all which is important about an entity is its simulation behavior *as perceived by the outside world*. So, in this respect it is irrelevant whether the description in the architecture is given by a complete cover for the boolean function as is the case in Figure 11 or by a chain of interrelated processes.

Figure 11 A Black Box Description

```

entity Decoder is

port(Enable: in Bit;

Sel: Bit Vector(2 downto 0);

Dout: out Bit Vector(7 downto 0));

constant Delay: Time := 5 ns;

end Decoder;

architecture Selected of Decoder is

type vec8x8 is array(integer range 0 to 7) of bit_vector(0 to 7);

constant one hot: vec8x8 := (

"00000001", "00000010", "00000100", "00001000",

"00010000", "00100000", "01000000", "10000000");

function cvt(bv: in bit vector(2 downto 0)) return integer is

variable sum: integer := 0;

begin

if bv(0) = 1' then

sum := sum + 1;

end if;

if bv(1) = '1' then

sum := sum + 2;

end if;

if bv(2) = 1' then

sum := sum + 4;

end if;

return sum;

end cvt;

begin

with Sel select

Dout <= one_hot(cvt(Sel));</pre>

end Selected;

```

Some synthesis systems accept this type of description as a specification because it is interpreted as specifying combinational logic only. That interpretation is due to the use of the dataflow with construct in the main body of the architecture.

<sup>10.</sup> This example is taken from [LSU89], page 100.

The with construct need not indicate combinational logic, especially in the presence of feedback or if the after clauses are not all the same.

Typically though black box models are written with simulation efficiency in mind as they are to be used *inside* of other models as leaf nodes. As such, black box models are typically not considered as specifications. They could be considered as such though if the consuming tool were powerful enough to disambiguate the specification of behavior from the typically hyper-efficient coding of function at the behavioral level of VHDL.

#### **Behavioral Specification**

This is the level of description that is typically considered the most interesting use of VHDL for synthesis or verification. The designs are written to be clear and expository, as opposed to being efficiently executable in a compiled-code simulator. For example, contrast the two styles of description for the same decoder in Figure 11 and Figure 12; one is clearly going to be faster to simulate in a compiled-code environment than the other.

Figure 12 A Specification of the Decoder

```

entity Decoder is

port(Enable: in Bit;

Sel: Bit Vector(2 downto 0);

Dout: out Bit Vector(7 downto 0));

end Decoder;

architecture Selected of Decoder is

begin

with Sel select

Dout <= "00000001" when "000",

"00000010" when "001",

"00000100" when "010",

"00001000" when "011",

"00010000" when "100",

"00100000" when "101",

"01000000" when "110",

"10000000" when "111";

end Selected

```

While both could be treated as specifications, it is more natural to consider the description in Figure 12 as a specification and Figure 11 as a description. There is more to this than a simple intuitive notion of what is declarative and what is efficiently executable. The notion of interpreter bias, which is described in more detail in Section 2.4 clarifies this by codifying the effect of the operational model with which a description is given meaning on the interpretation of the description as a specification. Interpreter bias is the effect of a specification being forced to look like an interpreter for the programming language due to undesired corner conditions in the operational model.

In this example, the interpreter bias would predispose the specification of Figure 11 to *look like* a simulator with a stack for the function call and some memory for the constants and variable. It would take a very fancy set of analyses to determine that the design of Figure 12 was the true intent of the specification. Maybe these sorts of analyses for VHDL-style languages will exist some day; for now however, they don't and so it is useful to draw a distinction between efficiently-executable black-box models and expository specification models in VHDL.

#### **Netlist Declaration**

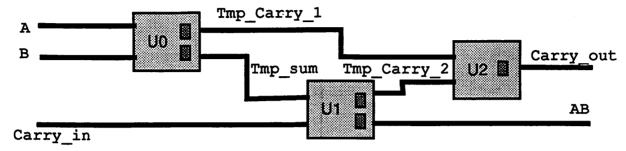

This sort of VHDL description is simply the assembly of pre-existing parts. It is not terribly important or interesting but it is brought up here because it is a *specification* in the pure sense; a netlist is a partial specification for the placement and routing portion of the design process (the remaining items being composed of information describing constraints and estimates of resistances, capacitances, areas, delays and so forth). An example of netlist-based description is shown in Figure 13.<sup>11</sup> These descriptions are pure structural description and amount to only a *very* fancy netlist format.

Figure 13 An Example of Netlist-Based Description

```

entity Full adder is

port (A: in Bit; B: in Bit;

Carry in: in Bit;

AB: out Bit;

Carry out: out Bit);

end Full adder;

architecture Structure of Full adder is

signal Temp sum: bit;

signal Temp_carry_1: bit;

signal Temp carry 2: bit;

component Half adder

port(X: in Bit; Y: in Bit;

Sum: out Bit;

Carry: out Bit);

end component;

component Or_gate

port(In1: in Bit: In2: in Bit;

Out1: out Bit);

end component;

begin

U0: Half_adder

port map (X \Rightarrow A, Y \Rightarrow B,

Sum => Temp_sum, Carry => Temp_carry_1);

U1: Half_adder

port map(X => Temp sum, Y => C,

Sum => AB, Carry => Temp carry 2);

U2: Or gate

port map(In1 => Temp_carry_1, In2 => Temp carry 2,

Out1 => Carry out);

end Structure;

```

#### Switch-Level Modeling

VHDL is a modeling language and one common problem in electronic design automation is the need to model the behavior of a digital circuit at the transistor level, viewing the circuit as a network of switches. In this case, an attempt is made to approximate the continuous phenomenon of transistor operating-point behavior with a discrete approximation: that of a bidirectional switch. When the switch-level circuit modeling problem is cast within the discrete-event framework a further

<sup>11.</sup> This example is taken from [LSU89], pages 20-21.

approximation must be made as the discrete-event paradigm is a unidirectional one, events propagate unidirectionally down wires, whereas the switch-level model is bidirectional as switches can carry information both forwards and backwards.

The key point here is that descriptions such as switch-level models are attempting to model *physics*. In this case, an attempt is being made to approximate a continuous phenomenon within the discrete-event framework. This is very bad for specification for it depends heavily on the level of the description: there is a huge reduction in detail from the continuous domain to the abstract discrete-event domain and much of the meaning in the description is held in the mind of the beholder. Such descriptions are very ambiguous due to this implicit reduction and can hardly be expected to be intuited by automated means. Expecting a synthesis system to be able to intuit the continuous behavior from the abstract discrete-event behavior is effectively asking for the inverse of the reduction shown in Figure 4. Although this sort of low-level representation is not useful for specifying designs, many current simulator implementations are oriented towards this level of simulation [MCC91] and provide special-cased value systems which are known to be more efficiently treated by the simulator.

Ause of VHDL to model a bidirectional transmission gate is shown in Figure 14.<sup>12</sup> This gate is part of a larger switchlevel modeling package and value system which is developed in [Coe89]. As one might expect, attempting to model bidirectional switches with a unidirectional switch-level simulator is inefficient, but not impossible. The essential trick involved in switch-level modeling using VHDL is the abstraction of a transistor (as a switch) into a small finite-state machine. The various strengths emitted by the switch are modeled as values in a lattice-like value system encoded in VHDL's enumerated data types.

Figure 14 Modeling a Transmission Gate

```

USE std.std logic.ALL;

USE work.ALL;

ENTITY nfet IS

GENERIC(gdelay: time := 3 ps;

maxstrength: t strength := `R');

PORT(g: IN t wlogic;

src, drn: INOUT t_wlogic);

END nfet;

ARCHITECTURE nfet behavior OF nfet IS

COMPONENT bxfr type

GENERIC(gdelay: time := 3 ps;

maxstrength: t strength := `R');

PORT(g: IN t wlogic;

src, drn: INOUT t_wlogic);

END COMPONENT;

BEGIN

il: bxfr type

GENERIC MAP(gdelay, maxstrength)

PORT MAP(g, src, drn);

END nfet behavior;

```

<sup>12.</sup> This example is taken from [Coe89], pages 104-108. The **bxfr\_type** model implements a bidirectional transmission gate as a finite state machine; that description covers two full pages and is omitted here.

This example of the use of VHDL to model digital circuits at the switch-level seem to be so egregious as to be rejected outright as a misuse of the language. It is important however for it is an example of an interpretation of VHDL text which is given meaning beyond the context of the VHDL language and as such it illuminates a far subtler issue of specification: the use of different **Bit** data types:

```

type Bit is ('0', '1');

```

but for historical and simulation accuracy reasons they were written with the commonly-declared type MVBit,

```

type MVBit is ('0', '1', 'X', 'Z');

```

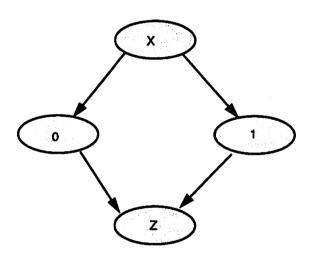

which has an intuitive interpretation as a "bit" which is embedded in the lattice shown in Figure 15. This lattice is extremely useful for simulation purposes as it allows the propagation of unknown or undefined values. There are even more complicated ones which have been proposed[Coe89] and some have even been standardized in their interpretation by the EIA and the IEEE<sup>13</sup> such the one shown in Figure 16.

Figure 15 A Four-Valued Bit Lattice

The relevance to specification here is that the specification interpretation of these "bits" is not the ones with which they have been imbued by their designers. As far as a specification interpretation is concerned, these are all multi-valued variables and it will take the relevant number of bits to encode them. For example, the specification interpretation of the data type shown in Figure 16 which is taken from the IEEE LOGIC\_SYSTEM package [BIL90] is that of a multi-valued variable with 9 possible values. Thus, with respect to specifying a digital circuit, at least 4 bits to encode each of the possible values of the data type; this was certainly not the intent of the IEEE models-standardization committee.

The interpretation as a specification of the various gate-level value systems is certainly not what the designers of these systems intended. They had an idea which was more like that of Figure 4 wherein these value systems approximate reality within the framework of VHDL. To a certain extent they accomplish that aim. The importance for the consumer of specifications to be made aware of the limitations of the specification interpretation of VHDL; that there is an implicit level of

<sup>13.</sup> The example is taken from [Bil90]

#### Figure 16 A Multi-Valued Bit Type Declaration

```

TYPE std_ulogic is (

'U', -- Uninitialized

'X', -- Forcing 0 or 1

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak 0 or 1

'L', -- Weak 0 (for ECL open emitter)

'H', -- Weak 1 (for open Drain or Collector)

'D' -- don't care

);

```

specification and that the reductions in detail described in Figure 4 do not apply to specifications where everything is defined explicitly.

#### **Analog Modeling and Other Exotic Uses**

There are a number of other uses to which VHDL has been put. One of the most inventive uses is modeling analog signals for mixed analog-digital simulation *completely within VHDL*<sup>14</sup>. This is accomplished by defining behavioral VHDL models which update the values on signals as per the usual methods of analog behavioral modeling. The values on signals are records which contain the coefficients of polynomials that, if evaluated, would give the analog voltage on the wire. This may be inelegant and inefficient, but it is a "recommended" practice for certain government contracts.

#### Summary

The point of this tour through the range of possible descriptions in VHDL was to provide some idea of where VHDL specifications might fit, were it to be defined. Of all of the descriptions that have been presented, none of them indicate in *any* way, save for the English words used in the identifiers, which sort of description they are. The policy is in the mind of the beholder.

Upon being given a random chunk of VHDL text, a simulator can analyze it, compile it and simulate it, independent of the intended user's interpretation of the description. The operational rules for simulation are fixed; it is the user's interpretation of the results which change across the various styles. On the other hand, it is a much different situation for a synthesis system to interpret VHDL as a specification, for there is some *presumed level* of description at which the VHDL text is written. This cannot change over time if the specification is to be considered sound and rigorous.

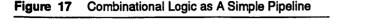

A synthesis system cannot be expected to analyze any arbitrary VHDL description and intuit the writer's original idea. As a specific example of this, consider the 1-bit combinational full-adder shown in Figure 13. While it is described as a full adder and a simulator will produce the outputs of a full adder on **AB** and **Carry\_out**, that is not what is being *specified*. What is being indicated in that VHDL text, when interpreted as a specification, is three communicating finite state machines **U0**, **U1** and **U2** each with its own state: the drivers of the output signals of each instance: **Temp\_carry\_1** and **Temp\_sum** for **U0**, **Temp\_carry\_2** and **AB** for **U1** and **Carry\_out** for **U2**.

In spite of the fact that the system of Figure 13 describes a network of three finite state machines, it can be interpreted by the user as a combinational network. This is because the three machines **UO**, **U1** and **U2** are connected in a unidirectional

<sup>14.</sup> This was first described to me by Alfred Gilman of Intermetrics as part of a modeling standard for DoD projects.

manner thereby forming an acyclic pipeline as shown in Figure 18. Viewing the behavior of whole entity, one can interpret its behavior as that of a full adder. With respect to the inputs **A**, **B** and **Carry\_in** then, the two externally-visible outputs **AB** and **Carry\_out** are recognizable as the cover of the 1-bit combinational adder. Such is the distinction between an interpretation of VHDL as a specification *declaration* and as an executable *simulation* model.

This presumed level of specification relates directly to the policy level shown in Figure 18. With respect to the use of VHDL for simulation this policy level can change radically; it can change from being a test bench to being a registertransfer description to being a switch-level transistor netlist or even something else. With respect to an interpretation of VHDL as a specification for synthesis or verification, the definition of this policy level cannot change; it must always remain fixed.

Figure 18 The Traditional Levels of A Simulation Model

Concretely this means that it is not possible to have mixed interpretations of the VHDL descriptions which can still be interpreted as specifications. The interpretation that is proposed here is the synchronous one and that means that the interpretation of the VHDL, the presumed level of description, is one of communicating finite state machines: there is no structure and there is no "physics" allowed. This means for example, that there is no provision for an "extra" piece of combinational logic or a "declaration" of a clocking discipline, or an asynchronous handshake or anything of that nature.

The *whole* VHDL model is being interpreted as a specification for a finite automata, independent of what the syntax of the model or the identifiers used in the model mean to the reader.

To drive home how this affects a user's view of the language, consider the example of Figure 19. This example shows what one might think of as a three-input "and" gate operating on a "bit" signal on a domain of *true*, *false* and *unknown*. In fact, however the synchronous semantics of VHDL would interpret this as three communicating finite state machines, each of which has one state variable which ranges over three possible values. The important point is that each VHDL process is interpreted as an individual finite state machine *for the purposes of specification*.

igure 19 Really a Finite State Machine

```

package ThreeValued is

type Bit3 is ('0', '1', 'X');

function "and" (A, B: Bit3) return Bit3;

end ThreeValued;

package body of ThreeValued is

function "and" (A, B: Bit3) return Bit3 is

begin

if A = X' or B = X' then

return 'X';

elsif A = 1' and B = 1' then

return '1';

else

return '0';

end if;

end "and";

end ThreeValued;

use Work.ThreeValued.all;

entity and3 is

port(In1: in Bit3; In2: in Bit3; In3: in Bit3;

Out1 out Bit3);

end and3;

architecture really is an fsm of and3 is

signal tmp1, tmp2: Bit3;

begin

tmpl <= inl and in2;</pre>

tmp2 <= in2 and in3;</pre>

Out1 <= tmp1 and tmp2;

end;

```

#### 2.3 The Nature of Parallelism

In addition to the presumed level of interpretation of VHDL, there is the aspect of parallelism involved in its specification of computing systems. Parallelism is a complex phenomenon for it deals with both *occurrence* and *time*. The attributes of parallelism in a language semantics drastically affects the form that any realizations of programs written in that language

can take. The most problematic aspect of parallelism is that of time (not of occurrence); what is assumed about time in the semantics affects all else. It is useful to consider that time has the following aspects:

#### **Partial Ordering of Events**

Events can be considered to occur only in relation to one another via the relations *before* or *after*. Some events may be incomparable under this relation; such events are said to occur in parallel.

#### **Equivalence of Events**

In addition to the ordering of before and after, there is the notion of *at the same time*. Under this model only events occurring at the same time are said to occur in parallel.

#### **Delay Between Events**

Finally, there is delay where events are not points in time, but rather intervals. This reflects the aspect of reality wherein devices react in finite time. Two events are said to occur in parallel under this model if each occurs *during* the other.

The following section describes the idea of parallelism as found in VHDL and then synchronous parallelism is presented in contrast.

#### 2.3.1 Asynchronous Parallelism

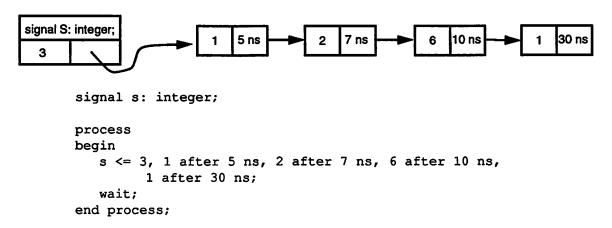

The fundamental goal of the VHDL simulator is to provide a means for simulating the parallel execution of the models. Most VHDL simulators are purely sequential programs<sup>15</sup> and use the standard techniques to simulate parallelism within their sequential framework. These techniques involve maintaining queues of pending values and lists of processes to be executed based on their sensitivities to signals on which the values are propagated.

What ultimately results from this operational model is that the type of parallelism which is exposed at the programmer level is *asynchronous parallelism*. In this sort of parallelism, two events can only occur in relation to each other; either one is first and the other is second, or vice versa. Two events on two separate signals never occur at the same time.

#### 2.3.2 Synchronous Parallelism

The standard notions of VHDL parallelism is asynchronous parallelism because it is not possible to relate state changes in any stronger way than by a partial ordering of events. Nothing can happen at the same time and so there is only before and after.

The synchronous model of time abstracts time into discrete instants between which nothing of interest occurs. Synchronous parallelism then requires that events in parallel occur at the same time. There is still a notion of before and after, but the partial ordering of events is not used to define parallelism.

Synchronous parallelism does not offer or allow nondeterminism. Because of this restriction, and due to the fact that there are only a finite number of possible events, an interpretation of synchronous parallelism as a finite automaton can be generated; Section 3.3.2 outlines how this is done for an existing synchronous language - Esterel.

#### The Synchrony Hypothesis

The interpretation of synchronous systems as finite automata is driven by two hypotheses: the synchrony hypothesis and the strong synchrony hypothesis. These are termed hypotheses because synchronous systems are only guaranteed to func-

<sup>15.</sup> The VHDL simulator described in [Wil90] is one that is not; it distributes the simulation across a network of workstations.

tion correctly if these preconditions are true. The verification that the preconditions are met in any given implementation of a synchronous system is a proof obligation imposed on the designer.

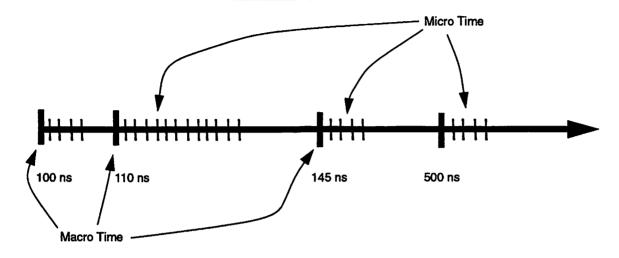

The synchrony hypothesis states that only explicit delay exists. All else (all other computations) are instantaneous. This implies that the program only *reacts* in response to its environment. The strong synchrony hypothesis requires the synchrony hypothesis and requires in addition that control steps take no time.

Both of these hypotheses are clearly not true in any physically realizable system. However, because time is measured only at specific *instants* between which nothing of interest to the system occurs, it is possible to preserve this rather elegant fiction through a timing analysis step. So long as the implementor can assure that for the given instance of the system, all computations triggered by an event finish before the arrival of the next event then the conditions of the two synchrony hypotheses can be considered to have been met. This is the timing verification step, and it corresponds exactly to timing verification in hardware design.

#### 2.4 Language Interpreters versus Program Specifications

In addition to the issues of the presumed level of interpretation and the definition of parallelism, there is also the issue of how the language and the language's semantics affects the specification. It has been said that language affects what can be said to such a degree that certain concepts which are inelegantly dealt with in language simply are not treated. Thus a qualification of the effect of the phrasing of the description on its interpretation as a specification needs to be made.

The comments of this section are phrased in terms of *programming languages* and *interpreters* and generally have a software orientation. This is done on purpose to accentuate the operational aspects of the VHDL simulator as an *interpreter* for the VHDL language which is a *parallel programming language*. It is within this framework of a formal language and its interpreter that a notion of specification is being proposed. This extraction process is more difficult than it might seem due to the of the intrusive effects of the language's interpreter as explained below.

For the purposes here, the ultimate goal of hardware description languages is in the expression of computing, not in the generation of the specific syntax by which that computation is expressed; *i.e.* the language is a means to an end, not an end unto itself. While this seems obvious, there are those who take the opposite tack - namely that the purpose of the programming language is to record all relevant design decisions and further, that any support for comments in a programming language are an admission that providing such all-encompassing design flow support has not been possible. Such an extreme position is not necessary here as only the aspects of the specification represented in the language is relevant.

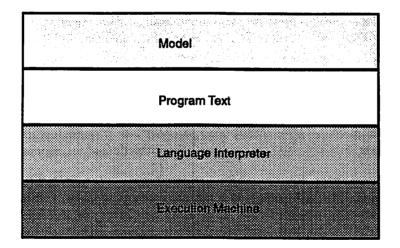

In Figure 18 the traditional levels of a hardware description language program are shown. Description is accomplished through various levels of abstraction until finally a machine can be instructed to perform the computation; this defines the meaning of that hardware description. The trick of hardware description is to define the intervening abstractions so that they can ultimately be implemented efficiently.

The following sections argue that the two intervening levels of Figure 18, the *program* and *interpreter* levels, are incidental to the task at hand and introduce *interpreter bias* into implementations. Interpreter bias is the term that is being used here for tendency of final implementations to look more and more like a general facility which indirectly computes by manipulating a data structure representing the computation. Optimizations tend to reduce this effect, but do not completely erase it because of their partial nature. A language's interpreter bias prevents the optimization of these data structure manipulations into native machine-level operations.

One can treat the top level of the hierarchy shown in Figure 18 as a *specification* of the computation to be performed on the machine. The job of the synthesis system, in the case of hardware, or the compiler in the case of software, is then to produce *something* executable at the lowest level (the *machine*) which will satisfy the specification. An option for defining

the meaning of the top-level specification is to use quantified logic formulae or some sort of exhaustive listing of input/ output pairings. Clearly though, for this notion of specification to be practically useful it must to be more concrete and succinct than large masses of formulae or an unstructured mapping. Elaborating the representation of a true and meaningful specification for computation is the subject of the next sections.

#### **Program Specifications**

The goal of high-level design is to take a specification (an idea) and produce something (an executable) that will compute the required function. A specification is something which defines the relationships that shall hold on any implementation. Many specifications are considered to be but an exhaustive list of the possible input/output relationships that hold over all possible implementations. Ideally this exhaustive list is succinct. For a small class of simple functions, this can be done. The boolean functions are such an example, for succinct specifications of logic functions can be given in either sum-of-products or as a binary decision diagram. For more complex functions, especially those whose output depends on past inputs or outputs (*i.e.* they maintain internal state) the task is far more complicated.

The key point to notice about a specification is that it indicates what observations the environment wishes to be able to make about any implementation. At the extreme case, if nothing can be observed, as is the case with a so-called "black box," then the exhaustive list of input/output pairs is required. At the other extreme, if everything can be observed, then the result is a "glass box" that is a pure structural description of the computation. Somewhere in the middle is the notion of specification that is desired here.

The idea is to define specifications that allow for a trade-off along the axis of internal visibility; ranging from black box to glass box. Each of these alternatives will have varying degrees of succinctness and, conversely, flexibility of implementation.

#### **Regular Expressions as FSM Specifications**

What can be observed from the study of regular expressions [HU79] is that they provide just such a specification for the class of finite automata. As has already been argued, the use of the finite state machine model<sup>16</sup> is a good one in the case of real-time software and simulator kernels, so it is very convenient that regular expressions are a succinct specification for the domain of finite state machines.

For each regular expression, there is some set of finite automata that recognize that regular expression. In fact, it is convenient, for this example, to examine the software tool which produces one of these automata for the case of software: **lex** [LS75]. The input to the program is a set of regular expression which is taken as the specification of the automaton to produce. Depending on the required state-space size and code-size trade-offs requested, the resulting implementation is either larger and faster or smaller and slower.

On the other hand, examine this same example in the light of interpreter bias. by considering the case of a hand-coded scanner versus the **lex**-generated one. It would take an extremely powerful optimizer to determine the function of the hand-generated scanner to the level of detail required for use as a specification for the automaton. On the other hand, the regular expression specification is entirely adequate for it only identifies the minimal set of points of user-observability in the final automaton.

The use of regular expressions as a specification for a finite automaton was not presented only to illustrate the notion of a language interpreter versus a program specification. This exact idea is used to define the specification nature and thus the compilation procedure for the seemingly imperative language, Esterel and that procedure is outlined in Section 3.3.2.

<sup>16.</sup> Finite state machines, finite automata, (finite) state transition graphs and regular expressions can all be shown to be equivalent [HU79]. Here these terms are used interchangeably with *regular expression* emphasizing specification and *finite automata* or *finite state machine* emphasizing implementation.

# Chapter 3

# Synchronous/Reactive Languages

One of the most well-developed and extensively published synchronous languages is the Esterel language [CIS88] [Ber91] [BDS91] [BCG86] [BC84].<sup>17</sup> What is presented here by no means represents the whole language, rather only the most relevant highlights of semantics are presented with a few examples of syntax. This chapter is focused mostly on Esterel but the final section, Section 3.4, will describe the implications of the synchronous assumptions for VHDL.

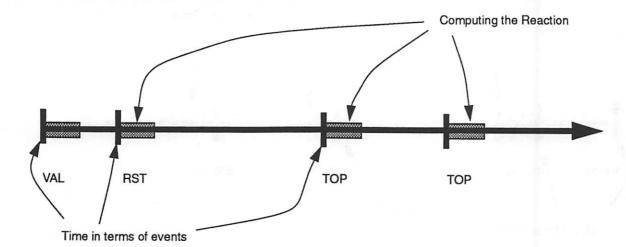

Esterel, like other synchronous languages, requires that the strong synchrony hypothesis hold, as described in Section 2.3.2. The Esterel program is thus a specification for the computing which is to be performed rather than a representation of a data structure on which computation shall occur. Also, as a synchronous language, an Esterel program is reactive, that is it computes only in response to changes in its environment. All changes in the environment, even the passage of "real" time are measured in terms of events impinging on the program. This indistinguishability between metric time (in seconds) and symbolic time (in "ticks") will become important in the next section as the examples show the interchangeability between the signals **SECOND** and **BUTTON** with no loss of description.

The strong synchrony hypothesis allows the following claims can be made about Esterel semantics: non-delay events take zero time and delay elements take exactly the amount of time specified. The effect of the strong synchrony hypothesis is the separation of the correctness of an Esterel program into two independent parts: a functional correctness part and a temporal correctness part. This independence of function and time is much the same as that which is found in clocked digital circuits where so long as the circuit is able compute its next-state and output functions faster than the clock cycle time, the circuit is considered to be correct. Different methods are used to verify the function and performance of the circuit, within the clocked-digital paradigm they are seen to be independent. In the case of Esterel programs, the strong synchrony hypothesis allows for different means of verification to be applied to each aspect, *e.g.* automata-theoretic methods to verify functional correctness.

#### 3.1 Overview of the Language

The Esterel language is divided into two levels in order to define a simpler sound semantics for the language. There is a *core language* over which the semantics is defined. In addition, there is an extended language which is defined in terms of the core. I will only review the key concepts of the core language as the extended language provides only syntactic convenience and it adds no new semantic power.

The important semantic feature of the language is that it has both an interpretive aspect and a specification aspect and these are both exposed in the construction of the Esterel interpreter and the Esterel compiler respectively. These aspects are described in Section 3.3.1 and Section 3.3.2. The interpretive aspect indicates how the execution of a statement changes the state of the interpreter and what successor statement will be executed. The specification aspect is consistent with the interpretive aspect but indicates only what computations and states must be observed in any realization of the specification so that the compiler generates software which respects this minimal set of observability conditions.

The execution semantics of Esterel follows the synchronous paradigm. Time is separated into discrete *instants* between which nothing of interest occurs. State transition computations are considered to be instantaneous and the only delays are

<sup>17.</sup> The descriptions presented here are from [BDS91] and so should be consistent with the latest available compiler [CIS88].

those which are explicitly declared. There is an issue of the causal correctness of an Esterel program; but [BC84] demonstrates how checking for this condition can be performed statically during compilation.

Esterel programs consist of networks of *signals* and *processes* with processes maintaining *statements* and *variables*. Signals are the only means by which processes are allowed to communicate (shared variables are disallowed). A process has an interpretative aspect as the statement which will be executed in the current instant and a specification aspect as the current state (of a finite state machine). Variables hold data values which are local to a process. The variable values and the signal values available on the input signals determine the next statement to be executed, or the next state to be entered, depending on which aspect of a process one is considering.

#### 3.2 Core Language Constructs

Seven core language constructs are presented here which show the essential characteristics of Esterel. There are of course a host of other constructs which are not presented here; they can be found in [CIS88].