Copyright © 1995, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# MINIMIZING COMMUNICATION AND SYNCHRONIZATION OVERHEAD IN MULTIPROCESSORS FOR DIGITAL SIGNAL PROCESSING

by

Sundararajan Sriram

Memorandum No. UCB/ERL M95/90

outer and

7 November 1995

# MINIMIZING COMMUNICATION AND SYNCHRONIZATION OVERHEAD IN MULTIPROCESSORS FOR DIGITAL SIGNAL PROCESSING

Copyright © 1995

by

Sundararajan Sriram

Memorandum No. UCB/ERL M95/90

7 November 1995

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

.

### Abstract

# MINIMIZING COMMUNICATION AND SYNCHRONIZATION OVERHEAD IN MULTIPROCESSORS FOR DIGITAL SIGNAL PROCESSING

by

Sundararajan Sriram

### **Doctor of Philosophy in Electrical Engineering**

Professor Edward A. Lee, Chair

This thesis is concerned with embedded systems for Digital Signal Processing (DSP) that consist of multiple programmable digital signal processors augmented with custom VLSI components; we will refer to such systems by the term "multiprocessor." The dataflow model of computation has been widely used for providing a formal methodology for specifying computations and mapping them to such multiprocessor systems.

In this thesis, we focus on DSP algorithms that can be specified as Synchronous Data Flow graphs and its extensions. Such algorithms can be efficiently scheduled onto multiple processing elements (a processor could be either programmable or a custom VLSI component) at compile time - computations in the graph are assigned to processors at compile time and the execution order of tasks assigned to each processor is also determined at compile time.

In such a compile-time (static) scheduling strategy, it is possible to predict

the run time inter-processor communication (IPC) pattern. We present two techniques that make use of this compile-time determined communication pattern, for minimizing IPC and synchronization overhead in the parallel implementation. The first technique is aimed at eliminating arbitration and synchronization costs when using shared memory for IPC. We call this the Ordered Transactions strategy; the idea is to determine the order in which processors require access to shared resources and to enforce this order at run time. Enforcing such an order eliminates contention for shared resources and the need for explicit synchronization. We describe the design and hardware implementation details of a prototype multiprocessor board that was built as a proof-of-concept for the ordered transactions strategy.

The second technique we present in this thesis consists of efficient algorithms for minimizing synchronization costs in statically scheduled multiprocessors. These include procedures for detecting and eliminating redundant synchronization points in the schedule and systematically adding certain synchronization points with a view towards reducing the overall synchronization cost.

Surand A Zee Nov. 7, 1995

Edward A. Lee, Thesis Committee Chairman

# Table of Contents

| 1 | INTROL | DUCTION1                                            |

|---|--------|-----------------------------------------------------|

|   | 1.1    | The Synchronous Dataflow model                      |

|   |        | 1.1.1 Background7                                   |

|   |        | 1.1.2 Utility of dataflow for DSP11                 |

|   | 1.2    | Parallel scheduling                                 |

|   |        | 1.2.1 Fully-static schedules15                      |

|   |        | 1.2.2 Self-timed schedules19                        |

|   |        | 1.2.3 Execution time estimates and static schedules |

|   | 1.3    | Application-specific parallel architectures         |

|   |        | 1.3.1 Dataflow DSP architectures                    |

|   |        | 1.3.2 Systolic and wavefront arrays25               |

|   |        | 1.3.3 Multiprocessor DSP architectures              |

|   | 1.4    | Thesis overview: our approach and contributions27   |

| 2 | TERMIN | NOLOGY AND NOTATIONS                                |

|   | 2.1    | HSDF graphs and associated graph theoretic notation |

|   | 2.2    | Schedule notation                                   |

| 3 | THE OR | DERED TRANSACTION STRATEGY                          |

|   | 3.1    | The Ordered Transactions strategy                   |

|   | 3.2    | Shared bus architecture                             |

|   |        | 3.2.1 Using the OT approach46                       |

|   | 3.3    | Design of an Ordered Memory Access multiprocessor47 |

|   |        | 3.3.1 High level design description48               |

|   |        | 3.3.2 A modified design49                           |

|   | 3.4    | Design details of a prototype                       |

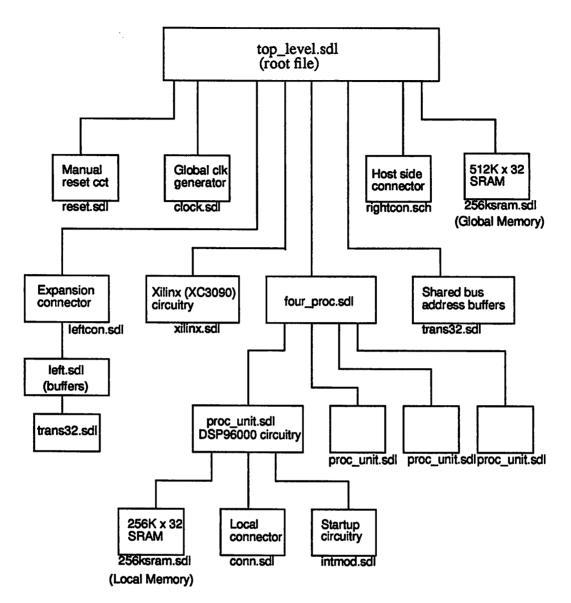

|   |        | 3.4.1 Top level design53                            |

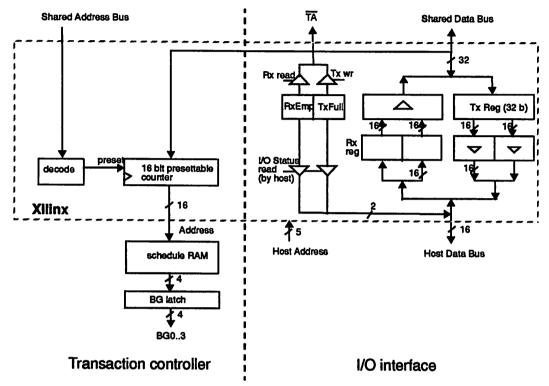

|   |        | 3.4.2 Transaction order controller                  |

|   |        | 3.4.2.1. Processor bus arbitration signals          |

|   |        | 3.4.2.3. Presettable counter                            | 58  |

|---|--------|---------------------------------------------------------|-----|

|   |        | 3.4.3 Host interface                                    | 60  |

|   |        | 3.4.4 Processing element                                | 61  |

|   |        | 3.4.5 Xilinx circuitry                                  | 62  |

|   |        | 3.4.5.1. I/O interface                                  | 64  |

|   |        | 3.4.6 Shared memory                                     | 65  |

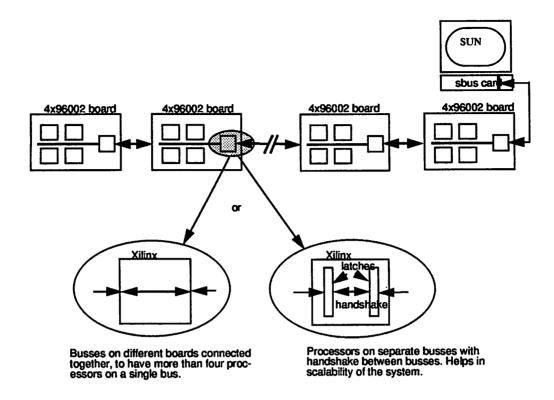

|   |        | 3.4.7 Connecting multiple boards                        | 65  |

|   | 3.5    | Hardware and software implementation                    | 66  |

|   |        | 3.5.1 Board design                                      | 66  |

|   |        | 3.5.2 Software interface                                | 69  |

|   | 3.6    | Ordered I/O and parameter control                       | 71  |

|   | 3.7    | Application examples                                    | 73  |

|   |        | 3.7.1 Music synthesis                                   | 73  |

|   |        | 3.7.2 QMF filter bank                                   | 75  |

|   |        | 3.7.3 1024 point complex FFT                            | 76  |

|   | 3.8    | Summary                                                 | 78  |

| 4 | AN ANA | LYSIS OF THE OT STRATEGY                                | 79  |

|   | 4.1    | Inter-processor Communication graph $(G_{ipc})$         | 82  |

|   | 4.2    | Execution time estimates                                |     |

|   | 4.3    | Ordering constraints viewed as edges added to $G_{ipc}$ |     |

|   | 4.4    |                                                         |     |

|   | 4.5    | Optimal order                                           | 92  |

|   | 4.6    | Effects of changes in execution times                   |     |

|   |        | 4.6.1 Deterministic case                                | 97  |

|   |        | 4.6.2 Modeling run time variations in execution times   | 99  |

|   |        | 4.6.3 Implications for the OT schedule                  |     |

|   | 4.7    | Summary                                                 | 106 |

| 5 | MINIMI | ZING SYNCHRONIZATION COSTS IN SELF-TIMED                |     |

| - | SCHEDI | ULES                                                    | 107 |

| 5.1   | Related work                                                        |

|-------|---------------------------------------------------------------------|

| 5.2   | Analysis of self-timed execution                                    |

|       | 5.2.1 Estimated throughput114                                       |

| 5.3   | Strongly connected components and buffer size bounds                |

| 5.4   | Synchronization model116                                            |

|       | 5.4.1 Synchronization protocols116                                  |

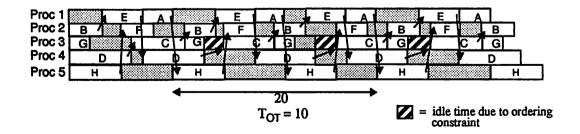

|       | 5.4.2 The synchronization graph G <sub>s</sub> 118                  |

| 5.5   |                                                                     |

| 5.6   | Removing redundant synchronizations                                 |

|       | 5.6.1 The independence of redundant synchronizations125             |

|       | 5.6.2 Removing redundant synchronizations                           |

|       | 5.6.3 Comparison with Shaffer's approach128                         |

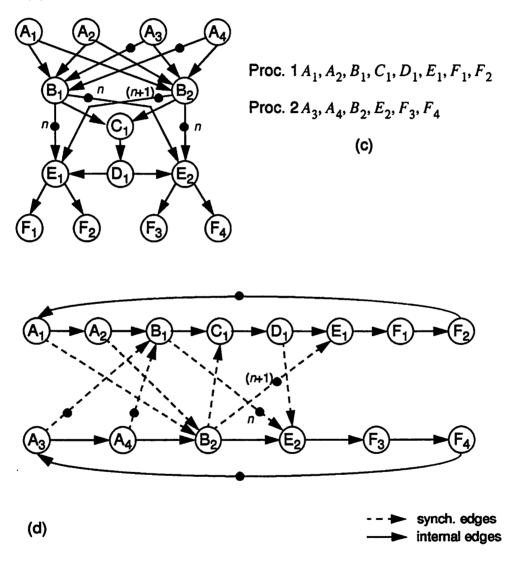

|       | 5.6.4 An example                                                    |

| 5.7   | Making the synchronization graph strongly connected                 |

|       | 5.7.1 Adding edges to the synchronization graph                     |

|       | 5.7.2 Insertion of delays137                                        |

| 5.8   | Computing buffer bounds from G <sub>s</sub> and G <sub>ipc141</sub> |

| 5.9   |                                                                     |

| 5.1   | 0 Summary                                                           |

| EXTEN | ISIONS147                                                           |

|       | The Boolean Dataflow model                                          |

|       | 6.1.1 Scheduling148                                                 |

| 6.2   | Parallel implementation on shared memory machines                   |

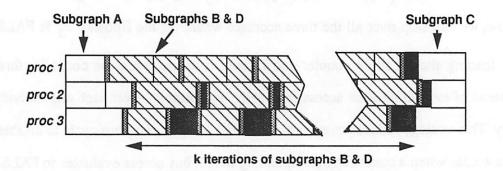

|       | 6.2.1 General strategy                                              |

|       | 6.2.2 Implementation on the OMA                                     |

|       | 6.2.3 Improved mechanism                                            |

|       | 6.2.4 Generating the annotated bus access list                      |

| 6.3   |                                                                     |

| 6.4   |                                                                     |

6

.

| 7 | CONCLUSIONS AND FUTURE DIRECTIONS166 |

|---|--------------------------------------|

| 8 | REFERENCES170                        |

•

•

# List of Figures

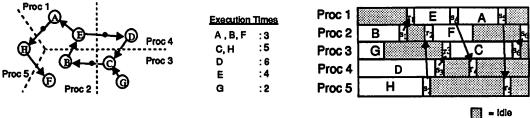

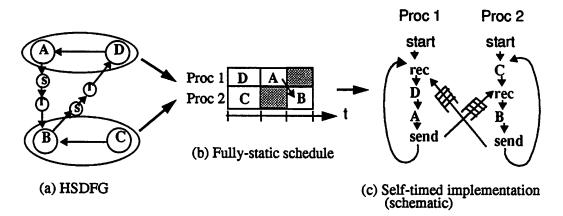

| Figure 1.1.  | Fully static schedule 1                                                | 6  |

|--------------|------------------------------------------------------------------------|----|

| Figure 1.2.  | Fully-static schedule on five processors                               | .7 |

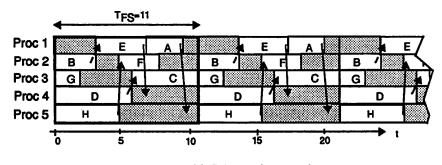

| Figure 1.3.  | Steps in a self-timed scheduling strategy                              | 20 |

| Figure 3.1.  | One possible transaction order derived from the fully-static schedul   | e  |

|              |                                                                        | 11 |

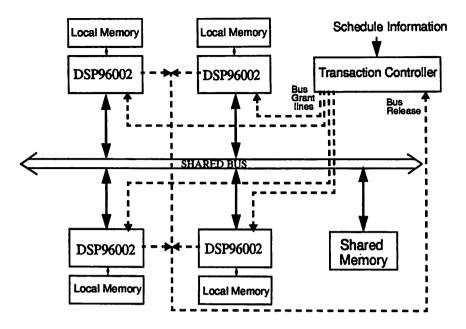

| Figure 3.2.  | Block diagram of the OMA prototype 4                                   | 19 |

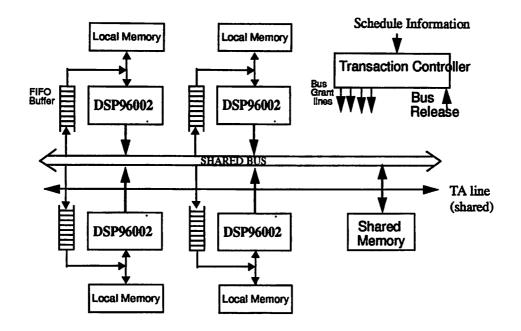

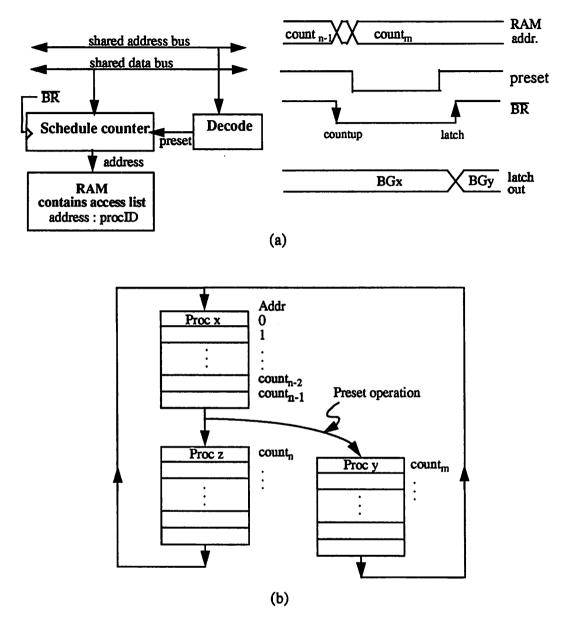

| Figure 3.3.  | Modified design                                                        | 50 |

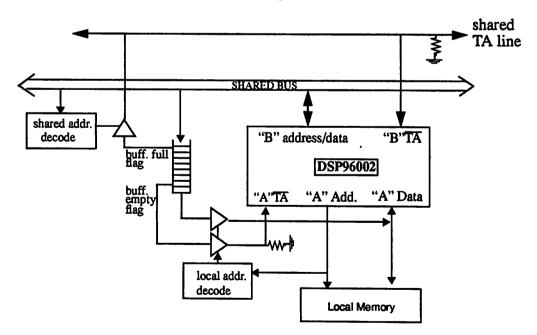

| Figure 3.4.  | Details of the "TA" line mechanism (only one processor is shown)       | •  |

|              | 5                                                                      | 51 |

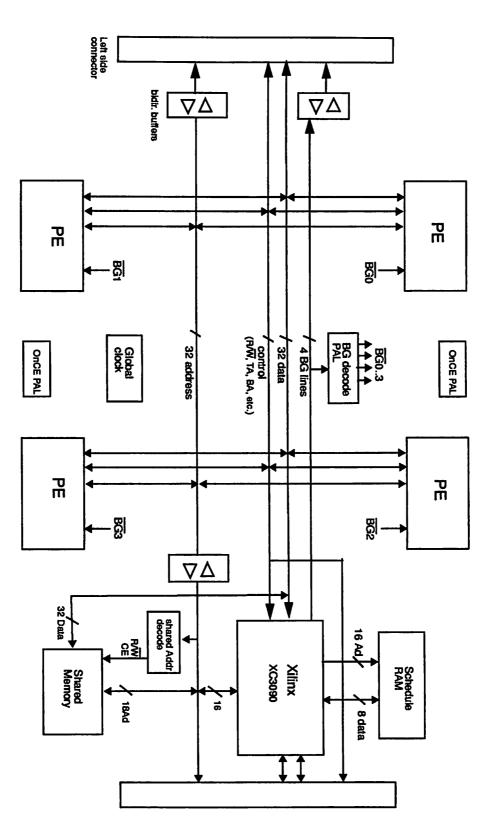

| Figure 3.5.  | Top-level schematic of the OMA prototype                               | 54 |

| Figure 3.6.  | Using processor bus arbitration signals for controlling bus access.    | 56 |

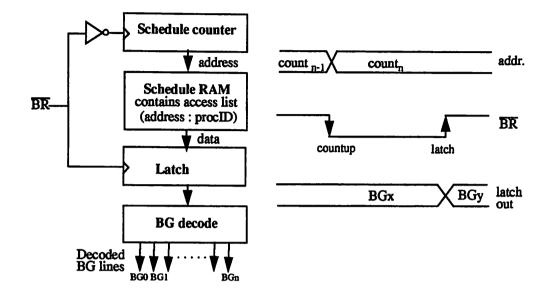

| Figure 3.7.  | Ordered Transaction Controller implementation                          | 58 |

| Figure 3.8.  | Presettable counter implementation                                     | ;9 |

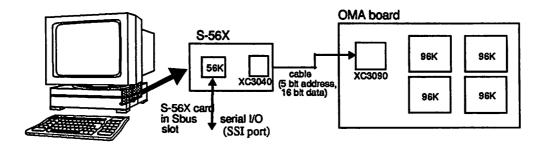

| Figure 3.9.  | Host interface                                                         | 51 |

| Figure 3.10. | Processing element                                                     | 52 |

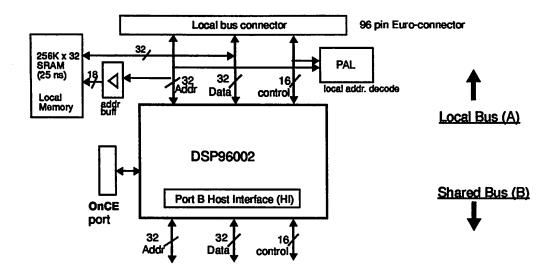

| Figure 3.11. | Xilinx configuration at run time                                       | 54 |

| Figure 3.12. | Connecting multiple boards                                             | 57 |

| Figure 3.13. | Schematics hierarchy of the four processor OMA architecture 6          | 58 |

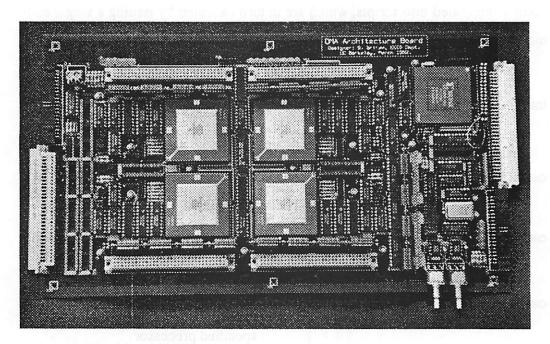

| Figure 3.14. | OMA prototype board photograph                                         | 59 |

| Figure 3.15. | Steps required for downloading code (tcl script omaDoAll)              | 0' |

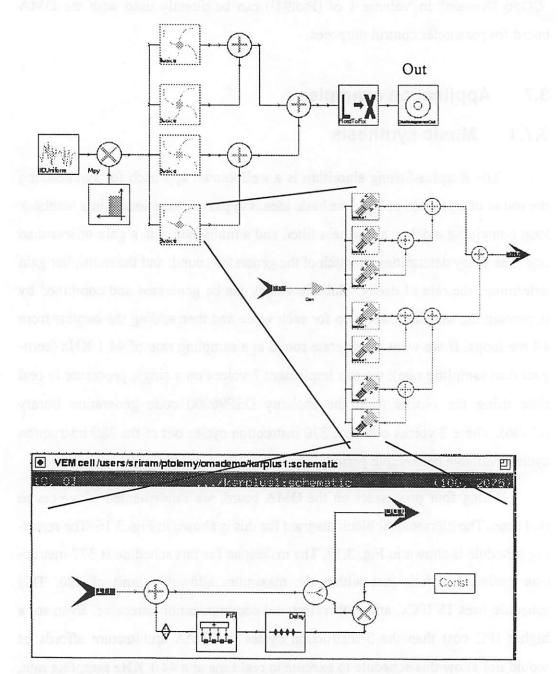

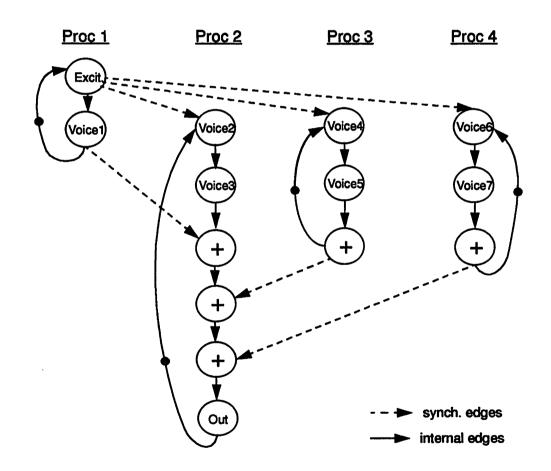

| Figure 3.16. | Hierarchical specification of the Karplus-Strong algorithm in 28       |    |

|              | voices                                                                 | '4 |

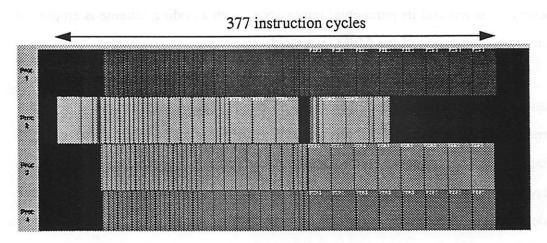

| Figure 3.17. | Four processor schedule for the Karplus-Strong algorithm in 28         |    |

|              | voices. Three processors are assigned 8 voices each, the fourth (Pro-  | с  |

|              | 1) is assigned 4 voices along with the noise source                    | '5 |

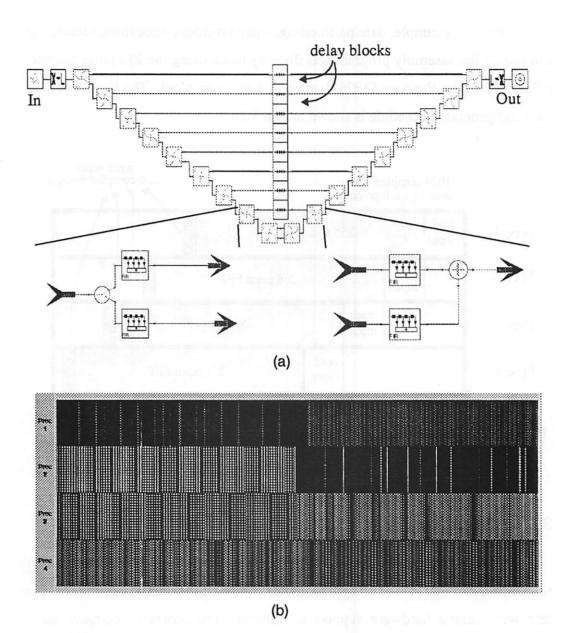

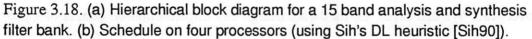

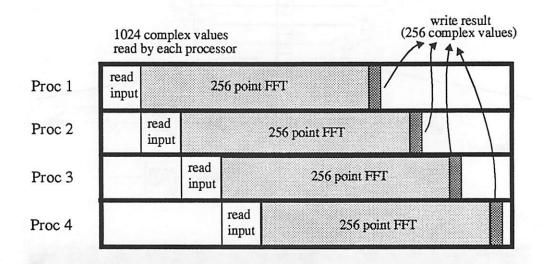

| Figure 3.18. | (a) Hierarchical block diagram for a 15 band analysis and synthesis    |    |

|              | filter bank. (b) Schedule on four processors (using Sih's DL heuristic |    |

|              | [Sih90])7                                                              | 7  |

| Figure 3.19. | Schedule for the FFT example                                                      |

|--------------|-----------------------------------------------------------------------------------|

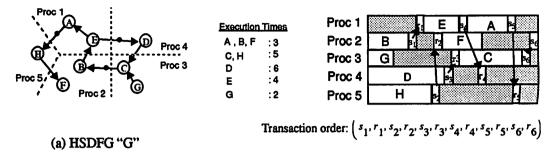

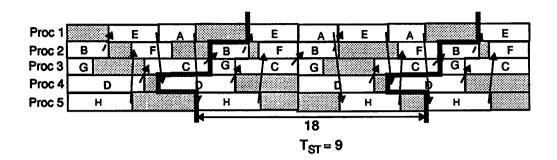

| Figure 4.1.  | Fully-static schedule on five processors                                          |

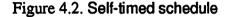

| Figure 4.2.  | Self-timed schedule                                                               |

| Figure 4.3.  | Schedule evolution when the transaction order of Fig. 3.1 is                      |

|              | enforced 81                                                                       |

| Figure 4.4.  | The IPC graph for the schedule in Fig. 4.1                                        |

| Figure 4.5.  | Transaction ordering constraints                                                  |

| Figure 4.6.  | Modified schedule S <sup>2</sup>                                                  |

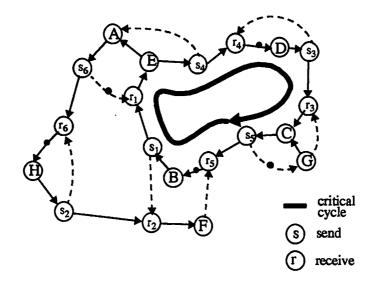

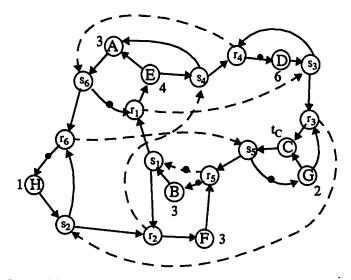

| Figure 4.7.  | $G_{ipc}$ , actor C has execution time $t_c$ , constant over all invocations of C |

|              |                                                                                   |

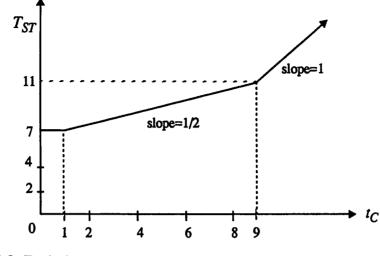

| Figure 4.8.  | <i>T</i> <sub>ST</sub> ( <i>t</i> <sub>C</sub> )                                  |

| Figure 4.9.  | $G_{ipc}$ with transaction ordering constraints represented as dashed lines       |

|              |                                                                                   |

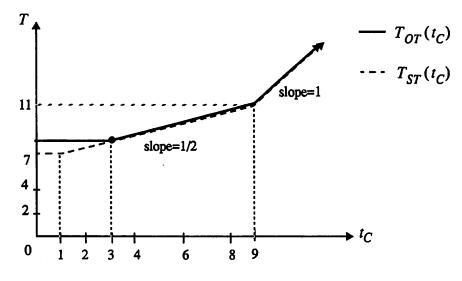

| Figure 4.10. | $T_{\rm ST}(t_{\rm C})$ and $T_{\rm OT}(t_{\rm C})$                               |

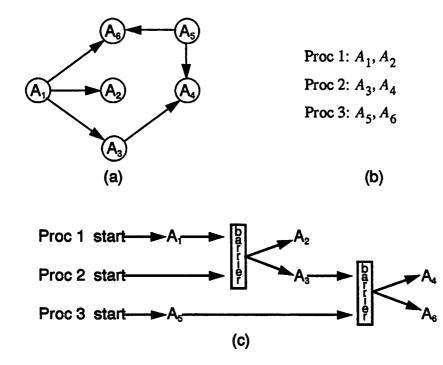

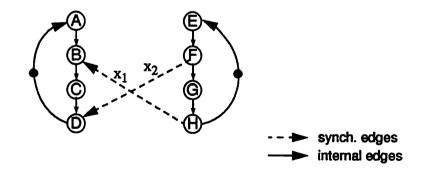

| Figure 5.1.  | (a) An HSDFG (b) A three-pro(a) An HSDFG (b) A three-processor                    |

|              | self-timed schedule for (a). (c) An illustration of execution under the           |

|              | placement of barriers                                                             |

| Figure 5.2.  | Self-timed execution                                                              |

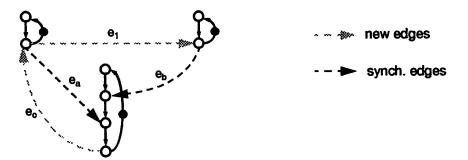

| Figure 5.3.  | An IPC graph with a feedforward edge: (a) original graph (b) impos-               |

|              | ing bounded buffers                                                               |

| Figure 5.4.  | x <sub>2</sub> is an example of a redundant synchronization edge                  |

| Figure 5.5.  | An algorithm that optimally removes redundant synchronization                     |

|              | edges                                                                             |

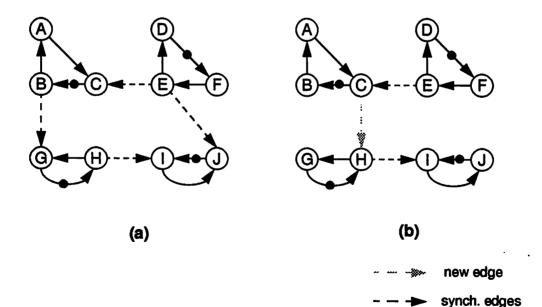

| Figure 5.6.  | (a) A multi-resolution QMF filter bank used to illustrate the benefits            |

|              | of removing redundant synchronizations. (b) The precedence graph                  |

|              | for (a). (c) A self-timed, two-processor, parallel schedule for (a). (d)          |

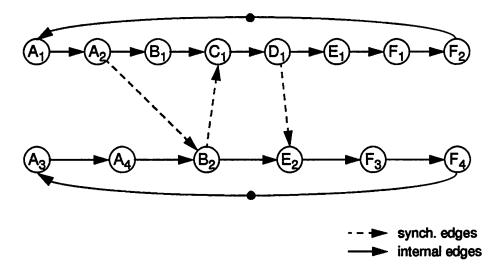

|              | The initial synchronization graph for (c)                                         |

| Figure 5.7.  | The synchronization graph of Fig. 5.6(d) after all redundant synchro-             |

|              | nization edges are removed                                                        |

| Figure 5.8.  | An algorithm for converting a synchronization graph that is not                   |

•

|              | strongly connected into a strongly connected graph                      |

|--------------|-------------------------------------------------------------------------|

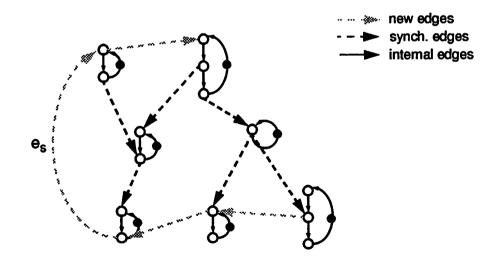

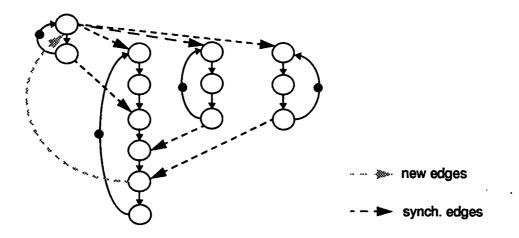

| Figure 5.9.  | An illustration of a possible solution obtained by algorithm Convert-   |

|              | to-SC-graph134                                                          |

| Figure 5.10. | The synchronization graph, after redundant synchronization edges        |

|              | are removed, induced by a four-processor schedule of a music syn-       |

|              | thesizer based on the Karplus-Strong algorithm                          |

| Figure 5.11. | A possible solution obtained by applying Convert-to-SC-graph to the     |

|              | example of Figure 5.10                                                  |

| Figure 5.13. | An example used to illustrate a solution obtained by algorithm Deter-   |

|              | mineDelays                                                              |

| Figure 5.12. | An algorithm for determining the delays on the edges introduced by      |

|              | algorithm Convert-to-SC-graph                                           |

| Figure 5.14. | An example of resynchronization                                         |

| Figure 5.15. | The complete synchronization optimization algorithm                     |

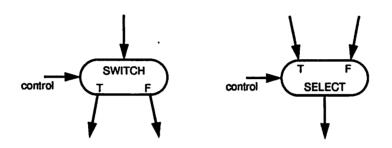

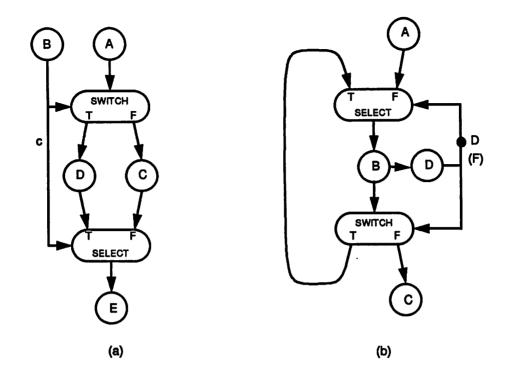

| Figure 6.1.  | BDF actors SWITCH and SELECT                                            |

| Figure 6.2.  | (a) Conditional (if-then-else) dataflow graph. The branch outcome is    |

|              | determined at run time by actor B. (b) Graph representing data-         |

|              | dependent iteration. The termination condition for the loop is deter-   |

|              | mined by actor D                                                        |

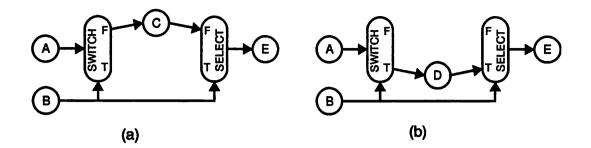

| Figure 6.3.  | Acyclic precedence graphs corresponding to the if-then-else graph of    |

|              | Fig. 6.2. (a) corresponds to the TRUE assignment of the control         |

|              | token, (b) to the FALSE assignment                                      |

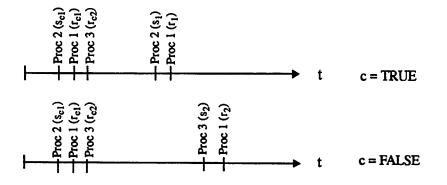

| Figure 6.4.  | Quasi-static schedule for a conditional construct (adapted from         |

|              | [Lee88b])                                                               |

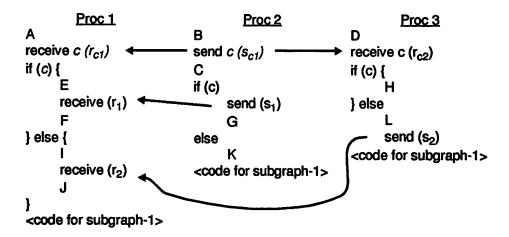

| Figure 6.5.  | Programs on three processors for the quasi-static schedule of Fig.      |

|              | 6.4                                                                     |

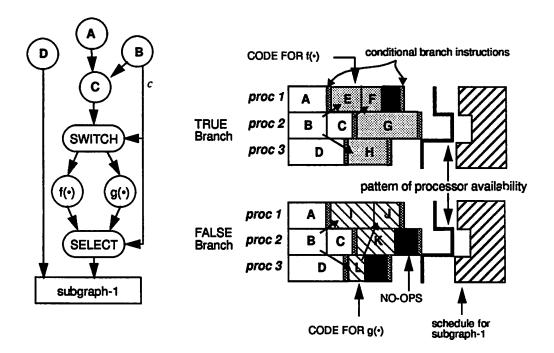

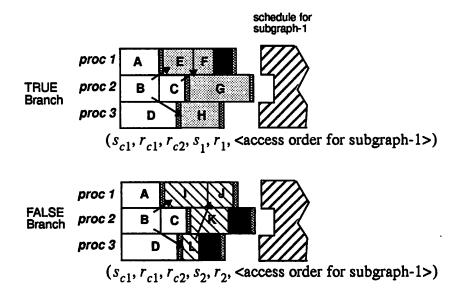

| Figure 6.6.  | Transaction order corresponding to the TRUE and FALSE branches .        |

|              |                                                                         |

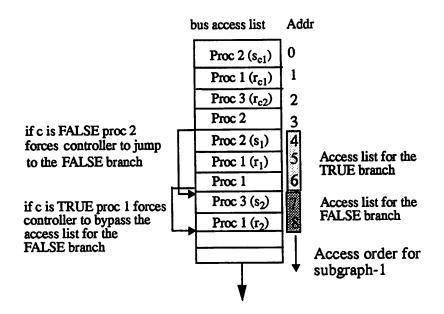

| Figure 6.7.  | Bus access list that is stored in the schedule RAM for the quasi-static |

|              | schedule of Fig. 6.6. Loading operation of the schedule counter con-    |

|              | ditioned on value of c is also shown                                  |

|--------------|-----------------------------------------------------------------------|

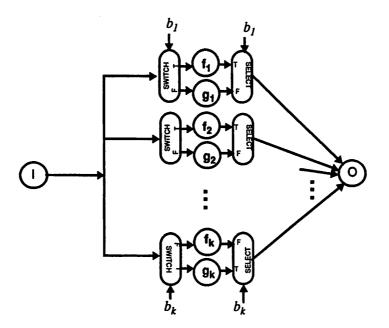

| Figure 6.8.  | Conditional constructs in parallel paths 158                          |

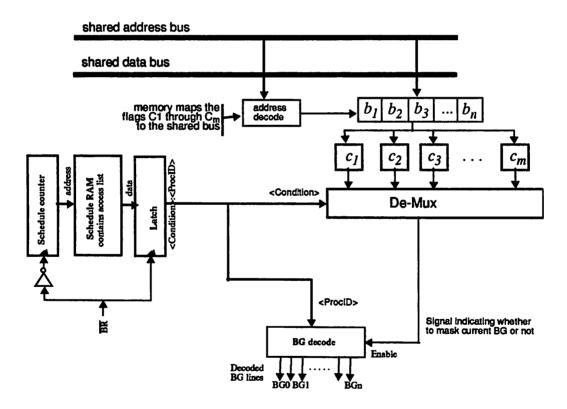

| Figure 6.9.  | A bus access mechanism that selectively "masks" bus grants based      |

|              | on values of control tokens that are evaluated at run time            |

| Figure 6.10. | Bus access lists and the annotated list corresponding to Fig. 6.6 161 |

| Figure 6.11. | Quasi-static schedule for the data-dependent iteration graph of Fig.  |

|              | 6.2(b)                                                                |

| Figure 6.12. | A possible access order list corresponding to the quasi-static sched- |

|              | ule of Fig. 6.11                                                      |

| Figure 7.1.  | An example of how execution time guarantees can be used to reduce     |

|              | buffer size bounds                                                    |

• •

## ACKNOWLEDGEMENTS

I have always considered it a privilege to have had the opportunity of pursuing my Ph.D. at Berkeley. The time I have spent here has been very fruitful, and I have found the interaction with the exceptionally distinguished faculty and the smart set of colleagues extremely enriching. Although I will not be able to acknowledge all the people who have directly or indirectly helped me during the course of my Ph. D., I wish to mention some of the people who have influenced me most during my years as a graduate student.

First and foremost, I wish to thank Professor Edward Lee, my research advisor, for his valuable support and guidance, and for having been a constant source of inspiration for this work. I really admire Professor Lee's dedication to his research; I have learned a lot from his approach of conducting research.

I also thank Professors Pravin Varaiya and Henry Helson for serving on my thesis committee. I thank Professor Messerschmitt for his advice; I have learned from him, both in the classroom as well as through his insightful and humorous "when I was at Bell Labs ..." stories at our Friday afternoon post-seminar gettogethers. I have also greatly enjoyed attending classes and discussions with Professors Avideh Zakhor, Jean Walrand, John Wawrzynek, and Robert Brayton.

During the course of my Ph. D. research I have had the opportunity to work closely with several fellow graduate students. In particular I would like to mention Shuvra Bhattacharyya, in collaboration with whom some of the work in this thesis was done, and Praveen Murthy. Praveen and Shuvra are also close friends and I have immensely enjoyed my interactions with them, both technical as well as nontechnical (such as music, photography, tennis, etc.). I want to thank Phil Lapsley, who helped me with the DSP lab hardware when I first joined the DSP group; Soonhoi Ha, who helped me with various aspects of the scheduling implementation in Ptolemy; and Mani Srivastava, who helped me a great deal with printed circuit board layout tools, and provided me with several useful tips that helped me design and prototype the 4 processor OMA board.

I should mention Mary Stewart and Carol Sitea for helping me with reimbursements and other bureaucratic paperwork, Christopher Hylands for patiently answering my system related queries, and Heather Levien for cheerfully helping me with the mass of graduate division related paperwork, deadlines, formalities to be completed, etc.

I have enjoyed many useful discussions with some of some of my friends and colleagues, in particular Alan Kamas (I have to mention his infectious sense of humor), Louis Yun, Wan-teh Chan, Rick Han, William Li, Tom Parks, Jose Pino, Brian Evans, Mike Williamson, Bilung Lee and Asawaree Kalavade, who have made my (innumerable) hours in Cory Hall much more fun than what would have been otherwise. I will miss the corridor/elevator discussions (on topics ranging from the weather to Hindu philosophy) with Sriram Krishnan (the *other* Sriram), Jagesh Sanghavi, Rajeev Murgai, Shankar Narayanaswami, SKI, Angela Chuang, Premal Buch; and so will I miss the discussions, reminiscences and retelling of old tales with the sizable gang of graduate students in Berkeley and Stanford with whom I share my alma mater (IIT Kanpur) — Vigyan, Adnan, Kumud, Sunil, Amit Narayan, Geetanjali, Sanjay, Vineet, Ramesh, to name a few.

While at Berkeley, I have met several people who have since become good friends: Juergen Teich, Raghuram Devarakonda, Amit Lal, Amit Marathe, Ramesh Gopalan, Datta Godbole, Satyajit Patwardhan, Aparna Pandey, Amar Kapadia. I thank them all for their excellent company; I have learned a lot from their talents and experiences as well.

I also wish to thank my long time friends Anurag, Ashish, Akshay, Anil, Kumud, Nitin, RD, Sanjiv — our occasional get-togethers and telephone chats have always provided a welcome relief from the tedium that grad school sometimes tends to become.

Of course, the Berkeley experience in general — the beautiful campus with great views of the San Francisco bay and the Golden Gate, the excellent library system, the cafe's and the restaurants, the CD shops and the used book stores, student groups and cacophonic drummers on Sproul plaza, the Hateman and the Naked Guy — has left me with indelible memories, and a wealth of interesting stories to tell, and has also helped keep my efforts towards a Ph. D. in perspective.

Finally, I wish to thank my parents for all their support and belief in me, and my sister, who has a knack for boosting my morale during rough times. I dedicate this thesis to them.

# 1

# INTRODUCTION

The focus of this thesis is the exploration of architectures and design methodologies for application-specific parallel systems for embedded applications in digital signal processing (DSP). The hardware model we consider consists of multiple programmable processors (possibly heterogeneous) and multiple applicationspecific hardware elements. Such a heterogeneous architecture is found in a number of embedded applications today: cellular radios, image processing boards, music/sound cards, robot control applications, etc. In this thesis we develop systematic techniques aimed at reducing inter-processor communication and synchronization costs in such multiprocessors that are designed to be application-specific. The techniques presented in this thesis apply to DSP algorithms that involve simple control structure; the precise domain of applicability of these techniques will be formally stated shortly.

Applications in signal processing and image processing require large computing power and have real-time performance requirements. The computing engines in such applications tend to be embedded as opposed to general-purpose. Custom VLSI implementations are usually preferred in such high throughput applications. However, custom approaches have the well known problems of long design cycles (the advances in high-level VLSI synthesis notwithstanding) and low flexibility in the final implementation. Programmable solutions are attractive in both these respects: the programmable core needs to be verified for correctness only once, and design changes can be made late in the design cycle by modifying the software program. Although verifying the embedded software to be run on a programmable part is also a hard problem, in most situations changes late in the design cycle (and indeed even after the system design is completed) are much easier and cheaper to make in the case of software than in the case of hardware.

Special processors are available today that employ an architecture and an instruction set tailored towards signal processing. Such software programmable integrated circuits are called "Digital Signal Processors" (DSP chips or DSPs for short). The special features that these processors employ are discussed by Lee in [Lee88a]. However, a single processor — even DSPs — often cannot deliver the performance requirement of some applications. In these cases, use of multiple processors is an attractive solution, where both the hardware and the software make use of the application-specific nature of the task to be performed.

Over the past few years several companies have been offering boards consisting of multiple DSP chips. More recently, semiconductor companies are offering chips that integrate multiple CPUs on a single die: Texas Instruments (the TMS320C80 multi-DSP), Star Semiconductors (SPROC chip), Adaptive Solutions (CNAPS processor), etc. Multiple processor DSPs are becoming popular because of variety of reasons. First, VLSI technology today enables one to "stamp" 4-5 standard DSPs onto a single die; this trend is only going to continue in the coming years. Such an approach is expected to become increasingly attractive because it reduces the testing time for the increasingly complex VLSI systems of the future. Second, since such a device is programmable, tooling and testing costs of building an ASIC (application-specific integrated circuit) for each different application are saved by using such a device for many different applications, a situation that is going to be increasingly important in the future with up to a tenfold improvement in integration. Third, although there has been reluctance in adopting automatic compilers for embedded DSP processors, such parallel DSP products make the use of automated tools feasible; with a large number of processors per chip, one can

afford to give up some processing power to the inefficiencies in the automatic tools. In addition new techniques are being researched to make the process of automatically mapping a design onto multiple processors more efficient — this thesis is also an attempt in that direction. This situation is analogous to how logic designers have embraced automatic logic synthesis tools in recent years — logic synthesis tools and VLSI technology have improved to the point that the chip area saved by manual design over automated design is not worth the extra design time involved: one can afford to "waste" a few gates, just as one can afford to waste processor cycles to compilation inefficiencies in a multiprocessor DSP.

Finally, there are embedded applications that are becoming increasingly important for which programmability is in fact indispensable; set-top boxes capable of recognizing a variety of audio/video formats and compression standards, multimedia workstations that are required to run a variety of different multimedia software products, programmable audio/video codecs, etc.

The generalization of such a multiprocessor chip is one that has a collection of programmable processors as well as custom hardware on a single chip. Mapping applications onto such an architecture is then a hardware/software codesign problem. The problems of inter-processor communication and synchronization are identical to the homogeneous multiprocessor case. In this thesis when we refer to a "multiprocessor" we will imply a heterogeneous architecture that may be comprised of different types of programmable processors and may include custom hardware elements too. All the techniques we present here apply to such a general system architecture.

Why study application-specific parallel processing in the first place instead of applying the ideas in general purpose parallel systems to the specific application? The reason is that general purpose parallel computation deals with a userprogrammable computing device. Computation in embedded applications, however, is usually one-time programmed by the designer of that embedded system (a digital cellular radio handset for example) and is not meant to be programmable by the end user. The computation in embedded systems is specialized (the computation in a cellular radio handset involves specific DSP functions such as speech compression, channel equalization, modulation, etc.). Furthermore, embedded applications face very different constraints compared to general purpose computation: non-recurring design costs, power consumption, and real-time performance requirements are a few examples. Thus it is important to study techniques that are application-specific, and that make use of the special characteristics of the applications they target, in order to optimize for the particular metrics that are important for that specific application. These techniques adopt a design methodology that tailors the hardware and software implementation to the particular application. Some examples of such embedded computing systems are in robot controllers [Sriv92] and real-time speech recognition systems [Stolz91]; in consumer electronics such as future high-definition televisions sets, compact disk players, electronic music synthesizers and digital audio systems; and in communication systems such as digital cellular phones and base stations, compression systems for video-phones and video-conferencing, etc.

The idea of using multiple processing units to execute one program has been present from the time of the very first electronic computer in the nineteen forties. Parallel computation has since been the topic of active research in computer science. Whereas parallelism within a single processor has been successfully exploited (instruction-level parallelism), the problem of partitioning a single user program onto multiple such processors is yet to be satisfactorily solved. Instruction-level parallelism includes techniques such as pipelining (employed in traditional RISC processors), vectorization, VLIW (very large instruction word), superscalar — these techniques are discussed in detail by Patterson and Hennessy in [Patt90]. Architectures that employ multiple CPUs to achieve task-level parallelism fall into the shared memory, message passing, or dataflow paradigms. The Stanford DASH multiprocessor [Len92] is a shared memory machine whereas the Thinking Machines CM-5 falls into the message passing category. The MIT Monsoon machine [Pap90] is an example of a dataflow architecture.

Although the hardware for the design of such multiple processor machines

— the memory, interconnect network, IO, etc. — has received much attention, software for such machines has not been able to keep up with the hardware development. Efficient partitioning of a general program (written in C say) across a given set of processors arranged in a particular configuration is still an open problem. Detecting parallelism, the overspecified sequencing in popular imperative languages like C, managing overhead due to communication and synchronization between processors, and the requirement of dynamic load balancing for some programs (an added source of overhead) makes the partitioning problem for a general program hard.

If we turn away from general purpose computation to application-specific domains, however, parallelism is easier to identify and exploit. For example, one of the more extensively studied family of such application-specific parallel processors is the systolic array architecture [Kung88][Quin84][Rao85]; this architecture consists of regularly arranged arrays of processors that communicate locally, onto which a certain class of applications, specified in a mathematical form, can be systematically mapped. We discuss systolic arrays further in section 1.3.2.

The necessary elements in the study of application-specific computer architectures are: 1) a clearly defined set of problems that can be solved using the particular application-specific approach, 2) a formal mechanism for specification of these applications, and 3) a systematic approach for designing hardware from such a specification.

In this thesis, the applications we focus on are those that can be described by Synchronous Dataflow Graphs (SDF) [Lee87] and its extensions; we will discuss this model in detail shortly. SDF in its pure form can only represent applications that have no decision making at the task level. Extensions of SDF (such as the *Boolean dataflow* (BDF) model [Lee91][Buck93]) allow control constructs, so that data-dependent control flow can be expressed in such models. These models are significantly more powerful in terms of expressivity, but they give up some of the useful analytical properties that the SDF model has. For instance, Buck shows that it is possible to simulate any Turing machine in the BDF model [Buck93]. The BDF model can therefore compute all Turing computable functions, whereas this is not possible in the case of the SDF model. We discuss the Boolean dataflow model further in Chapter 6.

In exchange for the limited expressivity of an SDF representation, we can efficiently check conditions such as whether a given SDF graph deadlocks, and whether it can be implemented using a finite amount of memory. No such general procedures can be devised for checking the corresponding conditions (deadlock behaviour and bounded memory usage) for a computation model that can simulate any given Turing machine. This is because the problems of determining if any given Turing machine halts (the halting problem), and determining whether it will use less than a given amount of memory (or tape) are *undecidable* [Lew81]; that is, no general algorithm exists to solve these problems in finite time.

In this thesis we will first focus on techniques that apply to SDF applications, and we will propose extensions to these techniques for applications that can be specified essentially as SDF, but augmented with a limited number of control constructs (and hence fall into the BDF model). SDF has proven to be a useful model for representing a significant class of DSP algorithms; several DSP tools have been designed based on the SDF and closely related models. Examples of commercial tools based on SDF are the Signal Processing Worksystem (SPW), developed by Comdisco Systems (now the Alta group of Cadence Design Systems) [Pow92][Barr91]; and COSSAP, developed by Cadis in collaboration with Meyr's group at Aachen University [Ritz92]. Tools developed at various universities that use SDF and related models include Ptolemy [Pin95a], the Warp compiler [Prin92], DESCARTES [Ritz92], GRAPE [Lauw90], and the Graph Compiler [Veig90].

The SDF model is popular because it has certain analytical properties that are useful in practice; we will discuss these properties and how they arise in the following section. The property most relevant for this thesis is that it is possible to effectively exploit parallelism in an algorithm specified in SDF by scheduling computations in the SDF graph onto multiple processors at compile or design time rather than at run time. Given such a schedule that is determined at compile time, we can extract information from it with a view towards optimizing the final implementation. The main contribution of this thesis is to present techniques for minimizing synchronization and inter-processor communication overhead in statically (i.e. compile time) scheduled multiprocessors where the program is derived from a dataflow graph specification. The strategy is to model run time execution of such a multiprocessor to determine how processors communicate and synchronize, and then to use this information to optimize the final implementation.

### **1.1** The Synchronous Dataflow model

### 1.1.1 Background

Dataflow is a well-known programming model in which a program is represented as a directed graph, where the vertices (or actors) represent computation and edges (or arcs) represent FIFO (first-in-first-out) queues that direct data values from the output of one computation to the input of another. Edges thus represent data precedences between computations. Actors consume data (or tokens) from their inputs, perform computation on them (fire), and produce certain number of tokens on their outputs.

Programs written in high-level functional languages such as pure LISP, and in dataflow languages such as Id and Lucid can be directly converted into dataflow graph representations; such a conversion is possible because these languages are designed to be *free of side-effects*, i.e. programs in these languages are not allowed to contain global variables or data structures, and functions in these languages cannot modify their arguments [Ack82]. Also, since it is possible to simulate any Turing machine in one of these languages, questions such as deadlock (or, equivalently, terminating behaviour) and determining maximum buffer sizes required to implement edges in the dataflow graph become undecidable. Several models based on dataflow with restricted semantics have been proposed; these models give up the descriptive power of general dataflow in exchange for properties that facilitate formal reasoning about programs specified in these models, and are useful in practise, leading to simpler implementation of the specified computation in hardware or software.

One such restricted model (and in fact one of the earliest graph based computation models) is the computation graph of Karp and Miller [Karp66]. In their seminal paper Karp and Miller establish that their computation graph model is *determinate*, i.e. the sequence of tokens produced on the edges of a given computation graph are unique, and do not depend on the order that the actors in the graph fire, as long as all data dependencies are respected by the firing order. The authors also provide an algorithm that, based on topological and algebraic properties of the graph, determines whether the computation specified by a given computation graph will eventually terminate. Because of the latter property, computation graphs clearly cannot simulate all Turing machines, and hence are not as expressive as a general dataflow language like Lucid or pure LISP. Computation graphs provide some of the theoretical foundations for the SDF model.

Another model of computation relevant to dataflow is the Petri net model [Peter81][Mur89]. A Petri net consists of a set of *transitions*, which are analogous to actors in dataflow, and a set of *places* that are analogous to arcs. Each transition has a certain number of input places and output places connected to it. Places may contain one or more *tokens*. A Petri net has the following semantics: a transition *fires* when all its input places have one or more tokens and, upon firing, it produces a certain number of tokens on each of its output places.

A large number of different kinds of Petri net models have been proposed in the literature for modeling different types of systems. Some of these Petri net models have the same expressive power as Turing machines: for example if transitions are allowed to posses "inhibit" inputs (if a place corresponding to such an input to a transition contains a token, then that transition is not allowed to fire) then a Petri net can simulate any Turing machine (pp. 201 in [Peter81]). Others (depending on topological restrictions imposed on how places and transitions can be interconnected) are equivalent to finite state machines, and yet others are similar to SDF graphs. Some extended Petri net models allow a notion of time, to model execution times of computations. There is also a body of work on stochastic extensions of timed Petri nets that are useful for modeling uncertainties in computation times. We will touch upon some of these Petri net models again in Chapter 4. Finally, there are Petri nets that distinguish between different classes of tokens in the specification (*colored* Petrinets), so that tokens can have information associated with them. We refer to [Peter81] [Mur89] for details on the extensive variety of Petri nets that have been proposed over the years.

The particular restricted dataflow model we are mainly concerned with in this thesis is the SDF — Synchronous Data Flow — model proposed by Lee and Messerschmitt [Lee87]. The SDF model poses restrictions on the firing of actors: the number of tokens produced (consumed) by an actor on each output (input) edge is a fixed number that is known at compile time. The arcs in an SDF graph may contain *initial tokens*, which we also refer to as **delays**. Arcs with delays can be interpreted as data dependencies across iterations of the graph; this concept will be formalized in the following chapter. In an actual implementation, arcs represent buffers in physical memory.

DSP applications typically represent computations on an indefinitely long data sequence; therefore the SDF graphs we are interested in for the purpose of signal processing must execute in a nonterminating fashion. Consequently, we must be able to obtain periodic schedules for SDF representations, which can then be run as infinite loops using a finite amount of physical memory. Unbounded buffers imply a sample rate inconsistency, and deadlock implies that all actors in the graph cannot be iterated indefinitely. Thus for our purposes, correctly constructed SDF graphs are those that can be scheduled periodically using a finite amount of memory. The main advantage of imposing restrictions on the SDF model (over a general dataflow model) lies precisely in the ability to determine whether or not an arbitrary SDF graph has a periodic schedule that neither deadlocks nor requires unbounded buffer sizes [Lee87]. The buffer sizes required to implement arcs in SDF graphs can be determined at compile time (recall that this is not possible for a general dataflow model); consequently, buffers can be allocated statically, and run time overhead associated with dynamic memory allocation is avoided. The existence of a periodic schedule that can be inferred at compile time implies that a correctly constructed SDF graph entails no run time scheduling overhead.

An SDF graph in which every actor consumes and produces only one token from each of its inputs and outputs is called a homogeneous SDF graph (HSDFG). An HSDF graph actor fires when it has one or more tokens on all its input edges; it consumes one token from each input edge when it fires, and produces one token on all its output edges when it completes execution. A general (multirate) SDF graph can always be converted into an HSDF graph [Lee86]; this transformation may result in an exponential increase in the number of actors in the final HSDF graph (see [Pin95b] for an example of an SDF graph in which this blowup occurs). Such a transformation, however, appears to be necessary when constructing periodic multiprocessor schedules from multirate SDF graphs. There is some recent work on reducing the complexity of the HSDFG that results from transforming a given SDF graph by applying graph clustering techniques to that SDF graph [Pin95b]. Since we are concerned with multiprocessor schedules in this thesis, we assume we start with an application represented as a homogeneous SDF graph henceforth, unless we state otherwise. This of course results in no loss of generality because a multirate graph is converted into a homogeneous graph for the purposes of multiprocessor scheduling anyway. In Chapter 6 we discuss how the ideas that apply to HSDF graphs can be extended to graphs containing actors that display data-dependent behaviour (i.e. dynamic actors).

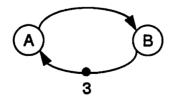

We note that an HSDFG is very similar to a marked graph in the context of Petri nets [Peter81]; transitions in the marked graph correspond to actors in the HSDFG, places correspond to edges, and initial tokens (or initial marking) of the marked graph correspond to initial tokens (or delays) in HSDFGs. We will represent delays using bullets (•) on the edges of the HSDFG; we indicate more than one delay on an edge by a number alongside the bullet, as in Fig. 1.1(a).

SDF should not be confused with synchronous languages [Hal93][Ben91] (e.g. LUSTRE, SIGNAL, and ESTEREL), which have very different semantics from SDF. Synchronous languages have been proposed for formally specifying and modeling reactive systems, i.e. systems that constantly react to stimuli from a given physical environment. Signal processing systems fall into the reactive category, and so do control and monitoring systems, communication protocols, manmachine interfaces, etc. In these languages variables are possibly infinite sequences of data of a certain type. Associated with each such sequence is a conceptual (and sometimes explicit) notion of a clock signal. In LUSTRE, each variable is explicitly associated with a clock, which determines the instants at which the value of that variable is defined. SIGNAL and ESTEREL do not have an explicit notion of a clock. The clock signal in LUSTRE is a sequence of Boolean values, and a variable in a LUSTRE program assumes its n th value when its corresponding clock takes its n th TRUE value. Thus we may relate one variable with another by means of their clocks. In ESTEREL, on the other hand, clock ticks are implicitly defined in terms of instants when the reactive system corresponding to an ESTEREL program receives (and reacts to) external events. All computations in synchronous language are defined with respect to these clocks.

In contrast, the term "synchronous" in the SDF context refers to the fact that SDF actors produce and consume fixed number of tokens, and these numbers are known at compile time. This allows us to obtain periodic schedules for SDF graphs such that the average rates of firing of actors are fixed relative to one another. We will not be concerned with synchronous languages in this thesis, although these languages have a close and interesting relationship with dataflow models used for specification of signal processing algorithms [Lee95].

### 1.1.2 Utility of dataflow for DSP

As mentioned before, dataflow models such as SDF (and other closely related models) have proven to be useful for specifying applications in signal processing and communications, with the goal of both simulation of the algorithm at the functional or behavioural level, and for synthesis from such a high level specification to a software description (e.g. a C program) or a hardware description (e.g. VHDL) or a combination thereof. The descriptions thus generated can then be compiled down to the final implementation, e.g. an embedded processor, or an ASIC.

One of the reasons for the popularity of such dataflow based models is that they provide a formalism for block-diagram based visual programming, which is a very intuitive specification mechanism for DSP; the expressivity of the SDF model sufficiently encompasses a significant class of DSP applications, including multirate applications that involve upsampling and downsampling operations. An equally important reason for employing dataflow is that such a specification exposes parallelism in the program. It is well known that imperative programming styles such as C and FORTRAN tend to over-specify the control structure of a given computation, and compilation of such specifications onto parallel architectures is known to be a hard problem. Dataflow on the other hand imposes minimal data-dependency constraints in the specification, potentially enabling a compiler to detect parallelism. The same argument holds for hardware synthesis, where it is important to be able to exploit concurrency.

The SDF model has also proven useful for compiling DSP applications on single processors. Programmable digital signal processing chips tend to have special instructions such as a single cycle multiply-accumulate (for filtering functions), modulo addressing (for managing delay lines), bit-reversed addressing (for FFT computation); DSP chips also contain built in parallel functional units that are controlled from fields in the instruction (such as parallel moves from memory to registers combined with an ALU operation). It is difficult for automatic compilers to optimally exploit these features; executable code generated by commercially available compilers today utilizes one and a half to two times the program memory that a corresponding hand optimized program requires, and results in two to three times higher execution time compared to hand-optimized code [Zivo95]. There has been some recent work on compilation techniques for embedded software target-

ted towards DSP processors and microcontrollers [Liao95]; it is still too early to determine the impact of these techniques on automatic compilation for large-scale DSP/control applications, however.

Block diagram languages based on models such as SDF have proven to be a bridge between automatic compilation and hand coding approaches; a library of reusable blocks in a particular programming language is hand coded, this library then constitutes the set of atomic SDF actors. Since the library blocks are reusable, one can afford to carefully optimize and fine tune them. The atomic blocks are fine to medium grain in size; an atomic actor in the SDF graph may implement anything from a filtering function to a two input addition operation. The final program is then automatically generated by concatenating code corresponding to the blocks in the program according to the sequence prescribed by a schedule. This approach is mature enough that there are commercial tools available today, for example the SPW and COSSAP tools mentioned earlier, that employ this technique. Powerful optimization techniques have been developed for generating sequential programs from SDF graphs that optimize for metrics such as memory usage [Bhat94].

Scheduling is a fundamental operation that must be performed in order to implement SDF graphs on both uniprocessor as well as multiprocessors. Uniprocessor scheduling simply refers to determining the sequence of execution of actors such that all precedence constraints are met and all the buffers between actors (corresponding to arcs) return to their initial states. We discuss the issues involved in multiprocessor scheduling next.

### **1.2 Parallel scheduling**

We recall that in the execution of a dataflow graph, actors fire when sufficient number of tokens are present at their inputs. The task of scheduling such a graph onto multiple processing units therefore involves assigning actors in the HSDFG to processors (the **processor assignment** step), ordering execution of these actors on each processor (the **actor ordering** step), and determining when each actor fires such that all data precedence constraints are met. Each of these three tasks may be performed either at run time (a dynamic strategy) or at compile time (static strategy). We restrict ourselves to **non-preemptive** schedules, i.e. schedules where an actor executing on a processor can not be interrupted in the middle of its execution to allow another task to be executed. This is because preemption entails a significant implementation overhead and is therefore of limited use in embedded, time-critical applications.

Lee and Ha [Lee89] propose a scheduling taxonomy based on which of the scheduling tasks are performed at compile time and which at run time; we use the same terminology in this thesis. To reduce run time computation costs it is advantageous to perform as many of the three scheduling tasks as possible at compile time, especially in the context of algorithms that have hard real-time constraints. Which of these can be effectively performed at compile time depends on the information available about the execution time of each actor in the HSDFG.

For example, dataflow computers first pioneered by Dennis [Denn80] perform the assignment step at compile time, but employ special hardware (the *tokenmatch* unit) to determine, at runtime, when actors assigned to a particular processor are ready to fire. The runtime overhead of token-matching and dynamic scheduling (within each processor) is fairly severe, so much so that dataflow architectures have not been commercially viable; even with expensive hardware support for dynamic scheduling, performance of such computers has been unimpressive.

The performance metric of interest for evaluating schedules is the average iteration period T: the average time it takes for all the actors in the graph to be executed once. Equivalently, we could use the throughput  $T^{-1}$  (i.e. the number of iterations of the graph executed per unit time) as a performance metric. Thus an optimal schedule is one that minimizes T.

In this thesis we focus on scheduling strategies that perform both processor assignment and actor ordering at compile time, because these strategies appear to be most useful for a significant class of real time DSP algorithms. Although assignment and ordering performed at run time would in general lead to a more flexible implementation (because a dynamic strategy allows for run time variations in computation load and for operations that display data dependencies) the overhead involved in such a strategy is usually prohibitive and real-time performance guarantees are difficult to achieve. Lee and Ha [Lee89] define two scheduling strategies that perform the assignment and ordering steps at compile time: fullystatic and self-timed. We use the same terminology in this thesis.

### **1.2.1** Fully-static schedules

In the fully-static (FS) strategy, the exact firing time of each actor is also determined at compile time. Such a scheduling style is used in the design of systolic array architectures [Kung88], for scheduling VLIW processors [Lam88], and in high-level VLSI synthesis of applications that consist only of operations with guaranteed worst-case execution times [DeMich94]. Under a fully static schedule, all processors run in lock step; the operation each processor performs on each clock cycle is predetermined at compile time and is enforced at run time either implicitly (by the program each processor executes, perhaps augmented with "nop"s or idle cycles for correct timing) or explicitly (by means of a program sequencer for example).

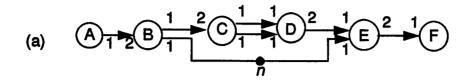

A fully-static schedule of a simple HSDFG G is illustrated in Fig. 1.1. The FS schedule is schematically represented as a Gantt chart that indicates the processors along the vertical axis, and time along the horizontal axis. The actors are represented as rectangles with horizontal length equal to the execution time of the actor. The left side of each actor in the Gantt chart corresponds to its starting time. The Gantt chart can be viewed as a processor-time plane; scheduling can then be viewed as a mechanism to tile this plane while minimizing total schedule length and idle time ("empty spaces" in the tiling process). Clearly, the FS strategy is viable only if actor execution time estimates are accurate and data-independent or if tight worst-case estimates are available for these execution times.

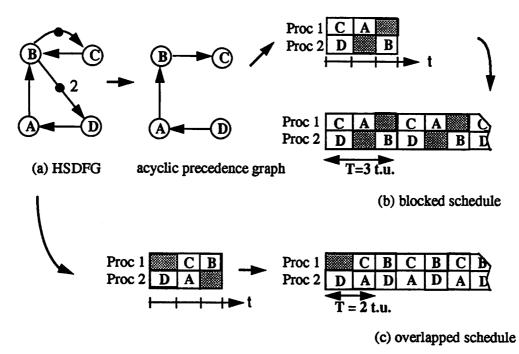

As shown in Fig. 1.1, two different types of FS schedules arise, depending

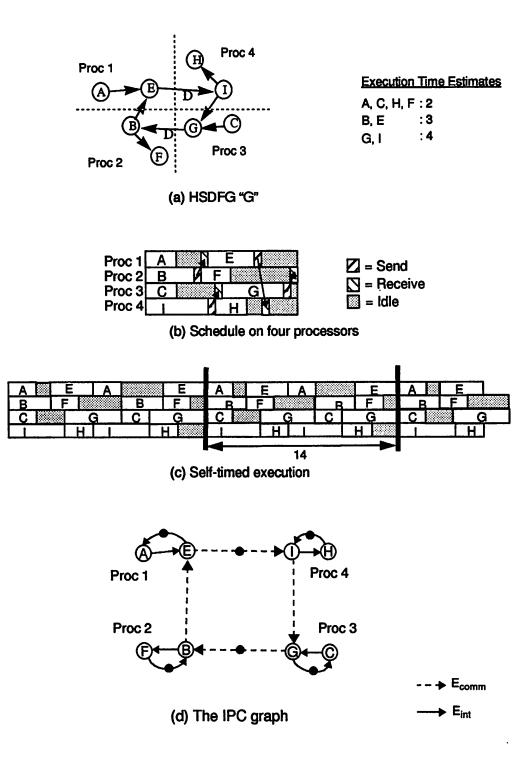

Figure 1.1. Fully static schedule

on how successive iterations of the HSDFG are treated. Execution times of all actors are assumed to be one time unit (t.u.) in this example. The FS schedule in Fig. 1.1(b) represents a blocked schedule: successive iterations of the HSDFG in a blocked schedule are treated separately so that each iteration is completed before the next one begins. A more elaborate blocked schedule on five processors is shown in Fig. 1.2. The HSDFG is scheduled as if it executes for only one iteration, i.e. inter-iteration dependencies are ignored; this schedule is then repeated to get an infinite periodic schedule for the HSDFG. The length of the blocked schedule determines the average iteration period T. The scheduling problem is then to obtain a schedule that minimizes T (which is also called the makespan of the schedule). A lower bound on T for a blocked schedule is simply the length of the critical path of the graph, which is the longest delay-free path in the graph.

Ignoring the inter-iteration dependencies when scheduling an HSDFG is equivalent to the classical multiprocessor scheduling problem for an Acyclic Precedence Graph (APG): the acyclic precedence graph is obtained from the given

(a) HSDFG "G"

(b) Static schedule

(c) Fully-static execution

HSDFG by eliminating all edges with delays on them (edges with delays represent dependencies across iterations) and replacing multiple edges that are directed between the same two vertices in the same direction with a single edge. This replacement is done because such multiple edges represent identical precedence constraints; these edges are taken into account individually during buffer assignment, however. Optimal multiprocessor scheduling of an acyclic graph is known to be NP-Hard [Garey79], and a number of heuristics have been proposed for this problem. One of the earliest, and still popular, solutions to this problem is *list scheduling*, first proposed by Hu [Hu61]. List scheduling is a greedy approach: whenever a task is ready to run, it is scheduled as soon as a processor is available to run it. Tasks are assigned priorities, and among the tasks that are ready to run at any instant, the task with the highest priority is executed first. Various researchers have proposed different priority mechanisms for list scheduling [Adam74], some of which use critical path based (CPM) methods [Ram72][Koh75][Blaz87] ([Blaz87] summarizes a large number of CPM based heuristics for scheduling).

The heuristics mentioned above ignore communication costs between processors, which is often inappropriate in actual multiprocessor implementations. An edge of the HSDFG that crosses processor boundaries after the processor assignment step represents interprocessor communication (IPC) (illustrated in Fig. 1.3(a)). These communication points are usually implemented using send and receive primitives that make use of the processor interconnect hardware. These primitives then have an execution cost associated with them that depends on the multiprocessor architecture and hardware being employed. Fully-static scheduling heuristics that take communication include costs into account [Sark89][Sih91][Prin91].

Computations in the HSDFG, however, are iterated essentially infinitely. The blocked scheduling strategies discussed thus far ignore this fact, and thus pay a penalty in the quality of the schedule they obtain. Two techniques that enable blocked schedules to exploit inter-iteration parallelism are **unfolding** and **retiming**. The unfolding strategy schedules J iterations of the HSDFG together, where J is called the **blocking factor**. Thus the schedule in Fig. 1.1(b) has J = 1. Unfolding often leads to improved blocked schedules (pp. 78-100 [Lee86], [Parhi91]), but it also implies a factor of J increase in program memory size and also in the size of the scheduling problem, which makes unfolding somewhat impractical.

Retiming involves manipulating delays in the HSDFG to reduce the critical path in the graph. This technique has been explored in the context of maximizing clock rates in synchronous digital circuits [Lei83], and has been proposed for improving blocked schedules for HSDFGs ("cutset transformations" in [Lee86], and [Hoang93]).

Fig. 1.1(c) illustrates an example of an overlapped schedule. Such a schedule is explicitly designed such that successive iterations in the HSDFG overlap. Obviously, overlapped schedules often achieve a lower iteration period than blocked schedules. In Fig. 1.1, for example, the iteration period for the blocked schedule is 3 units whereas it is 2 units for the overlapped schedule. One might wonder whether overlapped schedules are fundamentally superior to blocked schedules with the unfolding and retiming operations allowed. This question is settled in the affirmative by Parhi and Messerschmitt [Parhi91]; the authors provide an example of an HSDFG for which no blocked schedule can be found, even allowing unfolding and retiming, that has a lower or equal iteration period than the overlapped schedule they propose.

Optimal resource constrained overlapped scheduling is of course NP-Hard, although a periodic overlapped schedule in the absence of processor constraints can be computed efficiently and optimally [Parhi91][Gasp92].

Overlapped scheduling heuristics have not been as extensively studied as blocked schedules. The main work in this area is by Lam [Lam88], and deGroot [deGroot92], who propose a modified list scheduling heuristic that explicitly constructs an overlapped schedule. Another work related to overlapped scheduling is the "cyclo-static scheduling" approach proposed by Schwartz. This approach attempts to optimally tile the processor-time plane to obtain the best possible schedule. The search involved in this process has a worst case complexity exponential in the size of the input graph, although it appears that the complexity is manageable in practice, at least for small examples [Schw85].

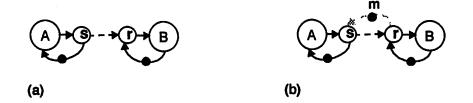

#### 1.2.2 Self-timed schedules

The fully-static approach introduced in the previous section cannot be used when actors have variable execution times; the FS approach requires precise knowledge of actor execution times to guarantee sender-receiver synchronization. It is possible to use worst case execution times and still employ an FS strategy, but this requires tight worst case execution time estimates that may not be available to us. An obvious strategy for solving this problem is to introduce explicit synchronization whenever processors communicate. This leads to the self-timed scheduling (ST) strategy in the scheduling taxonomy of Lee and Ha [Lee89]. In this strategy we first obtain an FS schedule using the techniques discussed in section 1.2, making use of the execution time estimates. After computing the FS schedule (Fig. 1.3 (b)), we simply discard the timing information that is not required, and only retain the processor assignment and the ordering of actors on each processor as specified by the FS schedule (Fig. 1.3(c)). Each processor is assigned a sequential list of actors, some of which are *send* and *receive* actors, that it executes in an infinite loop. When a processor executes a communication actor, it synchronizes with the processor(s) it communicates with. Exactly when a processor executes each actor depends on when, at run time, all input data for that actor are available, unlike the fully-static case where no such run time check is needed. Conceptually, the processor sending data writes data into a FIFO buffer, and blocks when that buffer is full; the receiver on the other hand blocks when the buffer it reads from is empty. Thus flow control is performed at run time. The buffers may be implemented using shared memory, or using hardware FIFOs between processors. In a self-timed strategy, processors run sequential programs and communicate when they execute the communication primitives embedded in their programs, as shown schematically in Fig. 1.3 (c).

Figure 1.3. Steps in a self-timed scheduling strategy

An ST strategy is robust with respect to changes in execution times of actors, because sender-receiver synchronization is performed at run time. Such a strategy, however, implies higher IPC costs compared to the fully-static strategy because of the need for synchronization (e.g. using semaphore management). In addition the ST strategy faces arbitration costs: the FS schedule guarantees mutually exclusive access of shared communication resources, whereas shared resources need to be arbitrated at run time in the ST schedule. Consequently, whereas IPC in the FS schedule simply involves reading and writing from shared memory (no synchronization or arbitration needed), implying a cost of a few processor cycles for IPC, the ST strategy requires of the order of tens of processor cycles, unless special hardware is employed for run time flow control. We discuss in detail how this overhead arises in a shared bus multiprocessor configuration in Chapter 3.

Run time flow control allows variations in execution times of tasks; in addition, it also simplifies the compiler software, since the compiler no longer needs to perform detailed timing analysis and does not need to adjust the execution of processors relative to one another in order to ensure correct sender-receiver synchronization. Multiprocessor designs, such as the Warp array [Ann87][Lam88] and the 2-D MIMD (Multiple Instruction Multiple Data) array of [Ziss87], that could potentially use fully-static scheduling, still choose to implement such run time flow control (at the expense of additional hardware) for the resulting software simplicity. Lam presents an interesting discussion on the trade-off involved between hardware complexity and ease of compilation that ensues when we consider dynamic flow control implemented in hardware versus static flow control enforced by a compiler (pp. 50-68 of [Lam89]).

#### **1.2.3** Execution time estimates and static schedules

We assume we have reasonably good estimates of actor execution times available to us at compile time to enable us to exploit static scheduling techniques; however, these estimates need not be exact, and execution times of actors may even be data-dependent. Thus we allow actors that have different execution times from one iteration of the HSDFG to the next, as long as these variations are small or rare. This is typically the case when estimates are available for the task execution times, and actual execution times are close to the corresponding estimates with high probability, but deviations from the estimates of (effectively) arbitrary magnitude occasionally occur due to phenomena such as cache misses, interrupts, user inputs or error handling. Consequently, tight worst-case execution time bounds cannot generally be determined for such operations; however, reasonably good execution time estimates can in fact be obtained for these operations, so that static assignment and ordering techniques are viable. For such applications selftimed scheduling is ideal, because the performance penalty due to lack of dynamic load balancing is overcome by the much smaller run time scheduling overhead involved when static assignment and ordering is employed.

The estimates for execution times of actors can be obtained by several different mechanisms. The most straightforward method is for the programmer to provide these estimates when he writes the library of primitive blocks. This strategy is used in the Ptolemy system, and is very effective for the assembly code libraries, in which the primitives are written in the assembly language of the target processor (Ptolemy currently supports the Motorola 56000 and 96000 processors). The programmer can provide a good estimate for blocks written in such a library by counting the number of processor cycles each instruction consumes, or by profiling the block on an instruction-set simulator.

It is more difficult to estimate execution times for blocks that contain control constructs such as data-dependent iterations and conditionals within their body, and when the target processor employs pipelining and caching. Also, it is difficult, if not impossible, for the programmer to provide reasonably accurate estimates of execution times for blocks written in a high-level language (as in the C code generation library in Ptolemy). The solution adopted in the GRAPE system [Lauw90] is to automatically estimate these execution times by compiling the block (if necessary) and running it by itself in a loop on an instruction-set simulator for the target processor. To take into account data-dependent execution behaviour, different input data sets can be provided for the block during simulation. Either the worst case or the average case execution time is used as the final estimate.

The estimation procedure employed by GRAPE is obviously time consum-

ing; in fact estimation turns out to be the most time consuming step in the GRAPE design flow. Analytical techniques can be used instead to reduce this estimation time; for example, Li and Malik [Li95] have proposed algorithms for estimating the execution time of embedded software. Their estimation technique, which forms a part of a tool called *cinderella*, consists of two components: 1) determining the sequence of instructions in the program that results in maximum execution time (program path analysis) and 2) modeling the target processor to determine how much time the worst case sequence determined in step 1 takes to execute (micro-architecture modeling). The target processor model also takes the effect of instruction pipelines and cache activity into account. The input to the tool is a generic C program with annotations that specify the loop bounds (i.e. the maximum number of iterations that a loop runs for). Although the problem is formulated as an integer linear program (ILP), the claim is that practical inputs to the tool can be efficiently analyzed using a standard ILP solver. The advantage of this approach, therefore, is the efficient manner in which estimates are obtained as compared to simulation.

It should be noted that the program path analysis component of the Li and Malik technique is in general an undecidable problem; therefore for these techniques to function, the programmer must ensure that his or her program does not contain pointer references, dynamic data structures, recursion, etc. and must provide bounds on all loops. Li and Malik's technique also depends on the accuracy of the processor model, although one can expect good models to eventually evolve for DSP chips and microcontrollers that are popular in the market.

The problem of estimating execution times of blocks is central for us to be able to effectively employ compile time design techniques. This problem is an important area of research in itself, and the strategies employed in Ptolemy and GRAPE, and those proposed by Li and Malik are useful techniques, and we expect better estimation techniques to be developed in the future.

#### **1.3** Application-specific parallel architectures

There has been significant amount of research on general purpose highperformance parallel computers. These employ expensive and elaborate interconnect topologies, memory and Input/Output (I/O) structures. Such strategies are unsuitable for embedded DSP applications as we discussed earlier. In this section we discuss some application-specific parallel architectures that have been employed for signal processing, and contrast them to our approach.

#### **1.3.1 Dataflow DSP architectures**

There have been a few multiprocessors geared towards signal processing that are based on the dataflow architecture principles of Dennis [Denn80]. Notable among these are Hughes Data Flow Multiprocessor [Gau85], the Texas Instruments Data Flow Signal Processor [Grim84], and the AT&T Enhanced Modular Signal Processor [Bloch86]. The first two perform the processor assignment step at compile time (i.e. tasks are assigned to processors at compile time) and tasks assigned to a processor are scheduled on it dynamically; the AT&T EMPS performs even the assignment of tasks to processors at runtime.

Each one of these machines employs elaborate hardware to implement dynamic scheduling within processors, and employs expensive communication networks to route tokens generated by actors assigned to one processor to tasks on other processors that require these tokens. In most DSP applications, however, such dynamic scheduling is unnecessary since compile time predictability makes static scheduling techniques viable. Eliminating dynamic scheduling results in much simpler hardware without an undue performance penalty.

Another example of an application-specific dataflow architecture is the NEC  $\mu$ PD7281 [Chase84], which is a single chip processor geared towards image processing. Each chip contains one functional unit; multiple such chips can be connected together to execute programs in a pipelined fashion. The actors are statically assigned to each processor, and actors assigned to a given processor are

scheduled on it dynamically. The primitives that this chip supports, convolution, bit manipulations, accumulation, etc., are specifically designed for image processing applications.

#### **1.3.2** Systolic and wavefront arrays

Systolic arrays consist of processors that are locally connected and may be arranged in different topologies: mesh, ring, torus, etc. The term "systolic" arises because all processors in such a machine run in lock-step, alternating between a computation step and a communication step. The model followed is usually SIMD (Single Instruction Multiple Data). Systolic arrays can execute a certain class of problems that can be specified as "Regular Iterative Algorithms (RIA)" [Rao85]; systematic techniques exist for mapping an algorithm specified in a RIA form onto dedicated processor arrays in an optimal fashion. Optimality includes metrics such as processor and communication link utilization, scalability with the problem size, achieving best possible speedup for a given number of processors, etc. Several numerical computation problems were found to fall into the RIA category: linear algebra. matrix operations. singular value decomposition, etc. (see [Kung88][Leigh92] for interesting systolic array implementations of a variety of different numerical problems). Only fairly regular computations can be specified in the RIA form; this makes the applicability of systolic arrays somewhat restrictive.

Wavefront arrays are similar to systolic arrays except that processors are not under the control of a global clock. Communication between processors is asynchronous or self-timed; handshake between processors ensures run time synchronization. Thus processors in a wavefront array can be complex and the arrays themselves can consist of a large number of processors without incurring the associated problems of clock skew and global synchronization. Again, similar to FS versus ST scheduling, the flexibility of wavefront arrays over systolic arrays comes at the cost of extra handshaking hardware.

The Warp project at Carnegie Mellon University [Anna87] is an example

of a programmable systolic array, as opposed to a dedicated array designed for one specific application. Processors are arranged in a linear array and communicate with their neighbors through FIFO queues. Programs are written for this computer in a language called W2 [Lam88]. The Warp project also led to the iWarp design [Bork88], which has a more elaborate inter-processor communication mechanism than the Warp machine. An iWarp node is a single VLSI component, composed of a computation engine and a communication engine; the latter consists of a crossbar and data routing mechanisms. The iWarp nodes can be connected in various single and two dimensional topologies, and point to point message-passing type communication is supported.

#### **1.3.3 Multiprocessor DSP architectures**

In this section we discuss multiprocessors that make use of multiple off the shelf programmable DSP chips.