Copyright © 1999, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## BSIMSOI v2.0 MOSFET MODEL - USER'S MANUAL FOR BSIMDD2.0

by

BSIM Research Group Professor Chenming Hu Manual authors: JianNong Feng, WeiDong Liu, Samuel K. H. Fung, Pin Su & Stephen Tang

Memorandum No. UCB/ERL M99/43

15 April 1999

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## **Developers:**

4 -- · h

## The BSIMDD2.0 MOSFET model is developed by

- Prof. Chenming Hu

- Dr. Weidong Liu

- Mr. Jiannong Feng

- Mr. Pin Su

- Mr. Stephen Tang

## **Developers of Previous Versions:**

- Dr. Samuel K. H. Fung

- Mr. Stephen Tang

- Mr. Pin Su

- Dr. Dennis Sinitsky

- Dr. Robert Tu

- Prof. Mansun Chan

- Prof. Ping K. Ko

- Prof. Chenming Hu

How to get a copy of this manual and source code for the model:

http://www-device.eecs.berkeley.edu/~bsim3soi

Please note that the SPICE3 core engine is distributed separately by ILP at:

http://www.eecs.berkeley.edu/~sotfware

# **Table of Content**

## Part I

\$

Chapter 1: IntroductionChapter 2: InstallChapter 3: Get StartedChapter 4: Examples

## Part II

### **Chapter 5: MOS I-V Model**

- 5.1. General Information

- 5.2. Notes on Floating Body Operation

- 5.3. Dynamic Depletion Approach

- 5.4 Body Potential for Full Depletion

- 5.5 Effective V<sub>bs</sub>

- 5.6. Bulk Charge Effect with Dynamic Depletion

- 5.7. Subthreshold Drain Current

- 5.8. Single Drain Current Equation

- 5.9. Modified Impact Ionization Current

- 5.10. Gate Induced Drain Leakage Current

- 5.11. Body Contact Current

- 5.12. Temperature Dependence

- 5.13. Notes on Compatibility with BSIM3v3.1

#### Chapter 6: MOS C-V Model

- 6.1. General Information

- 6.2. Charge Conservation

- 6.3. Intrinsic Charges

- 6.3.1. Accumulation and Inversion Charges

- 6.3.2. Channel Depletion Charge

- 6.3.3. Discussion of Body-to-Gate/Drain coupling

- 6.3.4. Backgate Charges

- 6.4. Junction Charges

- 6.5. Extrinsic Capacitances

#### **Chapter 7: Diode and BJT Model**

- 7.1. General Information

- 7.2. Notes on "Kink" in Fully Depleted Devices

- 7.3. Diode I-V Formulation

#### **Chapter 8: Parameter Extraction**

- 8.1. Extraction Strategy

- 8.2. IV Measurement

- 8.3. IV Extraction Procedure

## Part III

Appendix A: Command Line Syntax Appendix B: Parameter List Appendix C: Equation List Appendix D: Some Useful Charge Derivations Appendix E: References

# Part I

## **Chapter 1: Introduction**

BSIMSOI is the officially released SOI MOSFET model from the Device Group at the University of California at Berkeley. The model can be used for both Partially Depleted (PD) and Fully Depleted (FD) devices. Many advanced concepts are introduced so as to allow transition between PD and FD operation dynamically and continuously, namely the *Dynamic Depletion Approach*. The basic IV model is modified from BSIM3v3.1 equation set. The major features are summarized as follows:

- Dynamic depletion approach is applied on both I-V and C-V. Charge and Drain current are scaleable with T<sub>box</sub> and T<sub>si</sub> continuously.

- Supports external body bias and backgate bias; a total of 6 nodes.

- Real floating body simulation in both I-V and C-V. Body potential is properly bounded by diode and C-V formulation.

- Self heating implementation improved over the alpha version.

- An improved impact ionization current model.

- Various diode leakage components and parasitic bipolar current included.

- New depletion charge model (EBCI) introduced for better accuracy in capacitive coupling prediction. An improved BSIM3v3 based model is added as well.

- Dynamic depletion can suit different requirements for SOI technologies.

- Single I-V expression as in BSIM3v3.1 to guarantee continuities of I<sub>ds</sub>, G<sub>ds</sub> and G<sub>m</sub> and their derivatives for all bias conditions.

# **Chapter 2: Install**

BSIMDD2.0 is a UNIX application. It can be run at any computers with UNIX operating systems, such as SUN Solaris, SUN4 and so on. To display curves of simulation results, the X window system is needed. To run this model, the Berkeley SPICE3f4/3E2 engine is to be installed.

When the Berkeley SPICE is installed, two of subdirectories, *src* and *util*, can be found under the SPICE home directory. BSIMDD2.0 code has to be placed at the directory of *src/lib/dev/b3soi*. There are two SPICE engine files needed to be replaced by the files provided with this model code, *inp2m.c* and *inpdomod.c*. The two engine files are to be placed in the directory of *src/lib/inp*. There are two model card files named *nmosdd.mod* and *pmosdd.mod* which should be placed in user directory. The source code of this model can be downloaded from the BSIMSOI webpage at *http://wwwdevice.eecs.berkeley.edu/~bsim3soi*. After downloading the file named *bsimdd2.c.tar.Z*, it needs to be decoded by the UNIX utilities of *tar* and *compress* to get the source code. The command lines for decoding are:

- > uncompress bsimdd2.c.tar

- > tar -xvf bsimdd2.c.tar

When the model source code is got, place the files in correct directories described above. Then run compiling command in SPICE home directory as following,

> util/build solaris (suppose you work with Solaris computer) When finishing the compiling, the executable code named *spice3* will be placed in the directory of solaris/obj/bin which is located in outside SPICE home directory.

We strongly recommend you read the content of *BsimTerms\_use* file before you run the model code.

# **Chapter 3: Get Started**

Because the executable code is located in the directory of *solaris/obj/bin* which is outside SPICE home directory, so the path need to be set in the file of *.cshrc* or *.login* so that it can be accessed anywhere.

To run the source code, type the name of executable code in user directory,

#### > <u>spice3</u>

# Remember that the model card files should be placed in this directory for BSIMSOI models.

If the *init* file is not built (usually like this), the message as following will appear on the screen:

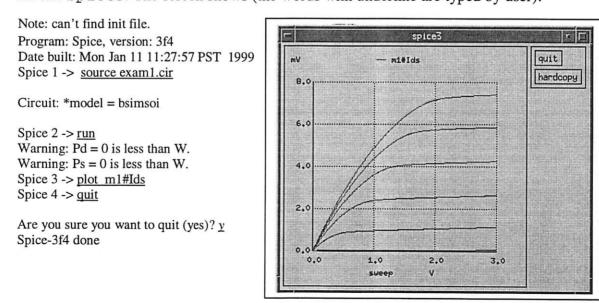

Note: can't find init file. Program: Spice, version: 3f4 Date built: Mon Jan 11 11:27:57 PST 1999 Spice1->\_

Use *source* command to input deck file containing the circuit description you want to simulate. Suppose the deck name is *mycircuit.cir*, it is

Spice1-> <u>source mycircuit.cir</u>

Circuit: \* This is an example for SPICE3

Spice2->\_

Typing run can get the simulation results. Then by typing display, all displayable parameters will be displayed on screen. Each displayable parameter can be printed or plotted by print command or plot command. More detail information about SPICE command refer to SPICE Manual.

.

## **Chapter 4: Example**

Here is an example to show how the model works. The example is to simulate a single transistor, doing DC analysis by sweeping  $v_d$  and  $v_g$ , and then plot out its  $I_{ds}$  curve. The circuit deck is as following.

```

* filename: exam1.cir

*

*model = bsimsoi

*Berkeley Spice Compatibility

*

* DD SOI NMOSFET, floating body simulation

vd d 0 dc 1.5

vs s 0 dc 0

ve e 0 dc 0

vg g 0 dc 3

m1 d g s e n1 w=10u l=0.25u debug=-1

.option gmin=1e-25 itl1=500

.dc vd 0 3 0.01 vg 0.5 3 0.5

.include nmosfd.mod

```

Put the file named *examl.cir* in user's directory, and set SPICE path to *solaris/obj/bin* (suppose the computer is SUN Solaris Workstation with X-window). In user's directory, invoke spice3. The screen shows (the words with underline are typed by user):

BSIMDD2.0 Manual Copyright © 1999, UC Berkeley

# Part II

# **Chapter 5: MOS I-V Model**

## 5.1. General Information

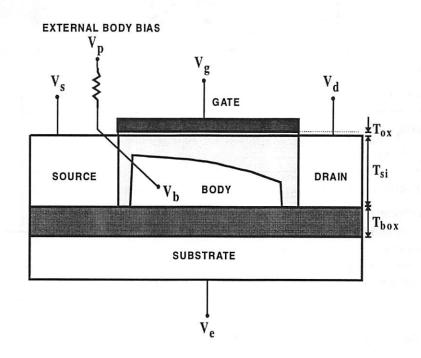

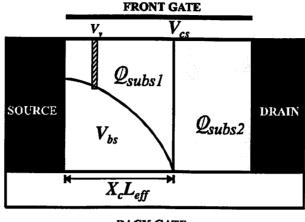

A typical SOI MOSFET structure is shown in Fig. 5-1. The device is formed on a thin SOI film of thickness  $T_{si}$  on top of a layer of buried oxide with thickness  $T_{box}$ . In the floating body configuration, there are four external biases which are gate voltage  $(V_g)$ , drain voltage  $(V_d)$ , source voltage  $(V_s)$  and substrate bias  $(V_e)$ . The voltage of internal body node  $(V_b)$  is usually iterated in circuit simulation. If a body contact is applied, there will be one more external bias, the external body contact voltage  $(V_p)$ .

#### Fig. 5-1 Schematic of a typical SOI MOSFET.

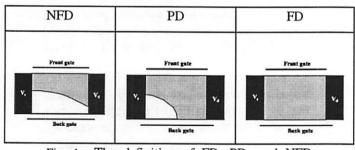

SOI MOSFET can be classified into three categories: Non-fully Depleted (NFD), Partially Depleted (PD) and Fully Depleted (FD). NFD and PD devices are often lumped into the PD category. Some researchers even classify the device right at the edge of FD as nearly Fully Depleted (n-FD). For the ease of device modeling, we would like to keep the NFD/PD/FD classification and the differences among them are summarized in Table 5.1. NFD device has almost identical characteristics as bulk device. That is why most NFD SOI models reported [5-1, 2] are developed by adding some SOI specific effects onto a bulk model. These effects include parasitic bipolar effect, self-heating and body contact resistance.

| ne il der luc                          | NFD<br>(Non-fully Depleted) | PD<br>(Partially Depleted) | FD<br>(Fully Depleted)         |

|----------------------------------------|-----------------------------|----------------------------|--------------------------------|

|                                        | Front gate                  | Front gate                 | Front gate                     |

| Backgate coupling at strong inversion  | Back gate<br>decoupled      | Back gate                  | Back gate<br>coupled           |

| Backgate coupling at subthreshold      | decoupled                   | decoupled                  | decoupled/coupled              |

| Bulk charge effect on<br>drain current | Similar to bulk MOSFET      | in between NFD and FD      | constant bulk charge +<br>DICE |

| B-S junction                           | conventional                | conventional               | fully depleted diode           |

| B-D junction                           | conventional                | fully depleted diode       | fully depleted diode           |

Table 5-1 summarizes the DC characteristics of three depletion modes.

FD SOI has very different characteristics as pointed out in the table. This is why FD SOI models are usually developed separately. There are a few FD SOI models proposed so far [5-3,4]. These models assume that the body is fully depleted in all bias configurations. FD device has very strong backgate effect. Unlike a NFD model, the

body is not floating and the body charge is constant in the model derivation. PD device has intermediate characteristic between NFD and FD. A device is classified as PD if there is possible full depletion at the drain end in normal operation. Consequently, the bulk charge effect and the body-drain diode characteristic are different than in a NFD device.

Possible transition between FD and PD behavior during transient and even DC operation has been pointed out by Sleight [5-5]. Such transition will be more significant in nearly FD device or if the buried oxide thickness is thin. The devices in advanced FD SOI technology nowadays are usually operating at nearly FD condition because the minimum SOI thickness is limited to around 40nm. In addition, buried oxide thickness is also scaled down to about 100nm so as to minimize self-heating [5-6] and short channel effect through the buried oxide [5-7]. When the backgate bias is negative with respect to the source, the back interface will be in accumulation and then it turns the device into PD. The transition can also be significant in short channel PD device [5-5]. Hence this FD/PD transition is very important in general.

A single model for all NFD/PD/FD SOI devices is necessary. For FD SOI, it is definitely needed because the transitional behavior is usually very strong. For PD SOI, the transitional behavior may be insignificant in normal bias conditions. However, as technology advances, both SOI film and buried oxide thickness may be reduced to suppress short channel effect and self-heating. In that case, the transitional behavior will become stronger. If such a model is used, this change of technology can be transparent to the circuit designer.

BSIMSOI is designed to allow automatic transition between NFD, PD and FD modes. The approach adopted in this model is named Dynamic Depletion because it can model dynamically the varying depletion conditions. Backgate effect is included in I-V and C-V formulation. SOI specific effects such as body contact, parasitic bipolar and selfheating are included. The model is formulated on top of the BSIM3v3 framework [5-8]. In this way, a lot of physical effects which are common in bulk and SOI device can be shared. These effects are reverse short channel effect, poly depletion, velocity saturation, DIBL in subthreshold and output resistance, short channel effect, mobility degradation, narrow width effect and source/drain series resistance.

## **5.2.** Notes on Floating Body Operation

One important question to ask is whether the body should be floating or not in a SOI model. In some proposed FD SOI models, the body voltage is directly derived from diode, leakage and impact ionization current. Therefore the body is not floating in these models. The advantages of non-body floating approach are a simpler model and faster computation time. However, this approach cannot model the possible transition between PD to FD. In addition, it can model the DC kink but not the frequency or time dependent kink effect [5-9, 10]. For these reasons, the body is always floating in BSIMSOI. The floating body voltage is iterated by the SPICE engine. The result of iteration is determined by the body currents. In the case of DC, body currents include diode current, impact ionization, GIDL and body contact current. For AC or transient simulations, the displacement currents originated from the capacitance also contribute.

## **5.3. Dynamic Depletion Approach**

There are several new concepts that assist the modeling of dynamic depletion. The full depletion body voltage ( $V_{bs0eff}$ ) is modeled. When  $V_{bs}$  is closed to  $V_{bs0eff}$ , the device is operating in FD condition. Another concept is the effective body bias ( $V_{bseff}$ ), which allows the use of single equation for threshold voltage, mobility and subthreshold for both the cases with and without quasi-neutral body region. The third concept is the effective bulk charge effect, which accounts for the different bulk charge effect in PD and FD operation. The final concept is the incorporation of vertical coupling dependency into the diode current. Using these concepts, the SOI physics can be integrated seamlessly into the BSIM3v3 model without much modifications. In the following, the formulation of  $V_{bs0eff}$ ,  $V_{bseff}$  and  $A_{beff}$  will be presented first. Then the expression of drain current, GIDL, diode leakage/BJT current, body contact current and temperature dependence will be described.

## 5.4. Body Potential for Full Depletion

The PD to FD transition is predominantly dependent on the body potential at full depletion. Let us denote this potential to be  $V_{bs0}$  at strong inversion and  $V_{bs0eff}$  for all

regions of operation. The conventional classification of SOI can be phrased as : if  $V_{bs0}$  is larger than 0, it is FD. Otherwise, it is PD/NFD.  $V_{bs0}$  higher than 0.4V can be considered as a "strongly" fully depleted device. It means that kink and floating body effect will be negligible. On the other hand, if  $V_{bs0}$  is less than  $-V_{dd}$ , the device will be operated as NFD most of the time. Backgate bias can have strong effect on  $V_{bs0}$  if the buried oxide is thin. It is very informative to use  $V_{bs0}$  as an index of the degree of partial depletion instead of the conventional NFD/PD/FD classification. The relationship between  $V_{bs0eff}$  and the transistor characteristic is explained first and then the formulation will be derived.

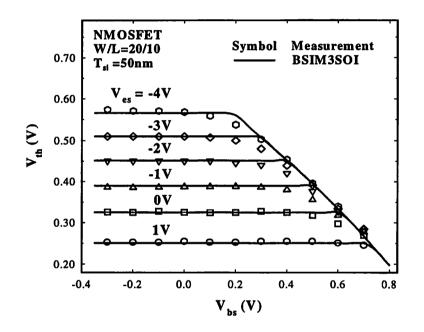

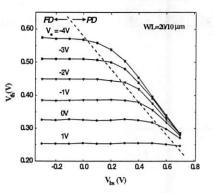

Fig. 5-2 Threshold voltage versus body bias with various backgate biases for a body-contacted FD device.

The turn-on characteristics can be affected by both the backgate bias and the external bias as shown in Fig. 5-2 and Fig. 5-3. If the device is PD (i.e.  $V_{ps} > V_{bs0eff}$ ), the external bias can contact the body and hence control the threshold voltage  $V_{th}$ . When the device becomes FD by increasing  $V_{es}$  or decreasing  $V_{ps}$  (i.e.  $V_{ps} < V_{bs0eff}$ ), the backgate bias takes over the control of  $V_{th}$ . In subthreshold operation,  $V_{bs0eff}$  increases as  $V_{gs}$  increases. As long as  $V_{bs0eff}$  is smaller than the external body bias  $(V_{ps})$ , the subthreshold swing S is the non-ideal one. When  $V_{bs0eff}$  is larger than  $V_{ps}$ , the device becomes FD and  $V_{bs}$  is tied to  $V_{bs0eff}$ . Since  $V_{bs}$  increases with  $V_{gs}$ , the subthreshold swing S is reduced.

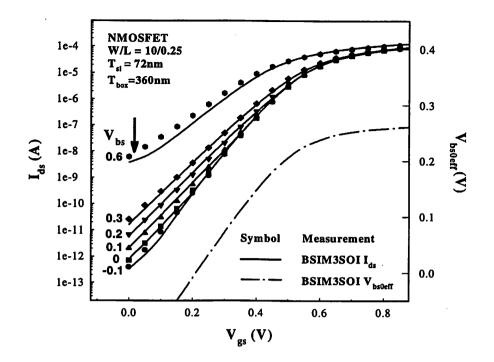

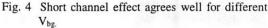

Fig. 5-3 Subthreshold characteristic of a body-contacted FD device with  $T_{si}$ =72nm under different body biases. The full depletion body voltage ( $V_{bs0eff}$ ) calculated by BSIMSOI is also plotted. The device is FD or PD depending on both  $V_{bs}$  and  $V_{gs}$ . It is PD when  $V_{bs}$  has significant effect on  $I_{ds}$ .

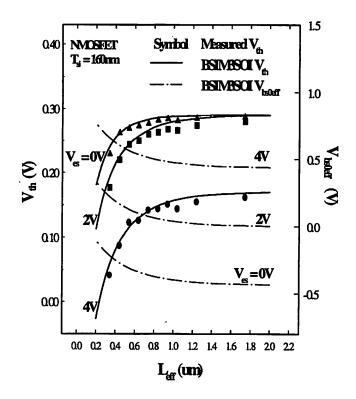

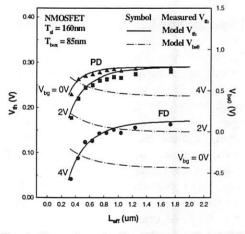

In short channel devices, the source and drain junction depletion can increase  $V_{bs0}$  [5-5]. Fig. 5.4 illustrates how this effect affects the turn-on characteristics. The long channel devices are partially depleted for  $V_{es}=0$  and 2V. As a result,  $V_{th}$  is the same for these two biases. However, short channel devices show different  $V_{th}$ . It is because  $V_{bs0}$ becomes positive in shorter devices, i.e. the devices become FD. It is therefore necessary to model the channel length dependence of  $V_{bs0}$ .

$V_{bs0}$  is derived as follows. With charge sheet approximation, the surface potential at source end is assumed to be clamped to  $\Phi_s$  at strong inversion. Hence  $V_{bs0}$  is a constant for a given backgate bias. Let us denote the  $V_{bs0}$  at back interface flatband condition to be  $V_{bs0t}$ .  $V_{bs0t}$  is also the  $V_{bs0}$  for infinitely thick buried oxide.  $V_{bs0t}$  is formulated as

$$V_{bs0t} = \phi_s - 0.5 \cdot Q_{si} / C_{si} + V_{bsa} + D_{vbd0} \cdot \left[ \exp\left(-D_{vbd1} \frac{L_{eff}}{2litl}\right) + 2 \exp\left(-D_{vbd1} \frac{L_{eff}}{litl}\right) \right] \cdot \left(V_{bi} - \phi_s\right)$$

(5.1)

where  $Q_{si}$  is the total body charge,  $C_{si}$  is the silicon film capacitance, *litl* is the characteristic length and  $V_{bi}$  is the PN junction built-in potential.  $V_{bsa}$ ,  $D_{vbd0}$  and  $D_{vbd1}$  are fitting parameters. The exponential terms account for the short channel effect on  $V_{bs0}$ ,

using a similar functional form as  $V_{th}$  [12].  $V_{bsa}$  is used to account for the error between experimental measurement and the ideal  $V_{bs0t}$  (equal to  $\phi_s - 0.5 \cdot Q_{si}/C_{si}$ ). This error can be induced by non-uniform body doping. The *electrical*  $T_{si}$ ,  $C_{si}$  and  $Q_{si}$  are then recalculated based on the non-zero  $V_{bsa}$ .

$$T_{sieff} = \sqrt{T_{si}^{2} - 2\frac{\varepsilon_{si}V_{bsa}}{qN_{a}}}, \quad C_{sieff} = \frac{\varepsilon_{si}}{T_{sieff}}, \quad Q_{sieff} = qN_{a}T_{sieff} \quad (5.2)$$

These parameters are used in all I-V calculation.

In general  $V_{bs0}$  can be expressed as a function of  $V_{bs0t}$  and the backgate bias  $V_{es}$  as follow

$$V_{bs0} = V_{bs0t} - K_{b1} \frac{V_{bs0t} - V_{es} + V_{fbb}}{1 + \frac{C_{sieff}}{C_{box}}}$$

(5.3)

where  $K_{b1}$  is a fitting parameter and  $V_{fbb}$  is the back interface flatband voltage. To keep the formulation simple, the derivation does not distinguish between back interface depletion or accumulation.

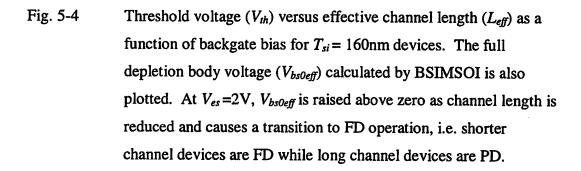

In order to extend the full depletion body potential into weak inversion, the full depletion threshold voltage  $(V_{thfd})$  is first calculated by using normal  $V_{th}$  calculation with  $V_{bs}$  substituted by  $V_{bs0}$ . In subthreshold,  $V_{bs0eff}$  and  $V_{bs0teff}$  are formulated as linear functions of  $V_{gs}$

$$V_{bs0eff} = V_{bs0} + n_{Fb} \left( V_{gs} - V_{thfd} \right)$$

(5.4)

$$V_{bs0teff} = V_{bs0t} + \left(V_{gs} - V_{thfd}\right)$$

(5.5)

where  $n_{Fb}$  is the front gate to body potential coupling ratio. This ratio is one for infinite  $T_{box}$  but less than one for finite  $T_{box}$  (Fig. 5.5).  $n_{Fb}$  is derived as follows:

At the threshold of full depletion,  $V_{bseff} = V_{bs0mos}$  where  $V_{bs0mos}$  is the effective  $V_{bs}$  if  $V_{bs}=V_{bs0}$ . The gate to body charge capacitance in our CV model is

$$\frac{dQ_b}{dV_g} = \frac{C_{ox}}{\sqrt{1 + \frac{4}{K_1^2} \left(\phi_s + K_1 \sqrt{\phi_s - V_{bs0mos}} - V_{bs0mos}\right)}}$$

(5.6)

Since the body-to-gate coupling factor is  $\frac{\frac{dQ_b}{dV_g}}{\frac{dQ_b}{dV_g} + C_{box}}, \text{ then}$   $n_{Fb} = \frac{1}{1 + K_{3b} \frac{C_{box}}{C_{ox}} \sqrt{1 + \frac{4}{K_1^2} \left(\phi_s + K_1 \sqrt{\phi_s - V_{bs0mos}} - V_{bs0mos}\right)}}$ (5.7)

where  $K_{3b}$  is a fitting parameter. This formulation allows the best match for the coupling factor between I-V and C-V models.

Figure 5-5  $V_{bs0eff}$  and  $V_{bs0teff}$  vs.  $V_{gs}$ .

## 5.5. Effective V<sub>bs</sub>

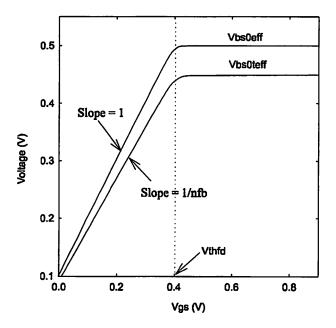

In BSIMSOI, the bulk equation for threshold and mobility calculation are used directly by replacing  $V_{bs}$  with  $V_{bseff}$ . In bulk,  $V_{bs}$  refers to the body bias of a neutral body region. An alternative interpretation is that the electric field coming from the surface channel is terminated in the body. This condition is not always true in SOI. When  $V_{bs} < V_{bs0teff}$ , the channel depletion can reach the buried oxide and the electric field terminates in the substrate below the buried oxide. In other words, the channel is coupled to the backgate. Since device parameters  $V_{th}$  and  $\mu_{eff}$  at small  $V_{ds}$  depend on the vertical E-field at channel, it is necessary to derive an effective  $V_{bs}$  that gives the same vertical electric field. The  $V_{bseff}$  calculation is illustrated in Fig. 5-6 and the expression of  $V_{bseff}$  is

$$V_{bseff} = V_{bs} - \frac{C_{sieff} \left( V_{bs0teff} - V_{bs} \right)^2}{2 \cdot Q_{sieff}}$$

(5.8)

Figure 5-6 Diagram to illustrate the calculation of  $V_{bseff}$ . The electric field at the bottom of silicon film is extrapolated to zero. By assuming the absence of buried oxide, the potential at this point is  $V_{bseff}$ .

The difference between  $V_{bseff}$  and  $V_{bs}$  becomes significant only if a large negative  $V_{es}$  is applied.

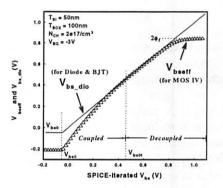

In BSIMSOI,  $V_{bs}$  is used for diode and BJT calculation while  $V_{bseff}$  is used for MOS calculation. When  $V_{bs} < V_{bs0teff}$ ,  $V_{bseff}$  is smaller than  $V_{bs}$ .  $V_{bs}$  has a lower bound of  $V_{bs0eff}$ . When  $V_{bs} > V_{bs0teff}$ ,  $V_{bs}$  and  $V_{bseff}$  are equal up to the point when  $V_{bs}$  is close to the strong inversion surface potential  $\Phi_s$ . This is because the MOS model becomes invalid at this body bias.  $V_{bseff}$  is clamped below  $\Phi_s$  by a smoothing function.

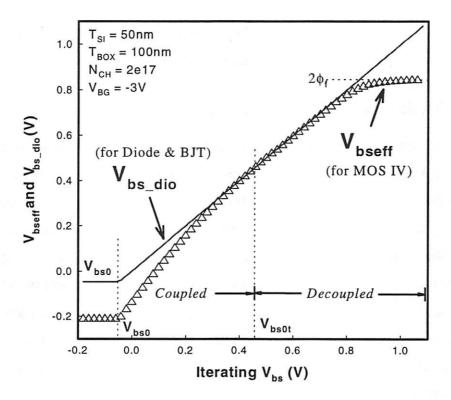

Figure 5-7  $V_{bs\_dio}$  and  $V_{bseff}$  vs. the  $V_{bs}$  being iterated by SPICE.  $V_{bs\_dio}$  is used for diode & BJT calculation while  $V_{bseff}$  is used for MOSFET.

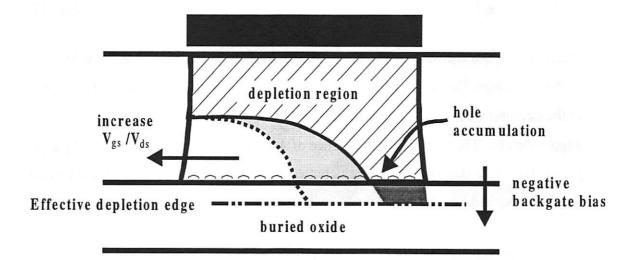

Fig. 5-8 Illustration for the dynamic depletion bulk charge effect. When a negative backgate bias is applied, a hole accumulation layer is formed. It extends the effective depletion edge into the buried

oxide and then the bulk charge effect is increased. This backgate effect is stronger under large gate and drain biases.

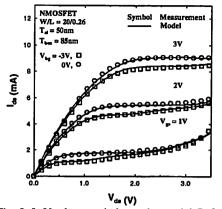

## 5.6. Bulk Charge Effect with Dynamic Depletion

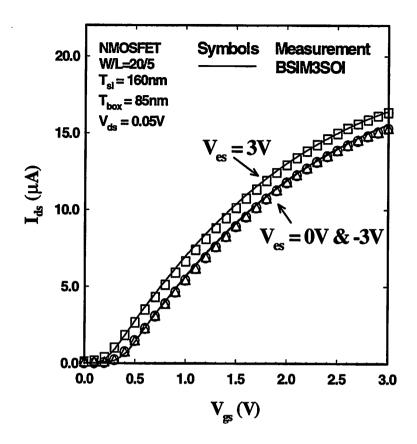

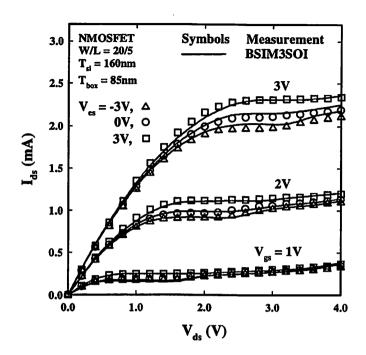

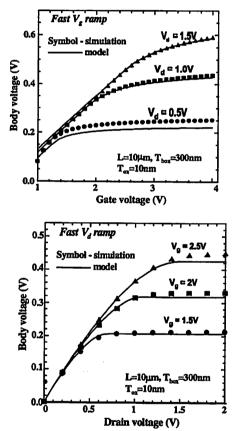

Under partially depleted condition, part of the channel near the drain is completely depleted. If a negative backgate bias is applied, the back interface is in accumulation. This can effectively thicken the silicon film as illustrated in Fig. 5-8. Then the bulk charge increases and drain current is reduced. If the gate and drain biases are large, this backgate effect becomes stronger. Fig. 5-9 and Fig 5-10 shows the experimental evidence of this phenomena. In Fig. 5-9, threshold voltage and low-field mobility are the same for backgate bias equal to -3V and 0V. However, at high drain bias, there is current enhancement from  $V_{es}$ =-3V to 0V as found in Fig. 5-10. To model this effect, a new bulk charge factor  $A_{beff}$  is extrapolated between  $A_{bulk}$  and  $A_{dice}$  using  $X_{csat}$ , the partial depletion factor at saturation

$$A_{beff} = X_{csat} A_{bulk} + (1 - X_{csat}) A_{dice}$$

(5.9)

$$A_{bulk} = 1 + \left(\frac{K_1}{2\sqrt{\phi_s}} \left(\frac{A_0 L_{eff}}{L_{eff} + 2\sqrt{T_{si} X_{dep}}} \left(1 - A_{gs} V_{gsteff} \left(\frac{L_{eff}}{L_{eff} + 2\sqrt{T_{si} X_{dep}}}\right)^2\right) + \frac{B_0}{W_{eff} + B_1}\right)\right) \frac{1}{1 + Keta \cdot V_{bseff}}$$

(5.10)

where  $A_{bulk}$  is the BSIM3v3 bulk charge factor with minor modification to avoid problems at high  $V_{bs}$ , which is quite common in SOI. The original square-root of  $(\phi_s - V_{bs})$ at the denominator is replaced by square-root of  $\phi_s$  as it can go to infinity as  $V_{bs}$ approaches  $\phi_s$ . The body bias dependence of  $A_{bulk}$  has to be adjusted by *Keta*.  $X_{csat}$  is a parameter which describes quantitatively the extent of partial depletion.  $X_{csat}=1$  means non-fully depleted operation while  $X_{csat}=0$  means fully depleted operation.

Figure 5-9 Drain current versus gate voltage for a 5 $\mu$ m long PD SOI MOSFET. The device is partially depleted for  $V_{es} = 0$  and -3V but fully depleted for  $V_{es} = 3V$ .

The surface potential with reference to source at which the film starts to be fully depleted is approximately equal to  $V_{cs}=V_{bs}-V_{bs0eff}$ .  $V_{cs}$  is always positive. In linear operation, the device is partially depleted if  $V_{cs}$  is smaller than  $V_{ds}$ . When the device is saturated, the surface potential at the pinch-off point is clamped at the drain saturation voltage  $V_{dsat}$ . Then the extent of partial depletion in the device stays unchanged in saturation. Using  $V_{cs}$ ,  $X_{csat}$  can be modeled as

$$X_{csat} = m_{xc} \left(\frac{V_{cs}}{A_{bp}V_{gst}}\right)^2 + \left(1 - m_{xc}\right) \left(\frac{V_{cs}}{A_{bp}V_{gst}}\right) \text{ where } 0 \le \frac{V_{cs}}{A_{bp}V_{gst}} \le 1$$

(5.11)

where  $A_{bp}$  and  $m_{xc}$  are fitting parameters. In SPICE implementation,  $(V_{cs}/A_{bp}*V_{gst})$  are limited to (0,1) by a smoothing function. As the device gets more fully depleted by increasing  $V_{gs}$ , reducing  $T_{si}$  or increasing  $V_{es}$ ,  $X_{csat}$  decreases and the bulk charge effect is reduced.

Figure 5-10 Drain current versus drain voltage for the same device as Fig. 5.9. The current enhancement from  $V_{es} = -3V$  to 0V is caused by the reduction of bulk charge effect.

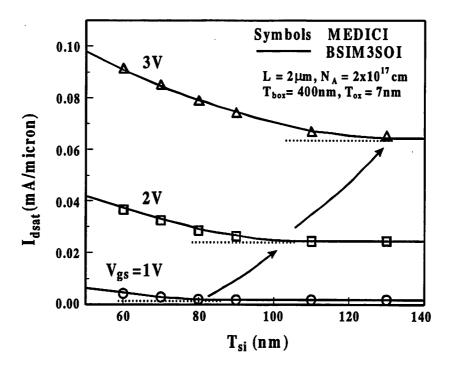

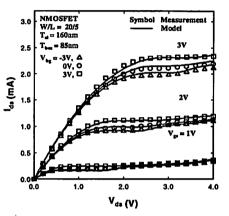

This  $A_{beff}$  model provides a simple way to incorporate back-gate dependence of bulk charge effect with the use of existing bulk MOSFET model. It predicts a continuous enhancement of drain saturation current as silicon film thickness reduces for a given technology. Fig. 5.11 shows that the saturation current calculated with this model shows a good agreement with MEDICI device simulation. At low  $V_{gs}$ , current enhancement occurs at around 80 nm in the simulation. But at  $V_{gs}=3V$ , current enhancement occurs at thicker film because of the partial reduction of body charge. This kind of  $T_{si}$  scalability is good for technology scaling and statistical analysis.

Figure 5-11 Saturation drain current  $(I_{dsat})$  vs SOI thickness  $(T_{si})$  from MEDICI simulation and BSIMSOI. At high  $V_{gs}$ , current enhancement starts at thicker  $T_{si}$ .

## 5.7. Subthreshold Drain Current

#### 5.7.1 Subthreshold current expression

BSIMSOI uses a single current formula with a smooth transition from strong inversion to subthreshold. The formula is based upon  $V_{gsteff}$  concept, directly borrowed from BSIM3v3:

$$V_{gsteff} = \frac{2nv_{t} \ln[1 + \exp(\frac{V_{gs\_eff} - V_{th}}{2nv_{t}})]}{1 + 2nC_{ox}\sqrt{\frac{2\Phi_{s}}{q\varepsilon_{si}N_{ch}}} \exp\left(-\frac{V_{gs\_eff} - V_{th} - 2V_{off}}{2nv_{t}}\right)}$$

(5-12)

### 5.7.2. Ideal, non-ideal, supra-ideal swing

The  $V_{bs0eff}$  and  $V_{bseff}$  formulation described in sections 5.4 and 5.5 can yield the experimentally observed SOI subthreshold phenomena. Assume  $V_{ds}=0$ . When the device

is in accumulation, the depletion layer width is zero, and the device is NFD. As  $V_{gs}$  increases, the device is NFD until the film is fully depleted. As long as the device is NFD, the subthreshold slope is the non-ideal one (>60mV/dec) as shown in Fig. 5.3. When the device is FD, the non-ideal subthreshold slope becomes an almost ideal one.

At high  $V_{ds}$ , body potential can be modulated by the substrate current  $I_{sub}$ . As  $V_{gs}$  is increased,  $I_{sub}$  increases to appreciably change equilibrium floating  $V_{bs}$ . Because of body effect, this translates to a change of  $V_{th}$  vs.  $V_{gs}$ , and results in a steeper subthreshold slope. Conversely, the subthreshold slope can fall below 60mV/dec even in devices that are FD for low  $V_{ds}$  (see Fig. 5.12).

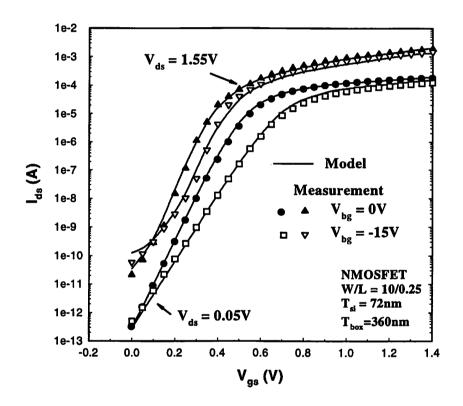

Figure 5-12 Subthreshold characteristic of a floating body "FD" device under different backgate and drain bias. The non-ideal subthreshold swing at low  $V_{ds}$  and anomalous swing at high  $V_{ds}$  are PD like behaviors brought on by negative  $V_{bg}$ .

## **5.8. Single Drain Current Equation**

The effective drain voltage  $V_{dseff}$  and effective gate overdrive voltage  $V_{gsteff}$  in BSIM3v3 are used in this model to link subthreshold, linear and saturation operation regions into an single expression. With the use of effective body voltage ( $V_{bseff}$ ) and effective bulk charge factor ( $A_{beff}$ ), the single continuous drain current formulation from BSIM3v3 can be used directly,

$$I_{ds,MOSFET} = \frac{I_{ds0}(V_{dseff})}{1 + \frac{R_{ds}I_{dso}(V_{dseff})}{V_{dseff}}} (1 + \frac{V_{ds} - V_{dseff}}{V_A})$$

(5-13)

where  $R_{ds}$  is the source/drain series resistance,  $\mu_{eff}$  is the mobility,  $E_{sat}$  is the critical electrical field at which the carrier velocity becomes saturated and  $V_A$  accounts for channel length modulation (CLM) and DIBL as in BSIM3v3. The substrate current body effect (SCBE) on  $V_A$  is eliminated because it has been taken into account explicitly by the floating body in SOI.

#### **5.9. Modified Impact Ionization Current**

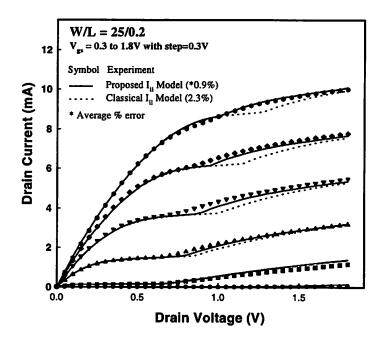

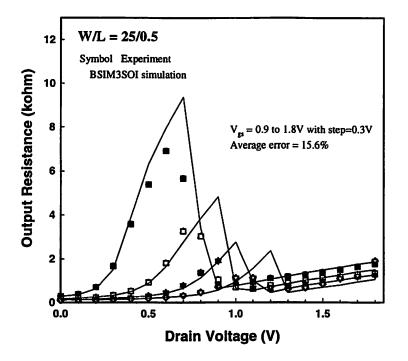

DC I-V curves in SOI depend on impact ionization current  $I_{ii}$  and so does the frequency dependence of output resistance [5-10]. That is why, unlike in bulk MOSFET simulations, it is crucial to model  $I_{ii}$  correctly. The classical  $I_{ii}$  model [5-11] is recalled as

$$I_{ii} = \frac{\alpha_0 + \alpha_1 L_{eff}}{L_{eff}} \cdot I_d \cdot \left(V_{ds} - V_{dsat}\right) \cdot \exp\left(-\frac{\beta_0}{V_{ds} - V_{dsat}}\right)$$

(5-14)

Fig. 5-13 Substrate current of a L=0.2µm device as a function of gate voltage.

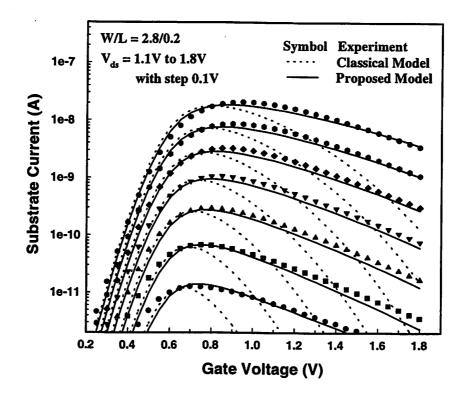

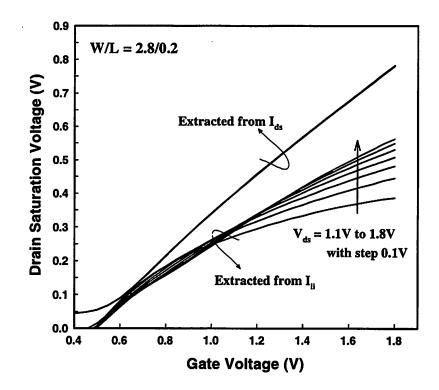

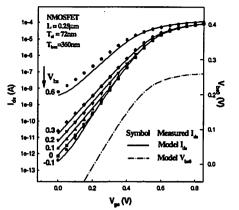

Notice that  $\alpha_1$  is added in BSIM3v3.2 to improve the channel length dependence. The classical model works well for long channel and predicting the peak  $I_{ii}$ . The  $I_{sub}$  versus  $V_{gs}$  plot of long channel devices usually shows a bell-shape. However, such plot of a 0.2µm device from current technology shows flatter curves as shown in Fig 5.13. Significant discrepancy is observed, especially for high gate bias. It is believed that  $V_{dsat}$  is not well modeled, causing a discrepancy. By using (5-15),  $V_{dsat}$  is extracted from the measured  $I_{ii}$  for the 0.2µm device with  $\alpha_0$ ,  $\alpha_1$  and  $\beta_0$  extracted at the threshold region. In Fig. 5.14, the extracted  $V_{dsat}$  is compared with the  $V_{dsat}$  used for drain current computation. The extracted  $V_{dsat}$  has a weaker gate voltage dependence. The slope of curves also has a strong  $V_{ds}$  dependency.

Fig. 5-14  $V_{dsat}$  extracted from measured  $I_{ii}$  in comparison with  $V_{dsat}$  extracted from  $I_d$  characteristics for a L=0.2µm device.

Fig. 5-15 Drain current characteristics of a L=0.2µm device.

One possible physical explanation is the channel length modulation at saturation that reduces the effective channel length. To model such behavior, we propose to use a different drain saturation voltage  $V_{dsatii}$  to replace the  $V_{dsat}$  in (5.15).  $V_{dsatii}$  is formulated by adding two modifiers  $M_1$  and  $M_2$  to the original  $V_{dsat}$  formula,

$$V_{dsatii} = \frac{E_{sat}L_{eff}V_{gst}}{M_1 E_{sat}L_{eff} + M_2 V_{gst}}, \quad M_1 = A_{ii} + \frac{B_{ii}}{L_{eff}}, \quad M_2 = 1 + \left(\frac{C_{ii}}{V_{ds} - D_{ii}}\right)^2$$

(5-15)

$M_1$  and  $M_2$  are used to correct the channel length and drain bias dependence respectively.  $M_2$  is properly bounded to avoid problem when  $V_{ds}$  is close to  $D_{ii}$ . The proposed model agrees extremely well with measurement data as shown in Fig. 5.13. Fig. 5.15 shows the  $I_d$ - $V_d$  fit for a 0.2µm device. Using the classical  $I_{ii}$  model, the simulated kink looks more abrupt and the onset drain voltage is higher. Using the proposed  $I_{ii}$  model, the average percentage error is reduced to below 1%. The DC output resistance fit is also improved as shown in Fig. 5.16. By modeling the impact ionization and diode current accurately, the self body bias can be modeled accurately as well. Hence the frequency dependence behavior can also be modeled accurately.

Fig. 5-16 DC output resistance characteristics of a L=0.2µm device.

#### 5.10. Gate Induced Drain Leakage Current

Gate Induced Drain Leakage (GIDL) can be important in SOI, because it can affect the DC body potential at low  $V_{gs}$  and high  $V_{ds}$  in long channel devices. The formula for GIDL current is:

$$I_{dgidl} = \alpha_{gidl} \cdot E_s \cdot \exp\left(-\frac{\beta_{gidl}}{E_s}\right), \ E_s = \frac{V_{ds} - V_{gs} - \chi}{3 \cdot T_{ox}}$$

(5-16)

Here  $\chi$  is the fitting parameter with a default value 1.2 which is the correct value for uniformly doped substrates with no LDD or fully overlapped LDD. However, in general  $\chi$  can be different from 1.2, depending on the doping profile at the drain edge [5-12]. For the sake of symmetry, GIDL current is accounted for both at the drain and source side.

### 5.11. Body Contact Current

For thick silicon film device, the body resistance is roughly constant. However, for thinner film, the body resistance becomes a function of body bias and backgate bias as well. When a device approaches full depletion, the body resistance becomes infinite and the device effectively turns into a floating body device. In BSIMSOI, the body resistance is expressed as

$$R_{body} = \frac{R_{bp}}{\sqrt{V_{bs} - V_{bs0eff}}} + R_{bodyext}$$

where  $R_{bp} = R_{body0} \frac{W_{eff}}{L_{eff}}$ ,  $R_{bodyext} = R_{sh}N_{rb}$  (5-17)

Here the first and second term represent the intrinsic and extrinsic body resistance respectively.  $N_{rb}$  is the number of square from the body contact to the device edge and  $R_{bsh}$  is the sheet resistance of the body contact diffusion.

#### **5.12. Temperature Dependence**

The temperature dependence of threshold voltage, mobility, saturation velocity and series resistances in BSIMSOI is identical to BSIM3v3. Temperature dependence of diode current from literature is used. Thermal resistance expression [5-6] is :

where

$$R_{th} = \frac{R_{th0}}{W_{eff}} \sqrt{\frac{T_{box}}{T_{si}}}$$

(5-18)

### 5.13. Notes on Compatibility with BSIM3v3.1

The physical  $V_{bseff}$  formulation allows complete compatibility with the bulk BSIM3v3.1 model. Basic equations for  $\mu_{eff}$ ,  $V_{th}$ ,  $V_{gsteff}$ ,  $V_{dseff}$ ,  $I_{ds0}$ ,  $V_A$  are the same or almost the same in both BSIMSOI and BSIM3v3.1. As a result the smoothness of BSIM3v3.1 is retained in BSIMSOI. Just like in BSIM3v3.1, all the parameters are physical and can be conveniently extracted. All parameters that are related to general MOSFET operation (not SOI-specific) are directly imported from BSIM3v3.1, and have the same name, which ensures parameter compatibility. The list of parameters can be found in Appendix B.

# **Chapter 6: MOS C-V Model**

## 6.1. General Information

BSIMSOI addresses physical short-channel capacitance modeling in partially and fully depleted devices. Backgate and SOI-specific parasitic capacitances are also included. The model incorporates features listed below. The new SOI-specific features are bold-faced and italicized.

- Separate effective channel length and width for IV and CV models.

- The CV model is not piece-wise (i.e. divided into inversion, depletion, and accumulation). Instead, a single equation is used for each nodal charge covering all regions of operation. This ensures continuity of all derivatives and enhances convergence properties. Just like in BSIM3v3.1, the inversion and body capacitances are continuous at the threshold voltage.

- Threshold voltage formulation is consistent with the IV model. Body effect and DIBL are automatically incorporated in the capacitance model.

- Intrinsic capacitance model has four options. The capmod =0 or 1 model option is based on simple piece-wise model from BSIM3v3.1 with the same capmod. The capmod = 2 option yields capacitance model based on BSIM3v3.1 short channel capacitance model. The channel depletion charge induced by drain voltage ( $Q_{subs}$ ) is modified to account for dynamic depletion. But it returns to the original BSIM3v3.1 formulation when silicon film is very thick as compared to depletion width. A new option (capmod=3) is introduced for better capacitive coupling prediction. This option has the same charge formulations as capmod=2 except for  $Q_{subs}$ .  $Q_{subs}$  is derived from direct integration of depletion charge from channel potential and it can yield better precision for high positive biased  $V_{bs}$ .

- Front gate overlap capacitance is comprised of two parts: 1) a bias independent part which models the effective overlap capacitance between the gate and the heavily doped source/drain, and 2) a gate bias dependent part between the gate and the LDD region.

- Bias independent fringing capacitances are added between the gate and source as well as the gate and drain. A sidewall source/drain to substrate (under the buried oxide) fringing capacitance is added.

- A source/drain-buried oxide-Si substrate parasitic MOS capacitor is added.

- Junction capacitance model accounting for dynamic depletion has been developed. It can predicts correct capacitive coupling between the source/drain and body.

- Front gate to back gate coupling charge for FD and PD devices has been developed. In a PD device, this charge is only in the fully depleted drain side region.

- Body to back gate coupling charge.

Device geometry dependencies related to  $L_{active}$  and  $W_{active}$  are the same as in BSIM3v3.1. The capacitance parameters can be found in Appendix B.

There has been significantly less work in the area of charge modeling in SOI and in MOSFETs in general. This is primarily due to the difficulty in measuring intrinsic capacitances in deep submicron MOSFETs. An alternative is the use of a 2D simulator. However, the results of a simulation are not always satisfactory.

A good intrinsic charge model is important in bulk MOSFETs because intrinsic capacitance comprises a sizable portion of the overall capacitance, and because a well behaved charge model is required for robust large circuit simulation convergence. In analog applications there are devices biased near the threshold voltage. Thus, a good charge model must be well behaved in transition regions as well. To ensure proper behavior, both the I-V and C-V model equations should be developed from an identical set of charge equations so that  $C_{ij}/I_d$  is well behaved.

A good physical charge model of SOI MOSFETs is even more important than in bulk. This is because transient behavior of a floating body node (and steady-state drain current) depends on capacitive currents, as well as the external bias point. Also, because of an extra floating body node (or a body node connected to a voltage through a body resistance), convergence issues in SOI are more volatile than in bulk, so that charge smoothness and robustness are important. For example, a large negative (floating)  $V_{bs}$  guess by SPICE can force a device into depletion, and a

smooth transition between depletion and inversion is a must. Since gate/source/drain to body capacitive coupling is important in SOI, the  $C_{body,j}=dQ_b/dV_j$  (j=gate, body, source, drain, backgate) capacitances are important as well.

As BSIMSOI is developed for NFD/PD/FD, the challenge of modeling body charge is even higher. When the silicon film thickness is comparable to the depletion width, the source/drain to body junction charge or capacitance becomes a strong function of backgate bias. Such dependence is important to model because the junction capacitance can affect the capacitive coupling in short channel devices. Besides, channel depletion is different than bulk because of possible partial depletion near the drain end. To meet the challenge, dynamic depletion approach is adopted. Full depletion body voltage and partial depletion factor described in IV section are included in the charge derivation.

## **6.2. Charge Conservation**

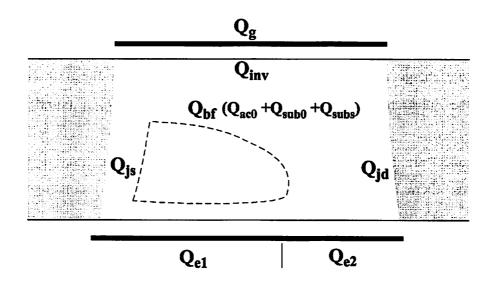

Figure 6-1 Intrinsic charge components in BSIMSOI CV model

To ensure charge conservation, terminal charges instead of terminal voltages are used as state variables. The terminal charges  $Q_g$ ,  $Q_d$ ,  $Q_s$ ,  $Q_b$ , and  $Q_e$  are the charges associated with the gate,

drain, source, body, and backgate respectively. These charges can be expressed in terms of inversion charge  $(Q_{inv})$ , accumulation charge  $(Q_{acc})$ , front body interface charge  $(Q_{bf})$ , source junction charge  $(Q_{js})$ , drain junction charge  $(Q_{jd})$ , back body interface charge  $(Q_{bb})$ , and front to back gate coupling charge  $(Q_{e2})$ . The intrinsic charges are distributed between the nodes as as shown in Fig. 6.1. The charge conservation equations are:

$$Q_{Bf} = Q_{ac0} + Q_{sub0} + Q_{subs} \tag{6.1}$$

$$Q_{inv} = Q_{inv,s} + Q_{inv,d} \tag{6.2}$$

$$Q_{g} = -(Q_{inv} + Q_{Bf} + Q_{e2})$$

(6.3)

$$Q_e = Q_{e1} + Q_{e2} \tag{6.4}$$

$$Q_b = Q_{Bf} - Q_{e1} + Q_{js} + Q_{jd}$$

(6.5)

$$Q_s = Q_{inv,s} - Q_{js} \tag{6.6}$$

$$Q_d = Q_{inv,d} - Q_{jd} \tag{6.7}$$

$$Q_g + Q_e + Q_b + Q_s + Q_d = 0 (6.8)$$

The substrate charge can be divided into two components: the substrate charge at  $V_{ds}=0$  ( $Q_{sub0}$ ), and the substrate charge induced by the drain bias ( $Q_{subs}$ ) (similar to  $\delta Q_{sub}$  in BSIM3v3.1).

All capacitances are derived from the charges to ensure charge conservation. Since there are 5 charge nodes, there are 25 (as compared to 16 in BSIM3v3.1) components. For each component:  $C_{ij} = \frac{dQ_i}{dV_j}$ , where *i* and *j* denote transistor nodes. In addition,  $\sum_i C_{ij} = \sum_j C_{ij} = 0$ .

## 6.3. Intrinsic Charges

#### 6.3.1 Accumulation and Inversion Charges

BSIMSOI uses the same expressions for accumulation charge  $(Q_{ac0})$ , body charge at  $V_{ds}=0V$  $(Q_{sub0})$  and inversion charges  $(Q_{inv})$  as in BSIM3v3.2. The three partitioning schemes for inversion charge (50/50, 40/60 and 0/100) are applicable in BSIMSOI. The  $Q_{subs}$  formulation is modified to account for dynamic depletion and provide better accuracy in capacitive coupling. The formulation of  $Q_{inv}$  and  $Q_{acc}$  are recalled below.

First, the bulk charge constant  $A_{bulkCV}$  is defined as:

$$A_{bulkCV} = A_{bulk0} \left( 1 + \frac{CLC}{L_{active}} \right)^{CLE}$$

(6.9)

where

$$A_{bulk0} = 1 + \left(\frac{K_1}{2\sqrt{\phi_s}} \left(\frac{A_0 L_{eff}}{L_{eff} + 2\sqrt{T_{si} X_{dep}}} + \frac{B_0}{W_{eff} + B_1}\right)\right) \frac{1}{1 + Keta \cdot V_{bseff}}$$

(6.10)

This is done in order to empirically fit  $V_{dsatCV}$  to channel length. Experimentally,

$$V_{dsatIV} < V_{dsatCV} < V_{dsatIV} \Big|_{L \to \infty} = \frac{V_{gsteffCV}}{A_{bulk}}$$

(6.11)

The effective CV  $V_{gst}$  is defined as:

$$V_{gsteffCV} = nv_t \ln\left(1 + \exp\left[\frac{V_{gs} - V_{th}}{nv_t}\right]\right)$$

(6.12)

Then we can calculate the CV saturation drain voltage:

$$V_{dsatCV} = V_{gsteffCV} / A_{bulkCV} .$$

(6.13)

Define effective CV  $V_{ds}$  as:

$$V_{dsCV} = V_{dsatCV} - \frac{1}{2} (V_{dsatCV} - V_{ds} - \delta_4 + \sqrt{(V_{dsatCV} - V_{ds} - \delta_4)^2 + 4\delta_4 V_{dsatCV}})$$

(6.14)

Then the inversion charge can be expressed similarly to BSIM3v3.1 as:

BSIMDD2.0 Manual Copyright © 1999, UC Berkeley

$$Q_{inv} = -W_{active} L_{active} C_{ox} \left( \left( V_{gsteffCV} - \frac{A_{bulkCV}}{2} V_{cveff} \right) + \frac{A_{bulkCV}^2 V_{cveff}^2}{12 \left( V_{gsteffCV} - \frac{A_{bulkCV}^2}{2} V_{cveff} \right)} \right)$$

(6.15)

The channel partition can be set by *Xpart* parameter. The exact evaluation of source and drain charges for each partition option are presented in Appendix C.

A parameter  $V_{FBeff}$  is used to smooth the transition between accumulation and depletion regions. The expression for  $V_{FBeff}$  is:

$$V_{FBeff} = V_{fb} - 0.5 \left( \left( V_{fb} - V_{gb} - \delta \right) + \sqrt{\left( V_{fb} - V_{gb} - \delta \right)^2 + \delta^2} \right)$$

(6.16)

where  $V_{gb} = V_{gs} - V_{bseff}$ ,  $V_{fb} = V_{th} - \phi_s - K_1 \sqrt{\phi_s - V_{bseff}}$ .

The physical meaning of the function is the following: it is equal to  $V_{gb}$  for  $V_{gb} < V_{FB}$ , and equal to  $V_{FB}$  for  $V_{gb} > V_{FB}$ . Using  $V_{FBeff}$ , the accumulation charge can be calculated as:

$$Q_{acc} = -W_{active} L_{active} C_{ox} (V_{FBeff} - V_{fb})$$

(6.17)

The gate-induced depletion charge is equal to:

$$Q_{sub0} = -W_{active} L_{active} C_{ox} \frac{K_1^2}{2} \left( -1 + \sqrt{1 + \frac{4(V_{gs} - V_{FBeff} - V_{gsteffcv} - V_{bseff})}{K_1^2}} \right)$$

(6.18)

The use of  $V_{bseff}$ , rather than  $V_{bs}$ , ensures that the body charge is constant in full depletion.

#### 6.3.2 Channel Depletion Charge

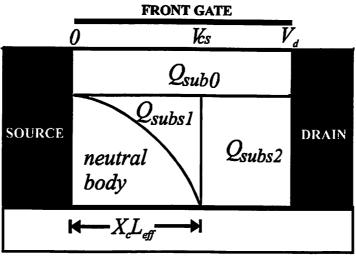

In order to allow a smooth transition from NFD, PD to FD, the channel depletion charge  $(Q_{subs})$  is partitioned into two regions: the undepleted region and depleted region. With this partition, the depletion charge can be modeled dynamically with varying terminal voltages and body charge condition. Two formulations of  $Q_{subs}$  are developed. The first one is modified from original BSIM3 CV model to incorporate the dynamic depletion effect. The second one, which based on direct integration of body charge from channel potential, yield more accurate capacitance particularly at high body bias.

#### 6.3.2.1 Dynamic Depletion BSIM3 Model

The partition of channel depletion charge is shown in Fig. 6.2.  $Q_{subsI}$  is the depletion charge induced by  $V_{ds}$  of a part of the device that is undepleted.  $Q_{subs2}$  is the depletion charge induced by  $V_{ds}$  of the depleted part at the drain side. The drain induced body charge density at distance y from the source is:

$$q_b(y) = K_1 C_{ox} \alpha \left( V_y - V_{bs} \right) \text{ where } \alpha = A_{bulkCV} - 1 \tag{6.19}$$

using the linear approximation of bulk charge with channel potential  $V_y$ . Full depletion starts to take place at the point where the depletion width is equal to

$$q_{sicv} = K_1 C_{ox} \alpha \, V_{bs0eff} \tag{6.20}$$

Notice that this body charge density  $q_{sicv}$  is not necessary equal to  $qT_{si}N_{ch}$  in the C-V model because there is body charge coupled to backgate at full depletion. Then  $V_{cs}$ , the surface potential at which full depletion starts to take place, can be solved from (6.19) and (6.20):

$$V_{cs} = V_{bs} - V_{bs0eff} \tag{6.21}$$

The distance between this point and source is  $X_c * L_{eff}$ . If the surface potential distribution along the channel  $(V_y(y))$  is known,  $X_c$  can be calculated easily by solving

$$V_{y}\left(y = X_{c}L_{eff}\right) = V_{cs} \tag{6.22}$$

and then  $Q_{subsl}$  is calculated by integrating from y=0 to  $X_c * L_{eff}$ .

$$Q_{subs1} = W \int_0^{X_c L_{eff}} K_1 C_{ox} \alpha \left( V_y - V_{bs} \right) dV_y = W K_1 C_{ox} \alpha \int_0^{V_{cs}} \left( V_y - V_{bs} \right) \left( \frac{dy}{dV_y} \right) dV_y \quad (6.23)$$

$$Q_{subs2} = WL_{eff} K_1 C_{ox} \alpha V_{cs} (1 - X_c)$$

(6.24)

**BACK GATE**

# Figure 6-2 Depletion charge partitioning in capMod = 2 BSIM3v3.1 based depletion charge model.

To find the expression for  $Q_{subsl}$ , we need to derive the channel potential profile. The drain current can be expressed as

$$I_d = WC_{ox}\mu \left[ V_{gsteff} - \alpha \ V_y \right] \frac{dV_y}{dy} = \frac{W}{L}\mu \ C_{ox} \left[ V_{gsteff} - \frac{A_{bulkCV}}{2} V_d \right] V_d$$

(6.25)

Integrating both sides from 0 to y, and changing coordinate variables to channel voltage, we get:

$$\int_{0}^{V_{y}} \left[ V_{gsteff} - \alpha \ V_{y} \right] dV_{y} = \frac{x}{L} \left[ V_{gsteff} - \frac{A_{bulkCV}}{2} V_{d} \right] V_{d}$$

(6.26)

This reduces to:

$$V_y^2 - \frac{2}{\alpha} V_y V_{gsteff} + \frac{x}{L} \left( \frac{2}{\alpha} V_{gsteff} - \frac{A_{bulkCV}}{\alpha} V_d \right) V_d = 0$$

(6.27)

Then  $V_y$  can be expressed as a function y,

$$V_{y} = \frac{1}{\alpha} V_{gsteff} - \sqrt{\frac{1}{\alpha^{2}} V_{gsteff}^{2} - \frac{y}{L} \left[ \frac{2}{\alpha} V_{gsteff} - \frac{A_{bulkCV}}{\alpha} V_{d} \right] V_{d}}$$

(6.28)

Put  $V_y = V_{cs}$  at  $x/L = X_c$ , we get  $X_c$  as

$$X_{c} = \frac{\left[\frac{2}{\alpha}V_{gsteff} - V_{cs}\right]V_{cs}}{\left[\frac{2}{\alpha}V_{gsteff} - V_{ds}\right]V_{ds}}$$

$$= \frac{\left[2 V_{dsatCV} - V_{cs}\right]V_{cs}}{\left[2 V_{dsatCV} - V_{ds}\right]V_{ds}} \quad where \quad V_{dsatCV} = \frac{V_{gsteff}}{\alpha}$$

(6.29)

The above equations only work for linear region and if  $V_{cs} < V_{ds}$ . First of all, the unification between linear region and saturation region is done by replacing  $V_{ds}$  with  $V_{dseff}$ . When  $V_{cs} > V_{ds}$ , the device is non-fully depleted and  $X_c$  should be clamped at 1. One can make sure that  $V_{cs}$  does not exceed  $V_{dseff}$  by defining

$$V_{csCV} = V_{cs} + 0.5 \left( T_1 - \sqrt{T_1^2 + \delta_{vcs} V_{dseff}}^2 \right) \text{ where } T_1 = V_{dseff} - V_{cs} - \delta_{vcs} V_{dseff}^2 \qquad (6.30)$$

By replacing  $V_{cs}$  by  $V_{csCV}$  in (6.23) and (6.24),  $Q_{subsl}$  and  $Q_{subs2}$  can vary from NFD to FD continuously. The front interface body charge induced by the drain bias ( $Q_{subs}$ ) is given by

$$Q_{subs} = Q_{subs1} + Q_{subs2} \tag{6.31}$$

#### 6.3.2.2 Exact Body Charge Integration (EBCI-BSIMSOI) Model

This model which corresponds to capMod = 3, does not derive  $Q_{subs}$  based on the approximation used in BSIM3. Instead, exact integration is carried out. This results in good accuracy of body capacitances even if  $V_{bs}$  is close to  $\Phi_s$ . The accumulation, gate-induced depletion charge and inversion charge formulation are the same as in BSIM3v3.1 based model. Below we outline the EBCI body charge model - a new model to derive SOI body charge from direct channel potential integration.

Figure 6-3 Depletion charge partitioning in capMod =3 EBCI BSIMSOI depletion charge model.

The body charge is directly integrated by using the following equation

$$q_b(y) = W_{active} L_{active} C_{ox} K_1 \sqrt{\phi_s - V_y(y)}$$

(6.32)

The charge partition is different from capMod=2 as shown in Fig. 6-3. The expression of  $Q_{subs}$  is

$$Q_{subs} = Q_{subs1} + Q_{subs2} - Q_{dep0} \tag{6.33}$$

$$Q_{dep0} = W_{active} L_{active} C_{ox} K_1 \sqrt{\phi_s - V_{bseff}}$$

(6.34)

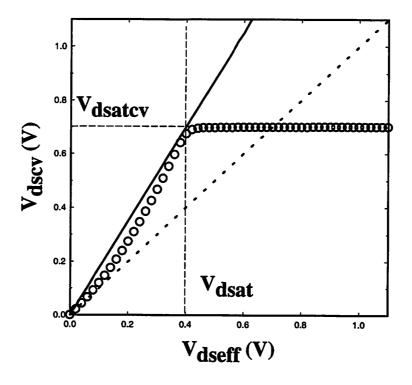

Here  $Q_{dep0}$  is the depletion charge at zero drain bias by using (6.32). To achieve the best body capacitance, the potential distribution is derived from the classical SPICE Level 2 [6-1] current model (see Appendix D for detail). The drain saturation voltage  $V_{dsatCV}$  from SPICEL2 is different from the I-V  $V_{dsat}$ :

$$V_{dsatCV} = V_{gsteff} + K_1 \sqrt{\phi_s} + \frac{K_1^2}{2} - K_1 \sqrt{V_{gsteff}} + K_1 \sqrt{\phi_s} + \phi_s + \frac{K_1^2}{4}$$

(6.35)

In this capacitance model, the drain saturation voltages for C-V and I-V are matched by defining the effective C-V drain voltage as (see Fig. 6-4)

$$V_{dsCV} = V_{dseff} + \left(V_{dsatCV} - V_{dsat}\right) \left(\frac{V_{dseff}}{V_{dsat}}\right)^2$$

(6.36)

This formulation makes sure that  $\frac{dV_{dsCV}}{dV_{dseff}} = 1$  at  $V_{dseff} = 0$  so that the drain coupling factor is equal to 0.5 at zero drain bias.

The derivation of  $X_c$  follows a similar procedure as in capMod=2 except that the formulas for channel potential and body charge density are different (see Appendix D for details).

$$X_{c} = \frac{V_{csCV} \left( V_{gsteff} + K_{1} \sqrt{\phi_{s} - V_{bs}} - 0.5 \cdot V_{csCV} \right) - \frac{2}{3} K_{1} \left[ \left( \phi_{s} + V_{csCV} - V_{bs} \right)^{\frac{1}{2}} - \left( \phi_{s} - V_{bs} \right)^{\frac{1}{2}} \right]}{V_{dsCV} \left( V_{gsteff} + K_{1} \sqrt{\phi_{s} - V_{bs}} - 0.5 \cdot V_{dsCV} \right) - \frac{2}{3} K_{1} \left[ \left( \phi_{s} + V_{dsCV} - V_{bs} \right)^{\frac{1}{2}} - \left( \phi_{s} - V_{bs} \right)^{\frac{1}{2}} \right]}$$

(6.37)

$$Q_{subs1} = W_{ef} L_{ef} C_{ac} K_{1} \frac{K_{1} \left[ \frac{2}{3} (V_{galef} + K_{1} \sqrt{\phi_{g} - V_{bs}} + (\phi_{g} - V_{bs})) ((\phi_{g} + V_{caCV} - V_{bs})^{Y_{1}} - (\phi_{g} - V_{bs})^{Y_{1}} -$$

$$Q_{subs2} = W_{effCV} L_{effCV} C_{ox} K_1 \sqrt{\phi_s - V_{bs0eff}} \cdot (1 - X_c)$$

(6.39)

Figure 6-4  $V_{dsCV}$  vs.  $V_{dseff}$

#### 6.3.3 Discussion of Body-to-Gate/Drain Coupling

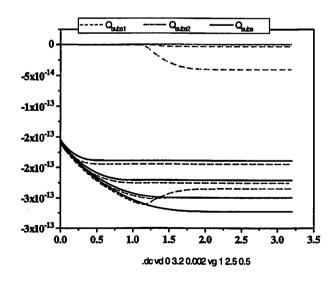

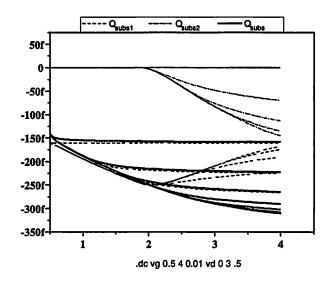

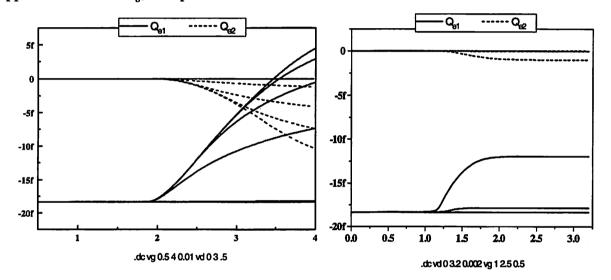

Due to a floating body node, body-to-gate/drain capacitive coupling factors are important in determining the transient value of  $V_{bs}$  [6-2]. A series of plots of front gate charge  $Q_{subs}$ , the charge components  $Q_{subs1}$  and  $Q_{subs2}$ , as well as body capacitances and body capacitive coupling ratios, unique to SOI, are presented below. The option capmod=3 was used, although analogous characteristics can be plotted for capmod=2. The corresponding .dc SPICE line is included under the plot. The Si film thickness of a device simulated is 1500Å, so that the device operates in PD mode, and there is full depletion at the drain and partial depletion at the source.

As  $V_{ds}$  increases, the total charge  $Q_{subs}$  increases, until  $V_{ds}$  reaches  $V_{dsat}$ .  $Q_{subs2}$  increases starting from the point when the drain gets fully depleted. Until that point,  $Q_{subs1}$  increases as well, but after that point it might decrease because  $X_c$  decreases. However, the total charge  $Q_{subs}$ exhibits monotonic behavior, as can be seen from both Fig. 6-5 and Fig. 6-6.

Fig. 6-5 Body charge components for the  $V_{ds}$  sweep.

Fig. 6-6 Body charge components for the  $V_{gs}$  sweep.

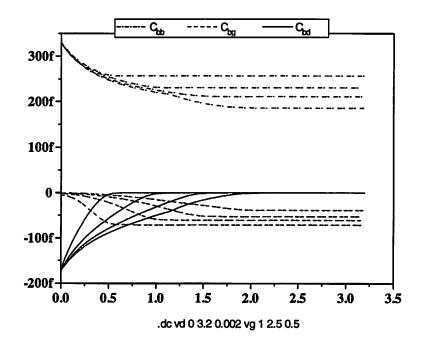

Fig. 6-7 Body capacitances for a  $V_{ds}$  sweep.

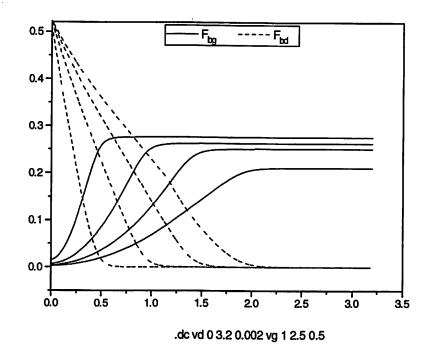

Fig. 6-8 Capacitive coupling factors as a function of a  $V_{ds}$  sweep.

Body capacitance vs.  $V_{ds}$  is plotted in Fig. 6-7. At  $V_{ds} > V_{dsat}$ , the body-to-drain capacitance  $(C_{bd})$  reduces to zero because the depletion charge becomes constant at saturation. At the same time, body-to-gate capacitance  $(C_{bg})$  and body-to-body capacitance  $(C_{bb})$  become constant. The body capacitive coupling factors  $F_{bd}(\equiv \frac{C_{bd}}{C_{bb}})$  and  $F_{bg}(\equiv \frac{C_{bg}}{C_{bb}})$  are plotted in Fig. 6-8. From

source-drain symmetry at  $V_{ds}=0, F_{bd}=0.5$ .

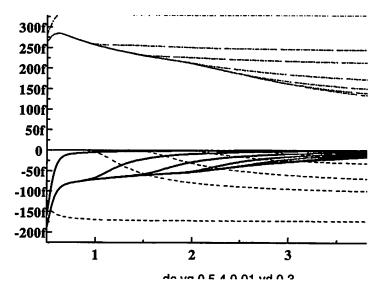

Fig. 6-9 Body capacitances as a function of a  $V_{gs}$  sweep.

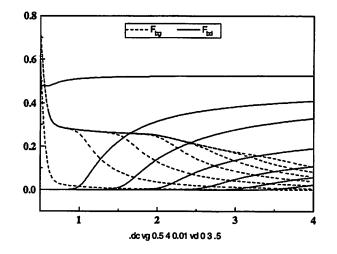

Fig. 6-10 Capacitive coupling factors as a function of a  $V_{gs}$  sweep.

As  $V_{gs}$  is increased,  $C_{bd}$  and  $C_{bb}$  follow the corresponding enveloping curves (Fig. 6-9).  $V_{gs}$  increases, the  $F_{bd}$  increases. It is because for higher  $V_{gs}$ , the device goes into triode regime and  $Q_{subs}$  becomes very sensitive to  $V_{ds}$ . At the same time, the gate gets decoupled from the body by the inversion layer and hence  $C_{bg}$  and  $F_{bg}$  drop.

#### 6.3.4 Backgate Charges

Typical SOI technology usually has buried oxide thickness ranging from 100nm to 400nm. Since the buried oxide is so thick, the backgate charge along the channel is normally negligible as compared to channel inversion and depletion charge. However, proper backgate charge model is still important in achieving a proper backgate coupling factor and the continuity of the gate charge.

As shown in Fig. 6-1, the backgate charge is divided into two parts:  $Q_{el}$  is coupled to the body and  $Q_{e2}$  is coupled to gate directly. Let first look at the case of  $V_{ds} = 0$ . The total body charge  $Q_{sicv}$  at full depletion using  $Q_{sub0}$  equation is

$$Q_{sicv} = C_{ox}WL \frac{K_1^2}{2} \left[ 1 - \sqrt{1 + \frac{4(\phi_s + K_1\sqrt{\phi_s - V_{bs0t}} - V_{bs0t})}{K_1^2}} \right]$$

(6.40)

Meanwhile, the channel depletion charge coupled to the front gate  $Q_{bf0}$  is equal to

$$Q_{bf0} = C_{ox}WL \frac{K_1^2}{2} \left( 1 - \sqrt{1 + \frac{4(\phi_s + K_1\sqrt{\phi_s - V_{bs0mos}} - V_{bs0mos})}{K_1^2}} \right)$$

(6.41)

Then  $Q_{sicv}$  -  $Q_{bf0}$  will be the amount of body charge coupled to the backgate, i.e.  $Q_{el}$ . In general when  $V_{ds}$  is greater than zero, a simple formula is derived for  $Q_{el}$

$$Q_{e1} = Q_{bf0} - Q_{sicv} - WLC_{box}X_cV_{cs}$$

(6.42)

The last term accounts for excess backgate charge when  $V_{bs}$  is larger than  $V_{bs0eff}$  in the undepleted region. The second part of backgate charge  $Q_{e2}$  is derived by assuming a linear channel potential profile from  $V_{cs}$  to  $V_{ds}$  (see Fig. 6-2) and the expression is

$$Q_{e2} = -WLC_{boxt} \frac{1 - X_c}{2} (V_{dsCV} - V_{csCV})$$

(6.43)

where  $C_{cboxt} = \frac{C_{si}C_{box}}{C_{si} + C_{box}}$  is the coupling ratio from channel to substrate. Backgate charges are plotted in Fig. 6.11 for an NFD device. The corresponding .dc SPICE input line is included in the picture. For the  $V_{ds}$  sweep, the backgate charge is nonzero when the drain side of the device becomes depleted for a high enough drain bias. Since  $V_{gst}$  modulates  $V_{dsat}$ , the same thing happens in case of a  $V_{gs}$  sweep.

Fig. 6.11 Backgate charges for a  $V_{gs}$  and a  $V_{ds}$  sweep.

#### 6.4. Junction Charges

Expressions for junction charges are similar to BSIM3v3.1. A diffusion capacitance term, which is important in forward  $V_{bs}/V_{bd}$  operation regime, is added. The parameter  $T_t$  represents the time of charge to transit across the junction. The appropriate depletion capacitance is multiplied by a factor  $G_1$ . This factor keeps track of full depletion and the variable neutral region thickness: in full depletion, since front gate-to-back gate coupling controls the channel potential, there is no coupling of the fully depleted node to the body (usually, this node is the drain). So the corresponding junction capacitance reduces to zero. The  $G_1$  formulation is dropped for the purely NFD case of ddMod=0. The expression for source-body junction charge is:

For

$$V_{bs} < 0$$

,  $Q_{jswg} = C_{jswg} \frac{T_{si}}{10^{-7}} G_{1s} \frac{P_{bswg}}{1 - Mj_{swg}} \left[ 1 - \left( 1 - \frac{V_{bs}}{P_{bswg}} \right)^{1 - M_{jswg}} \right] + T_t \cdot I_{bs1}$

else

$$Q_{jswg} = C_{jswg} \frac{T_{si}}{10^{-7}} G_{1s} V_{bs} \left( 1 + \frac{0.5M_{jswg} V_{bs}}{P_{bswg}} \right) + T_t \cdot I_{bs1}$$

(6.44)

$$G_{1s} = \sqrt{\phi_s - V_{bs0}} - \sqrt{\phi_s - V_{bs}} \tag{6.45}$$

Similarly, the drain side junction charge expression is derived by multiplying the body-drain depletion capacitance by the same factor as in (6.44), but with  $V_{bs}$  replaced by  $V_{bd}$ . The  $G_{1,2}$  term is necessary to achieve stability in full depletion, making sure that the appropriate body capacitive couplings reduce to zero due to constant body charge.

#### 6.5. Extrinsic Capacitances

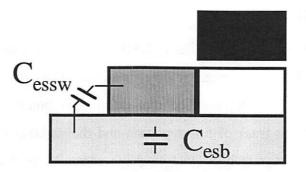

Expressions for extrinsic (parasitic) capacitances that are common in bulk and SOI MOSFETs were taken directly from BSIM3v3.1. They are source/drain-to-gate overlap capacitance and source/drain-to-gate fringing capacitance. Additional SOI-specific parasitics added are substrate-to-gource sidewall capacitance  $C_{essw}$ , and substrate-to-drain sidewall capacitance  $C_{edsw}$ , substrate-to-source bottom capacitance ( $C_{esb}$ ) and substrate-to-drain bottom capacitance ( $C_{edb}$ ) (Fig. 6-12).

Fig. 6-12 SOI MOSFET extrinsic charge components.  $C_{essw}$  is the substrate-to-source sidewall capacitance.  $C_{esb}$  is the substrate-to-source bottom capacitance.

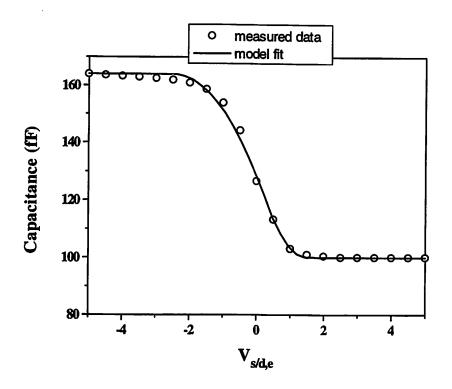

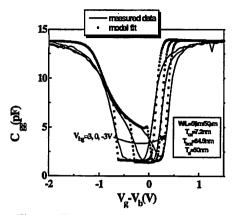

In SOI, there is a parasitic source/drain-buried oxide-Si substrate parasitic MOS structure with a bias dependent capacitance. If  $V_{s,d}=0$ , this MOS structure might be in accumulation. However, if  $V_{s,d}=V_{dd}$ , the MOS structure is in depletion with a much smaller capacitance, because the Si substrate is lightly doped. The bias dependence of this capacitance is similar to high frequency MOS depletion capacitance (Fig. 6.13). It might be substantial in devices with large source/drain diffusion areas. BSIMSOI models it by piece-wise expressions, with accurately chosen parameters to achieve smoothness of capacitance and continuity to the second derivative of charge. The substrate-to-source bottom capacitance  $C_{esb}$  is:

$$C_{esb} = \begin{cases} C_{box} & \text{if} \quad V_{se} < V_{sdfb} \\ C_{box} - \frac{1}{A_{sd}} (C_{box} - C_{\min}) \left( \frac{V_{se} - V_{sdfb}}{V_{sdth} - V_{sdfb}} \right)^2 & \text{elseif} \quad V_{se} < V_{sdfb} + A_{sd} \left( V_{sdth} - V_{sdfb} \right) \\ C_{\min} + \frac{1}{1 - A_{sd}} \left( C_{box} - C_{\min} \right) \left( \frac{V_{se} - V_{sdfb}}{V_{sdth} - V_{sdfb}} \right)^2 & \text{elseif} \quad V_{se} < V_{sdth} \\ C_{\min} & \text{elsei} \end{cases}$$

(6.46)

Physical parameters  $V_{sdfb}$  (flat-band voltage of the MOS structure) and  $V_{sdth}$  (threshold voltage of the MOS structure) can be easily extracted from measurement.  $C_{min}$  should also be extracted from measurement, and it can account for deep depletion as well. The expression for  $C_{edb}$  is similar to  $C_{esb}$ . Fig. 6.13 shows the comparison of the model and measured  $C_{esb}$ .

Fig. 6.13 Bottom source/drain to substrate capacitance for a PD SOI MOSFET.

# **Chapter 7: Diode and BJT Model**

#### 7.1. General Information

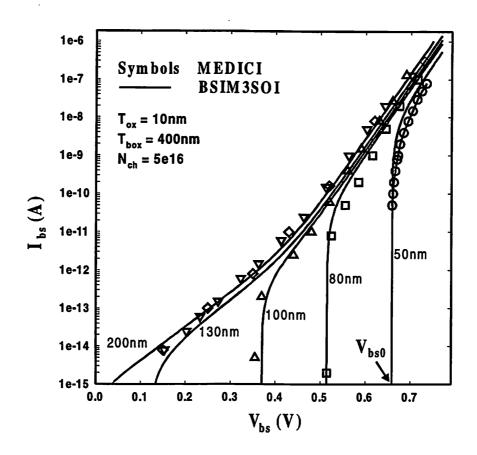

Diodes and parasitic BJT currents in SOI are extremely important in both DC and transient simulation. The current components included are body-to-source/drain injection, recombination in body-to-source/drain junction depletion region, source/drain-to-body injection, recombination in neutral body and tunneling current. Conventional p-n junction diode model is only applicable if there is presence of a neutral region. In full depletion, the minimum body potential is bound to  $V_{bs0eff}$ . As  $V_{bs}$  approaches  $V_{bs0eff}$  from above, diode can sink less and less current with a very small  $V_{bs}$  decrement. The physical explanation is that the amount of majority carriers available for diffusion or recombination becomes very small. When  $V_{bs}=V_{bs0eff}$ , diode current reduces to zero. The general equations used are

$$V_{bs0\_dio} = 0.5 \left[ V_{bs0eff} - \delta_1 + \sqrt{\left[ V_{bs0eff} - \delta_1 \right]^2 + 4\delta_1} \right]$$

(7.1)

$$I_{bs1} = W_{eff} T_{si} j_{sdif} \left( e^{\frac{V_{bs}}{n \cdot V_i}} - e^{\frac{V_{bs0\_dio}}{n \cdot V_i}} \right)$$

(7.2)

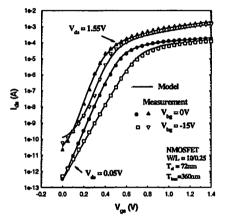

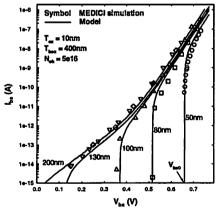

Equation (7.1) is a smoothing function that makes  $V_{bs0\_dio}$  equal to  $V_{bs0eff}$  if  $V_{bs0eff}$  is positive. Otherwise,  $V_{bs0\_dio}$  is equal to zero and the diode equation returns to the conventional diode model. The diode model shows good agreement with MEDICI simulation as shown in Fig. 7.11. The simulated structure is a gated-diode with the gate voltage biased at turn-on.

Figure 7-1 Body-source diode characteristic for different silicon film thickness from MEDICI simulation and model. The general equation used is  $I_{bs} = W \cdot T_{si} \cdot J_s \left( \exp(V_{bs}/nV_T) - \exp(V_{bs0}/nV_T) \right).$

#### 7.2. Notes on "Kink" in Fully Depleted Devices

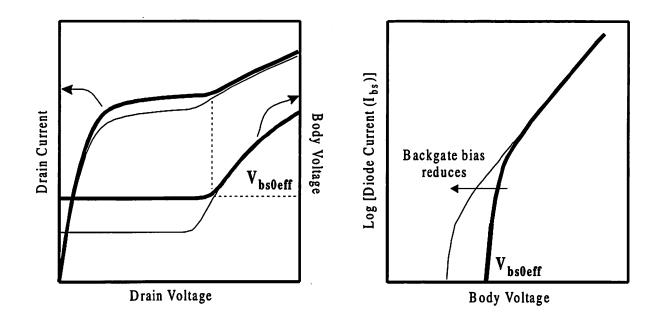

BSIMSOI relies on this diode model to tie  $V_{bs}$  to  $V_{bs0eff}$  in FD condition. When  $V_{bs}$  is close to  $V_{bs0eff}$ , the B-S diode can sink a large range of impact ionization or leakage with a small change of body potential. Hence  $V_{bs}$  will stay close to  $V_{bs0eff}$  until the level of body current is high. For this reason, the "kink" in I<sub>d</sub>-V<sub>d</sub> curve has strong dependence on  $V_{bs0eff}$  as illustrated in Fig. 7.2. If a negative backgate bias is applied,  $V_{bs0eff}$  is reduced. Hence the onset of kink occurs at smaller  $V_{ds}$  and the magnitude of kink becomes larger.

Figure 7-2 Relationship between the onset of kink in FD device and the diode current characteristics. The thinner lines have a reduced backgate bias compared to the thicker lines.

#### 7.3. Diode I-V Formulation

The formula for backward injection current in Body-Source diode is:

$$I_{bsl} = W_{eff} T_{si} j_{sdif} \left( e^{\frac{V_{bs}}{n_{dio} \cdot V_i}} - e^{\frac{V_{bs0\_dio}}{n_{dio} \cdot V_i}} \right)$$

(7.3)

Here  $n_{dio}$  is the diode non-ideality factor,  $j_{sbjt}$  and  $j_{sdif}$  are the saturation currents. The carrier recombination in the space-charge region is modeled in a similar fashion, with  $n_{dio}$  replaced by  $2n_{dio}$ :

$$I_{bs2} = W_{eff} T_{si} j_{srec} \left( e^{\frac{V_{bs}}{2n_{dio} \cdot V_i}} - e^{\frac{V_{bs0\_dio}}{2n_{dio} \cdot V_i}} \right)$$

(7.4)

The expression for the recombination current in the neutral body is assigned to  $I_{bs}$  as well, and is equal to:

$$I_{bs3} = (1 - \alpha_{bjt}) I_{bjt} \tag{7.5}$$

where  $I_{bjt}$  is the forward injection current in B-S diode and  $\alpha_{bjt}$  is the transport factor in the base (neutral body). The expression for  $I_{bjt}$  is described later.

Finally, reverse bias exponential current  $I_{bs4}$  is added to the body-to-source diode current. This current can be significant in junctions with high doping concentration (reverse bias tunneling). It can also model reverse bias avalanche junction breakdown for high negative  $V_{bs}$ . The expression is:

$$I_{bs4} = W_{eff} T_{si} j_{stun} \left( 1 - e^{-\frac{V_{bs}}{n_t \cdot V_t}} \right)$$

(7.6)

Since this current component supplies holes into the body, this current does not have a  $V_{bs0_{dio}}$  term. Finally, drain diode leakage has the same components as source, except for the body recombination component (see Appendix C).

The parasitic bipolar transistor current is very important in transient body discharge, especially in pass-gate floating body SOI designs. The BJT emitter current is modeled as

$$I_{bjt} = W_{eff} T_{si} j_{bjt} \left( e^{\frac{V_{bs}}{n \cdot V_t}} - e^{\frac{V_{bs0\_dio}}{n \cdot V_t}} \right) \left( 1 - e^{-\frac{V_{ds}}{2n \cdot V_t}} \right)$$

(7.7)

This formulation is different from the conventional BJT equations, in which the BJT current from emitter and collector are included. Inside the BSIMSOI model,  $V_{ds}$  is always positive and therefore BJT current is always flowing from source to drain and there is no need to implement the backward BJT current. This formulation gives less truncation error than the complementary implementation. The collector current becomes

$$I_{c} = I_{bjt} - I_{bs3} = \alpha_{bjt} I_{bjt}$$

, where  $\alpha_{bjt} = 1 - 0.5 \left(\frac{W_{b}}{Edl}\right)^{2}$  (7.8)

Here  $W_b$  is the basewidth including  $V_{ds}$ -dependent base shortening (see Appendix C).

The total diode leakage current is equal to  $I_{bs1}+I_{bs2}+I_{bs3}+I_{bs4}+I_{bd1}+I_{bd2}+I_{bd4}$ . The total drain current is  $I_{drain,total} = I_{ds,MOSFET} + I_c$ .

# **Chapter 8: Parameter Extraction**

#### 8.1. Extraction Strategy

The complicated physics in SOI MOSFETs makes parameter extraction quite involved. It is always preferable to have more measurements so that the parameters extracted can have more valid physical meaning. Similar to conventional bulk devices, two basic extraction strategies can be used: single device extraction, and group device extraction. The group device extraction is more popular because of several reasons. In analog circuit, channel length and width scalability is very important. In digital circuit, statistical modeling is often used to predict the circuit performance due to process variation. Hence channel length scalability is also important. Besides, model parameters extracted from group device extraction have better physical meaning than that from single device extraction. In this work, we shall emphasize on group device extraction.

Parameter extraction using body contact devices is highly recommended because parameters related to body effect, impact ionization and leakage currents can be directly extracted. This yields less ambiguity in extracting technology parameters for I-V fitting purposes.

#### 8.2. I-V Measurement

Measurement set A is used to extract basic MOS I-V parameters. For each body-contacted device :

- (A1)  $I_{ds}$  vs.  $V_{gs}$  @ small  $V_{ds}$  with different  $V_{bs}$ ,  $V_{es}=0V$ .

- (A2)  $I_{ds}$  vs.  $V_{gs}$  @  $V_{ds}=V_{dd}$  with different  $V_{bs}$ ,  $V_{es}=0$ V.

- (A3)  $I_{ds}$  vs.  $V_{ds}$  with different  $V_{gs}$  and different  $V_{bs}$ ,  $V_{es}=0V$ .

Parameters extracted include threshold voltage, body coefficient, delta L and W, series resistance, mobility, short channel effect, and subthreshold swing. (A2) is used to extract DIBL

parameters at subthreshold. (A3) is used to extract saturation velocity, body charge effect, output resistance, body contact resistance and self-heating parameters.

Measurement set B is used to extract PD/FD transition and backgate effect parameters. For each body-contacted device :

(B1)  $I_{ds}$  vs.  $V_{gs}$  @ small  $V_{ds}$  with different  $V_{bs}$  and different  $V_{es}$ .

$V_{th}$  at different  $V_{es}$  can be plotted against  $V_{bs}$  to extract  $N_{ch}$ ,  $K_1$ ,  $V_{bsa}$  and  $K_{b1}$ . Subthreshold  $V_{bs0eff}$  parameters  $(K_{b3})$  can be extracted from the subthreshold characteristic with different  $V_{es}$ 's. Length dependence parameters of  $V_{bs0}$  can be extracted by plotting  $V_{th}$  versus  $L_{eff}$ .

Measurement set C is used to extract impact ionization current parameters  $(L_1, \alpha, \beta, A_{ii}, B_{ii}, C_{ii}, D_{ii})$ . For each body-contacted device :

(C1)  $I_b$  vs.  $V_{gs}$  @ different  $V_{ds}$ ,  $V_{bs}=0V$ ,  $V_{es}=0V$ .

(C2)  $I_b$  vs.  $V_{ds}$  @ different  $V_{gs}$ ,  $V_{bs}=0V$ ,  $V_{es}=0V$ .

Measurement set D is used to extract MOS temperature dependent parameter. For a long channel body-contacted device:

(D1)  $I_{ds}$  vs.  $V_{gs}$  @ small  $V_{ds}$ ,  $V_{bs}=0V$ ,  $V_{es}=0V$ , repeat with several temperatures.

(D2)  $I_{ds}$  vs.  $V_{ds}$  @ different  $V_{gs}$ ,  $V_{bs}=0V$ ,  $V_{es}=0V$ , repeat with several temperatures.

Notice that the self-heating parameters have to be extracted from set A.

Measurement set E is used to extract diode parameters. For a long channel body-contacted device or gated diode :

(E1)  $I_{diode}$  vs.  $V_{bs}$  @  $V_{gs}$ =-1V,  $V_{es}$ =0V, repeat with several temperature

Measurement set F is used to extract BJT parameters. For each body-contacted device:

(F1)  $I_{ds}$  vs.  $I_b @ V_{gs} = -1V$ ,  $V_{es} = 0V$ ,  $V_{ds} = 1V$ .

Measurement set G is used to verify the floating body device data. For each floating-body device :

(G1)  $I_{ds}$  vs.  $V_{gs}$  @ small  $V_{ds}$  with different  $V_{es}$ .

(G2)  $I_{ds}$  vs.  $V_{gs}$  @  $V_{ds}=V_{dd}$  with different  $V_{es}$ .

(G3)  $I_{ds}$  vs.  $V_{ds}$  @ different  $V_{gs}$  and  $V_{es}$ .

Those transition parameters can be further fine tuned to fit this data set.

If the technology is NFD, those backgate related measurements can be skipped.

## 8.3. I-V Extraction Procedure

Before any model parameters can be extracted, some process parameters have to be provided. They are listed below in Table 8.1:

| Input parameter<br>names      | Physical meaning             |

|-------------------------------|------------------------------|

| T <sub>ox</sub>               | Front gate oxide thickness   |

| T <sub>box</sub>              | Back gate oxide thickness    |

| N <sub>ch</sub>               | Channel doping concentration |

| T <sub>nom</sub>              | Temperature at which data is |

|                               | taken                        |

| T <sub>si</sub>               | Si film thickness            |

| L <sub>drawn</sub>            | Mask level channel length    |

| $\mathbf{W}_{\mathbf{drawn}}$ | Mask level channel width     |

| R <sub>bsh</sub>              | Body contact external        |

|                               | diffusion resistance         |

Table 8-1 Prerequisite input parameters prior to extraction process

The procedure for parameter extraction is outlined below. These procedures are based on physical understanding of the model and based on local optimization. The availability of a body contact is assumed. The SOI-specific parameters are typed in bold letters. (Note: Fitting Target Data refers to measurement data for model extraction.)

#### Step 1

| Extracted Parameters & Fitted Target Data | Device & Experimental Data | ] |

|-------------------------------------------|----------------------------|---|

|-------------------------------------------|----------------------------|---|

| $V_{th0}, V_{bsa}, K_1, K_2$       | Large size device, A1 <sup>1</sup>                                        |

|------------------------------------|---------------------------------------------------------------------------|

|                                    | $I_{ds}$ vs. $V_{gs}$ @V <sub>ds</sub> =50mV at different V <sub>bs</sub> |

| Fitting Target Exp. Data: Vth(Vbs) | Extracted V <sub>th</sub> (V <sub>bs</sub> )                              |

# <u>Step 2<sup>2</sup></u>

| Extracted Parameters & Fitted Target Data                     | Device & Experimental Data                                 |

|---------------------------------------------------------------|------------------------------------------------------------|

| Kb <sub>1</sub>                                               | Large size device, B1                                      |

|                                                               | $I_{ds}$ vs. $V_{gs}$ @V_ds=50mV at different $V_{bs}$ and |

| Fitting Target Exp. Data: V <sub>bs0</sub> (V <sub>bs</sub> ) | V <sub>es</sub>                                            |

|                                                               | Extracted V <sub>th</sub> (V <sub>bs</sub> )               |

# <u>Step 3</u>

| Extracted Parameters & Fitted Target Data                         | Device & Experimental Data                                                |

|-------------------------------------------------------------------|---------------------------------------------------------------------------|

| μ <sub>0</sub> , μ <sub>a</sub> , μ <sub>b</sub> , μ <sub>c</sub> | Large size device, A1                                                     |

|                                                                   | $I_{ds}$ vs. $V_{gs}$ @V <sub>ds</sub> =50mV at different V <sub>bs</sub> |

| Fitting Target Exp. Strong inversion region                       |                                                                           |

| $I_{ds}(V_{gs},V_{bs})$                                           |                                                                           |

|                                                                   | Sten A                                                                    |

| Extracted Parameters & Fitted Target Data  | Device & Experimental Data                                                |

|--------------------------------------------|---------------------------------------------------------------------------|

| $L_{int}, R_{ds}(R_{dsw}W, V_{bs})$        | One set of devices (large and fixed W &                                   |

|                                            | different L), A1                                                          |

| Fitting Target Exp. Data: Strong inversion |                                                                           |

| region $I_{ds}(V_{gs}, V_{bs})$            | $I_{ds}$ vs. $V_{gs}$ @V <sub>ds</sub> =50mV at different V <sub>bs</sub> |

<sup>&</sup>lt;sup>1</sup> Measure set described in section 8.2