# Multimedia Instruction Sets for General Purpose Microprocessors: A Survey

Nathan T. Slingerland and Alan Jay Smith

## Report No. UCB/CSD-00-1124

December 2000

Computer Science Division (EECS)

University of California

Berkeley, California 94720

## Multimedia Extensions for General Purpose Microprocessors: A Survey

Nathan Slingerland and Alan Jay Smith {slingn, smith}@cs.berkeley.edu

Computer Science Division EECS Department University of California at Berkeley

December 21, 2000

#### Abstract

The last decade has seen the integration of audio, video, and 3D graphics into traditional workloads as well as the emergence of new workloads dominated by the processing of data representing such information. Initially, these emerging workloads were supported by dedicated, application specific integrated circuits and digital signal processors. In order to avoid the added cost and complexity of these dedicated hardware solutions, microprocessor vendors have extended their architectures with instructions targeting multimedia applications. Despite general agreement on the direction of evolving workloads, there is little agreement on the nature of the architectural changes that should be made to support them. The focus of this work is to survey existing multimedia instruction sets and examine how their functionality maps to a set of computationally important kernels extracted from the previously developed Berkeley multimedia workload.

#### 1 Introduction

The data paths of general purpose microprocessors are 32 or 64-bits wide, while multimedia applications operate on data that is typically 8 (video, imaging) or 16 (audio) bits wide. This mismatch means that only a fraction of the data path and functional units are actually utilized. Multimedia extensions recognize that by partitioning functional units (for example by simply blocking carry bits, in the case of an adder), processing resources can be utilized more efficiently. Partitioned arithmetic, subword parallelism, and single instruction multiple data (SIMD) processing are all used as synonyms for this method of performing parallel operations on lower-precision data packed into word-oriented datapaths (although the term "SIMD" has other meanings as well).

The remainder of this paper is organized as follows: Section 2 gives a brief background on the historical and architectural

Funding for this research has been provided by the State of California under the MICRO program, and by Cisco Corporation, Fujitsu Microelectronics, IBM, Intel Corporation, Maxtor Corporation, Microsoft Corporation, Sun Microsystems, Toshiba Corporation and Veritas Software Corporation.

motivations behind each vendor's multimedia instruction set, while Section 3 compares the instruction set design in detail (first comparing integer, then floating point and finally data type independent functionality). Section 4 surveys the available methods for programming with multimedia instruction sets. Our analysis is summarized in Section 5.

## 2 Background

All major microprocessor vendors have defined multimedia instruction set extensions for their architectures (Table 1). There are large differences in the degree and type of support which the various multimedia extensions offer. In this section we present an overview of the available multimedia instruction sets in the order of their introduction, as well as providing background on design goals and considerations where possible. The date of initial product release is noted in parentheses by the heading for each extension, with an asterisk (\*) denoting extensions which have not yet been implemented in released hardware.

#### 2.1 Hewlett Packard MAX-1 (1994)

Hewlett Packard's MAX-1 for speeding partitioned integer operations was the first multimedia extension. It allowed for the implementation of a totally software MPEG-1 (352x240) or SIF resolution) decoder on the low end HP712 workstation (PA-7100LC CPU running at 80MHz). Originally, a scalar high level language implementation of MPEG decoding took 2 seconds (0.5 frames per second) on a 50 MHz HP720 workstation for video only (no audio). The algorithms and software were then optimized (without any multimedia instructions), realizing 4-5 fps. At that time, multimedia enhancements to the forth coming PA-7100LC processor were considered. Since it was already deep in the implementation phase, a requirement was that any chip enhancements that were added should not adversely impact its design schedule, complexity, cycle time or chip area [Lee95b]. Rather than add special purpose MPEG circuitry to the processor, the same design principles were used as when selecting instructions for the original PA-RISC architecture. This involved finding the most frequent

| Vendor   | Extension       | Base ISA          | Announced      | Product        | Instructions | Register File              |

|----------|-----------------|-------------------|----------------|----------------|--------------|----------------------------|

| HP       | MAX-1           | PA-RISC           | unknown        | 1994 [Lee97b]  | 9            | Integer (31x64b)           |

| Sun      | VIS             | SPARC v9          | unknown        | 1995 [Kohn95]  | 121          | FP (32x64b)                |

| HP       | MAX-2           | PA-RISC w/MAX-1   | 1995 [HP95]    | 1995 [Lee97b]  | 8            | Integer (32x64b)           |

| MIPS     | MIPS-V          | MIPS-IV           | 1996 [SGI96]   | =              | 29           | FP (32x64b)                |

| MIPS     | MDMX            | MIPS-V            | 1996 [SGI96]   | =              | 74           | FP (32x64b), Acc. (1x192b) |

| Intel    | MMX             | x86               | 1996 [Intel96] | 1997 [Intel97] | 57           | FP (8x64b)                 |

| DEC      | MVI             | Alpha             | 1996 [Bann96]  | 1997 [Carl97]  | 13           | Integer (31x64b)           |

| Cyrix    | Extended MMX    | x86  w/MMX        | unknown        | 1997 [Cyrix]   | 12           | FP (8x64b)                 |

| AMD      | 3DNow!          | x86  w/MMX        | 1997 [AMD97]   | 1998 [AMDWP]   | 21           | FP (8x64b)                 |

| Intel    | SSE             | x86  w/MMX        | 1998 [Veit98]  | 1999 [Intel99] | 70           | 8x128b                     |

| Motorola | AltiVec         | PowerPC           | 1998 [Phil98]  | 1999 [Moto99]  | 162          | 32x128b                    |

| MIPS     | MIPS-3D         | MIPS64            | 1999 [Thek99]  | =              | 23           | FP (32x64b)                |

| AMD      | Enhanced 3DNow! | x86 w/MMX, 3DNow! | 1999 [AMD99]   | 1999 [AMD99]   | 24           | FP (8x64b)                 |

| Intel    | SSE2            | x86  w/MMX, SSE   | 2000[Intel00a] | -              | 144*         | 8x128b                     |

Table 1: **Microprocessor Multimedia Extensions** - the register file used by multimedia instructions may be shared with existing integer (Integer) or floating point (FP) registers, or be separate, with a geometry of N registers each with a width of W bits (NxWb). \*Note that 68 of the 144 SSE2 instructions are 128-bit wide versions of 64-bit wide MMX/SSE integer instructions.

operations, breaking them down into simple primitives, and accelerating their execution [Lee95]. The changes that were implemented allowed for the decoding of MPEG audio and SIF video simultaneously at up to 30 fps.

#### 2.2 Sun VIS (1995)

Sun's partitioned integer Visual Instruction Set (VIS) was first implemented in hardware on the UltraSPARC I processor, with all successive processors (UltraSPARC II, Ultra-SPARC III, UltraSPARC III) also supporting the instructions included in this extension. The primary motivation behind the creation of the VIS extension was to create a standard platform for multimedia applications such as 3D visualization and MPEG-1/MPEG-2 coding on future SPARC systems. Prior to the VIS extension, multimedia applications required specialized graphics hardware. By implementing VIS on the processor overall system cost is lowered and valuable expansion slots are freed. Unlike a cost conscious multimedia processor or ASIC, VIS is able to take advantage of agressive upgrades in frequency due to cutting edge technology and process improvements in the processor. VIS instructions were defined by examining a variety of graphics and multimedia algorithms. Any potential instruction had to execute in a single cycle or be easily pipelined, be applicable to several algorithms and not affect the cycle time of the processor [Trem 96].

#### 2.3 Hewlett Packard MAX-2 (1995)

Hewlett Packard further enhanced its PA-RISC processor multimedia capabilities with PA-RISC 2.0 (of which the partitioned integer MAX-2 extension is a subset), first implemented in the PA-8000 processor. In MAX-2 two approaches

were used for multiplication depending on the media stream being processed. For audio and 3D graphics transformations, the full power and versatility of the floating point multiply-accumulate functional units are proffered. In lower precision applications that are typified by multiplications by constants, multiplications are accomplished through a series of compound packed shift and add instructions [Lee97b].

An integer multiplier takes three to four times the area of an integer adder, three times the latency and produces a result that is longer than each operand [Lee 97c]. Using the floating-point FMAC (multiply-accumulate) units saved considerable die area. This was determined to outweigh the relatively minor disadvantage of using the same general-purpose integer registers normally used for addresses and loop counter variables for packed data. Architectures which utilize a separate register file or reuse floating point registers for SIMD operations are able to maintain a greater number of pointers and scalar integer variables in the integer register file without spilling to memory. In addition, pipeline complexity was reduced by not having a true integer multiply since it is a multicycle operation, while all other existing integer instructions are single cycle [Lee96b]. For applications such as MPEG decoding, video can be processed in the integer registers by MAX-2 instructions while audio is manipulated in parallel in floating point.

## 2.4 MIPS MDMX (1996\*)

MIPS' MDMX is a partitioned integer instruction set which shares 32 64-bit registers with the floating point register file, but has an architecture centered around a special purpose 192-bit accumulator register. Many of MDMX's arithmetic operations can either explicitly specify a destination register or implicitly accumulate into the accumulator. The parti-

tioning of the accumulator is determined by the format of the elements being accumulated and is set according to the particular instruction executed. When accumulating packed unsigned bytes, the accumulator is partitioned into eight 24-bit unsigned slices. Packed 16-bit operations cause the accumulator to be split into four 48-bit sections. This way multiple accumulations can occur without overflow, although the burden of remembering the current accumulator format is left to the programmer [MIPS97]. MIPS Technologies Inc. no longer manufactures its own processor designs. Instead, it licenses its intellectual property (core designs) to other companies interested in manufacturing MIPS designs for their own products. No processor designs implementing MDMX have yet been announced.

#### 2.5 MIPS MIPS-V/MIPS-64 (1996\*)

The MIPS64 instruction set (previously known as MIPS-V) is a superset of all previous MIPS instruction sets (MIPS-I through MIPS-IV), adding a paired single precision floating point data type. Target applications include 3D geometry processing for VRML and other OpenGL applications. MIPS-V will be implemented for the first time on the upcoming MIPS64 20K (code-named "Ruby") processor design, representing 6-8% of the total floating point die area [Thek99]. Both NEC and Toshiba are expected to manufacture the MIPS64 20K processor, which also has low power consumption as a design goal (estimated to be 900 mW at 300 MHz), beginning in late 2000. [Edwa00].

### 2.6 Intel MMX (1997)

Intel's MMX partitioned integer multimedia extension was first implemented in the P55 Pentium processor (AMD licensed MMX from Intel for their K6 processor around the same time). The design of MMX had as its first priority to substantially improve the performance of multimedia, communications and emerging Internet applications. The applications studied included MPEG-1 and MPEG-2 video, music synthesis, speech compression, speech recognition, image processing, 3D graphics in games, video conferencing, modems and audio. These were collected from a variety of sources and analyzed with profiling tools to determine the characteristics of their critical code sequences. An important design criterion was that processors implementing MMX be able to run existing operating systems without modification. This meant that no new architectural state could be introduced (no new registers or exceptions). MMX technology was mapped onto the existing floating point architecture and registers [Mitt97]. Sharing the x87 floating point register space meant that both multimedia and floating point instructions could not be used concurrently. In addition, in order to return the x87 FP stack to a sane state after MMX operations, an EMMS (empty multimedia state) instruction must be used. The EMMS instruction had very high latency in early implementations, but current processors have improved upon this significantly.

#### 2.7 DEC MVI (1997)

The DEC Alpha 21164PC processor was the first DEC processor to incorporate the partitioned integer Motion Video Instructions (MVI) multimedia extension. (Note that DEC is now a part of Compag corporation; we use the now obsolete name "DEC" for historical consistency.) All DEC Alpha processors released after the 21164PC (21264/21264A/21364) include the MVI instructions as well. The target applications during design were H.261 and H.263 teleconferencing at 30 fps, as well as DVD video playback at 30 fps with stereo audio [Carl97]. The goal of Alpha MVI was to enable software video encoders that would produce quality comparable to hardware encoders. DEC architects did not choose to implement a broader repertoire of multimedia instructions because they reasoned that available memory bandwidth limitations minimize the overall benefit of multimedia instructions. They point out that extensions such as MMX essentially try to fix some of the x86 legacy architecture deficiencies which are not present on Alpha, such as a severly limited number of registers and poor floating point organization [Rubi96].

### 2.8 Cyrix Extended MMX (1997)

Like AMD, Cyrix also licensed MMX from Intel for use in Cyrix's 6x86MX and later processors. They also extended MMX with a set of instructions which attempt to help alleviate the register pressure issues caused by the x86 destructive operand format (one operand register must also act as the destination register). This is accomplished by introducing the concept of implied registers. For a given first source register, an implied destination register is defined, effectively creating a three operand format. Besides augmenting basic MMX register utilization, packed average, sum of absolute differences, conditional moves and a 16-bit rounded multiplication operation were also added [Cyrix].

#### 2.9 AMD 3DNow! (1998)

For the K6-2 processor, AMD took an independent role by defining its own 3DNow! extension, which utilizes the same registers and basic instruction formats as MMX, but adds a partitioned floating point data type. This allows for two parallel single precision floating point operations to be computed in parallel. During their initial analysis of floating point multimedia codes, the architects of 3DNow! found two compelling possibilities in the design space. The first, being a floating point extension to MMX, was the path actually taken. The other was a full set of independent instructions as in Motorola's AltiVec (e.g. a large number of wide registers, four operand instruction format). They found that anything in between these two solutions would require significantly greater hardware area or complexity without a corresponding performance benefit [Ober99].

#### 2.10 Intel SSE (1999)

Intel's follow up to MMX, the Internet Streaming SIMD Extension (SSE), is primarily a partitioned floating point extension which addresses 3D geometry calculations, software rendering, video encoding/decoding, and speech recognition. It also incorporates feedback on MMX from software vendors in the form of new packed integer instructions. Unlike MMX, the floating point side of SSE does add new architectural state to the Intel architecture. This reduced implementation complexity and eased programming model issues, as well as allowing for SSE and MMX or x87 (normal floating point capabilities) to be used concurrently. The operating system support issue was avoided by having operating system vendors update their software well in advance of the release of SSE.

The Pentium III processor is the first from Intel to offer an implementation of SSE. Implementing a data path greater than 128-bits was not viewed as a reasonable option when balancing cost against potential benefits when first implementing the extensions during the design of the Pentium III chip. Pentium II floating point busses and registers were already 80bits wide due to the way x87 floating point is implemented. 128-bits was seen as a marginal increase, where as 256-bits, for example, would have a much larger impact. A 256-bit wide implementation would require doubling the width of existing floating point execution units as well as proportional increase in memory bandwidth in order to feed them. Finally, since the primary focus of the SSE extension was 3D geometry processing, greater than four wide single precision operations were felt to offer diminishing returns as most 3D geometry operations work with 4x4 matrices. In addition, geometry primitives such as the triangular strips that sophisticated 3D objects are composed of tend to be fairly short in current applications (on the order of 20 vertices per strip), limiting the potential benefit of longer vectors.

A 64-bit wide packed floating point implementation was also considered (as in AMD's competing and earlier to market 3DNow!). The AMD approach was not used because the x86 architecture has 3-bit register specifiers (i.e. a maximum of eight registers), thus implementing eight 128-bit wide registers  $(8 \times 128 \, bits = 1024 \, bits)$  effectively doubles the register space in comparison to a 64-bit wide register file  $(8 \times 64 \, bits = 512 \, bits)$ . Despite the 128-bit wide register file width defined by the SSE instruction set architecture, the Pentium-III SSE execution units are actually 64-bits (two single precision floating point elements) wide in hardware. The instruction decoder translates 4-wide (128-bit) SSE instructions into pairs of 2-wide (64-bit) internal micro-ops. Implementing the 128-bit SSE instruction set on a 64-bit datapath in this way limited the necessary changes to the instruction decoder, and allowed for the utilization of existing and new execution units [Thak99].

### 2.11 Motorola AltiVec (1999)

Motorola's AltiVec is an integral part of the Motorola 7400 (G4) processor, which extended the PowerPC architecture through the addition of a 128-bit wide vector (both parti-

tioned integer and floating point) execution unit. Unlike many other extensions, which have supported media processing by leveraging existing functionality from the integer or floating point data paths. AltiVec devotes a significant portion of the chip area to the new features and emphasizes the growing role of multimedia [Gwen98a]. AltiVec is a 128-bit wide extension with its own dedicated register file and four pipelined execution sub-units. The target applications for AltiVec included IP telephony gateways, multi-channel modems, speech processing systems, echo cancelers, image and video processing systems, scientific array processing systems, as well as network infrastructure such as Internet routers and virtual private network servers. In addition to accelerating nextgeneration applications, AltiVec can also accelerate many time-consuming traditional computing and embedded processing operations such as memory copies, string compares and page clears. Compared to other vendors, Motorola has targeted a much more general set of applications than just multimedia [Full98].

#### 2.12 MIPS MIPS-3D (1999\*)

MIPS-3D consists of application specific extensions (ASEs) which are intended to be separate, optional add-ons to the base MIPS-V instruction set [MIPS99]. MIPS-3D consists of partitioned floating point instructions targeting 3D geometry processing, and is planned for inclusion on the MIPS64 20K processor. It accounts for 3% of the floating point die area; the floating point silicon represents less than 15% of the total processor die area.

### 2.13 AMD Enhanced 3DNow! (1999)

AMD introduced Enhanced 3DNow! which extended 3DNow! and MMX, in their Athlon (previously known as the K7) processor by adding partitioned floating point and integer operations to make 3DNow! functionally equivalent to Intel's SSE extension. The added integer instructions are opcode equivalent to those included in Intel's SSE.

## 2.14 Intel SSE2 (2000\*)

Intel's SSE2 extension is included in the Pentium IV microprocessor. It extends the existing set of partitioned integer MMX operations to 128-bits wide with the addition of 68 new instructions which utilize the same set of eight 128-bit wide registers (XMM0-XMM7) introduced with the original SSE extension. A packed double precision data type is also added, targeted at applications other than multimedia such as scientific and engineering workloads, as well as advanced 3D geometry used in raytracing [Intel00a], [Intel00b]. No new architectural state is added with Intel's SSE2.

## 3 Comparison

In this section we review the functional architecture of each instruction set by describing the principles of operation of each. In discussing the functionality present in multimedia instruction sets, we will draw on the computational kernels extracted from the Berkeley Multimedia workload in order to demonstrate how well (or how poorly) a given functionality maps to a real multimedia workload based on our study of it in [Sling00d]. The Berkeley multimedia workload consists of a wide range of open source audio, speech, imaging, document, video and 3D graphics applications along with representative and realistic data sets. [Sling00a] discusses the design and characterization of this workload in detail.

#### 3.1 Integer

All of the multimedia extensions support integer operations, although the types and widths of available operations varies greatly. In our discussion, N-bit unsigned integer values are denotedU(a.b), where a indicates the number of significant bits to the left of the binary point, and b the number of bits to the right. Signed two's complement format is denoted S(a.b), where a = N - b - 1 and b is the number bits to the right of the binary point. A full discussion of this notation can be found in Appendix B.

#### 3.1.1 Saturation and Overflow

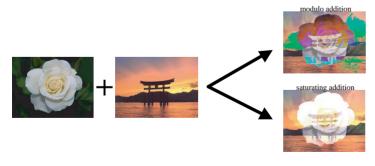

Traditional integer operations deal with overflow in a modulo fashion as exceeding the maximum or minimum representable range leads to a result in which only the lower N-bits of the intermediate result are retained and placed in an N-bit wide result register. This behavior is undesirable in many multimedia applications, where a better approach is to saturate positive overflow to the largest representable value or negative overflow to the largest negative value. This is because we are operating on media (often visual) data types, so we would like to be able to add two values and have the result not be obviously erroneous to our senses; for audio, for example, clipping is clearly preferably to wrap-around. The difference between the two types of overflow can be seen in the example of adding images with modulo and saturating addition shown in Figure 1, demonstrating the much more aesthetically palatable result achieved with saturating arithmetic.

Figure 1: Modulo and Saturating Operations - modulo arithmetic "wraps around" to the next representable value when overflow occurs, while saturating arithmetic clamps the output value to the highest or lowest representable value for positive and negative overflow respectively.

A second reason for employing saturating arithmetic is to have a mechanism to efficiently deal with multiple possible overflow situations in packed values. The main obstacle to exploiting data parallelism is data dependent instruction flow. There are five possible methods for dealing with overflow [Lee95]:

- 1. ignore it (modulo or wrap-around arithmetic)

- 2. trap

- 3. set a shared overflow flag

- 4. set an individual overflow flag for each element

- 5. clip the result to the desired range (saturation or clamping arithmetic)

If the overflow in each packed value had to be handled separately, the performance gain of parallel arithmetic would be negated [Lee97b]. This is especially true for the shared flag and trap solutions since the operation would have to be repeated and tested serially to determine which element overflowed. The only added cost of saturation is that unlike the modulo addition of 2's complement numbers, saturation requires separate operations for signed and unsigned values.

A good example of where saturating arithmetic is useful is in the add\_block() kernel taken from MPEG video decoding. Adding two blocks is an integral part of the block reconstruction step of motion compensation (Algorithm 1).

Algorithm 1 Add\_Block()Inner Loop - short \*bp and unsigned char \*rfp are pointers to the two 8x8 input arrays

```

for (i=0; i<8; i++) {

for (j=0; j<8; j++) {

*rfp = Clip[*bp++ + *rfp]; rfp++;

}

rfp+= iincr;

}</pre>

```

As can be seen, the high level language version of the code uses a lookup table to clamp the result of the addition. A SIMD version of the code with saturating addition does not require this additional overhead. An added advantage is that in the case of a 64-bit SIMD implementation, eight values can be loaded simultaneously and operated on simultaneously, further reducing memory overhead.

#### 3.1.2 Addition and Subtraction

Table 2 lists the data types supported for addition and subtraction operations on the architectures we have examined. Motorola's AltiVec includes a saturating 32-bit operation, but it is not clear how necessary this is, since the dynamic range of 32-bit numbers is great enough to avoid overflow for the 8-bit and 16-bit data types used in multimedia. Motorola's AltiVec also has a flag which is set whenever saturation has occurred. This can be useful in code which utilizes block floating point so that the appropriate scaling can be done when needed. (Block floating point is a scaling technique in which a single exponent is used for all the integer data in a block of

|                    | AMD           | Cyrix         | DEC    | HP      | Intel         | MIPS   | Motorola              | Sun   |

|--------------------|---------------|---------------|--------|---------|---------------|--------|-----------------------|-------|

| Modulo Add/Sub     | 8,16,32       | 8,16,32       | -      | 16      | 8,16,32,64    | 8,16   | 8,16,32               | 16,32 |

| Saturating Add/Sub | U8,U16,S8,S16 | U8,U16,S8,S16 | -      | U16,S16 | U8,U16,S8,S16 | S16    | U8,U16,U32,S8,S16,S32 | -     |

| Average            | U8,U16        | U8            | -      | S16     | U8,U16        | -      | U8,U16,U32,S8,S16,S32 | -     |

| Min/Max            | U8, S16       | S16           | U8,S16 | -       | U8,S16        | U8,S16 | U8,U16,U32,S8,S16,S32 | -     |

Table 2: Basic SIMD Integer Arithmetic Operations - Un indicates n-bit unsigned integer packed elements, Sn symbolizes n-bit signed integer packed elements, while values without a prefix, n, indicate operations which work for either signed or unsigned values. Average operations arithmetically average the corresponding elements in two partitioned input registers, while min/max output the minimum or maximum values of the corresponding elements in two partitioned input registers, repectively.

data. It has the advantage of being less expensive in terms of hardware than floating point, as well as faster, but is only appropriate where data values are clustered together.) None of the other architectures implement this feature. It is odd that Sun's VIS, which is likely the most imaging focused of all of the extensions does not have saturating operations, except during packing; this operation will be discussed later. Saturating arithmetic is of lesser importance with the MIPS extensions due to the 192-bit wide accumulator used for storing the result of integer operations.

Only DEC's MVI extension does not include any partitioned addition or subtraction operations, instead requiring either that intermediate calculations be done in wide enough precision to guarantee that overflow will not occur, or that max/min operations be used to clamp values appropriately to simulate saturation. An example of synthesizing a partitioned saturating unsigned add with this instruction set is shown in Algorithm 2. A 1's complement operation (eqv instruction) is used because the 1's complement of a number is the largest number that can be added to the original number without causing positive overflow to occur. By using the min instruction to get the smaller of either the second operand or 1's complement of the first addition operand it is possible to produce a clamped result.

## Algorithm 2 MVI Synthesized Saturating Unsigned Add

```

eqv r6, zero, t0 ;; 1's complement of r6

minuw4 r5, t0, r5 ;; get the smaller values

addq r5, r6, v0 ;; add r6 to r5 and place in v0

```

#### 3.1.3 Sum of Absolute Differences

One of the few operations that DEC did include in its MVI extension is an instruction to calculate the sum of absolute differences between unsigned packed bytes. Intel's MMX, although a much richer set of instructions, did not include this operation (it was included in the AMD, Cyrix and Intel extensions to MMX which came later). Sun's VIS also includes a sum of absolute differences instruction. DEC architects found that this operation provides the most computational benefit of all multimedia extension operations [Rubi96]. We found this to be true as well, since a SAD operation works with 8x parallelism on a 64-bit architecture, and replaces a significant amount of scalar code (Algorithm 3). Most ker-

nels are not able to perform computations with an 8-bit wide data type. It was found that on the Alpha architecture without multimedia extensions, motion estimation (dominated by computing sums of absolute differences) consumes 70% of the time spent encoding MPEG video. This code is found in the block\_match()kernel, and is centered around the loop listed in Algorithm 3 from MPEG-2 video encoding.

Algorithm 3 Block\_Match()Kernel Inner Loop - short \*blk1 and short \*blk2 are pointers to the 16x16 macro block arrays to be compared

```

for (row_index=0; row_index<height; row_index++)

if ((v = blk1[0]

b1k2[0] < 0 v = -v: sum+= v:

if ((v = blk1[1]

blk2[1])<0) v = -v; sum+= v;

if ((v = blk1[2]

b1k2[2])<0) v = -v; sum + = v;

if ((v = blk1[3]

b1k2[3] < 0 v = -v: sum+= v:

b1k2[4])<0) v = -v; sum + = v;

if ((v = b1k1[4]

if ((v = blk1[5]

v = -v; sum+=

b1k2[5])<0)

b1k2[6])<0) v = -v; sum += v;

if ((v = b1k1[6]

if ((v = blk1[7]

b1k2[7])<0) v = -v; sum + = v;

if ((v = h)k1[8]

b1k2[8] < 0 v = -v: sum+= v:

if ((v = b1k1[9])

b1k2[9](0) v = -v; sum += v;

if ((v = blk1[10])

blk2[10](0) v = -v: sum += v:

if ((v = blk1[11]

b1k2[11])<0) v = -v; sum+= v;

blk2[12])<0) v = -v; sum+= v;

if ((v = blk1[12]

if ((v = b)k1[13]

b1k2[13] < 0) v = -v; sum += v;

if ((v = blk1[14])

blk2[14])<0) v = -v; sum+= v;

if ((v = blk1[15])

b1k2[15])<0) v = -v; sum += v;

if (sum >= distlim) break:

blk1+= row offset: blk2+= row offset:

```

On 64-bit wide data paths, the central portion of this code can be replaced by two sum of absolute difference (SAD) instructions operating on packed bytes. Although this code is the primary computational aspect of this kernel, MPEG-2 encoding offers three other varieties of block matching involving half-pixel interpolation. *Interpolation* is done by averaging a set of pixel values with pixels offset by one horizontally, vertically or both. The original MPEG-2 code first performs the interpolation, and then computes the sum of absolute differences on the result. An instruction set such as MVI has no way to perform packed averaging, but it can trade some precision for speed. A similar interpolation operation can be done more efficiently (but not identically) on SIMD architectures with a SAD instruction by averaging the result of several SAD operations.

#### 3.1.4 Multiplication

SIMD or partitioned multiplication, involves the multiplication of corresponding packed elements. Partitioned mul-

|                             | AMD      | Cyrix    | DEC | HP | Intel      | MIPS   | Motorola        | Sun      |

|-----------------------------|----------|----------|-----|----|------------|--------|-----------------|----------|

| Truncating Multiply         | S16,U16  | S16      | -   | -  | S16,U16    | -      | S16             | S16, S32 |

| Rounded Truncating Multiply | S16      | S16      | -   | -  | -          | -      | S16             | =        |

| Full Multiply               | S16      | S16      | -   | -  | S16,U32    | U8,S16 | U8, U16, S8,S16 | =        |

| Shift Right Logical         | 16,32,64 | 16,32,64 | -   | 16 | 16, 32, 64 | 8,16   | 8,16,32         | =        |

| Shift Right Arithmetic      | 16,32    | 16,32    | -   | 16 | 16, 32     | 16     | 8,16,32         | =        |

| Shift Left                  | 16,32,64 | 16,32,64 | -   | 16 | 16, 32, 64 | 8,16   | 8,16,32         | -        |

Table 3: Supported SIMD Multiplication and Shift Data Types - the prefix 'S' indicates a signed operation, 'U' an unsigned operation, and no prefix indicates the same operation works for both signed and unsigned values

tiplication instructions demonstrate the greatest differences among the arithmetic operations available in the multimedia extensions. Compared to implementing packed addition or subtraction, multiplication is significantly more costly in terms of die area (3-4 times that of an integer adder) and latency (3 times that of an integer adder). Semantically, multiplication is difficult to deal with on SIMD architectures because the result of a multiply is longer than either operand [Lee97c]. Latency is of primary concern for those architectures implementing multimedia extensions on the integer data path. DEC's MVI and Hewlett Packard's MAX-1 and MAX-2 are the only extensions in this category, and it is unsurprising that neither have implemented partitioned multiplication.

The length of the result of a multiplication operation is greater than the length of its operands. On a SIMD architecture, a register typically contains the greatest number of packed values that will fit for a given precision. Because of this it necessary to deal with this expansion property of multiplication in some way that maps well to a SIMD architecture. The instruction sets we have examined (Table 3) deal with this in several ways:

- 1. reduction

- 2. even/odd

- 3. truncation

- 4. higher precision result register

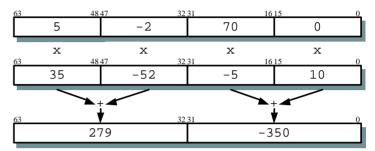

**3.1.4.1 Reduction** Reduction sums result vector subelements to produce fewer result values, and is useful because it is essentially a multiply-add; the core operation in digital signal processing. All that is needed is to ensure efficient processing is that the operands are arranged correctly to make the accumulation work. On Intel's MMX the pmaddwd instruction performs the operation depicted in Figure 2.

**3.1.4.2** Even/Odd AltiVec takes a different approach to dealing with the multiplication result width problem. It supports selectively multiplying either the *even or odd elements* of the source registers such that the full width results fit in the destination register. This does put a small extra burden on the programmer to take the unconventional result ordering into account (only even or odd elements in a given result register). On AltiVec, this is easily undone with a mix or data shuffle operation as soon as both even and odd results have been computed.

Figure 2: Partitioned Multiplication with Reduction

**3.1.4.3** Truncation Truncation predefines a set number of result bits to be thrown away. This primarily has application when multiplying n-bit fixed point values with fractional components which together take up a total of n-bits of precision. Pre-scaling of one or both of the operands may be needed to meet this criteria. For example, if we want to multiply each element of a vector of S(15.0) fixed-point (integer) values by the coefficient  $\sqrt{2} = 1.414$ , we can use an instruction such as MMX's pmulhw. Recall that our notation S(a.b) refers to a signed 2's complement integer requiring a + b + 1 bits of precision. In our example, we will use a S(3.12) representation for the coefficient:

$$\sqrt{2} \simeq \frac{5793}{2^{12}}$$

We will assume that the vector of 16-bit integers we wish to multiply by  $\sqrt{2} = 1.414$  by is:

| 63 48 | 47 32 | 31 | 1615 | 0 |

|-------|-------|----|------|---|

| 190   | 235   | 4  | -8   |   |

The pmulhw instruction truncates the result between the 15th and 16th bit positions of the internal 32-bit result, discarding the lower 16-bits. For this reason, we need to pad the operands with four extra bits so that the sum of the fractional bits in both multiplicands will equal 16 bits (thus the result will be scaled correctly and minimal precision will be lost). The S(3.12) fixed point coefficient 5793 would exceed the 16-bit signed range of  $-2^{15}\ldots+2^{15}-1$  if it was pre-shifted left by four bits, so instead the second multiplicand must be preshifted by left four bits. This can be accomplished through MMX's psllw instruction:

| 63 | 48   | 47 32 | 31 16 | 15 0 |

|----|------|-------|-------|------|

|    | 3040 | 3760  | 64    | -128 |

After shifting, the operation with pmulhw would be:

| 63 | 4    | 8.47 | 32 31 | 16   | 15   | 0 |

|----|------|------|-------|------|------|---|

|    | 3040 | 3760 |       | 64   | -128 |   |

|    |      |      |       |      |      | _ |

| 63 | 4    | 8 47 | 32 31 | 16   | 15   | 0 |

|    | 5793 | 5793 |       | 5793 | 5793 | ٦ |

|    |      |      |       |      |      |   |

|    | =    | =    |       | =    | =    |   |

| 63 |      | 8 47 | 32 31 | 16   | 15   | 0 |

|    | 268  | 332  |       | 5    | -11  |   |

|    |      |      |       |      |      | _ |

where the real numerical result when multiplying by the approximation  $5793/2^{12}$  would be:

| 63 48   | 47 32   | 31    | 1615 0  |

|---------|---------|-------|---------|

| 268.718 | 332.362 | 5.657 | -11.314 |

and the actual arithmetic result of multiplying by  $\sqrt{2}$  carried out to infinite precision would be:

| 63 48   | 47 32   | 31    | 1615 0  |

|---------|---------|-------|---------|

| 268.701 | 332.340 | 5.657 | -11.314 |

Note that there was some initial loss of precision in quantizing  $\sqrt{2}=1.4142135$  since  $5793/2^{12}=1.4143066$ . The other source of lost precision is due to the fact that the pmulhw instruction truncates the result rather than rounding it. In order to reduce this second type of precision loss, many architectures include 16-bit truncating multiplications that internally round the intermediate 32-bit result before the truncation to 16-bits takes place.

3.1.4.4 Higher Precision Result Register MIPS' MDMX extension avoids the multiplication result width problem by including a 192-bit accumulator register to act as the destination register for many operations including multiplication. This way there is the extra space required for the result to be stored in full precision. In addition, full precision results can be accumulated, and the total rounded only once at the end of the loop. While this may seem an elegant solution in principle, it ignores the architectural side of actually making such a design fast. The accumulator is a shared resource, and as such has a tendency to limit instruction level parallelism. We found that the existence of only a single accumulator was a severe handicap to avoiding data dependencies. On a non-accumulator but otherwise superscalar architecture it is usually possible to perform some other useful, non data dependent operation in parallel so that the processing can proceed at the greatest degree of instruction level parallelism possible. On MDMX all computations which need to use the accumulator must proceed serially.

In the MPEG decode pyrogen\_add\_block()kernel function listed as Algorithm 4, the bottleneck is quite evident. There is no data dependency which would prevent us

from starting to process four new elements every cycle in a pipelined implementation. Unfortunately, there is a resource conflict. Packing and clamping operations in MDMX are performed from the accumulator with the rx.fmt instruction.).

```

Algorithm 4 MDMX add block()

loop:

ldc1

f3. (a1)

# f3:

|r0|r1|r2|r3|r4|r5|r6|r7|

ldc1

f1, (a0)

# f1:

bp0 | bp1 | bp2 | bp3

ldc1

f2, 8(a0)

# f2:

bp4 | bp5 | bp6 | bp7

# unpack rfp data 8 -> 16

shfl.upuh f4, f3

r4 | r5 | r6 | r7

# f4:

| r0 | r1 | r2 | r3 |

shfl.upul f3, f3

# f3:

+ rfp [0..3]

addl.qh f1, f3

# acc: bp + rfp [0..3]

clamp to 8-bit unsigned

# f1: | 0|r0| 0|r1| 0|r2| 0|r3|

rzu.ob

f1, f0

# bp + rfp [4..7]

# acc: bp + rfp [4..7]

addl.qh f2, f4

# clamp to 8-bit unsigned

# f2: | 0|r4| 0|r5| 0|r6| 0|r7|

rzu oh

f2 f0

# pack output

shfl.pacl f1, f1, f2

# f1:

|r0|r1|r2|r3|r4|r5|r6|r7|

sdc1

(a1), f1

# store new rfp [0..7] values

add

a1, a1, a2

# rfp += iincr

# bp += 8 (pointer to INT16)

addi

a0, a0, 16

addi

a1, a1, 8

# rfp += 8 (pointer to UINT8)

subi

a3, a3, 1

# decrement loop counter

bgtz

a3, loop

```

In this example, it is possible to circumvent the accumulator problem by synthesizing the clamping operation with the min.fmt and max.fmt register-only instructions, thus avoiding the accumulator bottleneck. This work around costs two extra instructions and two extra registers to hold the maximum and minimum values we wish to clamp to. (See Algorithm 5). Placing exclusive functionality in the accumulator creates unnecessary bottlenecks and thereby inhibits instruction level parallelism. In general, any architectural feature which is not separately and independently available wherever it might be needed has the potential to be a bottleneck.

```

Algorithm 5 MDMX Alternative add block()

ldc1

f10, max_val # f3:

| 0 | 0 | 0 | 0

ldc1

f11, min_val # f1:

|255|255|255|255|

| bp4 | bp5 | bp6 | bp7 |

ldc1

f2, 8(a0)

# f2:

+ rfp [0..3]

f1, f1, f3

# f1: bp + rfp [0..3]

add.ah

+ rfp [4..7]

f2, f2, f4

# f2: bp + rfp [4..7]

add.qh

# clamp to 8-bit unsigned

f1, f1, f10

max.qh

max.qh

f2, f2, f10

min.ah

f1, f1, f11

min.qh

f2, f2, f11

# pack output

shfl.pacl f1, f1, f2 # f1:

|r0|r1|r2|r3|r4|r5|r6|r7|

```

**3.1.4.5 Multiplication Primitives** A potential problem with the VIS architecture is that it does not actually include full 16-bit multiply instructions. Instead it includes primitives, the results of which must be combined (see Algorithms 6 and 7).

#### Algorithm 7 Sun VIS 16-bit x 16-bit →32-bit Multiply

| fmuld8sux16 | %f0, | %f2, | %f4         |

|-------------|------|------|-------------|

| fmuld8ulx16 | %f0, | %f2, | %f6         |

| fpadd32     | %f4, | %f6, | <b>%f</b> 8 |

The disadvantage of dividing an operation into several instructions is that it increases register pressure, decreases instruction decoding bandwidth and creates additional data dependencies. Sun's VIS was the only multimedia instruction set with multiplication operations that do not directly support 16-bit operands. The reason for dividing up 16-bit multiplication in this way was to decrease die area. Not providing a full 16x16 multiplier subunit cut the size of the arrays in half [Trem96b].

#### 3.1.5 Shifts

It is a widely known optimization shortcut in binary arithmetic that a multiplication by an integer number N, which is a power of two, can be accomplished by a left shift of the other operand by  $log_2N$  bits. Division by the same class of integers can be performed in the same way, except that a right shift is used. This substitution is often a performance gain because a shift operation typically has a much lower latency than multiplication. Shifts are also needed for proper data alignment at the bit level of granularity, as opposed to the byte or higher level granularity most communication operations work with. The shift operations available on each platform are compared in Table 3.

3.1.5.1 Synthesizing Multiplication Although HP's multimedia instruction sets do not include partitioned multiplication, they do implement packed shift and add instructions, which can be used to synthesize multiplication by fractions with or without small integer components. Because the same shift amount is applied to each packed element, this substitution is only viable on a SIMD architecture when multiplying all of the subwords by the same constant. Although this criterion can often be met in multimedia applications, we found that programming shift-add combinations in place of multiplications made the job of assembly level programming considerably less flexible, more time consuming and more error prone. More importantly, this approach constrains the way in which data parallelism can be exploited.

**3.1.5.2 Graphics Status Register** Sun's VIS architecture does not include partitioned shift instructions, but does include a graphics status register (GSR). This register has a 3-bit addr\_offset field which is used implicitly for byte granularity alignment, as well as a 4-bit scale\_factor field for packing/truncation operations. Like other architectures, Sun included partitioned 8-bit and 32-bit integers as supported data types. What is unusual is that the 16-bit partitioned data type assumes a fixed point number with some fractional component (S(a.b) rather than S(a.0) as is more typical). This has important ramifications for other 16-bit operators. Pack operations work by first left shifting an element by the

number of bits specified in the  $scale_factor$  field of the GSR and clipping at some implicit binary point. For the signed 16-bit to unsigned 8-bit pack operation, the implicit binary point is between bits 6 and 7 of each element, so if 16-bit S(15.0) integers are the actual data type, it is necessary to place 0x7 in the  $scale_factor$  field of the GSR before executing the fpack16 instruction.

As is often the case with shared, singular resources, the VIS GSR turns out to be a serializing bottleneck. All of the data scaling functionality and alignment functionality is pushed through the GSR. Because VIS lacks partitioned shift operations, we found ourselves synthesizing such operations with the packing and alignment operations where no other algorithmic path was possible. We found that even with careful planning of packing and alignment operations it was often necessary to write to the GSR several times in each iteration of the loops of our multimedia kernels. The serializing effect of this singular resource prevented VIS operations from proceeding at the full possible degree of parallelism. To see this in action, consider the initial step of the color space conversion kernel which converts from band-interleaved to a more SIMD-friendly band-separated pixel form in Algorithm 8.

# Algorithm 8 Color Space Conversion Kernel Inner Loop

```

rgb_to_yuv_loop:

load band interleaved input data

alignaddr

%i0, %g0, %l0

[%10], %f2

[%10 + 8], %f4

faligndata %f2, %f4, %f2

%f2:

|RO|GO|BO|R1|G1|B1|R2|G2|

1dd

[%10 + 16], %f6

faligndata %f4, %f6, %f4

%f4:

| B2 | R3 | G3 | B3 | R4 | G4 | B4 | R5 |

[%10 + 24], %f8

faligndata %f6, %f8, %f6

%f6:

| G5 | B5 | R6 | G6 | B6 | R7 | G7 | B7 |

convert from band interleaved to band separated format

|RO|GO|BO|R1|G1|B1|R2|G2|

%f2:

%g0, 0x3, %gsr

set alignment for <<24

ur

|R1|G1|B1|R2|G2|B2|R3|G3|

faligndata %f2, %f4,

%f8

%f8:

%g0. 0x6.

%gsr

set alignment for <<48

wr

faligndata %f2,

%f10

%f10:

|R2|G2|B2|R3|G3|B3|R4|G4|

%f4,

%g0, 0x1,

%gsr

set alignment for <<48

wr

faligndata %f4,

|R3|G3|B3|R4|G4|B4|R5|G5|

%f12:

%f6.

%f12

set alignment for <<32

wr

%g0, 0x4,

%gsr

faligndata %f4,

| R4 | G4 | B4 | R5 | G5 | B5 | R6 | G6 |

%f6.

%f14:

%f14

wr

%g0, 0x7,

%gsr

set alignment for <<56

faligndata %f4,

%f6.

%f16

%f16:

| R5 | G5 | R5 | R6 | G6 | R6 | R7 | G7 |

wr

%g0, 0x2,

%gsr

set alignment for <<16

faligndata %f6, %f6,

%f18:

|R6|G6|B6|R7|G7|B7|G5|B5|

%f18

%g0. 0x5.

set alignment for <<40

%gsr

|R7|G7|B7|G5|B5|R6|G6|B6|

faligndata %f6, %f6,

%f20

%f20:

fpmerge

%f2, %f10, %f22

%f22:

| RO | R2 | GO | G2 | BO | B2 | XX | XX |

| R1 | R3 | G1 | G3 | B1 | B3 | XX | XX |

fpmerge

%f8, %f12,

%f24

%f24:

|R4|R6|G4|G6|B4|B6|XX|XX|

fpmerge

%f14, %f18, %f26

%f26:

fpmerge

%f16, %f20,

%f28

%f28:

| R5 | R7 | G5 | G7 | R5 | R7 | XX | XX |

fpmerge

%f22, %f24,

%f2

%f2:

|RO|R1|R2|R3|G0|G1|G2|G3|

fpmerge

%f23,

%f25.

%f4

%f4:

| BO | B1 | B2 | B3 | XX | XX | XX | XX |

fpmerge

%f26, %f28,

%f6

%f6:

| R4 | R5 | R6 | R7 | G4 | G5 | G6 | G7 |

fpmerge

%f27, %f29,

%f8

%f8:

| B4 | B5 | B6 | B7 | XX | XX | XX | XX |

```

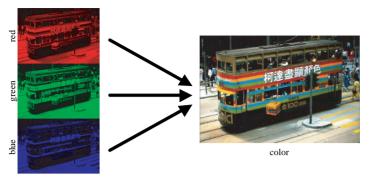

We will first explain what this kernel does and then come back to our discussion of the problematic GSR. Pixel data consists of one or more channels or bands, with each channel representing some independent value associated with a given pixel's (x, y) position. A single channel, for example, represents grayscale. A three channel image is typically color, while a more uncommon four channel image is also color but with the extra channel encoding some extra parameter (e.g. transparency). All of the imaging and video algorithms which

we looked at worked with three-band color image data, such as shown in Figure 3.

Figure 3: Three Band Color Images

The band data may be interleaved (each pixel's red, green, and blue data are adjacent in memory) or separated (e.g. the red data for adjacent pixels are adjacent in memory). In image processing algorithms such as color space conversion we operate on each channel in a different way, so band separated format is the most convenient for SIMD processing. Unfortunately, a lot of image data is stored in band-interleaved format, so it is often necessary to convert between the two. In the color conversion code fragment, each shift operation requires a write to the GSR, with each following instruction depending on the contents of the GSR to operate correctly. This is unfortunate because explicit writes to the GSR stall the processor (6 cycles in the case of UltraSPARC I) [Rice96]. If true shift operations (in this case, simply full register, 64bit shifts) had been included in VIS, a new shift could begin each cycle, assuming a pipelined implementation.

#### 3.1.6 Data Communication Operations

SIMD instructions perform the same operation on multiple data elements. Because all of the data within a register must be treated identically, instructions with the ability to efficiently rearrange data bytes within and between registers are crucial to efficiently utilizing a SIMD instruction set; we hinted at this earlier when discussing reducing multiplication operations. We refer to these types of instructions as data communication operations. The solutions of the various existing multimedia instruction sets are presented in Table 4. These operations are data type independent (they do not depend on knowing how a field of bits is to be interpreted), and so can be shared between partitioned integer and floating point data types assuming the same registers are used for both representations (for example, as in AMD's 3DNow!).

Interleave type communication instructions (also referred to as mixing, unpacking or merging) merge alternate data elements from the upper or lower half of the elements in each of two source registers. Align or rotate operations allow for arbitrary byte-boundary data realignment of the data in two source registers; essentially a shift operation that is done in multiples of 8-bits at a time. Both interleave and align type operations have hard coded data communication patterns. Insert and extract operations allow for a specific packed element

to be extracted as a scalar or a scalar value to be inserted to a specified location. The desired element location is typically specified as an immediate value encoded in the instruction.

Shuffle (also called permute) data communication operations allow greater flexibility than those operations with fixed communication patterns, but this added flexibility requires that the communication pattern be specified either in a third source register or as an immediate value in part of the instruction encoding. Instruction set architects have taken two approaches: either a set of predefined communications patterns can be provided, or full arbitrary mapping capabilities can be implemented. MIPS' MDMX uses a predefined set of eight 8-bit wide shuffles, and eight 16-bit wide shuffles to implement a partial shuffle operation (a canonical set of communication patterns is not provided). Hewlett Packard's mix instruction is able to achieve full shuffles for the four 16-bit elements packed within a 64-bit register because there are  $4^4 = 256$  possible ways to map the input values. This requires  $\lceil log_2(256) \rceil = 8$  bits to encode, which fits within the allocated immediate encoding bits of the HP PA-RISC architecture.

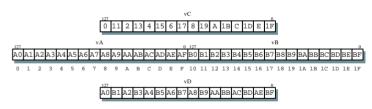

Encoding the desired full shuffle in an immediate field is not always a possibility, especially on architectures with larger register widths or those which shuffle at byte-level granularity. For example, on Motorola's 128-bit wide AltiVec extension, the vperm instruction, which concatenates two vectors to use as source elements, a full byte oriented shuffle would involve more than  $32^{16} = 1.2089 \times 10^{24}$  mappings, requiring 80 bits to encode as an immediate. Clearly, encoding the desired communication pattern as an immediate is not a reasonable approach. Instead, AltiVec offers a three operand format for shuffling in which the first two specified vectors are concatenated, and the bytes of the resulting 256-bit double register data has its bytes numbered as shown in Figure 4. Each element in vC specifies the index of the element in the concatenation of vA and vB to place in the corresponding element of vD.

Figure 4: AltiVec vperm vd,va,vb,vc Instruction - byte elements are selected from the concatenation of registers va and vb by the byte index specified in vc.

Although a full shuffle operation as is found in Motorola's AltiVec is extremely powerful, and is a superset of any other data communication operation, it is costly in terms of register space because every required data communication pattern must be kept in a register. It also increases memory bandwidth requirements to load the communication patterns from memory to registers. In practice, we found that simpler interleave and rotate operations could be used in place of full shuffles in many, although not all cases. The sufficiency of simpler data communication operations is also dependent on

|                  | AMD       | Cyrix   | DEC | HP        | Intel              | MIPS        | Motorola     | Sun |

|------------------|-----------|---------|-----|-----------|--------------------|-------------|--------------|-----|

| Interleave/Merge | 8,16,32   | 8,16,32 | -   | -         | 8,16,32            | 32          | 8,16,32      | 8   |

| Align/Rotate     | -         | -       | -   | -         | =                  | 8           | 8            | 8   |

| Shuffle/Permute  | $16(4^4)$ | -       | -   | $16(4^4)$ | $16(4^4), 32(4^4)$ | 8(8), 16(8) | $8(32^{16})$ | -   |

| Insert/Extract   | 16        | -       | -   | -         | 16                 | =           | 8,16,32      | -   |

Table 4: **Data Communication Operations** - Shuffle operations are specified as N(M), for N-bit wide data elements and M possible patterns

the vector length employed. For example, 128-bit AltiVec vectors contain eight elements, while a shorter extension such as Intel's 64-bit MMX contain only four of the same type of element. This means that simple data rearrangement operations (e.g. merge) cover a relatively larger fraction of all possible mappings in the case of the shorter vector length.

Data rearrangement operations which communicate between two registers can provide useful single register functionality when both source operands are set to be the same register. In addition, the functionalities of interleave, shuffle and align operations are certainly not exclusive. For example, the interleave operation on MIPS' MDMX is done through one of the provided communication patterns of the shf1 (partial shuffle) instruction. Unpack or interleave operations can also function as data width promotion for unsigned values if one of the source operands is zero.

```

Algorithm 9 AltiVec Matrix Transpose - matrix ele-

```

```

ments are 16-bits wide

;; v8:

0_0|0_1|0_2|0_3|0_4|0_5|0_6|0_7

;; v9:

1_0|1_1|1_2|1_3|1_4|1_5|1_6|1_7

;; v10:

|2_0|2_1|2_2|2_3|2_4|2_5|2_6|2_7

3_0|3_1|3_2|3_3|3_4|3_5|3_6|3_7

;; v11:

;; v12:

|4_0|4_1|4_2|4_3|4_4|4_5|4_6|4_7

|5_0|5_1|5_2|5_3|5_4|5_5|5_6|5_7

;; v13:

|6 0 | 6 1 | 6 2 | 6 3 | 6 4 | 6 5 | 6 6 | 6 7

;; v14:

;; v15:

|7_0|7_1|7_2|7_3|7_4|7_5|7_6|7_7

vmrghh v0, v8, v12

; v0:

|0_0|4_0|0_1|4_1|0_2|4_2|0_3|4_3|

|0_4|4_4|0_5|4_5|0_6|4_6|0_7|4_7|

vmrglh v1, v8, v12

: v1:

|1_0|5_0|1_1|5_1|1_2|5_2|1_3|5_3|

vmrghh v2, v9, v13

ν2:

vmrglh v3, v9, v13

v3:

|1_4|5_4|1_5|5_5|1_6|5_6|1_7|5_7|

vmrghh v4, v10, v14

ν4:

|2_0|6_0|2_1|6_1|2_2|6_2|2_3|6_3|

; v5:

vmrglh v5, v10, v14

|2_4|6_4|2_5|6_5|2_6|6_6|2_7|6_7|

vmrghh v6, v11, v15

v6:

|3_0|7_0|3_1|7_1|3_2|7_2|3_3|7_3|

vmrglh v7, v11, v15

; v7:

|3_4|7_4|3_5|7_5|3_6|7_6|3_7|7_7|

vmrghh v8, v0, v4

\hspace{-0.0cm} \mid \hspace{-0.0cm} 0 \hspace{-0.0cm} \mid \hspace{-0.0cm} 0 \hspace{-0.0cm} \mid \hspace{-0.0cm} 2 \hspace{-0.0cm} \mid \hspace{-0.0cm} 0 \hspace{-0.0cm} \mid \hspace{-0.0cm} 4 \hspace{-0.0cm} \mid \hspace{-0.0cm} 0 \hspace{-0.0cm} \mid \hspace{-0.0cm} 6 \hspace{-0.0cm} \mid \hspace{-0.0cm} 0 \hspace{-0.0cm} \mid \hspace{-0.0cm} 1 \hspace{-0.0cm} \mid \hspace{-0.0cm} 2 \hspace{-0.0cm} \mid \hspace{-0.0cm} 4 \hspace{-0.0cm} \mid \hspace{-0.0cm} 1 \hspace{-0.0cm} \mid \hspace{-0.0cm} 6 \hspace{-0.0cm} \mid \hspace{-0.0cm} 0 \hspace{-0.0cm} \mid \hspace{-0.0cm} 1 \hspace{-0.0cm} \mid \hspace{-0.0cm} 2 \hspace{-0.0cm} \mid \hspace{-0.0cm} 4 \hspace{-0.0cm} \mid \hspace{-0.0cm} 1 \hspace{-0.0cm} \mid \hspace{-0.0cm} 6 \hspace{-0.0cm} \mid \hspace{-0.0cm} 0 \hspace{-0.0cm} \mid \hspace{-0.0cm} 1 \hspace{-0.0cm} \mid \hspace{-0.0cm} 2 \hspace{-0.0cm} \mid \hspace{-0.0cm} 4 \hspace{-0.0cm} \mid \hspace{-0.0cm} 1 \hspace{-0.0cm} \mid \hspace{-0.0cm} 6 \hspace{-0.0cm} \mid \hspace{-0.0cm} 0 \hspace{-0.0cm} \mid \hspace{-0.0cm} 1 \hspace{-0.0cm} \mid \hspace{-0.0cm} 2 \hspace{-0.0cm} \mid \hspace{-0.0cm} 1 \hspace{-0.0cm} \mid \hspace{-0.0cm} 4 \hspace{-

; v8:

; v9:

vmrglh v9, v0, v4

10 2 2 2 4 2 6 2 0 3 2 3 4 3 6 3

; v10:

vmrghh v10, v1, v5

|0_4|2_4|4_4|6_4|0_5|2_5|4_5|6_5|

vmrglh v11, v1, v5

v11:

10 6 2 6 4 6 6 6 6 0 7 2 7 4 7 6 7

vmrghh v12, v2, v6

v12:

|1_0|3_0|5_0|7_0|1_1|3_1|5_1|7_1|

vmrglh v13, v2, v6

v13:

|1\_2|3\_2|5\_2|7\_2|1\_3|3\_3|5\_3|7\_3|

vmrghh v14, v3, v7

v14:

|1_4|3_4|5_4|7_4|1_5|3_5|5_1|7_5|

vmrglh v15, v3, v7

; v15:

|1_6|3_6|5_6|7_6|1_7|3_7|5_7|7_7|

; v0:

vmrghh v0, v8, v12

|0_0|1_0|2_0|3_0|4_0|5_0|6_0|7_0|

vmrglh v1, v8, v12

v1:

|0_1|1_1|2_1|3_1|4_1|5_1|6_1|7_1|

vmrghh v2, v9, v13

v2:

|0_2|1_2|2_2|3_2|4_2|5_2|6_2|7_2|

vmrglh v3, v9, v13

ν3:

|0_3|1_3|2_3|3_3|4_3|5_3|6_3|7_3|

vmrghh v4, v10, v14

|0_4|1_4|2_4|3_4|4_4|5_4|6_4|7_4|

ν4:

vmrglh v5, v10, v14

|0_5|1_5|2_5|3_5|4_5|5_5|6_5|7_5|

ν5:

vmrghh v6, v11, v15

|0_6|1_6|2_6|3_6|4_6|5_6|6_6|7_6|

ν6:

|0_7|1_7|2_7|3_7|4_7|5_7|6_7|7_7|

vmrglh v7, v11, v15

v7:

```

To see the importance of data communication operations, consider a two dimensional discrete cosine transform (DCT). Such a transform is efficiently computed as 1D transforms on each row followed by 1D transforms on each column. A SIMD algorithmic approach requires that multiple data ele-

ments from several algorithmic iterations be operated on in parallel for the greatest efficiency. This is straight forward for the 1D column DCT, since the corresponding elements of each column are linearly adjacent in memory, thus several columns can be operated on in parallel without rearranging the data as read from memory. A 1D row DCT is more problematic since the corresponding elements of adjacent rows are not adjacent in memory. It is possible to transpose a matrix making corresponding "row" elements adjacent in memory, perform the desired computation, and then transpose the matrix again (if needed) to put the resulting data back in the correct configuration. An example of a matrix transposition through SIMD data communication instructions for Motorola's AltiVec is shown in Algorithm 9.

#### 3.1.7 Width and Type Conversion

Data width promotion and demotion operations are critical to making a multimedia instruction set applicable to as many different applications as possible. Without a way to convert data between the formats used for storing the data and for operating on the data, SIMD computation cannot proceed efficiently. Although many multimedia data types are small integers (typically 8 or 16 bits), computations on these values often require greater precision. Also, many of the architectures offer operations on partitioned floating point in addition to partitioned integers. Thus, data conversion is a common operation. Supported width and type conversion operations of the examined architectures are listed in Table 5.

Pack or width demotion operations convert a larger width data type to a smaller width one either through truncation or by first clamping the values in question to the range of the smaller data type. Unpack or width promotion operations go the opposite direction, and so require no clamping, although the type of sign extension (zero extend or sign extend) is important. Unsigned unpacking can often be accomplished by utilizing the functionality of interleave or shuffle data communication operations. Saturating packs first clamp the input value to the range of the output data type, while truncating pack operations assume that the input values will fit in the output data type's representable range. Packing with truncation can similarly be done through data communication operations. Few architectures support signed packing and unpacking, although signed unpack can be accomplished somewhat awkwardly through a signed multiplication by 1, since the product will be twice as wide as the operands.

DEC MVI's pack and unpack operations are limited to truncation and zero extension, respectively, so signed values

|               | AMD                    | Cyrix                 | DEC                                   | HP       | Intel                                 | MIPS                                   | Motorola               | Sun                                    |

|---------------|------------------------|-----------------------|---------------------------------------|----------|---------------------------------------|----------------------------------------|------------------------|----------------------------------------|

| Saturating    | FP32→S32               | -                     | -                                     | -        | FP32→S32                              | -                                      | $FP \rightarrow S32$   | -                                      |

| FP Pack       | $FP32 \rightarrow S16$ |                       |                                       |          |                                       |                                        | $FP\rightarrow U32$    |                                        |

| Truncating    | =                      | =                     | -                                     | =        | $FP64 \rightarrow FP32$               | =                                      | =                      | -                                      |

| FP Pack       |                        |                       |                                       |          | $FP64 \rightarrow S32$                |                                        |                        |                                        |

| Saturating    | $S32\rightarrow S16$   | $S32 \rightarrow S16$ | -                                     | =        | $S32\rightarrow S16$                  | =                                      | $S32 \rightarrow S16$  | $S32{ ightarrow}U8$                    |

| 32-bit Pack   |                        |                       |                                       |          |                                       |                                        |                        | $S3\rightarrow S16$                    |

| Saturating    | $S16 \rightarrow S8$   | $S16 \rightarrow S8$  | -                                     | =        | S16→S8,                               | =                                      | S16→S8                 | $S16{ ightarrow}U8$                    |

| 16-bit Pack   | $S16{ ightarrow}U8$    | $S16{ ightarrow}U8$   |                                       |          | S16→U8                                |                                        | S16→U8                 |                                        |

| Truncating    | 32→16*                 | 32→16*                | $32\rightarrow 8$                     | 32→16*   | 32→16*                                | $32 \to 16$                            | $32 \to 16$            | -                                      |

| 32-bit Pack   | 32→8*                  | $32 \rightarrow 8*$   |                                       |          | 32→8*                                 |                                        |                        |                                        |

| Truncating    | 16→8*                  | 16→8*                 | $16 \rightarrow 8$                    | =        | 16→8*                                 | $16 \rightarrow 8$                     | 16→8                   | -                                      |

| 16-bit Pack   |                        |                       |                                       |          |                                       |                                        |                        |                                        |

| FP Unpack     |                        |                       |                                       |          | $\text{FP32}{\rightarrow}\text{FP64}$ |                                        |                        |                                        |

| 32-bit Unpack | $S32 \rightarrow FP32$ | -                     | -                                     | -        | S32→FP32                              | -                                      | U32→FP32               | -                                      |

|               |                        |                       |                                       |          | $S32 \rightarrow FP64$                |                                        | $S32 \rightarrow FP32$ |                                        |

| 16-bit Unpack | U16→U32*               | U16→U32*              | -                                     | U16→U32* | U16→U32*                              | $\mathrm{U}16{ ightarrow}\mathrm{U}32$ | U16→U32*               | $\mathrm{U}16{ ightarrow}\mathrm{U}32$ |

|               | $S16 \rightarrow FP32$ |                       |                                       |          |                                       |                                        |                        |                                        |

| 8-bit Unpack  | U8→U16*                | U8→U16*               | U8→U16                                | -        | U8→U16*                               | U8→U16                                 | U8→U16*                | U8→U16*                                |

|               |                        |                       | $\mathrm{U}8{ ightarrow}\mathrm{U}32$ |          |                                       | $S8\rightarrow S16$                    |                        |                                        |

Table 5: **Packed Data Type Conversion Operations** - The prefix 'S' indicates a signed operation, 'U' an unsigned operation, 'FP' a floating point operation, and no prefix indicates that an operation works for both signed and unsigned integer values. Saturating pack operations first clamp the input value to the range of the output data type, while truncating pack operations assume that the input values will fit in the output data type's representable range, and so simply truncate the input bits to the correct width. (\*) designates operations derived from data communication operations.

are not possible except when packing. HP's MAX depends entirely on its permute and mix instructions for width and type conversion. On HP's MAX-1/MAX-2 architecture, partitioned 8-bit operations were considered, but rejected due to insufficient precision. What this overlooks is that fact that even though many intermediate computations require greater precision than 8-bits, many types of video and imaging data are stored this way in existing multimedia file formats. Thus, packing and unpacking to and from 8-bit precision is a very common operation which is not supported in hardware, making HP's extensions inefficient at processing this type of data. The conclusion to be drawn from this is that all data types that occur in multimedia should be supported for packing and unpacking even for those widths not directly supported by arithmetic operations. It should always be possible to convert to a width that is supported for computation.

#### 3.2 Floating Point

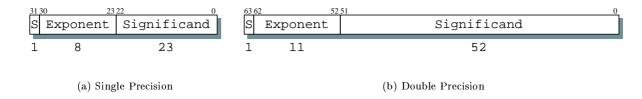

Within the Berkeley Multimedia workload, 3D graphics, MPEG audio coding and speech recognition applications all contain floating point intensive kernels. Most traditional scalar floating point architectures support single precision (32-bit) and double precision (64-bit) data types. Single precision is generally sufficient for all but numerical scientific applications requiring great precision. Intel's SSE2 is thus far the only extension to offer packed double precision floating point operations, and is targeted at applications beyond the domain of multimedia. A SIMD approach to floating point is useful, although it does not offer as much potential speedup

as integer SIMD.

Cyrix, DEC, Hewlett Packard and Sun currently do not offer packed floating point capabilities. Basic arithmetic functionality (add, subtract, multiply) is included by in all architectures supporting packed floating point extensions (AMD's 3DNow, Intel's SSE, and Motorola's AltiVec). These operations are generally useful on both audio and 3D applications. We found multiply-accumulate operations to be useful when implementing the fast Fourier transform, which is found in the LAME MPEG-1 layer III audio encoding and Rasta speech recognition applications. It was also useful in the synthesis filter bank kernel from the mpg123 MPEG-1 layer III audio decoding application.

#### 3.2.1 Square Root / Reciprocal Approximation

Beside basic arithmetic functionality, all of the floating point extensions include some form of reciprocal approximation and square-root approximation. These operations are targeted at the 3D geometry pipeline. A kernel derived from the Mesa source code (Mesa is an open source implementation of SGI's OpenGL API) is listed in Algorithm 10. Both the square root and reciprocal function can be seen to be central to this kernel.

Function approximation instructions are typically implemented as hardware lookup tables, returning k-bits of precision. In Intel's SSE, for example, approximate reciprocal (rcp) and reciprocal square root (rsqrt) return 12-bits of mantissa. Full IEEE compliant operations return 24-bits of mantissa. Intel's SSE supplies the full precision but slower

#### Algorithm 10 Transform and Normalize Kernel Code Fragment

```

for (i=0;i<n;i++) {

FLOAT64 tx, ty, tz;

{

FLOAT32 ux = u[i][0], uy = u[i][1], uz = u[i][2];

tx = ux * m0 + uy * m1 + uz * m2;

ty = ux * m4 + uy * m5 + uz * m6;

tz = ux * m8 + uy * m9 + uz * m10;

}

{

FLOAT64 len, scale;

len = sqrt( tx*tx + ty*ty + tz*tz );

scale = (len>1E-30) ? (1.0 / len): 1.0;

v[i][0] = tx * scale;

v[i][1] = ty * scale;

v[i][2] = tz * scale;

}

```

divide (div) and square root (sqrt) instructions, as well as full double precision (but no fast double precision approximations) in SSE2. None of the other architectures include full precision instructions, as the Newton-Raphson method can usually be employed where greater precision than the approximated value is required. One iteration of the Newton-Raphson method on a 12-bit precise approximation returns a 22-bit precise result [Thak99]. Motorola's AltiVec also returns 12-bits of precision for both the reciprocal and reciprocal square root approximation instructions. AltiVec also includes approximate  $log_2$  and  $exp_2$  instructions, which find application in the lighting stage of a 3D rendering pipeline.

AMD's 3Dnow! and MIPS' MIPS-3D extensions include instructions to automatically utilize the Newton-Raphson method to make initial approximations more precise. Intel's SSE architecture includes no such instructions nor does Motorola's AltiVec, but both point the programmer to using the Newton-Raphson method for greater precision. AMD's 3DNow! returns 14-bits of precision for the reciprocal approximation (pfrcp) instruction and 15-bits for the reciprocal square root approximation (pfrsqrt) instruction. The Newton-Raphson iteration instructions of 3Dnow! return full (24-bit) precision, so full precision versions of these operations are unnecessary. It should be noted that the AMD reciprocal and square root estimation instructions are actually scalar operations - only the lower element of a packed single precision register is used, with the scalar result being placed in both the top and bottom packed elements of the destination register. Intel's SSE, on the other hand, is a true vector operation, as it operates on each of the four specified packed single precision elements, computing four results in parallel.

#### 3.2.2 Exceptions

Exception handling has the same problem dealing with packed values as overflow and other instruction stream dependencies on data within SIMD architectures. Checking result flags or generating an exception from a packed operation requires considerable time to determine which packed element caused the problem. For this reason, AMD's 3DNow! instructions take the view that packed instructions should never raise exceptions. In multimedia applications there is little desire for

hardware status and exceptions at the expense of lower real time performance. Like saturating integer arithmetic, AMD's implementation of 3DNow! generates properly signed maximum representable numbers in the case of numeric overflow, and flushes results to zero in underflow situations [Ober99].

Motorola's AltiVec does not report IEEE floating point exceptions, although of course the regular scalar floating point instructions are IEEE compliant and report all appropriate exceptions. In most cases where an exception might be raised it is possible to fill in a value which will give reasonable results in most applications. This is similar to saturating integer arithmetic where maximum or minimum result values are substituted rather than checking for and reporting positive or negative overflow. This speeds execution because no error condition checking need be done. In the case of AltiVec, default values for all floating point exceptions are as specified by the Java Language Specification.