# Copyright © 2004, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## **LATENCY-INSENSITIVE DESIGN**

by

Luca Carloni

Memorandum No. UCB/ERL M04/29

3 August 2004

## **LATENCY-INSENSITIVE DESIGN**

by

Luca Carloni

Memorandum No. UCB/ERL M04/29

3 August 2004

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering

University of California, Berkeley

94720

## Latency-Insensitive Design

by

## Luca Carloni

Laurea (Università di Bologna, Italy) 1995 M. S. (University of California at Berkeley) 1997

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering-Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY of CALIFORNIA at BERKELEY

## Committee in charge:

Professor Alberto L. Sangiovanni-Vincentelli, Chair Professor A. Richard Newton Professor John H. Freeman

Fall 2004

# Chair Date Date

Date

The dissertation of Luca Carloni is approved:

University of California at Berkeley

Fall 2004

## Latency-Insensitive Design

Copyright 2004 by Luca Carloni

#### Abstract

### Latency-Insensitive Design

by

#### Luca Carloni

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California at Berkeley

Professor Alberto L. Sangiovanni-Vincentelli, Chair

Nanometer process technologies make hundreds of millions of transistors available for the design of an entire system on a single chip (system-on-chip). However, designs of this kind expose problems that were barely visible at previous levels of integration.

First, despite the increase in number of metal layers and in aspect ratio, the resistance-capacitance (RC) delay of an average metal line with constant length is getting worse with each process generation. This fact, combined with the increases in operating frequency and average interconnect length, cause on-chip interconnect delay to become the largest fraction of the clock cycle time. To make things worse, it is increasingly difficult to estimate early in the design process the actual interconnect latency because it is affected by several phenomena, like process variations and crosstalk, whose combined effect may vary across chip regions and periods of operation. As a result, nanometer technologies are forcing the semiconductor industry to experience a paradigm shift from computation- to communication-bound design: the number of transistors that a signal can reach in a clock cycle—not the number that designers can integrate on a chip—drives the design process.

Second, to manage the design complexity of a system-on-chip (SOC), the effective reuse of existing intellectual-property (IP) components is essential. Originally, IP cores were mostly functional blocks built for previous design generations within the same company. Frequently, today's IP cores are optimized modules marketed as off-the-shelf components by specialized vendors. The prerequisite for an easy trade, reuse and assembly of IP

cores is the ability to combine pre-designed components with little or no effort. The consequent challenge is addressing the communication and synchronization issues that naturally arise while assembling pre-designed components.

Currently available computer-aided design (CAD) tools struggle on handling the increasingly dominant impact of interconnect delay and fall short on providing support for IP reuse. With each process generation, the number of available transistors grows faster than the ability to meaningfully design them (design productivity gap) and designers are forced to iterate many times between circuit specification and layout implementation (timing-closure problem). Ironically, it is the introduction of nanometer technologies that threatens the outstanding pace of technological progress that has shaped the semiconductor industry.

The key to addressing these challenges is the development of methodologies based on formal methods to enable modularity, flexibility, and reusability in system design. The subject of this dissertation—Latency-Insensitive Design—is a step in this direction. My thesis is that "correct-by-construction methods combining the benefits of synchronous specification with the efficiency of asynchronous implementation are the key to design moderately distributed complex systems composed of tightly interacting concurrent processes."

Major contributions are the theory of latency-insensitive protocol and the companion latency-insensitive design methodology. Latency-insensitive systems are synchronous distributed systems composed by functional modules that exchange data on communication channels according to an appropriate protocol. The protocol works on the assumption that the modules are stallable (a weak condition to ask them to obey) and guarantees that systems made of functionally correct modules, behave correctly independently of channel latencies. The theory of latency-insensitive protocols is the foundation of a correct-by-construction methodology for integrated circuit design that handles latency's increasing impact on nanometer technologies and facilitates the assembly of IP cores for building complex SOCs, thereby reducing the number of costly iterations during the design process. Thanks to the generality of its principles, latency-insensitive design can be possibly applied to other research areas like distributed deployment of embedded software.

Alla mia cara Mê

# **Contents**

| De  | dicati  | on .                                                                                                                                                                                                                                                                                                                                                                                                                       | i                    |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Co  | ntent   |                                                                                                                                                                                                                                                                                                                                                                                                                            | ii                   |

| Lis | st of F | gures                                                                                                                                                                                                                                                                                                                                                                                                                      | vi                   |

| Lis | st of T | ables                                                                                                                                                                                                                                                                                                                                                                                                                      | ix                   |

| Ac  | know    | edgements                                                                                                                                                                                                                                                                                                                                                                                                                  | X                    |

| 1   | Intr    | duction                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                    |

|     | 1.1     | The Synchronous Paradigm                                                                                                                                                                                                                                                                                                                                                                                                   | 2<br>3<br>7<br>9     |

| 2   | Bac     | ground                                                                                                                                                                                                                                                                                                                                                                                                                     | 15                   |

|     | 2.1 2.2 | The Complexity of System-on-Chip Design  2.1.1 The Design Productivity Gap  2.1.2 Intellectual Property (IP) Reuse  The Impact of Latency on Nanometer Design  2.2.1 From Computation- to Communication-Bound Design  2.2.2 The Role of Latency in the Design of the One Billion Transistor Microprocessor  2.2.3 The Timing-Closure Problem  2.2.4 Coping with Volatile Latency  The Combination of Two Design Principles | 20<br>23<br>24<br>25 |

| 3   | The     | ory of Latency-Insensitive Protocols                                                                                                                                                                                                                                                                                                                                                                                       | 3                    |

|     | 3.1     | An Informal Presentation                                                                                                                                                                                                                                                                                                                                                                                                   | 32                   |

|     | 32      | I atency Insensitivity                                                                                                                                                                                                                                                                                                                                                                                                     | 34                   |

CONTENTS

|   |      | 3.2.1    | The Tagged-Signal Model                                          |

|---|------|----------|------------------------------------------------------------------|

|   |      | 3.2.2    | Informative Events and Stalling Events                           |

|   |      | 3.2.3    | Latency Equivalence                                              |

|   |      | 3.2.4    | Ordering the Set of Informative Events                           |

|   | 3.3  | Comp     | osing Patient Systems                                            |

|   |      | 3.3.1    | Compositionality of Patient Processes                            |

|   |      | 3.3.2    | Channels and Buffers                                             |

|   |      | 3.3.3    | Pipelining Patient Channels                                      |

|   |      | 3.3.4    | Relay Stations                                                   |

|   | 3.4  | Latenc   | cy-Insensitive Design                                            |

|   |      | 3.4.1    | Stallable Processes                                              |

|   |      | 3.4.2    | Shell Encapsulation of Stallable Processes 60                    |

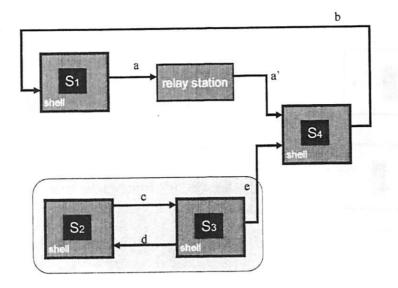

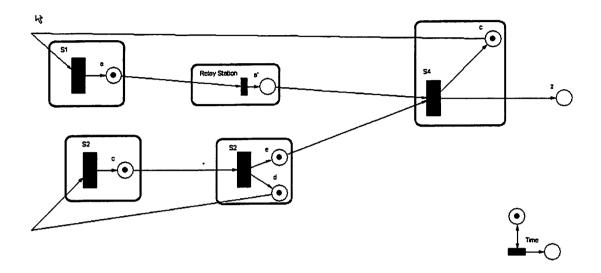

|   |      | 3.4.3    | Latency-Insensitive Design Methodology 64                        |

|   |      | 3.4.4    | Example: Latency-Insensitive Design Methodology for SOC 65       |

|   | 3.5  | Relate   | d Work                                                           |

|   |      | 3.5.1    | Latency Insensitive versus Asynchronous Design 66                |

|   |      | 3.5.2    | Latency Insensitivity and Slack Elasticity 69                    |

|   |      | 3.5.3    | Latency-Insensitive Protocols and High-Level Synthesis 69        |

|   |      | 3.5.4    | The Composition Principle                                        |

|   |      | 3.5.5    | Latency-Insensitive Protocols and Theory of Desynchronization 71 |

|   | 3.6  | Conch    | ading Remarks                                                    |

| 4 | Corr | rect-by- | -Construction SOC Design Methodology 77                          |

| • | 4.1  | •        | cy-Insensitive Design Methodology for SOC                        |

|   |      | 4.1.1    | Latency-Insensitive Design Flow                                  |

|   |      | 4.1.2    | The Stallability Requirement                                     |

|   | 4.2  | Latenc   | cy-Insensitive Communication Architecture                        |

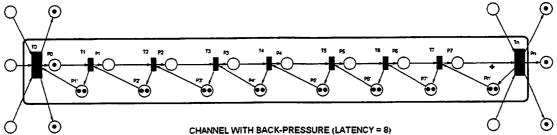

|   |      | 4.2.1    | Channels and Back-Pressure                                       |

|   |      | 4.2.2    | Shell Encapsulation                                              |

|   |      | 4.2.3    | Relay Stations                                                   |

|   | 4.3  | Impac    | t on System Performance                                          |

|   |      | 4.3.1    |                                                                  |

|   |      | 4.3.2    | Preserving Communication Throughput in DSM Design 96             |

|   | 4.4  | Case S   | Study: the PDLX Microprocessor                                   |

|   |      | 4.4.1    | PDLX Architecture and Instruction Flow                           |

|   |      | 4.4.2    | Latency-Insensitive Design of PDLX                               |

|   |      | 4.4.3    | Experimental Results with PDLX                                   |

|   | 4.5  | Relate   | d Work                                                           |

|   |      | 4.5.1    | DSM Design Methodologies                                         |

|   |      | 4.5.2    | Wire Buffering and Wire Pipelining                               |

|   |      | 4.5.3    | Related Work in Integrated Circuits Design                       |

|   | 16   | Canal    | uding Remarks                                                    |

CONTENTS

| 5 | Perf | ormanc         | e Analysis                                                     | 113   |

|---|------|----------------|----------------------------------------------------------------|-------|

|   | 5.1  | Petri N        | ets and Marked Graphs                                          | . 114 |

|   |      | 5.1.1          | Petri Nets                                                     | . 114 |

|   |      | 5.1.2          | Marked Graphs                                                  | . 118 |

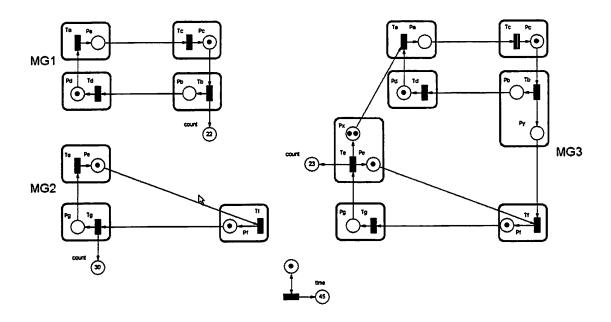

|   | 5.2  | Perform        | nance Analysis of Latency-Insensitive Systems                  | . 123 |

|   |      | 5.2.1          | Constructive Modeling of Latency-Insensitive Systems           | . 125 |

|   |      | 5.2.2          | Maximum Sustainable Throughput                                 | . 128 |

|   |      | 5.2.3          | Performance Analysis with the Infinite-Queue Model             |       |

|   |      | 5.2.4          | Performance Analysis with the Finite-Queue Model               |       |

|   | 5.3  | Relate         | d Work                                                         |       |

|   |      | 5.3.1          | Maximum Profit-To-Time Ratio and Maximum Cycle Mean            | . 152 |

|   |      | 5.3.2          | AND/OR Causality in Modeling Discrete Event Systems            | . 153 |

|   |      | 5.3.3          | Performance Analysis of Asynchronous Systems Using Petri Nets  | . 154 |

|   |      | 5.3.4          | Performance Analysis of Embedded Systems                       | . 154 |

|   |      | 5.3.5          | Marked Graphs versus Data Flow Models                          |       |

|   | 5.4  |                | ading Remarks                                                  |       |

|   |      |                |                                                                |       |

| 6 | Peri | formand        | ce Optimization                                                | 157   |

|   | 6.1  | The G          | lobal Impact of Channel Pipelining                             | . 158 |

|   |      | 6.1.1          | Channel Pipelining                                             |       |

|   |      | 6.1.2          | The Role of System Topology                                    |       |

|   |      | 6.1.3          | The Role of Back-Pressure                                      |       |

|   |      | 6.1.4          | Throughput Equalization in the Absence of Back-Pressure        |       |

|   |      | 6.1.5          | Case Study: an MPEG Video Encoder. Part One                    |       |

|   | 6.2  | Recyc          | ling                                                           | . 179 |

|   |      | 6.2.1          | The Role of Shell Encapsulation                                | . 180 |

|   |      | 6.2.2          | Recycling Transformations                                      |       |

|   |      | 6.2.3          | The Cycle Balancing Problem                                    |       |

|   |      | 6.2.4          | Case Study: an MPEG Video Encoder. Part Two                    | . 193 |

|   | 6.3  | Relate         | ed Work                                                        | . 200 |

|   | 6.4  | Concl          | uding Remarks                                                  | . 201 |

| - | Das  |                | Sum ah wan ana Cinanitwa                                       | 203   |

| 7 | 7.1  | yemig a        | Synchronous Circuitry  sing                                    |       |

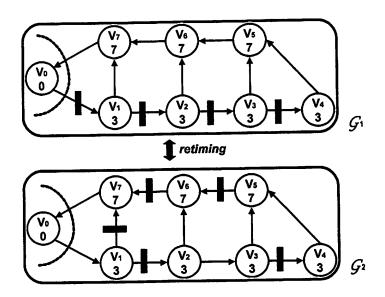

|   | 7.1  | 7.1.1          | The Basic Idea of Retiming                                     | 204   |

|   |      | 7.1.1          | Using Retiming to Pipeline Combinational Circuits              |       |

|   |      | 7.1.2          | The Invariant Rule of Retiming                                 | 208   |

|   | 7 2  |                | ring Recycling at the Gate Level                               |       |

|   | 7.2  | 7.2.1          | Differences between Recycling and Retiming                     |       |

|   |      | 7.2.1          | Combining Recycling And Retiming                               |       |

|   |      | 7.2.2          | Benefit Analysis on the Combination of Recycling and Retiming. |       |

|   |      | 7.2.3<br>7.2.4 | · · · · · · · · · · · · · · · · · · ·                          |       |

|   |      | 1.4.4          |                                                                |       |

| CONTENTS | • | 7 | 7 |

|----------|---|---|---|

| CONTENIS |   | · | , |

| In | dex        |                                                                      | 277   |

|----|------------|----------------------------------------------------------------------|-------|

|    | A.2        | Solving the Cycle Balancing Problem                                  | . 273 |

|    |            | A.1.4 Solving the Rate Equalization Problem                          |       |

|    |            | A.1.3 The Increasing Rate Equalization Problem                       |       |

|    |            | A.1.2 The Decreasing Rate Equalization Problem                       |       |

|    |            | A.1.1 The 2-Pair Decreasing Rate Equalization Problem                | . 264 |

|    | <b>A.1</b> | Rate Equalization Problems                                           |       |

| A  |            | Equalization and Cycle Balancing Problems                            | 263   |

| Bi | bliogr     | aphy                                                                 | 235   |

|    | 8.3        | Avenues of Future Research                                           | . 232 |

|    | 8.2        | Influence of Latency-Insensitive Design                              | . 229 |

|    | 8.1        | Contributions                                                        | . 227 |

| 8  | Con        | clusions and Future Directions                                       | 227   |

|    | 7.4        | Concluding Remarks                                                   | . 225 |

|    |            | 7.3.3 Recycling versus Architectural Retiming                        |       |

|    |            | 7.3.2 Recycling versus Timing Optimization via Software-Pipelining . |       |

|    |            | 7.3.1 Recycling versus Slowdown                                      |       |

|    | 7.3        | Related Work                                                         | . 222 |

# **List of Figures**

| 1.1<br>1.2<br>1.3                                                           | Diagram representing a sequential module at the register-transfer level RTL block diagram of a MAC circuit                                                                                                                                | 3<br>4<br>8          |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2.1<br>2.2                                                                  | Transitions simpled ber Jem [1.10].                                                                                                                                                                                                       | 17<br>21             |

| 3.1<br>3.2<br>3.3<br>3.4                                                    | A strict signal $s_1$ and a stalled signal $s_2$                                                                                                                                                                                          | 36<br>40<br>41<br>44 |

| 3.5<br>3.6                                                                  | Sketch for the proof on the compositionality of latency equivalence.  Relationships between the notion of nextEvent and corresponding events in pairs of latency-equivalent signals.                                                      | 47<br>50             |

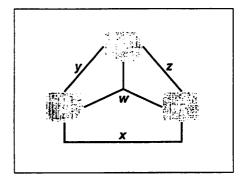

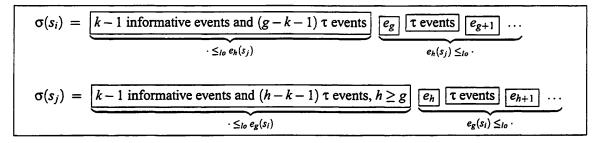

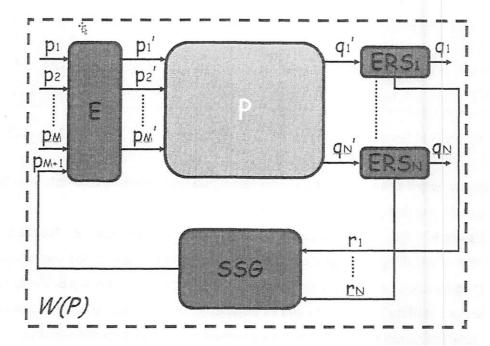

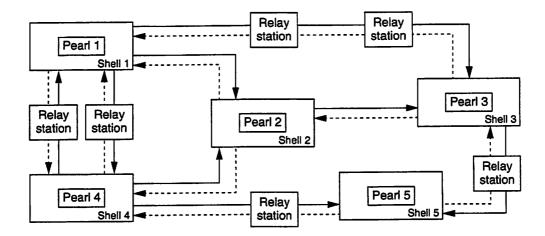

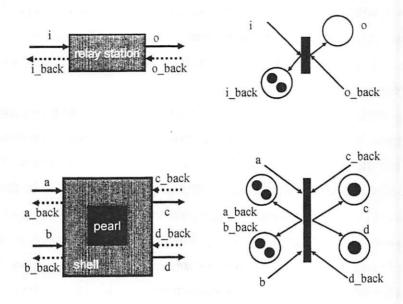

| 3.7<br>3.8<br>3.9                                                           | Comparing the behaviors of finite buffers $B_{1,1}^1(s_1,s_2)$ and $B_{1,1}^2(s_1,s_2)$ Example of a behavior of an equalizer $E$ with $I = \{1,2,3\}$ and $O = \{4,5,6\}$ . Encapsulation of a stallable process $P$ into a shell $W(P)$ | 56<br>61<br>62       |

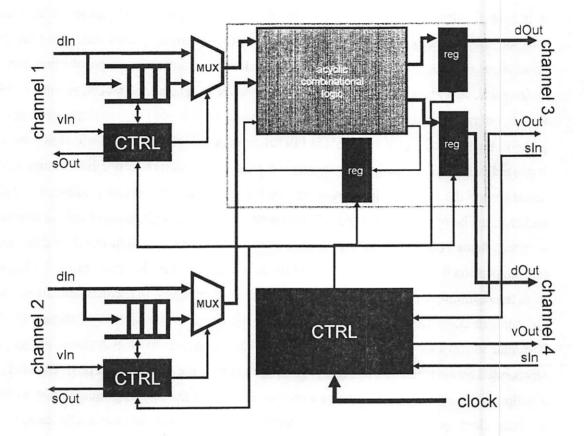

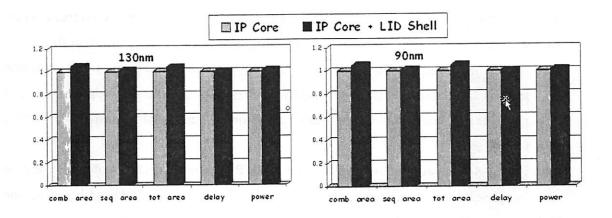

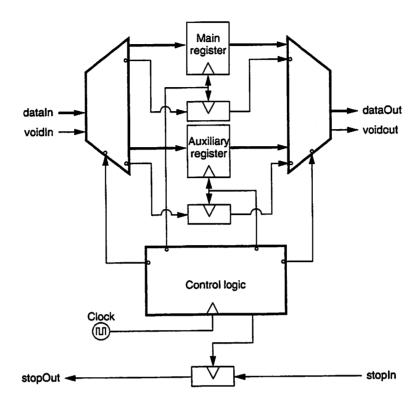

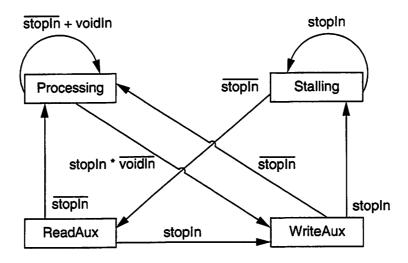

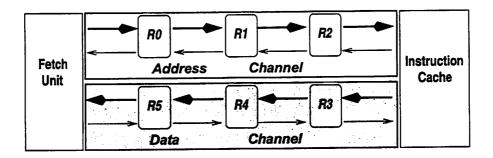

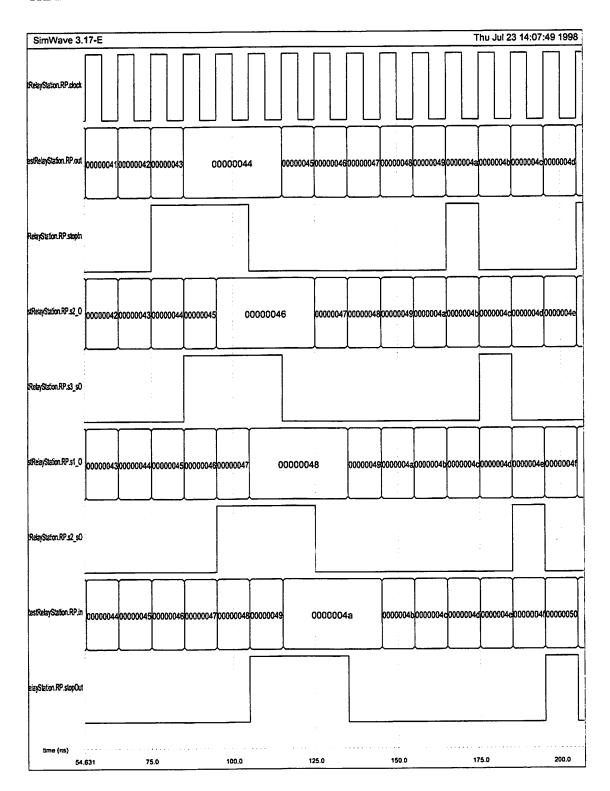

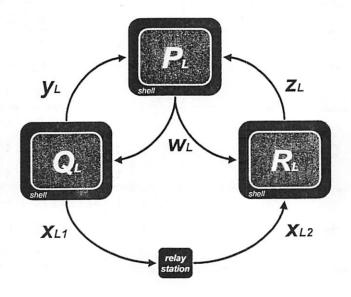

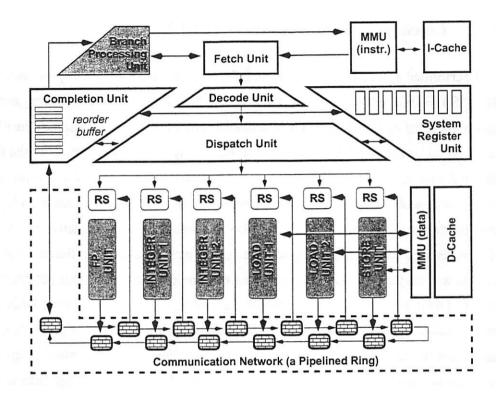

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11 | Wire buffering versus wire pipelining.                                                                                                                                                                                                    | 103<br>108           |

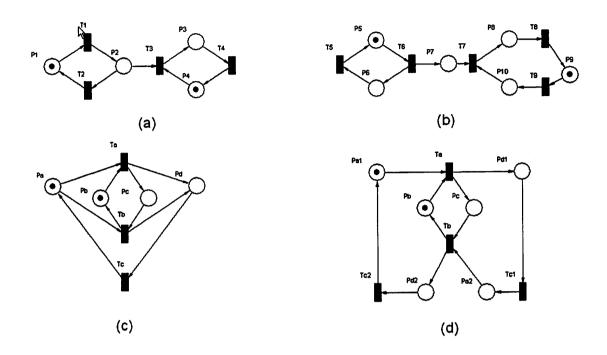

| 5.1                                                                         | Petri net examples taken from [176, 194]                                                                                                                                                                                                  | 11:                  |

LIST OF FIGURES vii

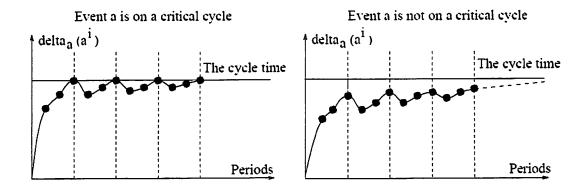

| 5.2   | Asymptotic behavior of average occurrence distances of transitions [179] I                                                       | 22  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|-----|

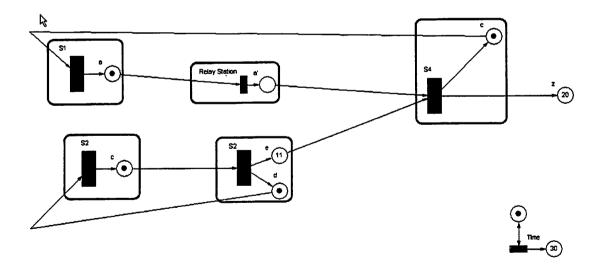

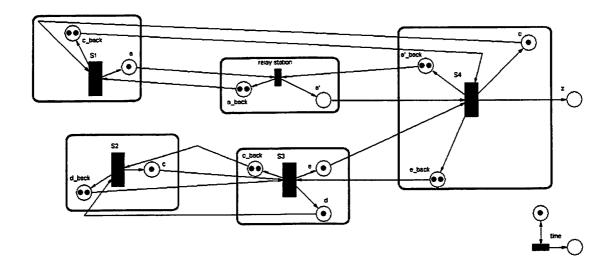

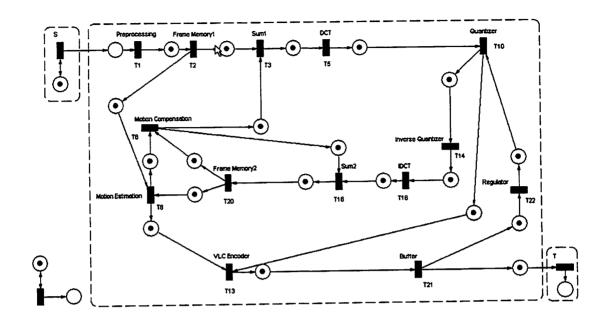

| 5.3   | Procedure to build a marked-graph model for a latency-insensitive system 1                                                       | 26  |

| 5.4   | Example of latency-insensitive system with no back-pressure                                                                      | 27  |

| 5.5   | Example of constructive modeling with marked graphs                                                                              | 28  |

| 5.6   | Primitive marked graphs from the infinite-queue model library $L_{IQ}$ 1                                                         | 33  |

| 5.7   | Channels in marked graph models                                                                                                  | 34  |

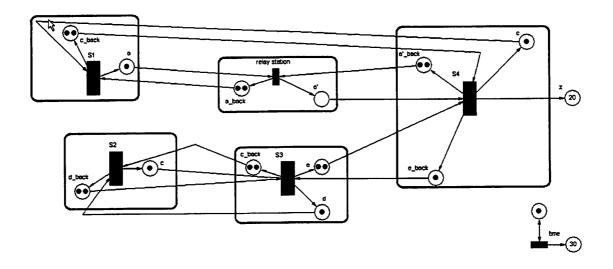

| 5.8   | The marked graph of Figure 5.5 after 45 timestamps                                                                               | 38  |

| 5.9   | A non-strongly connected latency-insensitive system without back-pressure. 1                                                     | 39  |

| 5.10  | Infinite-queue model for the latency-insensitive system of Figure 5.13 1                                                         | 40  |

| 5.11  | The marked graph of Figure 5.10 after 30 timestamps                                                                              | 40  |

| 5.12  | Primitive marked graphs from the 2-finite-queue model library $L_{2FQ}$ 1                                                        | 42  |

| 5.13  | Finite-queue model for the latency-insensitive system of Figure 5.9 1                                                            | 44  |

| 5.14  | Finite-queue model for the latency-insensitive system of Figure 5.13 (queues                                                     |     |

|       | length = 2)                                                                                                                      | 46  |

| 5.15  | The marked graph of Figure 5.14 after 30 timestamps                                                                              | 46  |

| 5.16  | Finite-queue model for the latency-insensitive system of Figure 5.13 (queues                                                     |     |

|       | length = 1). $\dots \dots \dots$ |     |

| 5.17  | The marked graph of Figure 5.16 after 30 timestamps                                                                              | 50  |

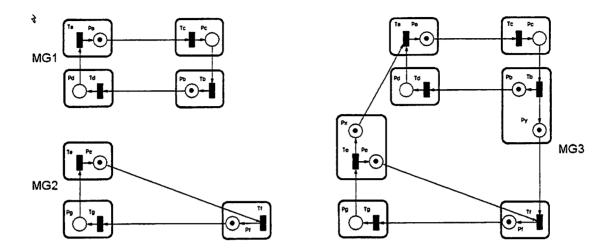

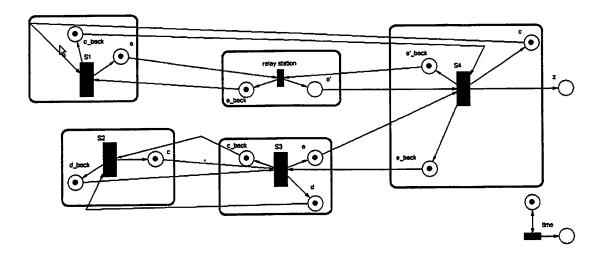

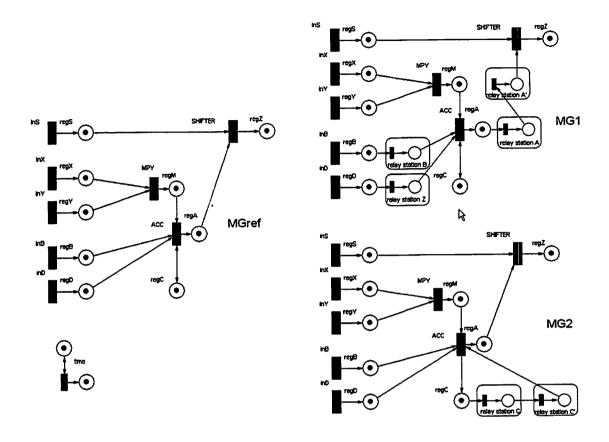

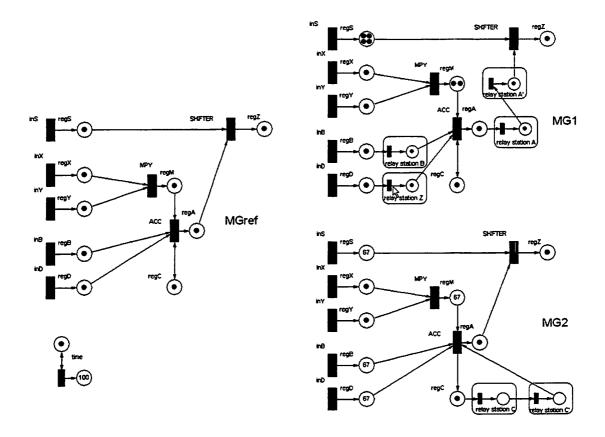

| 6.1   | Marked-graphs for three implementations of the MAC circuit of Figure 1.2. 1                                                      |     |

| 6.2   | Sequence of events on the channels of marked graph $\mathcal{MG}_1$ in Figure 6.4 1                                              |     |

| 6.3   | Sequence of events on the channels of marked graph $\mathcal{M} G_2$ in Figure 6.4 1                                             |     |

| 6.4   | The marked graphs of Figure 6.1 after 100 timestamps                                                                             |     |

| 6.5   | Models of cyclic latency-insensitive system with relay station on acyclic path. I                                                |     |

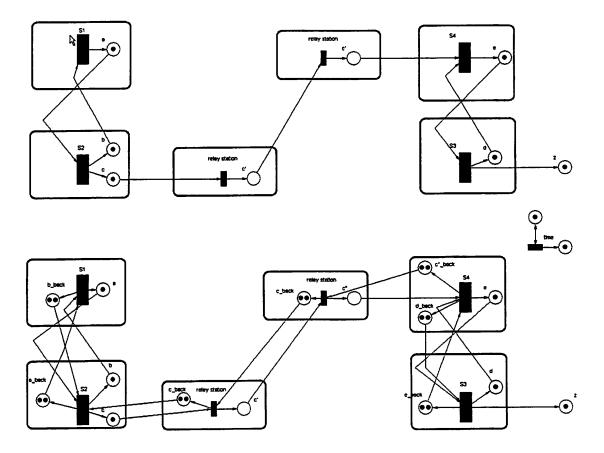

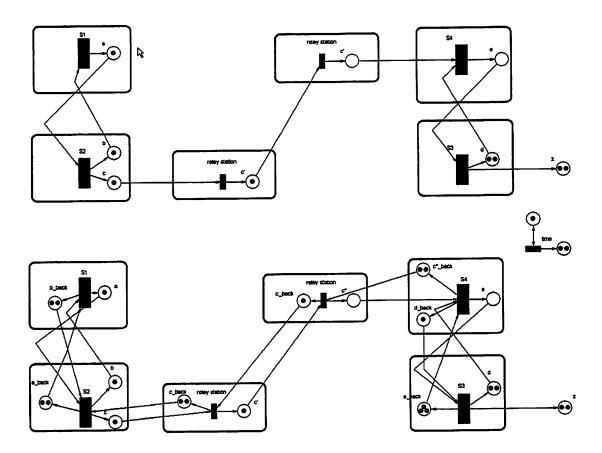

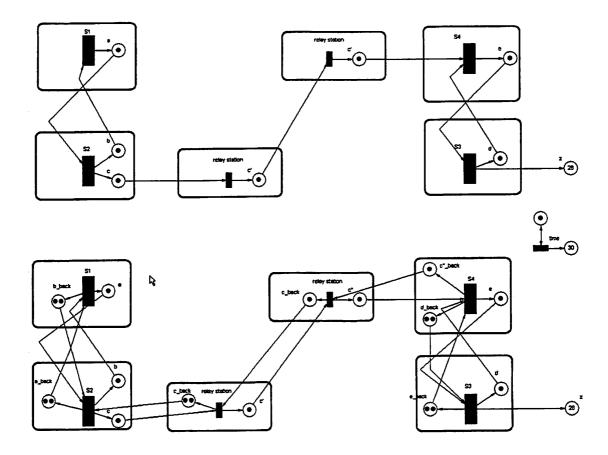

| 6.6   | The marked graphs of Figure 6.5 after 1 timestamp                                                                                |     |

| 6.7   | The marked graphs of Figure 6.5 after 30 timestamps                                                                              |     |

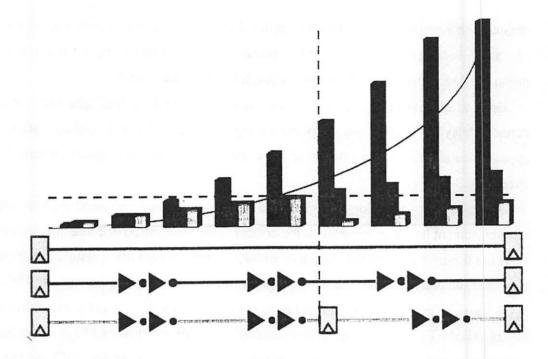

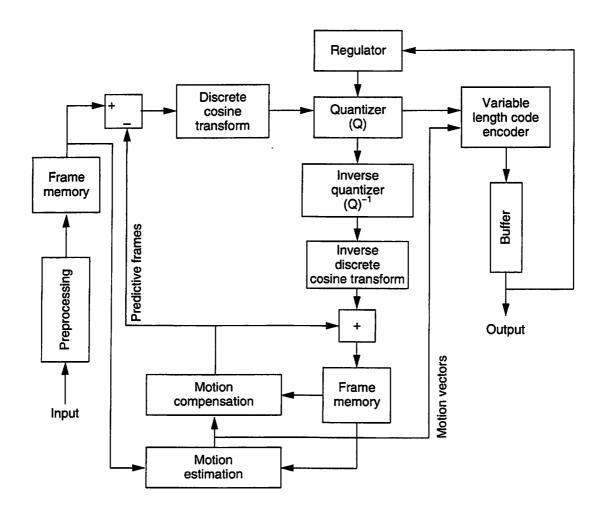

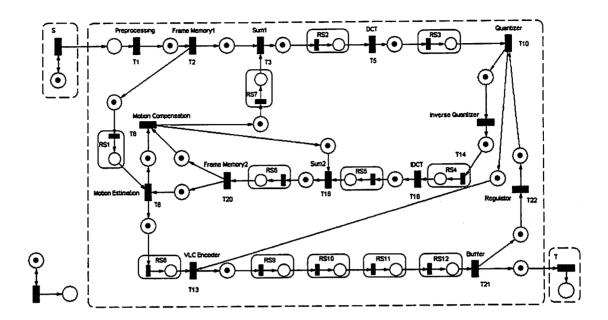

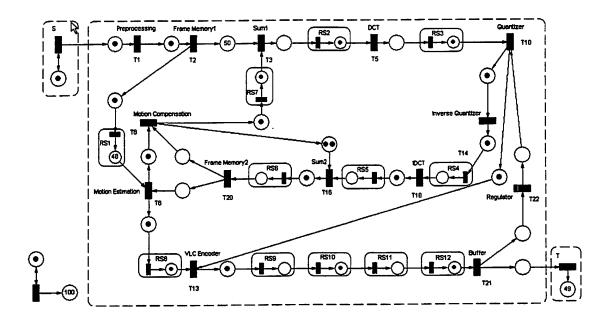

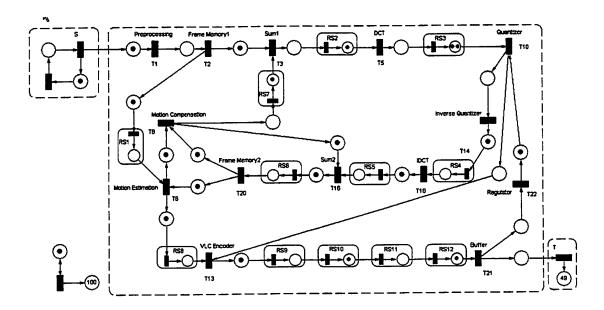

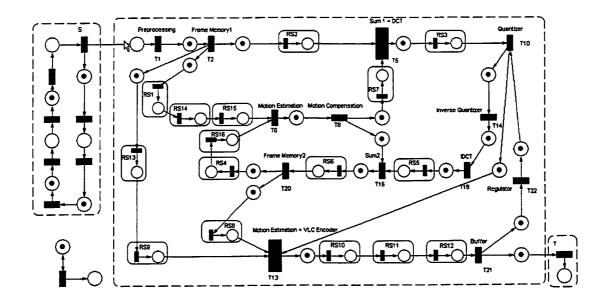

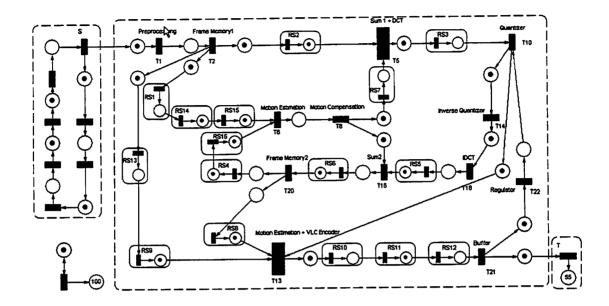

| 6.8   | MPEG-2 video encoder (functional block diagram)                                                                                  | .74 |

| 6.9   | Reference infinite-queue marked graph model for the MPEG-2 video en-                                                             |     |

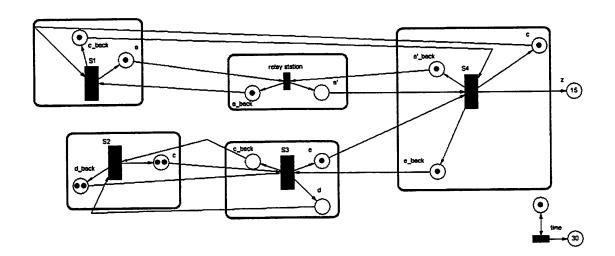

|       | coder of Figure 6.8                                                                                                              |     |

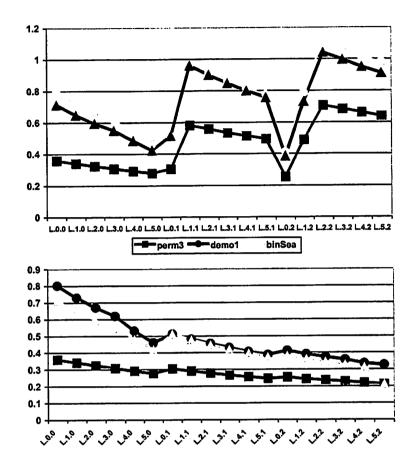

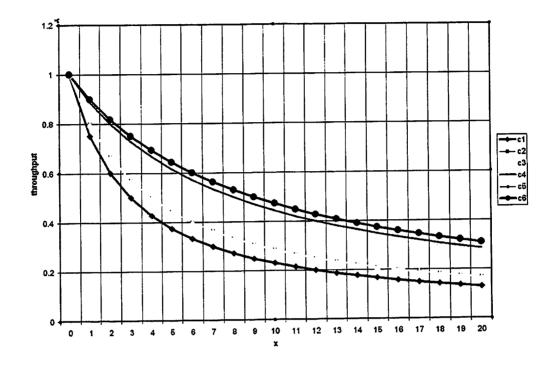

|       | MPEG-2 encoder: analysis of throughput degradation (worst-case scenario). 1                                                      | .77 |

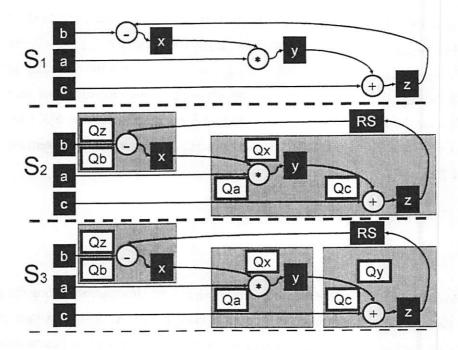

| 6.11  | Strict system specification of a pipelined data-path and two alternative                                                         |     |

|       | latency-insensitive implementations                                                                                              |     |

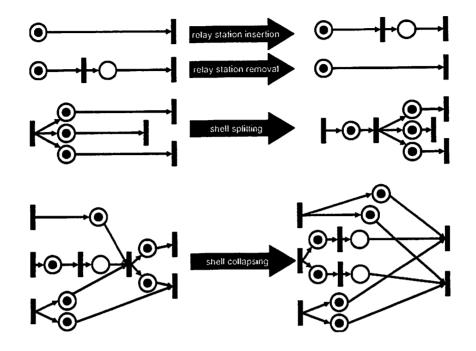

|       | Examples of recycling transformations                                                                                            | 87  |

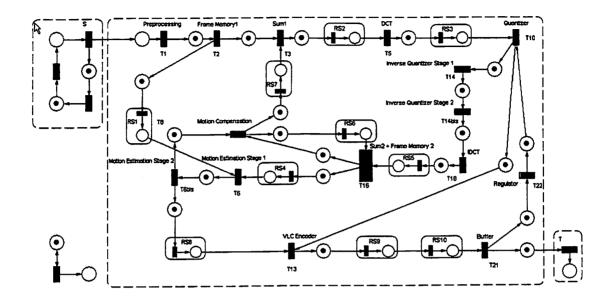

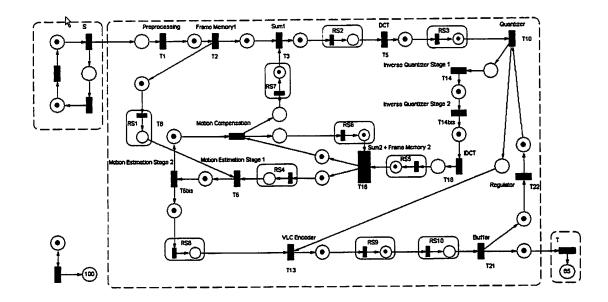

| 6.13  | Un-balanced implementation of the MPEG-2 video encoder of Figure 6.8                                                             |     |

|       | with $\vartheta(\mathcal{M} G_S) = 0.50$                                                                                         | 9:  |

| 6.14  | The marked graph of Figure 6.13 after 100 timestamps without equalized environment.                                              | 92  |

| 6 15  | The marked graph of Figure 6.13 after 100 timestamps with equalized en-                                                          |     |

| 0.13  |                                                                                                                                  | 92  |

| 6 16  | Balanced implementation of the marked graph of Figure 6.13 with $\vartheta(\mathcal{MG})$ =                                      |     |

| 5.10  | 0.57 obtained via recycling                                                                                                      | 196 |

| 6 17  | The marked graph of Figure 6.16 after 100 timestamps                                                                             | 191 |

| J. I. |                                                                                                                                  |     |

|             | Balanced implementation of the marked graph of Figure 6.13 with $\vartheta(\mathcal{MG}) = 0.66$ obtained via recycling |

|-------------|-------------------------------------------------------------------------------------------------------------------------|

| 6.19        | The marked graph of Figure 6.18 after 100 timestamps                                                                    |

| 7.1         | Retiming the correlator circuit [150]: the top graph has $\psi(G_1) = 24$ while                                         |

|             | the bottom one has $\psi(G_2) = 13$ (shading highlights critical paths) 205                                             |

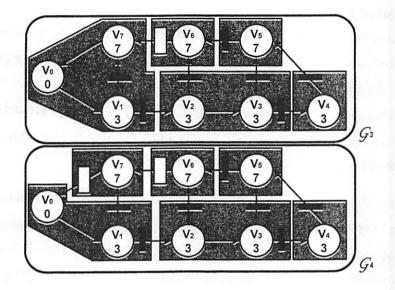

| 7.2         | Two recycled versions of the correlator circuit of of Figure 7.1 (shading                                               |

|             | shows the shell wrapping; light rectangles are relay stations initialized to $\tau$ ). 212                              |

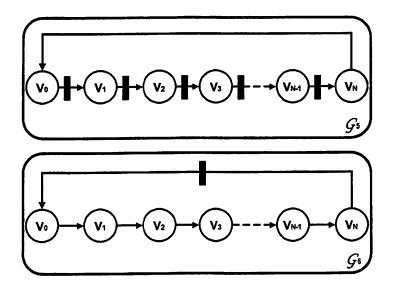

| 7.3         | Case studies for recycling benefit analysis: N-1 FFs (top), 1 FF (bottom) 218                                           |

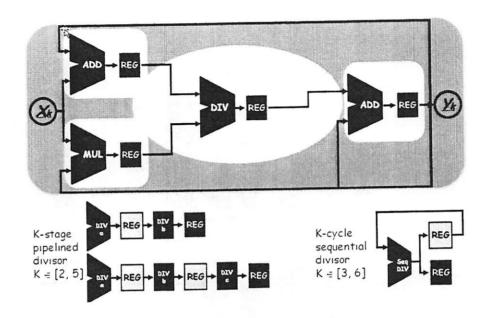

| 7.4         | Recycling-based design exploration of a pipelined data-path                                                             |

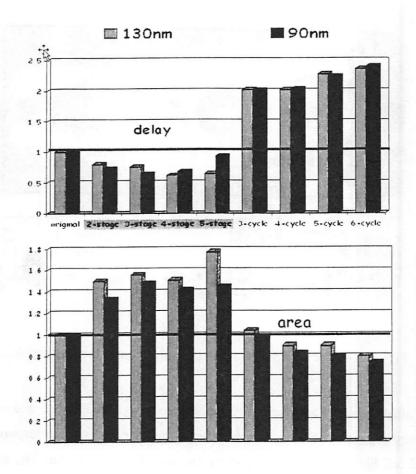

| 7.5         | Experimental results from recycling the data-path of Figure 7.4                                                         |

| <b>A</b> .1 | Algorithm to solve the 2-Pair Decreasing Rate Equalization Problem 265                                                  |

| A.2         | Algorithm to solve the Decreasing Rate Equalization Problem 266                                                         |

|             | Algorithm to solve the Rate Equalization Problem                                                                        |

| A.4         | 0.01                                                                                                                    |

|             | Algorithm to solve the Cycle Balancing Problem                                                                          |

|             | Recursive step inside algorithm CYCLEBALANCER of Figure A.5 275                                                         |

| A.D         | Recursive sied inside algorithin CYCLEDALANCER OF FIGURE A.3                                                            |

# **List of Tables**

| 1.1 | Example of RTL behavior of the MAC circuit of Figure 1.2                        |

|-----|---------------------------------------------------------------------------------|

| 2.1 | Comparing interconnect and transistor scaling properties [74] 23                |

| 4.1 | The periodic behavior of the latency-insensitive system of Figure 4.8 97        |

| 6.1 | Cycles and cycle times for the marked graph of Figure 6.9                       |

| 6.2 | Channels vs. cycles matrix for the marked graph of Figure 6.9 176               |

| 6.3 | The behavior of the strict system $S_1$ in Figure 6.11                          |

| 6.4 | The behavior of the latency-insensitive system $S_2$ in Figure 6.11 184         |

| 6.5 | The behavior of the latency-insensitive system $S_3$ in Figure 6.11 184         |

| 6.6 | Encoding of recycling transformations                                           |

| 6.7 | Cycles and cycle times for the marked graph of Figure 6.13 195                  |

| 7.1 | Cycles, delay, weights and delay-to-register cycle ratios for the circuit graph |

|     | of Figure 7.1                                                                   |

## Acknowledgements

"Blind hopes in them I made to dwell."

AESCHYLUS. PROMETHEUS BOUND.

During a late winter afternoon, back in December 1994, I met for the first time professor Alberto Sangiovanni-Vincentelli. I was a visiting undergraduate student from the University of Bologna, who spoke broken English while trying to cope with the diverse challenges of UC Berkeley Exchange Abroad Program. The meeting lasted less than ten minutes and changed my life. Eighteen months later, I would be starting Graduate School at Berkeley, thus guaranteeing to myself the luxury of working together with Alberto for all these years and, hopefully, for many more to come.

I could fill pages writing about Alberto's professional gifts. Gifts that, naturally, turn out to be mainly *presents* for his students: the gift of understanding (predicting seems often a more proper word) which research problems are the key ones to be addressed; the gift of combining a rich scientific talent with uncommon business intuition; the gift of putting the same careful attention to all the stages of a project, from involving the students in the drafting of the research proposal to refining the slides (and the voice intonation!) for their presentations; the (rare) gift of attacking each research problem with the same passion as if it were the first one <sup>1</sup>; the (even rarer) gift of constantly surrounding himself with brilliant collaborators, thus enabling the development of a unique work environment as the Berkeley CAD Group has been for over twenty years. In the end, however, it is Alberto's personal gifts that make it invaluable for his students (and for many less fortunate students, enviable) to work with him: Alberto's genuine interest for the balance between the student's personal and professional development is certainly uncommon, and, in my opinion, likely unmatched. That winter afternoon back in 1994 during our short conversation, I learned, as Musil teaches, to see a possible experience as a project, something yet to be invented.

Prof. Robert Brayton was my first teacher at UC Berkeley, when I attended his Logic Synthesis course as an undergraduate student, and has been like a second advisor throughout my master's thesis. As Tiziano Villa once perfectly wrote, Bob remains "a model of

<sup>&</sup>lt;sup>1</sup>A personal memory should be recorded here, because I suspect that there are not too many advisors who are ready to spend the night after Christmas supper exchanging the drafts of a theorem proof via transatlantic e-mail with a young graduate student who is writing his first paper.

dedication to scholarship and gentleman's style." Since the beginning of graduate school I looked at Prof. Richard Newton as a source of true enthusiasm and inspiring vision. I thank him for his comments on my work and for being part of my Qualifying Committee. Similarly, I thank the other two committee members Prof. Jan Rabaey and Prof. John Freeman. I also want to thank Prof. John Danner, who Socratically taught the *Workshop in Entrepreneurship* at the Haas School of Business during Fall 1999: truly one of the best teaching efforts I experienced at Berkeley.

Besides the professors, however, I believe that what makes graduate school special is the opportunity to learn from senior students. I have been blessed to learn from many of them and I have been trying, in return, to teach something to as many. In fact, I take this occasion to offer my final advice to a first year graduate student: get a mentor, two is not enough, three is not too many. During my first couple of years at Berkeley I had the fortune to work with Tiziano Villa (who introduced me to the world of academic research), Alex Saldanha (who introduced me to the world of industrial research), Evguenii Goldberg (who gave me a brilliant idea to work on for my master's thesis), Timothy Kam (whose elegant software packages were the first I read, when I learned that reading good code is the basis for writing good code), and Arlindo Oliveira (with whom I derived my first theorem proof). I just said my final advice, but here I have another one: do summer internships and collaborate with researchers at other institutions. I was lucky enough to have the possibility of spending four consecutive summers at Cadence Berkeley Laboratories, working together with such talented researchers as Alex Kondratyev, Luciano Lavagno, Ken McMillan, and Yoshinori Watanabe; and I was very lucky to collaborate with other talented researchers "across the ocean" who also influenced my research: Albert Benveniste, Benoît Caillaud, and Paul Caspi. And here a final (really final, now) advice: do different things. I believe that Graduate School is meant for engaging in many diverse projects and not for working only on a single problem with the goal of accelerating the coming of that day when your dissertation is ready for the famous three signatures. In my case, the time spent in 1999 attending classes at the Haas School of Business and working together with a team of MBA students for the Business Plan Competition, helped me to broaden the perspectives of my work and made me grow professionally.

When you are completing the following, traditional, mandatory, endless list of names

of friends and colleagues, you finally suspect that you may have spent just a few too many nights at Cory Hall. In any case, it is always a pleasure to recall fellow CAD Group students together with other members of that unique community which is UC Berkeley: Arthur Abnous, Joern Altmann, Felice Balarin, Alvise Bonivento, Eylon Caspi, Edoardo Charbon, Max Chiodo, Philip Chong, Luca Daniel, Fernando De Bernardinis, Alberto Ferrari, Varghese George, Naji Ghazal, Wilsin Gosti, Heloise Hse, Joe Higgins, Harry Hsieh, Adrian Isles, Sunil Khatri, Desmond Kirkpatrick, Christoforos Kozyrakis, Yuji Kukimoto, Freddy Mang, Amit Merothra, Trevor Meyerowitz, Paolo Miliozzi, Fan Mo, Rajeev Murgai, Amit Narayan, Alessandra Nardi, Georges Pappas, Roberto Passerone, Claudio Pinello, Alessandro Pinto, Vandana Prabhu, Mukul Prasad, Shaz Quadeer, Jacques-Christophe (Chris) Rudell, Marco Sabatini, Marco Sgroi, Niraj Shah, Farhana Sheikh, Narendra Shenoy, Michael Shilman, Tom Shiple, Vigyan Singhal, Subarnarekha Sinha, Mark Spiller, Lixin Su, Iason Vassiliou, Ken Yamaguchi, James Shin Young, and Stefano Zanella. Also, I would like to thank Mary Byrnes and Ruth Gjerde, whose kindness and professionalism make a trip to the Office of Graduate Matters always a pleasure, Brad Krebs, whose skills as system manager saved my work more than once, and, finally, Lorie Brofferio, Susan Gardner, Flora Oviedo, and Jennifer Stone for their administrative assistance. Finally, I am grateful to SRC, GSRC, and NSF which supported me for various research projects throughout graduate school as well as to Cadence Design Systems and Intel Corporation.

Still, and not surprisingly for an Italian, I must say that my biggest gratitude goes to my family, *la famiglia!* Without them, I simply wouldn't be here. Hence, without further ado:

Un forte abbraccio va a mio padre, Giulio Cesare, a mia madre, Anna, e ai miei cari fratelli, Fabio e Marco.

Um abraço com carinho para minha querida familia no Brasil: Emilia Yoko, Max e Denio.

My little princesses Kiara Tainá and Maira Paloma, the sweetest pretexts to postpone the completion of the present effort.

La mia cara Meika Alessandra, who paces the world around me in all directions, thus rendering it its equilibrium and harmony.

To pass freely through open doors, it is necessary to respect the fact that they have solid frames. This principle, by which the old professor had lived, is simply a requisite of the sense of reality. But if there is a sense of reality, and no one will doubt that it has its justifications for existing, then there must also be something we can call a sense of possibility. Whoever has it does not say, for instance: Here this or that has happened, will happen, must happen; but he invents: Here this or that might, could, or ought to happen. If he is told that something is the way it is, he will think: Well, it could probably just as well be otherwise. So the sense of possibility could be defined outright as the ability to conceive of everything there might be just as well, and to attach no more importance to what is than to what is not. The consequences of so creative a disposition can be remarkable, and may, regrettably, often make what people admire seem wrong, and what is taboo permissible, or, also, make both a matter of indifference. Such possibilists are said to inhabit a more delicate medium, a hazy medium of mist, fantasy, daydreams, and the subjunctive mood. Children who show this tendency are dealt with firmly and warned that such persons are cranks, dreamers, weaklings, know-it-alls, or troublemakers. Such fools are also called idealists by those who wish to praise them. But all this clearly applies only to their weak subspecies, those who cannot comprehend reality or who, in their melancholic condition, avoid it. These are people in whom the lack of a sense of reality is a real deficiency. But the possible includes not only the fantasies of people with weak nerves but also the as yet unwakened intentions of God. A possible experience or truth is not the same as an actual experience or truth minus its "reality value" but has - according to its partisans, at least - something quite divine about it, a fire, a soaring, a readiness to build and a conscious utopianism that does not shrink from reality but sees it as a project, something yet to be invented. After all, the earth is not that old, and was apparently never so ready as now to give birth to its full potential.

R. Musil.

# Chapter 1

## Introduction

In which what has been is not overlooked and what will follow is anticipated, at least partially.

Paradigms are "accepted examples of scientific practice—examples which include law, theory, application, and instrumentation together—[that] provide models from which spring particular coherent traditions of scientific research." This at least according to Kuhn in his classic, and influential, 1962 book [137]. The informal definition, which has been sometimes criticized for being too fuzzy, is centered around the English word that best translates the original Greek παράδειγμα (paradeigma), i.e. example. Therefore, paradigms are examples. These examples gain their value, which is ultimately a practical value ("to provide models"), from offering a combination of a diverse body of information ("law, theory, application, instrumentation"). As such, Kuhn's definition applies well to engineering design, particularly in the field of hardware and software systems. In their work engineers naturally follow fundamental laws and theories, but, as they strive to build their systems on time, they regularly find support in those practices, methods and tools which have been applied repeatedly and successfully before.

The present dissertation is very much about the practical importance of a paradigm in designing electronic systems, the paradigm of synchrony, and about the apparent crisis that this paradigm is facing. Though aware that "all crises begin with the blurring of a paradigm" and that "a crisis may end with the emergence of a new candidate for paradigm" [137], I make an attempt at presenting the old candidate as still a valid one, at least partially.

## 1.1 The Synchronous Paradigm

The *synchronous paradigm* is ubiquitous in electrical engineering and computer science. It is the basis of digital integrated circuit design, it is used in building discrete-time dynamical control systems, and it is the foundation of programming languages and design environments for real-time embedded systems.

With the synchronous paradigm, a complex system is represented as a collection of interacting concurrent components whose state is updated collectively in one instantaneous step. The system consists of a composition of sequential functional processes and evolves through a sequence of atomic reactions: at each reaction all processes, simultaneously, read the values of their input variables and use them, together with the values of their state variables, to compute new values for both their state and output variables; between two successive reactions the communication of the computed values across the processes occurs via instantaneous broadcasting.

The synchronous hypothesis is precisely the idea that at each reaction the computation in the functional modules and the subsequent communication of the computed values across modules do not overlap <sup>1</sup>. In the synchronous paradigm "time" progresses in lock-step, one reaction after the other. The idea of measuring time is confined to the concept of a virtual, or logical, clock, whose ticking indexes the totally ordered sequence of reactions by associating a new timestamp to each reaction (i.e. the set of timestamps coincides with the set of natural numbers).

The power of the synchronous paradigm lies essentially in its simplicity. It is an intuitive, but formal, model of computation [144] that offers many advantages:

- it simplifies the modeling of deterministic concurrent systems;

- it enables the incremental design of complex systems in a modular and hierarchical fashion;

- it facilitates the design process by separating functionality from the notion of time;

<sup>&</sup>lt;sup>1</sup>Some researchers talk of a zero-time step. This is misleading since it is not a matter of measuring computation or communication time, but simply to order subsequent reactions and maintain separated communication from computation.

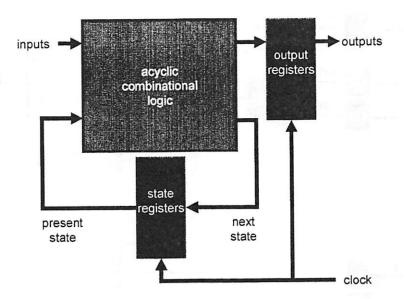

Figure 1.1: Diagram representing a sequential module at the register-transfer level.

- it encourages abstraction and reuse by leading to design specifications that are independent from the details of the particular implementation technology;

- it eases the development of design-automation tools for specification, validation, and synthesis;

## 1.1.1 Synchronous Paradigm and Hardware Design

In digital hardware design, methodologies and tools based on the synchronous paradigm have made it possible, over the last three decades, to build integrated circuits (IC) that are exponentially more complex and faster. Today's chips are built assembling hundreds of millions of transistors whose concurrent operations are tightly controlled by the beat of a single clock signal (the *physical*, or *real*, clock). Transistors and logic gates, however, are abstracted away during most stages of the design process. The core of the design effort occurs at the *register-transfer level (RTL)* where designers are assisted by hardware-description languages (HDL).

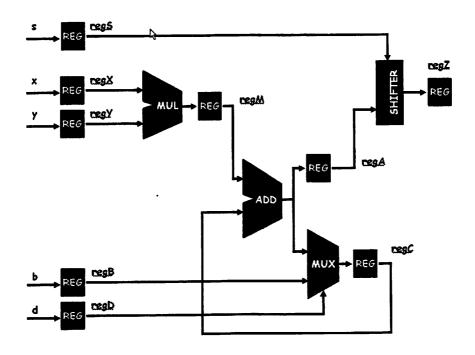

Figure 1.2: RTL block diagram of a MAC circuit.

Figure 1.1 illustrates a sequential module, the basic RTL building block and the ultimate result of applying the synchronous paradigm to IC design. The acyclic combinational logic implements the functionality of the module (an arbitrarily complex arithmetic or logic function) while the registers (memory elements controlled by the clock) store the values of the state and output variables over time [193, 216]. A sequential module is the direct implementation of a finite state machine (FSM) <sup>2</sup>, which is the model of computation commonly used to specify control blocks in IC design. Also, any pipelined data-path can be seen as a cascade of sequential modules. Using HDL languages, designers write software programs to specify the functionality of each module as well as their (possibly hierarchical) composition.

**Example** A multiplier-accumulator (MAC) is a very common digital circuit, because it facilitates the implementation of an operation like  $\sum x(n) \cdot y(n-k)$ , which is ubiquitous

<sup>&</sup>lt;sup>2</sup>Strictly speaking the diagram of Figure 1.1 represents the basic implementation of a Moore machine. Removing the output register gives the basic implementation of a Mealy machine [124, 240].

| i  |      |      | Input |      |      | i    | Internal |      | Output |

|----|------|------|-------|------|------|------|----------|------|--------|

| n  | regD | regB | regY  | regX | regS | regM | regC     | regA | regZ   |

| 1  | 0    | _    | 1     | 2    | 0    | 0    | 0        | 0    | -      |

| 2  | 0    | -    | 0     | 1    | 0    | 2    | 0        | 0    | -      |

| 3  | 0    | -    | 3     | 1    | 0    | 0    | 2        | 2    | -      |

| 4  | 0    | _    | 1     | 2    | 0    | 3    | 2        | 2    | 2      |

| 5  | 0    | _    | 2     | 4    | 0    | 2    | 5        | 5    | 2      |

| 6  | 1    | 10   | 1     | 1    | 0    | 8    | 7        | 7    | 5      |

| 7  | 0    | _    | 3     | 2    | 0    | 1    | 10       | 15   | 7      |

| 8  | 0    | _    | 1     | 3    | 0    | 6    | 11       | 11   | 15     |

| 9  | 0    | _    | 1     | 2    | 0    | 3    | 17       | 17   | 11     |

| 10 | 0    | _    | _     | _    | 0    | 2    | 20       | 20   | 17     |

| 11 | 0    | _    | _     | -    | 0    | _    | 22       | 22   | 20     |

| 12 | 0    | -    | -     | _    | 0    | _    | _        | _    | 22     |

Table 1.1: Example of RTL behavior of the MAC circuit of Figure 1.2.

in filters and vector arithmetic [110]. Fig. 1.2 illustrates a pipelined implementation of a MAC circuit: inX and inY are the input values to be multiplied, inD forces the accumulator register to be preset to the value of inB, inS controls the shift operation, and, finally, regZ is the output representing the sequence of indexed partial sums. The block diagram of the MAC can be decomposed in three sub-circuits and each of them can be designed as a separate RTL module. The sequential behavior of this circuit is captured by the following equations, written in "pseudo-HDL" with  $n \in \mathbb{N}$  denoting the timestamp:

$$regM_{n+1} = regX_n \cdot regY_n$$

$$regA_{n+1} = regC_n + regM_n$$

$$regC_{n+1} = \begin{cases} regC_n + regM_n & \text{if } regD = 0 \\ regB_n & \text{if } regD = 1 \end{cases}$$

$$regZ_{n+1} = shift(regA_n, regS_n)$$

Table 1.1 illustrates a possible RTL behavior of the MAC circuit spanning 12 clock cycles. The performance of the circuit is dictated by the delay of the combinational logic of its slowest component, which, in this case, is likely to be the multiplier.

The key point in RTL design is the separation of the design and validation of the functional behavior of the system from the analysis and optimization of its performance. The longest combinational path inside a module (critical path) dictates the minimum clock period  $\psi_i$  that makes it operate correctly. Therefore, given a target period  $\psi$  for the nominal clock signal, the task of designing a large digital circuit can be decomposed in sub-tasks aimed to design smaller RTL modules such that  $\psi_i < \psi$  for each module i. The modules can be specified, simulated, implemented, and verified independently from each other based only on the desired input/output functionality and the expected value of  $\psi$ . The separation of functional design from performance analysis consists of the following: a functionally correct design is obtained by simply assembling all the modules, while its speed is given by the slowest module. In other words, once all modules are composed, the overall circuit works correctly as far as it is running with a clock signal having a period  $\psi \ge \max_i \{ \psi_i \}$ . The effectiveness of this strategy is based on the assumption that the delay of any path connecting two modules (inter-module delay) is negligible, or at most comparable, to the delay of the combinational paths inside the slowest module in the system (intra-module delay). This has been the case for thirty years of progression of semiconductor process technologies as average interconnect inter-module delays have remained insignificant with respect to logic gate delays. Each new process generation has challenged designers to integrate twice the number of transistors running at twice the speed of the previous one, and designers have successfully done so by relying on the simplicity of the synchronous paradigm to build ever more powerful integrated circuits.

The other advantages of the synchronous paradigm mentioned above also translate in the hardware design environment. In particular: the design of the circuit as a deterministic concurrent system is simplified (different modules of the same system can be designed independently and simultaneously by different designers); RTL design is inherently incremental and hierarchical (e.g., portions of the circuit can be redesigned to improve their performance without touching the rest of the system); the RTL design of a module is independent from the particular semiconductor technology used to build the circuits; predesigned RTL modules can be reused for different projects; and, finally, designers can take advantage of a rich offering of commercial computer-aided design (CAD) tools, developed over the last twenty years, for RTL specification, simulation, synthesis, and validation,

## 1.1.2 Synchronous Paradigm and Embedded Software

Synchronous programming languages [16, 17, 99, 100] like ESTEREL, LUSTRE, and SIGNAL represent powerful instruments for the specification of complex real-time, safety-critical, embedded control systems (e.g., flight-control systems in flight-by-wire avionics and anti-skidding or anti-collision equipment in automotive electronics), which are becoming pervasive in today's society. Designers of such systems can rely on the solid mathematical foundation of synchronous languages to specify and formally validate their designs. They can also use the compilers and code generators that have been developed over the last thirteen years to compile these concurrent programs into embedded software code like executable C or JAVA.

Synchronous languages combine the simplicity of the synchronous hypothesis with the power of deterministic concurrency in functional specification. In doing so, they have their foundation in the synchronous paradigm, which guarantees a common formal semantics. Their shared synchronous programming model can be expressed by the following "pseudomathematical" statements [13, 15] <sup>3</sup>:

$$P \equiv R^{\omega}$$

$$P_1 || P_2 \equiv (R_1 \wedge R_2)^{\omega}$$

where  $P, P_1, P_2$  denote synchronous programs,  $R, R_1, R_2$  denote the sets of all the possible reactions of the corresponding programs, and the superscript  $\omega$  indicates non-terminating iterations. The first expression captures the essence of the synchronous paradigm: a synchronous program P evolves according to an infinite sequence of atomic reactions. The second expression denotes the parallel composition of two components as the conjunction of the reactions for each component. In other words, components communicate via shared variables, whose value they must agree upon at each reaction. Hence, parallel composition via conjunction of reactions implies that communication among components is performed via instantaneous broadcast.

Although they share a common mathematical semantics, synchronous languages interpret the synchronous paradigm slightly differently as each language targets its own distinc-

<sup>&</sup>lt;sup>3</sup> In [15], Benveniste *et. al* discuss how this pseudo-mathematical formulation captures also the composition of block diagrams in control engineering as well as the synchronous product of automata.

```

initialize memory elements;

loop each clock tick

read inputs;

compute outputs;

update memory elements;

end;

```

Figure 1.3: Schemes of synchronous execution [10].

tive application area: Lustre and Esterel follow a *strictly synchronous* approach in their focus on computation-dominated and control-dominated systems, respectively; SIGNAL is a multi-clock language targeting *open systems*, i.e. systems where each component must be designed without knowing the details of its operational environment, including the activity of the other components. In a strictly synchronous model, each variable in the system presents a value at each reaction. This is, for instance, the model for synchronous hardware discussed in the previous section. In a multi-clock synchronous model some variables may be absent at certain reactions. This feature is useful when modeling open systems because it allows us to represent the fact that some components are active while others are silent and synchronization occurs only occasionally. Being a synchronous language, SIGNAL encodes the absence of a variable with the special symbol  $\bot$ , thereby providing designers with the ability to write programs where decisions based on absence can also be made (another distinctive feature of the synchronous paradigm).

Figure 1.3 shows two typical synchronous execution schemes: event-driven on the left and sample-driven on the right [10]. The bodies of the two loops are examples of atomic reactions: at each reaction, a program sequentially reads input variables, computes output variables and updates its internal register. Moreover, all processes in the system do so concurrently and simultaneously. The execution is then repeated for the next reaction. Data computation (within a reaction) and data communication (across reactions) do not overlap. Clearly, the model of computation of a synchronous program is equivalent to the one of the RTL sequential module illustrated in Figure 1.1. Embedded-software engineers

write complex synchronous programs by composing simpler programs having the structure of Figure 1.3 very much in the same way as digital-hardware engineers design complex circuits by assembling simpler RTL modules <sup>4</sup>.

The advantages of the synchronous paradigm naturally translate into synchronous programming. In particular [10, 15, 100], the design of a real-time embedded system as a deterministic concurrent system is simplified (synchronous programs are concurrent and deterministic, differently from parallel languages which are based on asynchronous execution schemes where the competition of different processes for the same resource is resolved nondeterministically); synchronous programming is inherently modular; time and functionality are separated (the compiler takes care of processing functional concurrency to derive embedded code, thereby allowing critical applications to be deployed without the need for any operating system scheduler); synchronous languages make formal verification of programs feasible (the synchronous parallel composition greatly reduces the state-explosion problem, compared to the asynchronous interleaving approach to concurrency); and, finally, although synchronous languages have been around for only thirteen years, there is already a substantial amount of industrial offering in terms of tools and design environments.

In summary, synchronous languages are further evidence of the success of the synchronous paradigm. In the words of Benveniste et. al.: "the paradigm of synchrony has emerged as an engineer-friendly design method based on mathematically sound tools" [15].

## 1.1.3 The Crisis of the Synchronous Paradigm

If the crisis of a paradigm begins with its blurring, the synchronous paradigm may soon be facing one, paradoxically in application areas where it has been successful so far: integrated circuit design and embedded software development.

In general, while the synchronous hypothesis strongly simplifies system specification, the problem of deriving a correct and efficient physical implementation from it still remains. The difficulty of this problem grows dramatically when the final implementation has a

<sup>&</sup>lt;sup>4</sup>Synchronous parallel composition may suffer from the *combinational cycle problem*, i.e. the creation of cyclic instantaneous dependency between variables. In hardware design this may occur during the composition of Mealy machines. A discussion of the various methods to handle this issue can be found in [15].

distributed nature that poorly matches the synchronous hypothesis due to large variance in computation and communication times and to the challenge of maintaining a global notion of time.

This is increasingly the case for many important classes of embedded software applications in avionics, automotive electronics, and industrial-plant control where multiple processing elements operating at different clock frequencies are distributed on an extended area and are connected via communication media such as busses (e.g., CAN for automotive applications, ARINC for avionics, and Ethernet for industrial automation) or serial links [10, 14].

And it is also the case for integrated circuit design since the advent of nanometer technologies: as hundreds of millions of transistors can be integrated on a single die, the electronic chip becomes a distributed system with interconnect delays that are not only up to an order of magnitude larger than the switching delays of the logic gates but also extremely difficult to estimate in advance [39].

Hence, the crisis of the synchronous paradigm starts as the consequence of a spreading gap between the *synchronous hypothesis of the specification* and the *distributed reality of the implementation*. On one side, to assume instantaneous communication via broadcasting when it is more likely that the concurrent processes will be eventually implemented as distributed components may lead to poor design specifications. On the other side, even if it is still possible to take a synchronous specification and enforce a synchronous design style on the distributed implementation, the final result may likely be a system that either underperforms or performs wasting too many resources: in both cases a suboptimal design.

But has this crisis really started? After all, the large majority of today's digital chips are still synchronous circuits controlled by a single global clock. And the synchronous paradigm continues to play a fundamental role in the development of embedded systems not only through the adoption of synchronous languages but also with the increasing success of design environments like SIMULINK® & STATEFLOW® [162, 170], which largely benefit from the simplicity of the synchronous hypothesis. Nevertheless it is a fact that the design of high-performance integrated circuits is becoming increasingly more expensive and difficult, and that the demand for more formal methods in the design of distributed embedded systems continues to grow.

It may be debatable whether the crisis of the synchronous paradigm started, but it is clear that it has not ended. The proof is that a new candidate paradigm has not emerged yet. The present dissertation is an attempt to end this apparent crisis with a compromise. Being a compromise, it may eventually develop in either of the following directions: as a confirmation of the synchronous paradigm or as a candidate for a new paradigm.

The thesis presented here is that "correct-by-construction methods combining the benefits of synchronous specification with the efficiency of asynchronous implementation are the key to design moderately distributed complex systems, i.e. systems composed of tightly interacting distributed concurrent processes."

The main motivation behind this thesis is the desire to leverage the traditional tools and practices of synchronous design in the specification and optimization of these systems, while targeting efficient final implementations that are distributed in nature. I argue that the synchronous paradigm is still valid for designing systems whose functional correctness depends on the continuous interaction of several concurrent processes that communicate data more slowly than they process them. These are "moderately distributed" as opposed to "massively distributed", or simply distributed, systems where multiple components operate mostly in an autonomous fashion and their occasional, if any, interaction occurs without stringent time constraints. For instance, a system like the World Wide Web is certainly distributed, but its "correctness" does not depend on the tight interaction of all its components. Actually, the more independently its components can operate, the higher is its "performance" as measured by its offering of prompt and reliable services of various natures.

Instead, the functional correctness and the performance of a one billion transistor system-on-chip or of a drive-by-wire system continuously depends on the correct behavior of each distributed component as well as on their interactions. Consequently, communication and synchronization issues become paramount. Designers of these systems need a sound approach to handle the notion of global state and time, as well as efficient techniques to implement robust distributed communication schemes.

While a solution to the first challenge is found in the synchronous paradigm, it is asynchronous mechanisms such as handshake protocols that will provide answers to the second.

A third challenge is implicit: the need for design methods that can serve as a bridge between these two worlds. These methods must be *correct-by-construction* due to the high complexity of the systems being designed and the critical nature (business-critical, safety-critical) of their applications. Correct-by-construction methods formally guarantee the preservation of essential system properties during any successive refinement step of the design, from the original specification to the final implementation.

The main contribution of this dissertation—Latency-Insensitive Design—includes both a formalization of these ideas (the theory of latency-insensitive protocols) and an application to the case of integrated circuit design with nanometer technologies (the correct-by-construction latency-insensitive design methodology). In the future, thanks to the generality of its principles, Latency-Insensitive Design can possibly be applied to other research areas, like distributed deployment of embedded software.

## 1.2 Outline of the Dissertation

This dissertation is organized as follows:

In Chapter 2 I describe the background scenario that motivated my research work and the principles that guided my endeavor. I explain how, as it enters the realm of nanometer process technologies, the semiconductor industry is facing an exacerbation of two problems—productivity gap and timing-closure—which dramatically increase the complexity of designing high-performance integrated circuits. I argue that to manage the complexity of system-on-chip design and to address the challenges of gigascale integration it is necessary to develop new CAD tools in the context of innovative design methodologies that have their foundation on the *principle of orthogonalization of concerns* and the *principle of correct-by-construction design*.

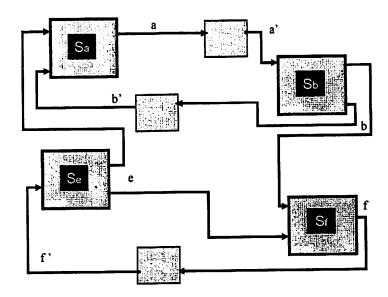

The theory of latency-insensitive protocols is first introduced informally and then presented in formal detail in Chapter 3. Latency-insensitive designs are synchronous, distributed systems that are built by composing functional sequential modules that exchange data on communication channels according to a latency-insensitive protocol. The goal of the protocol is to guarantee that a system composed of functionally correct modules be-

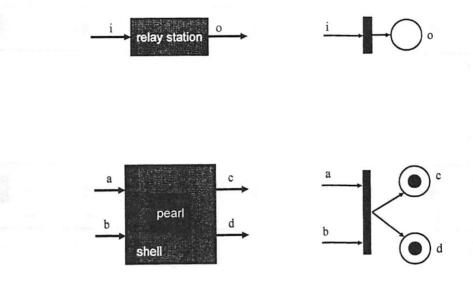

haves correctly independently of the channel latencies. At the core of the theory lie the notions of *latency equivalence* and *patience*, which are proved to be compositional properties. I also explain the relationship between patience and stallability, and introduce the concepts of *relay station* and *shell* process, which are the building blocks used to transform any synchronous system into a latency-insensitive one. The chapter concludes with a discussion of related work. Special emphasis is put in the comparison of latency-insensitive design with asynchronous design as well as between the theory of latency-insensitive protocol and the theory of desynchronization of synchronous programs.

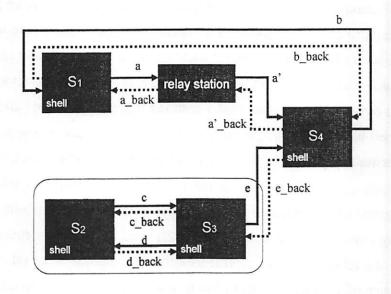

In Chapter 4 I present a correct-by-construction methodology for latency-insensitive design of systems-on-chip (SOC) with nanometer technologies. The methodology handles the increasing impact of global interconnect delays on integrated circuit design and it facilitates the reuse of intellectual-property (IP) cores for building complex systems-on-chip, thereby reducing the number of costly iterations in the design process. Specifically, the application of latency-insensitive design to integrated circuits presents two main advantages towards the productivity-gap and the timing-closure problems: (1) it facilitates the assembly of pre-designed components (IP cores), that, as long as they are stallable, can be automatically encapsulated within a shell-which interfaces them with the communication protocol—without changing their internal structure; and (2) it enables the a-posteriori automatic pipelining of long wires through the insertion of relay stations on the communication channels. I give an operational description of the main building blocks of a latencyinsensitive communication architecture (channels, relay stations, and shells) and provide a reference RTL implementation based on the concept of back-pressure. As a case study, I report on the RTL latency-insensitive design of PDLX, a microprocessor with out-of-order and speculative execution.

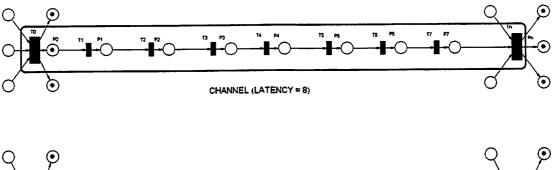

Performance analysis of latency-insensitive systems is the subject of Chapter 5. I show how latency-insensitive systems can be modeled using *marked graphs*, a subclass of Petri nets, and I provide two constructive models that address different styles of implementation for the building blocks of a latency-insensitive protocol. Both models can be used to compute exactly and efficiently the impact of the insertion of relay stations to pipeline long communication channels between shell processes. Ultimately, the highest processing throughput that can be sustained by a latency-insensitive system depends only on its

computation structure. I prove that the combination of the back-pressure mechanism and the introduction of input queues of length two within the shells is sufficient to support the maximum sustainable throughput in a system built under the singular assumption of the stallability of its components.

In Chapter 6 I discuss techniques to optimize the performance of a latency-insensitive system. Building on the modeling results of the previous chapter, I clarify how the *local* insertion of a relay station on any given channel can have a *global* impact on the overall system performance. I then describe simple criteria to optimize channel pipelining based on the analysis of the system topology. To explore alternative design implementations, I define the concept of *recycling*, i.e. the combined application of three design transformations: inserting relay stations, moving them across shell-core pairs, and redrawing the boundaries of the shells around the cores. To optimize the application of recycling and find the right balance between communication and computation latencies, I define the *cycle balancing* problem and present, in the appendix, an algorithm to solve it. This is the basis for developing an interactive design framework for SOCs that is centered on the optimization of the average-case performance of the system, driven by global throughput metrics, as opposed to the worst-case, driven by the minimization of local critical-path timing violations.

Recycling can be seen also as an extension to system-level design of retiming, a classic gate-level optimization techniques. In Chapter 7 I discuss the combination of retiming (a sequential circuit) and recycling (a network of sequential circuits). I provide an analytical model to guide the simultaneous application of these two techniques. This model identifies the conditions under which an optimally retimed synchronous circuit can be further accelerated and estimates the amount of the additional performance gain. Furthermore, I present a simple case study to illustrate how recycling enables high-level design exploration through the reuse of components from a library of pre-designed IP cores.

I conclude with Chapter 8 by summarizing the main contributions of the present work and by outlining the most promising avenues for future research. In particular I suggest that the ideas presented in this dissertation, as well as the general principles behind them, can be used to guide research efforts in other important areas such as: the deployment of synchronous embedded software on heterogeneous distributed architectures and the design of distributed systems that are globally robust and locally flexible.

# Chapter 2

# **Background**

In which two definitive principles are ultimately given, others will follow.

the traditional engineering practices in order to sustain the outstanding pace of progress of the information technology industry. The advent of nanometer process technologies makes available hundreds of millions of transistors for the design of an entire system on a single chip (system-on-chip). However, designs at this level of sophistication expose issues that were barely visible at previous levels of integration, thus exacerbating both the design productivity gap and the timing closure problem.

In the present chapter, I describe the background of the dissertation and highlight the motivations that prompted this research effort and the principles that guided me throughout my research. The chapter has a threefold structure. In the first two sections I analyze two critical challenges that the designers of electronic systems are facing today: the complexity of system-on-chip design and the impact of latency on nanometer technologies. In the third and final section I argue that the development of design methodologies aimed at assisting designers to address these challenges must be based on the combined application of two principles: the principle of orthogonalization of concerns and the principle of correct-by-construction design.

## 2.1 The Complexity of System-on-Chip Design

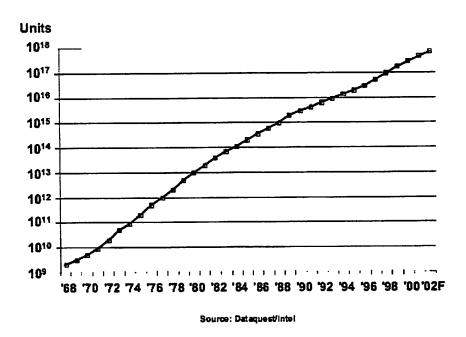

"I tried to illustrate this number, ten to the eighteenth, and I've used raindrops falling on California. E.O. Wilson, a noted Harvard biologist and expert on ants, estimates that the number of ants in the world is between ten to the sixteenth and ten to the seventeenth. So for years I used that. Now each ant has to carry ten to a hundred transistors." These are the words used by INTEL® co-founder, Gordon Moore, during his keynote address at the 50th anniversary of the International Solid-State Circuits Conference while commenting on the estimated number of transistors produced during the year 2002 by the semiconductor industry [174].