# Copyright © 2005, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# ULTRA-LOW POWER WIRELESS TECHNOLOGIES FOR SENSOR NETWORKS

by

Brian Patrick Otis

Memorandum No. UCB/ERL M05/16

29 April 2005

# ULTRA-LOW POWER WIRELESS TECHNOLOGIES FOR SENSOR NETWORKS

by

**Brian Patrick Otis**

Memorandum No. UCB/ERL M05/16

29 April 2005

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### Ultra-Low Power Wireless Technologies for Sensor Networks

by

#### Brian Patrick Otis

B.S. (University of Washington, Seattle) 1999 M.S. (University of California, Berkeley) 2002

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Dissertation Committee:

Professor Jan Rabaey, Chair Professor Roger Howe Professor Paul Wright

Spring, 2005

### The dissertation of Brian Otis is approved by:

Professor Jan Rabaey, Chair

Professor Roger Howe

Professor Paul Wright

University of California, Berkeley

Spring, 2005

Ultra-Low Power Wireless Technologies for Sensor Networks

Copyright 2005

by

Brian Patrick Otis

#### **Abstract**

Ultra-Low Power Wireless Technologies for Sensor Networks

by

Brian Patrick Otis

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Jan Rabaey, Chair

The new field of wireless sensor networks presents many opportunities and just as many challenges. One particularly difficult aspect of wireless sensing is the implementation of the radio link. To enable energy scavenging, a technique that harvests ambient energy to power the sensor node indefi-

nitely, sub-mW power levels are necessary for the receiver. To allow a small node form-factor, all external surface-mount components must be eliminated. Traditional RF transceiver design techniques are not suitable for achieving complete integration since they rely on frequency synthesis, requiring a surface mount quartz crystal and a power hungry on-chip phase locked loop.

This thesis demonstrates that subthreshold RF CMOS circuit design and high quality RF MEMS passive components are useful tools for reducing the power consumption and increasing the level of integration of GHz-range transceivers. To demonstrate these concepts, two transceivers using these principles were designed, implemented, and tested. One was a multiple channel 3mW receiver. The other is a  $400\mu$ W super-regenerative receiver with a 1mm³ total implementation volume. A 20m indoor wireless link and operation with scavenged energy was demonstrated. Finally, to further address integration concerns, a CMOS/MEMS reference clock was designed to replace the quartz crystal reference and flip-chip techniques were shown to further reduce the transceiver size.

# **Table of Contents**

| $\mathbf{A}$ | bstra | nct                                                            | 1  |

|--------------|-------|----------------------------------------------------------------|----|

| Li           | st of | Figures                                                        | v  |

| Li           | st of | Tables                                                         | ix |

| A            | ckno  | wledgements                                                    | хi |

| 1            | Wii   | eless Sensor Networks                                          | 1  |

|              | 1.1   | The PicoRadio Project                                          | 3  |

|              | 1.2   | System Requirements                                            | 4  |

|              | 1.3   | Energy Scavenging                                              | 5  |

|              | 1.4   | RF Transceiver Requirements                                    | 7  |

|              |       | 1.4.1 Power Consumption                                        | 8  |

|              |       | <u>−</u>                                                       | 8  |

|              |       | 1.4.3 Range                                                    | 9  |

|              |       | <del>-</del>                                                   | 10 |

|              |       | 1.4.5 Turn-On Time                                             | 11 |

|              |       | 1.4.6 Integration/Power Tradeoff                               | 12 |

|              | 1.5   | · · · · · · · · · · · · · · · · · · ·                          | 15 |

|              | 1.6   |                                                                | 16 |

| 2            | Low   | Power CMOS Design for Radio Frequencies                        | 21 |

|              | 2.1   | Weak Inversion RF CMOS                                         | 22 |

|              | 2.2   | MEMS Background                                                | 24 |

|              | 2.3   | Circuit Proof-of-Concept I: $300\mu W$ Pierce Oscillator       | 31 |

|              | 2.4   | Circuit Proof-of-Concept II: Differential $300\mu W$ BAW-Based |    |

|              |       | Oscillator                                                     | 11 |

## TABLE OF CONTENTS

|   |     | 2.4.1 Analysis/Design                      |

|---|-----|--------------------------------------------|

|   |     | 2.4.2 Experimental Results (1.9GHz) 46     |

|   |     | 2.4.3 Experimental Results (2.4GHz)        |

|   | 2.5 | ·                                          |

| 3 | Tw  | vo Channel BAW-Based Transceiver 63        |

|   | 3.1 | Architecture                               |

|   | 3.2 |                                            |

|   | 3.3 | _                                          |

|   |     | 3.3.1 Active Inductor                      |

|   |     | 3.3.2 Standalone RF Amplifier              |

|   |     | 3.3.3 In-Situ RF Amplifier                 |

|   | 3.4 |                                            |

|   | 3.5 | Transmitter Architecture and Design 83     |

|   | 3.6 | Experimental Results                       |

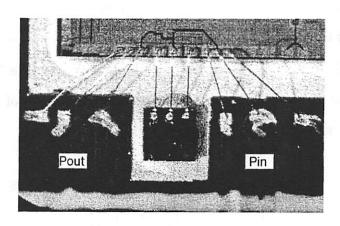

|   |     | 3.6.1 Implementation                       |

|   |     | 3.6.2 Receiver                             |

|   |     | 3.6.3 Transmitter                          |

|   | 3.7 |                                            |

| 4 | Sur | per-Regenerative Receiver Design 93        |

|   | 4.1 | History of the Super-regenerative Receiver |

|   | 4.2 | Motivation                                 |

|   | 4.3 | Architecture                               |

|   | 4.4 | Analysis                                   |

|   |     | 4.4.1 Operation                            |

|   |     | 4.4.2 Super-regenerative gain              |

|   |     | 4.4.3 Super-regenerative bandwidth         |

|   |     | 4.4.4 Quench frequency limitations         |

|   | 4.5 |                                            |

|   | 4.6 | Additional Circuitry                       |

|   | 4.7 | Experimental Results                       |

|   |     | 4.7.1 Board Design                         |

|   |     | 4.7.2 Testing Methodology                  |

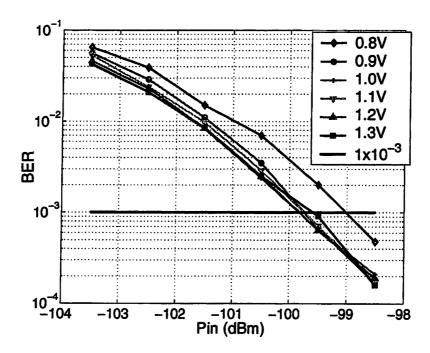

|   |     | 4.7.3 Results                              |

|   | 4.8 | Discussion 121                             |

### TABLE OF CONTENTS

| 5  | Ful        | ly Integrated Super-Regenerative Transceiver | 123 |

|----|------------|----------------------------------------------|-----|

|    | 5.1        | Architecture                                 | 124 |

|    | 5.2        | RF Front-End Circuit Design                  | 124 |

|    | 5.3        | Pulse Width Demodulator                      |     |

|    |            | 5.3.1 Filter Specifications                  |     |

|    |            | 5.3.2 Filter Synthesis and Design            |     |

|    | 5.4        | Capacitance Tuning                           |     |

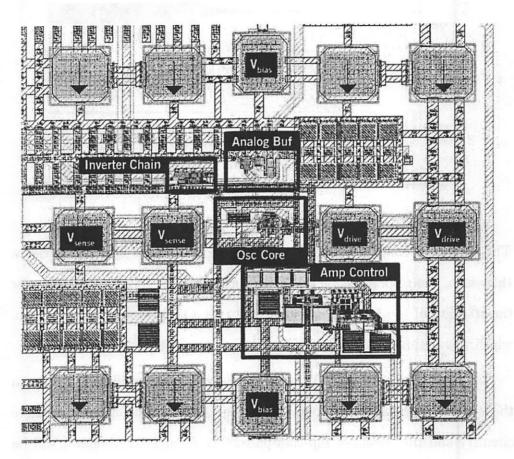

|    | 5.5        | Chip Implementation                          |     |

|    | 5.6        | Measured Results                             |     |

|    |            | 5.6.1 Serial Interface                       |     |

|    |            | 5.6.2 RF Front-End                           |     |

|    |            | 5.6.3 Temperature Compensation               |     |

|    |            | 5.6.4 Baseband                               |     |

|    |            | 5.6.5 Link Demonstration                     |     |

|    | 5.7        | Discussion                                   |     |

| 6  | Into       | egration Techniques 1                        | 51  |

| U  | 6.1        |                                              |     |

|    | 0.1        | 6.1.1 Silicon Resonator Background           |     |

|    |            |                                              |     |

|    | 6.2        | <b>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,</b>       |     |

|    | 0.2        | Flip-Chip Packaging                          |     |

|    |            |                                              |     |

|    | <i>c</i> o | 6.2.2 Super-Regenerative Flip-Chip           |     |

|    | 6.3        | Conclusions                                  | 113 |

| 7  | Con        | aclusions 1                                  | 75  |

| Ri | hling      | rranhy 1                                     | 84  |

# List of Figures

| 1.1  | Hardware blocks for sub-mW sensor network implementations                      | 3          |

|------|--------------------------------------------------------------------------------|------------|

| 1.2  | Radio range for receiver with a -70dBm sensitivity                             | 11         |

| 2.1  | The transconductance efficiency is plotted vs. the inversion                   |            |

|      | coefficient                                                                    | 23         |

| 2.2  | 50MHz Capacitively Driven/Sensed Resonator                                     | 25         |

| 2.3  | Simplified circuit equivalent model of a BAW resonator                         | 29         |

| 2.4  | Simplified oscillator schematic                                                | 34         |

| 2.5  | Optimization of BAW resonator area. Three curves are shown                     |            |

|      | with various values of $C_1 = C_2 \ldots \ldots \ldots \ldots$                 | 36         |

| 2.6  | Photograph of the CMOS/BAW prototype oscillator                                | 38         |

| 2.7  | Measured phase noise performance of the oscillator                             | 39         |

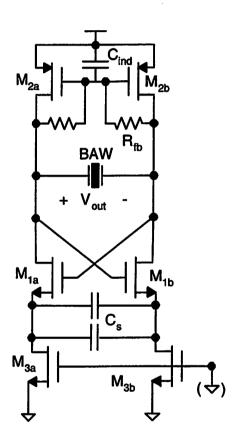

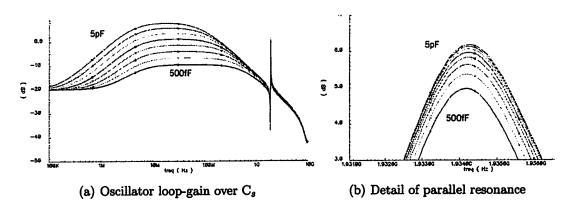

| 2.8  | Simplified schematic of differential oscillator                                | 43         |

| 2.9  | Simulation results of oscillator loopgain for varying values of C <sub>s</sub> | 44         |

|      | (a) Oscillator loop-gain over $C_s$                                            | 44         |

|      | (b) Detail of parallel resonance                                               | 44         |

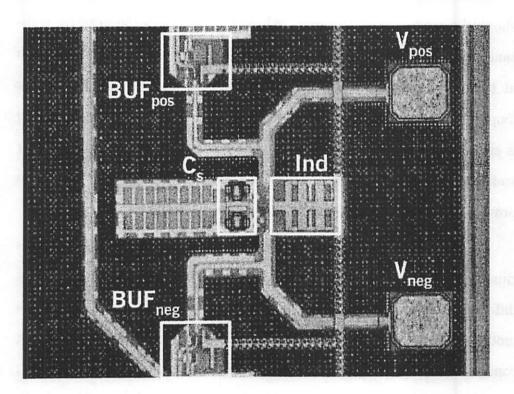

| 2.10 | Differential oscillator layout detail                                          | 46         |

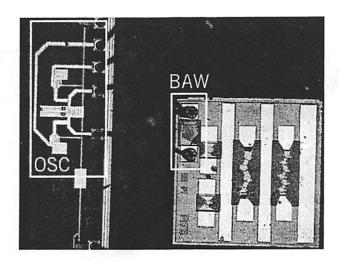

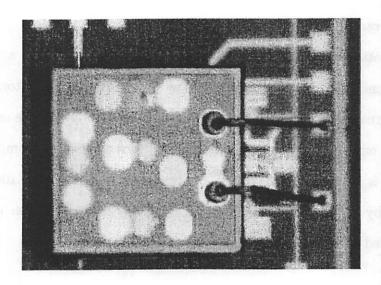

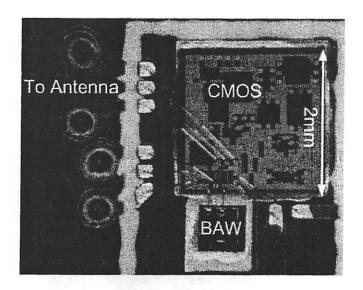

| 2.11 | Differential oscillator COB assembly                                           | 47         |

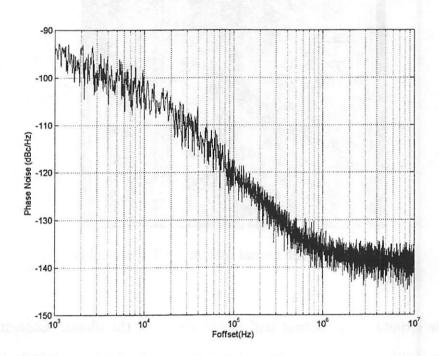

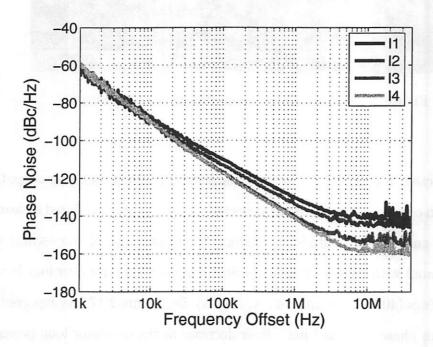

| 2.12 | Measured differential oscillator phase noise                                   | 48         |

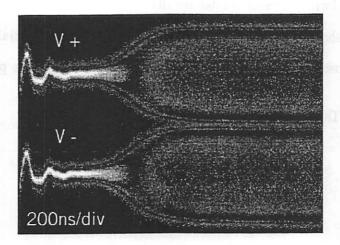

| 2.13 | Measured differential oscillator start-up transient                            | 50         |

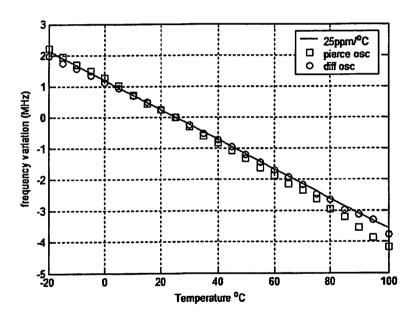

| 2.14 | Measured temperature coefficient of oscillation for two CMOS                   |            |

|      | oscillators                                                                    | 52         |

| 2.15 | ISM implementation of differential oscillator                                  | 54         |

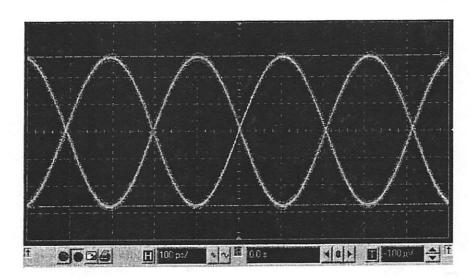

| 2.16 | ISM differential oscillator transient output                                   | 55         |

| 2.17 | ISM differential oscillator phase noise                                        | 56         |

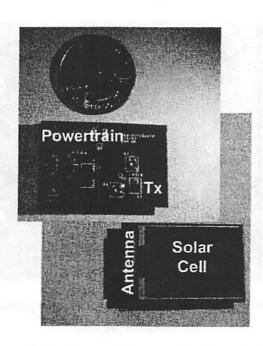

| 2.18 | RF Transmitter COB implementation                                              | 59         |

|      | Transmit beacon implementation                                                 | <b>6</b> 0 |

| 2.20 | RF transmit beacon under low light conditions                                  | 61         |

### LIST OF FIGURES

| 3.1                                                                                        | Block diagram of the two-channel transceiver 6                                                                                    |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 3.2                                                                                        | Simplified receiver front-end schematic 6                                                                                         |

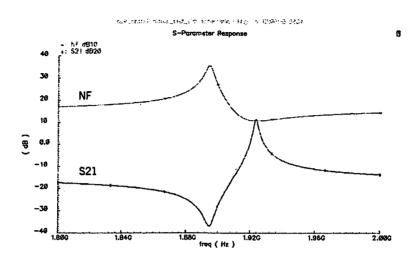

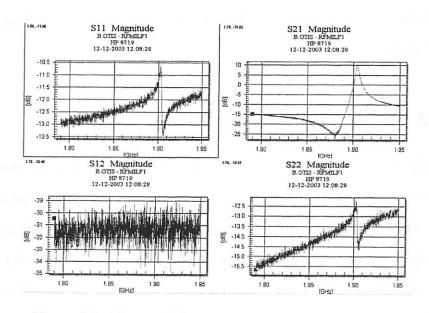

| 3.3                                                                                        | Measured S-parameters of the LNA test structure 6                                                                                 |

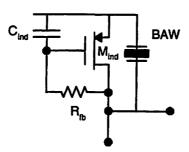

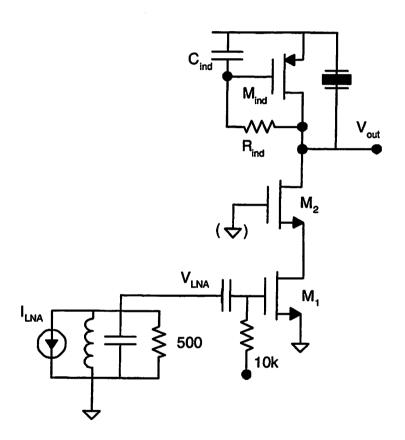

| 3.4                                                                                        | Schematic of active choke inductor structure                                                                                      |

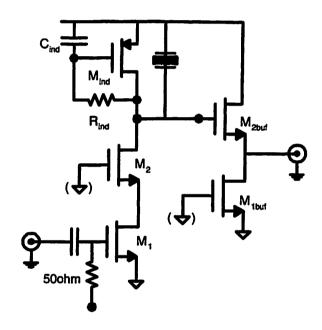

| 3.5                                                                                        | Standalone RF amplifier schematic                                                                                                 |

|                                                                                            |                                                                                                                                   |

| 3.6                                                                                        |                                                                                                                                   |

| 3.7                                                                                        | <b>0</b> 1                                                                                                                        |

| 3.8                                                                                        | Measured S-Parameters of the RF Amplifier                                                                                         |

| 3.9                                                                                        | Schematic of in-situ RF amplifier                                                                                                 |

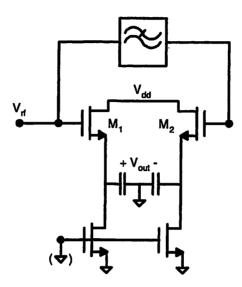

|                                                                                            | Schematic of the RF Detector                                                                                                      |

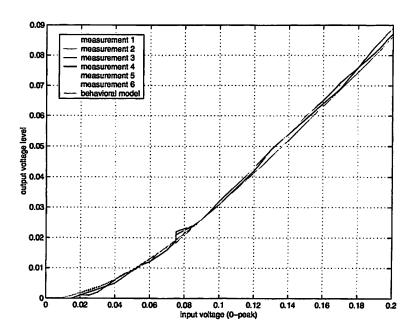

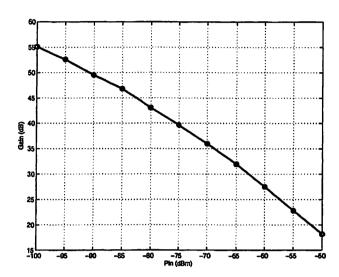

|                                                                                            | Measured conversion gain of the envelope detector 83                                                                              |

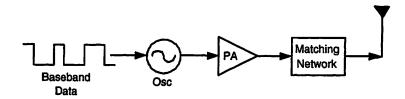

|                                                                                            | Block diagram of the transmitter                                                                                                  |

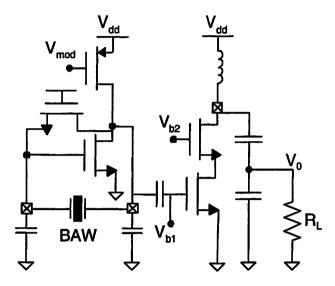

|                                                                                            | OOK Transmitter Schematic                                                                                                         |

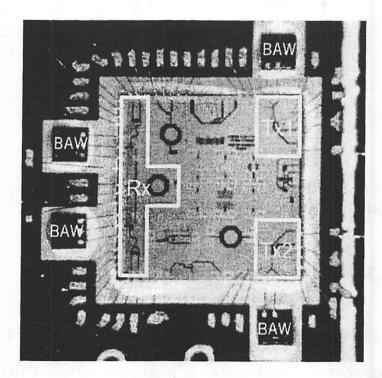

|                                                                                            | Photograph of the transceiver implementation 86                                                                                   |

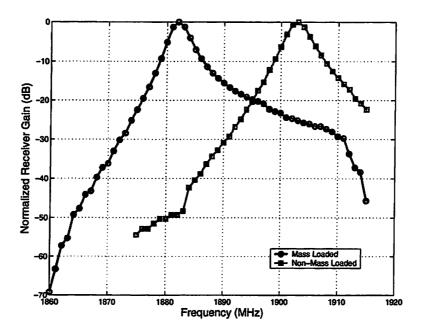

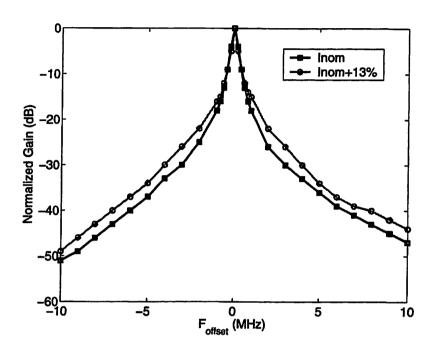

|                                                                                            | Normalized receiver gain of both channels 87                                                                                      |

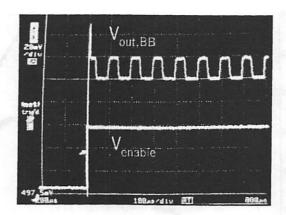

|                                                                                            | Receiver enable-to-data start-up time                                                                                             |

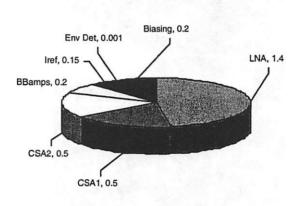

|                                                                                            | Breakdown of the receiver current consumption (mA) 89                                                                             |

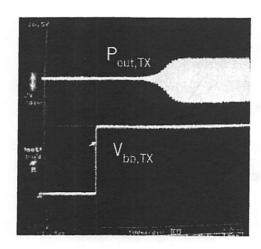

| 3.18                                                                                       | Transmitter modulation start-up time                                                                                              |

|                                                                                            |                                                                                                                                   |

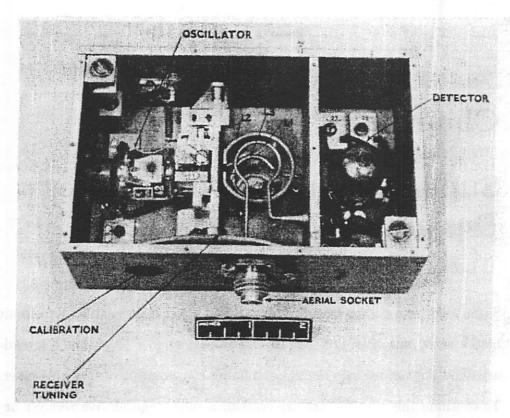

| 4.1                                                                                        | Vintage 1940s two-tube super-regenerative detector [1] 94                                                                         |

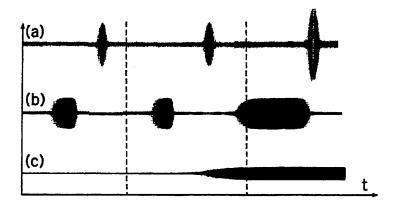

| 4.1<br>4.2                                                                                 | Vintage 1940s two-tube super-regenerative detector [1] 94<br>Conceptual diagram of super-regenerative detection 96                |

|                                                                                            | Conceptual diagram of super-regenerative detection 96                                                                             |

| 4.2                                                                                        | Conceptual diagram of super-regenerative detection 96 Modes of super-regenerative operation. a) Linear b) Logarith-               |

| 4.2                                                                                        | Conceptual diagram of super-regenerative detection 96 Modes of super-regenerative operation. a) Linear b) Logarithmic c) RF Input |

| 4.2<br>4.3                                                                                 | Conceptual diagram of super-regenerative detection 96 Modes of super-regenerative operation. a) Linear b) Logarithmic c) RF Input |

| 4.2<br>4.3<br>4.4                                                                          | Conceptual diagram of super-regenerative detection                                                                                |

| 4.2<br>4.3<br>4.4<br>4.5                                                                   | Conceptual diagram of super-regenerative detection                                                                                |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6                                                            | Conceptual diagram of super-regenerative detection                                                                                |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7                                                     | Conceptual diagram of super-regenerative detection                                                                                |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                                              | Conceptual diagram of super-regenerative detection                                                                                |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                                       | Conceptual diagram of super-regenerative detection                                                                                |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                                       | Conceptual diagram of super-regenerative detection                                                                                |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                                       | Conceptual diagram of super-regenerative detection                                                                                |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10                               | Conceptual diagram of super-regenerative detection                                                                                |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12               | Conceptual diagram of super-regenerative detection                                                                                |

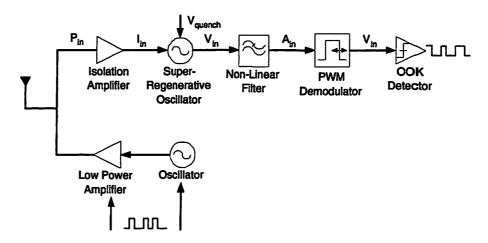

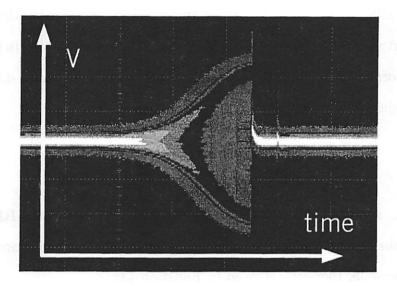

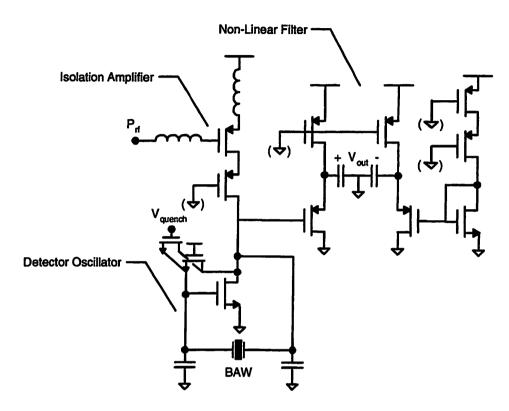

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>5.1        | Conceptual diagram of super-regenerative detection                                                                                |

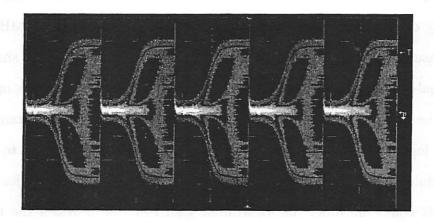

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>5.1<br>5.2 | Conceptual diagram of super-regenerative detection                                                                                |

### LIST OF FIGURES

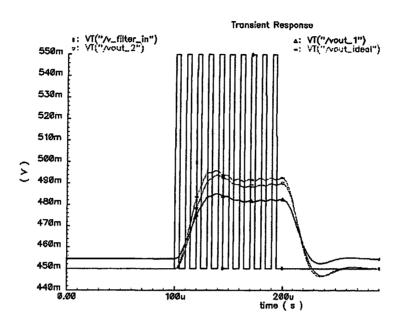

| 5.4         | System-level simulation of pulse-width demodulator              | 129 |

|-------------|-----------------------------------------------------------------|-----|

| 5.5         | Pulse width demodulator filter ladder                           | 130 |

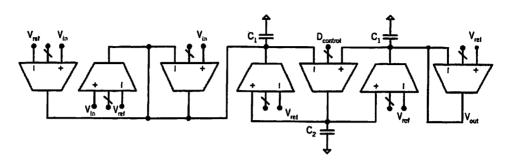

| 5.6         | Schematic of the filter transconductor                          |     |

| 5.7         | Layout of the filter OTA                                        |     |

| 5.8         | Layout of the pulse width demodulator                           |     |

| 5.9         | Schematic of binary weighted switched capacitor tuning array    | 135 |

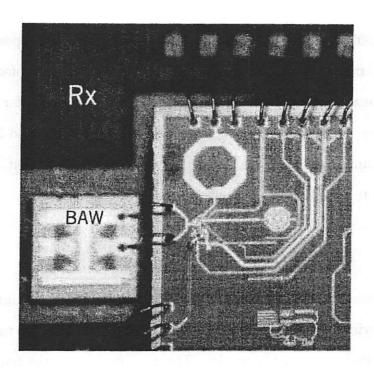

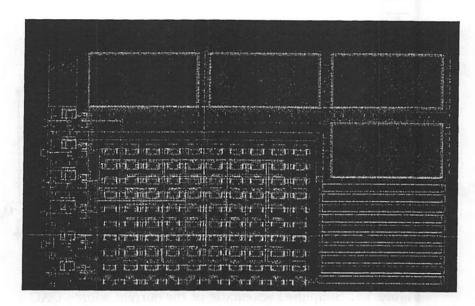

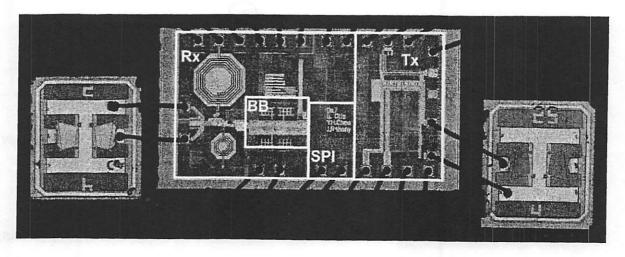

| 5.10        | Chip photograph of the assembled integrated transceiver         | 136 |

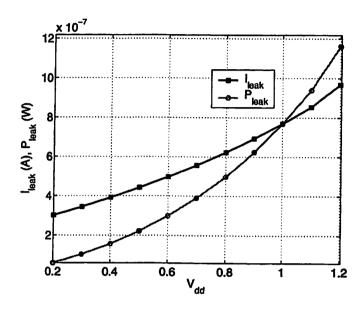

| 5.11        | Measured leakage current and power of digital control block .   | 138 |

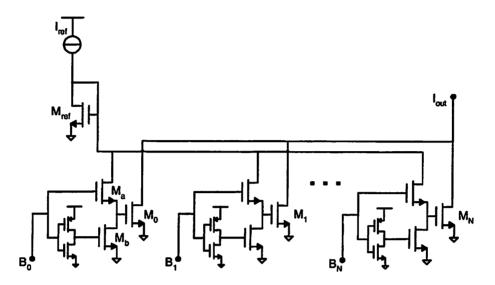

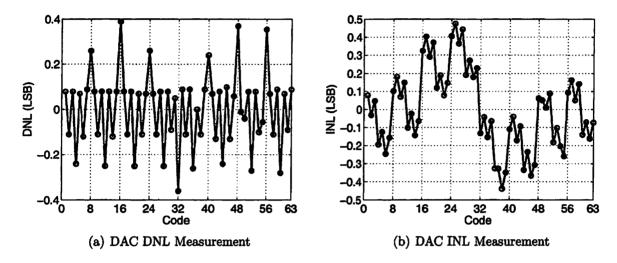

| 5.12        | Measured linearity of the current source DAC                    | 139 |

|             | (a) DAC DNL Measurement                                         |     |

|             | (b) DAC INL Measurement                                         | 139 |

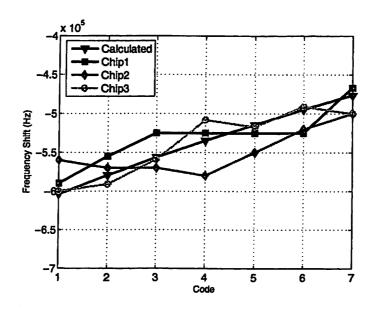

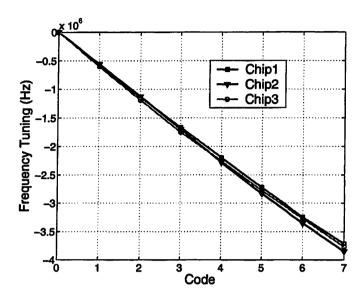

| 5.13        | Incremental frequency shift over all codes                      | 140 |

| 5.14        | Switched capacitor frequency tuning of receiver                 | 141 |

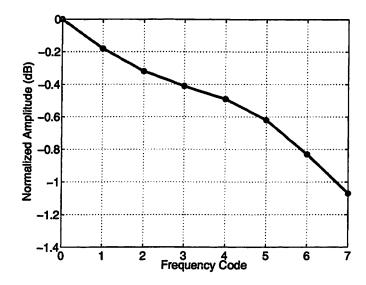

| 5.15        | Measured super-regenerative oscillator amplitude vs. frequency  |     |

|             | code                                                            | 142 |

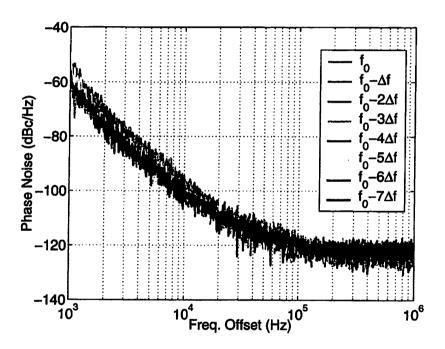

| 5.16        | Measured phase noise of detector oscillator over tuning range . | 143 |

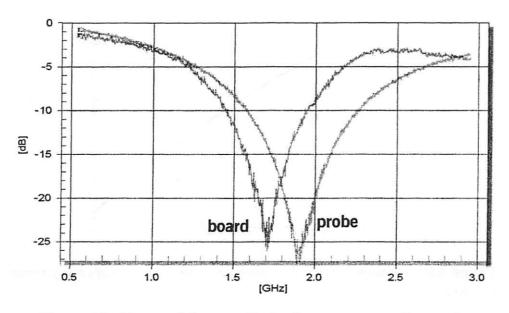

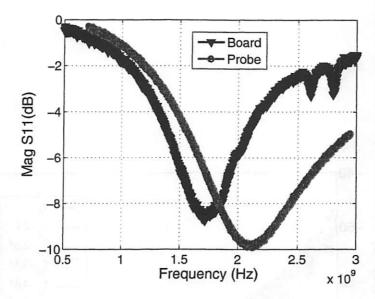

| 5.17        | Magnitude of receiver S <sub>11</sub> :                         | 144 |

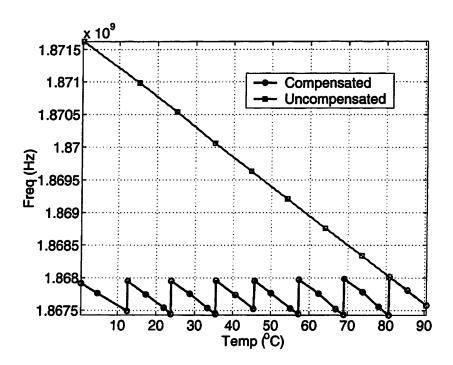

| 5.18        | Temperature compensation of BAW-based receiver                  | 145 |

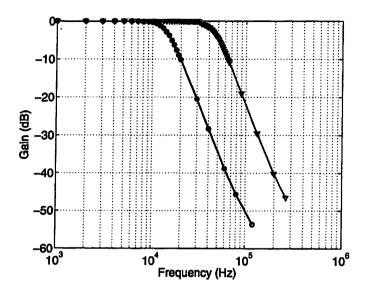

| 5.19        | Measured frequency response of baseband filter at the high      |     |

|             | and low bandwidth settings                                      | 147 |

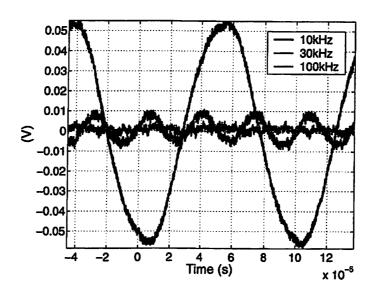

| 5.20        | Measured ripple of the pulse-width demodulator at quench        |     |

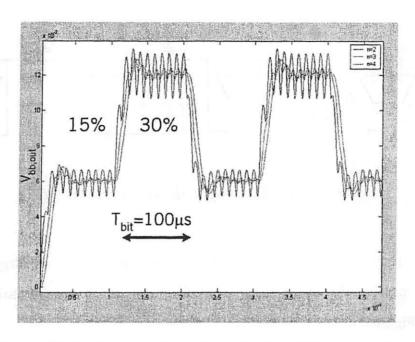

|             | frequencies of 10kHz, 30kHz, and 100kHz                         | 148 |

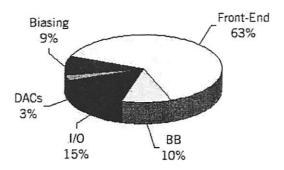

| 5.21        | Power breakdown of the fully integrated super-regenerative      |     |

|             | receiver                                                        | 149 |

| C 1         | A recent wireless sensor network transceiver implementation .   | 153 |

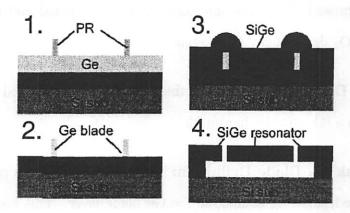

| 6.1         | Cross-sectional process sequence                                | 156 |

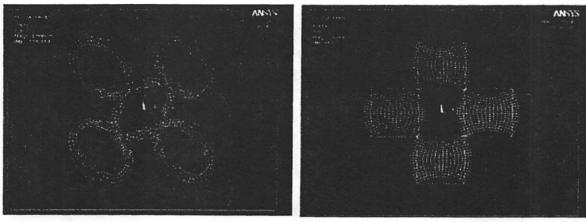

| 6.2         | Simulation of the coupled wineglass and lamé mode resonators    | 157 |

| 6.3         |                                                                 | 157 |

|             | (a) Coupled wineglass mode resonator                            |     |

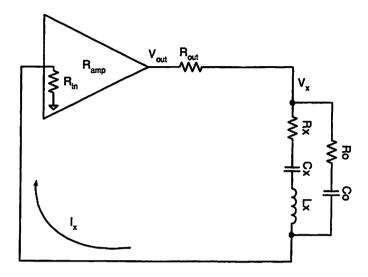

| 6.4         | Conceptual schematic of 16MHz clock oscillator                  | 159 |

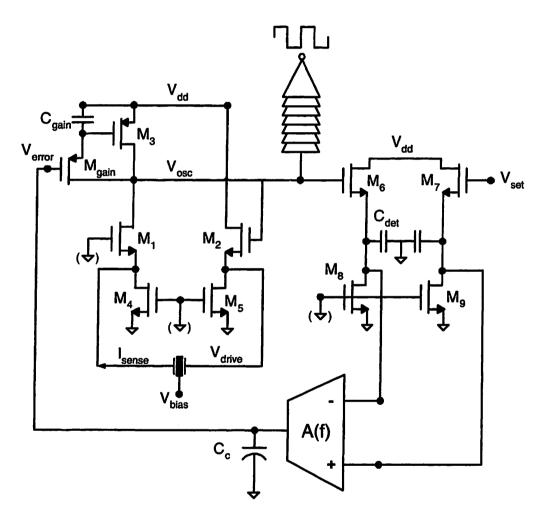

| 6.5         | Schematic of 16MHz clock oscillator                             | 161 |

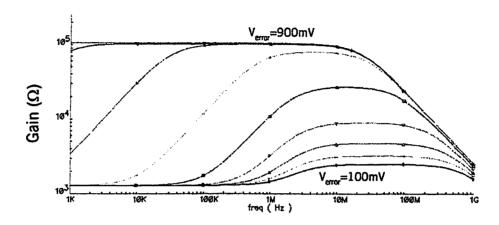

| 6.6         | Gain $(\Omega)$ of the transimpedance amplifier                 | 162 |

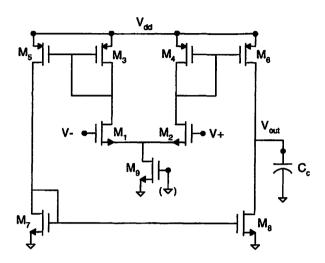

| 6.7         | Schematic of amplitude control OTA                              | 163 |

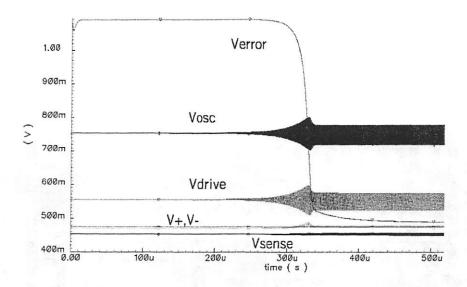

| 6.8         | Simulation of amplitude control loop convergence                | 165 |

| 6.9         | Layout of 16MHz reference clock                                 | 166 |

| 6.3<br>6.10 | BAW flipped on a 0.18µm CMOS oscillator                         | 169 |

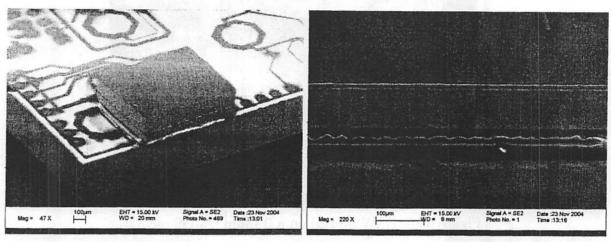

| 6 11        | SEM image of super-regenerative flip-chip                       | 170 |

### LIST OF FIGURES

|      | (a)  | BAW flip-chip                                                            |

|------|------|--------------------------------------------------------------------------|

|      |      | Detail of BAW/CMOS interface                                             |

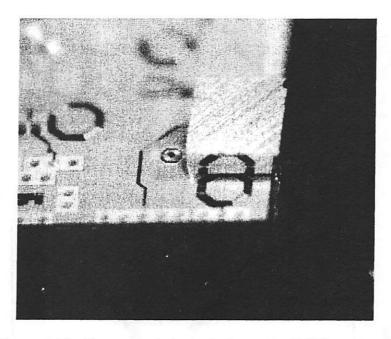

|      |      | rage of planar inductor by BAW resonator 171                             |

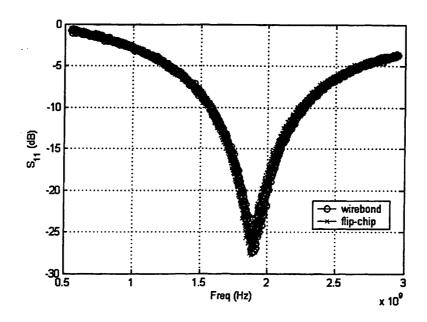

| 6.13 | Supe | r-regenerative S <sub>11</sub> : Effect of flip-chip proximity on planar |

|      | indu | ctors                                                                    |

# List of Tables

| 1.1 | Average power density of various energy storage and scavenging devices [2] |

|-----|----------------------------------------------------------------------------|

| 2.1 | Comparison of recently published RF oscillators 40                         |

| 2.2 | Measured oscillator phase noise $(\frac{dBc}{Hz})$                         |

| 2.3 | Measured oscillator harmonic distortion $(dBc)$ 50                         |

| 3.1 | Active inductor design values                                              |

| 3.2 | Breakdown of RF amplifier noise sources                                    |

| 3.3 |                                                                            |

| 3.4 |                                                                            |

| 4.1 | Super-Regenerative Receiver Performance Summary 122                        |

| 5.1 | Measured demodulator performance over tuning range 146                     |

| 6.1 | Predicted resonator parameters for different achieved gaps 157             |

| 6.2 | Flip-chip epoxy characteristics                                            |

| 6.3 |                                                                            |

# Acknowledgements

The past six years in Berkeley has truly been a fascinating experience. To acknowledge everyone who contributed to these experiences would double the length of this thesis. Thank you all.

First, I'd like to thank my advisor Professor Jan Rabaey for all he has done to make this research possible. Jan is a true visionary. He will continue to influence my work long after he signs my thesis.

My work with Professor Paul Wright and his students has been a pleasure.

I would also like to thank Professor Ali Niknejad for his valuable advice and suggestions about research, careers, and academic positions.

A long and intensive collaboration with Agilent Technologies was an integral part of this work. Mike Frank and Richard Ruby have supported this project from the beginning. Jeff LaTourette went to great lengths to secure a Bit Error Rate tester. Brian Kautz was extremely helpful in taking accurate phase noise and amplifier noise figure measurements. Dorie Delapena has turned complex wirebonding and assembly into an artform, and has enabled many of the unique prototypes presented here. I look forward to continuing

to work with all of you.

It has been great working with the creative individuals at the Berkeley Sensor and Actuator Center (BSAC). In particular, Professor Roger Howe, Sunil Bhave, Emmanuel Quévy, Peter Chen, and Carrie Low have been great to work with on the IMT project. Special thanks to Carrie for helping with the SEM images in this thesis and Peter for the wirebonding help.

The Berkeley Wireless Research Center (BWRC), founded and conceived by Bob Brodersen and Jan Rabaey, has been a wonderful place to study over the years. Thanks to everyone at "The Center" for making this time memorable. In particular, the PicoRadioRF team (Yuen-Hui Chee, Nate Pletcher, Richard Lu, Simone Gambini) has been instrumental in turning these ideas into reality. Special thanks to Nate for helping to keep it real. Tom Boot and Brenda Vanoni have made everything at the BWRC run smoothly and have created a great environment in which to work.

I would like to acknowledge Professor Eve Riskin from the University of Washington for her candid advice over the years. Thanks to Professors Ralph Freeman (U.C. Berkeley) and Kelly Tremblay (U. Washington) who took a chance on an Electrical Engineer wanting to learn more about the brain.

Thanks to my family for their support over the years. My Mom, Dad, and sister Sara have now spent years feigning interest while looking through a microscope at a die or a layout plot of one of my chips. I will conclude with a schematic drawn by my Grandpa Moose on a Post-It note during a brief lecture he gave me many years ago on vacuum tube amplification. Even

though I didn't fully understand the concepts at the time, it goes to show that inspiration can come from strange places...

Brian P. Otis

Berkeley, 2005

# Chapter 1

# Wireless Sensor Networks

The accurate quantification of environmental parameters has been an important part of human existence for centuries. In 1612, Santorio Santorio invented the graduated thermometer, and human curiosity and quest for knowledge has been growing ever since. Modern sensing parameters include humidity, seismic activity, building occupation, airflow, particulate detection, and many others. A wireless sensor monitors one or more environmental parameters and transmits the data to the network for automatic control or human evaluation. This process could include data compression and accumulation to reduce the amount of transmitted data. One could conceive of a huge network of these sensors that are able to communicate with each other. Decades of technological advances have made it conceivable to build and deploy dense wireless networks of autonomous nodes collecting and disseminating wide ranges of environmental data. Wireless sensor networks

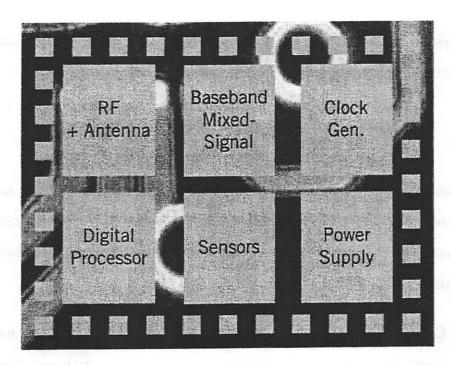

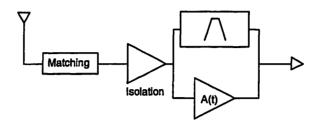

have many valuable potential applications, ranging from closed-loop environmental control of office buildings and homes to wildlife monitoring. Other possible applications are robot control and guidance in automatic manufacturing environments, warehouse inventory, integrated patient monitoring, diagnostics and drug administration in hospitals, home providing security, identification and personalization, and interactive museums. Successful deployment of wireless sensor and actuator networks in sufficient numbers to provide true ambient intelligence will require the confluence of progress in several disciplines: networking, low power RF and digital IC design, MEMS techniques, energy scavenging, and packaging. Figure 1.1 shows the various specialized blocks of a sensor node.

In large-scale system designs, some of these blocks (clock generation, for example) are often considered negligible in terms of power and volume. However, in the implementation of extremely small sensor nodes, each of these components becomes crucial. The most challenging aspect of sensor node implementation is the integration of ultra-low power RF transceivers. It will be shown that the requirements of these transceivers are fundamentally different from those of existing wireless applications, such as cellular telephony, Bluetooth specification radios, and wireless local area network (WLAN) transceivers. The goal of this dissertation is to address some of the design challenges involved with integrating RF communication functionality in a self-contained sensor node.

This chapter introduces the University of California, Berkeley PicoRadio

Figure 1.1: Hardware blocks for sub-mW sensor network implementations

project and describes system level requirements for ad-hoc sensor nodes. The RF transceiver challenges are discussed, including range, sensitivity, power consumption, and integration requirements.

# 1.1 The PicoRadio Project

The *PicoRadio* Project at the University of California, Berkeley was founded by Professor Jan Rabaey to identify and address technical barriers to the implementation and large-scale deployment of wireless ad-hoc sensor networks [3]. As will be shown in this chapter, the most challenging aspect of

the system implementation is the radio frequency communication datalink. We will begin with a description of the system requirements.

## 1.2 System Requirements

To make dense node deployment possible in practical scenarios, each node must be physically and economically unobtrusive. A node's "obtrusiveness" can be measured by three important metrics: energy scavenging capability, cost and size. These requirements are outlined below.

- Energy Scavenging: To reduce installation cost and to allow for a

flexible method of deployment, most nodes must be untethered. Maintenance cost considerations render frequent replacement of the energy

source of the node unrealistic. Thus, the nodes must scavenge their

energy from the environment. This leads to a very aggressive node

average power budget of approximately 100μW.

- Low Cost Implementation: Commercial viability dictates that the unit cost  $(\frac{\$}{m^2})$  of the wireless sensor network mesh be very small. For network reliability and high sensing resolution, the node density  $(\frac{nodes}{m^2})$  must be high. Thus, the cost of each node must be extremely low (<1\$US).

- Small Form Factor: Embedding the components into the existing infrastructure of daily environments (walls, furniture, lighting, etc.)

requires a very small form factor of the entire sensor node. Typically, node volumes less than 1cm<sup>3</sup> (much smaller than a AA battery) are necessary. A very high level of integration is mandatory if such small dimensions are to be achieved.

The ubiquitous deployment of sensor nodes is economically feasible only if the individual nodes are negligible in cost and size. Achieving such a diminutive stature requires a minimal number of components, a high level of integration, simple and cheap packaging and assembly, and avoidance of expensive components and/or technologies. In the next section, energy scavenging for wireless sensor networks will be discussed, which determines the transceiver power consumption requirements.

## 1.3 Energy Scavenging

The considerations discussed above dictate that each sensor node be self-sufficient from an energy perspective for the lifetime of the node. This may span up to 10 years for certain building environmental control applications. The energy storage capability of a node is limited by the storage medium (battery or capacitor) and the size constraints. While a single-time charge could work for applications with life cycles below one year, replenishment of the energy supply using energy scavenging is often a necessity. Table 1.1 illustrates the finite power density of state-of-the-art energy sources [2].

Thus, the average power dissipation of the node is severely constrained

Table 1.1: Average power density of various energy storage and scavenging devices [2]

| Power Source          | Power Density $\frac{\mu W}{cm^3}$ | Lifetime |

|-----------------------|------------------------------------|----------|

| Lithium Battery       | 100                                | 1 year   |

| Micro Fuel Cell       | 110                                | 1 year   |

| Solar Cell            | $10-15000(\frac{\mu W}{cm^2})$     | 8        |

| Vibrational Converter | 375                                | ∞        |

| Air Flow              | 380                                | ∞        |

| Temperature Gradients | 50                                 | ∞        |

by the energy scavenging volume of the node. These sources can be broadly grouped into two categories: energy scavenging sources and energy storage sources. From a volume of  $1 \text{cm}^3$ , an average continuous power output of  $100 \mu\text{W}$  could be supplied by one or a combination of these power sources. If a one year lifetime were acceptable, either a lithium battery or fuel cell would suffice. However, micro fuel cell technology is still in the early stages of research, and is prohibitively complex and expensive. Another active area of research is in thin-film battery technology, which will yield large benefits for sensor node implementations. For desired node lifetimes greater than one year, however,  $1 \text{cm}^3$  does not provide ample storage for the node's  $3110 \frac{J}{year}$  energy requirements. Typical node deployment scenarios would demand a 10 year lifetime (31kJ). This is a prohibitively large amount of energy to store in a  $1 \text{cm}^3$  volume, necessitating the harvesting of energy from the environment.

Solar power is a proven, universal method of collecting ambient energy. For outdoor or high-light conditions, this is the obvious solution. However, in dim lighting conditions, the power output drops dramatically. In these environments, an additional energy source is needed. Vibrational converters, air flow generators, and temperature gradient generators all produce  $50\text{-}400\frac{\mu W}{cm^3}$ , as listed in Table 1.1. Of the three, vibrational converters are the simplest and have the most potential for wafer-scale fabrication. In conclusion, a 1cm<sup>3</sup> sensor node can support an average power draw of  $100\mu W$ . A combination of solar and vibrational energy scavenging and battery energy storage is likely to yield the most robust and inexpensive solution.

In addition to limitations on average power dissipation, the available peak power levels that can be supplied to the electronics are also limited. Since most microscale energy scavenging and storage devices provide a naturally high impedance, the peak current drive capability is small (less than a few mA). Providing high drive current would require excessively large storage capacitors and complex voltage regulators. The RF datalink circuit design must address this issue by presenting a low peak active current draw.

The next section describes the implication of the energy scavenging requirements on the RF datalink.

## 1.4 RF Transceiver Requirements

This section describes the transceiver requirements that are unique to sensor node communication. As will be shown, the radio requirements are very different from traditional low power transceivers (pager receivers, RFID tags, Bluetooth-specification radios, keyless-entry).

### 1.4.1 Power Consumption

In the design of prototype sensor nodes, the wireless interface consumes the largest fraction of the power and size budget of the node. While the demands of the sensing and digital processing components cannot be ignored, their duty cycle is typically very low. A combination of advanced sleep, power-down, and leakage reduction techniques makes it possible to make their average power dissipation virtually negligible [4]. Thus, the wireless interface for sensor networks is the dominant source of power consumption. While optical communication approaches offer the potential of very low power and small size, line-of-sight and directivity considerations make them less attractive [5]. For this work, we will limit our discussion to RF interfaces.

#### 1.4.2 Datarate

As mentioned, the requirements of a transceiver for wireless sensor networks differ dramatically from a traditional wireless link. Thus, common performance metrics such as  $\frac{energy}{bit}$  and  $\frac{bits}{Hz}$  should be applied with the realization that other factors prevail. For example, a modified metric such as  $\frac{energy}{useful-bit}$  is relevant if all sources of power and overhead (for example: synchronization, the impact on energy storage) are included. First we will examine the typical operation mode of the sensor node. An investigation of the traffic patterns and data payloads reveal that the transceiver operation is fundamentally different than a wireless LAN or Bluetooth-specification radio. Data packets

in sensor networks tend to be relatively rare and unpredictable events. In most application scenarios, each node in the network sees only a few packets/second. In addition, the packets are relatively short (typically less than 200 bits/packet). This is expected as the payloads normally represent slowly varying and highly correlated environmental data measurements. Combined, this means that the average data rate of a single node rarely exceeds  $1 \frac{kbit}{s}$ . These observations are of foremost importance when designing the wireless transceiver, as we will highlight in the following sections.

### 1.4.3 Range

In the rest of the discussion, we will assume that the sensor networks of interest are dense, which means that the nodes in the network are placed relatively closely (the average distance between nodes is less than or equal to 10m). For a given sensitivity, scaling the node to larger ranges would require additional transmit power or increased coding gain (longer transmit times). As the transmitted power increases in low power transmitters, the global transmitter efficiency increases. Thus, in short-distance links, increasing the transmitted power the preferred approach over increased coding gain. As the transmitted power increases, a linear increase in the link budget is obtained for a sub-linear increase in the transmitter power consumption. Improving the link budget through coding gain would involve linear or super-linear increases in the receive power consumption due to increased packet length and/or higher received bandwidths. Indeed, at transmitted power levels of

-10dBm and below, a majority of the transmit mode power is dissipated in the circuitry and not radiated from the antenna. However, at high transmit levels (over 0dBm), the active current draw of the transmitter is high. It is difficult to source high active currents with micro-scale energy scavengers and batteries. Convenient and efficient transmit power levels for sensor node applications are roughly in the range of -10 to +3 dBm.

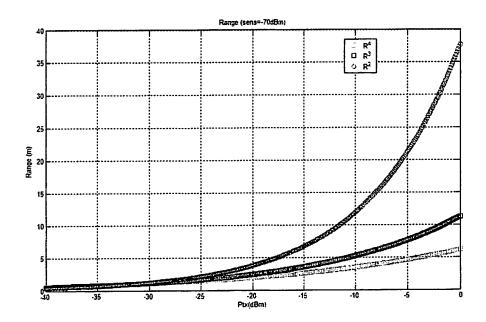

### 1.4.4 Sensitivity

Figure 1.2 plots the theoretical range for a radio with a -70dBm sensitivity for various RF propagation models at 2GHz. As shown, the range varies greatly depending on the radio environment. For free space (where the path loss exponent r=2), a range of 37m is achieved with a 0dBm transmit power. However, in indoor environments, a higher exponent (r=3 or r=4) is more appropriate. In that regime, a transmit power of at least 0dBm is required for a 10m range. To add a margin for deep fading, the receiver sensitivity for a 0dBm transmit signal and a 10m range should be greater than -75dBm. Thus, for this application, a receiver sensitivity of better than -75dBm is imposed. Higher sensitivities will allow lower transmitted power levels, subject to the constraints in the previous section.

Figure 1.2: Radio range for receiver with a -70dBm sensitivity

#### 1.4.5 Turn-On Time

In an environment in which the radio is in idle or off mode most of the time, and in which data communications are rare and packets short, it is essential that the radio start up very quickly. For instance, a typical 1Mbps Bluetooth-specification radio with a  $500\mu$ s turn-on time would be poorly suited for the transmission of short packets. The on-time to send a 200 bit packet would be only  $200\mu$ s. Start-up and acquisition represent an overhead that is larger than the actual payload cost, and could easily dominate the power budget (given that channel acquisition is typically the most power-

hungry operation). Thus, fast start-up and acquisition is essential to minimize this overhead. An agile radio architecture that allows for quick and efficient channel acquisition and synchronization is desirable. Complex wireless transceivers tend to use sophisticated algorithms such as interference cancellation and large constellation modulation schemes to improve bandwidth efficiency. These techniques translate into complex and lengthy synchronization procedures and may require accurate channel estimations. Packets are spaced almost seconds apart, which is beyond the coherence time of the channel. This means that these procedures have to be repeated for every packet, resulting in major overhead unsuitable in a low-power environment. Simple modulation and communication schemes are hence the desirable solution if agility is a prime requirement.

## 1.4.6 Integration/Power Tradeoff

Achieving the goal of a very low power/low cost RF design is complicated by a well documented power/integration (cost) tradeoff. For example, the use of high performance SiGe processes, while offering the designer high  $f_T$  operation and low bias current levels, eliminates the possibility of integration with low power digital systems. A multi-chip solution would prohibitively increase the cost and area for sensor network applications. Another common strategy for CMOS RF designers trying to reduce power consumption is to use high quality passive surface mount components [6]. This solution also prohibitively increases cost and board area, as each surface mount inductor

is larger than the entire transceiver chip.

Recently published "fully integrated" transceivers typically refer to a transceiver that has simply eliminated the need for external ceramic or surface acoustic wave (SAW) filters. They still, however, require an off-chip quartz crystal and various passive components. To meet the cost and formfactor requirements of this application, a truly fully integrated transceiver is mandatory. In addition to increasing the size, off-chip passives add to the complexity and cost of the board manufacturing and package design. In addition, these macro-fabricated components increase the manufactured performance distributions of the radio by adding completely uncorrelated component variations. One method that can be used to achieve a high level of integration is the use of a relatively high carrier frequency. Currently available simple low power radios, as used in control applications, typically operate at low carrier frequencies between 100 and 800MHz. A high carrier frequency has the distinct advantage of reducing the required values of the passive components, making integration easier. For example, a  $2.53\mu\mathrm{H}$ inductance is needed to tune out a 1pF capacitor in a narrow-band system at 100MHz, requiring a surface mount inductor. For a 2GHz carrier frequency, the inductance needed is only 6.33nH, which can easily be integrated on-chip using interconnect metallization layers. In addition, the critical antenna physical dimensions are linearly related to the carrier frequency. For a given antenna radiation pattern and efficiency, a higher carrier frequency allows for a much smaller antenna. A quarter-wavelength monopole antenna at 100MHz would be 0.75m long. At 2GHz, the size shrinks to 37.5mm, allowing very efficient and inexpensive board-trace antennae. However, the drive to higher carrier frequencies in the interest of high integration is in direct conflict with the need for low power consumption. As the carrier frequency increases, the active devices in the RF signal path must be biased at higher cutoff frequencies, increasing the bias current and decreasing the transconductance-to-current  $\frac{g_m}{I_d}$  ratio. The results is an increased power dissipation at higher carrier frequencies. Thus, there exists an inherent tradeoff between integration and power consumption that must be addressed through architectural decisions and the use of new technologies.

To reduce the die area and cost of the transceiver, the entire physical layer must be taken into account. For example, a simple, low power frontend with a large, power hungry A/D and complex digital baseband would be counterproductive. Thus, modulation schemes, datarates, and packet sizes that reduce baseband complexity must be embraced to optimize the global power consumption.

In conclusion, RF transceivers for wireless sensor networks must be simple, consume a minimum amount of on-current, and operate at high carrier frequencies to allow high levels of integration. In the next section, the current state-of-the-art in low power RF transceivers is discussed.

### 1.5 State-of-the-art

There has been substantial work in the field of low power transceivers for wireless sensing. Much of this work has focused on scaling down the power and datarate of traditional transceiver architectures for use in wireless sensing applications. As a case study, a two recent architectures reported in [7] and [8] will be discussed.

The first case study, reported by Peiris [7], achieves impressive sensitivity performance and low power consumption, truly representing the state-of-the-art in heterodyne transceivers for sensor networks.

The receiver, which can utilize either OOK or FSK modulation, was implemented in a 0.18 $\mu$ m CMOS process. Integration of a the transceiver, A/D converters, RISC microcontroller core and an SRAM block were achieved on the same chip. The receiver consumed 2.1mA from a 1V supply with a high sensitivity of -111dBm and -108dBm in the 433MHz and 868MHz band, respectively. The low current consumption is possible due to the relatively low carrier frequency used. External high Q inductors in the VCO tank reduce the power consumption and improve the phase-noise of the synthesizer block. The VCO phase noise was measured as -110  $\frac{dBc}{Hz}$  at 600kHz offset. The low carrier frequency prohibits the full integration of the VCO and LNA matching inductors, necessitating off-chip components. The antenna form-factor would also suffer from the relatively low carrier frequencies.

The second case study, reported by Molnar [8], uses an FSK modulation

scheme with a 900MHz carrier frequency. The transceiver operated from a 3V supply and dissipated 1.2mW for a sensitivity of -93dBm. A low-IF architecture was used. The transceiver made use of the relatively large supply voltage to share bias current between the LNA and the local oscillator. To reduce the power consumption, an off-chip high Q inductor was used for the VCO.

This work demonstrates that, although low power consumption and good sensitivity performances are possible using traditional architectures, complete integration remains elusive. An integration/power tradeoff is observed: as carrier frequencies are lowered to reduce the power consumption, passive components become more difficult to integrate and the antenna grows. In addition, a quartz crystal reference is still needed for the synthesizer. Thus, to achieve sub-mW receive power consumptions and full integration, new techniques must be explored.

# 1.6 Contributions of this Thesis

The following Chapters generally explore the following two main areas:

CMOS/MEMS Co-Design: Techniques for designing new MEMS

technology with sub-micron CMOS circuitry are introduced. Many

design examples are presented, including RF local oscillators, RF amplifiers, and low frequency reference clocks. Both low frequency electrostatic silicon resonators and high frequency bulk-acoustic wave res-

onators are covered. The increasing  $f_T$  of sub-micron CMOS processes is leveraged by using weak inversion biasing in all circuit blocks, from DC to 2GHz.

2. Ultra-Low Power, Highly Integrated Radio Design: Techniques and philosophies increasing the level of integration and decreasing the power consumption of CMOS transceivers beyond the current state-of-the-art are presented. A RF transmit beacon operating purely from scavenged energy is presented. Two fully functional receivers have been designed, implemented, and tested to validate these concepts. The first, a two-channel tuned radio frequency (TRF) architecture, demonstrates passive channel selection using MEMS resonators and is scalable to multiple channels. The second, using a super-regenerative architecture, achieves extremely low power dissipation (400μW) by using a MEMS resonator to set the RF frequency.

Chapter 2 outlines the design philosophies used in this research, such as MEMS/CMOS co-design and weak-inversion RF circuit design, and energy scavenging. To verify these philosophies, three proof-of-concept designs are presented: two RF circuit blocks and one system implementation. Advanced CMOS/RF MEMS circuit co-design research included the analysis, design, and implementation of a fully differential oscillator. Section 2.4 describes the circuit and compares the testing results to a single ended version with the same power consumption. To demonstrate the potential for energy scaven-

ing, a 2GHz transmit beacon operating indefinitely on scavenged energy is discussed.

Based on these concepts, a fully functional two-channel transceiver was designed, implemented, and tested. Chapter 3 fully documents this effort from the initial analysis phase through the testing methodology.

To further reduce power consumption, a super-regenerative radio architecture was investigated. A fully functional, prototype  $400\mu$ W receiver was demonstrated. Chapter 4 presents the theory behind the receiver operation. The circuit design, implementation, and subsequent receiver testing results are revealed.

Chapter 5 describes a fully-integrated transceiver based on the super-regenerative radio. The pulse-width demodulator synthesis, analysis, and circuit design is described. In addition, a digitally programmable interface is implemented, which allows control over the receiver biasing, super-regenerative RF frequency, and the transmitter output tank frequency.

Chapter 6 describes an efficient and robust integration methodology for the transceiver. To address an important bottleneck in the implementation of wireless sensor networks, a proof-of-concept CMOS/MEMS 16MHz reference clock with amplitude control loop was designed and implemented. Section 6.1 provides a brief background into micromachined silicon resonators before describing the circuit design. Robust packaging techniques of the MEMS and CMOS components are then discussed. Performing a flip-chip of the MEMS chips directly onto the CMOS chips provides a low parasitic, low form-factor

#### 1.6 Contributions of this Thesis

system that saves both die and board area. Two proof-of-concept examples are provided.

Finally, Chapter 7 concludes the thesis with a summary and a discussion of directions for future work.

## Chapter 2

# Low Power CMOS Design for Radio Frequencies

In Chapter 1, an integration/power tradeoff was identified as one main obstacle to the implementation of small, cheap, low power transceivers for wireless sensor networks. This chapter describes the circuit design philosophies that have been developed to address these tradeoffs.

An important metric for RF blocks is the transconductance, which typically determines the total current consumption of the circuit. This chapter begins with a discussion of weak inversion circuit design, which is an increasingly relevant way of achieving efficient transconductance and is becoming more feasible with each technology node. Next, combining MEMS components with CMOS circuitry is shown to greatly reduce the reliance on external passive components. Three proof-of-concept chips are discussed to demonstrate the validity of these design strategies:

1. Circuit Proof-of-Concept I: 300μW Pierce BAW-Oscillator

- 2. Circuit Proof-of-Concept II: Differential 300μW BAW-Based Oscillator

- 3. System Proof-of-Concept: Energy Scavenging Transmit Beacon

We now turn to a discussion of weak inversion CMOS for Radio Frequencies.

#### 2.1 Weak Inversion RF CMOS

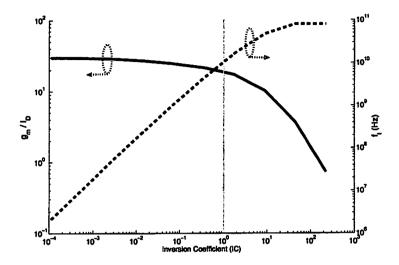

As technology scaling relentlessly provides increasing digital clock frequencies, the effects on analog/RF circuit design continue to accumulate. Aggressive supply voltage scaling impedes the implementation of high dynamic range A/D converters and other precision analog circuitry. However, the increasing thickness and reduced resistivity of the copper metallization, coupled with the increased distance to the lossy substrate, allows the fabrication of high quality inductors and transmission lines. Subthreshold circuit design has been identified as a powerful tool in reducing the power consumption of the transceiver. Weak inversion circuit biasing has been used for years in low frequency analog circuit design [9] to achieve increased transconductance efficiency. However, increasing transistor  $f_T$ s allows weak-inversion operation in some RF circuit blocks. The inversion coefficient (IC) describes the relative level of channel inversion, which is most easily determined by the device current density. As the current density decreases, the transconductance efficiency increases. Equation 2.1 shows the inversion coefficient as a function

Figure 2.1: The transconductance efficiency is plotted vs. the inversion coefficient

of the transistor process parameters and operating point.

$$IC = \frac{I_d}{2nk'\frac{W}{L}V_t^2} = \frac{I_d}{I_o S}$$

(2.1)

Where n is the subthreshold slope factor,  $k' = \mu C_{ox}$ ,  $V_t = \frac{KT}{q}$ ,  $I_o$  is the specific device current, and S is the transistor aspect ratio. See Figure 2.1 for the transconductance efficiency vs. the inversion coefficient (IC) for a commonly used  $0.13\mu m$  process [10].

The plot clearly shows the increase in transconductance efficiency as the inversion coefficient decreases. The line at IC=1 is considered the middle of moderate inversion. Since the performance of many RF circuit blocks is directly related to device transconductance, it is advantageous to maximize

the transconductance efficiency of all critical devices in order to reduce the necessary bias current. However, reducing the current density also results in a severely decreased device  $f_T$ . An optimization of the current density is required to provide the correct balance between transconductance efficiency and bandwidth. Plots such as Figure 2.1 are useful tools for designers when choosing appropriate transistor bias points. Technology scaling allows greatly increased  $f_T$  realization for a given IC. Thus, weak inversion biasing for RF design will become increasingly useful in future technology nodes.

Throughout this work, the IC of critical transistors will be discussed. Most of the RF devices are biased in moderate to weak inversion to achieve enhanced transconductance efficiency and reduced bias current.

### 2.2 MEMS Background

The relatively new field of Radio Frequency Microelectro Mechanical Systems (RF MEMS) provides unique opportunities for RF transceiver designers. This section provides background on RF MEMS and provides insight into the opportunities presented by these new technologies. The field of RF MEMS includes the design and utilization of RF filters, resonators, switches, and other passive mechanical structures constructed using bulk processed integrated circuit fabrication techniques. To date, these devices have been commercially used as discrete board-mounted components, primarily used to enhance the miniaturization of mobile phones. However, RF MEMS com-

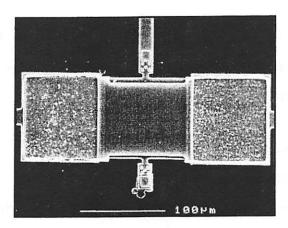

Figure 2.2: 50MHz Capacitively Driven/Sensed Resonator

ponents have the potential to be batch fabricated using existing integrated circuit fabrication techniques. Recent capacitively driven and sensed structures offer the potential of integration on the same substrate as the CMOS circuitry. In addition, because the resonant frequency of the structure is set lithographically, rather than by a deposition layer thickness, it is possible to fabricate devices with many unique resonant frequencies on the same die. See Figure 2.2 for an example of this technology. This resonator was constructed of micromachined polysilicon on a silicon wafer [11]. The continued improvement in the performance, reliability, and manufacturability of these structures will greatly change the performance and form-factor of RF transceivers by allowing the reliable fabrication of advanced mechanical structures on the same substrate as the circuitry. However, as will be shown in this chapter, these devices hold the potential to enable new circuit blocks and architectures even in their present state as off-chip components.

At the onset of this project, RF MEMS was identified as an emerging technology with the potential to benefit low power RF transceivers. These devices provide three main benefits to circuit designers:

High quality factor (Q) resonant structure. BAW resonators can achieve quality factors greater than 1000, about 100X higher than onchip LC resonators. The resulting increased RF filtering ability both reduces oscillator phase noise and reduces frequency pulling/pushing of oscillators.

When used in the design of bandpass filters and duplexers, high Q resonators help to realize the steep skirts necessary to meet cell phone specifications [12]. High Q resonators are further useful in a variety of other transceiver blocks. For example, high Q resonators provide the potential for radio frequency channel select filtering, as their bandwidth is much narrower than what can be obtained from integrated LC filters. This passive channel select filtering can be exploited to simplify the receiver architecture and to reduce the number of active components. In addition, when used in an RF oscillator, RF MEMS resonators provide a vastly improved phase noise compared to a standard, low Q LC resonator [13].

2. Passive RF frequency reference. For all narrowband communication systems, an RF carrier frequency generator is necessary. The absolute frequency reference used is typically a low frequency quartz

crystal oscillator. The low frequency sinusoid is then multiplied up to radio frequencies by a frequency synthesizer. This technique has a few disadvantages for low power radio design. First, even for a fully integrated frequency synthesizer, an off-chip quartz crystal is always necessary, rendering true full integration impossible. In addition, frequency synthesizers are a large source of power dissipation in low power radios [6]. The VCO and frequency dividers tend to dominate the power consumption of frequency synthesizers. Radio frequency MEMS components provide an inherent high-frequency reference without the need for a power hungry frequency synthesizer.

3. CMOS/MEMS co-design. Since MEMS structures are fabricated using the same thin-film fabrication techniques as integrated circuits, each device may be custom-designed for its intended application. This provides additional degrees-of-freedom to the circuit designer. Unlike quartz crystals or discrete 50Ω filters, this flexibility allows the circuit designer to control impedance levels for minimal power consumption. One of the most exciting aspects of RF micromachined components is the potential for co-designing the MEMS devices with the CMOS circuitry. Until now, passive components are either low quality on-chip devices (inductors, capacitors) or high quality off-chip components (inductors, SAW filters, quartz crystals, duplexers). The on-chip components allow customization to meet the requirements of the circuitry, but their performance is usually poor. Meanwhile, high quality off-chip

passives offer few designer degrees of freedom. For example, most filters and duplexers are designed for  $50\Omega$  input and output impedances. This rigid impedance level is very detrimental from a low power point of view, and has been extremely troublesome in past receiver implementations [14]. The potential of integrating RF MEMS components and circuitry on the same die or on the same substrate using, for instance, fluidic self assembly (FSA) could allow the circuit designer to size the MEMS components and the circuitry simultaneously [15]. The ability to design these devices alongside the circuitry provides increased system performance and additional designer degrees of freedom.

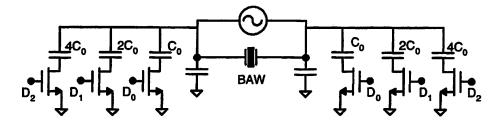

Currently, many industrial (Infineon, ST Microelectronics, Agilent) and academic (University of Michigan, U.C. Berkeley) organizations have begun development of RF MEMS resonators. One promising technology is the Bulk Acoustic Wave (BAW, FBAR) piezoelectric resonator [16]. The FBAR employs a metal-piezo-metal sandwich to achieve a high frequency, tightly controlled second order resonance with an unloaded Q of approximately 1200. As shown in Figure 2.3, the resonator can be modeled as a series LCR circuit, with a series resonance occurring at  $f_s = \frac{1}{\sqrt{L_x C_x}}$  or approximately 1.9GHz in this design. Capacitor  $C_o$  represents a parasitic feedthrough capacitance created by the parallel plates of the resonator.  $R_o$  models the finite quality factor of the feedthrough capacitance.  $Z_s$  and  $Z_p$  represent the loading effects of the CMOS circuitry on the resonator. These external impedances have a large effect on the resonator quality factor, resonant frequency, and

Figure 2.3: Simplified circuit equivalent model of a BAW resonator.

frequency stability. In current applications, FBARs are combined into ladder structures and used as duplexers and bandpass filters for wireless applications [16]. Used in this manner, a much smaller form factor is achieved over traditional RF duplexers and filters. For low power transceivers, it is desirable to use single resonators to achieve a high quality factor and very narrow bandwidth. Referring to Figure 2.3, it is possible to distinguish two different resonant modes. The first, occurring at the series resonance, allows a low impedance path through the resonator at RF frequencies. At the series resonance, the effective series impedance is approximately  $R_x$ . Above the series resonance, the structure looks inductive and will naturally tune out any parallel capacitive elements. This produces the parallel resonance, which occurs approximately 20MHz above the series resonance. At the parallel resonance, there is a circulation of RF current through the resonator and the feedthrough capacitor  $C_0$ . Due to this current circulation, at the parallel resonance the impedance of the structure increases dramatically to a

value approximately 3 orders of magnitude higher than the series resonance. To avoid detuning the resonator in the series resonant mode, the impedance added to the resonator by the electronics  $(Z_s)$  must be small compared to  $R_x$ , or a few ohms. This is typically not possible using low power RF design techniques, where high impedances are necessary to reduce the current consumption. To avoid detuning the parallel resonant mode, the shunting impedance presented by the electronics  $(Z_p)$  must be much higher than the resonator impedance at parallel resonance (approximately  $2k\Omega$ ). Thus, for low power RF transceiver design, it is desirable to operate on the parallel resonance of the resonator [17]. It should be noted, however, that the intrinsic quality factor of the series resonance will be higher than the parallel resonance due to the additional resistive losses of the circulating RF current.

The frequency stability of high Q resonators is a key feature that provides much more reliable operation that other LC-based frequency generators. Equation 2.2 shows the sensitivity of the parallel resonance<sup>1</sup> to capacitive variation.

$$\frac{\delta f_p}{\delta C_T} \simeq f_{series} \frac{-C_x}{2C_T^2} \tag{2.2}$$

$C_T$  describes the total capacitive loading on the resonator This equation corresponds to a sensitivity of approximately -10kHz/fF of frequency variation due to process, temperature, or non-linear capacitor bias point shift. Equa-

<sup>&</sup>lt;sup>1</sup>And thus the subsequent oscillation frequency.

tion 2.3 shows the frequency sensitivity of an LC tank to capacitive variation.

$$\frac{\delta f}{\delta C_T} = \frac{-C^{-3/2}}{4\pi\sqrt{L}} \tag{2.3}$$

For a tank defined by a 5nH inductance at 2GHz, a typical value for a fully-integrated oscillator, the frequency sensitivity is -856kHz/fF, nearly two orders of magnitude higher than the BAW resonator. Thus, an LC resonance would always need to be frequency locked to a reference even if perfect frequency accuracy were possible. In contrast, a BAW resonator, if sufficient accuracy were available, would not need to be frequency locked. This is a fundamental benefit of using high Q MEMS resonators in low power transceivers.

# 2.3 Circuit Proof-of-Concept I: $300 \mu W$ Pierce Oscillator

To demonstrate the concepts presented in Sections 2.2 and 2.1, a proof-of-concept circuit was designed, implemented, and measured in a  $0.18\mu m$  standard CMOS process [13] [17]. The goals of this project were threefold:

A proof-of-concept circuit would verify the resonator/CMOS models and the co-design methodology. This verification is necessary as the accuracy of the models for MEMS components and weak inversion CMOS at RF frequencies are not as heavily developed as the traditional models for strong inversion CMOS circuitry, which designers have become accustomed to.

- A prototype would allow the refinement of the unresolved resonator/CMOS packaging and interconnect problem.

- This circuit, when used as a local oscillator, would also provide a stepping-stone to the implementation of an entire low power transceiver.

This section describes the state-of-the-art in transceiver local oscillator design. Used to generate the transmitted carrier frequency and the local oscillator (LO) signal, a stable, low-noise RF sinusoid generator is crucial for the performance of an RF link. Traditionally, this signal is obtained through frequency synthesis, which entails multiplying the frequency of a stable low frequency crystal oscillator via a phase- or delay-locked loop (PLL or DLL) [18]. There are, however, serious drawbacks with a frequency synthesizer. First, due to the low Q of the voltage controlled oscillator (VCO) tank and finite loop bandwidth of the PLL, the phase noise of the crystal oscillator is severely degraded by the frequency synthesizer. Secondly, the synthesizer consumes large amounts of power in the VCO and frequency dividers.

A few examples are useful for putting the problem in perspective. In a recent ultra low power frequency synthesizer design, approximately  $400\mu$ W was consumed to provide a 434MHz carrier [6]. As the carrier frequency of these systems is increased into the GHz range, the power consumption of

the frequency synthesizer increases dramatically. Outstanding phase noise performance can be achieved at the expense of high power dissipation. A recent high-performance 900MHz frequency synthesizer consumed 130mW with a phase noise of  $-127\frac{dBc}{Hz}$  at a 330kHz offset [18]. The start-up time of a traditional frequency synthesizer is relatively long, and can be very inefficient if the transceiver requires agile duty-cycling and short packet transmission. Additionally, even with a "fully integrated" synthesizer, an off-chip quartz crystal is always required. Crystal oscillators typically exhibit very low phase noise due to the high quality factor of the crystal resonator. However, the resonant frequencies of quartz crystals are lower than most desired carrier frequencies, so frequency synthesis is usually required. A recent crystal oscillator implementation reports a phase noise of  $-113\frac{dBc}{Hz}$  at 300Hz offset for a 78MHz oscillation frequency with a power dissipation of  $340\mu$ W [19] .

Another option is to use an integrated free-running LC-oscillator without a frequency reference. This could satisfy the need for a fast start-up time and low power dissipation, but the frequency variation and phase noise of such a design would be prohibitively poor. In [13], we presented an alternate method of sinusoid generation. A frequency reference is generated directly at the RF frequency of interest, with no low frequency reference. This is accomplished by placing a BAW resonator in the feedback path of a CMOS oscillator, ultimately combining the frequency stability of a mechanical resonance with the low power capability of standard submicron CMOS. The technique of co-designing the resonator with the CMOS electronics provides an extremely

Figure 2.4: Simplified oscillator schematic

low power solution.

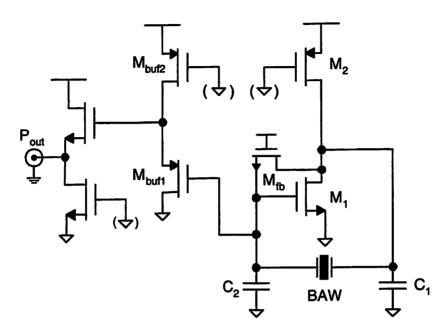

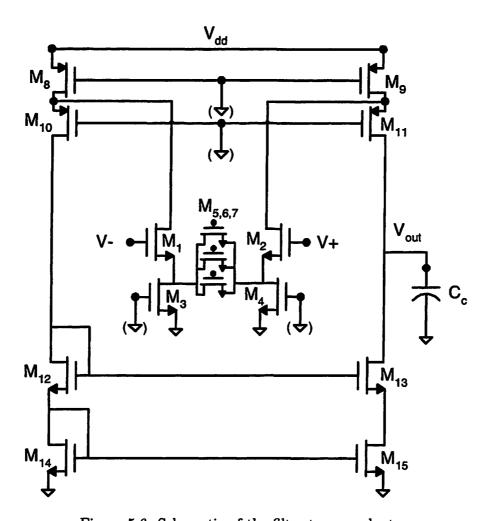

In this design, a single resonator is used to maximize the loaded Q of the oscillator. The impedance of the resonator is less than  $5\Omega$  at series resonance and larger than 1500 ohms at parallel resonance. Thus, to avoid severely loading the natural Q of the resonator, operation at the parallel resonance of the FBAR was chosen. The resonator occupies an area of approximately  $100\mu m \times 100\mu m$  and is wire-bonded directly to the CMOS chip containing the circuitry. The Pierce oscillator topology was chosen for its low phase noise potential and because it operates on the parallel resonance of the FBAR, allowing a higher loaded Q. A circuit schematic of the oscillator is shown in Figure 2.4. The signal is DC coupled to the first stage of the output buffer

$(M_{buf1})$ . Capacitors  $C_1$  and  $C_2$  represent the device, interconnect, and pad capacitances. Accurate modeling and prediction of these values is crucial for the high frequency implementation of this topology. Transistor  $M_{fb}$  acts as a large resistor to provide bias to  $M_1$ . At the parallel resonance of the resonator,  $C_1$ ,  $C_2$ , and  $C_o$  are tuned out.  $M_1$  sees a high impedance at its drain node, allowing oscillation at this frequency. The sizing and layout of the circuit and resonator was optimized to minimize the power consumption of the oscillator.

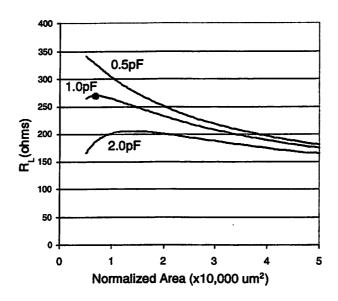

At resonance, the initial loop gain is  $A_L = g_{m1} R_L \frac{C_1}{C_2}$  where  $R_L$  is the real impedance seen at the drain of  $M_1$  at the parallel resonance of the resonator. It can be shown that the optimal frequency stability and start-up factor are achieved with  $C_1=C_2$  [20]. Therefore, to minimize the transconductance necessary for oscillation and to maximize the output voltage swing for a given bias current,  $R_L$  was maximized. For a given frequency, BAW resonators may be designed with various membrane areas. As the area increases, the motional resistance  $(R_x)$  decreases. However, increasing the area also increases the feedthrough capacitance  $C_o$ . Increasing  $R_x$  degrades the loaded Q of the oscillator, thus decreasing  $R_L$ . Increasing  $C_o$  has a similarly detrimental effect. Thus, it is possible to calculate an optimal resonator area that minimizes the power dissipation and phase noise of the oscillator. Figure 2.5 plots  $R_L$  vs. the normalized resonator area for various values of  $C_1=C_2$ . Using this technique, an optimal resonator area of approximately  $(100 \times 100) \mu m^2$  was chosen for fabrication. The curve marker in Figure 2.5

Figure 2.5: Optimization of BAW resonator area. Three curves are shown with various values of  $\mathcal{C}_1=\mathcal{C}_2$

indicates the design point. It is important to note that the finite Q of the CMOS device and pad capacitance must be taken into account, as they also reduce the loaded Q of the oscillator. This optimization led to a maximized value of  $R_L$  at parallel resonance. The desired voltage swing of the oscillator was 100mV zero-peak. The equation  $V_0 = I_1 R_L$  relates the desired voltage swing to the first harmonic component of the drain current of  $M_1$ . Thus, since the oscillator is operated in the current-limited regime, the necessary oscillator core bias current is  $300\mu A$ . As discussed in Section 2.1, weak inversion operation provides higher transconductance efficiency  $(\frac{g_m}{I_d})$ . The sizing of transistor  $M_1$  (500/0.18) $\mu$ m was chosen as to provide subthreshold operation, ensuring sufficient initial transconductance for reliable start-up. For transistor  $M_1$ , IC = 0.2, yielding  $\frac{g_m}{I_d} = 23$ .

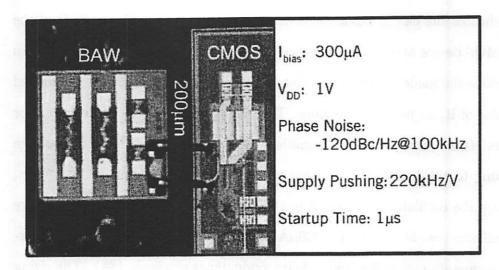

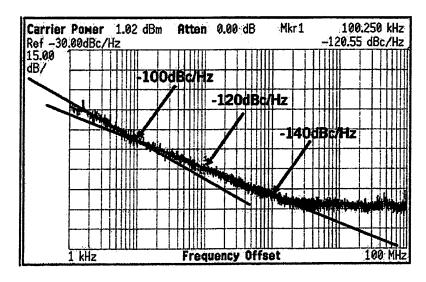

A symmetric resonator layout allowed equal loading on the drive and sense electrode. The resonator was wirebonded directly to the CMOS chip to eliminate board parasitics, which would drastically degrade the resonator response. To accomplish this, the CMOS and BAW pad layouts were constructed with equal spacing so the chips could be mounted in close proximity to each other and directly wirebonded. See Figure 2.6 for a photograph of the completed prototype. The two chips were bonded with conductive epoxy to a grounded substrate, resulting in A  $200\mu$ m spacing between the chips. A custom assembly with two bondwires per interconnect was used in the initial prototype to reduce the bondwire inductance, but subsequent experimentation showed that standard chip-on-board (COB) assembly using one

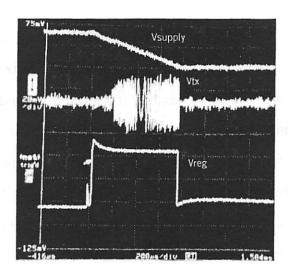

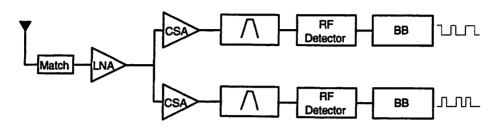

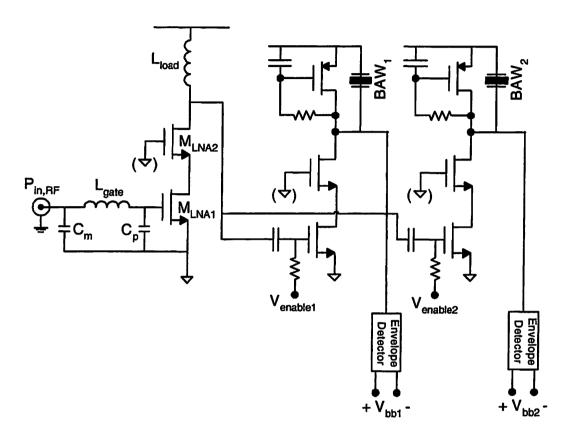

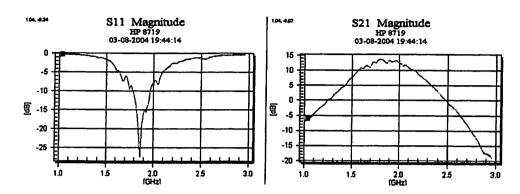

Figure 2.6: Photograph of the CMOS/BAW prototype oscillator