## Modularly Integrated MEMS Technology

Marie-Ange Naida Eyoum

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2006-78 http://www.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-78.html

May 23, 2006

Copyright © 2006, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

Acknowledgement

Tsu-Jae King, Roger T. Howe, Sanjay Govingjee, Nils Hoivik, Chris Jahnes, John Cotte, UC Berkeley Microfabrication Laboratory, Darpa Funding.

# MODULARLY INTEGRATED MEMS TECHNOLOGY

By

Marie-Ange Naida Eyoum

B.S. (Virginia Union University) May 2001 M.S. (University of California, Berkeley) May 2003

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

### Engineering-Electrical Engineering and Computer Sciences

in the

### GRADUATE DIVISION

of the

### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in Charge Tsu-Jae King, Chair Roger T. Howe Sanjay Govindjee

Spring 2006

# MODULARLY INTEGRATED MEMS TECHNOLOGY

By

Marie-Ange Naida Eyoum

BS, Virginia Union University, May 2001 M.S. University of California at Berkeley, May 2003 Ph.D. University of California at Berkeley, May 2006

Submitted in partial satisfaction of the requirements for the degree of Doctorate of Philosophy

Department of Electrical Engineering and Computer Sciences College of Engineering University of California, Berkeley

> Committee in Charge Tsu-Jae King (Chair) Roger T. Howe (Co-chair) Sanjay Govindjee (Outside member)

> > Spring 2006

University of California, Berkeley Spring 2006

# **Modularly Integrated MEMS Technology**

**Copyright 2006**

By

Marie-Ange Naida Eyoum

### Abstract

#### Modularly Integrated MEMS Technology

By

Marie-Ange Naida Eyoum Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences University of California,Berkeley Professor Tsu-Jae King, Chair

Process design, development and integration to fabricate reliable MEMS devices on top of VLSI-CMOS electronics without damaging the underlying circuitry have been investigated throughout this dissertation. Experimental and theoretical results that utilize two "Post-CMOS" integration approaches will be presented.

The first integration approach uses SiGe MEMS technology for the "Post-CMOS" monolithic integration of the MEMS devices with electronics. Interconnects between SiGe MEMS and Al-TiN metallized layers have been characterized and optimized. A thorough study on Boron doping and Ge content effects on the electrical, mechanical, and chemical properties of SiGe MEMS technology has been performed. Two CMOS-compatible micromachining fabrication procedures have been developed for RF and inertial sensing MEMS applications. First, a process flow that uses Ge ashing technique to define nanogaps in SiGe electrostatic MEMS transceivers for wireless communication applications has been demonstrated. Second, a multilayer SiGe MEMS process flow has been implemented for the fabrication of a freely moving disk used to pave the way towards an integrated electrostatically levitated disk sensor system for low loss inertial sensing applications. The sensor system is comprised of a disk-shaped proof-mass that is

to be electrostatically suspended between sense and drive electrodes located above, below, and at the sides of the disk.

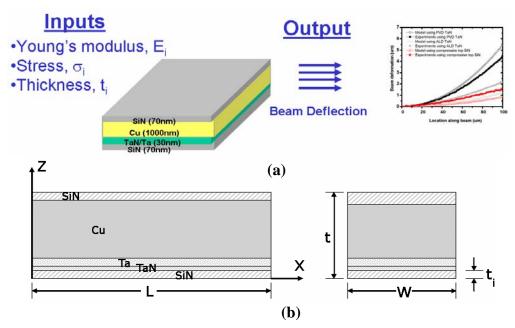

The second "Post-CMOS" integration employs the state-of-art "back-end" materials already available in the integrated circuitry to fabricate the MEMS devices. Copper-based MEMS technology is used for the fabrication of low loss RF MEMS switches directly on top of the electronics. A model accounting for multilayer cantilever beam deflection suitable for MEMS devices fabricated with conventional "back-end" materials was derived. Experimental results characterizing stress gradients in copper-based RF MEMS switches will be presented. The effect of Physical Vapor Deposition (PVD), Atomic Layer Deposition (ALD) deposited TaN films, and compressive SiN films on beam deformation have been studied, as well as the effect of annealing on the reliability properties of the RF MEMS switches.

Professor Tsu-Jae King, Dissertation Committee Chair To my mother

"Thanks for everything you've poured into my life!"

"I have learnt in life that success should not be defined by the position that someone holds; rather, it should be measured through all the obstacles that one has overcome while trying to succeed"

### **Booker T. Washington**

# **Table of contents**

| Acknowledgements | vi   |

|------------------|------|

| List of Figures  | xi   |

| List of Tables   | xvii |

## **Chapter 1: Introduction**

| 1.1. Integration of MEMS with Electronics                               | 1   |

|-------------------------------------------------------------------------|-----|

| 1.1.1. What are MEMS?                                                   | 1   |

| <b>1.1.2.</b> The need for a monolithic modularly integrated technology | 2   |

| 1.2. Different modular integration approaches                           | 3   |

| 1.3. Poly SiGe, a low temperature mechanical material                   | 7   |

| 1.3.1. Summary of SiGe for VLSI-CMOS applications                       | 7   |

| 1.3.2. Summary of SiGe MEMS research                                    | 8   |

| 1.3.3. Properties of poly-Si <sub>1-x</sub> Ge <sub>x</sub>             | 10  |

| 1.2.4. Deposition of poly-Si <sub>1-x</sub> Ge <sub>x</sub>             | .12 |

| 1.3.5. Etching of poly-Si <sub>1-x</sub> Ge <sub>x</sub>                | 12  |

| 1.4. Dissertation overview                                              | 14  |

| References                                                              | 16  |

## Chapter 2: Low Contact Resistance Si<sub>1-x</sub>Ge<sub>x</sub> MEMS Technology

| 2.1. Motivation                                                         | 21 |

|-------------------------------------------------------------------------|----|

| 2.2. Fabrication process flow                                           |    |

| 2.2.1: Test Structures                                                  |    |

| 2.2.2. Cleaning issues for metallized wafers                            | 24 |

| 2.2.3. Deposition of p+ poly-Si <sub>1-x</sub> Ge <sub>x</sub> films    | 24 |

| 2.3. Characterization of Si <sub>1-x</sub> Ge <sub>x</sub> films        | 26 |

| 2.3.1. Resistivity                                                      |    |

| 2.3.2. Ge concentration and film microstructure                         |    |

| 2.4. Contact resistance                                                 | 28 |

| 2.4.1. Pre-cleaning issues                                              |    |

| 2.4.1.1. Helium plasma pre-cleaning                                     | 29 |

| 2.4.1.2. Argon plasma pre-cleaning                                      |    |

| 2.4.1.3. Discussion                                                     | 32 |

| 2.4.2. Si <sub>1-x</sub> Ge <sub>x</sub> deposition temperature effects | 33 |

| 2.4.2.1. Contact measurements results                                   | 33 |

| 2.4.2.2. Discussion                                                     | 34 |

| 2.5. Germanosilicide process           | 35 |

|----------------------------------------|----|

| 2.5.1. Fabrication process flow        |    |

| 2.5.2. Contact measurement results     |    |

| 2.5.3. Discussion                      |    |

| 2.6. Annealing effects                 |    |

| 2.6.1. Thermal annealing               |    |

| 2.6.2. Excimer laser annealing         |    |

| 2.6.3. Discussion                      |    |

| 2.7. SiGe to SiGe contact resistance   |    |

| 2.7.1. Motivation                      | 40 |

| 2.7.2. Experiments                     |    |

| 2.7.3. Ge in-situ pre-cleaning process | 41 |

| 2.7.4. Contact measurement results     | 42 |

| 2.7.5. Discussion                      | 44 |

| 2.8. Summary                           | 46 |

| References                             |    |

## **Chapter 3: Boron Doping Effect on Structural Properties of Si<sub>1-x</sub>Ge<sub>x</sub> Films**

| 3.1. Introduction                                                                      | 49 |

|----------------------------------------------------------------------------------------|----|

| 3.2. Experimental details                                                              |    |

| 3.2.1. Processing of p+ poly-Ge sacrificial layer                                      |    |

| <b>3.2.2.</b> Processing of p+ poly-Si <sub>1-x</sub> Ge <sub>x</sub> structural layer |    |

| 3.3. Results                                                                           | 58 |

| 3.3.1. p+ Ge as a sacrificial material                                                 |    |

| 3.3.1.1. Processing parameters                                                         | 58 |

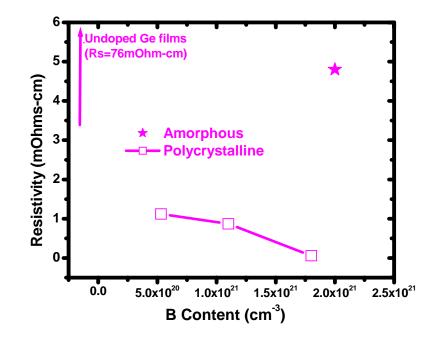

| 3.3.1.2. Surface roughness                                                             | 61 |

| 3.3.1.3. Film microstructure                                                           | 63 |

| <b>3.3.2.</b> p+ Si <sub>1-x</sub> Ge <sub>x</sub> structural material                 | 64 |

| 3.3.2.1. Electrical properties                                                         | 64 |

| 3.3.2.2. Mechanical properties                                                         | 65 |

| 3.3.2.3. Boron segregation at the grain boundaries                                     | 68 |

| 3.3.2.4. XRD results                                                                   |    |

| <b>3.3.3.</b> Codifusion between p+ Si <sub>1-x</sub> Ge <sub>x</sub> and p+ Ge        | 72 |

| <b>3.4. Summary</b>                                                                    | 75 |

| References                                                                             | 76 |

| <b>Chapter 4: Applications of Si<sub>1-x</sub>Ge<sub>x</sub> MEMS Technol</b>           | ogy |

|-----------------------------------------------------------------------------------------|-----|

| 4.1. Nanogap SiGe RF MEMS filter                                                        |     |

| 4.1.1. Introduction                                                                     | 79  |

| 4.1.2. Motivation of Ge blade process                                                   | 80  |

| 4.1.3. Short loop fabrication process details                                           |     |

| 4.1.4. Experimental results                                                             | 83  |

| 4.1.4.1. Polymer residues after DRIE of p+Ge films                                      | 83  |

| 4.1.4.2. Nanometer lateral gaps                                                         | 84  |

| 4.2. SiGe floating electromechanical systems (FLEMS)                                    | 85  |

| 4.2.1. Introduction                                                                     |     |

| 4.2.2. Benefits                                                                         | 86  |

| 4.2.3. Experimental Details                                                             | 87  |

| 4.2.3.1. Overview                                                                       | 87  |

| 4.2.3.2. Mask layout design                                                             | 88  |

| 4.2.3.3. Design considerations                                                          | 90  |

| 4.2.3.4. Device fabrication process                                                     | 91  |

| 4.2.3.5. Structural layer process module development                                    | 95  |

| 4.2.3.6. Definition of disk layer using bi-layer p+ Si <sub>1-x</sub> Ge <sub>x</sub> f |     |

| 4.2.3.7. Release process module development                                             |     |

| 4.2.4. Electrical Measurement                                                           | 108 |

| 4.2.4.1. Theory of electrostatic lift-off                                               |     |

| 4.2.4.2. Sensing of the disk                                                            | 109 |

| 4.3. Summary                                                                            | 111 |

| References                                                                              | 113 |

|                                                                                         |     |

## Chapter 5: RF MEMS Switches using Standard "Back-End-Of-Line" Materials

| 5.1. | Background                                     |     |

|------|------------------------------------------------|-----|

|      | 5.1.1. MEMS technology using standard "back-er |     |

|      | materials                                      |     |

|      | 5.1.2. Overview                                | 118 |

| 5.2. | Previous studies on multilayer modeling        | 120 |

| 5.3. | Development of theoretical model               | 121 |

|      | 5.3.1. Overview                                |     |

|      | 5.3.2. Modeling                                | 122 |

| 5.4. | Experimental details                           | 124 |

|      | 5.4.1. Fabrication of test structures          | 124 |

|      | 5.4.2. Residual stress characterization        | 125 |

|      |                                                |     |

| 5.5. | Results and Discussion                          |     |

|------|-------------------------------------------------|-----|

|      | 5.5.1. Theory compared to experiments           | 127 |

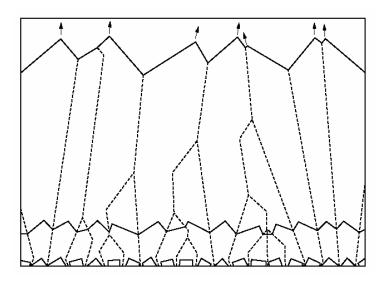

|      | 5.5.2. Thermal cycling of cantilever beams      | 128 |

|      | 5.5.3. Copper hysteretic behavior               | 130 |

|      | 5.5.3.1. Thermal cycling of the test structures |     |

|      | 5.5.3.2. Discussion                             |     |

| 5.6. | Optimization                                    | 133 |

|      | Summary                                         |     |

|      | rences                                          |     |

## **Chapter 6 Conclusions**

| 6.1. Summary of contributions                                                           | .139 |

|-----------------------------------------------------------------------------------------|------|

| 6.1.1. Interconnects between p+SiGe MEMS and Al-CMOS                                    | .139 |

| 6.1.2. Boron doping effect on structural SiGe MEMS technology                           | .140 |

| 6.1.3. SiGe MEMS applications                                                           | .141 |

| 6.1.4. Multilayer modeling of copper-based MEMS structures                              | .142 |

| 6.2. Recommendations for future work                                                    | .143 |

| 6.2.1. Reliability of Si <sub>1-x</sub> Ge <sub>x</sub> MEMS technology                 | .143 |

| 6.2.2. Thermal budget of the Si <sub>1-x</sub> Ge <sub>x</sub> Structural Layer         | .145 |

| 6.2.3. Packaging of Si <sub>1-x</sub> Ge <sub>x</sub> MEMS technology using porous Ge   | .146 |

| 6.2.4. Electrostatic levitation of Si <sub>1-x</sub> Ge <sub>x</sub> MEMS sensor system | .147 |

| References                                                                              | .148 |

# Appendices

| A. Process Parameters                                                                                        |

|--------------------------------------------------------------------------------------------------------------|

| A1. Processing parameters of $Si_{1-x}Ge_x$ films deposited using $B_2H_6$                                   |

| doping source149                                                                                             |

| A2. TEM cross section and deposition conditions of p+Ge amorphous                                            |

| layer149                                                                                                     |

| <b>B.</b> Spreading Resistance Profile (SRP) Results of Boron Content                                        |

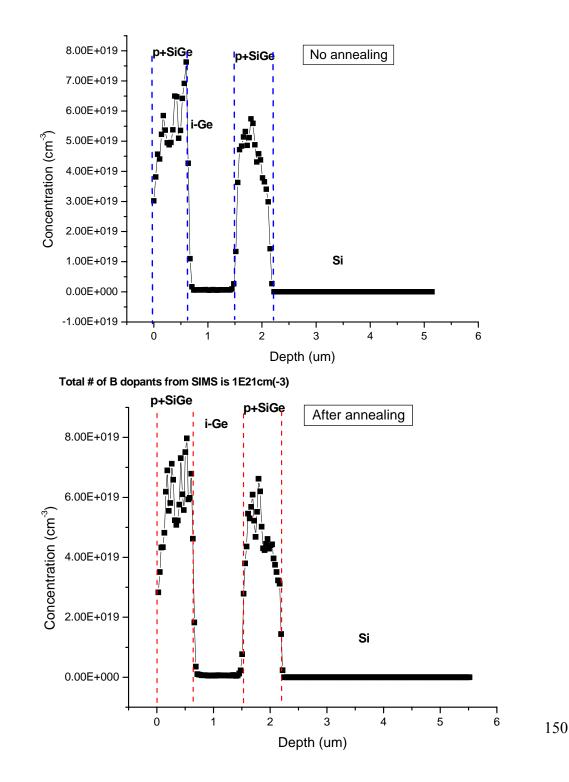

| B1. SRP data for p+Si <sub>1-x</sub> Ge <sub>x</sub> /i-Ge/p+Si <sub>1-x</sub> Ge <sub>x</sub> ) tri-layer   |

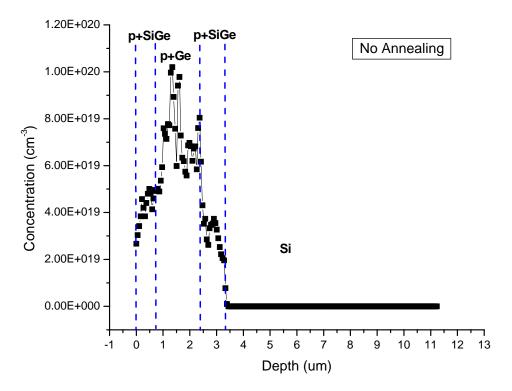

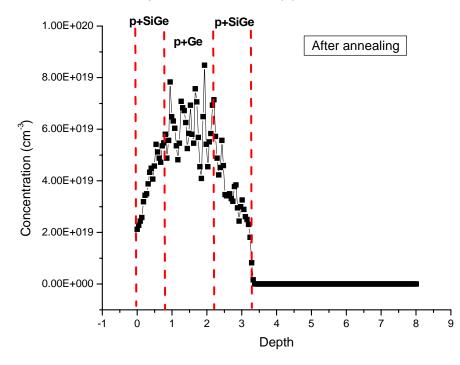

| B2. SRP data for p+Si <sub>1-x</sub> Ge <sub>x</sub> /p+Ge/p+Si <sub>1-x</sub> Ge <sub>x</sub> )tri-layer151 |

| C. FLEMS Fabrication Details                                                                                 |

| C1. Detailed fabrication process flow of the FLEMS devices152                                                |

| D. Programs                                                                                                  |

| D1. MATLAB code of copper-based multilayer beam model154                                                     |

## Acknowledgements

Getting a PhD from UC Berkeley EECS Department, one of the world's top research institutions is definitely a dream that has come true! Therefore above all, I am grateful to the Almighty God who has been my primer dream Giver as well as dream Fulfiller for guiding my paths till this day where I can finally edit the pages of this dissertation. In order to get to the end of my graduate research work, it certainly took a strong sense of perseverance and courage, as well as a deep attitude of serenity and faith whenever things didn't work the way I'd planned. For this, I have hundreds of people to thank, people who have invested in me as well as in my research, their technical advices, time, ideas, beliefs and consistent encouragements. I am filled with such a deep appreciation and I would like to take the necessary time to acknowledge all of them.

I first and foremost express my sincere, deep and profound gratitude to my research advisor Professor Tsu-Jae King who has been tremendously helpful throughout my graduate career at CAL. I am most grateful for all her technical advices in the scope of my PhD as well as her human care for all her students well beyond her research expectations. Her knowledgeable advices, insightful directions and support are deeply appreciated. I am very thankful for all the times she devoted to meet with me weekly and provided useful ideas along the course of my PhD work. I feel very fortunate to have been under her tutelage these past five years. I am also very appreciative to have had the opportunity to work very closely with Professor Roger Howe. As one of the main investigators of the Modular SiGe Project/Integrated Microwatt Transceiver, his enthusiasm in the subject, his valuable experience, as well as technical expertise has tremendously helped me during this study. He has a knack for keeping research into

perspective and it is really great collaborating with him. I thank Professor(s) Morris and Attwood for serving in my PhD qualifying examination. Professor Attwood offered me financial support my first year at CAL, I am still very grateful to him for believing in me. During my last year of graduate school, I had the opportunity to collaborate closely with Professor Sanjay Govindjee in our "cool" and "exciting" poly-Si<sub>1-x</sub>Ge<sub>x</sub> levitated inertial sensor system project, popularly known as the FLEMS project (FLEMS stands for Floating Electro Mechanical System). I've learnt a lot on control theory from these "FLEMS" meetings, and I would like to thank Sanjay for accepting to be part of my dissertation committee, as well as Andreas Kominek and David Garmire who did most of the simulations and testing work for the FLEMS devices that I fabricated.

I appreciate all the efforts of the Microfabrication staff to keep the lab working properly. Bob Hamilton and Jimmy Chang are particularly appreciated for their devoted work on Tystar 20. Without the furnace being up and running periodically, this work would have not been possible. Special Thanks go to Hideki Takeuchi, Christoph Duenn and Xiaofeng Meng who helped me a lot in the during my qualification process in the microlab. They spent a lot of time teaching me how to use different equipment, and suggesting valuable insights when experiments failed. I thank Joe Donnelly who was always more than available to help me out in the lab.

Great discussions with former and current SiGe/IMT students are greatly appreciated. It has been very rewarding collaborating and interacting with my dear friend and big sister Andrea Franke (peace to her soul), Sunil Bhave, Di Gao, Brian Bircumshaw, Gang Liu, Carrie Low, Blake Lin, Donovan Lee, Anderson Hei Kam, Emmanuel Quevy. Since my research scope fell into the intersection of MEMS and Device Physics, collaborating with both BSAC and Device students has been a gratifying experience. I feel particularly blessed to have gotten to know and interact with Vidya Varadarajan, Sriram Balasubramanian, Mohan Dunga, Daewon Ha, Joanna Lai, Yuri Yassida, Kyoungsub Shin, Hiu Yung Wong, Pankaj Kalra, Alvaro Padilla, Andrew Carlson, Yu-Chih Tseng, Chung-Hsun Lin, Kinyip Phoa, Anupama Bowonder, Xin Sun, Noel Arellano, Frank Zendejas, Justin Black, William Holtz, Caroline White, Gianluca Piazza, Phillip Stephanou, Peter Chen, Maryam Ziaie-Moayyed, Christopher Roper..etc. Fun and relaxing discussions in our 373 Cory cubic about life, research, graduate school survival, what's next after graduate school, religion (basically everything), have been more than helpful to make my graduate tenure in Cory Hall more enjoyable.

Millions thanks go to Mary Byrnes and Ruth Gjerde in the graduate office for all the useful advices, the care and attention during my years in the EECS department. They both have been great source of support and information. I am also very appreciative to my two grant administrators, Linda Manly in the SiGe/IMT project and Tom Parsons in the FLEMS project, for all their help and assistance in filling out paper-work necessary for sending out my SiGe wafers to vendors for films' characterization, attending conferences and all reimbursement issues. Other administrative assistants who have also been an awesome resource of support are deeply appreciated. This includes Robin Lake, Rosita Alvarez-Croft, Jontae Gray, Charlotte Jones, Loretta Lutcher and Helen Kim.

My summer internships in the RF MEMS group of IBM Watson Research Center and INTEL Santa Clara have provided me with deep insight about the nature of industrial research, and part of my work at Watson has been included in this thesis. I am grateful to my manager John Margelein, my mentor Nils Hoivik as well as others members of the RF MEMS group which include Christopher Jahnes and John Cotte for all their support and invaluable advices during my time at Watson. At Intel, I have learnt a great deal about RF MEMS switches testing from the MEMS group members Quan Tran, Allen Chou and John Heck. Thank you for giving me the opportunity to work with you and learn from you on RF MEMS switches testing.

I acknowledge funding from the DARPA IMT Project (Dan Radack Program manager) and DARPA FLEMS Project (John Evans program manager) as well as Robert Bosch Corporation.

WICSE (Women in Computer Science and Electrical Engineering) and BGESS (Black Graduate Student in Engineering and Science) have also helped to make my time at "CAL" a special and unique experience by keeping me out of "insanity". In these two organizations, I have met wonderful women and underrepresented minorities students that I've befriended over the years. This includes: Sheila Humphrey, Megan Thomas, Chris Hildrum, Tiffany Grant, Tiffany Crawford, Jennifer Wade, Debbie Jones, Doug Densmore, Hakim Weatherspoon, Greg Lawrence, Mark McKelvin, Koffi Boakye, Nerayo Petros Teclemariam. I cherish all the great discussions we had weekly or biweekly around a lunch or dinner table concerning issues that are dear and near to my heart. Such issues include the real need for our involvement in an active recruitment of more women and underrepresented minorities in science and engineering related fields through mentoring, tutoring and reaching out to younger folks in our community.

I am thankful to my mother who has always encouraged me to pursue my dreams even from a very young age in our home country (Cameroon) where it was too daring to have high "dreams". I dearly and deeply thank her for all the sacrifices she has made into

ix

making what I am today. I am also very grateful to my older sister, Stephanie who has always spoke affirming words of encouragements and blessings over my life throughout the years. She helped to pay my undergraduate tuition and I sincerely appreciate her. Finally, I am thankful to Maurice Brenyah-Addow for his genuine care during the last quarter of my graduate career. He has helped to build my character in different areas, taught me a lot as of how to have "fun" outside of Cory Hall as well as how to be less stressed-out and trust in God in all what I do. Your amazing faith, your great sense of calmness and your deep wisdom have been a tremendous example for me.

# **List of Figures**

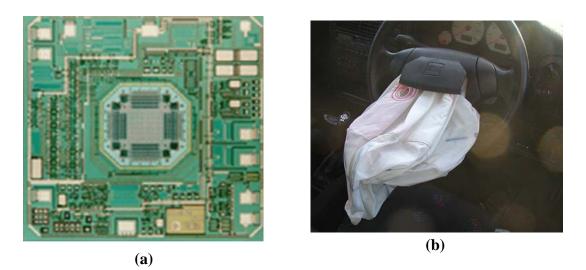

**1.1** An early accelerometer from *Motorola Inc*. showing a MEMS chip placed next to a CMOS chip placed in a ceramic package. Electrical connection is made possible by using metal wires. These wires introduce unwanted parasitics that cause degradation of the system performance [Howe lecture notes, 2005].

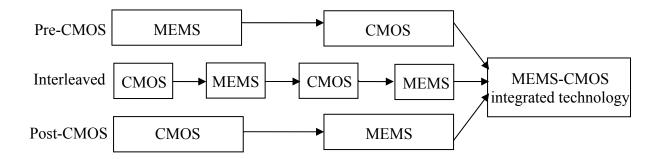

**1.2** Schematic description of the three monolithic integration schemes approaches that could be used to integrate micromachined devices with CMOS electronics [1.5].

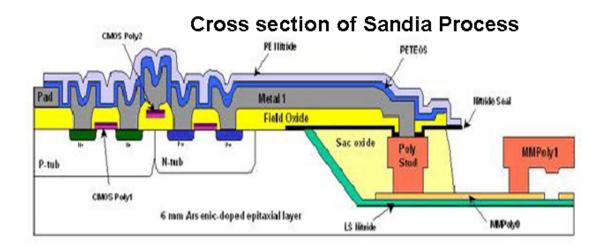

**1.3** Cross section of the *Sandia National Laboratory* SUMMIT foundry process where MEMS are fabricated inside a trench before the definition of the electronics. [1.11]

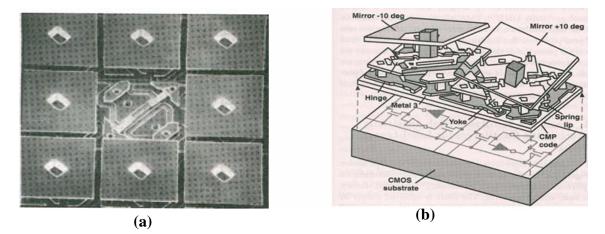

**1.4** Plan and cross section view of the DMD (Digital Micro-Mirror) device developed by *Texas Instruments Inc.* Here, MEMS are fabricated using Al films after the CMOS electronics [1.12]

**1.5 (a)** The *Analog Devices Inc.* ADLX-202 of about 5mm<sup>2</sup> holding in the middle a MEMS accelerometer around which are electronic sense and calibration circuitry. Hundreds of such devices have been sold. (b) Airbag of car that crashes into the back of a stopped Mercedes. Within 0.3 seconds after the deceleration, the air bag is empty, so that driver does not get hurt [1.13].

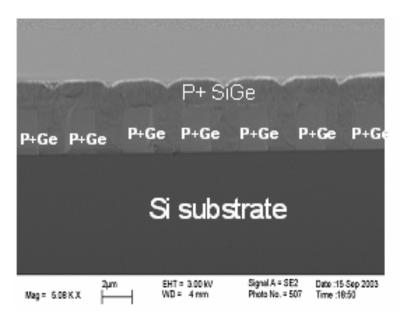

**1.6.** SEM showing conformal deposition of p+ Ge sacrificial films on top of p+ Si<sub>1-x</sub>Ge<sub>x</sub> films. After complete fabrication of the MEMS devices, the p+ Ge films are often released using H<sub>2</sub>O<sub>2</sub>, which does not attack Si<sub>1-x</sub>Ge<sub>x</sub> (x<0.65).

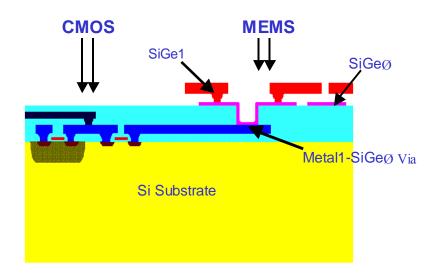

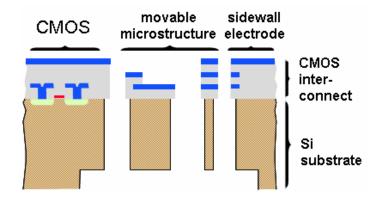

**2.1** Schematic cross-section of a modularly integrated SiGe MEMS technology. The "SiGe0" layer is used for routing of electrical signals between the MEMS and the electronics.

**2.2** (a) Poly Si<sub>1-x</sub>Ge<sub>x</sub> on Al showing pinholes and (b) on Al with TiN (no pinholes).

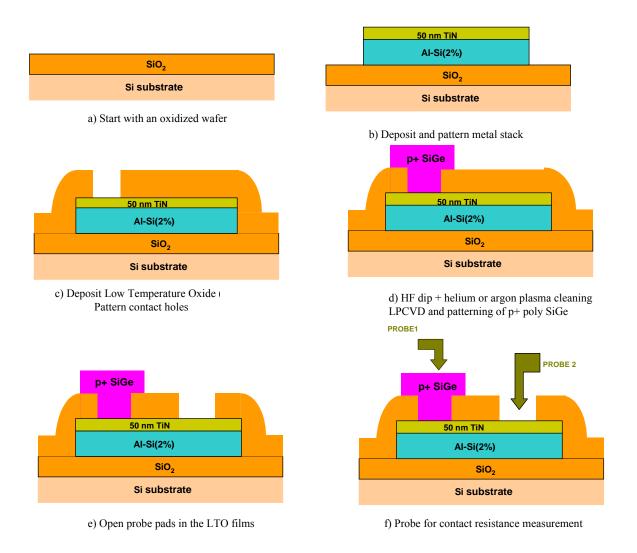

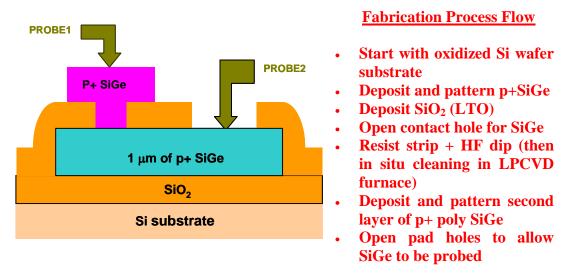

**2.3** Fabrication process flow for the Kelvin test structure used to measure contact resistance in this work.

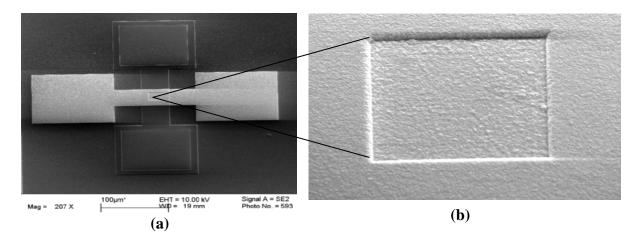

**2.4 (a)** Scanning electron micrograph of fabricated Kelvin test structure (b) Close-up view of a  $(10 \ \mu m)^2$  contact.

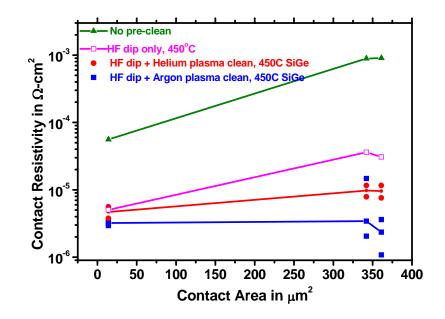

**2.5** Effect of pre-clean treatment on contact resistivity of  $Si_{1-x}Ge_x$  films deposited at 450°C for a  $(5\mu m)^2$  contact.

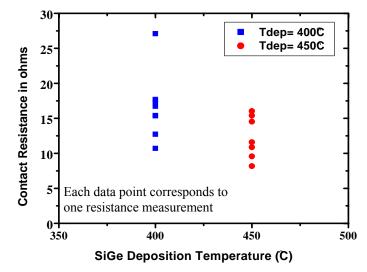

**2.6** Effect of poly-Si<sub>1-x</sub>Ge<sub>x</sub> deposition temperature on contact resistance for a  $(5\mu m)^2$  contact. HF dip + helium plasma were used as pre-furnace cleaning treatments. Ge concentration are similar at both temperatures.

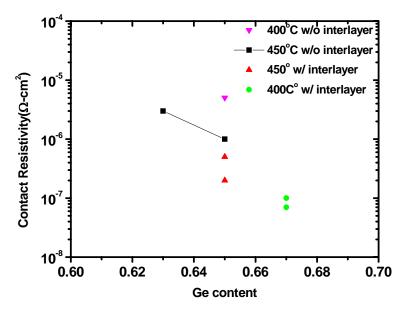

**2.7** Contact resistivity dependence on Ge content and temperature for a  $(5\mu m)^2$  contact. HF dip + Ar plasma were used as the pre-furnace cleaning treatments.

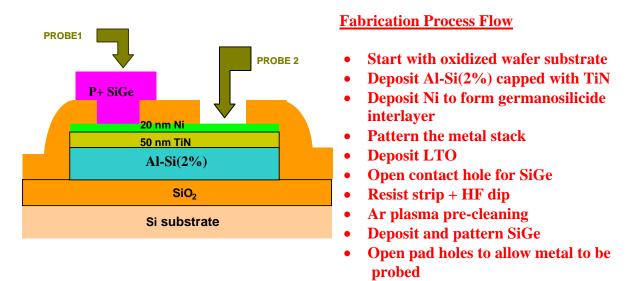

**2.8** Schematic cross-section and fabrication process flow of Ni-germanosilicide contact process.

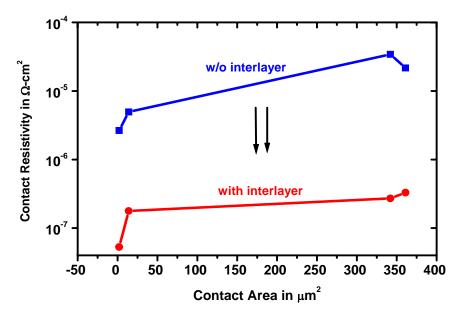

**2.9** Comparison of contact resistivity measurement for process flow with an interlayer metal against that without an interlayer. HF dip + Ar plasma were used as pre-furnace cleaning treatments.  $Si_{1-x}Ge_x$  films were deposited at 400°C.

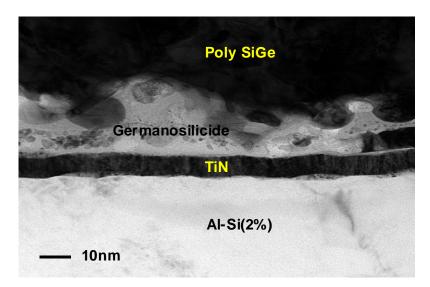

**2.10** TEM micrograph showing cross section of the contact region using a silicide interlayer.  $P+Si_{0.35}Ge_{0.65}$  films were deposited by LPCVD at 450°C.

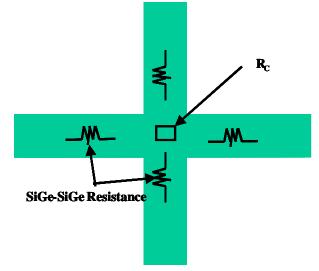

**2.11** Cross-section of the Kelvin structure used for SiGe to SiGe contact

2.12 Kelvin structure taking into account series resistance Si<sub>1-x</sub>Ge<sub>x</sub> -to- Si<sub>1-x</sub>Ge<sub>x</sub>

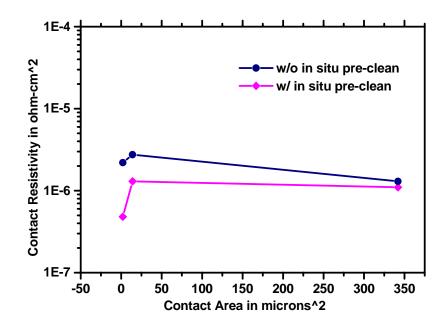

**2.13** Si<sub>1-x</sub>Ge<sub>x</sub> to Si<sub>1-x</sub>Ge<sub>x</sub> contact resistivity results with and without *in-situ* treatment

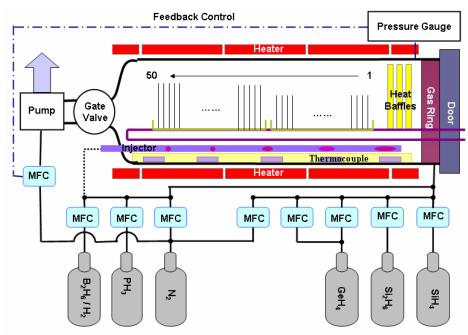

**3.1** Cross section of the LPCVD reactor used to deposit the p+Ge and p+  $Si_{1-x}Ge_x$  films:

- SiH<sub>4</sub> and GeH<sub>4</sub> are fed through the back of the tube, resulting in the fact that wafers placed at back of the furnace have higher Ge content.

- B<sub>2</sub>H<sub>6</sub> is fed through the front injector, resulting in the fact that wafers placed at front of the furnace have higher B content.

(Figure is a courtesy of *C. Low*)

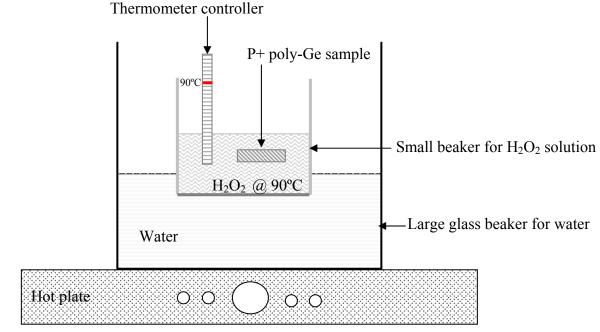

**3.2** Experimental set-up for the characterization of  $p+Si_{1-x}Ge_x$  and p+Ge etch rates in a 90°C heated solution of hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) for the study of boron doping effects on the etching properties of the  $p+Si_{1-x}Ge_x$  structural films as well as p+Ge sacrificial films.

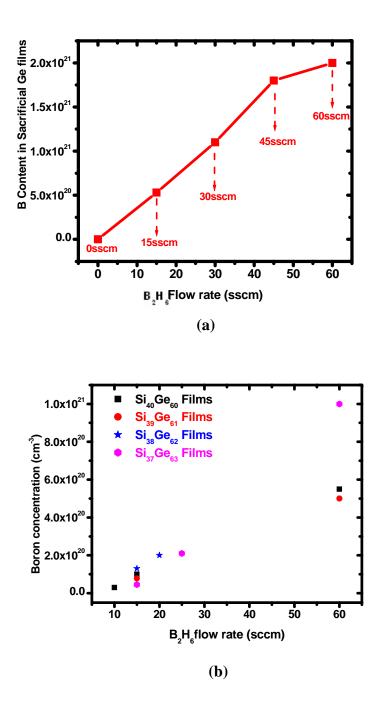

**3.3** Boron concentration *vs.*  $B_2H_6$  flow rate for (a) sacrificial p+ Ge films deposited by LPCVD at 350°C and 300 mTorr, with GeH<sub>4</sub> flow rate = 170 sccm (b) structural poly-Si<sub>1-x</sub>Ge<sub>x</sub> films deposited by LPCVD at 425°C and 400 mTorr, GeH<sub>4</sub> flow rate = 45 sccm, SiH<sub>4</sub> flow rate = 15 sccm.

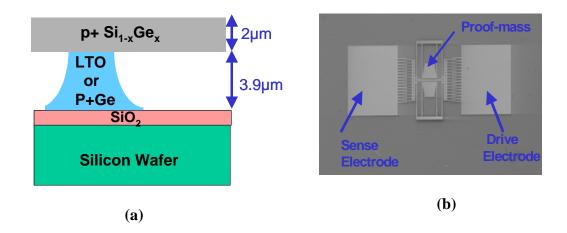

**3.4 (a)** Schematic cross section of cantilever beams used to determine the strain gradient in structural poly-Si<sub>1-x</sub>Ge<sub>x</sub> films. (b) SEM micrograph of fabricated comb-drive test structure.

**3.5** Van der drift construction through thickness, grain size and grain orientation evolution resulting from growth velocity anisotropy during film thickening [3.19].

Note that as the  $p+Si_{1-x}Ge_x$  films become thicker, their microstructure become more columnar and uniform, thus resulting in a lower strain gradient compared to thinner films.

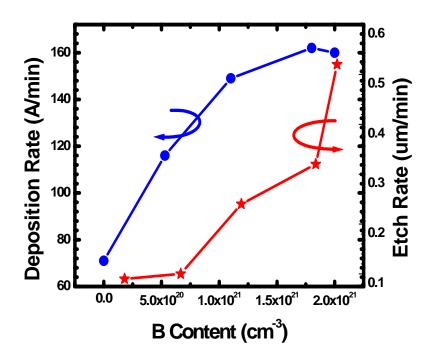

**3.6** Deposition and etch rates for Ge as a function of  $B_2H_6$  flow rate. The Ge films were deposited by LPCVD at 350°C and 30 mTorr, with GeH<sub>4</sub> flow rate = 170 sccm.

**3.7** SEM micrograph showing how Peroxide attacks p+ Ge at the grain boundaries after (a) No etching (b) after 15 seconds in  $H_2O_2$  (c) after 45 seconds in  $H_2O_2$

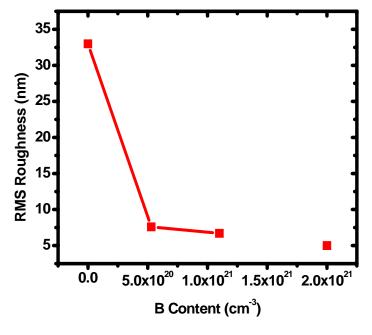

**3.8(a)** Ge film surface roughness, as a function of  $B_2H_6$  flow rate. The Ge films were deposited by LPCVD at 350°C and 300 mTorr, with GeH<sub>4</sub> flow rate = 170 sccm. (b) Close-up image showing surface roughness of films deposited with GeH<sub>4</sub> flow rate = 15 sccm

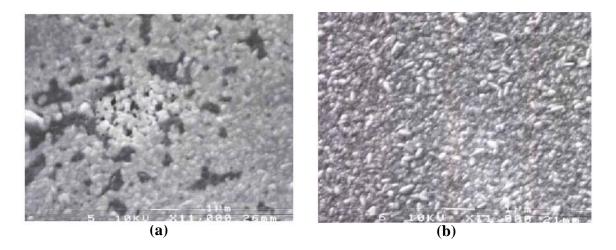

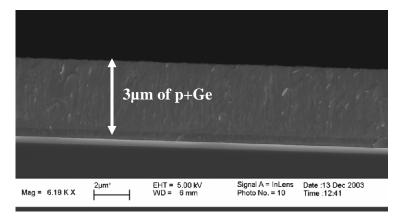

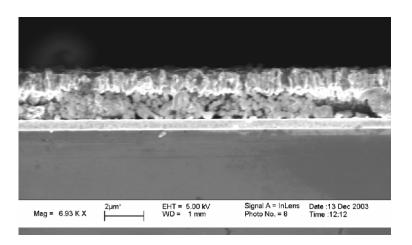

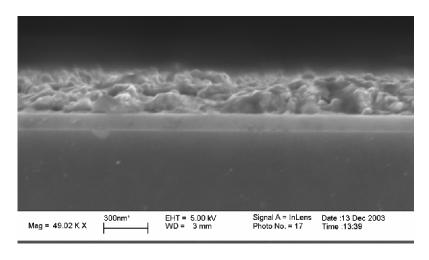

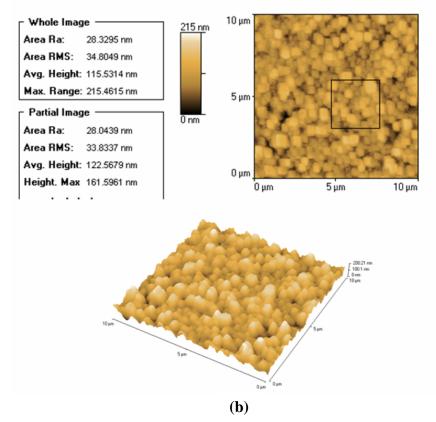

**3.9** X-TEM micrographs of p+ Ge films reported in Figures 3.4-3.6; (a)  $B=5.3x10^{20}$  cm<sup>-3</sup>, (b)  $B=1.1x10^{21}$  cm<sup>-3</sup>, (c)  $B=1.8x10^{21}$  cm<sup>-3</sup>, (d)  $B=6.2x10^{21}$  cm<sup>-3</sup>. Average grain size becomes smaller as [B] increases because of the increase in deposition rate due to increase in [B] content in p+ Ge films (Courtesy of TEM Analysis).

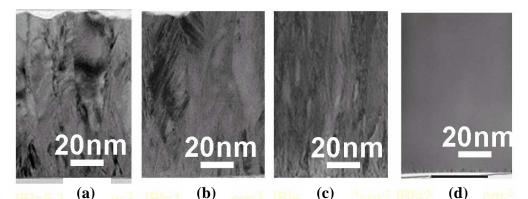

**3.10** Resistivity of p+ Ge films as a function of B concentration. The Ge films were deposited by LPCVD at 350°C and 300 mTorr, with GeH<sub>4</sub> flow rate = 170 sccm

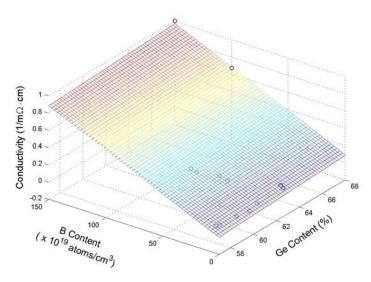

**3.11** Conductivity *vs.* boron concentration, for structural poly-Si<sub>1-x</sub>Ge<sub>x</sub> films deposited by LPCVD at 425°C and 400 mTorr, GeH<sub>4</sub> flow rate = 45 sccm, SiH<sub>4</sub> flow rate = 115 sccm

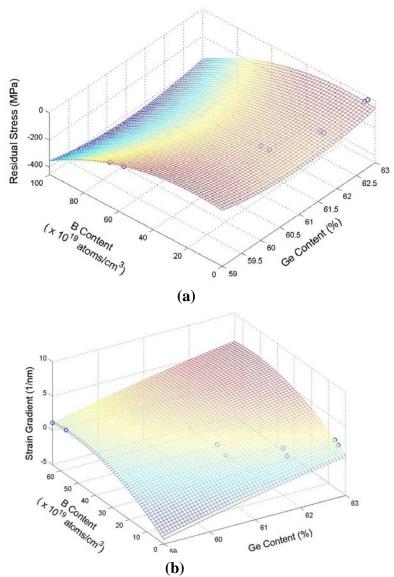

**3.12** Regression function analysis plots of (a) average residual stress, and (b) strain gradient of boron-doped poly- $Si_{1-x}Ge_x$  structural films, as a function of boron content

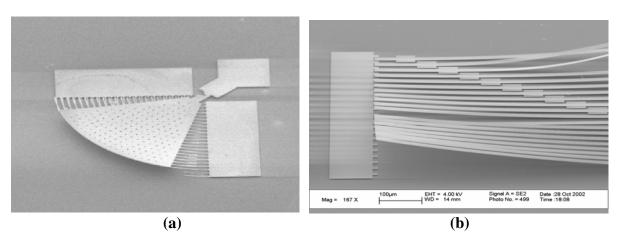

**3.13** SEM images showing severe strain gradient in As-deposited of boron-doped poly- $Si_{1-x}Ge_x$  structural films (a) test structure used for fatigue study (b) cantilever beams test structures used for strain gradient characterization

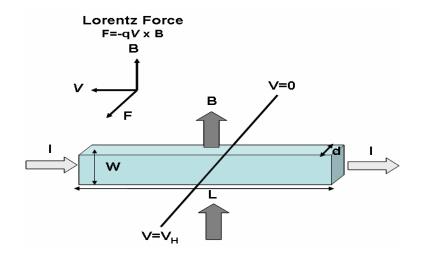

**3.14** Hall-Effect experiment showing a slab of silicon, where and E-field is applied parallel while a B field is applied perpendicular to the sample

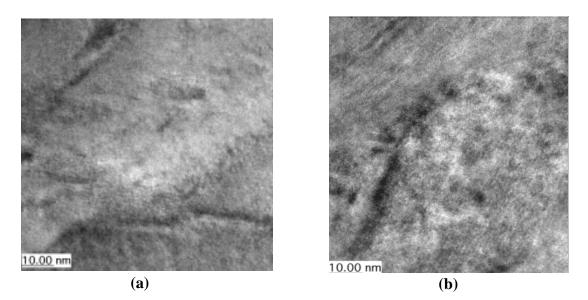

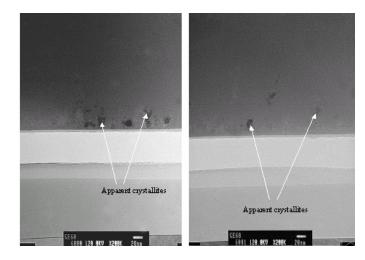

**3.15** Transmission Electron Microscopy of (a) Sample A and (b) Sample B. There is a concentration of texture at the grain boundaries of sample B as compared to Sample A, what would indicate clustering of boron atoms at the grain boundaries.

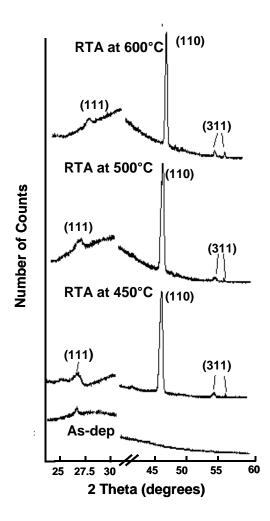

**3.16** XRD results of as-deposited as well as annealed p+ SiGe films at different RTA (Rapid Thermal Annealing) temperatures. RTA was performed in a N<sub>2</sub> ambient.

**3.17** Schematic cross-section of the tri-layer films fabricated

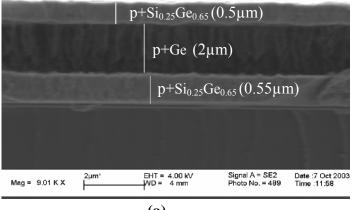

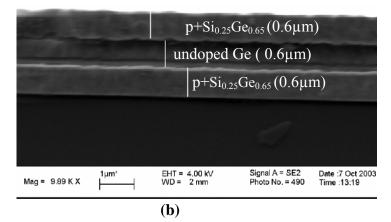

(a) SEM image of tri-layer made of  $p+Si_{0.25}Ge_{0.65}/p+Ge/p+Si_{0.25}Ge_{0.65}$

(b) SEM image of tri-layer made of p+Si<sub>0.25</sub>Ge<sub>0.65</sub>/i-Ge/ p+ Si<sub>0.25</sub>Ge<sub>0.65</sub>

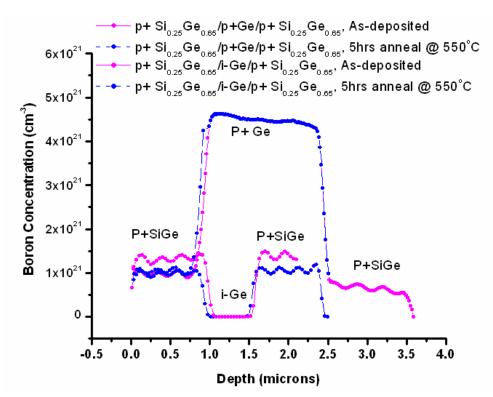

**3.18** Boron concentration verse depth using SIMS analysis (accuracy with 2-3%)

For the two tri-layers:  $p+Si_{0.25}Ge_{0.65}/p+Ge/p+Si_{0.25}Ge_{0.65}$  and  $p+Si_{0.25}Ge_{0.65}/i-Ge/p+Si_{0.25}Ge_{0.65}$ . Boron concentration is compared for As-deposited films and annealed films Note that the slight shift observed is accounted through the 2.5% accuracy of SIMS analysis.

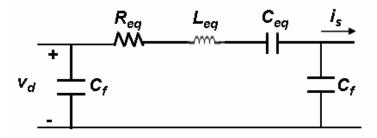

**4.1** A schematic picture for the lumped model of a MEMS filter that includes an equivalent resistance ( $R_{eq}$ ), capacitance ( $C_{eq}$ ), inductance ( $L_{eq}$ ) and some feedthrough capacitances ( $C_f$ ).

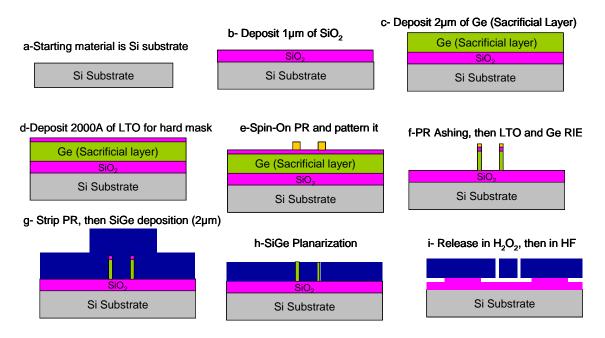

4.2 Fabrication process flow of RF MEMS filters using Ge ashing technique.

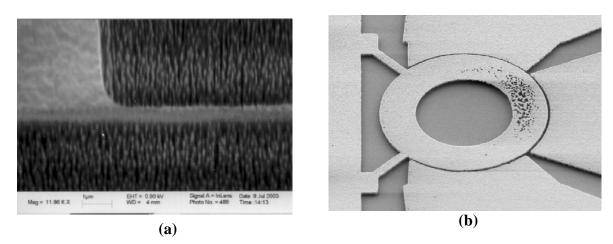

**4.3** (a) Close-view of photoresist residues observed after deep reactive ion etch process of p+ Ge films (b) Example of RF MEMS filter device that encountered polymers residues problem on the resonating ring mass.

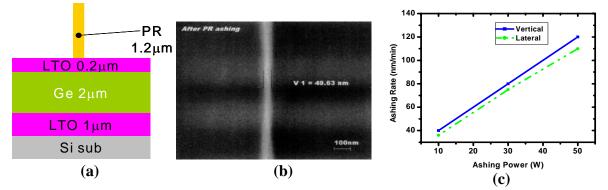

**4.4 (a)** Cross section of structure prior to resist ashing and **(b)** SEM top view of a PR line obtained after ashing, **(c)** linear relation between ashing rate and ashing power.

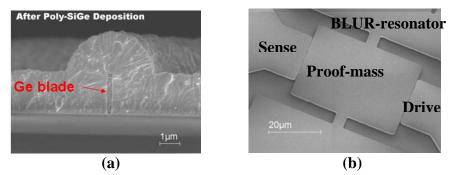

**4.5 (a)** Side-view of Ge blade after  $Si_{1-x}Ge_x$  deposition (b) Top view of a fabricated working Bulk Longitudinal Resonator.

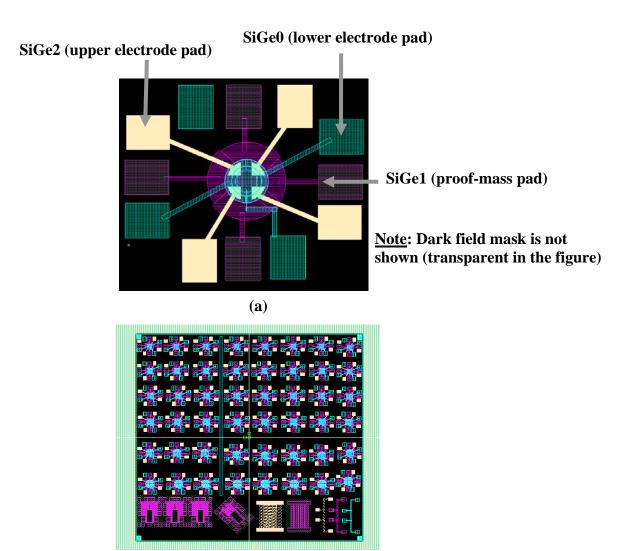

**4.6 (a)** FLEMS-gyro device layout **(b)** View of test die containing devices of various sizes and test structures (for measurement of stress, strain gradient, resistivity, and Young's Modulus).

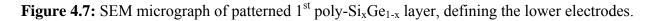

**4.7** SEM micrograph of patterned  $1^{st}$  poly-Si<sub>x</sub>Ge<sub>1-x</sub> layer, defining the lower electrodes.

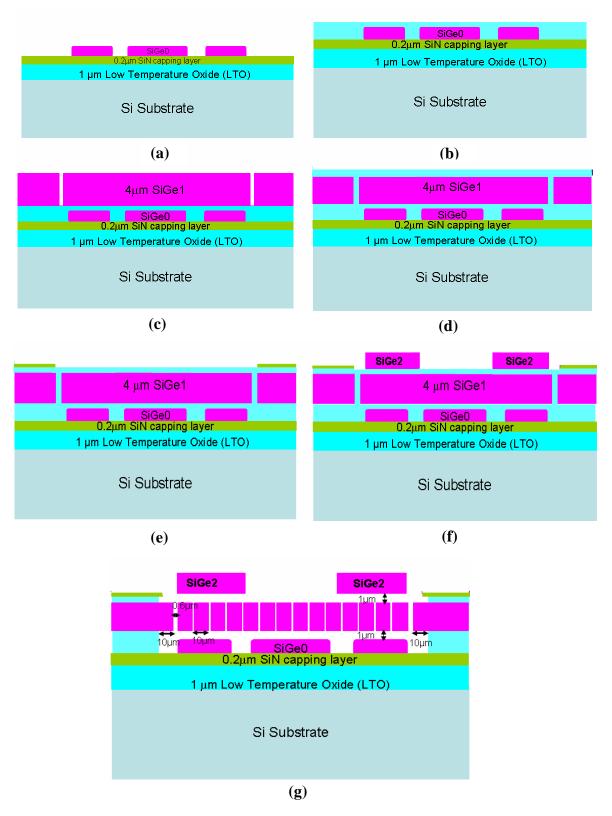

**4.8** Cross sectional schematics (not drawn to scale) to illustrate the FLEMS-gyro fabrication process. Etch holes in levitated mass are not shown in (a)-(f) for simplicity.

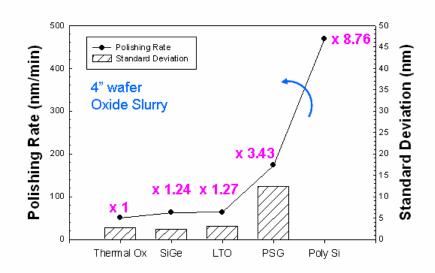

**4.9** CMP polishing rate of various materials used in semiconductor/MEMS processing [4.27].

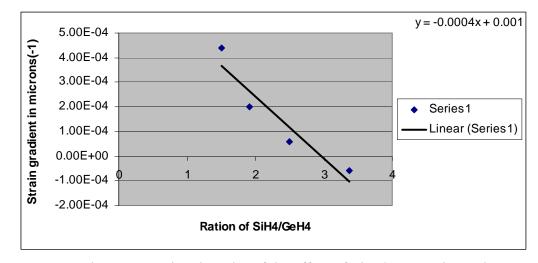

**4.10** Linear approximation plot of the effect of  $SiH_4/GeH_4$  ratio on the p+  $Si_{1-x}Ge_x$  strain gradient (data are taken from the Design of Experiment Matrix to achieve low strain gradient films using bi-layer procedure for stress gradient cancellation)

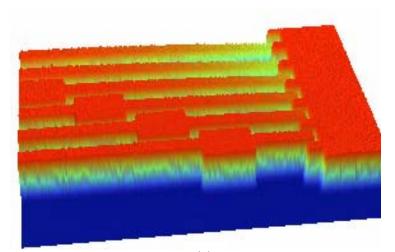

**4.11** Interferometry images of  $p + Si_{1-x}Ge_x 100\mu m$ -long cantilever beams

- (a) flat films corresponding to a deflection of  $0.1 \mu m$

- (b) slightly positive strain gradient corresponding to a deflection of  $0.2\mu m$

(c) slightly negative strain gradient corresponding to a deflection of  $-0.3\mu m$ .

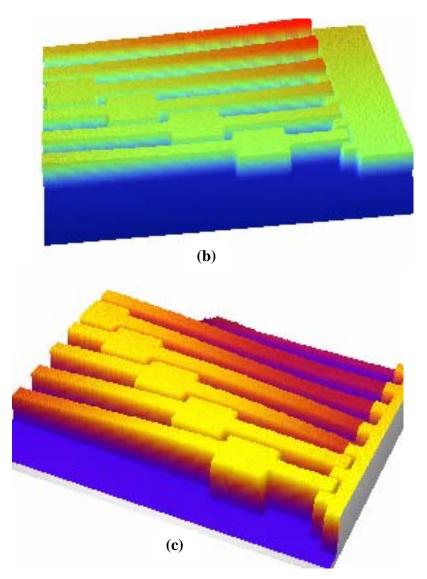

**4.12** Images of released p+ poly-Si<sub>1-x</sub>Ge<sub>x</sub> cantilever beams.

(a) using a Veeco Instrument WYKO interferometer (b) plan-view scanning electron micrograph. The beams are comprised of bilayer Si<sub>1-x</sub>Ge<sub>x</sub> films:

- The bottom  $Si_{1-x}Ge_x$  layer was deposited at 425°C and 600 mTorr, with GeH<sub>4</sub> flow rate = 70 sccm, SiH<sub>4</sub> flow rate = 105 sccm and BCL<sub>3</sub> flow rate = 12 sccm,  $\sigma$ =-51MPa

- The top  $Si_{1-x}Ge_x$  layer was deposited at 410°C and 600 mTorr, with  $GeH_4$  flow rate = 50 sccm,  $SiH_4$  flow rate = 125 sccm and  $BCL_3$  flow rate = 12 sccm,  $\sigma$ =-215MPa

Out-of-plane tip deflection is 0.1µm for a 100µm-long beam.

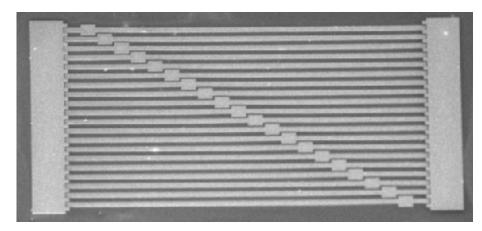

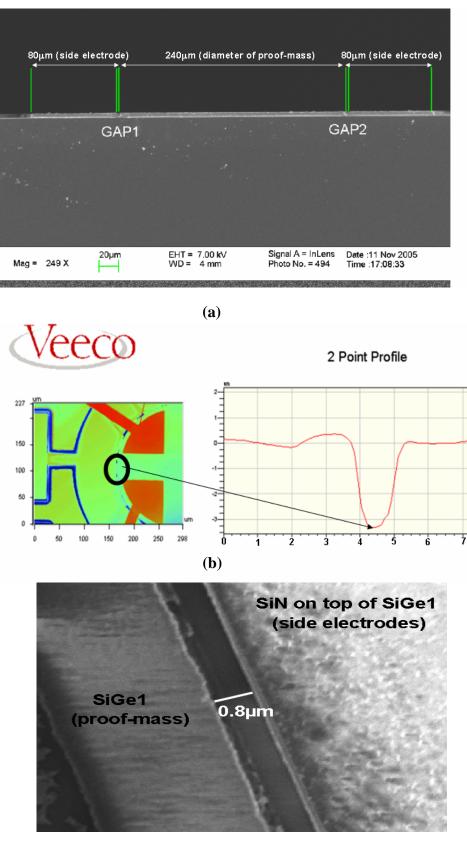

**4.13 (a)** Plan-view SEM image of patterned p+ Si<sub>1-x</sub>Ge<sub>x</sub> proof-mass disk and side electrodes (b) image showing proof-mass disk layer as well as the lower electrodes.

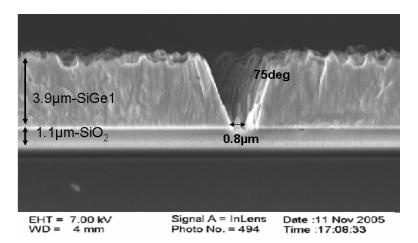

**4.14** 75°C angled lateral gap achieved when using chlorine based chemistry to etch  $4\mu m$  bi-layer p+ Si<sub>1-x</sub>Ge<sub>x</sub> used for the definition of the proof-mass disk layer.

**4.15 (a)** SEM cross section of the proof-mass and side electrodes, **(b)** zoomed-in interferometry image of a  $0.6\mu$ m lateral gap and **(c)** SEM plan view image of a  $0.8\mu$ m lateral gap.

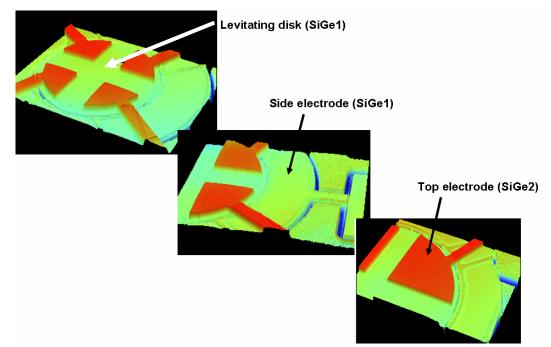

**4.16** Interferometry images of  $p+Si_{1-x}Ge_x$  top electrodes taken using a Veeco Instrument WYKO interferometer showing flat  $p+Si_{1-x}Ge_x$  films. Stress cancellation methodology that uses a bilayer deposition procedure was performed for the definition of the top electrodes

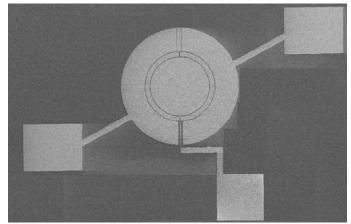

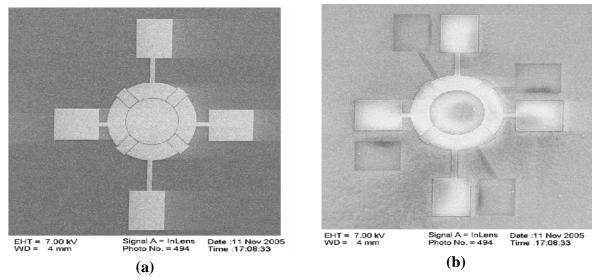

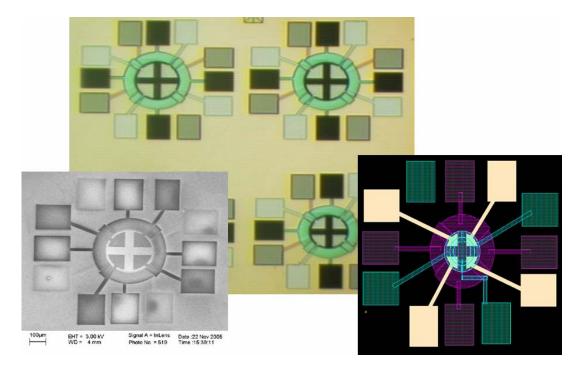

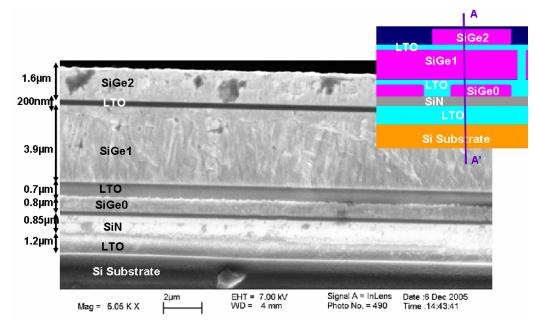

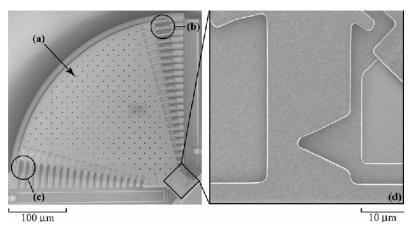

**4.17** FLEMS devices after complete fabrication process flow (microscopy, SEM and layout insert images are shown).

**4.18** SEM cross section of the FLEMS device after complete fabrication process flow (A-A' view). Final cross section closely agrees well with the expected cross section inserted

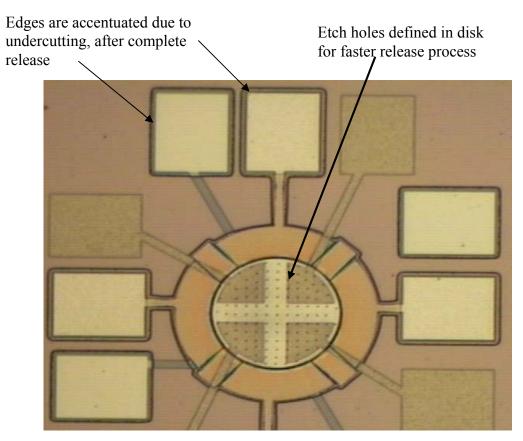

**4.19** FLEMS device revealing HF etching contour after complete release in 40°C HF vapor

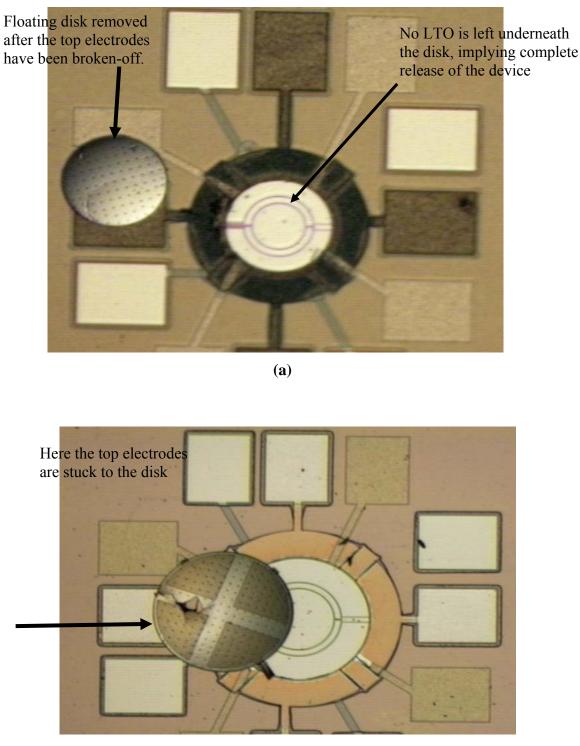

4.20 (a) Example of an optimal released device that does not have stiction issue(b) Example of released device with potential stiction issue between the top electrodes and the proof-mass disk

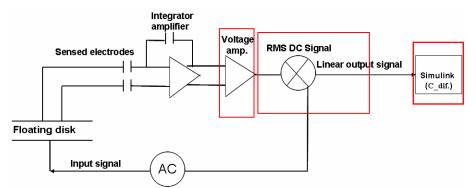

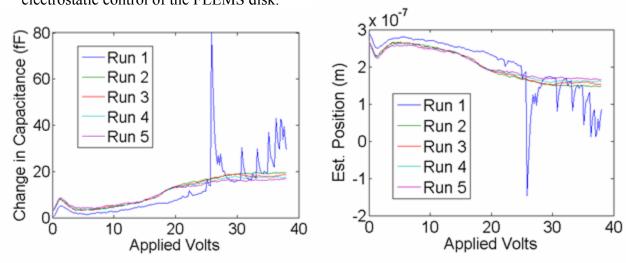

**4.21** Schematic of the electronics apparatus used for the sensing and electrostatic control of the FLEMS disk.

**4.22** (a) Change in Capacitance vs Voltage (b) Estimated lift position vs Voltage (Courtesy of *D. Garmire*).

**5.1** A post-CMOS micromachined lateral accelerometer fabricated using aluminum based interconnects [5.1].

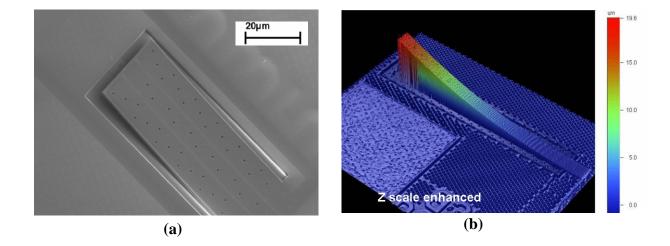

**5.2 (a)** SEM of released copper-based cantilever beam showing significant deformation due to an overall compressive stress gradient. (b) Interferometric image of same device with enhanced Z-scale.

**5.3** (a) Schematic description of the analytical approach used to derive the copper-based multilayered model. (b) Cross section of multilayer copper-based MEMS cantilever beam (not drawn to scale)

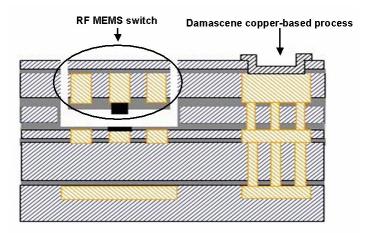

**5.4** Schematic of copper interconnect structures used to fabricate RF MEMS devices (switches and resonators) using conventional back-end-of-line (BEOL) materials.

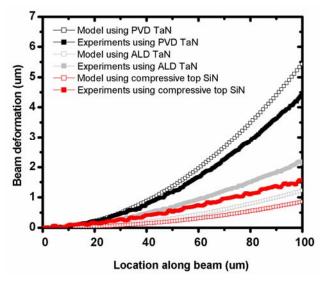

**5.5** Comparison of measured and modeled deformation of composite copper-based MEMS beams fabricated using PVD or ALD TaN liner material, and PVD liner material with compressive top SiN layer. The analytical model shows a similar trend as experimental data (reduction in beam curvature when ALD TaN is used instead of PVD TaN, as well as when compressive top SiN is used). Model accuracy is within 20%.

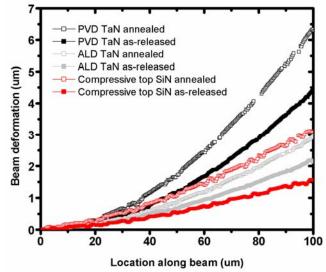

**5.6** Measured increase in deformation of composite copper-based MEMS beam (reported in Figure 5.5) for as-released and annealed devices. Annealing was performed at 400°C for 2 min in N<sub>2</sub> ambient to mimic the deposition of a final dielectric layer used for packaging. The overall beam deformation increased by 35 - 40% following annealing

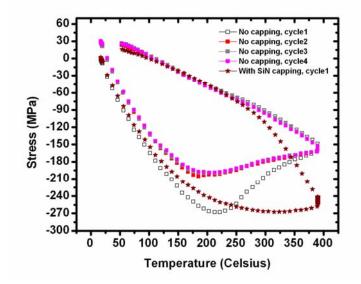

**5.7** Measured hysteretic stress behavior in SiN/TaN/Ta/Cu. As the temperature is increased from room temperature to 400°C, copper relaxes and yields around 225°C. Upon cooling the copper film returns back to tensile stress.

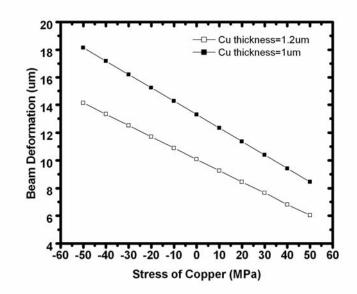

**5.8** Model of composite copper-based MEMS beam deformation as a function of copper stress for copper thickness =1.0 $\mu$ m and 1.2 $\mu$ m. A slightly ticker copper film shows less deformation

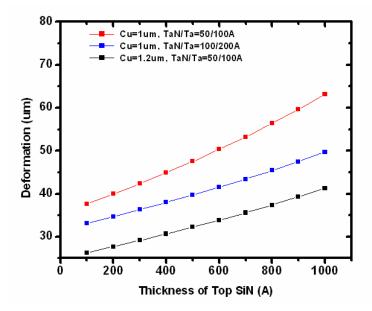

**5.9** Model of composite copper-based MEMS beam deflection as a function of SiN thickness for copper thickness =1.0 $\mu$ m and 1.2 $\mu$ m, and liner thickness =100A/200A or 50A/100A.

# **List of Tables**

**1.1** Mechanical properties of poly-Si compared to those of poly-Ge [1.46]-[1.47]

**1.2** Table showing etching rate/chemistries of poly-Ge, p+ poly-Si<sub>0.2</sub>Ge<sub>0.8</sub>, p+ poly-Si<sub>0.4</sub> Ge<sub>0.6</sub>, p+ poly-Si and annealed Phospho-silicate glass (etch rates are in  $\mu$ m/min) [1.25].

**2.1** P+ poly- Si<sub>1-x</sub>Ge<sub>x</sub> deposition parameters

**2.2** Average contact resistance and resistivity for Si <sub>0.65</sub>Ge<sub>0.35</sub> deposited at 450°C

2.3 Helium plasma pre-clean treatment compared to argon plasma pre clean treatment

**2.4** P+ poly  $Si_{1-x}Ge_x$  deposition conditions of seed layer and  $Si_{1-x}Ge_x$  layers

**2.5** Contact resistance and resistivity compared for process with and without *in-situ* cleaning.

**2.6** Summary of specific contact resistivity ( $\Omega$ -cm<sup>2</sup>) of this study. Data were extracted for a (2 $\mu$ m)<sup>2</sup> contact.

**3.1** Results from Hall-Effect measurement of dopant activation on Sample A (low compressive residual stress) verse Sample B (high residual stress).

**4.1** Summary of the array of FLEMS devices designed in the mask layout (Note that all the dimensions are in micrometer)

**4.2** Deposition process parameters of SiGe0 (ground plane layer) and SiGe1 (proof-mass levitated layer).

**4.3** Design of Experiment Matrix for development of a bi-layer deposition procedure to achieve a low strain gradient  $p+Si_{1-x}Ge_x$  structural layer.

**4.4** Bosch RIE recipe for Si, Ge and  $Si_{1-x}Ge_x$  to achieve high aspect ratio side walls (Courtesy of *M. Wasilik*, UC Berkeley Microlab Centura Operational Manual).

**5.1** Material properties of thin films used in the MEMS multilayered beam. Young's modulus and Poisson ratio data were obtained from the literature. Thickness and stress values are experimental data

# Chapter 1

## Introduction

## **1.1. Integration of MEMS with Electronics**

#### 1.1.1. What are MEMS?

Micro-Electro-Mechanical Systems (MEMS) are micron-scale devices that can sense or manipulate the physical world. MEMS are usually created using micromachining processes (surface or bulk micromachining), which are operations similar to those used to produce integrated circuits (ICs) devices, except that the final MEMS devices are released (free to move) at the end of the fabrication procedure [1.1]-[1.3].

To date, MEMS represent a growing technology with critical applications across diverse fields (optical, electrical, mechanical, biology, chemistry, biomedical...etc). Pressure sensors, accelerometers and angular rate gyroscopes still represent the vast majority of high-volume MEMS production. In the next decade, other MEMS devices such as optical MEMS switches, RF MEMS filters and chemical/biological MEMS sensors are predicted to experience widespread applications [1.4].

#### **1.1.2.** The need for a monolithic modularly integrated technology

The decision to merge CMOS and MEMS devices to realize a given product is mainly driven by performance and cost.

On the performance side, co-fabrication of MEMS structures with drive/sense capabilities with control electronics is advantageous to reduce parasitics, device power consumption, noise levels as well as packaging complexities, yielding to improved system performance [1.5]-[1.10]. With MEMS and electronic circuits on separate chips, the parasitic capacitance and resistance of interconnects, bond pads, and bond wires can attenuate the signal and contribute significant noise (**Figure 1.1**). Therefore, fabricating the MEMS devices directly on top of the CMOS metal interconnects will result in a reduction of the parasitics, that will greatly improve the system performance.

On the economic side, an improvement in system performance of the integrated MEMS device would result in an increase in device yield and density, which ultimately translates into a reduction of the chip's cost. Moreover, eliminating wire bonds to interconnect MEMS and ICs could potentially result in reduced packaging complexities which will eventually lead to more reliable systems, and in lower manufacturing cost.

However, in order to achieve high performance, reliable, and modularly integrated MEMS technology, many issues still need to be resolved. Some of these issues have been addressed and investigated in this dissertation with the use of two "Post-CMOS" low temperature MEMS technologies approaches: poly-Si<sub>1-x</sub>Ge<sub>x</sub> and copper-based MEMS technologies.

**Figure 1.1**: An early accelerometer from *Motorola Inc.* showing a MEMS chip placed next to a CMOS chip placed in a ceramic package. Electrical connection is made possible by using metal wires. These wires introduce unwanted parasitics that cause degradation of the system performance [Howe lecture notes, 2005].

## **1.2. Different modular integration approaches**

Modular integration will allow the separate development and optimization of electronics and MEMS processes. There are three main integration strategies that have been presented in the literature: "Pre-CMOS", "Post-CMOS" and the "interleaved approach". A schematic description of these three basic approaches is shown on **Figure 1.2**.

**Figure 1.2**: Schematic description of the three monolithic integration schemes approaches that could be used to integrate micromachined devices with CMOS electronics [1.5].

The first integration approach is the "Pre-CMOS" scheme that was first demonstrated by *Sandia National Laboratory* through their IMEMS foundry process [1.11]. With the use of surface micromachining process, the IMEMS process utilizes one sacrificial oxide layer and one structural poly-Si layer. High performance MEMS are fabricated in a trench etched in the silicon wafer. The trench is filled with PECVD (Plasma Enhanced Chemical Vapor Deposited) oxides and planarized to reduce the films' surface topography for further processing steps. Then, the MEMS devices are annealed to release their residual stress. After the annealing procedure, a passivation step of the MEMS is needed so that subsequent CMOS processes are MEMS compatible (in this case LPCVD nitride was used as the passivation layer). Next, a conventional CMOS fabrication process is performed followed by passivation of the CMOS devices. Finally, a trench is opened and the MEMS structures are released using hydrofluoric acid. A cross section of the integrated MEMS is shown in **Figure 1.3**.

**Figure 1.3**: Cross section of the *Sandia National Laboratory* IMEMS foundry process where MEMS are fabricated inside a trench before the definition of the electronics [1.11].

The major hurdles of the "Pre-CMOS" approach include the MEMS topography which can compromise subsequent state-of-the art CMOS lithography steps, larger die areas due to the fact that the MEMS and CMOS devices cannot be easily stacked and the fact that that integrated circuits foundries are usually not inclined to accept pre-processed wafers because of material compatibility and contamination issues.

The second integration approach is the "Post-CMOS" scheme which was successfully demonstrated by *Texas Instruments Inc.* through the DMD (Digital Micro-Mirror Device), which uses an electrostatically controlled mirror to modulate light digitally, thus producing a stable high quality image on a screen (**Figure 1.4a**) [1.12]. Each mirror corresponds to a single pixel programmed by an underlying SRAM cell (**Figure 1.4b**). Post-CMOS integration process is made possible through the usage of low temperature metal films (aluminum) as the structural layer and polymers (photoresist) as the sacrificial material.

The main hurdle when using the "Post-CMOS" integration approach is the temperature compatibility of both processes, so that a low temperature MEMS process is necessary to avoid damaging the CMOS interconnects.

**Figure 1.4**: Plan and cross section view of the DMD (Digital Micro-Mirror) device developed by *Texas Instruments Inc.* Here, MEMS are fabricated using Al films after the CMOS electronics [1.12].

In this work, two "Post-CMOS" integrations approaches have been studied with the use of SiGe MEMS technology and copper-based MEMS technology.

The third integration approach is the interleaved approach. This approach has been successfully demonstrated by *Analog Devices Inc.* in their 50G accelerometer (ADLX 50) technology which was the first commercially proven MEMS-CMOS integrated process [1.13]. While the main advantage of an interleaved integration process approach is the potential better control of both the MEMS and the CMOS process, the major drawback is the often need for a compromise of the MEMS and/or CMOS steps to achieve the necessary performances. A figure showing a complete integrated ADLX 50 chip is shown in **Figure 1.5**.

**Figure 1.5**: (a) The *Analog Devices Inc.* ADLX-202 of about 5mm<sup>2</sup> holding in the middle a MEMS accelerometer around which are electronic sense and calibration circuitry. Hundreds of such devices have been sold. (b) Airbag of car that crashes into the back of a stopped Mercedes. Within 0.3 seconds after the deceleration, the air bag is empty, so that driver does not get hurt [1.13].

### **1.3.** Poly SiGe, a low temperature mechanical material

#### **1.3.1. Summary of SiGe research for VLSI-CMOS applications**

Very recently, there has been a growing body of knowledge on silicon germanium technology within the integrated circuit community for multiple applications across the electronics manufacturing industry. While silicon germanium films have been intensively used for hetero-junction bipolar transistors, recent studies have shown silicon germanium as a good candidate for the replacement of poly-silicon gate technology in CMOS applications. Gate work function engineering can be performed by adjusting the Ge content in the films so that a complementary CMOS technology can still be implemented on the same substrate [1.14]-[1.15]. Strained silicon germanium channels are also being studied for the increase of electron mobility in CMOS technology [1.16]-[1.17]. Finally, silicon germanium can also be used in elevated source-drain CMOS technology for the reduction of the series resistance, thus increasing the transistor ON-current [1.18]-[1.19].

Taking advantage of such an extensive body of knowledge and experience on silicon germanium technology for VLSI-CMOS applications, MEMS researchers could build-up their wisdom from the integrated circuit community in order to implement this semiconductor alloy for micromachining applications.

#### **1.3.2. Summary of recent SiGe MEMS research**

An extensive overview of the research in SiGe MEMS technology has been recently been published by *S. Sedky* [1.20]. Two groups have been leading research in this field. Here at the University of California-Berkeley, the initial work of silicon germanium as a potential material for surface micromachining applications was performed by *A. Franke et al.* who successfully fabricated low frequency comb-drives devices on top of 0.25  $\mu$ m CMOS circuitry (with the electronics fully operational after the MEMS fabrication process) [1.21]-[1.22]. During the same period of time, *S. Sedky et al.* working at the Interuniversity MicroElectronics Center (IMEC) in Leuven (Belgium), also investigated the structural and mechanical properties of polycrystalline silicon germanium for micromachining applications [1.23]-[1.24].

In more recent years, there have been further investigations of the mechanical, electrical and chemical properties of poly-Si<sub>1-x</sub>Ge<sub>x</sub> MEMS technology. Polycrystalline p+ Ge films was suggested to be a convenient sacrificial layer with  $p+Si_{1-x}Ge_x$  as the structural layer since it can be selectively etched with peroxide at a temperature of 90°C [1.25]-[1.26], and an etching model was developed to optimize the Ge content in the films [1.27]. Other wet chemical etchants have been reported to release  $p+Si_{1-x}Ge_x$  micromachined films [1.28]-[1.29].

Phosphine doped poly-Si<sub>1-x</sub>Ge<sub>x</sub> films have been investigated for micromachining applications [1.30]. Two main findings came out of that study. Firstly, similar to phosphorus in poly-Si, phosphorus atoms retard the deposition of poly Si<sub>1-x</sub>Ge<sub>x</sub> films. The slower deposition rate of the n-type Si<sub>1-x</sub>Ge<sub>x</sub> films would result in an increase in the cost of the technology. Secondly, it was found that the resistivity of the n-type Si<sub>1-x</sub>Ge<sub>x</sub> films

was unacceptably high for most MEMS applications. Therefore, a high temperature annealing process (> 450°C) was often necessary to activate the dopants, thus reducing the films' resistivity [1.22],[1.30].

More lately, poly-Si<sub>1-x</sub>Ge<sub>x</sub> was reported to be a high Q mechanical material for both low and high frequency applications. Q value above 30,000 has been achieved for low frequency filtering applications (f=15kHz) [1.31] as well Q value ~ 30,000 for high frequency wireless communications (f=30MHz) [1.32].

Moreover, new techniques that include multilayer approach [1.33] and laser excimer annealing crystallization [1.6],[1.34]-[1.36] to reduce the stress and strain gradient of Si<sub>1-x</sub>Ge<sub>x</sub> films have been reported. All the studies performed in the SiGe MEMS Berkeley group use a Low Pressure Chemical Vapor Deposition (LPCVD) process to form the polycrystalline Si<sub>1-x</sub>Ge<sub>x</sub> films. LPCVD is a well understood technique that yields films with properties that are relatively insensitive to the process tool [1.37]-[1.38]. Also LPCVD is an extremely conformal process, which is important for the reliable fabrication of simple MEMS structures such as beam anchors.

Researchers at IMEC have intensively investigated Plasma Enhanced Chemical Vapor Deposition (PECVD) polycrystalline  $Si_{1-x}Ge_x$  films for MEMS applications. The main advantage of using a PECVD deposition process as compared to a LPCVD deposition process is a tremendous increase in deposition rate that greatly affects the cost of the technology. The PECVD poly- $Si_{1-x}Ge_x$  films have been demonstrated to have properties comparable to LPCVD poly- $Si_{1-x}Ge_x$  films qualities [1.39]-[1.42]. Novel processes that include metal induced crystallization [1.41] and multilayer approach to reduce the strain gradient of PECVD poly- $Si_{1-x}Ge_x$  films have been reported [1.42].

Micro gyroscopes inertial sensor devices have been successfully fabricated on top of standard  $0.35\mu m$  Al-CMOS process using low strain gradient multilayered PECVD Si<sub>x</sub>Ge<sub>1-x</sub> structural films [1.43].

#### **1.3.3.** Properties of poly-Si<sub>1-x</sub>Ge<sub>x</sub>

The mechanical properties of silicon germanium are comparable to those of polycrystalline silicon [1.44]-[1.45], and the films can be deposited in a conformal process (**Figure 1.6**) using low pressure chemical vapor deposition or plasma enhanced chemical vapor deposition [1.43]. **Table 1.1** compares the mechanical properties of silicon to those of germanium.

Certainly the most exciting characteristic of poly-Si<sub>1-x</sub>Ge<sub>x</sub> film, which makes this film a great candidate for MEMS micromachining integrated technology, is its low thermal budget that allows modular integration of MEMS with electronics by relaxing the high processing temperature required when poly-silicon films are used as the MEMS structural layers.

From **Table 1.1**, it is important to note that the density of poly-germanium film is almost twice that of poly-silicon, making it attractive for inertial sensing applications where a large mass is crucial to provide a large momentum for the achievement of high accuracy and precision in linear or angular acceleration measurements. Another valuable property of interest for MEMS applications is the smaller band gap of germanium, which yields to its low intrinsic resistivity compared to poly-silicon films.

**Figure 1.6**: SEM showing conformal deposition of p+ Ge sacrificial films on top of p+ Si<sub>1-x</sub>Ge<sub>x</sub> films. After complete fabrication of the MEMS devices, the p+ Ge films are often released using H<sub>2</sub>O<sub>2</sub>, which does not attack Si<sub>1-x</sub>Ge<sub>x</sub> (x<0.65).

|                                                  | Poly Si                     | Poly Ge              |  |  |

|--------------------------------------------------|-----------------------------|----------------------|--|--|

| Density (g/cm <sup>3</sup> )                     | 2.32                        | 5.33                 |  |  |

| Young modulus (GPA)                              | 170                         | 130                  |  |  |

| Melting point (°C)                               | 1412                        | 937                  |  |  |

| Thermal Conductivity W(cm °K) <sup>-1</sup>      | 1.5                         | 0.6                  |  |  |

| Lattice constant                                 | 5.4307                      | 5.6575               |  |  |

| Coef. of thermal expansion $(^{\circ}K)^{^{-1}}$ | 2.5x10 <sup>-6</sup>        | 5.7x10 <sup>-6</sup> |  |  |

| Dielectric constant                              | 11.7                        | 16                   |  |  |

| Bandgap at 300°K (eV)                            | 1.12                        | 0.66                 |  |  |

| Electron mobility (cm <sup>2</sup> /Vs)          | 1350                        | 3900                 |  |  |

| Hole mobility (cm <sup>2</sup> /Vs)              | 480                         | 1900                 |  |  |

| Intrinsic resistivity ( $\Omega$ -cm)            | 2.3x10 <sup>5</sup>         | 47                   |  |  |

| Quality Factor                                   | 45-80,000 <sub>n+poly</sub> | $30,000_{n^+ poly}$  |  |  |

**Table 1.1:** Mechanical properties of poly-Si compared to those of poly-Ge [1.46]-[1.47].

### 1.3.4. Deposition of poly-Si<sub>1-x</sub>Ge<sub>x</sub>

$Si_{1-x}Ge_x$  films are deposited in a conventional LPCVD reactor using germane (GeH<sub>4</sub>) as the germanium source gas, in addition to silane (SiH<sub>4</sub>) or disilane (Si<sub>2</sub>H<sub>6</sub>) as the silicon source gas, and phosphine (PH<sub>3</sub>), diborane (B<sub>2</sub>H<sub>6</sub>) or boron-trichoride (BCL<sub>3</sub>) [1.48] as the *in-situ* doping gas sources. The alloy composition during film deposition is dependent on several parameters: the deposition temperature, the gas partial pressure and the gas flow ratio. If the films are deposited on oxides, a very thin (<10nm thick) amorphous-Si seed layer is often needed to reduce the incubation time, thus allowing easy nucleation of the poly- Si<sub>1-x</sub>Ge<sub>x</sub> films on SiO<sub>2</sub>.

### 1.3.5. Etching of poly-Si<sub>1-x</sub>Ge<sub>x</sub>

The wet etching properties of polycrystalline boron doped silicon germanium and germanium films have been characterized by *J. Heck* for MEMS applications [1.25]. It was found that germanium films are easily etched in a 90°C heated solution of peroxide (H<sub>2</sub>O<sub>2</sub>), thus can be used as sacrificial material with p+ Si<sub>0.4</sub>Ge<sub>0.6</sub> as structural films. **Table 1.2** summarizes the main findings of this work. Other wet chemical etchants have been reported in [1.26].

|                                          | HF  | RCA, SC1 | $H_2O_2$ | Cl <sub>2</sub> /HBr Plasma |

|------------------------------------------|-----|----------|----------|-----------------------------|

| Poly-Ge                                  | ~0  | 3.0      | 0.4      | 0.41                        |

| Poly-Si <sub>0.2</sub> Ge <sub>0.8</sub> | ~0  | 0.75     | 0.08     | 0.37                        |

| Poly-Si <sub>0.4</sub> Ge <sub>0.6</sub> | ~0  | 0.06     | ~0       | 0.31                        |

| Poly-Si                                  | ~0  | ~0       | ~9       | 0.16                        |

| Annealed PSG                             | 3.6 | ~0       | ~0       | ~0                          |

**Table 1.2**: Table showing etching rate/chemistries of poly-Ge, p+ poly-Si<sub>0.2</sub>Ge<sub>0.8</sub>, p+ poly-Si<sub>0.4</sub>Ge<sub>0.6</sub>, p+ poly-Si and annealed Phospho-silicate glass (etch rates are in  $\mu$ m/min) [1.25].

## **1.4. Dissertation overview**

The monolithic integration of MEMS with CMOS remains an active research area that is crucial for the large scale production of high performance, high yield and low cost MEMS devices. It is important to mention that the right integration approach is largely dependent on a specific MEMS application.

This dissertation has investigated two "Post-CMOS" modular integration approaches:

- Boron doped poly-Si<sub>1-x</sub>Ge<sub>x</sub> MEMS films for high performance MEMS applications.

- 2. Copper-based MEMS technology for low loss RF MEMS applications.

**Chapter 2:** In order to attain a robust modular integration using SiGe MEMS technology, the poly-Si<sub>1-x</sub>Ge<sub>x</sub> micromachined films need to be deposited directly on top of the CMOS metalized lines to reduce parasitic capacitances and resistances. For this to be possible, the contact resistance between Si<sub>1-x</sub>Ge<sub>x</sub> films and Al-CMOS interconnects needs to be as low as possible *i.e.* comparable to that achieved between metal and poly silicon in modern integrated circuits (<  $10^{-6} \Omega$ -cm<sup>2</sup>). This chapter reports experimental results of contacts study between p+ poly-Si<sub>1-x</sub>Ge<sub>x</sub> films and aluminum interconnects when the poly-Si<sub>1-x</sub>Ge<sub>x</sub> MEMS devices are fabricated directly on top of the Al-CMOS circuitry lines. Process development and optimization have been intensively performed to reduce the contact resistivity to the desired minimal value (~ $10^{-7} \Omega$ -cm<sup>2</sup>) [1.49]-[1.51].

**Chapter 3:** In order to achieve a high performance integration technology scheme of the poly-Si<sub>1-x</sub>Ge<sub>x</sub> micromachined devices, the Si<sub>1-x</sub>Ge<sub>x</sub> films need to be heavily doped with boron to reduce the films resistivity as well as increase the films deposition rate [1.20]. In this chapter, a thorough study on the effects of boron doping and germanium content on the properties of p+ poly-Si<sub>1-x</sub>Ge<sub>x</sub> MEMS films has been performed. Experimental results will be presented as they pertain to the effects of boron concentration on the chemical, electrical, and mechanical properties of p+ polycrystalline germanium (poly-Ge) film used as sacrificial layer and p+ polycrystalline silicon germanium (poly-Si<sub>1-x</sub>Ge<sub>x</sub>) film used as structural layer [1.52]. The ultimate goal of this study is to pave the way for the realization of a robust and reliable SiGe MEMS technology, by providing a better understanding of the film property dependence on boron doping and Ge content.

**Chapter 4:** After understanding the effects of Ge and B concentrations on the mechanical, electrical and chemical properties of SiGe MEMS, we can go ahead and fabricate functioning MEMS devices using SiGe MEMS technology. This chapter presents experimental results of two MEMS systems fabricated using  $p+Si_{1-x}Ge_x$  MEMS technology. First, results of a short loop fabrication procedure that used Ge ashing technique to fabricate reliable RF MEMS filters for wireless communication applications are presented [1.53]-[1.55]. Second, surface micromachining results of a fabricated poly-Si<sub>1-x</sub>Ge<sub>x</sub> free moving disk used to pave the way towards an integrated electrostatically levitated disk sensor system for low loss inertial sensing applications are reported [1.56].

**Chapter 5:** The unknown reliability of many MEMS devices limits their incorporation into commercial products. The long-term stability of these devices can only be ensured with greater knowledge of the basic material properties and failure mechanisms of the materials employed in MEMS designs. In this chapter, reliability issues of MEMS structures as they pertain to the intrinsic stress gradient of MEMS switches used in low loss RF MEMS applications have been addressed [1.57]. An analytic model that predicts the deflection of RF MEMS switches fabricated using the state-of-the art copper-based "back-end" technology has been generated. The model matches the experimental data within 20% and could be used for design and process optimization in order to attain a low loss modularly integrated MEMS technology. Moreover, experimental evidence that provides a better understanding of the copper stress relaxation behavior is presented; this turns out to be essential for designing MEMS devices tolerant to high temperature packaging process.

**Chapter 6:** This chapter summarizes the main findings of this work as well as provides future directions for the modular integration MEMS field that utilizes  $p+Si_{1-x}Ge_x$  and copper-based MEMS technologies. A thorough study on the "long-term stability" of  $p+Si_{1-x}Ge_x$  MEMS devices (switches, resonators, gyroscopes...etc) remains necessary in order bring  $Si_{1-x}Ge_x$  MEMS devices into high volume production as well as the development of a low temperature CMOS-compatible packaging technology that is needed for the vacuum encapsulation of many integrated MEMS systems.

# **References:**

[1.1] M. Madou, Fundamentals of Microfabrication, CRC Press, New York, 1997.

[1.2] S. D. Senturia, Mycrosystem design, Kluwer Academic Publishers, 2001.

[1.3] G. Kovacs, Micromachined Transducers, McGraw-Hill, New York, 1998.

[1.4] N. Maluf, An introduction to Microelectromechanical Systems Engineering, The Artech House Inc., 2000.

[1.5] C. T-.C. Nguyen, Micromechanical Signal Processors, PhD. Dissertation, Dept of Electrical Engineering and Computer Sciences, UC Berkeley Fall 1994.

[1.6] T.-J. King, R.T. Howe, S.Sedky, G. Liu, B.C. Lin, M. Wasilik and C. Duenn, "Recent Progress in Modularly Integrated MEMS Technologies", Technical Digest of International Electron Device Meeting, pp.199-202, 2002.

[1.7] M. Biebl, G. T. Mulhern, and R.T. Howe, "In situ phosphorus-doped polysilicon for integrated MEMS," 8<sup>th</sup> International Conference on Solid-State Sensors and Actuators(Transducers 95), Stockholm Sweden, Vol.1, pp.198-201, 1995.

[1.8] H. Xie, L. Erdmann, X. Zhu, K. Gabriel, and G. Fedder, "Post-CMOS processing for high- aspect ratio integrated silicon microstructures," Solid-State Sensor and Actuator Workshop, Hilton Head -SC., pp.77-80, 2000.

[1.9] M. Lemkin, M. Ortiz, M. Wongkomet, B.E. Boser, and J.H. Smith, "A 3-axis surface micromachined Sigma-Delta accelerometer," ISSCC Digest of Technical Papers, pp.202-203, 1997.

[1.10] K.A. Shaw and N. C. MacDonald, "Integrating SCREAM micromachined devices with integrated circuits," Proceedings 9<sup>th</sup> International Workshop on Micro-Electromechanical Systems, San Diego CA, pp.4-48, 1996.

[1.11] J.H. Smith, S. Montague, J.J. Sniegowski, J.R. Murray, R.P. Manginell, and P. J. McWhorter, "Characterization of the embedded micromechanical device approach to the monolithic integration of MEMS with CMOS," SPIE, Vol. 2879, pp.306-314, 1996.

[1.12] P. F. Van Kessel, L. J. Hornbeck, R. E. Meier, and M. R. Douglass, "A MEMS Based projection Display," Proceedings of IEEE, Vol 86, No.8, pp.1687-1704, 1998.

[1.13] T. A. Core, W. K. Tsang, and S. J. Sherman, "Fabrication technology for an integrated surface-micromachined sensor," Solid State Technology, pp. 39-47, 1993.

[1.14] T.-J. King, J. P. McVittie, K. C. Saraswat, J. R. Pfiester, "Electrical properties of heavily doped polycrystalline silicon-germanium films," IEEE Transactions on Electron Devices, Vol. 41, No.2, pp. 228-232, 1994.

[1.15] T.J. King, Applications of Polycrystalline Silicon Germanium Thin Films in Metal-Oxide-Semiconductor Technologies, Ph.D. Thesis, Dept of Electrical Engineering and Computer Sciences, Stanford University, March 1994.

[1.16] S. Thompson, R. S. Chau, T. G. Kaisad Mistry, S. Tyagi, and M. T. Bohr, "In search of forever transistor scaling one new material at a time," IEEE Transactions of Semiconductors Materials, Vol. 18. No.1, pp. 26-36, 2005.

[1.17] M. L. Lee, E. A. Fitzgerald, M. T. Bulsara, M. T. Currie, and A. Lochtefeld, "Strained Si, SiGe and Ge channels for high-mobility metal-oxide-semiconductor field-effect transistors," Journal of Applied Physics, Vol. 97, pp. 1-27, 2005.

[1.18] Y-K Choi, D. Ha, T-J King and C. Hu, "Nanoscale Ultrathin Body PMOSFETs with Raised Selective Germanium Source/Drain" IEEE Electron Device Letters, Vol.22, No.2, pp. 279-286, 2002.

[1.19] M. C. Ozturk, J. Liu, X. Mo, and N. Pesovic, "Advanced SiGe Source/Drain and Contact Technologies for Sub-70nm CMOS", Technical Digest of International Electron Device Meeting, pp. 375-378, 2002.

[1.20] S. Sedky, Post-Processing Techniques for Integrated MEMS, Artech House Inc, Norwood-MA, November 2005.

[1.21] A.E. Franke, Y. Jiao, M. T. Wu, T. -J. King and R. T. Howe, "Post CMOS Modular integration of Poly-SiGe microstructures using poly-Ge sacrificial layers," Solid-State Sensor and Actuator Workshop, Hilton Head-SC, pp.18-21, 2000.

[1.22] A.E. Franke, Polycrystalline Silicon-Germanium Films for Integrated Microsystems, PhD Dissertation, Dept of Electrical Engineering and Computer Sciences, UC Berkeley Fall 2000.

[1.23] S. Sedky, P. Fiorini, M. Caymax, S.Loreti, K.Baert, L.Hermans, and R.Mertens, "Structural and mechanical properties of polycrystalline silicon germanium for micromachining applications," Journal of Microelectromechanical Systems, Vol.7, No. 4, pp.365-372, 1998.

[1.24] S. Sedky, A. Witvrouw, and K. Baert, "Poly SiGe, a promising material for MEMS monolithic integration with driving electronics," Sensors and Actuators A, Vol. 97-98C, pp. 496-504, 2002.

[1.25] John Heck, Polycrystalline Silicon Germanium for Fabrication, Release, and Packaging of Microelectromechanical Systems, Dept of Applied Science and Technology, University of California-Berkeley, Spring 2001. [1.26] B. Li, B. Xiong, L. Jiang, Y. Zohar, and M. Wong, "Germanium as a Versatile Material for Low-Temperature Micromaching," Journal of Microelectromechanical Systems, Vol.8, No.4, pp.366-372, 1999.

[1.27] B. L. Bircumshaw, M. L. Wasilik, E. B. Kim, Y. R. Su, H. Takeuchi, C.W. Low, C. Liu, A. P. Pisano, T.-J. King, R. T. Howe, "Hydrogen peroxide etching and stability of P-type poly-SiGe films," Proceedings of the 17th International Conference on Microelectromechanical Systems, pp. 514-520, 2004.

[1.28] G.S. Supin, "Dissolution of Monocrystalline Germanium in Hydrogen Peroxide," Journal of Applied Chemistry of the USSR, Vol.32, No.3, pp.506-509, March 1959.

[1.29] D.W. Oxtoby, N.H. Nachtrieb and W. A. Freeman, Chemistry: Science of change, Saunders College Publishing and Winston Inc, Philadelphia, 1990.

[1.30] Y.-C. Jeon, T.-J. King and R.T. Howe, "Properties of Phosphorus-Doped Poly-SiGe Films for Microelectromechanical System Applications", Journal of Electrochemical Society, Vol .150, No.1, pp.1-6, 2003.

[1.31] S. A. Bhave, B. Burcumshaw, C. W. Low, Y-S Kim, A. Pisano, T.J. King, R.T. Howe, "Poly-SiGe: A high-Q structural material for integrated RF MEMS," Solid-State Sensor and Actuator Workshop, Hilton Head-SC, pp.34-37, 2002.

[1.32] E. Quevy, S. Bhave, H. Takeuchi, T.-J. King and R. Howe, "Poly-SiGe high frequency resonators based on lithographic definition on nano-gap lateral transducers," Solid-State Sensor and Actuator Workshop, Hilton Head-SC, pp. 360-364, 2004.

[1.33] B. C.-Y. Lin, T.-J. King, R. T. Howe, "Optimization of poly-SiGe deposition processes for modular MEMS integration," Proceedings of the MRS 2003 Fall Meeting, Symposium A: Micro- and Nanosystems (Boston, MA), 2003.

[1.34] S. Sedky, R. T. Howe, T.-J. King, "Pulsed laser annealing, a low thermal budget technique for eliminating stress gradient in poly-SiGe MEMS structures," Journal of Microelectromechanical Systems, Vol.13, No.4, pp.669-675, 2004.

[1.35] R Murto, K Jones, M Rendon, S Talwar, "Activation and deactivation studies of laser thermal annealed boron, arsenic, phosphorus, and antimony ultra-shallow abrupt junctions," Proceedings of International Conference on Ion Implantation Technology, pp.17-22, 2000.

[1.36] S. Sedky, Jeremy Schroeder, Timothy Sands, T-J- King, R.T. Howe, "Pulsed Laser Annealing of Silicon Germanium Films," Material Research Society Proceedings, Vol. 741, No. J4.2, 2002.

[1.37] R.T. Howe and T.J. King, "Low-Temperature LPCVD MEMS Technologies" Material Research Society Proceedin gs, Vol.729, No. U5.1, 2002.

[1.38] T.-J. King and K. C. Saraswat, "Deposition and properties of low-pressure chemical-vapor deposited polycrystalline silicon-germanium films," Journal of the Electrochemical Society Vol. 141, No.8, pp-2235-2241, 1994.

[1.39] C. Rusu, S. Sedky, B. Parmentier, A. Verbist, O. Richard, A. Witvrouw, F. Larmer, S. Kronmuller, V. Leca, and B. Otter, "New low-stress PECVD poly-SiGe layers for MEMS," Journal of Microelectromechanical Systems, Vol.12, No.6, 2003.

[1.40] A. Mehta, M. Gromova, C. Rusu, R. Olivier, K. Baert, C. Van Hoof and A. Witvrouw, "Novel High Growth Rate Processes for Depositing Poly SiGe Structural Layers at CMOS Compatible Temperature" Proceedings of the 17th International Conference on Micro-electromechanical Systems, pp.514-520, 2004.

[1.41] S. Sedky, K. Baert, C. Van Hoof, Y. Wang, O. Van Der Biest and A. Witvrouw, "Low tensile stress SiGe deposited at 370°C for monolithically integrated MEMS applications," Material Research Society symposium proceedings, Vol. 808, A4.19, Spring 2004.

[1.42] A. Mehta, M. Gromova, P. Czarnecki, K. Baert and A. Witvrouw, "Optimization of PECVD poly-SiGe layers for MEMS post processing on top of CMOS deposition processes for modular MEMS integration," 13<sup>th</sup> International Conference on Solid-State Sensors and Actuators (Transducers 05), pp.1326-1329, 2005.

[1.43] A. Witvrouw, A. Mehta, A. Verbist, B. Du Bois, S. Van Aerde, J. Ramos-Martos, J. Ceballos, A. Ragel, J. M. Mora, M.A. Lagos, A. Arias, J. M. Hinojosa, J. Spengler, C. Leinenbach, T. Fuchs, S. Kronmuller, "Processing of MEMS gyroscopes on top of CMOS ICs," Technical Digest of the 2005 IEEE International Solid-State Circuits Conference, pp.88-89, 2005.

[1.44] A.E. Franke, D. Billic, D.T. Chang, P.T. Jones, T.J. King, R.T. Howe, G.C. Johnson, "Optimization of poly-silicon Germanium as a microstructural material,"10<sup>th</sup> International Conference on Solid-State Sensors and Actuators (Transducers 99), Sendai Japan, Vol.1, pp.530-533, 1999.

[1.45] B. Li, B. Xiong, L. Jiang, Y. Zohar, and M. Wong, "Applications of germanium to low temperature micro-machining," Proceedings of 12<sup>th</sup> International Workshop on Micro-Electromechanical Systems, Orlando FL, pp. 638-643, 1999.

[1.46] A.S. Grove, Physics and Technology of Semiconductor Devices, Wiley-New York, 1967.

[1.47] S. M. Sze, Physics of Semiconductor Devices, Wiley-New York, 1969.

[1.48] C. W. Low, M. L. Wasilik, H. Takeuchi, T.-J. King and R. T. Howe, "In-situ doped Poly-SiGe Process Using BCl<sub>3</sub> for Post-CMOS Integration of MEMS Devices," SiGe Materials, Processing, and Devices Symposium, Electrochemical Society, Honolulu, Oct. pp.3-8, 2004.

[1.49] M.A. Eyoum and T.-J.-King, "Low Resistance Silicon-Germanium Contact Technology for Modular Integration of MEMS with Electronics." Journal of Electrochemical Society, Vol. 151, No.3, February 2004.

[1.50] M.A. Eyoum, Polycrystalline Silicon Germanium Contact Resistance Study for Integrated MEMS Technology, Master's thesis UC Berkeley, May 2003.

[1.51] T.J. King, R. Howe, M.A. Eyoum, S. Bhave, "Interconnect Issues for Interconnect MEMS Technology," Advanced Metallization Conference, October 2002.

[1.52] M.A. Eyoum, R. Suy, R. Howe, T.J. King, "Effects of Boron concentration on  $Si_xGe_{1-x}$  properties for Integrated MEMS Technologies." Solid-State Sensor and Actuator Workshop, Hilton Head, SC, June 2004.

[1.53] M.A. Eyoum, E. Quevy, H. Takeuchi, T.-J. king, R. T. Howe, "Ashing Technique For Nano-gap Fabrication of Electrostatic Transducers." MRS Spring 2003 Proceedings, December 2003.

[1.54] H. Takeuchi, E. Quevy, S. Bhave, T.-J. King and R. Howe, "Ge blade damascene process for post-CMOS integration of nanomechanical resonators," IEEE Electron Device Letters, Vol. 25, No. 8, pp. 529-531, 2004.

[1.55] E. Quevy, S. Bhave, H. Takeuchi, T.-J. King and R. Howe, "Poly-SiGe high frequency resonators based on lithographic definition on nano-gap lateral transducers," Solid-State Sensor and Actuator Workshop, Hilton Head-SC, pp. 360-364, 2004.

[1.56] M.A. Eyoum, "Fabrication of a Floating Electromechanical Systems-Gyro using SiGe MEMS technology," DARPA Final Project Report.

[1.57] M.A. Eyoum, N. Hoivik, C. Jahnes, J. Cotte, X. Liu, "Analysis and Modeling of Curvature in Copper Based MEMS Structures Fabricated Using CMOS Interconnect Manufacturing Technology","12<sup>th</sup> International Conference on Solid-State Sensors and Actuators (Transducers 05), June 2005.

# Chapter 2

# Low Contact Resistance Si<sub>1-x</sub>Ge<sub>x</sub> MEMS Technology

## 2.1. Motivation

Depending on the application, it is often desirable to fabricate the MEMS structures directly on top of the CMOS circuitry, in order to achieve a high performance "Post-CMOS" MEMS integrated technology. Direct deposition of micromachined structures onto metallized films will result in a reduction of the parasitics associated with the MEMS to CMOS routing [2.1]-[2.3].