## Compositionality in Deterministic Real-Time Embedded Systems

Slobodan Matic

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-12 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-12.html

February 11, 2008

Copyright © 2008, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### **Compositionality in Deterministic Real-Time Embedded Systems**

by

Slobodan Matic

B.S. (University of Belgrade)

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

### GRADUATE DIVISION

of the

### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Thomas A. Henzinger, Chair Professor Edward A. Lee Professor Raja Sengupta

Spring 2008

The dissertation of Slobodan Matic is approved.

Chair Date Date

Date

University of California, Berkeley Spring 2008

### Abstract

#### Compositionality in Deterministic Real-Time Embedded Systems

by

Slobodan Matic

### Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Thomas A. Henzinger, Chair

Many computing applications, especially those in safety critical embedded systems, require highly predictable timing properties. However, time is often not present in the prevailing computing and networking abstractions. In fact, most advances in computer architecture, software, and networking favor average-case performance over timing predictability. This thesis studies several methods for the design of concurrent and/or distributed embedded systems with precise timing guarantees. The focus is on flexible and compositional methods for programming and verification of the timing properties. The presented methods together with related formalisms cover two levels of design:

- Programming language/model level. We propose the distributed variant of Giotto, a coordination programming language with an explicit temporal semantics - the logical execution time (LET) semantics. The LET of a task is an interval of time that specifies the time instants at which task inputs and outputs become available (task release and termination instants). The LET of a task is always non-zero. This allows us to communicate values across the network without changing the timing information of the task, and without introducing nondeterminism. We show how this methodology supports distributed code

generation for distributed real-time systems. The method gives up some performance in favor of composability and predictability. We characterize the tradeoff by comparing the LET semantics with the semantics used in Simulink.

- Abstract task graph level. We study interface-based design and verification of applications represented with task graphs. We consider task sequence graphs with general event models, and cyclic graphs with periodic event models with jitter and phase. Here an interface of a component exposes time and resource constraints of the component. Together with interfaces we formally define interface composition operations and the refinement relation. For efficient and flexible composability checking two properties are important: incremental design and independent refinement. According to the incremental design property the composition of interfaces can be performed in any order, even if interfaces for some components are not known. The refinement relation is defined such that in a design we can always substitute a refined interface for an abstract one. We show that the framework supports independent refinement, i.e., the refinement relation is preserved under composition operations.

> Professor Thomas A. Henzinger Dissertation Committee Chair

# Contents

| C                  | onten                          | ts            |                                                |     | i    |

|--------------------|--------------------------------|---------------|------------------------------------------------|-----|------|

| Li                 | st of l                        | Figures       |                                                |     | iv   |

| Li                 | st of '                        | <b>Fables</b> |                                                |     | vii  |

| A                  | cknov                          | vledgen       | ients                                          |     | viii |

| 1                  | Intr                           | oductio       | n                                              |     | 1    |

|                    | 1.1                            | Motiva        | ation                                          |     | 1    |

|                    | 1.2                            | Comp          | osable Code Generation for Distributed Systems |     | 5    |

|                    | 1.3                            | Comp          | onent Resource Abstraction and Tradeoffs       |     | 9    |

|                    | 1.4                            | Interfa       | ace-based Formalisms for Real-time Components  |     | 12   |

|                    | 1.5                            | Thesis        | Organization and Contributions                 | • • | 17   |

| 2                  | Con                            | ıposabl       | e Code Generation for Distributed Giotto       |     | 19   |

|                    | 2.1                            | Introd        | uction                                         |     | 19   |

|                    | 2.2                            | Giotto        |                                                |     | 24   |

|                    | 2.3                            | Comp          | osable Design with Giotto                      |     | 30   |

|                    | 2.4                            | Timin         | g Interfaces                                   |     | 36   |

| 2.5 Implementation |                                | mentation     |                                                | 40  |      |

|                    | 2.6 Compositional SCC Analysis |               | ositional SCC Analysis                         |     | 42   |

|                    |                                | 2.6.1         | Giotto-Generated Distributed SCC               |     | 42   |

|                    |                                | 2.6.2         | Formal Distributed SCC Semantics               |     | 46   |

|                    |                                | 2.6.3         | Interface Compliance and Time Safety           |     | 48   |

|   |      | 2.6.4                                           | Distributed Code Generation Correctness | 52   |  |

|---|------|-------------------------------------------------|-----------------------------------------|------|--|

|   | 2.7  | Conclu                                          | usion                                   | 56   |  |

| 3 | Con  | iponent                                         | Resource Abstraction and Tradeoffs      | 58   |  |

|   | 3.1  | Introdu                                         | uction                                  | 58   |  |

|   | 3.2  | Multir                                          | ate Task Programs                       | 61   |  |

|   | 3.3  | Task C                                          | Group Abstraction                       | 65   |  |

|   |      | 3.3.1                                           | Independent Task Set Abstraction        | 65   |  |

|   |      | 3.3.2                                           | Intragroup Task Precedence Abstraction  | . 67 |  |

|   | 3.4  | Distrib                                         | outed Task Precedence Abstraction       | 71   |  |

|   | 3.5  | Hierar                                          | chical Intergroup Abstraction           | . 76 |  |

|   | 3.6  | Conclu                                          | usion                                   | . 84 |  |

| 4 | Inte | Interface Formalism for Real-time Components 86 |                                         |      |  |

|   | 4.1  | Introdu                                         | uction                                  | 86   |  |

|   | 4.2  | Real-T                                          | Time Components                         | 91   |  |

|   |      | 4.2.1                                           | Resource Model                          | 91   |  |

|   |      | 4.2.2                                           | Task Group Composition                  | . 93 |  |

|   | 4.3  | Task S                                          | equence Interfaces                      | . 96 |  |

|   |      | 4.3.1                                           | Informal Description                    | . 96 |  |

|   |      | 4.3.2                                           | Interface Algebra                       | 101  |  |

|   | 4.4  | Real-T                                          | Time Component-Based Design             | 107  |  |

|   |      | 4.4.1                                           | Incremental Design                      | 107  |  |

|   |      | 4.4.2                                           | Independent Refinement                  | 109  |  |

|   | 4.5  | Task C                                          | Graph Interfaces                        | 111  |  |

|   |      | 4.5.1                                           | Component Model                         | 113  |  |

|   |      | 4.5.2                                           | Interface                               | 117  |  |

|   |      | 4.5.3                                           | Interface Algebra                       | 120  |  |

|   |      | 4.5.4                                           | Interface Algebra Properties            | 127  |  |

|   | 4.6  | Conclu                                          | usion                                   | 138  |  |

| 5 | Con  | clusion                                         | s and Outlook                           | 140  |  |

## Bibliography

# **List of Figures**

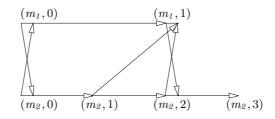

| 2.1  | Audio mixer Giotto program $G_A$                                                               | 25 |

|------|------------------------------------------------------------------------------------------------|----|

| 2.2  | Data dependency graph for the program $G_A$                                                    | 25 |

| 2.3  | Additional mode for the Giotto program $G_A$                                                   | 27 |

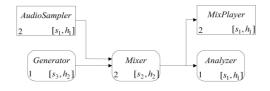

| 2.4  | E code blocks for the program $G_A$                                                            | 28 |

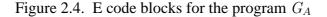

| 2.5  | S code blocks for the program $G_A$                                                            | 29 |

| 2.6  | E code modules for the program $G_A$ compiled by Alg. 1 $\ldots \ldots \ldots$                 | 36 |

| 2.7  | Timing interface for the program $G_A$                                                         | 38 |

| 2.8  | <b>S</b> code modules for the program $G_A$                                                    | 40 |

| 2.9  | Cycle of the communication protocol [19]                                                       | 41 |

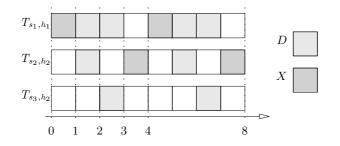

| 2.10 | Graph related to $\mathcal{P}_{s,h}$ for $G_A$ with additional mode $m_2$                      | 50 |

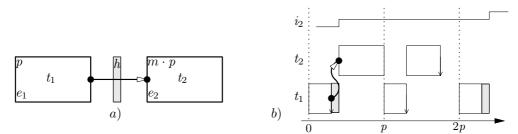

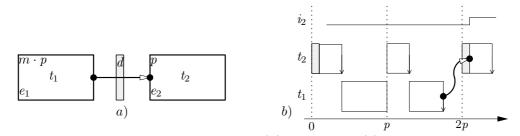

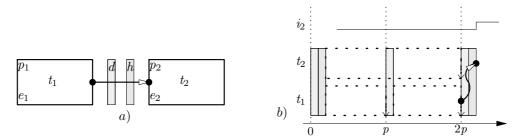

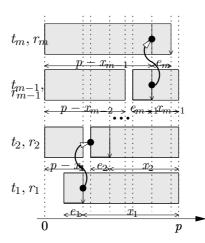

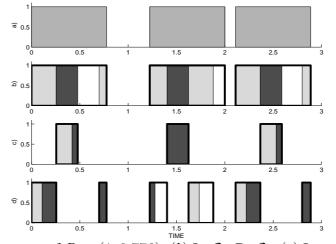

| 3.1  | RTW: fast to slow data transfer - $(a)$ task graph; $(b)$ task and signal timeline for $m = 2$ | 62 |

| 3.2  | RTW: slow to fast data transfer - $(a)$ task graph; $(b)$ task and signal timeline for $m = 2$ | 62 |

| 3.3  | LET data transfer - (a) task graph; (b) task and signal timeline for $p_1 = p_2/2 = p$         | 63 |

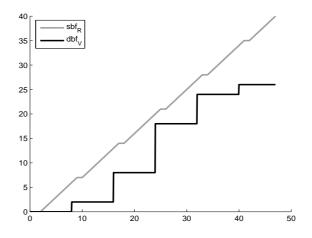

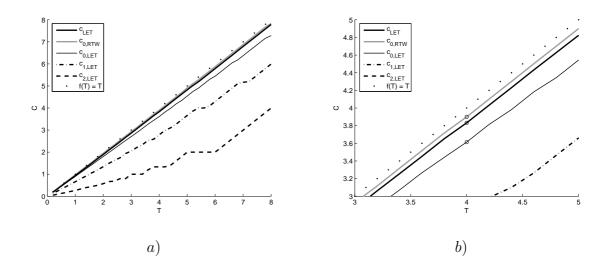

| 3.4  | Supply and demand bound functions                                                              | 66 |

| 3.5  | Hierarchical scheduling framework                                                              | 67 |

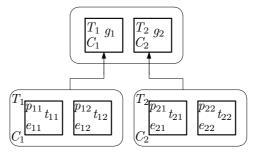

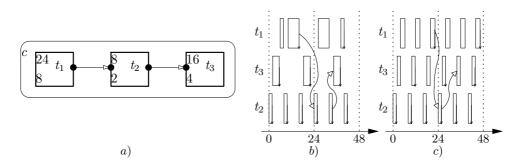

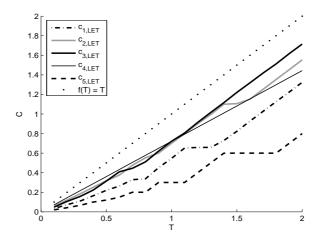

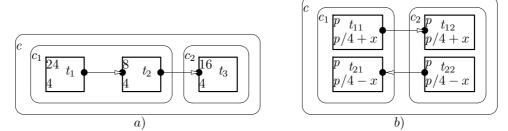

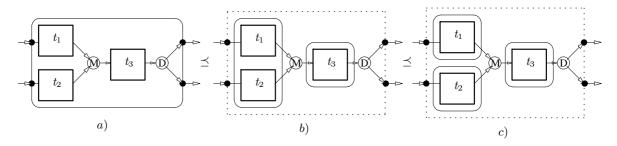

| 3.6  | $(a)$ Task graph; $(b)$ RTW schedule; $(c)$ LET schedule (RR schedule) $\ . \ . \ .$           | 69 |

| 3.7  | Abstraction functions for Fig. 3.6 $(a)$                                                       | 70 |

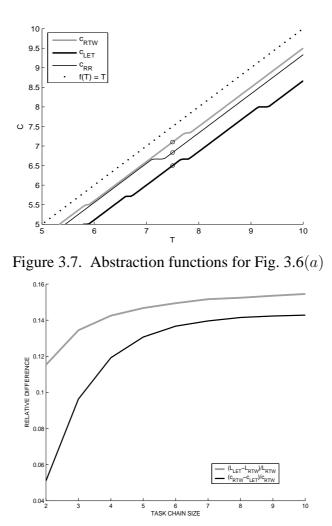

| 3.8  | Relative difference between RTW and LET semantics w.r.t. latency and composability             | 70 |

| 3.9  | Teleconferencing application task graph                                                        | 72 |

| 3.10 | Example for $m = 2$ resources: (a) task graph; (b) resource partition                          | 74 |

| 3.11 | Resource partition for Prop. 6                                                                                                                                                  | 75  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.12 | LET abstraction functions for Fig. 3.9                                                                                                                                          | 76  |

| 3.13 | Video stream hierarchical abstraction                                                                                                                                           | 77  |

| 3.14 | LET abstraction functions for Fig. 3.13                                                                                                                                         | 80  |

| 3.15 | (a) Instance of $R = (1, 0.776)$ ; (b) L: $\mathcal{G}_2$ , D: $\mathcal{G}_1$ ; (c) L: $t_{11}$ , D: $t_{14}$ ; (d) L: $t_{13}$ , D: $t_{12}$ (L=light, D=dark)                | 83  |

| 3.16 | Intergroup precedence abstraction examples for $(a)$ Prop. 8(2); $(b)$ Prop. 9(2)                                                                                               | 83  |

| 3.17 | (a) Component abstraction function for the hierarchical program in Fig.3.16( $a$ ); ( $b$ ) Detailed view                                                                       | 84  |

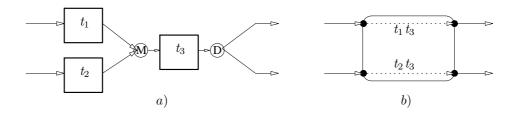

| 4.1  | (a) Task graph; (b) Component                                                                                                                                                   | 91  |

| 4.2  | Capacity functions for Tab. 4.1                                                                                                                                                 | 95  |

| 4.3  | Interface for single task sequence                                                                                                                                              | 97  |

| 4.4  | Interface for multiple task sequences                                                                                                                                           | 97  |

| 4.5  | Interface composition                                                                                                                                                           | 98  |

| 4.6  | Interface connection                                                                                                                                                            | 98  |

| 4.7  | Bursty functions for $t_1 t_2$ sequence $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                 | 99  |

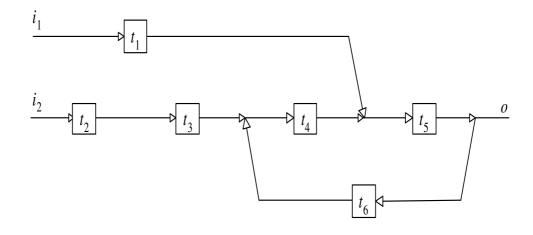

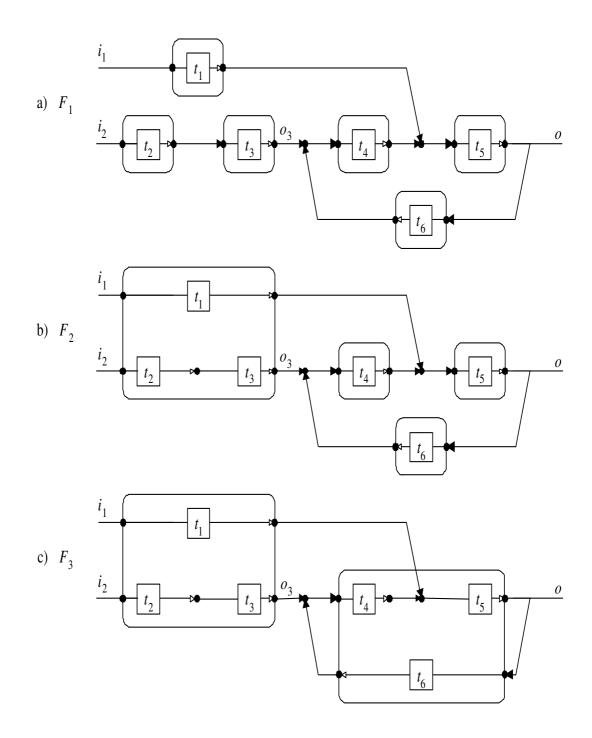

| 4.8  | (a) $F_a = F_{1,2,3} \oplus \{\pi_{13}, \pi_{23}\};$ (b) $F_b = (F_{1,2} \  F_3) \oplus \{\pi_{13}, \pi_{23}\};$ (c) $F_c = (F_1 \  F_2 \  F_3) \oplus \{\pi_{13}, \pi_{23}\}1$ | .00 |

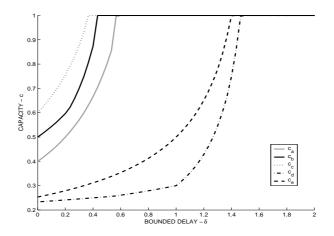

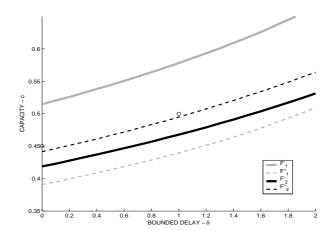

| 4.9  | Capacity functions from Tab. 4.2                                                                                                                                                | 01  |

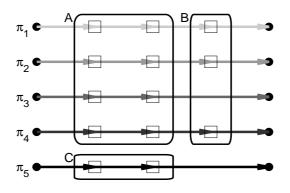

| 4.10 | $(F_A \  F_B \  F_C) \theta_{AB}$                                                                                                                                               | 08  |

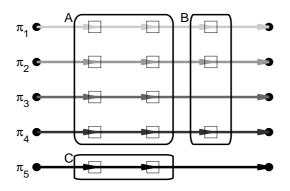

| 4.11 | Levels of service of $(F_A    F_B) \theta_{AB}$ and $(F_A    F_B    F_C) \theta_{AB} \dots \dots \dots \dots \dots \dots \dots \dots$                                           | 09  |

| 4.12 | $(F_a \  F_b \  F_C) \theta_{ab}$                                                                                                                                               | 10  |

| 4.13 | Levels of service of $(F_a    F_b) \theta_{ab}$ and $(F_a    F_b    F_C) \theta_{ab}$                                                                                           | 10  |

| 4.14 | Capacity functions for $F'_1, F''_1, F''_2, F''_2$                                                                                                                              | 12  |

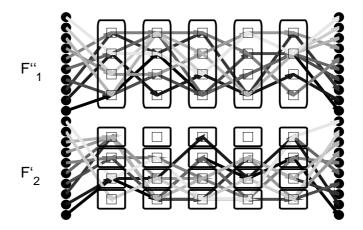

| 4.15 | $F_1'' \  F_2' \preceq F$                                                                                                                                                       | 12  |

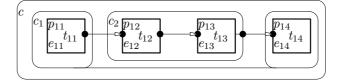

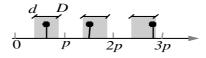

| 4.16 | Periodic event model with jitter and phase                                                                                                                                      | 15  |

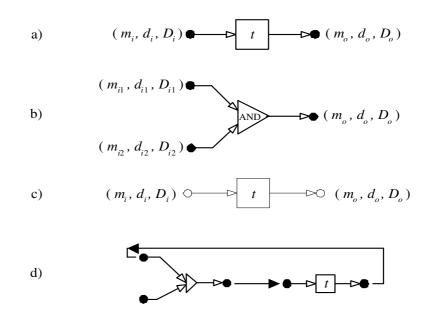

| 4.17 | Simple graph components with port event models                                                                                                                                  | 16  |

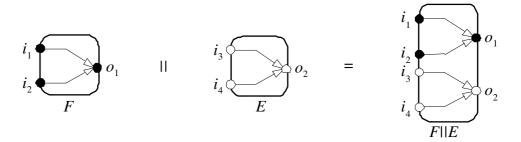

| 4.18 | Interface composition operation for graphs                                                                                                                                      | 20  |

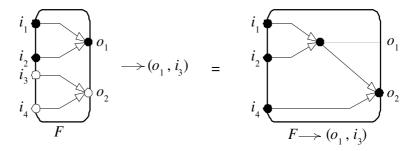

| 4.19 | Interface connection operation for graphs                                                                                                                                       | 21  |

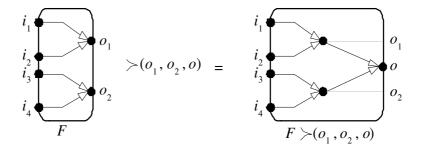

| 4.20 | Interface join operation for graphs                                                                                                                                             | 23  |

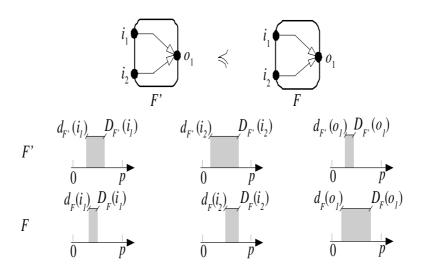

| 4.21 | Interface refinement relation for graphs                                                                                                                                        | 27  |

| 4.22 | Example task graph                                                                                                                                                              | 37  |

| 4.23 | Independent refinement | for the task gr | aph in Fig. | 4.22 | <br>139 |

|------|------------------------|-----------------|-------------|------|---------|

|      |                        |                 |             |      |         |

# **List of Tables**

| 3.1 | Example teleconferencing application data                 | 72  |

|-----|-----------------------------------------------------------|-----|

| 4.1 | Temporal interface and weet's for tasks in Fig. 4.1 $(a)$ | 94  |

| 4.2 | Interface refinement                                      | 100 |

| 4.3 | Task data for robotic application                         | 108 |

### Acknowledgements

For every ailment under the sun, There is a remedy, or there is none; If there be one, try to find it; If there be none, never mind it.

Mother Goose rhyme

My coming from troubled but revived Serbia, only few weeks before September 11th, was a departure from the safety of a familiar environment and the only way to become aware of one's own virtues and vices. One better drown learning to swim than spend the entire life sitting on the shore watching ships pass by. No doubt, the University of California at Berkeley and its EECS Department were offering much more than one can chew. Professors, students and researchers striving to live up to their potential while being occupied with intellectual feats and scholarly combats. And Ruth Gjerde, who listens to students attentively, nods with compassion, and navigates them through administrative mazes. Living in the International House Berkeley for three years reinforced my will to understand both other cultures and my own culture through the other's perspectives. Serbia is one of those places located on the cusps of a few cultural divides, and thus challenged after every major shift of power in the world. I am grateful to all the people, on all sides of all divides, who ever felt the need or even struggled to keep communication open while standing up for their own principles.

This thesis is the result of research under the guidance of Prof. Thomas Henzinger. There is no memory of working with him more vivid than the time spent in problem solving discussions. And these have all the potential to be fruitful. Beforehand, there is just enough pressure put upon a student to focus and come prepared. During a discussion, the exchange of arguments is conducted almost with a belief that the most important problem in the world is being unraveled. Prof. Henzinger looks absorbed in the problem as if there were no other meetings waiting. And each time a step forward, no matter how small, is being taken. Afterwards, the student is encouraged even to go risky and remains full of hope, at least until the next meeting. Some argue that, in research, feeling confused is essential to progress. I always admired Prof. Henzinger's fortitude to feel lost at first, only to be able to regroup on the spot and reap the results a few moments later. And I can clearly see the marker in his hands, coming back and forth to the whiteboard, on and on, while he is thinking out loud and recollecting his thoughts before he starts to write. I am thankful to him for sharing his ideas, intuition, vision and work ethic.

When Prof. Henzinger decided to move to Switzerland, he generously offered his students either to come with him and work at the EPF Lausanne, or to stay at and get the degree from UC Berkeley, or to do something in between. I have never regretted choosing the third option and have only benefited from both environments and his continuing support. Incidentally, if it hadn't been for him, I would have never had a chance to come close to the ominous but so beguiling north face of Matterhorn. I cherish those paper deadline moments when Prof. Henzinger calls me in Berkeley at 1am Europe time and comments on everything from the definite article usage in English language to the cogent reformulation of propositions. And I also never forgot the positive appraisal he gave after my first EM-SOFT presentation, knowing what burden for me public speaking could be at that moment. He has this delicate sense to know when to show his laissez-faire attitude and when to push a student in a certain direction. A good advisor has to help students both accept the fact that they may not be the best and develop the belief that they can still do well and keep maturing if they work hard. I am not sure whether Prof. Henzinger agrees with the simple yet often elusive message that the verses of the rhyme given above convey, but working with him helped such a sentiment become closer to my mind.

All research for this thesis was done within the Center for Hybrid and Embedded Software Systems. Around Cory Hall, and the Donald O. Pederson Center in particular, I got to know and interact with so many fascinating people, and I feel obliged to keep valuable memories of them all. Unfortunately, due to the inevitable limits of human interaction, for most of them I only scratched a bit of what they have to offer. Prof. Edward Lee used to advise me even before he kindly accepted to be my Berkeley co-advisor. Not only are his advanced material lectures smooth as silk, but he emanates a tremendous passion for knowledge and discovery. He seems so open to appreciate other people's work, integrate it with his own and already known research, and pass it to others. Towards research he almost comes as playful, clearly demonstrating how joy of research often means the joy of truly understanding ideas and concepts. I will remember Prof. Christoph Kirsch, a postdoc in my early days at Berkeley, for helping me define problems, putting up with my ideas, and initially serving as an interpreter between Prof. Henzinger and me.

With my office mates, Krishnendu Chatterjee and Arindam Chakrabarti, I shared much more than piles of papers, office commandments or courteous talk. That blissful Yosemite trip all with its 270° car rotation accident comes to mind. I find disheartening that, despite good will and intention, we did not get to work on a problem together, and do hope we somehow correct this in future. Krishnendu, so breezy yet engrossed, so "never do anything" yet weeks ahead of all deadlines, so self accomplished yet without a breath of arrogance. With Arindam I spent countless hours in social and economic discussions, often not knowing what stand Arindam would take in an argument and thus enjoying every second of it even more. I am thankful to him for disturbing my narrow perception of the role of the free market. Rational people may reasonably disagree on a matter, but despite that, it always seemed that both of us yearned to share those daily stories that had captivated us. I do realize, sadly, that one is offered only few lifetime opportunities to make such a meaningful connection with a friend.

I hope never to forget what, while staying in Berkeley, I learned to deem very precious: mid-afternoon fog rolling over the northern crest of Berkeley Hills, the Bridge and its symbolism, reflection of Alta Peak over Pear Lake in Sequoia National Park, small collection of Giacometti's sculptures in San Francisco Museum of Modern Art, homeless old lady that I kept seeing in the middle of the night on the corner of Telegraph and Channing, Bay Area citizens' activism, KGO 810 news talk and Gene Burns' commentary, Aspan Dahmubed's April Fools' Day "love" letter, soft and distant sounds of Sunday 6pm Campanile concerts and swarms of students around Sather Gate at noon.

I revere my parents, Milena and Milivoje, for empowering me to accept immaterial wealth and values, and for embedding me with moral virtues of hard work and diligence. I salute them hoping they can hear the message that I am still on track of the dream they had for me (Slobodan - the one who is free, Serbian). My siblings, Radina and Ljubisa, are the foremost ones to follow example of and permanent sources of both benevolent critique and motivation. Living with all of them bestowed upon me a unique blend of soulful empathy and existential felicity. Throughout these years I constantly felt frustrated for not being able to explain them exactly the relevance of the research problems I was working on. Therefore, although I know they always stood by me, it somehow feels not right to say this thesis is devoted to them. I would rather now pledge my word that I shall devote more time to them in future. My work was, however, worth their sacrifice of being far away from me. That they should have no doubt about. No matter how (in)significant this work may be in the grand scheme of things, it means so much to me. I feel very fortunate.

## Chapter 1

# Introduction

## **1.1 Motivation**

Embedded computing systems are nowadays common in most spheres of life. In fact, as popular definition suggests, everywhere where computation is subject to physical constraints. It is estimated that an average American comes into contact with about a hundred embedded computers per day, and that by the year 2010 software for embedded computers will account for 90% of all software being written. The design of such a system asks for a specified behavior to be mapped on a computing platform under certain constraints. In the application domains such as automotive, mechatronics, and multimedia, power consumption and size constraints are commonly not of the highest concern. Instead, *time related constraints* such as latency, deadline, throughput, response-time predictability are required by specification. For instance, in safety-critical systems the deterministic and timely response is often required for fault-tolerance. A common way to achieve it is through replica determinism that demands the redundant system nodes to take the same decision at about the same time.

Lee observes in [49] that time is not present in the prevailing computing and network-

ing abstractions used to design embedded systems. Unfortunately, this is true not only for hardware components, but also for software components such as operating systems, middleware concepts, and even design tools. In fact, the vast majority of dynamic or virtual features designed to increase the average-case performance have detrimental effects on *timing predictability*. Moreover, there are common examples in which a decrease of the average-case latency results with an increase of the worst-case latency. As Ziegenbein et al. note in [84] with respect to multiprocessor scheduling anomalies, in some cases the bestcase performance needs to be considered simultaneously. In general, time predictability is defined as the difference between estimated upper and lower bound of an event time, or as the difference between estimated and measured worst-case times. In this thesis we consider systems in which timing predictability is far more important than average performance.

Theile and Wilhelm notice that most cases of low timing predictability fall in two categories, *unknown external interference* and *limited analyzability* [73]. In the former case, low predictability is caused by the limited knowledge or unavailability of the system information relevant for the implementation. For instance, inter-arrival event times or the underlying scheduling mechanism are unknown during the system design. In the latter case, system components and their parameters are substantially known, but such a knowledge is too complex to be analyzed effectively. For instance, many microprocessor architecture techniques like out-of-order execution or cache replacement strategies are too complicated for the time bounds to be estimated. Thus, there are at least two ways to attack the timing predictability problem in embedded systems: reduce the sensitivity to unknown system information (see, e.g., [31, 81]), and, use architectures or implementation techniques that can be analyzed more easily ([38, 20]). The elements of both strategies can be found in solutions for the problems we address in this thesis.

Both [49] and [73] analyze system architecture layers pertinent to time determinism. [73] lists four layers: hardware architecture (includes all design aspects below the instruction set), single task software development (code synthesis, intratask analysis and optimization tools), task level (scheduling, shared resources, intertask synchronization), and distributed operation (distributed resources, end-to-end deadlines). In this study we focus on the methods addressing the two uppermost layers in this classification.

The step in the design process during which system performance, including power and timing, is validated against its specification is called *performance verification*. This step is often performed simultaneously with design-space exploration. According to a recent Embedded Market Forecasters [21] analysis, one quarter of embedded system designs missed the project schedule by at least 50%, about one third missed at least 50% of functional specifications, and more than 70% missed performance specifications by at least 30%. As discussed in the International Technology Roadmap for Semiconductors [66], the performance verification is already named as one of the top three issues in system-on-chip design.

The current industrial practice in performance verification is almost exclusively limited to (cycle-true) simulation and prototype testing. The examples include Seamless [55] in system-on-chip and AutoBox [18] in automotive domains. Even though simulation often seems viable for functional verification it is less so for the validation of performance, in particular, timing. Two major reasons are often quoted. The corner-case simulation vectors that result in worst-case performance are often not intuitive and, thus, very difficult to find, which makes the simulation procedure very time-consuming. Second, these methods require executable code, which can often be provided only in the later stages of design.

On the other hand, formal performance validation methods are yet to get significant attention from industry. The tools that do exist are typically only applied to individual component analysis, because system-level heterogeneity and complexity are still difficult to capture precisely in most formalisms. In principle, formal timing analysis should give both bounds for critical scenarios and the corner-case vectors that produce the scenario. Also, formal performance analysis seems suitable for design-space exploration since it runs considerably faster than simulation. Most of existing methods of formal timing analysis fall in two categories, *code execution time* analysis and *resource sharing* analysis. The former methods are based on program path analysis and cycle-true processor modeling, and the latter on the research in scheduling for real-time operating systems. Notable industry-level examples are tools aiT [1] for C-code worst-case execution time analysis, and RapidRMA [74] for rate monotonic fixed priority scheduling.

Beside the fact that the applications are becoming more complex in the number, character and interaction of consisting components, what makes the timing determinism in embedded systems specific and less tractable? Up until recently, in traditional hardware design, system timing was guaranteed by hierarchical composition of individual hardware subsystems. This was possible since the component control was mostly single threaded. However, the reactive character of embedded software requires preemption and corresponding scheduling strategies. It is well-known (see, for instance, the work of Richter et al. [62]) that preemptive and time-driven scheduling introduces timing dependencies between components that are functionally independent. Recent system-on-chip designs use networks to connect multiple programmable processor cores with specialized hardware subsystems. Optimization of performance in such systems, e.g. optimization of power consumption, requires component specialization which increases system heterogeneity. Heterogeneous platforms, on the other hand, add to the problem complexity through combined effects of different scheduling strategies needed for different components. If distributed embedded systems are considered additional resource sharing is involved for communication, often with event buffering and bursts. All these factors render standard approaches to resource sharing ineffective.

Embedded systems are complex as a whole, but very often consist of smaller modules minimally interacting with each other. Such a structure makes embedded systems amenable to *component-based design*. This approach provides a means for decomposing a system into components, enabling the reduction of a complex design problem into multiple simpler design problems. Thus, in contrast to holistic methodologies, in this approach there is no

need to perform global analysis for every system configuration. It is often argued that, as the system complexity increases, component "cut-and-paste" methodologies are the only way to reach design productivity, because designers must work at higher levels of abstraction, reusing already designed and verified components.

Heterogeneous component-based frameworks (e.g. Ptolemy [48], Metropolis [25], UML [17]) are currently primarily used for functional verification and for performance analysis they need to be extended with analytical models. This is important because in component-based designs it is mostly the case that only local performance problems have the potential to impact other parts of the system. As noted in [62], functional problems are typically confined because of the practice to modularize functions such that most interdependencies are localized. However, there is no simple performance modularization, since performance interdependencies are introduced even between functionally independent processes.

This thesis studies several methods for the component-based design of systems with precise timing requirements. The focus is on formal flexible and scalable methods for programming and verification of timing properties. We address issues such as models of computation, design principles, qualitative properties of composition, and performance/predictability/efficiency tradeoffs. In the following sections we describe the problems with more details, briefly explain our solutions, and review the related work.

# 1.2 Composable Code Generation for Distributed Systems

According to Frischkorn in [22], by 2015 up to 40% of the costs of an automotive vehicle will be driven by electronics and software. About 60% of all development costs for a car electronic control unit will be related to software. In addition, while the number of pro-

cessors is expected to level in the range 60-70, the growth rate of software functions will be 300%. This is closely related to one of the goals of Autosar [3], a huge project in automotive industry: to decouple growth rate of number of functions from growth rate of number of electronic components. Similar trend exists in avionics software, where previously each control subsystem had its own dedicated resource, whereas new solutions increasingly offer a common computing platform for multiple functions.

Clearly, software integration issues will play the major role in design of such distributed control systems. Note that in standard design techniques, e.g. in those that use simulation for performance validation, the design errors often show up only during system integration. In addition, different software parts are often developed by different suppliers. Thus, the integrator should also have a freedom in choosing between in-house and externally developed components. In the Autosar project, the description of software components, their interfaces, resource needs and network topologies are based on Unified Modeling Language, a generalized specification language for object modeling. In this thesis we address similar issues by using a coordination language Giotto [31] extended with suitably defined component timing interfaces.

There exists a vast literature on synchronous-reactive design and a part of it targets distributed deterministic systems (see, for instance, the works of Benveniste and his collaborators [5, 6, 4]). This methodology is primarily successful at the specification level. In globally synchronous specifications, parallel components are assumed to execute at exactly the same points in time enforced by perfect clocks. Also, execution and communication are assumed to be timeless. Synchronous reactive programs written in Lustre have been compiled globally for distributed real-time systems [10], but this approach of Caspi et al. resolves underlying scheduling problems through integer linear programming, a method that is not compositional. Two often quoted problems that prevent synchronous specifications to scale well to distributed implementations are large variance in component computation or communication times and the difficulty of maintaining a global notion of time. To address

the former problem the clock typically has to run as slow as the slowest system component. In addition, in a distributed implementation, the synchronous communication lines between system components are often replaced with asynchronous ones and designers have to insure that such a composition does not change the semantics. The desynchronization procedure introduced by Benveniste et al. in [5] is a formal technique to replace the synchronous communication lines with unbounded buffers. The procedure has been applied from loosely time-triggered architectures [6] to traffic signal control systems [80].

On the other hand, the global timing in a properly implemented distributed synchronous system can be predictable and fault-tolerant, although such a design often becomes inefficient. In fact, most software architectures and communication protocols used in safetycritical distributed real-time systems are time-triggered, i.e., all actions are initiated by temporal events that follow a global statically computed schedule. As argued by Kopetz et al. in [45, 44], such conservative designs attempt to avoid nonfunctional dependencies between components, and thus, support independent verification of each component. The time-triggered approach is preferred for its compositionality, but it becomes inefficient with increasing system complexity, especially if the network traffic is irregular. According to Richter et al. [62] it results in larger buffer size requirements, smaller utilization factors and larger power consumption. This overhead often drives designers towards asynchronous or event-triggered solutions. Some recent solutions use global time synchronization but support event-triggered processing, where the schedule unfolds dynamically during runtime, depending on the occurrences of different events. For instance, to preserve discrete-event model semantics in such a setting Zhao et al. [81] develops theoretical concept of relevant dependency. However, distributed Giotto can be thought of as purely software-based timetriggered architecture. Consequently, in our research on flexibility in software integration the focus is not on performance parameters.

**Thesis Work.** We present a compositional approach to the implementation of hard real-time software running on a distributed platform. We explain how several code suppli-

ers, coordinated by a system integrator, can independently generate different parts of the distributed software. The purpose of our effort [34, 36, 35] is to provide the application programmer with a programming interface that hides most of the implementation details (e.g. scheduling, handling of shared resources), but provides useful services (e.g. component communication and synchronization).

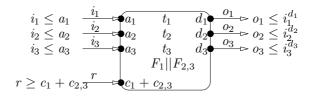

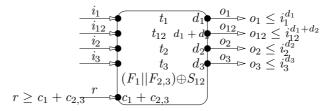

The task structure, interaction, and timing is specified as a Giotto program. Giotto is an example of a methodology based on a restricted model that attempts to reduce the sensitivity of unknown system information such as task execution time. A Giotto program executes a periodic set of LET (Logical Execution Time) tasks and the set of tasks, or their periods, may change whenever a Giotto mode switch occurs. Instead of just a deadline, a LET task has a release and a termination time: the release time specifies the exact time at which the task inputs are made available to the task; the termination time specifies when the task outputs become available to other tasks. Therefore, the times when a LET task reads and writes data are decoupled from the task execution. The LET of a task is always non-zero. This allows us to communicate values across the network without changing the timing information of the task, and without introducing nondeterminism. Thus, LET tasks can be replaced and composed without modifying their behavior or timing.

We demonstrate how Giotto can be implemented on a distributed platform by distributed compilation with little global coordination. Each supplier is given a part of the Giotto program and a timing interface, from which the supplier generates task and scheduling code. The timing interface specifies the time slots that can be used by the supplier for computation on the hosts, and the time slots that can be used by the supplier for communication over the network. The integrator then checks, individually for each supplier, in pseudo-polynomial time, if the supplied code complies to the timing interface and meets, on the given hardware, the release and termination times specified by the Giotto program. If all checks succeed, then the supplied software parts are guaranteed to work together and implement the original Giotto program. We demonstrate the feasibility of the approach by a prototype implementation.

A supplier may be replaced by another one, and as long as the code produced by the new supplier complies to its component specification and timing interface, it will work together properly with all other code in the system. Likewise, if new functionality is added to the system, say by adding a new supplier, as long as the new software passes the two checks (interface compliance and time safety), it will not change the behavior (neither functionality nor timing) of the original system in any way. The advantage of our approach lies in the fact that the two checks can be performed automatically, and the system integrator need not rely exclusively on testing to see if the upgraded system behaves correctly.

## **1.3** Component Resource Abstraction and Tradeoffs

A general methodology for temporal protection in traditional real-time systems research is the resource reservation framework studied, for instance, by Lipari [51] and Almeida [2]. The idea is that each task, or a component of tasks, is assigned a server that is reserved a fraction of the processor available bandwidth: if a task tries more than it has been assigned, it is slowed down. This way one can isolate the unpredictability of execution times of different tasks or streams of tasks from each other. In such solutions, a failing component cannot influence the behavior of other components in the system, since there is a temporal isolation between components.

Recently, these methods were extended to hierarchical scheduling systems which consist of real-time components arranged in a scheduling hierarchy [56, 57, 61, 65]. This is a form of "divide and conquer" technique, where resource partitioning is performed over multiple levels. Each component consists of a real-time task workload and a scheduling policy for the workload. A resource is allocated by a higher to a lower scheduling level through a *scheduling interface*. The interface specifies the resource requirement from the lower level and the resource guarantee from the higher-level scheduler. A hierarchical scheduling framework should exhibit *separation* among levels, i.e., the interface should be minimal. Moreover, the main benefits of hierarchical scheduling arise if the framework is fully *compositional*, i.e., if properties established at the lower also hold at the higher level.

These methods demonstrate how to perform composition of components in a hierarchical scheduling framework, but do not address the problem of generating the timing properties of a component. Shin et al. [68] defines this problem as *abstracting* the collective real-time requirements of a component as a single real-time requirement. This single requirement should be a sufficient and necessary requirement for all the collective requirements of the component. Abstraction of the internal complexity of a task group into a single requirement is used to reduce scheduling difficulties in the hierarchical scheduling framework.

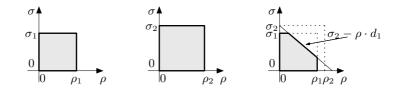

Early work in task group abstraction by Lipari [51] or Shin [68] considers the *periodic* resource model (T, C), a resource abstraction under which a component is guaranteed to get C units of the resource every T units of time. This research showed how to abstract a group of independent periodic tasks with EDF (Earliest Deadline First) or RM (Rate Monotonic) scheduling algorithms into a single periodic task characterized with a pair (T, C). The exact procedures were given in [51] for a component with RM scheduling, and in [68] for a component with EDF scheduling. The compositionality of the framework was demonstrated by combining multiple scheduling interfaces into a single higher-level interface. The work by Easwaran et al. [19] is specific because the component at the topmost level can select a value for period T that minimizes the resource demand of the system. The corresponding periodic resource model is exported to the operating system for scheduling and the chosen value for period is propagated to all the components in the system where resource capacities are given by the corresponding interfaces. The component model by Almeida et al. [2] refines the periodic resource model by including release jitter, deadlines earlier than periods and synchronization blocking. In addition, this is one of the rare efforts to study trade-offs between complexity and tightness of abstraction.

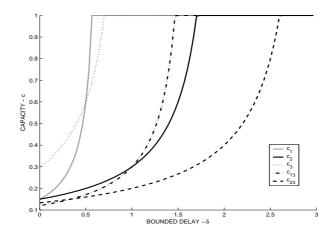

In [59] Mok et al. introduce another resource partition model, the *bounded-delay re*source model. The bounded delay resource model  $(c, \delta)$ , guarantees fraction c of the resource with at most  $\delta$  time units of delay. This model is suitable when different components aimed at the same resource have considerably different latency requirements. Later work [69] by Shin shows how to abstract a set of independent periodic tasks into a bounded-delay interface. They also show how to use the bounded-delay model together with the periodic model as scheduling interface models, i.e., they show how to abstract a set of periodic and bounded-delay tasks into a single periodic or bounded-delay task.

**Thesis Work.** We showed that the previous results ([68, 69]) can be extended for supporting interacting tasks with data dependencies. We assume that all applications that execute on the considered resources are specified in the conventional periodic *task* model with an underlying task precedence graph. We study the periodic *resource* model for hierarchical scheduling model in the presence of dataflow constraints between the tasks within a group (intragroup dependencies), and between tasks in different groups (intergroup dependencies) [53].

We consider two natural semantics for dataflow constraints, namely, RTW (Real-Time Workshop) semantics and LET (logical execution time) semantics. While RTW follows the semantics of real-time code generated from a Simulink environment ([71]), LET has been used in Giotto domain-specific language, as discussed above. The most important semantics difference between the two models is as follows. The RTW scheme transfers the output of a task as soon as the task completes execution. The LET scheme makes the output of a task available at the prespecified time, namely, at the relative deadline defined by the task period.

We show that while RTW semantics offers better end-to-end latency on the task group

level, LET semantics allows tighter resource bounds in the abstraction hierarchy and therefore provides better composability properties. This result holds both for intragroup and intergroup dependencies, as well as for shared and for distributed resources. In addition, for a suitable chosen composability metrics, we prove some bounds on the composability difference between the two models. Finally, we show that, in contrast to the RTW semantics, the LET semantics both exhibits separation between levels and is fully compositional.

# 1.4 Interface-based Formalisms for Real-time Components

Although the performance verification community has different techniques than the real-time systems community, the goals are often similar [83]: to achieve high productivity, designers must work at higher levels of abstraction, reusing already designed and verified components. The goal of abstraction is to be able to verify correctness using the abstract interface without implementation or prototype. Thus, in both communities, the validation task is decomposed into the *analysis* of individual processes for which formal analysis techniques are known and on the *composition* of the results in order to obtain system-level timing information. However, the methods they use differ in either the analysis, or the composition parts, or both.

A group of methods by Ernst and his group integrate local analysis with a global eventflow based analysis, typically using existing models and analysis techniques [40, 63, 29]. To avoid traps of simulation these methods do not consider each event individually, but abstract events to *event streams*. Activating events may be aperiodic by nature, e.g. alarms, or periodic with jitter, e.g. packets in a communication protocol. Even strictly periodic task activation can be seen as event-driven, since it is the result of the expiration of a timer. Event streams are represented by standard event models, and the corresponding compositional analysis methodology is based on the event propagation models. In most cases, the analysis requires only a few simple properties of event streams, such as event period, maximum jitter, or event burst. In such a context, global schedulability can be seen as flow-analysis problem for event streams that can be solved iteratively using event stream propagation. In principle, based on event stream manipulation one can identify worst-case scenarios, potentially even buffer overflows and missed deadlines as a result of transient overload.

In [40] the local analysis techniques are composed on the system level by connecting their input and output event streams. For such a compositional approach, it is required that the output event models of one component be compatible with the input event models of the connected components. Incompatible event models may also need to be connected by the overall application and communication structure. For instance, an aperiodic event model is to be connected to a periodic one. To overcome this problem certain transformation functions are defined and applied in order to adapt event models. In general, the method allows local scheduling results from the real-time systems research to be used, which is a major advantage over holistic analysis approaches such as the one by Pop et al. [60]. Another difference to the holistic approach is that the formal event stream equations are much better structured with respect to the architecture. The SymTA/S tool is based on this approach [29]. It supports heterogeneous architectures, complex task dependencies and context aware analysis, and it determines system-level performance data such as end-to-end latencies, bus and processor utilization, and worst-case scheduling scenarios. Furthermore, SymTA/S combines optimization algorithms with system sensitivity analysis for rapid design space exploration.

A similar compositional performance analysis approach is based on the *real-time calculus* by Thiele and his group [75, 11, 76, 72]. This approach is geared towards performance analysis of embedded and network processors and uses the event model representation known from the network calculus theory developed by Boudec et al. [7]. The work [75] by Wandeler et al. is the first research effort that formally combines the network calculus and interface design theories in the real-time context. Each component represents a task, so there is no abstraction of task groups into components. Also, the task model in [75] assumes independent tasks, so interface compatibility checking does not have to take into account dataflow constraints. Finally, they assume preemptive fixed-priority scheduling, where each component (task) is specified with a certain priority. The research in [76] extends this work for other scheduling algorithms such as EDF and polling servers, whereas [72] moves from static interfaces by introducing formalism that can adapt system guarantees according to the system environment.

This approach is not limited to a particular task set characterization (e.g. periodic task set) or to a particular resource model (e.g. bounded-delay model). In contrast, they use network calculus notions of upper and lower bound event arrival curves for event streams, and service curves for resource modeling. This generality comes with a price. Since the event stream models are not the standard ones, new scheduling analysis procedures for the local components have to be developed. So, the existing work in real-time system research cannot be reused. Furthermore, the complexity of the equations makes the approach less intuitive than some simple local techniques such as rate monotonic analysis. As often advocated, a system-level analysis, especially a compositional or hierarchical one, should be comprehensible to be successful.

**Thesis Work.** In the area of interface-based timing verification we present an assumeguarantee interface algebra for real-time components [37]. This approach is based on interface theory methodology [13, 14] by de Alfaro et al. In general, the input/output behavior of a system component is captured by an automaton. Two interfaces are compatible if there is a way to use them together such that their input expectations are met. Thus, the interface automaton of a composition is constructed by pruning all violating states from the product of the component automata. In particular, the timed interfaces theory [15] can be applied when timing of inputs and outputs are important. A timed interface is specified as a timed game between two players, representing the inputs and outputs of the component. However, in the results presented here, and since we always abstract events into a suitable event stream that can be represented by a simple predicate, the form of the interface is stateless, and thus the composition is much simpler. Our approach is also similar to the real-time interfaces approach of Wandeler et al. [75]. However, for the components we do not use general event and resource models, but only those for which effective resource abstraction results can be derived. Thus, we can extend and reuse some of the theory discussed in Sec. 1.3. The objective is to enable automatic, efficient, and flexible composition of such real-time interfaces.

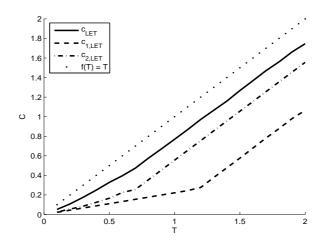

In the first problem we address in this area, a component implements a set of *task sequences* that share a resource. The arrival rate function bounds the number of task (sequence) requests in a given interval of time. We show how to abstract such a task group using the bounded-delay or periodic resource models. Then we consider such a task group as a part, i.e., a component, of a larger real-time system specified with a set of task sequences that define task precedence constraints.

Due to the task dependencies between different components, the interface cannot just contain resource constraints, but also dataflow propagation constraints. A component interface consists of an arrival rate function and a latency for each task sequence, and a capacity function for each shared resource. A capacity function defines a fraction of processing power that is reserved for the component, or, more generally, a resource partition model such as bounded-delay model. The interface specifies that the component guarantees certain task latencies depending on assumptions about task arrival rates and allocated resource capacities. Together with interfaces we formally define interface composition operations, and the compatibility and refinement relation. Interface sare yet unknown. In this case interface composition computes as new assumptions the weakest constraints on the unknown components that are necessary to satisfy the specified guarantees. For efficient and flexible composability checking two properties are important: incremental design and independent refinement. According to the *incremental design property* the composition of interfaces can be performed in any order, i.e., it is associative, even if interfaces for some components are not known. Note that resource abstraction procedures described in Sec. 1.3 and most of other approaches described in Sec. 1.4 are not associative. However, we prove that our interface algebra satisfies the incremental design property. The refinement relation is defined such that in a design we can always substitute a refined interface for an abstract one. We show that the framework supports *independent refinement*, i.e., the refinement relation is preserved under composition operations. Our algebra thus formalizes an interface-based design methodology that supports both the incremental addition of new components and the independent stepwise refinement of existing components.

Little previous work exists that considers compositional performance analysis in the presence of complex task dependencies that include cycles. However, this is an important problem in practice since nonfunctional dependency cycles are often introduced by communication sharing as noted by Richter et al. [62]. The research presented by Yen et al. in [78] or Goddard et al. [24, 23] are notable examples, but these are holistic methods in real-time tradition, that do not allow compositional analysis. Zhou et al. [82] studies causality interfaces for general dataflow model, but the approach is targeted towards deadlock detection, and does not include real-time properties. In the SymTA/S tool limited set of cyclic graphs is allowed [63] in the models. For instance, a cycle can have only one external input. The cycles are analyzed by iterative propagation of event streams until the event stream parameters converge or until a process misses a deadline or exceeds a buffer bound. The iteration process terminates because the event timing uncertainty grows monotonically with every iteration, but that typically ends in uncompatibility error rather than in a fixed-point solution that satisfies interface constraints.

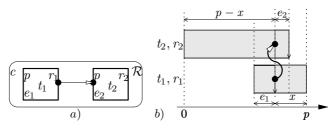

In the final part of the thesis we study interface-based verification of general task graphs, arbitrary directed graphs where each node represents a task, and each edge represents the data flow between tasks [54]. Since input degree of a node can be greater than one, a task may execute only after data is available on all input edges (AND type of task triggering). The graph is allowed to have cycles, i.e., we allow for cyclic functional dependencies between tasks. We assume that the primary inputs of a task graph are specified with event arrival curves that bound the number of task executions. In particular, we concentrate on periodic event models with jitter and burst. In order to avoid iteration problems of [63] one has to specify also phase information between events in different event streams. Therefore, our objective is to define the form of interface and interface operations that would enable flexible interface-based design similar to the case of task sequences. In this case, three operations are needed for construction of composite task graphs, the composition, connection, and join operations. Finally, we study requirements that enable the incremental design and independent refinement properties discussed above.

## **1.5** Thesis Organization and Contributions

We now present the organization of the thesis and the main results of each chapter.

• In Chapter 2 we present a compositional approach for the implementation of hard real-time software running on a distributed platform. We explain how several code suppliers, coordinated by a system integrator, can generate parts of the distributed software in a distributed manner. We present the algorithm that generates the necessary Giotto code and timing interface for each host and each supplier. We also present pseudo-polynomial checks for interface compliance (w.r.t. a timing interface) and time safety (w.r.t. the worst-case execution times of tasks), and formally prove the distributed Giotto compiler correct. The feasibility of the approach is demonstrated by a prototype implementation. A preliminary version of this Chapter appeared in [35].

- In Chapter 3 we first study the abstraction of a task group that executes on a single resource and with precedence constraints among tasks within the group (intragroup task precedences). We show the tightness difference in favor of the LET semantics. For the case of a task group distributed over several resources we characterize how large the gap in the tightness of abstractions between the two schemes, RTW and LET, can be. In the context of higher levels of the hierarchical scheduling framework, we allow for the task precedences among different task groups (intergroup task precedences). The LET semantics again results in tighter and simpler abstractions. In addition, and contrary to the RTW semantics, we show that the LET semantics enables a compositional framework with separation between levels. The results of this Chapter were published in [53].

- In Chapter 4 we first study real-time components consisting of task sequences [37]. We give procedure to obtain resource partition parameters for a group of aperiodic tasks given with arrival rates and deadlines. The right form of the interface and corresponding algebra are presented and discussed. We formally prove that the framework satisfies incremental design and independent refinement properties. The approach is then extended for the case of task graph components that include task cycles [54]. Due to the different event model a different interface algebra has to be defined. The two properties adapted to allow cycles are shown to hold even for this interface-based design methodology.

- Chapter 5 concludes the thesis and gives some pointers for future research. The relevant problems and concluding remarks are given at the end of each chapter.

## Chapter 2

# **Composable Code Generation for Distributed Giotto**

## 2.1 Introduction

In this chapter we suggest that the competing goals of *timely execution* and *compos-able design* can be achieved together by adopting a software solution that requires only basic hardware services such as clock synchronization and redundancy management. We base our work on the LET (*logical execution time*) paradigm, and the LET-based language Giotto, previously proposed as a software model that guarantees predictable real-time execution and at the same time supports portable, composable code [31]. The chapter demonstrates how Giotto can be implemented on a distributed platform by distributed compilation with little global coordination. In this way, Giotto offers a framework for the compositional design of hard real-time systems.

Giotto is a domain-specific language for control applications [31]. A Giotto program executes a periodic set of LET tasks, and the set of tasks, or their periods, may change whenever a Giotto mode switch occurs. Instead of just a deadline, a LET task has a *release*

and a *termination time*: the release time specifies the exact time at which the task inputs are made available to the task; the termination time specifies when the task outputs become available to other tasks. The task must start running, may be preempted, and must complete execution during its LET, which is the time from release to termination. Thus the times when a LET task reads and writes data are decoupled from the task execution. LET avoids race conditions, and thus ensures the predictable, deterministic execution of a set of realtime tasks. LET tasks can be replaced and composed without modifying their behavior or timing. Since LET is an abstract programming model, the compiler must ensure that the generated code satisfies the LET assumption. This can be achieved by compiling Giotto into schedule-carrying code (SCC) [35] for a pair of virtual machines: the E (embedded) machine mediates between tasks and the physical environment [32]; the S (scheduling) machine mediates between tasks and the CPU [35]. E code specifies when sensors and task inputs are read, and when actuators and task outputs are written; S code specifies when a task is executed on the CPU. We have implemented the E and S machine as part of a high-performance microkernel for real-time systems [42], and used Giotto to successfully implement flight control systems for model helicopters [30].

A Giotto program specifies the functional and timing behavior of a dynamic set of tasks, for example, the tasks of an automotive control system. Such a system is typically executed by an on-board network with several hosts (CPUs). Moreover, such a system is typically put together from several parts, which correspond to different control problems, for example, fuel injection and anti-lock brake control. While the different software parts may interact, they are often developed by different *suppliers*: the brake supplier will deliver its own software, etc. Furthermore, to optimize the use of computational resources, there need not be a one-to-one correspondence between hosts and suppliers. The contracting company, or *integrator* (e.g., the car manufacturer), then faces the challenge of putting together and maintaining the entire system. Using today's methodologies, a simple modification in the software of a single supplier may induce a series of modifications in the whole system.

For example, a change of timing attributes (e.g., task execution times) in one software component may cause the schedule of other components to change. We show how this problem can be avoided using Giotto.

We view the Giotto program as the overall system specification (timing and task interaction). Each supplier is given a part of the Giotto program with the charge to implement the corresponding tasks. This information can be regarded as a *component specification*. So that all supplied software parts will fit together, each supplier also receives timing information in the form of a *timing interface*. The timing interface specifies the time slots that can be used by the supplier for computation on the hosts, and the time slots that can be used by the supplier for computation over the network. From a component specification and a timing interface each supplier produces code. The integrator then checks that the produced code complies to the timing interface and meets, on the given hardware, the release and termination times specified by the Giotto program. The first check is called *interface compliance*; the second, *time safety*. Both checks are local for each piece of supplied code and can be performed in pseudo-polynomial time. If all checks go through, the integrator is assured that all supplied software parts fit together and correctly implement the original Giotto program (note that correctness includes the satisfaction of all real-time constraints).

The distributed implementation of hard real-time systems is a key challenge in modern control systems, especially in automobile (drive-by-wire) and aircraft (fly-by-wire) control. Much of the work in this area has been devoted to hardware-focused solutions, such as the time-triggered architecture [43], which guarantees hard real-time constraints across a distributed system by strict adherence to clock-synchronized networking protocols. The cost of such a solution is paid in terms of flexibility, and even recent efforts in the automotive industry (FlexRay, Autosar [70, 3]) require that all component processes, their dependencies, and their timing profiles be known in advance. Essentially, we build a fully software-based instance of the time-triggered paradigm. Instead of having the hardware and network protocol enforce all timing interfaces, each timing interface is enforced sepa-

rately by the compiler (during distributed code generation by the suppliers) and by program analysis (during code integration by the integrator). The LET assumption is crucial to this approach. The LET (release to termination) of a task is always non-zero. This allows us to communicate values across the network without changing the timing of a task, and without introducing nondeterminism, as long as the timing interface ensures that all values are available in time to meet all task release and termination times, and all sensor read and actuator update times. By contrast, the synchrony assumption used by other real-time languages [26] does not offer this flexibility, and hence an important approach to distributing synchronous programs is based on the Globally Asynchronous, Locally Synchronous paradigm [4].

We obtain the benefits of the time-triggered paradigm in terms of real-time assurance, and at the same time achieve a high degree of flexibility. For example, a supplier may be replaced by another one, and as long as the code produced by the new supplier complies to its component specification and timing interface, it will work together properly with all other code in the system. Likewise, if new functionality is added to the system, say by adding a new supplier, as long as the new software passes the two checks (interface compliance and time safety), it will not change the behavior (neither functionality nor timing) of the original system in any way. This is because interface compliance succeeds only if the original set of timing interfaces can accommodate an additional timing interface with sufficient capacity, and time safety succeeds only if the original set of hosts can accommodate the new tasks. The advantage of our approach lies in the fact that the two checks can be performed automatically, and the system integrator need not rely exclusively on testing to see if the upgraded system behaves correctly.

Previously, Giotto had only been compiled for single-CPU systems [33]. The contribution of this chapter is two-fold: we describe a methodology that supports (1) *distributed* real-time code generation for (2) *distributed* real-time systems. Multiple suppliers (1) can independently compile different parts of a Giotto program to run on a system of multiple CPUs (2). Because of the time-driven nature of our timing interfaces, (1) immediately enables (2) on clock-synchronized systems. Other approaches for (2), however, may not necessarily support (1); for example, synchronous reactive programs written in Lustre have been compiled globally for distributed real-time systems [10]. Aimed at (1) are scheduling techniques that address the problem of dividing tasks into groups, and scheduling tasks within groups [58, 68]: the challenge is to develop compositional schemes for resource partitioning such that each task group may be programmed as if it had dedicated access to the resource and may be tested for schedulability without global task knowledge. However, these techniques typically assume a single CPU and no interaction between tasks. In distributed real-time systems there are efforts [46] to define minimal but complete interfaces that link components together. In avionics software, where previously each control subsystem had its own dedicated resource, new solutions are proposed which offer a common computing platform for multiple functions; [64] presents requirements for the temporal partitioning of such a platform. The car manufacturers' and suppliers' perspectives on embedded software reuse are described in [28], which presents a general framework in which different software components can be classified according to their degree of reusability, albeit without considering real-time communication in detail.

**Outline of the Chapter.** In Sec. 2.2 we present a brief review of Giotto and introduce a running example that we will use throughout this chapter. In Sec. 2.3 we discuss the algorithm that generates from a given Giotto program virtual machine code (SCC) for each host and each supplier. In Sec. 2.4 we introduce timing interfaces and show how they can be composed. Sec. 2.5 describes our prototype implementation of distributed Giotto. In Sec. 2.6 we give the formal semantics of distributed SCC, we analyze distributed SCC generated from Giotto, present pseudo-polynomial checks for interface compliance (w.r.t. a timing interface) and time safety (w.r.t. the worst-case execution times of tasks), and prove the distributed Giotto compiler correct.

### 2.2 Giotto Language

We give a brief introduction to Giotto and refer to [31] for details. A simple example of a Giotto program  $G_A$  is shown in Fig. 2.1. For now ignore the distribution annotations given in the brackets to the right of the program. In this audio application a prerecorded PCMformat audio file is read, processed, analyzed, and reproduced by three real-time tasks. The *Generator* task synthesizes the digital audio samples of the sound that resembles the plucking of a string. This is done according to the Karplus-Strong algorithm [41], where the period of the task determines the pitch of the generated sound. The *Mixer* task merges the file samples with the synthesized samples amplifying the string pluck sound. The *Analyzer* task computes a short-time Fourier series of the mix sound.

A Giotto program begins with port declarations. A port is a typed variable. The set *Ports* is partitioned into the following four sets: a set *SensePorts* of sensor ports, a set *ActPorts* of actuator ports, a set *InPorts* of task input ports, and a set *OutPorts* of task output ports. The sensor ports include the integer-typed port  $p_c$ , a discrete clock. In Fig. 2.1 the sensor port *AudioSampler* represents a vector of audio file samples, the actuator port *MixPlayer* a vector of final waveform samples, and the task output ports *Spectrum*, *MixSound*, and *StringSound*, respectively, represent vectors of Fourier coefficients, mix samples, and string samples. The Fig. 2.2 shows the data dependency graph for the tasks (rectangles with rounded corners), the sensor, and the actuator.

Each sensor (resp. actuator) port p is read (resp. written) by a device driver dev[p]. Each task output port is double-buffered, i.e., it is implemented by two copies, a local copy that is used by the task only, and a global copy that is accessible to the rest of the program including other tasks. The copy driver copy[p] copies data from the local copy to the global copy of the task output port p.

Giotto has two kinds of computational activities, tasks and drivers. Tasks are released and their execution take time, while drivers are executed in logically zero time. A Giotto

| sensor                                                 |              |

|--------------------------------------------------------|--------------|

| AudioSampler uses dev[AudioSampler];                   | $[s_1, h_1]$ |

| actuator                                               |              |

| MixPlayer uses dev[MixPlayer];                         | $[s_1, h_1]$ |

| output                                                 |              |

| Spectrum uses copy[Spectrum];                          | $[s_1, h_1]$ |

| MixSound uses copy[MixSound];                          | $[s_2, h_2]$ |