# **Energy Efficient Wireless Transmitters: Polar and Direct-Digital Modulation Architectures**

Jason Thaine Stauth Seth R. Sanders

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-22 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-22.html

February 4, 2009

Copyright 2009, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# **Energy Efficient Wireless Transmitters: Polar and Direct-Digital Modulation Architectures**

by

Jason Thaine Stauth

B.A. (Colby College) 1999 B.E. (Dartmouth College) 2000 M.S. (University of California, Berkeley) 2006

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION  $\qquad \qquad \text{of the} \\ \text{UNIVERSITY OF CALIFORNIA, BERKELEY}$

Committee in Charge Professor Seth R. Sanders, Chair Professor Ali M. Niknejad Professor Paul K. Wright

Fall 2008

| The dissertation of Jason Thaine Star | ith is approved: |

|---------------------------------------|------------------|

|                                       |                  |

| Chair                                 | Date             |

|                                       |                  |

|                                       |                  |

|                                       |                  |

|                                       | Date             |

|                                       |                  |

|                                       |                  |

|                                       |                  |

|                                       | Date             |

|                                       |                  |

|                                       |                  |

University of California, Berkeley

# Energy Efficient Wireless Transmitters: Polar and Direct-Digital Modulation Architectures

Copyright 2008

Ву

Jason Thaine Stauth

#### **Abstract**

Energy Efficient Wireless Transmitters: Polar and Direct-Digital Modulation

Architectures

Ву

#### Jason Thaine Stauth

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Seth R. Sanders, Chair

Power consumption is an increasingly important issue in highly integrated wireless systems. While advances in semiconductor technology have driven continuous integration of features and services into portable devices, power consumption is now a major limiting factor on computational complexity and the ability to communicate over long distances. In portable communication devices, the wireless transmitter is often the dominant source of power consumption, such that in recent years there has been a major effort to improve the power efficiency of transmitter circuits, especially the power amplifier (PA). In addition to power consumption, it is now apparent that energy consumption is an important metric for transmitter circuits. Energy consumption more accurately predicts the battery life, especially when a portable system operates with a wide range of output power.

In this work, polar transmitter architectures are presented as a promising alternative to conventional Cartesian architectures. Traditional polar systems use dynamic modulation of the PA power supply to transmit amplitude information. This helps polar systems achieve higher average (energy) efficiency than Cartesian systems. Polar systems have suffered from drawbacks related to linearity, time-alignment of amplitude and phase signals, and power supply noise. Furthermore, the amplitude and phase paths require bandwidth significantly higher than the Cartesian I-Q basis vectors to represent the wideband polar representation of the wireless signal.

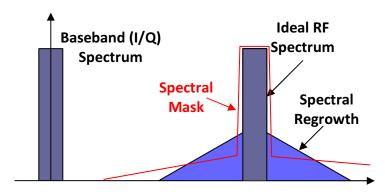

This work focuses on several contributions related to improving the operation of energy efficient polar transmitters. The first contribution is a power supply noise analysis framework for nominally linear power amplifiers. This analysis helps predict upconversion of supply noise to RF frequencies — a scenario that is likely in polar and envelope tracking supply-modulated transmitters. Supply noise upconversion can cause violation of the spectral mask and it is important to understand the underlying circuit mechanisms for this phenomenon.

A second contribution is an optimal operating strategy for hybrid switching-linear voltage regulators. These regulators are attractive for polar systems since they achieve the wideband, high-fidelity performance of a linear regulator with the power efficiency of a switching regulator. We show that past implementations of hybrid regulators could achieve higher efficiency with an optimized control objective. We use time-domain averaging to determine the optimum current for the DC-DC converter in the hybrid regulator. The optimized solution achieves substantially higher efficiency across the

output power range than the traditional solution. We develop expressions for optimum

efficiency as a function of characteristics of the envelope signal and the supply voltage

for the linear regulator.

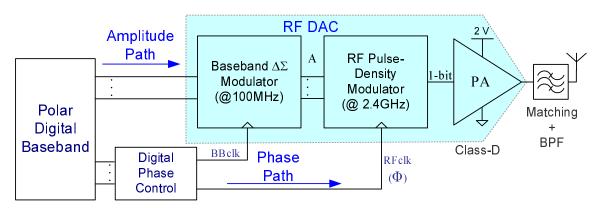

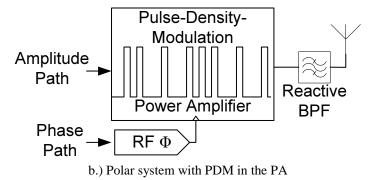

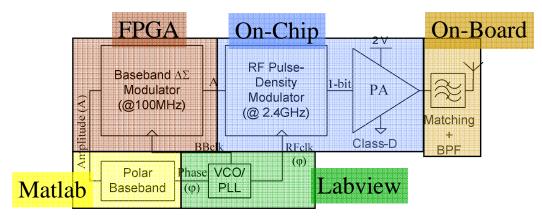

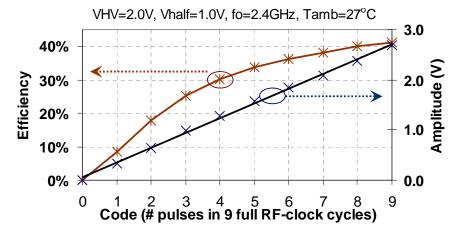

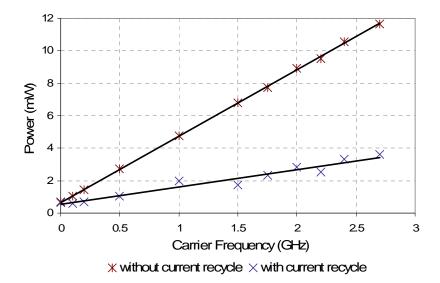

The final contribution is a digital-polar transmitter based on pulse-density modulation

of the RF carrier. Instead of using power supply modulation, the amplitude path is

controlled with a digital noise-shaping process. To reduce power consumption, noise

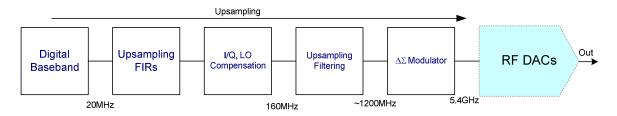

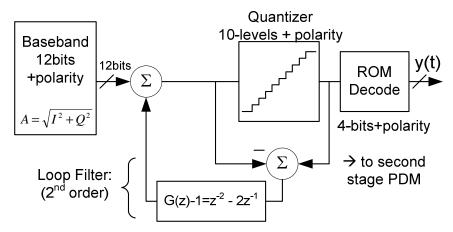

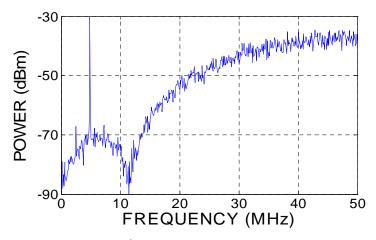

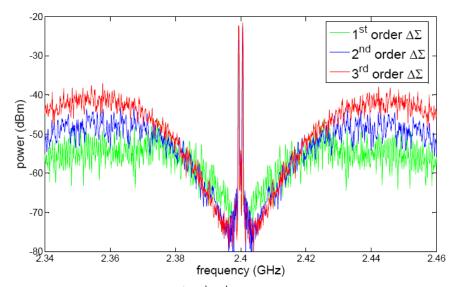

shaping is implemented in two stages: a baseband  $\Delta\Sigma$  modulator operating at 100MHz

and a programmed pulse-density modulator operating at 2.4GHz. A circuit

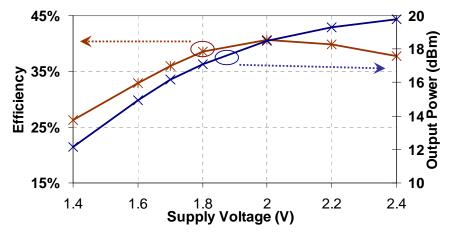

implemented in 90nm CMOS uses a class D PA to achieve up to 20dBm output power.

The system achieves peak efficiency of 38.5% at 2.4GHz including power of the PA

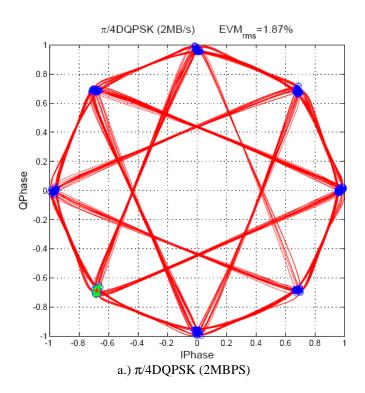

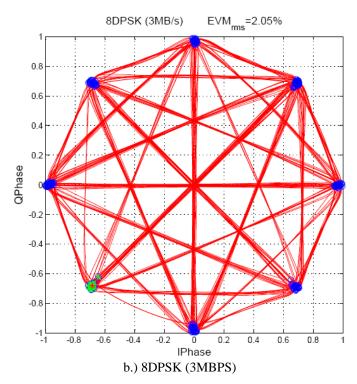

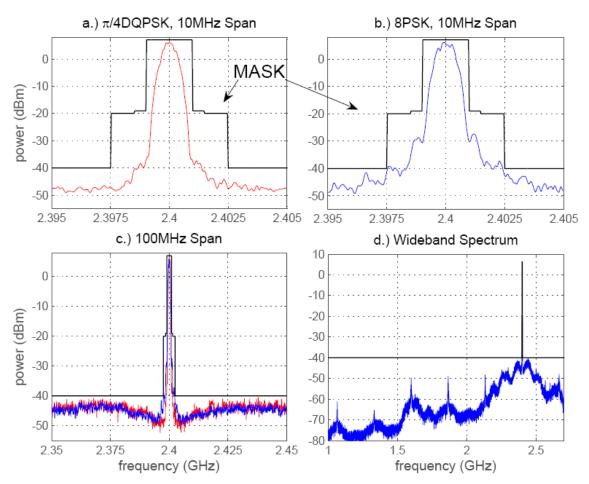

drivers and filter insertion loss. EVM is approximately 2.0% for 8DQPSK and  $\pi/4DQPSK$

constellation trajectories. The spectral mask for Bluetooth 2.1+EDR is satisfied under

normal conditions.

Overall this work highlights several techniques that help improve energy efficiency of

wireless systems. Hopefully these solutions will paint a roadmap of future work that will

help commercial development and lead to many challenging research problems and

academic contributions.

Professor Seth R. Sanders Dissertation Committee Chair *Contents* i

# **Contents**

| Chapter 1            | Introduction                                                                                                                       | 1   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 2            | Transmitter Fundamentals                                                                                                           | 5   |

| 2.1.1                | Complex Modulation                                                                                                                 | 6   |

| 2.1.2                | Digital Modulation Limitations                                                                                                     | 9   |

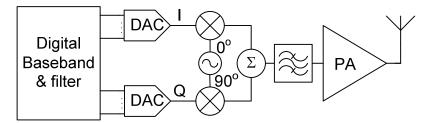

| 2.2 Car              | tesian Transmitter                                                                                                                 |     |

| 2.2.1                | Cartesian Transmitter: General Operation and Issues                                                                                | 12  |

| 2.3 Pol              | ar Transmitters                                                                                                                    | 14  |

| 2.3.1                | Polar Implementations                                                                                                              | 16  |

| 2.3.2                | Issues in Polar Systems                                                                                                            | 17  |

| <b>2.4 Pov</b> 2.4.1 | wer and Energy Efficiency: Polar and Cartesian Architectures  Typical Use Patterns: Probability Density Function (PDF) of Transmit |     |

| Power                | 23                                                                                                                                 |     |

| <b>2.5 Pov</b> 2.5.1 | wer amplifier overview: general operation and power efficiency  Power Amplifier Operation                                          |     |

| 2.5.2                | Linear Power Amplifiers: Class AB                                                                                                  | 26  |

| 2.5.3                | Switching Power Amplifiers: Class E example                                                                                        | 29  |

| 2.5.4                | Efficiency in Power Backoff                                                                                                        | 33  |

| Chapter 3            | Power Management for RF Transmitters and Polar Syst 36                                                                             | ems |

| 3.1 Mo               | tivation: Efficiency                                                                                                               | 37  |

| 3.1.1                | Envelope Tracking System                                                                                                           | 39  |

| 3.1.2                                                             | 2 Dynamic Supply Polar Modulation                          | 42                               |

|-------------------------------------------------------------------|------------------------------------------------------------|----------------------------------|

| <b>3.2</b> 3.2.1                                                  | Voltage Regulator Topologies  Linear Regulators            |                                  |

| 3.2.2                                                             | 2 Switching Voltage Regulators                             | 46                               |

| 3.2.3                                                             | B Hybrid Voltage Regulators: Introduction                  | 52                               |

| Chapter                                                           | Power Supply Noise Analysis for RF Amplifiers              | 55                               |

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.4<br>4.5<br>4.6<br>4.6.1 | Multiple-Port Volterra Analysis                            | 57<br>60<br>63<br>64<br>68<br>70 |

| 4.6.2                                                             |                                                            |                                  |

| 4.6.3                                                             |                                                            |                                  |

| 4.7                                                               | Conclusion                                                 |                                  |

| Chapter<br>Regulate                                               | Optimum Operating Strategies for Hybrid Voltage            |                                  |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                     | Introduction                                               | 91<br>93<br>96<br>101<br>106     |

| Chapter<br>Systems                                                |                                                            |                                  |

| <b>6.1</b><br><b>6.2</b><br>6.2.1                                 | Transmitter concepts revisited  Data conversion principles | 123                              |

| 6.2.2     | Discrete-time sampling                                       | 125 |

|-----------|--------------------------------------------------------------|-----|

| 6.2.3     | Practical sampling and reconstruction                        | 127 |

| 6.2.4     | Sampling with non-bandlimited signals, and relationship with |     |

| quantiza  | tion noise                                                   | 128 |

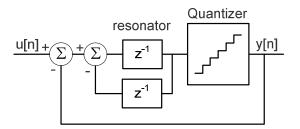

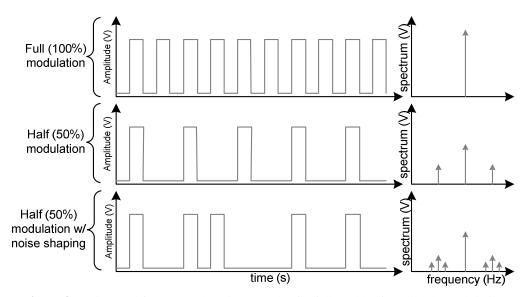

| 6.3 Ove   | ersampled Data Converters                                    | 130 |

| 6.3.1     | Noise Shaping                                                | 131 |

| 6.3.2     | RF (Narrowband) Digital-Analog Conversion (DAC)              | 135 |

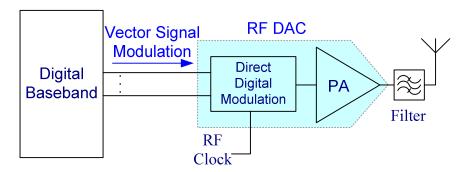

| 6.4 Dire  | ect-digital modulation for RF transmitters                   |     |

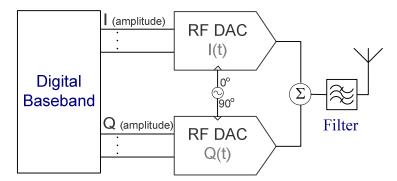

| 6.4.1     | Cartesian RF Data Conversion                                 | 139 |

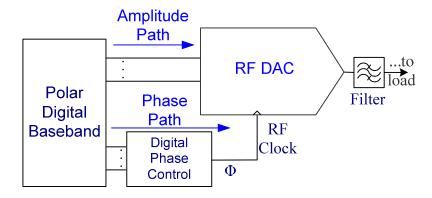

| 6.4.2     | Polar RF Data Conversion                                     | 140 |

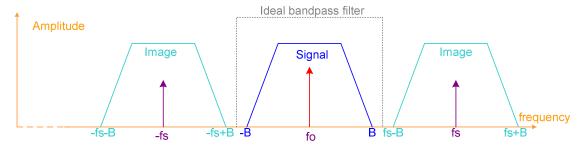

| 6.4.3     | Issues with spectral images                                  | 141 |

| 6.5 A 2.  | 4GHz RF Polar Transmitter for Bluetooth 2.1+EDR              | 144 |

| 6.5.1     | Introduction                                                 | 144 |

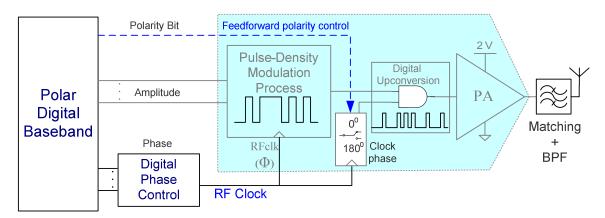

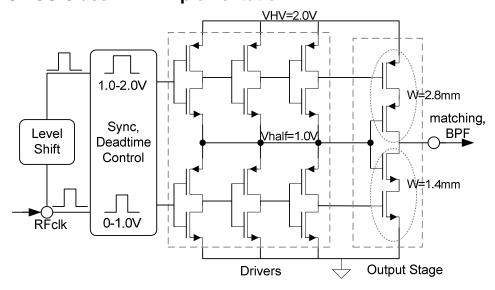

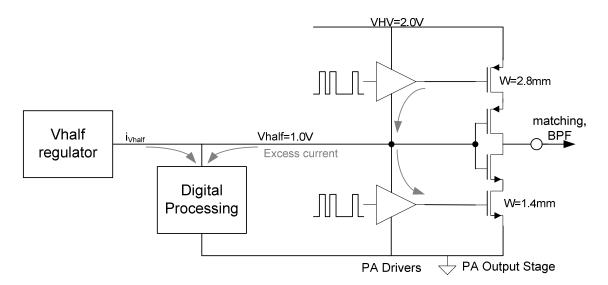

| 6.5.2     | Architecture                                                 | 146 |

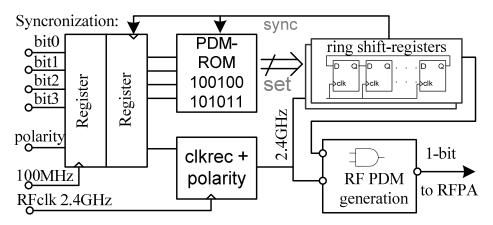

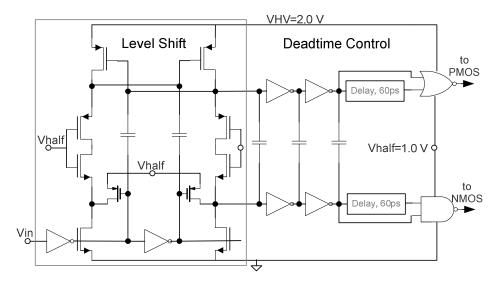

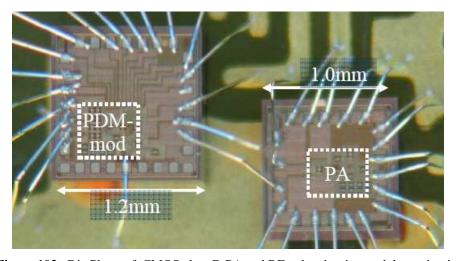

| 6.5.3     | Pulse-density modulator (PDM)                                | 150 |

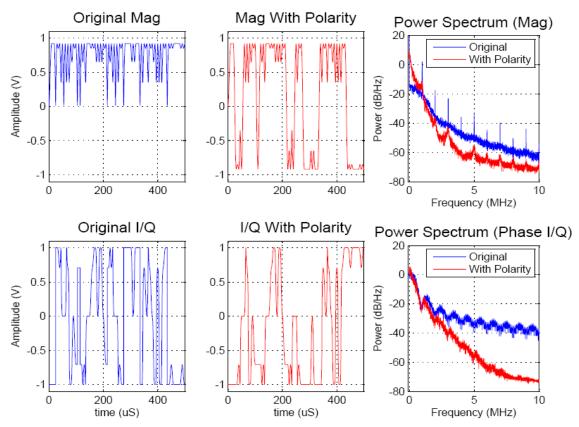

| 6.5.4     | Polarity Bit                                                 | 151 |

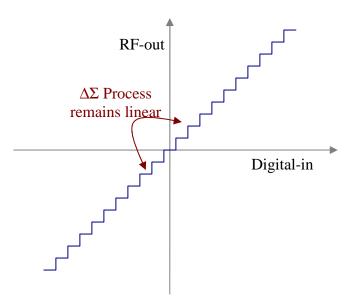

| 6.5.5     | $\Delta\Sigma$ Noise-shaping process                         | 156 |

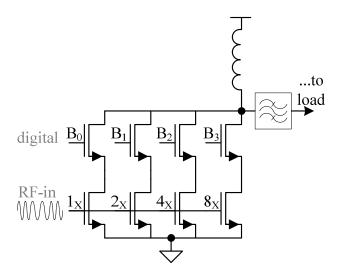

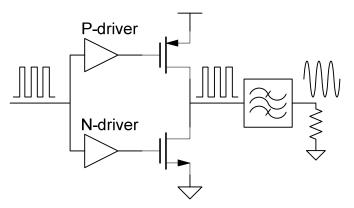

| 6.5.6     | Class-D PA                                                   | 159 |

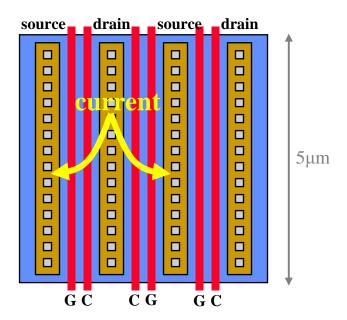

| 6.5.7     | CMOS Class D PA Implementation                               | 162 |

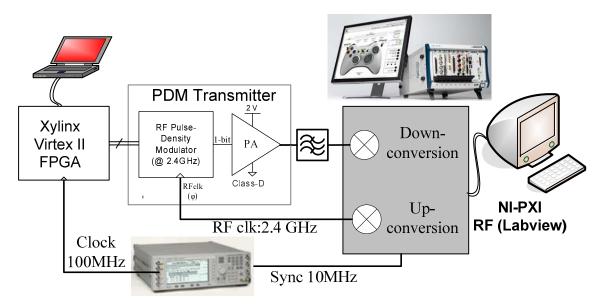

| 6.5.8     | System Implementation                                        | 166 |

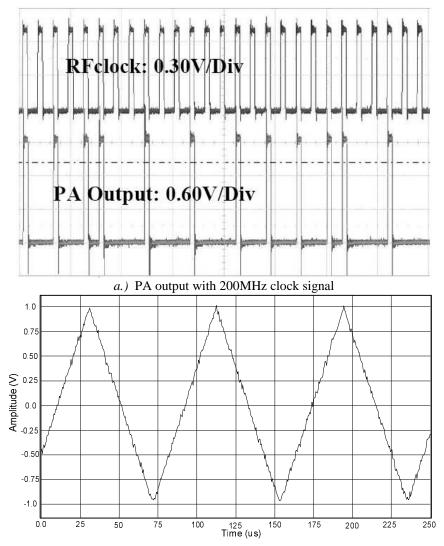

| 6.5.9     | Experimental results                                         | 167 |

| Chapter 7 | Conclusion and Future Work                                   | 175 |

List of Figures i

# **List of Figures**

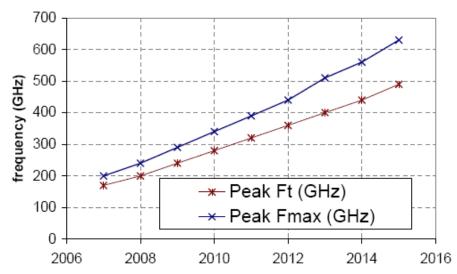

| Figure 1. CMOS $f_t$ and $f_{max}$ (performance analog/mixed signal devices), International  |      |

|----------------------------------------------------------------------------------------------|------|

| technology roadmap for semiconductors (ITRS) [1]                                             |      |

| Figure 2 Wireless system: transmitter, channel, and receiver                                 | 5    |

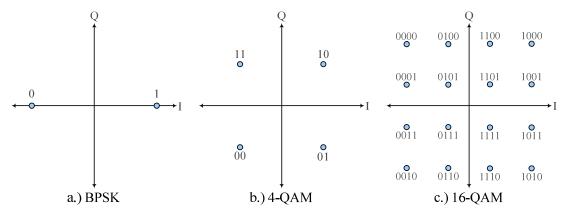

| Figure 3. Symbol constellations with different numbers of bits/symbol                        | 6    |

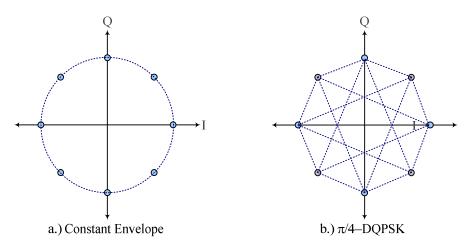

| Figure 4. Complex constellation diagram and trajectory for (a) constant envelope             |      |

| modulation and (b) $\pi/4$ DQPSK, which uses amplitude modulation for the same               |      |

| constellation points as (a)                                                                  | 7    |

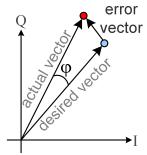

| Figure 5. Error vector is the difference between the actual and ideal symbol vectors         | 9    |

| Figure 6. Typical transmitter distortion mechanisms affecting EVM                            | 10   |

| Figure 7. Transmitter output spectrum showing spectral regrowth                              | 11   |

| Figure 8. Direct-conversion Cartesian transmitter schematic diagram                          | 12   |

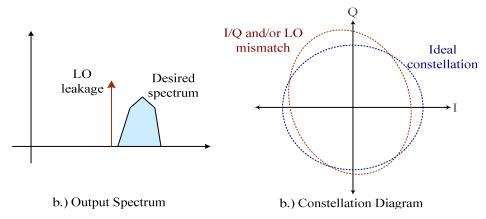

| Figure 9. Effects of I/Q and quadrature LO gain and phase imbalance                          | 13   |

| Figure 10. Kahn envelope elimination and restoration (EER) transmitter architecture          |      |

| [19]                                                                                         | 14   |

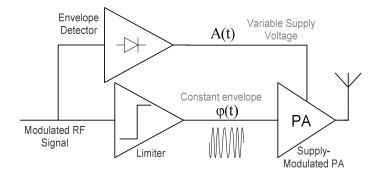

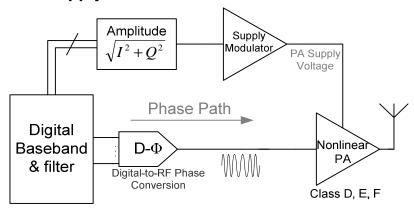

| Figure 11. General representation of the polar transmitter architecture                      | 15   |

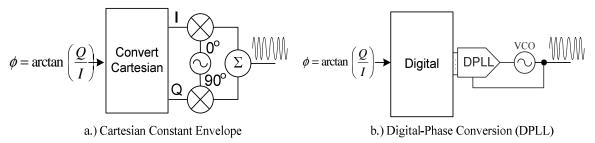

| Figure 12. Phase-path circuit architectures: representative techniques                       | 17   |

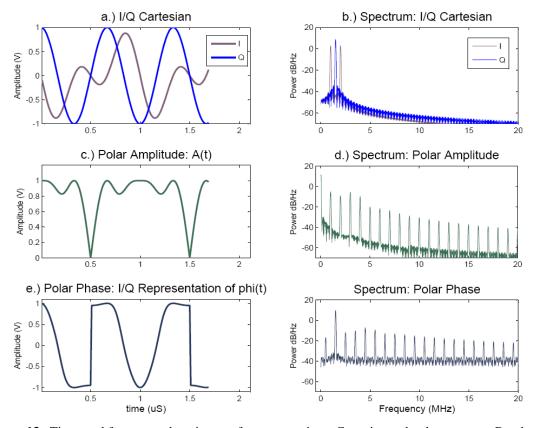

| Figure 13. Time- and frequency-domain waveform comparison: Cartesian and polar               |      |

| systems. Baseband I/Q waveform with two-tone zero mean sinusoid                              | 18   |

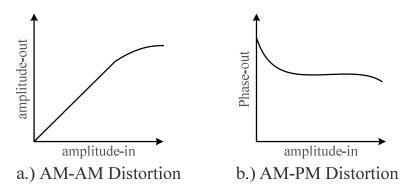

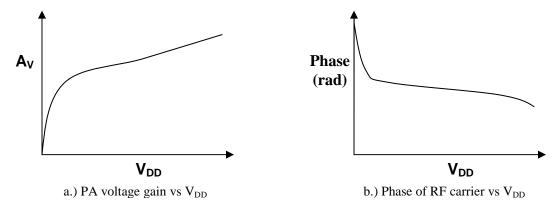

| Figure 14. Distortion mechanisms in polar systems: gain and phase vs supply voltage          | . 20 |

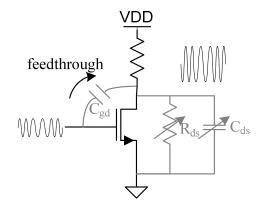

| Figure 15. Common-source amplifier circuit showing mechanisms for AM-AM, AM-                 |      |

| distortion                                                                                   | 20   |

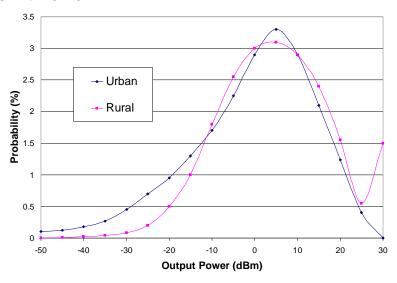

| Figure 16. Representative probability distribution function (PDF) for CDMA                   |      |

| applications [31]                                                                            |      |

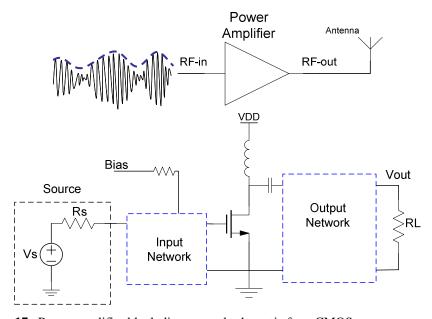

| Figure 17. Power amplifier block diagram and schematic for a CMOS common-source              |      |

| PA                                                                                           |      |

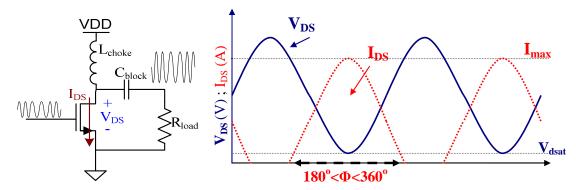

| Figure 18. Class-AB PA voltage and current waveforms                                         |      |

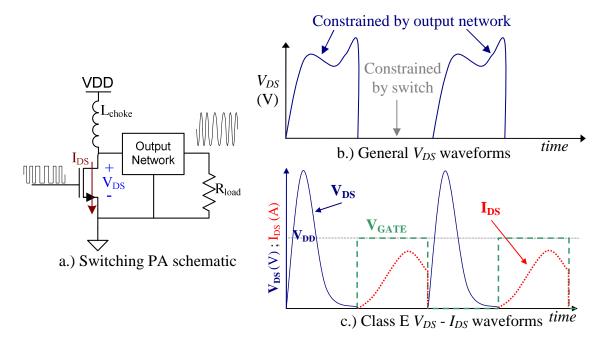

| Figure 19. Switching PA schematic and time-domain waveforms                                  |      |

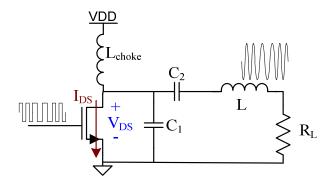

| Figure 20. Class E PA schematic                                                              |      |

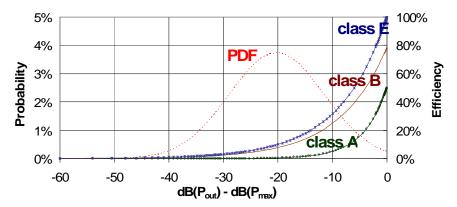

| Figure 21. Power amplifier efficiency in power backoff overlaid with a representative        |      |

| PDF                                                                                          |      |

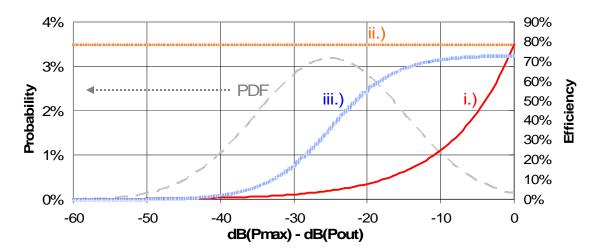

| Figure 22. Efficiency versus output power: i.) conventional class B PA, ii.) class B PA      |      |

| with dynamic supply regulation, iii.) class B PA, dynamic VDD with realistic los             |      |

| mechanisms.                                                                                  |      |

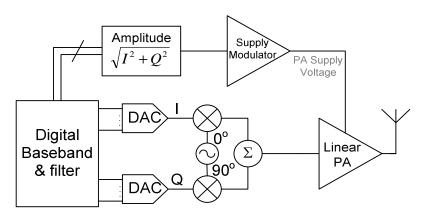

| Figure 23. Envelope tracking transmitter using traditional Cartesian architecture with       |      |

| dynamic supply modulator to improve average efficiency.                                      |      |

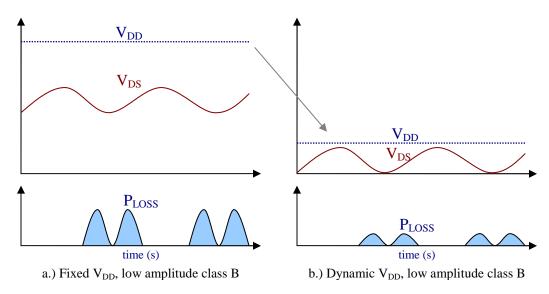

| Figure 24. Time domain waveforms for V <sub>DS</sub> RF carrier waveform and power loss: fix |      |

| V <sub>DD</sub> and dynamic V <sub>DD</sub>                                                  |      |

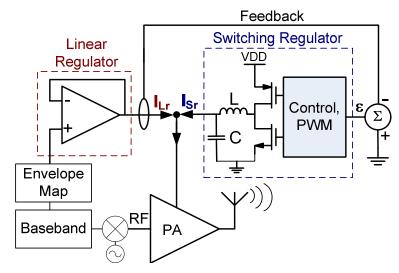

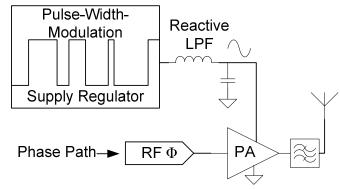

| Figure 26. Dynamic supply polar modulation system                                            |      |

|                                                                                              |      |

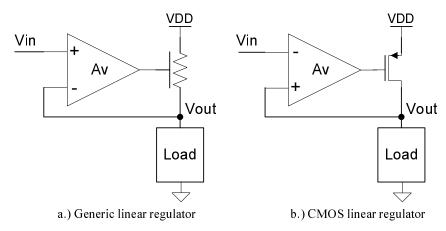

| Figure 27. | Linear regulator topologies                                                     | 45  |

|------------|---------------------------------------------------------------------------------|-----|

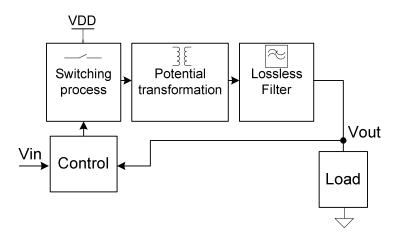

| Figure 28. | Generic voltage-mode switching regulator block diagram                          | 46  |

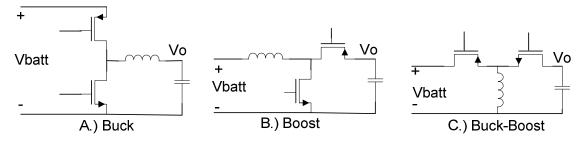

| Figure 29. | DC-DC conversion cells: buck, boost, and inverting buck-boost                   | 46  |

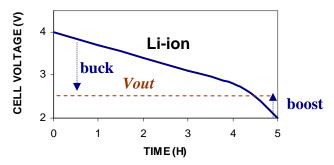

| Figure 30. | Typical battery discharge curve and power converter mode of operation           | 46  |

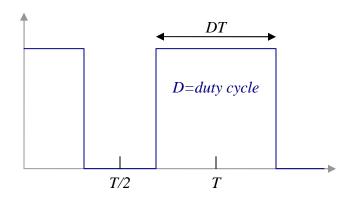

| Figure 31. | Pulse-width-modulation (PWM) waveform                                           | 48  |

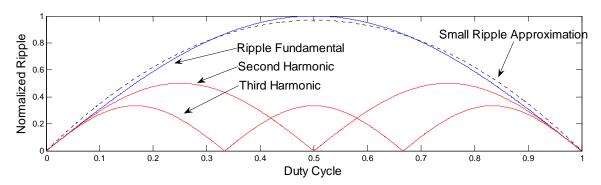

| Figure 32. | Fundamental and harmonics of pulse-width modulated waveform versus du           | ty  |

| cycle,     | , normalized to fundamental peak                                                | 48  |

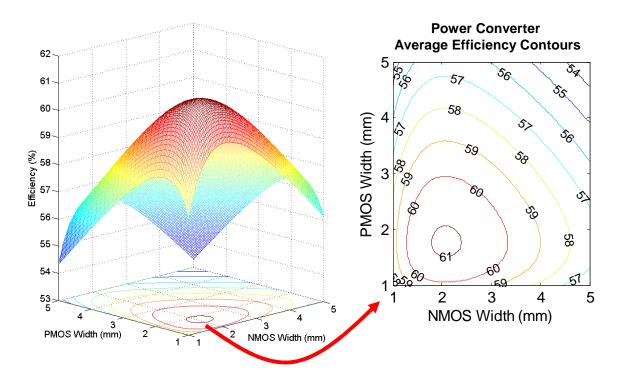

| Figure 33. | Contour representation of average efficiency of the switching regulator vs      |     |

| gate v     | vidth                                                                           | 51  |

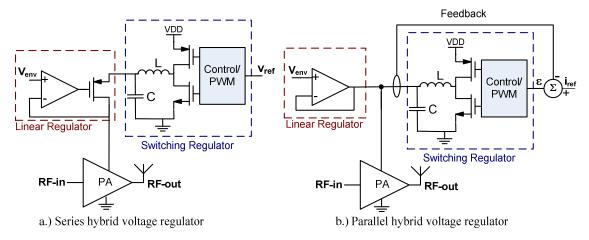

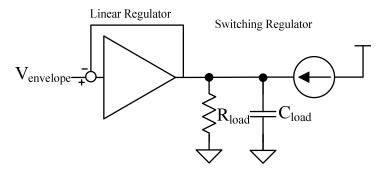

| Figure 34. | Hybrid voltage regulator schematic: a.) Series hybrid, b.) Parallel hybrid      | 52  |

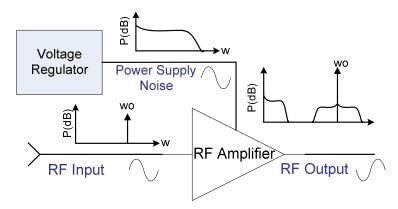

| Figure 35. | Effect of supply noise on RF amplifier output spectrum                          | 55  |

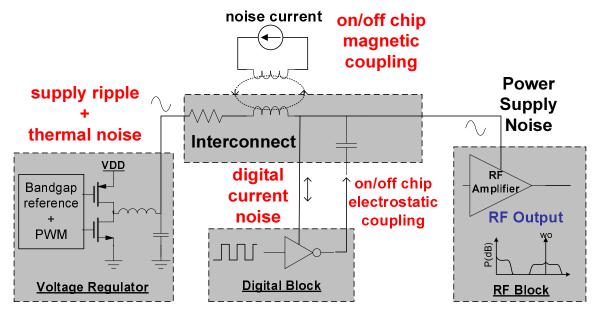

| Figure 36. | Noise sources in RF systems                                                     | 59  |

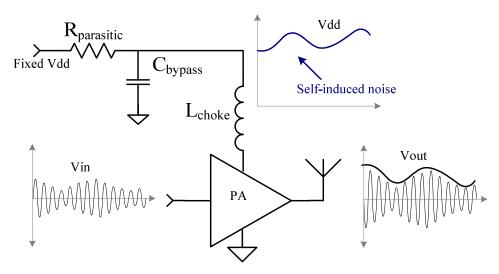

| Figure 37. | Self-induced power supply noise from high supply impedance at the envelo        | pe  |

|            | ency                                                                            | 66  |

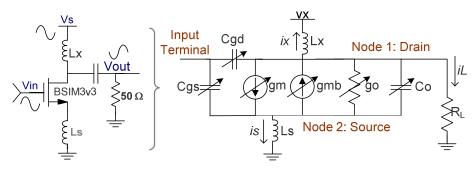

| _          | CMOS inductor-degenerated common source amplifier showing nonlinear             |     |

|            | ents.                                                                           | 68  |

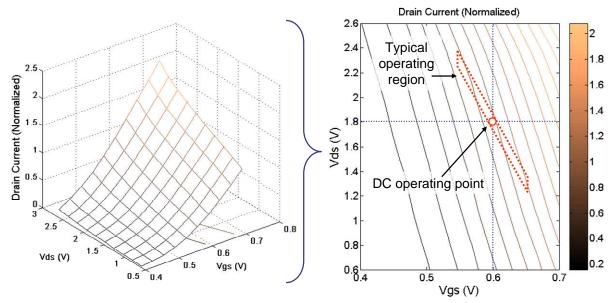

|            | MOSFET drain current versus gate-source and drain-source voltage.               |     |

| Nonli      | nearities are extracted around the dc operating point highlighted in the figure |     |

|            |                                                                                 |     |

| •          | Common-source amplifier model                                                   |     |

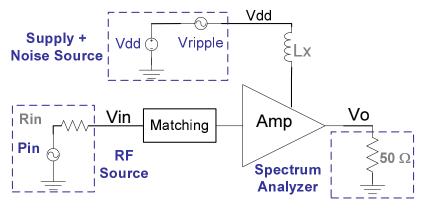

| _          | Laboratory test setup                                                           | 77  |

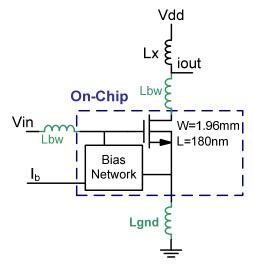

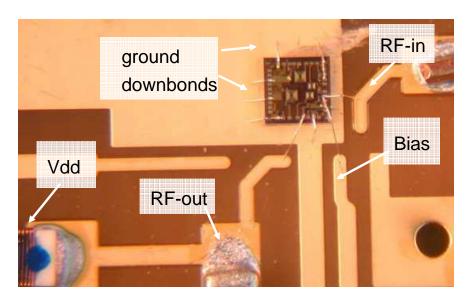

| -          | Photograph of the die bonded on the gold-plated test board. Die area is         |     |

|            | mX1.4mm                                                                         |     |

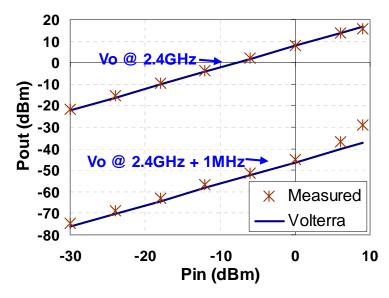

| Ū          | Comparison of measured and calculated fundamental and ripple sideband           |     |

| •          | r                                                                               |     |

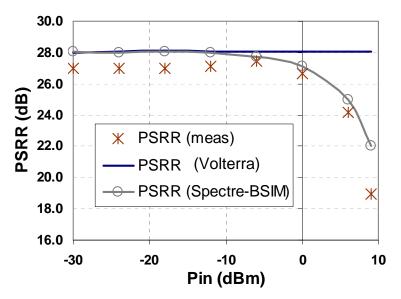

| Figure 44. | Comparison of measured and calculated ripple sideband in decibles-below         | '   |

| carrie     | r                                                                               | 80  |

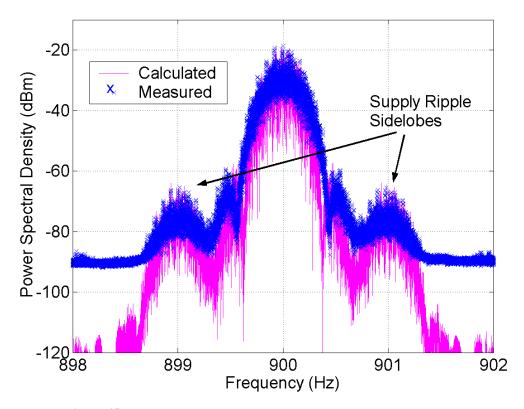

| Figure 45. | Measured versus calculated power spectral density at 900MHz                     | 82  |

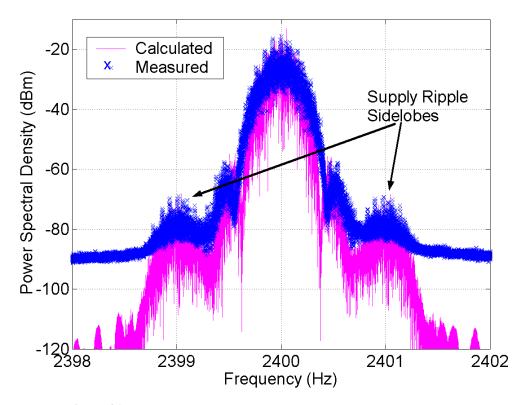

| Figure 46. | Measured versus calculated power spectral density at 2.4GHz                     | 83  |

| Figure 47. | PSRR vs carrier frequency, from Volterra-series analysis, showing               |     |

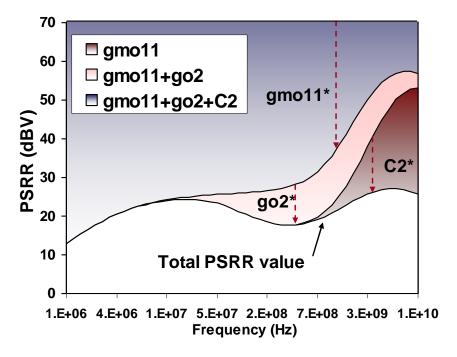

| contr      | ibutions of dominant circuit-level nonlinearities                               | 85  |

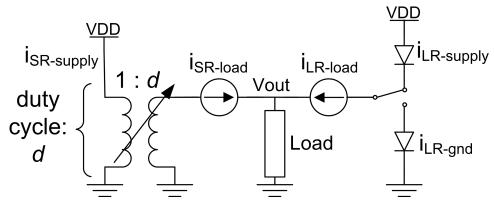

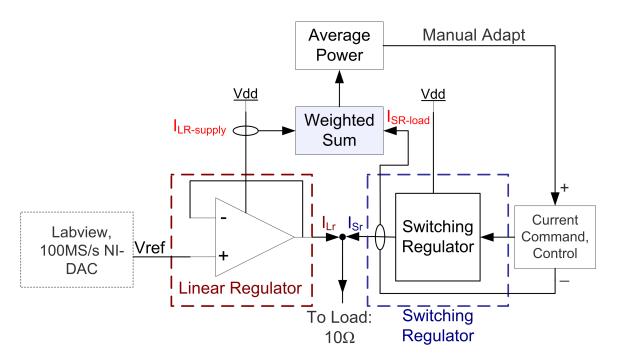

|            | Traditional parallel linear-switching hybrid regulator topology                 |     |

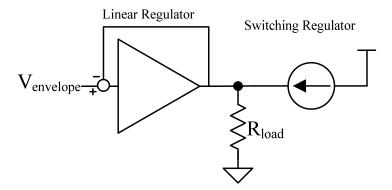

| _          | Model for parallel hybrid switching-linear regulator                            |     |

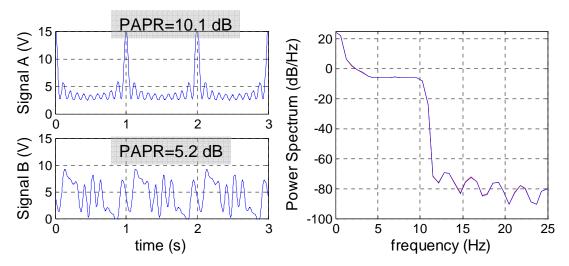

| _          | Two different time-domain envelope signals that share the same power            |     |

|            | rum: one with peak-average power ratio (PAPR) of 10.1dB, and another with       | 1   |

|            | R or 5.2dB                                                                      |     |

|            | Proposed hybrid switching regulator model                                       |     |

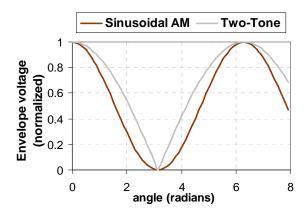

| _          | Envelope Waveforms: Sinusoidal AM and 2-tone modulation                         |     |

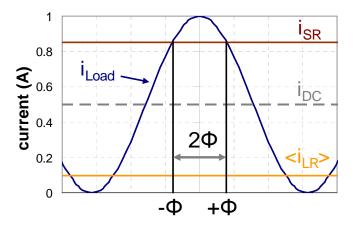

| _          | Conduction angle derivation: Sinusoidal AM modulation, normalized peak          | -   |

| •          | current = 1A                                                                    | 98  |

|            | Theoretical efficiency vs voltage amplitude: sin-AM and two tone cases,         | - 0 |

| _          | ving (54) and (59)                                                              | 02  |

|            | Efficiency vs normalized voltage amplitude: IS-95 CDMA, from simulation 1       |     |

| Figure 56. Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

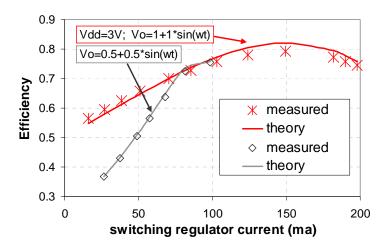

| Figure 57. Average efficiency vs switching regulator current contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 108             |

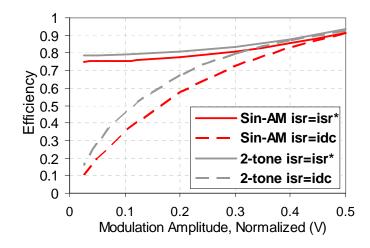

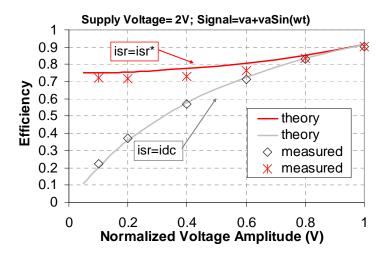

| Figure 58. Average efficiency vs envelope modulation amplitude: Sinuso                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | idal AM         |

| modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 108             |

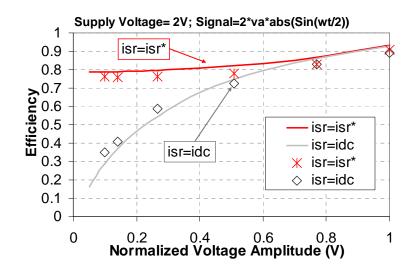

| Figure 59. Two-tone modulation: comparison of theory to measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t 110           |

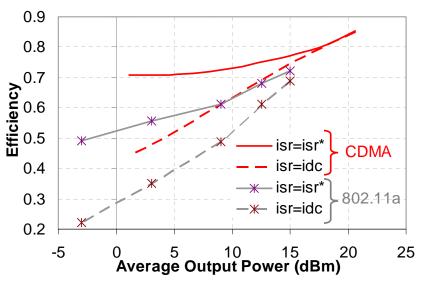

| Figure 60. IS-95 CDMA, 802.11a WLAN measured efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 110             |

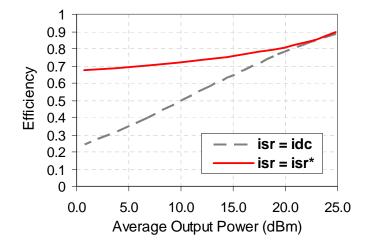

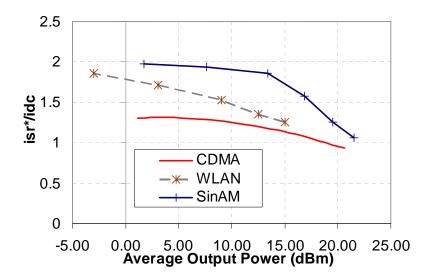

| Figure 61. Optimum switching regulator current (normalized $i_{S\!R}^*$ / $i_{D\!C}$ ) vs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | output power    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

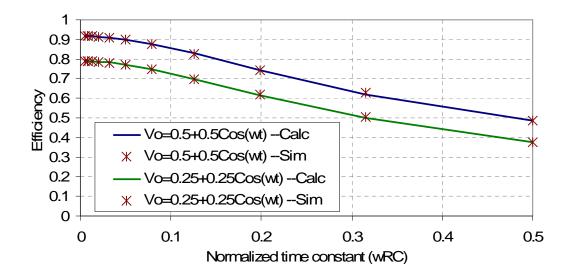

| Figure 62. Hybrid regulator model including output capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

| Figure 63. Hybrid regulator with load capacitance: efficiency versus norm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |

| constant (simulation vs theory)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

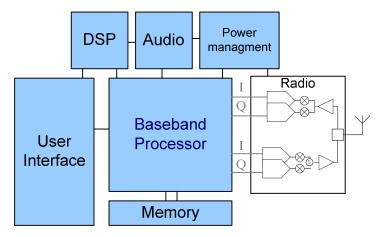

| Figure 64. Conventional cellular phone block diagram: digital application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | n processor,    |

| DSP, Audio, Power management; Radio is still largely analog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 119             |

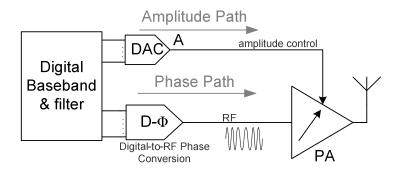

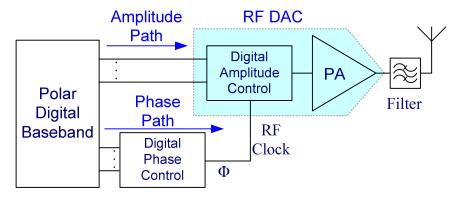

| Figure 65. Proposed digital polar architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

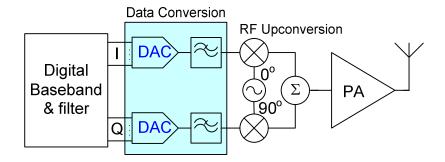

| Figure 66. Traditional Cartesian transmitter architecture: lowpass data co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nversion        |

| followed by upconversion mixers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 121             |

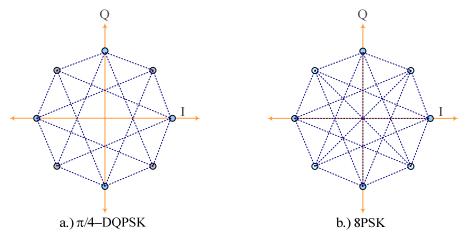

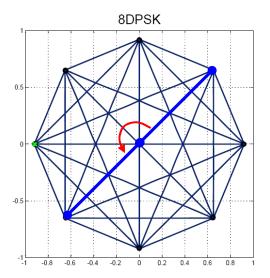

| Figure 67. $\pi$ /4DQPSK and 8PSK constellation diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121             |

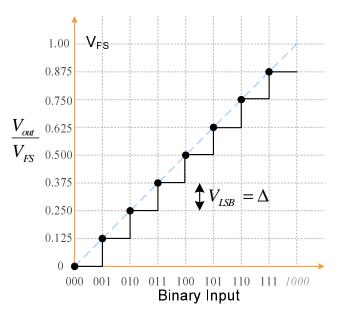

| Figure 68. Input-output transfer characteristics for a 3-bit D-A converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 123             |

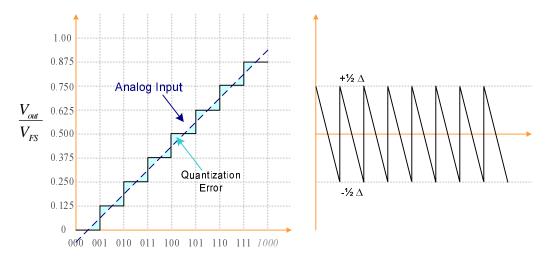

| Figure 69. Comparison of continuous and quantized signal levels showin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | g error between |

| ±½ LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 124             |

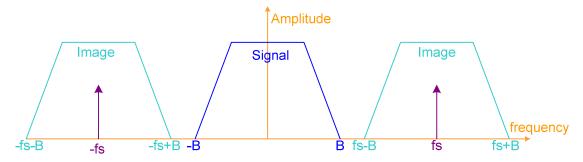

| Figure 70. Frequency-domain representation of discrete-time sampling processing from the company of the company |                 |

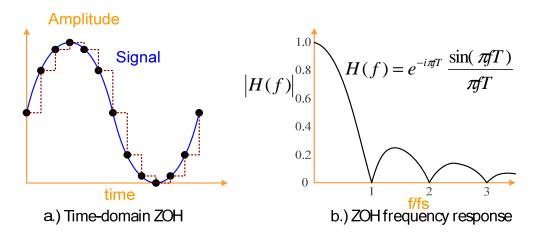

| Figure 71. Time- and frequency-domain characteristics: zero order hold (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |

| reconstruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

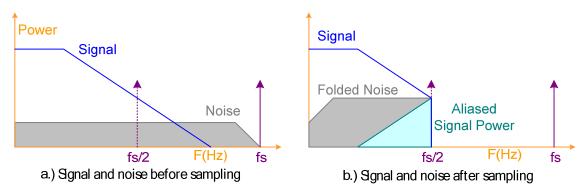

| Figure 72. Signal and noise before and after sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |

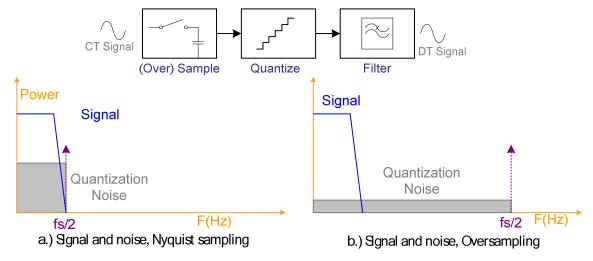

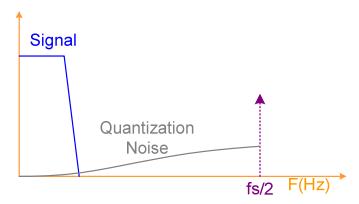

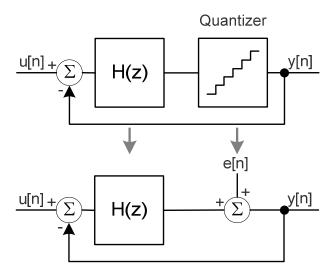

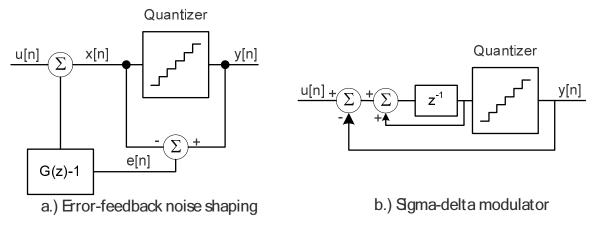

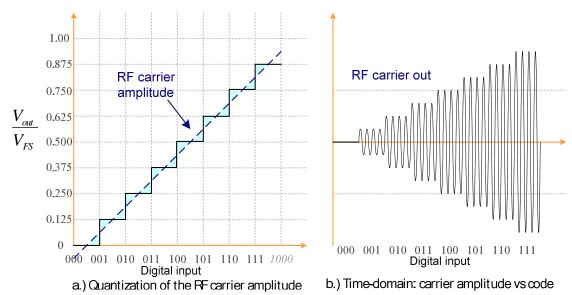

| Figure 73. Quantization noise spectral density: a.) Nyquist-rate sampling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |