# Millimeter - Wave CMOS Power Amplifiers Design

Mounir Youssef Bohsali

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-25 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-25.html

February 6, 2009

Copyright 2009, by the author(s).

All rights reserved.

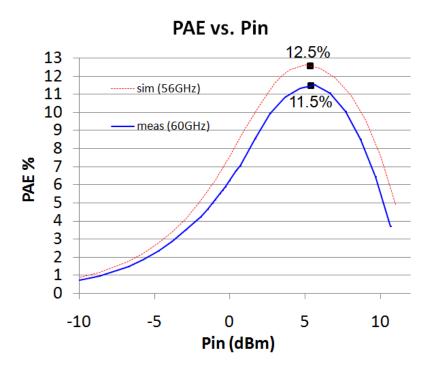

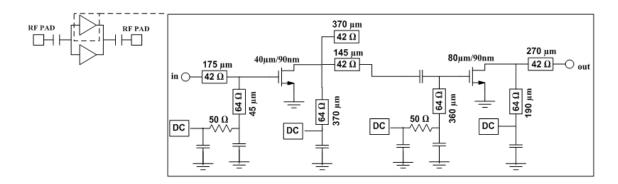

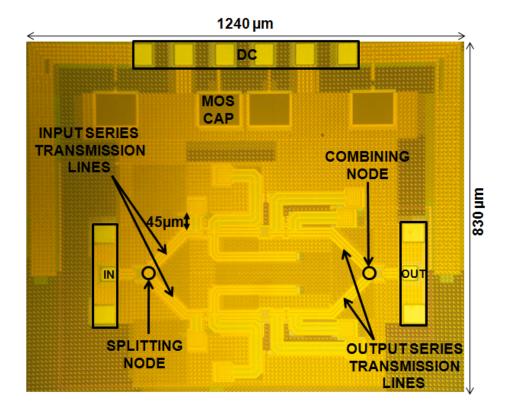

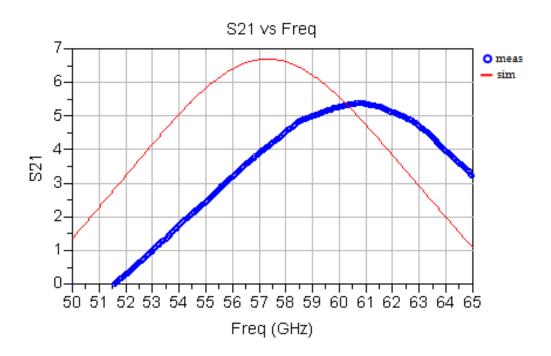

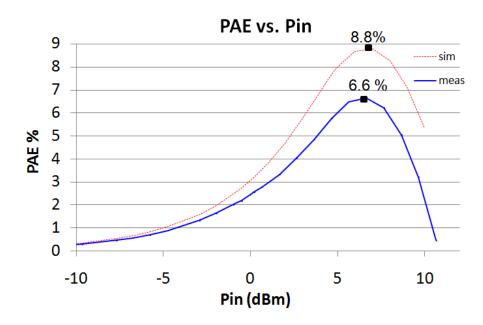

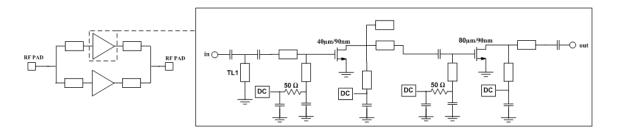

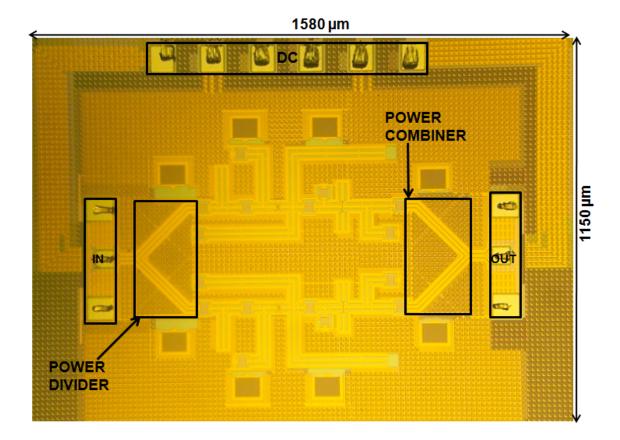

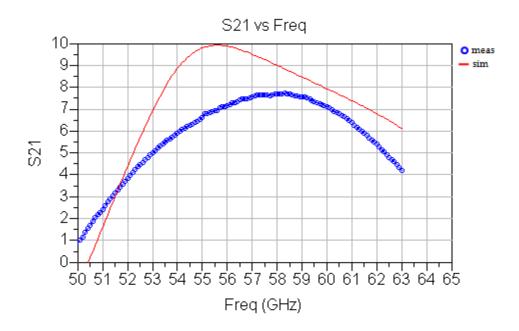

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### **Millimeter - Wave CMOS Power Amplifiers Design**

By

Mounir Youssef Bohsali

B.S. (North Carolina State University) 2001 M.S. (University of California, Berkeley) 2004

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Seth Sanders Professor David Ahn

Fall 2008

| The dissertation of Mounir Youssef Bohsali is approved: |      |

|---------------------------------------------------------|------|

| Professor Ali M. Niknejad, Chair                        | Date |

|                                                         |      |

| Professor Seth Sanders                                  | Date |

|                                                         |      |

| Professor David Ahn                                     | Date |

University of California, Berkeley Fall 2008

# Millimeter - Wave CMOS Power Amplifiers Design

Copyright © 2008

By

Mounir Youssef Bohsali

#### **Abstract**

Millimeter - Wave CMOS Power Amplifiers Design

by

#### Mounir Youssef Bohsali

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali M. Niknejad, Chair

In the last few years we have seen an increased interest in millimeter-wave CMOS circuits and communication systems both in academia and industry. The feasibility of CMOS circuits at 60 GHz, the rising interest in digital video, short range, and other high data rate applications, along with the worldwide availability of unlicensed spectrum around 60 GHz have spurred a wave of research targeting integrated 60 GHz CMOS transceivers as a way to achieving low cost, highly integrated, high bandwidth, high data rate communication systems.

In recent years, a number of 60 GHz CMOS building blocks and integrated receivers have been demonstrated. However, the low supply voltage, thin gate oxide, low breakdown voltage, lossy silicon substrate, and power gain - output power tradeoff of CMOS technology result in the millimeter wave power amplifier being the most difficult block to implement in CMOS. A number of 60 GHz CMOS power amplifiers employing different topologies have been reported to date, however the output power has been relatively low, limiting the amplifiers to short-range applications. It is becoming

increasingly important to use more efficient power combining techniques in order to increase the output power capability of power amplifiers in order to enable medium and long-range applications.

This research aims at exploring the challenges facing the design and implementation of 60 GHz power amplifiers in standard 90 nm CMOS processes. The design, modeling, and layout optimization of both passive structures such as transmission lines, capacitors, RF pads as well as active devices operating at 60 GHz are investigated. A low-loss power combining technique taking advantage of millimeter-wave amplifiers topologies is presented. Four power amplifiers are implemented in a standard 90 nm 1V CMOS process. Record performance is reached in terms of 1dB compression and saturation output power.

Professor Ali M. Niknejad, Chair

Date

### Acknowledgments

If only one page of this dissertation is worth reading, it is this one.

My sincere gratitude goes to my advisor, Professor Ali M. Niknejad, without whom this work would not have been possible. His continuous guidance and support in my research were invaluable. His encouragement throughout the years was indispensible. I was extremely lucky to have an advisor with such a vast knowledge and always available and involved in my research. I also would like to acknowledge Professor Robert Brodersen for his help and support.

My thanks go to my parents who poured all what they had into me to see this day.

My father provided me an education he could not afford and my mother taught me how to fight and fight and never give up on my goals.

My respect goes to Abir, my wife, who believed in me when I was a teenager and stood by me in the ups and downs, when I was right and when I was wrong, and never doubted my abilities.

My heart goes to Lana. Lana is why I wake up every morning, and Lana is why I stay awake many nights. Lana is all what I live for.

Majd, my newborn son, made sure to always wake me up in the middle of the night to finish writing my thesis.

Amro, my brother, always available for discussions about life and people behavior, and Tamara, my sister, were very supportive over the years.

My appreciation goes to Lina and Ghassan Chehab, the best friends I ever had, people who shaped me in many ways.

My Ph.D. years at Berkeley could have been easily cut in half if not for the time spent with my family: Lana and Hisham Noeimi, Dima and Ammar Rafei, Dina and Mahmoud Hachem, Mohammad and Soumaya Zalloukh, Nadia and Ziad Hafza. These people will never comprehend what they mean to me. People who make abroad feel like home.

I would like to thank my colleagues at Berkeley who have made my experience most agreeable. Hakan Dogan has been a great friend and roommate. Axel Berny was very helpful and always willing to spend time in research discussions. Babak Heydari with whom I worked very closely has provided great input into my research. Other members of the mm-wave CMOS research group, Ehsan Adabi, Bagher Afshar, Mohammad Amin Arbabian, Debopriyo Chowdhury, and Christian Marcu were very supportive.

To the memory of my father

To my mother

# **Table of Contents**

| C | CHAPTE | R 1                                                          | 1    |

|---|--------|--------------------------------------------------------------|------|

| 1 | Intro  | duction                                                      | 2    |

|   | 1.1    | Motivation for 60 GHz CMOS Power Amplifiers                  | 2    |

|   | 1.2    | Existing 60 GHz CMOS Power Amplifiers                        | 5    |

|   | 1.3    | Research Contributions                                       | . 11 |

|   | 1.4    | Organization of the Thesis                                   | . 12 |

| C | HAPTE  | R 2                                                          | . 14 |

| 2 | Tech   | nnology Challenges                                           | 15   |

|   | 2.1    | Low Supply Voltage                                           | . 16 |

|   | 2.2    | Transistor Sizing in the Power Gain - Output Power Tradeoff  | . 18 |

|   | 2.2.1  | Optimization of Finger Width                                 | . 18 |

|   | 2.2.2  | Optimization of the Number of Fingers                        | . 23 |

|   | 2.3    | Impedance Matching in the Power Gain - Output Power Tradeoff | . 26 |

|   | 2.3.1  | Matching for Maximum Power Gain.                             | . 27 |

|   | 2.3.2  | Matching for Maximum Output Power                            | 30   |

|   | 2.4    | Power Combining                                              | . 32 |

|   | 2.4.1  | Wilkinson Power Combiners                                    | . 33 |

|    | 2.4.2  | Transformer-Based Power Combiners          | 35 |

|----|--------|--------------------------------------------|----|

|    | 2.4.3  | mm-Wave Power Combining                    | 35 |

| 4  | 2.5    | Conclusion                                 | 39 |

| СН | [APTE] | R 3                                        | 40 |

| 3  | Mod    | eling Methodology                          | 41 |

| 3  | 3.1    | Need for 60 GHz Models                     | 42 |

| 3  | 3.2    | Modeling Strategy                          | 43 |

| 3  | 3.3    | Test Chips                                 | 47 |

| 3  | 3.4    | Conclusion                                 | 49 |

| СН | [APTE] | R 4                                        | 51 |

| 4  | Passi  | ive Structures Design and Modeling         | 52 |

| 4  | 4.1    | Transmission Lines Design and Modeling     | 52 |

|    | 4.1.1  | Transmission Line Concepts                 | 53 |

|    | 4.1.2  | Advantages of Using Transmission Lines     | 57 |

|    | 4.1.3  | Coplanar vs. Microstrip Transmission Lines | 59 |

|    | 4.1.4  | Transmission Lines Library                 | 60 |

|    | 4.1.5  | Transmission lines modeling with ADS       | 62 |

|    | 4.1.6  | Transmission Lines Modeling with HFSS      | 75 |

| 2  | 4.2    | Capacitor Modeling                         | 78 |

| 4.    | 2.1 AC Coupling Capacitors               | 79  |

|-------|------------------------------------------|-----|

| 4.    | 2.2 Supply - Ground Bypass Capacitors    | 86  |

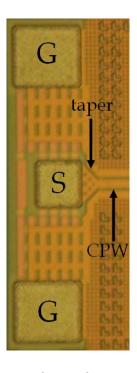

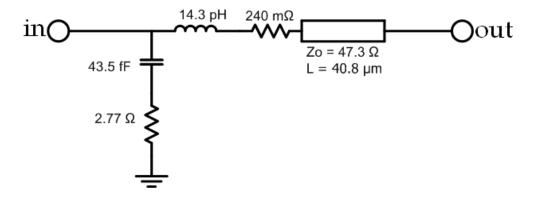

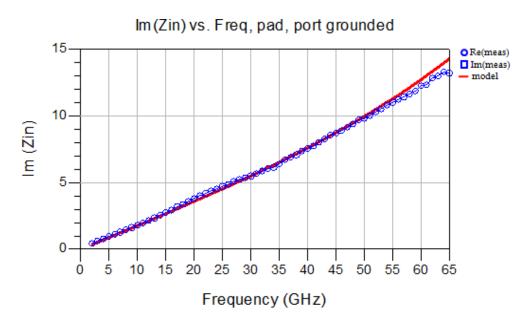

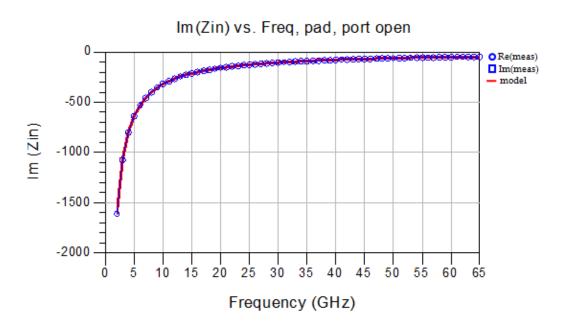

| 4.3   | RF Ground-Signal-Ground Pad Modeling     | 89  |

| 4.    | 3.1 RF Ground-Signal-Ground pad geometry | 89  |

| 4.    | 3.2 RF Ground-Signal-Ground Pad Modeling | 90  |

| 4.4   | Conclusion.                              | 92  |

| CHAP' | TER 5                                    | 93  |

| 5 A   | Active Devices Design and Modeling       | 94  |

| 5.1   | Transistors Design and Layout            | 94  |

| 5.2   | Transistors Small Signal Modeling        | 98  |

| 5.3   | Transistors Large Signal Modeling        | 101 |

| 5.4   | Conclusion                               | 102 |

| CHAP' | TER 6                                    | 104 |

| 6 N   | Modeling Verification                    | 105 |

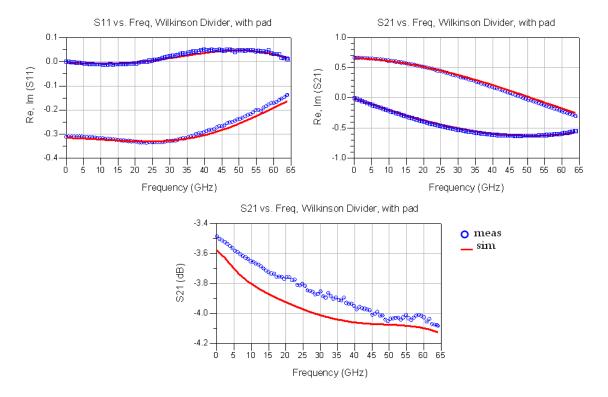

| 6.1   | Wilkinson Power Combiner                 | 106 |

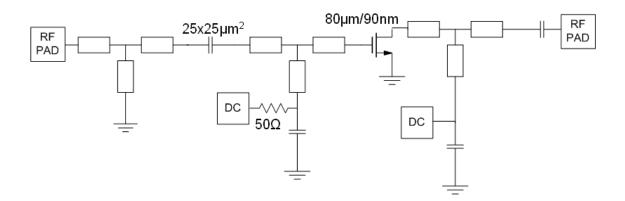

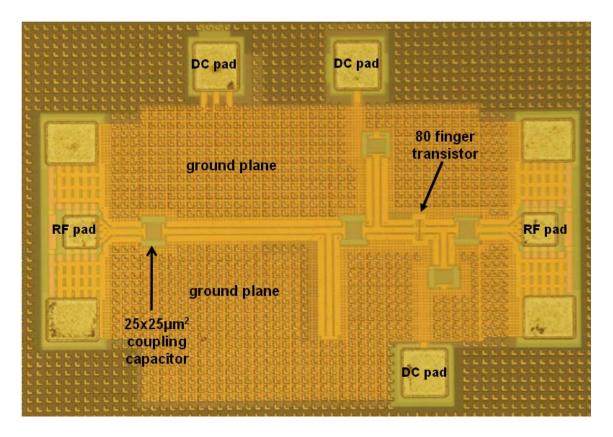

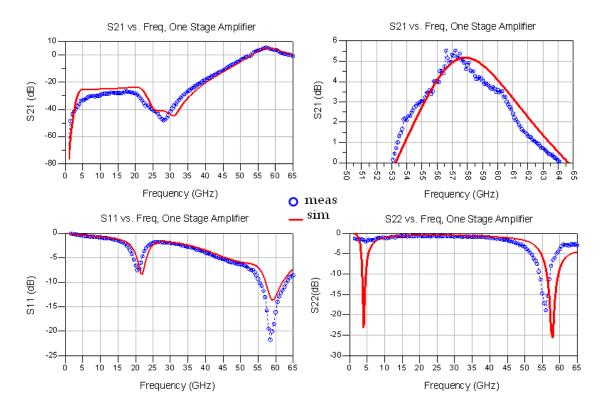

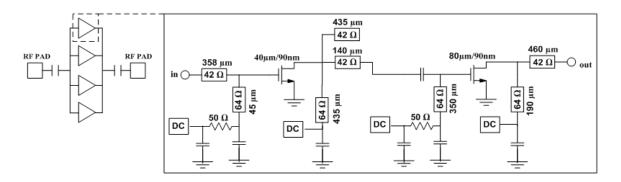

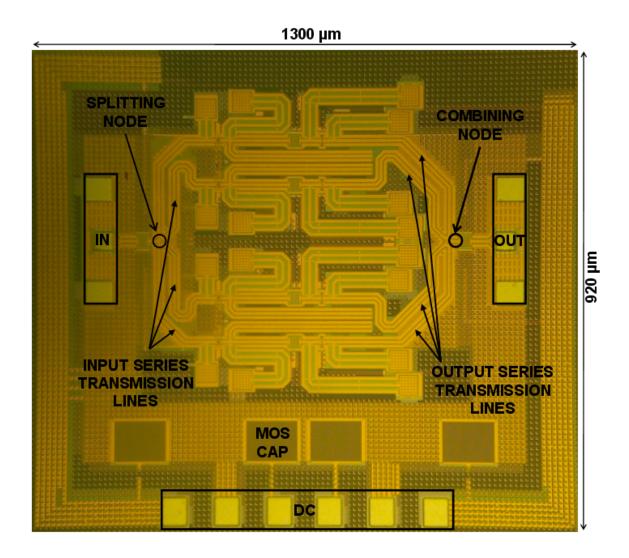

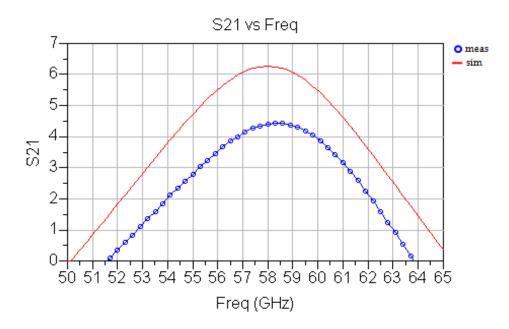

| 6.2   | One-Stage Amplifier                      | 109 |

| CHAP' | TER 7                                    | 113 |

| 7 P   | ower Amplifiers                          | 114 |

| 7.1   | Four-Way Power Amplifier                 | 114 |

| 7.1.1 Circuit Description                                      | 115 |

|----------------------------------------------------------------|-----|

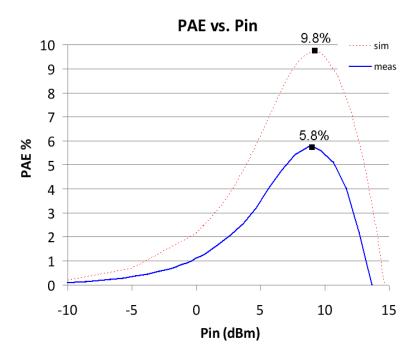

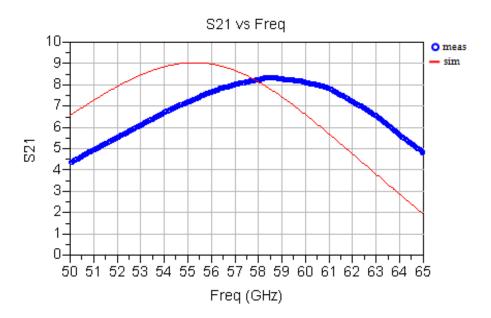

| 7.1.2 Measurement and Simulation Results                       | 118 |

| 7.2 Two-Way Power Amplifier                                    | 125 |

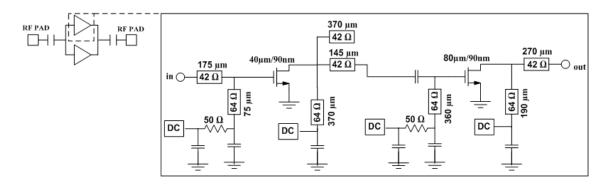

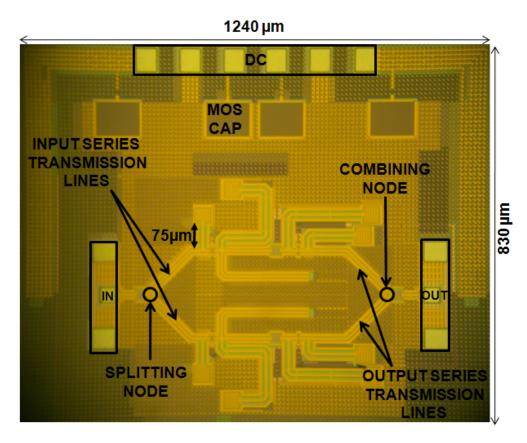

| 7.2.1 Circuit Description                                      | 126 |

| 7.2.2 Measurement and Simulation Results                       | 127 |

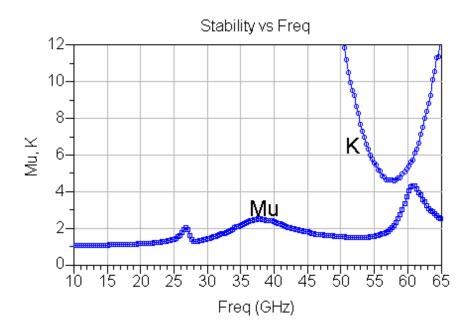

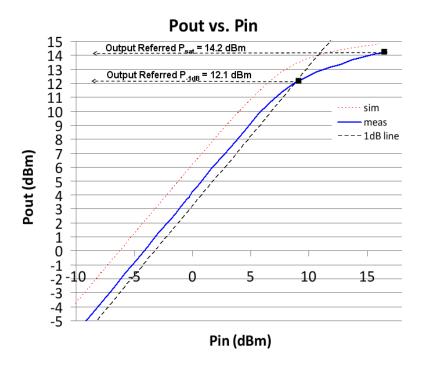

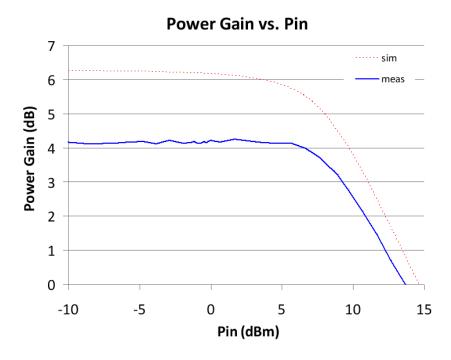

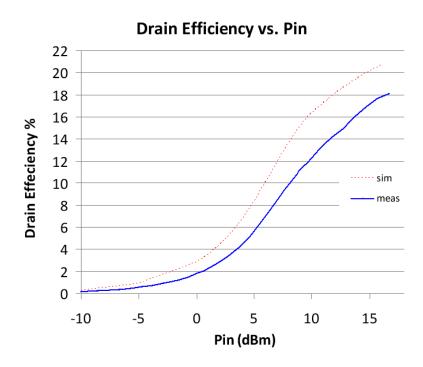

| 7.3 Two-Way High Stability – Low Gain Power Amplifier          | 134 |

| 7.3.1 Circuit Description                                      | 135 |

| 7.3.2 Measurement and Simulation Results                       | 136 |

| 7.4 Two-Way Power Amplifier with Inductive Source Degeneration | 143 |

| 7.4.1 Circuit Description                                      | 144 |

| 7.4.2 Measurement and Simulation Results                       | 147 |

| 7.5 Comparison to Power Amplifiers in the Literature           | 154 |

| 7.6 Measurement Setup                                          | 154 |

| 7.7 Conclusions                                                | 155 |

| CHAPTER 8                                                      | 156 |

| 8 Conclusions                                                  | 157 |

| Bibliography                                                   | 160 |

# **CHAPTER 1**

# **INTRODUCTION**

#### 1 Introduction

#### 1.1 Motivation for 60 GHz CMOS Power Amplifiers

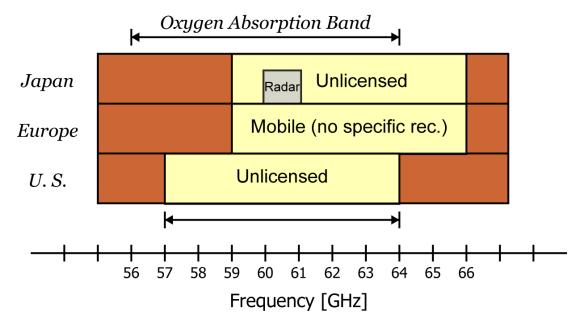

In the last few years we have seen an increased interest in millimeter-wave (mm-wave) circuits and communication systems both in academia and industry. The feasibility of CMOS circuits at 60 GHz, the rising interest in digital video, short range, and other high data rate applications, along with the worldwide availability of unlicensed spectrum around 60 GHz as shown in Figure 1.1 have spurred a wave of research targeting integrated 60 GHz CMOS transceivers as a way to achieving low cost, highly integrated, high bandwidth, high data rate communication systems.

Figure 1.1: Allocation of spectrum around 60 GHz in the U.S., Japan, and Europe

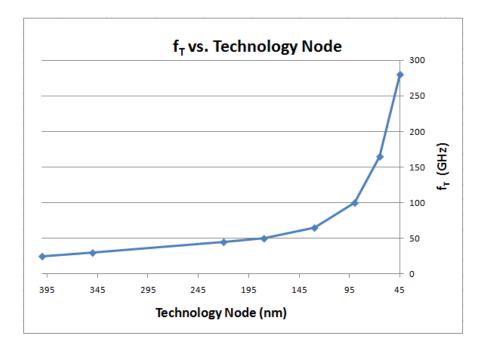

While SiGe and III-V technologies are in general more suitable for mm-wave applications as they provide higher speed active devices and lower loss substrates, CMOS technology provides substantive advantages including low cost and potential of integration with other parts of the system which makes it a natural candidate for exploration. Moreover, the performance of CMOS technologies is continuously improving. Decreasing minimum feature size with every new generation leads to higher speed devices as shown in Figure 1.2. The unity current gain frequency ( $f_T$ ) for the 90 nm technology node is above 100 GHz and it is continuing to increase for smaller nodes, reaching 280 GHz for 45 nm processes [1].

Figure 1.2:  $f_T$  vs. CMOS technology node

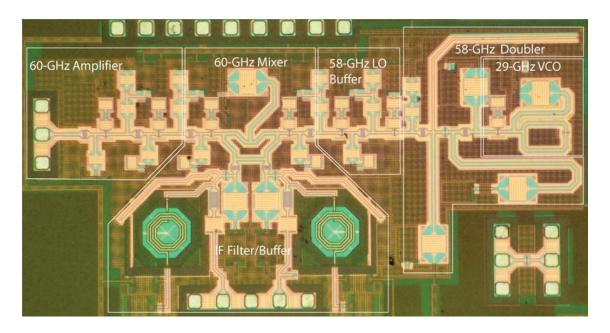

In recent years, a number of 60 GHz CMOS building blocks [2-7] have been demonstrated, and even complete 60 GHz integrated receivers [8-10] as the one shown in Figure 1.3 have been published.

Figure 1.3: Die photo of a 60 GHz CMOS integrated receiver published in [8]

However, the low supply voltage, thin gate oxide, low breakdown voltage, and lossy Si substrate of CMOS technology result in the mm-wave power amplifier being the most difficult block to implement in CMOS. Many of the techniques used to realize high output power levels in the low GHz regime cannot be used at frequencies around 60 GHz because they necessitate the application of large CMOS transistors with a high degree of parasitics which considerably reduces the power gain at mm-wave frequencies. Thus, techniques other than using large bulky transistors need to be used in order to realize power amplifiers operating at mm-wave frequencies.

#### 1.2 Existing 60 GHz CMOS Power Amplifiers

A number of 60 GHz CMOS power amplifiers have been reported to date [11-19], however the output power has been relatively low, limiting the amplifiers to short-range applications. It is becoming increasingly important to use more efficient power combining techniques in order to increase the output power capability of power amplifiers in order to enable medium and long-range applications.

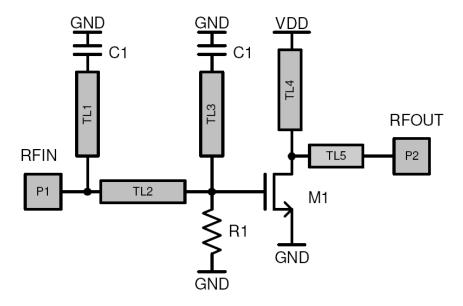

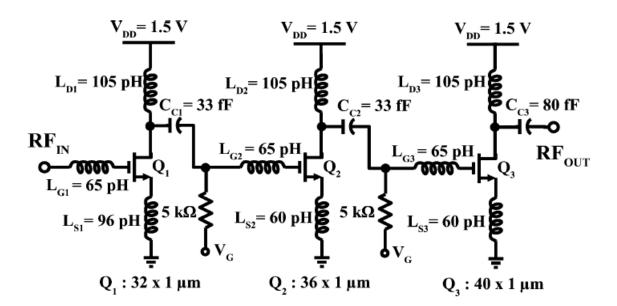

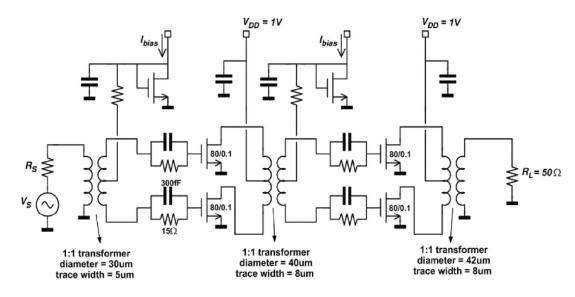

In [11], a single-stage, single-ended power amplifier whose schematic is shown in Figure 1.4 is implemented in a 65 nm bulk CMOS process operating from a 1.2 V supply.

Figure 1.4: Schematic of single stage power amplifier presented in [11]

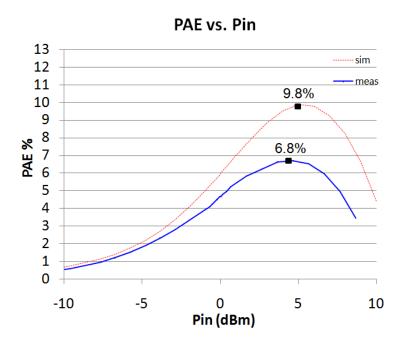

The amplifier achieves a peak power gain of 4.5 dB with 1 dB compression and saturation output power levels of +6 dBm and +9 dBm respectively with peak power added efficiency of 8.5%. While the layout, size, bias level, input impedance, and output impedance of the active device in a single stage power amplifier can be all optimized to

achieve the high output power with acceptable power gain, the fundamental mm-wave transistor power gain - output power tradeoff described in sections 2.2 and 2.3 poses an upper limit on the transistor size that can be used, and thus on the maximum output power that can be obtained from a single stage unit amplifier when operating at mm-wave frequencies. Optimizing the transistor size and impedances for maximum output power leads to low overall power gain, and optimizing for high power gain leads to low output power capability. Multi-stage amplifiers where the initial stages can be optimized for maximum gain and the output stage can be optimized for maximum output power are required to realize power amplifiers with both high gain and high output power levels.

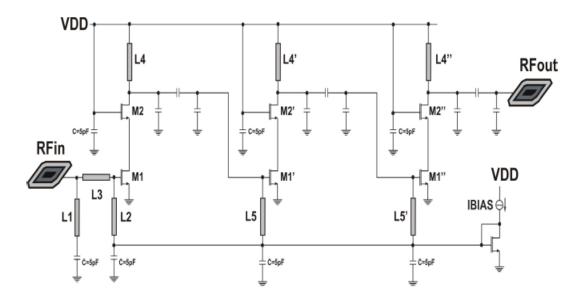

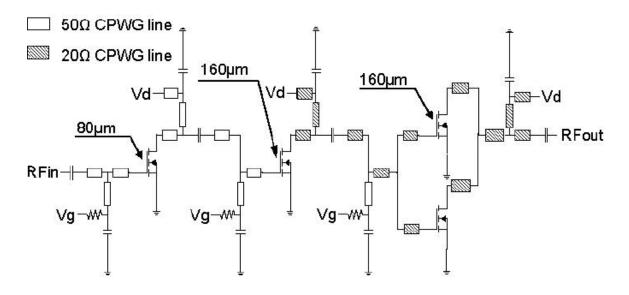

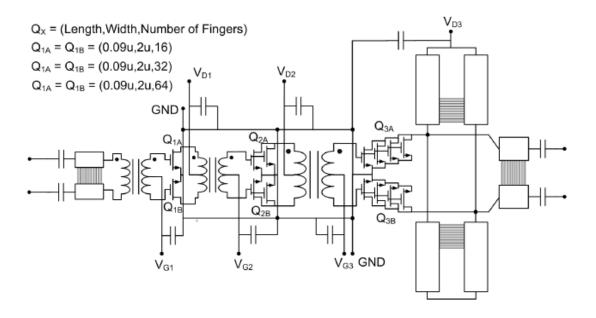

In an attempt to achieve high output power with high gain, the three-stage power amplifiers whose schematics are shown in Figure 1.5 and Figure 1.6 were implemented in 90 nm bulk CMOS and presented in [14, 15].

Figure 1.5: Schematic of three-stage power amplifier presented in [14]

Figure 1.6: Schematic of three-stage power amplifier presented in [15]

The first power amplifier uses ring inductors extensively in lieu of transmission lines to achieve power gain of 5.2 dB with 1 dB compression and saturation output power levels of +6.4 dBm and +9.3 dBm respectively with peak power added efficiency of 7%. The second power amplifier uses microstrip transmission lines and cascade stages. It achieves a power gain of 10 dB and delivers 1 dB compression and saturation output power levels of 5 dBm and 8 dBm respectively with peak power added efficiency of 7%. While increasing the number of active stages can increase the overall power gain, the output power level is determined by the last stage. Since the last stage gain should not be made less than unity, the power gain - output power tradeoff plays a fundamental role in determining the size of the output stage, and thus puts an upper limit on the maximum output power that can be delivered from a single unit amplifier. Combining the power

from a number of unit amplifiers is necessary to achieving considerably higher output power levels.

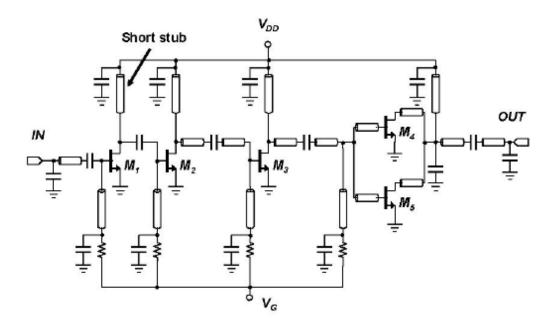

In an attempt to increase the output power delivered from the last stage, the multistage amplifiers implemented in 90 nm bulk CMOS and presented in [18, 19] use two maximum size transistors in parallel in the last stage. Their schematics are shown in Figure 1.7 and Figure 1.8.

Figure 1.7: Schematic of three-stage power amplifier presented in [18]

The first power amplifier delivers 1dB compression and saturation output power levels of +10.5 dBm and +11.3 dBm respectively whereas the second provides power gain of 8 dB and delivers 1dB compression and saturation output power levels of +8.2 dBm and +10.6 dBm respectively.

Figure 1.8: Schematic of three-stage power amplifier presented in [19]

Since the output stage of these amplifiers employ two large size transistors in parallel, the stage just before the last one will need to be composed of a transistor of about the same size in order to guarantee that compression starts at the output stage and is not determined by previous stages. As will be shown in section 2.2, large size transistors exhibit low gain characteristics due to the added parasitic losses in the gate and drain networks. Thus, in order to obtain high gain from the overall amplifier, more than two stages are needed in this topology. This increases the power consumption and reduces the amplifier efficiency. In order to optimize the output power, power gain, and efficiency of the amplifier, the output power from two unit amplifiers each employing a maximum size transistor at the output stage can be combined using on-chip power combiners.

In [12, 13], fully integrated two-way 60 GHz transformer-coupled differential power amplifiers are implemented in 90 nm standard CMOS. Both schematics are shown in Figure 1.9 and Figure 1.10.

Figure 1.9: Schematic of two-way power amplifier presented in [12]

Figure 1.10: Schematic of two-way power amplifier presented in [13]

These power amplifiers use compact on-chip transformer-based power splitters and combiners in order to split and combine the output power of two unit amplifiers. The first delivers 1dB compression and saturation output power levels of +9 dBm and +12.3 dBm respectively while occupying only 660x380 µm² of chip area, whereas the second delivers +12 dBm of saturated output power while occupying only 0.15 mm² of area. While the extensive use of on-chip transformers for power splitting and combining results in a compact two-way power amplifier combining the output power of two unit amplifiers occupying a relatively very small area, this technique has two main disadvantages. First, as the transformer maximum gain is less than unity, power combining through the transformers can result in power loss and thus reduced output power levels and drain efficiency. Second, while combining the output power from two unit amplifiers using transformers is relatively easy, combining the output power from a larger number of unit amplifiers in order to provide even higher output power levels while keeping the transformer loss low becomes increasingly more difficult.

#### 1.3 Research Contributions

This research aims at exploring the challenges facing the design and implementation of 60 GHz power amplifiers in standard 90 nm CMOS processes. The design, modeling, and layout optimization of both passive structures such as transmission lines, capacitors, RF pads as well as active devices operating at 60 GHz are investigated. A low-loss power combining technique taking advantage of millimeter-wave amplifier topologies is presented. Four power amplifiers are implemented in a standard 90 nm 1V CMOS

process. A record performance is reached in terms of 1dB compression and saturation output power.

#### 1.4 Organization of the Thesis

Chapter 2 covers the technology challenges that face the design and implementation of 60 GHz power amplifiers in standard 90 nm CMOS processes. Section 2.1 presents the challenges pertaining to delivering high output power in the presence of the downward scaling of supply voltages. While section 2.2 covers the optimization of the transistor size and layout in the presence of the power gain – output power tradeoff, impedance matching in the presence of the power gain – output power tradeoff is presented in section 2.3. Power combining techniques as a means to increasing the output power of power amplifiers is discussed in section 2.4. The modeling methodology of passive structures and active devices at 60 GHz is presented in chapter 3. The design and modeling of passive structures is discussed in detail in chapter 4. Transmission lines, capacitors, and RF Ground-Signal-Ground pads are covered in sections 4.1, 4.2, and 4.3 respectively. Chapter 5 presents the design and modeling of 60 GHz active devices. The transistors design and layout optimization are covered is section 5.1, whereas small signal and large signal modeling are discussed in sections 5.2 and 5.3 respectively. Chapter 6 presents the implementation of two simple circuits in order to verify the modeling of passive structures and active devices up to 60 GHz. The measurement and simulation results of a Wilkinson power combiner and a simple 60 GHz amplifier are presented in sections 6.1 and 6.2 respectively. Four 60 GHz power amplifiers are presented in chapter

7. A four-way power amplifier is discussed in section 7.1, and three different two-way power amplifiers are presented in sections 7.2, 7.3, and 7.4. The measurement setup is described in section 7.6. Conclusions are given in chapter 8.

# CHAPTER 2 TECHNOLOGY CHALLENGES

## 2 Technology Challenges

CMOS technology scaling has resulted in transistors with increasingly higher  $f_T$  and unity power gain frequency ( $f_{max}$ ) such that the maximum available gain at frequencies around 60 GHz has become high enough to implement 60 GHz CMOS transceivers at the 130 nm technology node and beyond. However, many challenges still exist especially for implementing mm-wave power amplifiers. First, the low supply voltage, thin gate oxide, and low breakdown voltage that accompany smaller technology nodes make it harder to achieve high output power levels. Second, the power gain – output power tradeoff due to transistor sizing that presents itself at mm-wave frequencies poses an upper limit on the maximum transistor size that can be achieved with reasonably high gain and thus on the maximum output power of a single transistor. As a result, power combining becomes necessary to achieve high output power levels and presents the next challenge. Moreover, the power gain - output power tradeoff due to impedance matching makes it more challenging to achieve high output power levels with reasonable power gain from a single stage amplifier.

This chapter discusses the above mentioned challenges that face mm-wave power amplifiers design. Section 2.1 shows how decreasing supply voltages with smaller CMOS processes technology nodes necessitates the design of ever larger transistors in order to obtain high output power levels. Then, section 2.2 discusses how to optimize the power transistor size in the presence of the power gain – output power tradeoff. Section 2.3 investigates the power gain – output power tradeoff that results from impedance matching in transistors operated at mm-wave frequencies, and finally power combining as a way to

achieve higher output powers is presented in section 2.4. The challenges in mm-wave modeling of passive structures and active devices are presented in chapters 4 and 5 respectively.

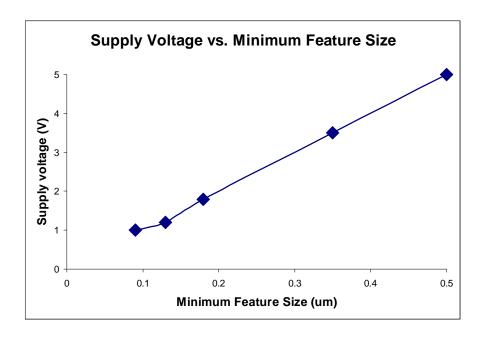

#### 2.1 Low Supply Voltage

Besides enabling operation at 60 GHz, CMOS technology scaling to 90 nm and beyond makes it harder to deliver high output power due to lower supply and breakdown voltages. As shown in Figure 2.1, the supply voltage has been decreasing as smaller technology nodes are introduced, although this trend has slowed considerably with the most recent processes. As transistors channel lengths are getting smaller, thinner oxides are required in order for the gate to control the channel which results in lower breakdown voltage. This necessitates the use of lower supply voltages. In order to keep the transistor current drive capability high, the overdrive voltage  $(V_{GS} - V_{th})$  has to be kept high. As the transistor gate to source voltage  $V_{GS}$  is decreasing due to supply voltage scaling, the threshold voltage  $V_{th}$  has to be reduced. However, a lowering of the threshold voltage results in a considerable increase in the transistor leakage current, which has recently caused a deceleration in voltage scaling. The already low supply voltages make it considerably difficult to deliver high output power. The process used in this work dictates a 1 V supply voltage.

Figure 2.1: Supply voltage vs. CMOS process minimum feature size

Since the output power delivered by a transistor to a given load is limited by

$$P_{out} < V_{DD}I_Q \tag{2.1}$$

where  $V_{DD}$  is the supply voltage and  $I_Q$  is the transistor bias current, as the voltage is decreasing, the amplifier current drive capability has to be increased in order to keep the delivered power unchanged. The DC current in a CMOS transistor operating in the saturation region is [20]

$$I_D = \frac{1}{2}K'\frac{W}{L}(V_{GS} - V_{th})^2$$

(2.2)

where K' is the process transconductance and W and L are the transistor gate width and channel length respectively. K' and  $V_{th}$  are technology constants,  $V_{GS}$  is determined by the supply voltage, and the minimum channel length is usually used in order to maximize the transistor  $f_T$  and  $f_{max}$ . Thus, in order to increase its current drive capability, the

transistor width W has to be increased proportionately since all other parameters are fixed either by the technology or the design.

#### 2.2 Transistor Sizing in the Power Gain - Output Power Tradeoff

We have seen in the previous section that delivering high output power in the presence of supply voltage downward scaling requires an increase of the transistor total width, W. Since the transistor total effective width equals the number of fingers multiplied by the finger width, this can be achieved through either increasing the finger width, or increasing the number of fingers, or both. However, optimizing either the finger width or the number of fingers leads to a power gain — output power tradeoff. Optimization of the finger width is covered in section 2.2.1 while optimizing the number of fingers is discussed in section 2.2.2.

#### 2.2.1 Optimization of Finger Width

In multi-finger CMOS transistors, a larger finger width results in higher gate resistance. This is because the gate resistance of each individual finger behaves as a distributed RC network which can be approximated by [20, 21]

$$R_g = \frac{R_{poly}W_F}{3n^2L} \tag{2.3}$$

where  $R_{poly}$  is the polysilicon gate sheet resistance,  $W_F$  is the finger width, L is the channel length, and n=1,2 depending on the number of gate contacts. In turn, a higher gate resistance, while it does not affect the  $f_T$  of the transistor because  $f_T$  can be approximated as [23]

$$f_T \approx \frac{g_m}{C_{gs}} \tag{2.4}$$

where  $g_m$  is the transistor transconductance and  $C_{gs}$  is its gate to source capacitance, and thus is independent of the gate resistance, it introduces additional power losses and causes a reduction in the transistor  $f_{max}$  and maximum stable gain (MSG) since  $f_{max}$  can be approximated as [24-26] (neglecting the drain resistance and substrate losses)

$$f_{max} = \frac{f_T}{2\sqrt{R_g\left(g_m \frac{C_{gd}}{C_{gg}}\right) + \left(R_g + r_{ch} + R_s\right)g_{ds}}}$$

(2.5)

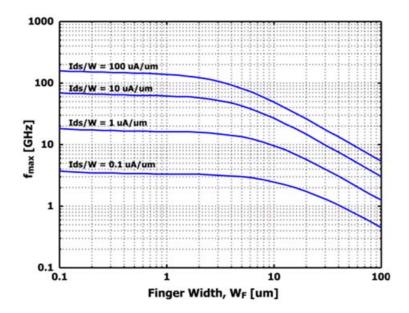

where  $g_m$  is the transistor transconductance,  $C_{gg} = C_{gs} + C_{gd}$  is its total gate capacitance,  $C_{gd}$  and  $C_{gs}$  are the gate to drain and gate to source capacitors respectively,  $R_g$ ,  $r_{ch}$ , and  $R_s$  are the gate, channel, and source resistances respectively, and  $g_{ds}$  is the transistor output conductance. It is shown in Figure 2.2 from [27] that a transistor  $f_{max}$  decreases as its finger width increases. Thus, maximizing  $f_{max}$  places an upper limit on the maximum finger width of a transistor and thus on its output power capability. It can be noticed from the figure that  $f_{max}$  decreases slowly as the finger width approaches 1  $\mu$ m but it decreases with much a higher slope beyond 1  $\mu$ m. The optimum finger width given the  $f_{max}$  - output power tradeoff is around 1  $\mu$ m. As the frequency of operation in mm-wave CMOS power amplifiers is already a large fraction of  $f_{max}$ , the designer cannot sacrifice significant loss in  $f_{max}$  when optimizing the finger width.

Figure 2.2:  $f_{max}$  vs. finger width [27]

In addition to reducing the transistor  $f_{max}$ , an increase in the transistor finger size can also generally cause a decrease in its maximum stable gain because of the increased gate resistive losses. A very small finger width results in very small gate resistance, which is usually smaller than that required to stabilize the device in the mm-wave band. For a device operated in the conditionally stable state, the calculation of MSG assumes that fictitious loss is added at the gate of the transistor to stabilize it, and therefore increasing the finger width further does not affect MSG. This is the case as long as the device is operated in the conditionally stable regime, i.e. at a frequency below the unconditional stability frequency. This frequency is associated with the kink of the transistor maximum available power gain which is a function of the gate resistance. Three test transistors with 100 fingers each but different finger widths of 1  $\mu$ m, 2  $\mu$ m, and 4  $\mu$ m

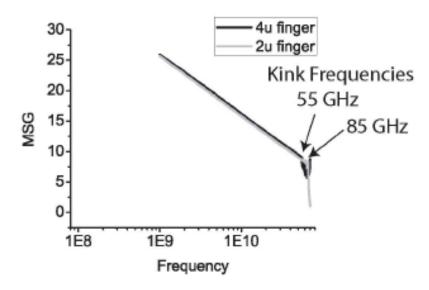

were fabricated and their S-parameters measured. Figure 2.3 shows a comparison of the maximum stable gain for the 2  $\mu$ m and the 4  $\mu$ m finger widths transistors.

Figure 2.3: Measured MSG vs. frequency of 100 fingers, 2μm and 4μm per finger devices [28]

The maximum stable power gains at frequencies before the kink where both devices are conditionally stable are similar and independent of the finger width. However, the kink happens earlier for the 4  $\mu$ m width device and thus the available gain of the 2  $\mu$ m width device is larger beyond this frequency. That is the case because the maximum stable power gain decreases with a much steeper slope after the kink frequency.

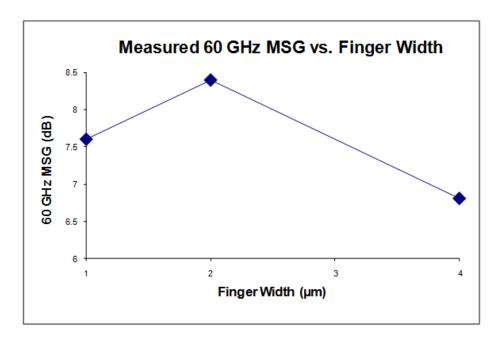

The measured 60 GHz *MSG* of the three devices biased at the same current density is plotted in Figure 2.4.

Figure 2.4: Measured 60 GHz MSG vs. finger width, 100 finger devices

The transistor with 4  $\mu$ m wide fingers clearly shows a lower MSG than the other two. Contrary to the general trend, the transistor with 2  $\mu$ m finger width shows a higher MSG than that with 1  $\mu$ m finger width. The reason for this effect is that since both transistors have the same number of fingers, they both have identical source networks, i.e. identical total source resistances. However, since one transistor has larger finger width, it possesses lower source resistance per width unit, and thus lower source degeneration and higher MSG. The larger gate resistance effect takes over for the case of 4  $\mu$ m finger width and results in overall lower MSG.

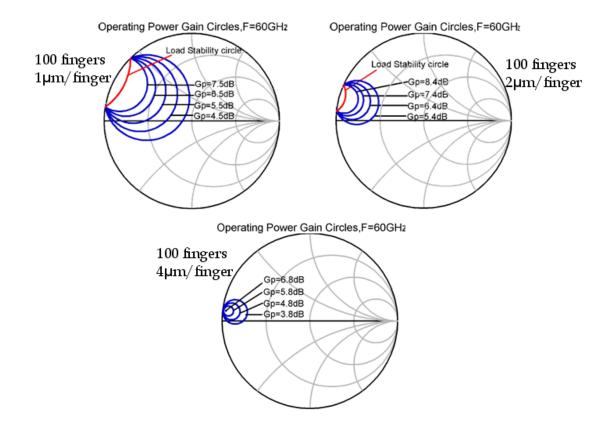

Despite its lower gain, the 100 fingers, 4  $\mu$ m per finger device should in theory be able to deliver four times the output power than the 100 fingers, 1  $\mu$ m / finger device because it would be biased at four times the current. However, as shown from the measured 60 GHz operating power gain circles of the three devices in Figure 2.5, the gain

variation is much more rapid for the 4  $\mu$ m device as we move away from the optimal operating point. The operating power gain circles become much closer to each other as the finger width size increases. This results in lower design robustness in the presence of process variation and modeling inaccuracies.

Figure 2.5: Measured 60 GHz operating power gain circles for different finger widths

#### 2.2.2 Optimization of the Number of Fingers

Once the finger width is optimized to maximize  $f_{max}$ , in order to increase the effective transistor size, the number of fingers should be maximized. When operating at low frequencies, the number of fingers in a CMOS power device can be increased to the limits that process rules permit or until line edge roughness results in large gate resistance

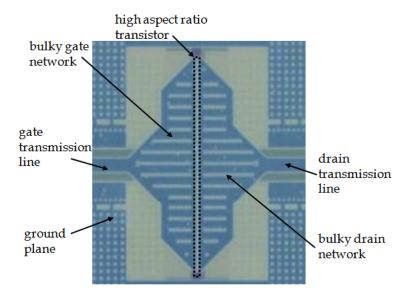

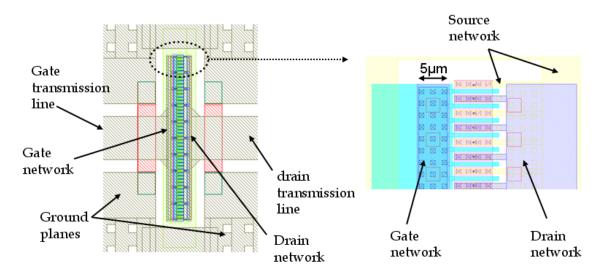

variations. However, this is not the case when operating at mm-wave frequencies. As the number of fingers increases, the height of the transistor layout, as shown in Figure 2.6 and Figure 2.7, grows proportionately and results in large layout aspect ratio. As the number of fingers stays lower than around 100, the size of the gate, drain, and source networks used to connect these ports to all the fingers can be kept relatively small resulting in low gate, drain, and source resistances. This is evident in the layout of the 80 finger transistor in Figure 2.6 where very small gate and drain networks are needed. The transistor length is about 30  $\mu$ m, only three times the width of the transmission line used to connected it to the rest of the circuit.

Figure 2.6: 80 finger transistors layout

Figure 2.7: 400 finger transistors layout

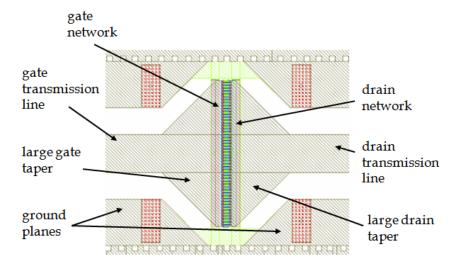

However, as more fingers are added, larger networks with large tapers are needed introducing additional gate and drain resistive losses as well as resistive source degeneration, leading to lower  $f_{max}$  and MSG. This is evident in the layout of the 400 finger device in Figure 2.7. As the transistor length is much larger than the width of the transmission line feeding its gate and drain, large gate and drain networks are needed to reduce the gate and drain inductances.

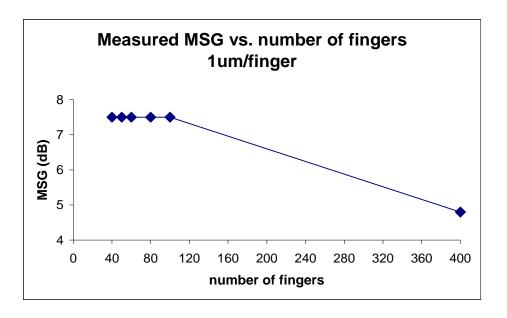

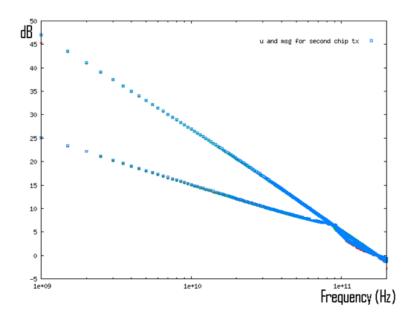

In order to verify this effect, six transistors of varying number of fingers but of the same 1 µm finger width and biased at the same current density level were fabricated and their 60 GHz *MSG* was measured. The results shown in Figure 2.8 clearly indicate a lower *MSG* for the 400 finger device. All the other devices with less than 100 fingers have almost the same value of *MSG*.

Figure 2.8: Measured MSG vs. number of fingers, 1μm/finger, all same current density

### 2.3 Impedance Matching in the Power Gain - Output Power Tradeoff

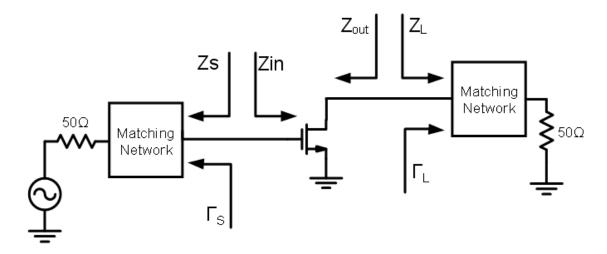

We have seen in section 2.2 that optimizing the transistor size, both its finger width and the number of fingers, leads to a power gain – output power tradeoff. In this section, the power gain – output power tradeoff resulting from the transistor input and output impedance matching is discussed. A transistor is typically driven with a 50  $\Omega$  source and drives a 50  $\Omega$  load as well. However, as shown in Figure 2.9, typically, input and output matching networks are used in order to transform these driving source and output load impedances and provide the power device with source and load impedances that insure stability and maximize power gain and output power. Both the power gain and the output power depend on the transistor load and source reflection coefficients, and thus on its load, source, output, and input impedances. However, the conditions on these impedances

that lead to maximum power gain are different than those that lead to maximum output power, thus the power gain – output power tradeoff. Input and output impedance matching for maximizing the power gain is covered in section 2.3.1 while matching for maximizing the output power is discussed in section 2.3.2.

Figure 2.9: Transistor with input and output matching networks

#### 2.3.1 Matching for Maximum Power Gain

There exist three different power gain definitions that are usually used in conjunction with power amplifiers. These are the transducer power gain  $G_T$ , the power gain, also called the operating power gain,  $G_P$ , and the available power gain  $G_A$ . They are defined as follows: [29]

$$G_T = \frac{P_L}{P_{AVS}} = \frac{power\ delivered\ to\ the\ load}{power\ available\ from\ the\ source} \tag{2.6}$$

$$G_P = \frac{P_L}{P_{IN}} = \frac{power\ delivered\ to\ the\ load}{power\ input\ to\ the\ network}$$

(2.7)

$$G_A = \frac{P_{AVN}}{P_{AVS}} = \frac{power\ available\ from\ the\ network}{power\ available\ from\ the\ source}$$

(2.8)

The source impedance  $Z_S$ , the input impedance  $Z_{in}$ , the load impedance  $Z_L$ , and the output impedance  $Z_{out}$  shown in Figure 2.9 determine the amplifier gain figures defined in equations (2.6)-(2.8). In order to obtain maximum transducer power gain, the source and input impedances should be conjugately matched, as well as the load and output impedances [29]. This is referred to as the simultaneous conjugate matched condition. This is possible only if the device is unconditionally stable, i.e. its stability factor K is larger than unity [29] where

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + -|\Delta|^2}{2|S_{12}S_{21}|}$$

(2.9)

and

$$\Delta = S_{11}S_{22} - S_{12}S_{21} \tag{2.10}$$

Under these conditions, all the power gain definitions are equal, i.e.

$$G_T = G_P = G_A \tag{2.11}$$

and thus

$$G_{T,max} = G_{P,max} = G_{A,max} = \frac{S_{21}}{S_{12}} \left( K - \sqrt{K^2 - 1} \right)$$

(2.12)

The maximum stable gain, MSG, is defined as the value of  $G_{T,max}$  when K=1 which leads to [29]

$$G_{T,max} = \frac{S_{21}}{S_{12}} \tag{2.13}$$

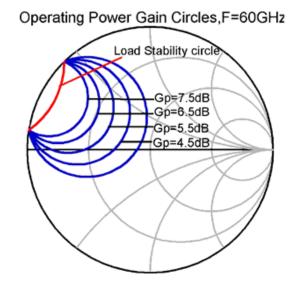

If the device is operated in the conditionally stable case where K < 1, a simultaneous conjugate match is not possible, and it is more useful to consider the operating power gain  $G_P$  in this situation. Even though the value of  $G_P$  can approach infinity when the transistor is operated in the potentially unstable case, values of  $G_P$  that are above the MSG figure of merit result in values of  $\Gamma_L$  and  $\Gamma_S$  that are very close to the unstable region and thus decrease the design robustness. It is shown in [29] that the values of  $\Gamma_L$ that produce a constant power gain lie on a circle, called an operating power gain circle, when plotted on a Smith chart. In order to design an amplifier yielding a given power gain, a number of operating power gain circles corresponding to a transistor in a two-port common-source configuration can be drawn, a value of  $\Gamma_L$  corresponding to a given  $G_P$ value can be chosen from the stable region and not too close to the stability circle, and the output matching network can be designed to transform the load impedance, usually 50  $\Omega$ , into the corresponding  $Z_L$ . The resulting Zin can be calculated. In order to obtain maximum power gain under the given  $\Gamma_L$  chosen, the input matching network can then be designed to conjugately match  $Z_{in}$  and  $Z_{S}$  if this would result in a  $\Gamma_{S}$  in the stable region. 60 GHz operating power gain circles derived from measured S-parameters of a 100 fingers, 1 µm per finger transistor are shown in Figure 2.10.

Figure 2.10: 60 GHz operating power gain circles, 100 fingers, 1  $\mu$ m per finger, 90 nm NMOS transistor

#### 2.3.2 Matching for Maximum Output Power

In power amplifiers, the matching requirements for maximizing the amplifier output power are different than those used for optimizing the amplifier power gain as presented in section 2.3.1. Even though the input matching requirement is the same, i.e. the input matching network needs to be designed such that the transistor source and input impedances are conjugately matched, the output match requirement is different. The transistor load and source impedances should not be conjugately matched as that would lead to sub-optimal output power capability, even in the case where the transistor is operated in the unconditionally stable region where such a match does exist. The exact value of the optimum output power match impedance is best found using load-pull measurement or simulation [30]. In such a measurement, tuning devices are connected

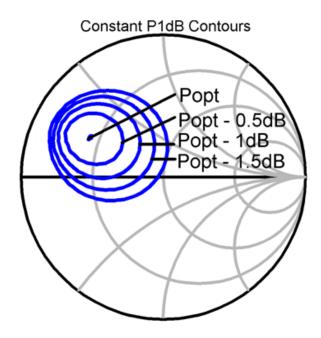

between the driving source and the transistor gate on the input side, as well as between the load and the transistor drain at the output side. The tuners are set such that the load impedance seen by the transistor is varied across a large range while the input is always conjugately matched. The measurement is done at a given frequency. The values of the output power for each load impedance can be plotted on a Smith chart as in Figure 2.11 which shows the results of a load-pull simulation of the 80 fingers, 1  $\mu$ m per finger NMOS transistor. After performing such a measurement, the load impedance corresponding to the maximum output power can be chosen and the output matching network can be designed in order to change the 50  $\Omega$  load to the corresponding impedance.

Figure 2.11: 60 GHz power contours, 100 fingers, 1  $\mu$ m per finger, 90 nm NMOS transistor

#### 2.4 Power Combining

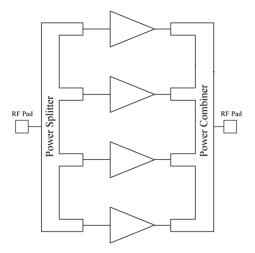

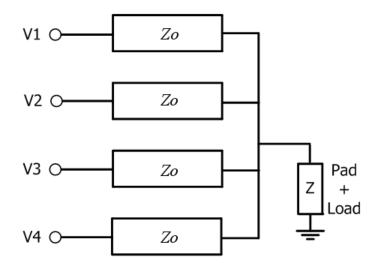

Once the finger width and the number of fingers in a power transistor as well as the input and output matching networks are optimized in the presence of the power gain – output power tradeoff in order to obtain the maximum output power with reasonable power gain, an optimum unit size power amplifier can be designed. In order to increase the output power capability of the amplifier, a number of these unit size amplifiers can be combined to form one high output power amplifier as shown in Figure 2.12. The input power is equally split to the unit amplifiers at the input node using a passive power splitter and the output power of all unit amplifiers is combined using a passive power combiner at the output node.

Figure 2.12: Power combining architecture

There exist different techniques to implement the power splitter and combiner. Wilkinson power combiners are covered in section 2.4.1 while transformer-based power combiners are presented in section 2.4.2. A low loss mm-wave power combining

technique that takes advantage of certain mm-wave amplifier topologies is discussed in section 2.4.3 and used in the power amplifiers implemented in this work and presented in chapter 7.

#### 2.4.1 Wilkinson Power Combiners

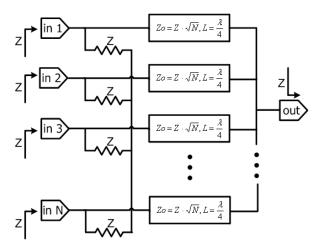

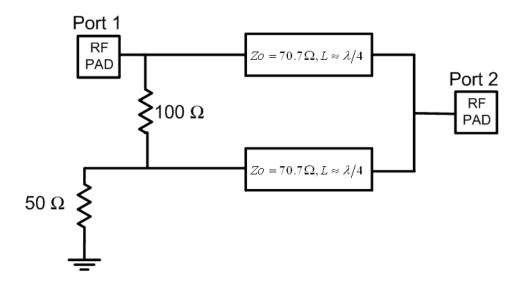

Wilkinson power splitters and combiners [31] are popular because they can simultaneously provide port-to-port isolation, impedance matching, and the ability of being lossless, at least theoretically. In addition to introducing equal phase delay from the output of each amplifier to the combining node so that all signals add in phase, the Wilkinson power combiner transmission lines can be sized such that no impedance transformation is performed through the combiner as shown in Figure 2.13. If the inputs and outputs are reversed, it can also be used as a power splitter. A thorough analysis of Wilkinson power combiners can be found in [34]. At 60 GHz, the on-chip wavelength is around 2.5 mm, enabling the use of integrated Wilkinson power combiners which require transmission line lengths in the order of  $\lambda/4$ .

Figure 2.13: N-way Wilkinson power combiner

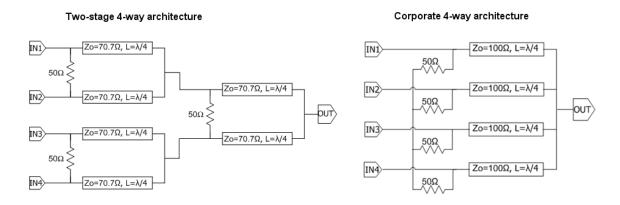

Integrated Wilkinson power splitters and combiners can be used in mm-wave CMOS power amplifiers, but they introduce significant power loss and thus lower the amplifier maximum output power and efficiency. For example, a four-way Wilkinson power combiner can be realized in two stages as shown in Figure 2.14 where two 2-way combiners are used in the first stage and their outputs are combined with one 2-way combiner in the second stage. Another method would be to use the Corporate structure shown in Figure 2.14 where the power of all four stages is combined simultaneously in one stage.

Figure 2.14: Four-way Wilkinson power combiner architectures

Even though the signal travels a total length of  $\lambda/2$  in the two-stage architecture compared to only  $\lambda/4$  in the corporate structure, the former employs transmission lines with characteristic impedance of 70.7  $\Omega$  while the latter uses transmission lines with characteristic impedance of 100  $\Omega$ . If implemented as coplanar waveguides, the higher characteristic impedance transmission lines will exhibit larger gap spacing resulting in higher loss as a larger portion of the electro-magnetic field will enter the substrate. Simulation of the two structures using practical coplanar transmission lines shows that

the two-stage architecture suffers an insertion loss of 2.2 dB while the corporate structure exhibits an insertion loss of only 1.4 dB. This amount of insertion loss can significantly reduce the amplifier output power and efficiency.

#### 2.4.2 Transformer-Based Power Combiners

Transformer based power splitters and combiners have been used at 60 GHz [12, 13] as described in section 1.2. These combiners can simultaneously perform impedance transformation, AC coupling, and DC biasing, in addition to power splitting and combining. They have the advantage of being very compact. At 60 GHz, they can be achieved with one turn of diameter less than 50 µm [12]. It is shown also in [12] that 60 GHz transformer based power combiners can achieve an insertion loss as low as 0.85 dB when terminated with the optimal source and load impedances. Mm-wave transformer-based power combiners can be easily designed for two-way power amplifiers, but they become increasingly more complex when combining power form four or more amplifiers simultaneously.

#### 2.4.3 mm-Wave Power Combining

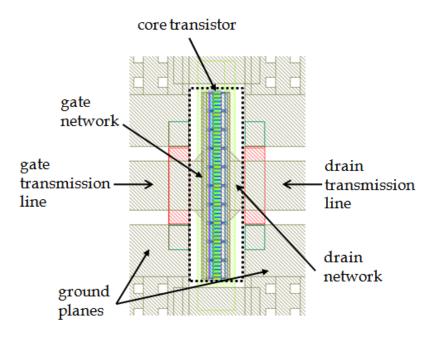

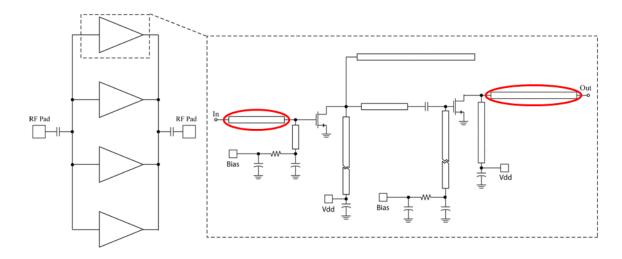

In this work, a low-loss mm-wave power combining technique that takes advantage of mm-wave power amplifier topologies is introduced. Instead of using power splitters and combiners that are extrinsic to the unit amplifiers, these structures can be incorporated into the amplifier input and output matching networks. A schematic of a generic mm-wave power amplifier employing power splitting and combining is shown in Figure 2.15. The input and output matching networks are realized with transmission lines.

They usually present long series transmission lines at the input and output of each unit amplifier.

Figure 2.15: Generic mm-wave four-way amplifier

In order to realize power splitting and combining, these transmission lines of the different unit amplifiers, if long enough, can be routed to feed a common node. The matching networks topology would not need to be modified, but the transmission lines have to be routed in such a way that they all meet at a single point. Note that these transmission lines are present in the unit amplifier even if no power splitting and combining is performed, and thus do not introduce additional insertion loss. The feeding point itself presents additional capacitance and inductance seen by all the amplifiers, and thus the matching networks have to be changed accordingly in order to provide the desired impedance. There is obviously a practical layout limit to the number of amplifiers that can be used in such a scheme. It is shown in section 7.1 that combining the power from four amplifiers is possible. The power combiners resemble Wilkinson power combiners with two main

at the end of the power splitter and combiner transmission lines. This proves crucial in the four-way splitter and combiner where adding those resistors requires long leads that add considerable inductance and capacitance. Second, the transmission lines characteristic impedance and lengths are not chosen in such a way to preserve the impedances. Instead, the transmission lines of the matching networks themselves are used to perform the power splitting and combining as well as the impedance matching at the same time. This considerably reduces the insertion loss and the layout size.

If the transmission lines at the input and output of the unit amplifiers are not long enough, the input and output matching networks can be modified such that the input and output transmission lines are longer. This however would lead to higher loss in the matching networks.

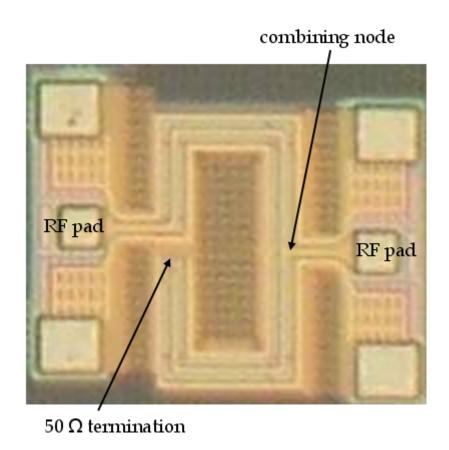

Figure 2.16 shows a schematic of the described power combiner. The transmission lines represent the series lines in the output matching networks of the unit amplifiers. The power combiner drives the output pad and whatever load is presented at the output. The combiner is driven by the drains of the power transistors.

Figure 2.16: Power combiner schematic

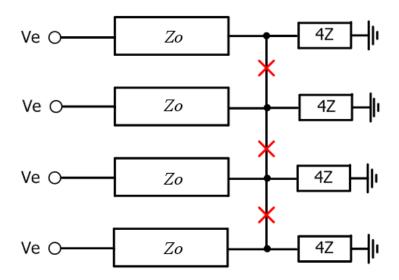

As all unit amplifiers are identical, the four branches of the power combiner are driven with equal amplitude and phase, and thus  $V_1 = V_2 = V_3 = V_4 = V_e$  as shown in Figure 2.17. The load driven by the combiner can be represented as four loads in parallel, each with four times the initial load impedance and driven by one branch of the combiner.

Figure 2.17: Power combiner with even mode excitation

As the voltages on the right side of the transmission lines are of equal amplitude and phase, no current flows in the short circuits that connect the right side of the transmission lines, and thus they can be eliminated without affecting the circuit behavior. This shows that the different amplifiers do not load each other, and each effectively drives four times the load represented by the output pad and the amplifier output load.

#### 2.5 Conclusion

Although CMOS technology scaling at the 130 nm technology node and beyond has resulted in  $f_T$  and  $f_{max}$  levels high enough to implementing 60 GHz CMOS transceivers, mm-wave power amplifiers still face many challenges. Decreasing supply voltages necessitate the design of ever larger transistors in order to obtain high output power levels while the mm-wave power gain – output power tradeoff limits both the maximum finger width and the maximum number of fingers that can be used. Power combining as a way to achieve higher output power levels is investigated and a low-loss power combining technique taking advantage of millimeter-wave amplifiers topologies is presented. Impedance matching in the presence of the power gain – output power tradeoff necessitates the use of multi-stage amplifiers.

As supply voltages scale even further with future CMOS technology nodes, it will become even more challenging to deliver high output power levels and thus power combining will become more crucial. On the other hand, smaller technology nodes will provide higher gain, and thus relatively larger transistors will become feasible as the designer will afford to exchange gain for output power.

## CHAPTER 3 MODELING METHODOLOGY

#### 3 Modeling Methodology

Modeling of passive structures and active devices becomes increasingly more complex and plays an increasingly crucial role at mm-wave frequencies. As the frequency of operation increases, on one hand, losses in passive structures become more pronounced due to skin effect, proximity effect, and substrate loss, and, on the other hand, the maximum gain that can be obtained from active devices decreases as the operating frequency approaches  $f_T$  and  $f_{max}$ . At 60 GHz, the passive losses are substantially high and the active devices gains are considerably low such that circuit design barely meets specifications. Under these conditions, it is important that actual silicon performance be close to the simulated performance. Relatively small deviation between the simulated and the actual performance can result in chip failure because there exists a very small margin between simulation and specifications in the first place. Moreover, standard CMOS processes are in general not intended for operation around 60 GHz but rather at frequencies up to around 10 GHz. Thus, these processes usually ship with models that are accurate up to around 10 GHz, and no substantial effort is made to model them up to 60 GHz. For these reasons, extensive effort is spent in optimizing and modeling passive structures and active devices at mm-wave frequencies. Section 3.1 discusses why custom 60 GHz models are needed. The modeling strategy followed is covered in section 3.2, and the test chips fabricated for the modeling effort are described in section 3.3.

#### 3.1 Need for 60 GHz Models

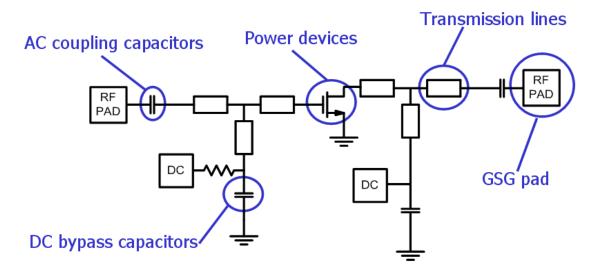

A generic CMOS power amplifier operating at microwave frequencies is shown in Figure 3.1.

Figure 3.1: Schematic of generic amplifier operating at microwave frequencies

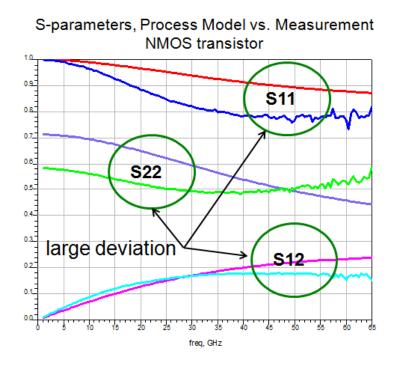

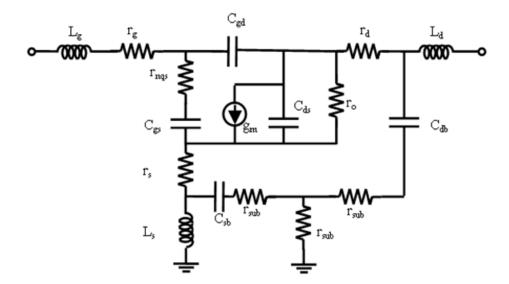

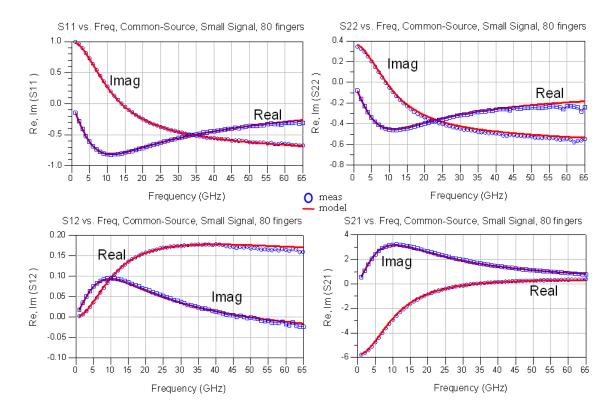

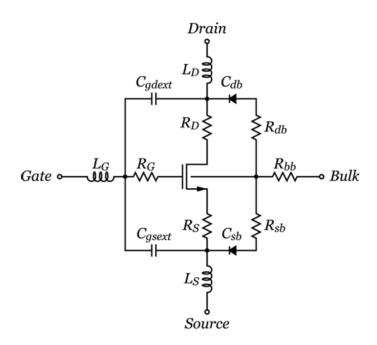

The amplifier is composed of a CMOS transistor, transmission lines, AC coupling and supply-ground bypass capacitors, resistors, RF Ground-Signal-Ground pads, and DC pads. Since the BSIM3V3 transistor models that ship with the employed 90 nm process are inaccurate at 60 GHz, custom models that take into account the extrinsic layout parasitics and are accurate in both small and large signal regimes are needed and discussed later in chapter 5. Figure 3.2 shows the large deviation between the measured S-parameters of a multi-fingered transistor and those simulated with the BSIM3V3 models that ship with the process. Large deviations exist around 60 GHz. Moreover, because the process does not ship with readily available and modeled transmission lines, custom designed transmission lines are modeled and used in the amplifier design. In

order not to use additional mask layers and thus reduce cost, no Metal-Insulator-Metal capacitors are used. Instead, metal multi-finger custom capacitors are designed and modeled to be used for AC coupling and supply-ground bypass. The junctions that connect the components together can result in significant parasitic capacitance and need to be modeled. Finally, RF Ground-Signal-Ground pads are considered part of the design, i.e. they are integrated into the input and output matching networks, and thus their losses are not de-embedded from the S-parameter measurements. Thus, accurate pad models are needed as well.

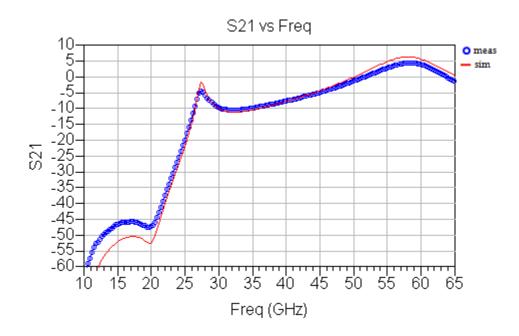

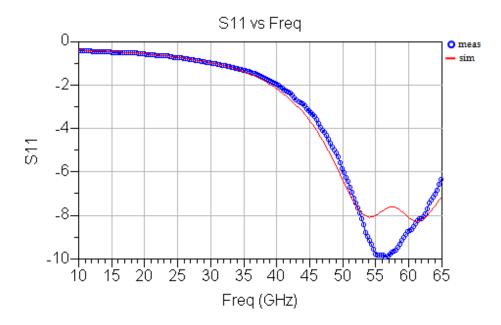

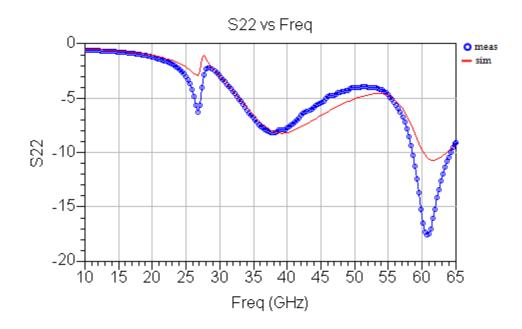

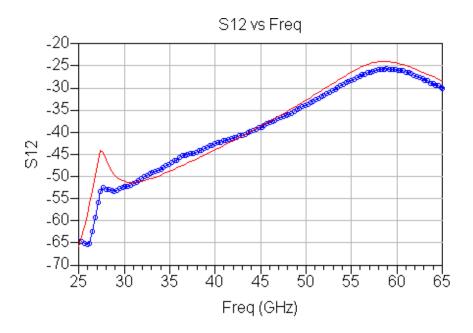

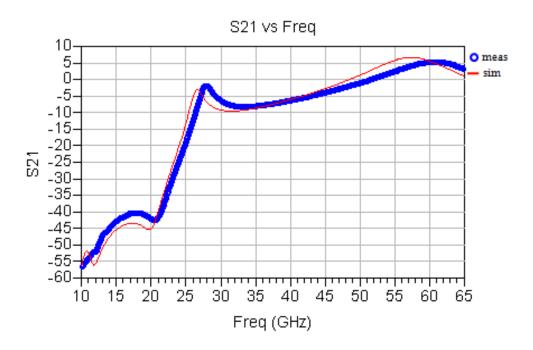

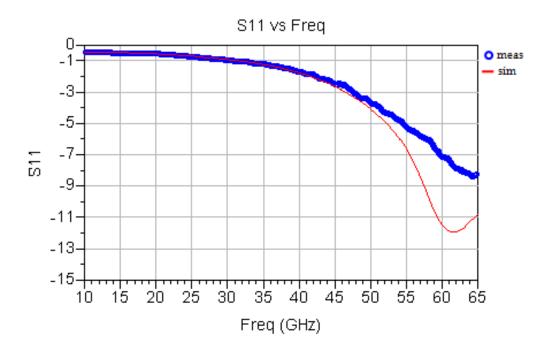

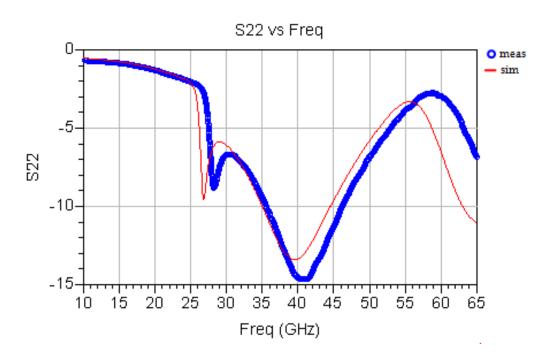

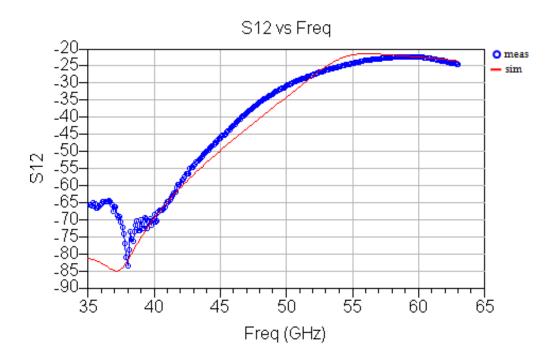

Figure 3.2: Measured vs. process model S-parameters of an NMOS transistor

#### 3.2 Modeling Strategy

In order to achieve good agreement between measurement and simulation at 60 GHz, none of the models that ship with the process were employed. Instead, custom

models were created for each element and used in the simulations. The modeling strategy followed in this work consists in breaking up the amplifier into its basic constituent components, building test structures for each component, measuring their S-parameters at frequencies up to 65 GHz, modeling each component on its own by optimizing the model parameters to fit the measured data, and then putting together the complete model.

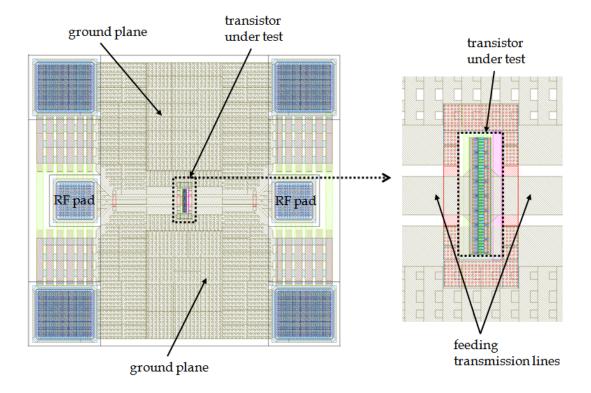

First, test structures were built for each of the basic constituent components of the power amplifier, i.e. active devices, transmission lines, AC coupling capacitors, low and high frequency supply-ground bypass capacitors, resistors, and Ground-Signal-Ground pads. As shown in Figure 3.3, each test structure consists of two RF Ground-Signal-Ground pads, the device under test in between, and coplanar transmission lines connecting the pads to the element under test.

Figure 3.3: Test structure layout

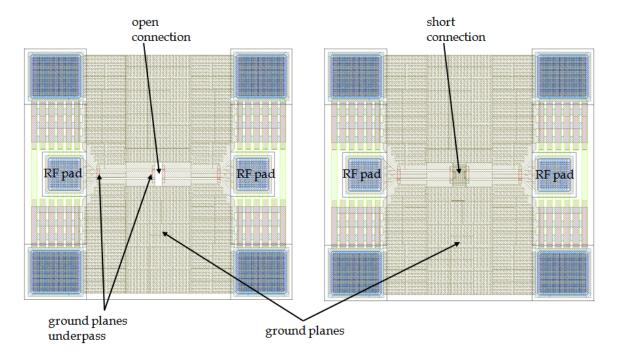

Second, each test structure's S-parameters were measured up to 65 GHz. In order to obtain the S-parameters of the structure of interest excluding the pads and the transmission lines leading to it, the latter two were de-embedded using the "open-short" de-embedding procedure where a pad "open" structure is first measured to obtain the pad admittance, and the pad "short" structure is used to obtain the pad impedance versus frequency. The "open" and "short" structures used in the de-embedding are shown in Figure 3.4. The "open" structure consists of the test structure used to measure the element under test but with the element removed. The "short" resembles the "open" structure but with the ends of the transmission lines connected to their adjacent ground planes.

Figure 3.4: Open and short de-embedding strutures layout

Next, a custom model was created for each component, and its parameter values were optimized in order to reach a good agreement between the simulated and measured S-

parameters. A detailed discussion of the models and fitting procedure for each component are presented in chapters 4 and 5.

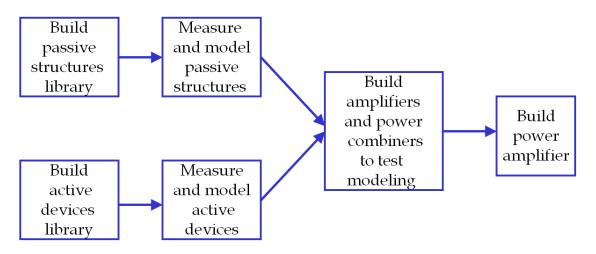

In order to verify the models, a simple one-stage amplifier employing all the above mentioned components as well as a Wilkinson power combiner were built, and their measured performance compared to the simulated performance. These are presented in chapter 6. Once the models were verified, more complex power amplifiers, presented in chapter 7, are built. Figure 3.5 below shows a graphical description of the modeling milestones.

Figure 3.5: Modeling milestones

This modeling methodology results in geometry dependent, non scalable models. In other words, since the model parameter values are optimized through a curve fitting algorithm in order to match the simulated and measured results of a given structure, the values cannot be easily scaled as the structure geometry scales. As a result, only the structures that are built, measured, and modeled can be used in the amplifier design. Thus, in order to provide design flexibility, a large library of passive components and

active devices was built, measured, and modeled. The library is described next in section 3.3.

#### 3.3 Test Chips

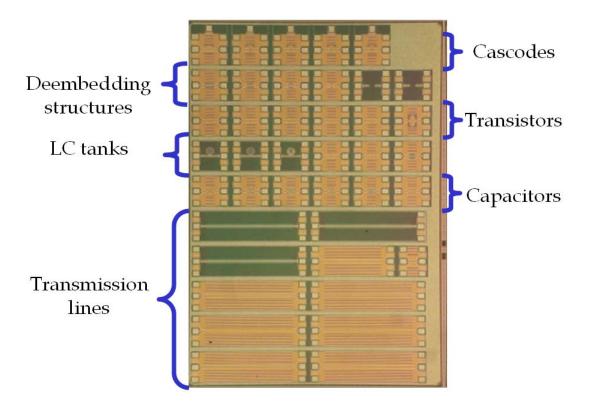

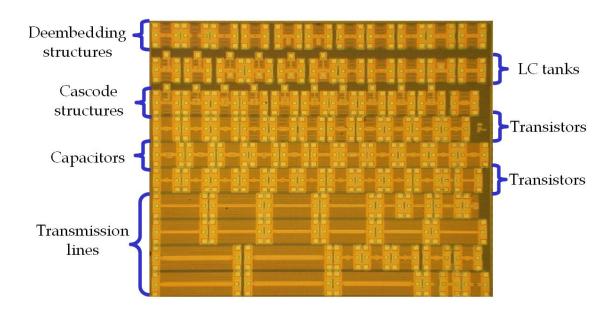

In order to create libraries of passive structures and active devices and to model each basic component on its own, two test chips comprising passive and actives structures of different sizes and types were built and measured. The two test chips die photos are shown in Figure 3.6 and Figure 3.7.

Figure 3.6: Test chip 1

Figure 3.7: Test chip 2

The following is a detailed list of the fabricated test structures:

#### 1. Transistors

- a. Common-source configuration, NMOS, 40 fingers, 1µm per finger

- b. Common-source configuration, NMOS, 50 fingers, 1 µm per finger

- c. Common-source configuration, NMOS, 60 fingers, 1µm per finger

- d. Common-source configuration, NMOS, 80 fingers, 1 µm per finger

- e. Common-source configuration, NMOS, 100 fingers, 1 µm per finger

- f. Common-source configuration, NMOS, 400 fingers, 1 µm per finger

- g. Cascode configuration, NMOS, 20 fingers, 1 µm per finger

- h. Cascode configuration, NMOS, 40 fingers, 1 µm per finger

- i. Cascode configuration, NMOS, 60 fingers, 1 µm per finger

- j. Cascode configuration, NMOS, 80 fingers, 1 µm per finger

- k. Cascode configuration, NMOS, 100 fingers, 1µm per finger

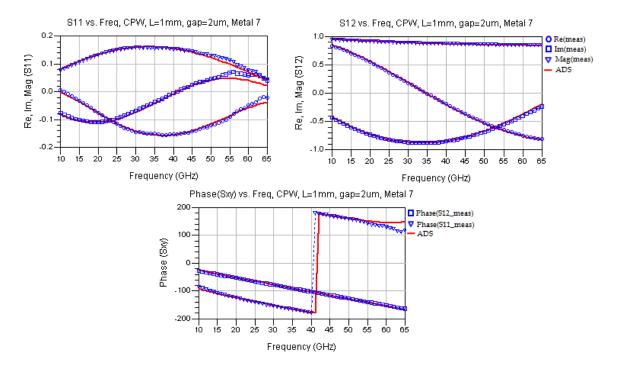

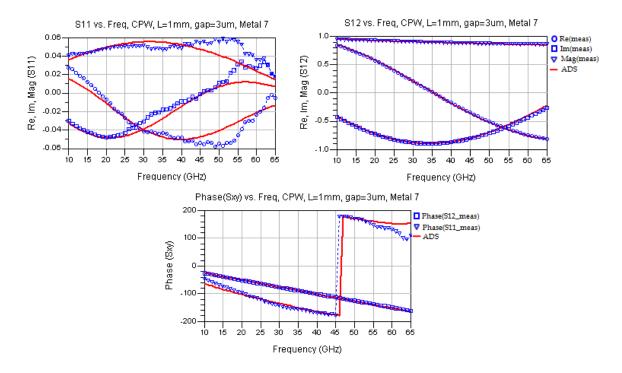

#### 2. Transmission lines

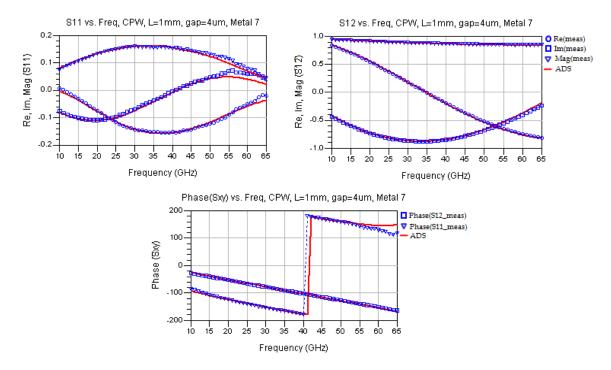

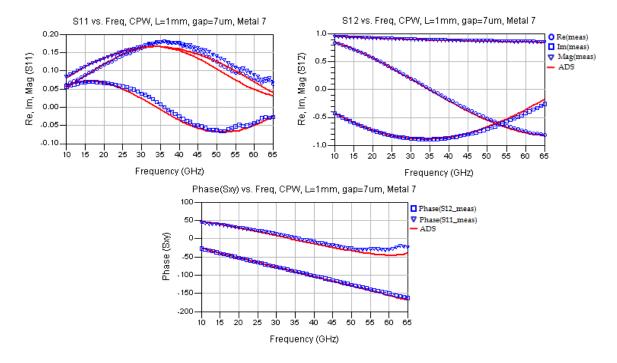

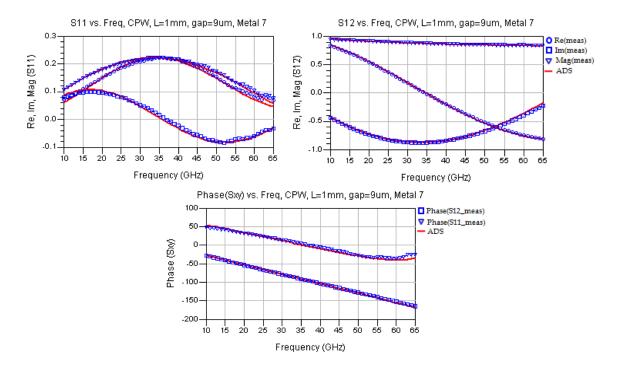

- a. Coplanar, on metal 7, 1mm length, 10 µm metal width, 2 µm gap

- b. Coplanar, on metal 7, 1mm length, 10 µm metal width, 3 µm gap

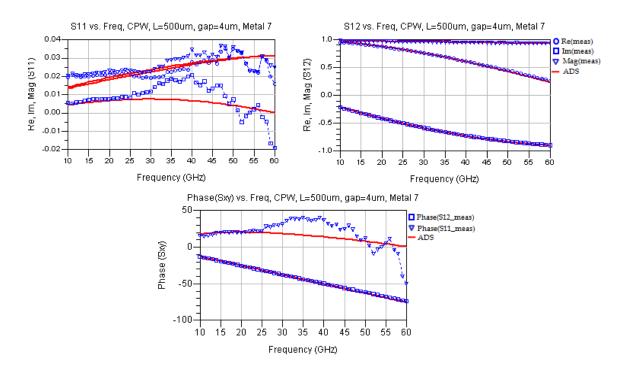

- c. Coplanar, on metal 7, 1mm length, 10 µm metal width, 4 µm gap

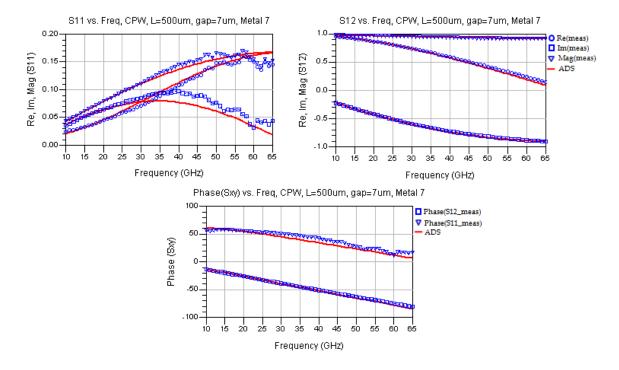

- d. Coplanar, on metal 7, 1mm length, 10 μm metal width, 7 μm gap

- e. Coplanar, on metal 7, 1mm length, 10 µm metal width, 9 µm gap

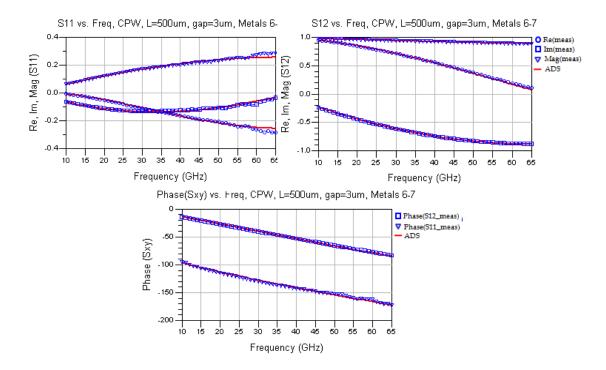

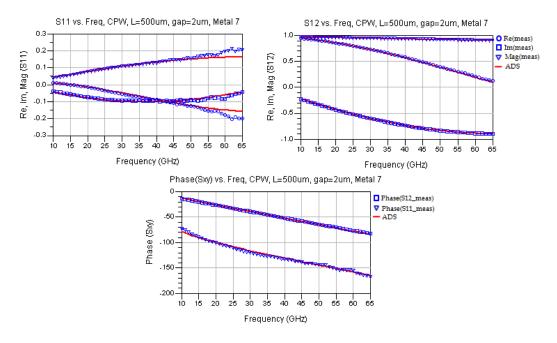

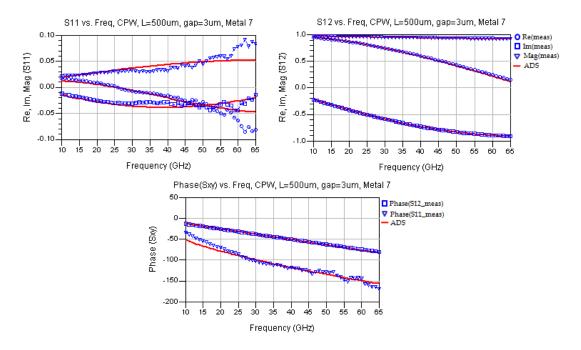

- f. Coplanar, on metal 7, 500 μm length, 10 μm metal width, 2 μm gap

- g. Coplanar, on metal 7, 500 µm length, 10 µm metal width, 3 µm gap

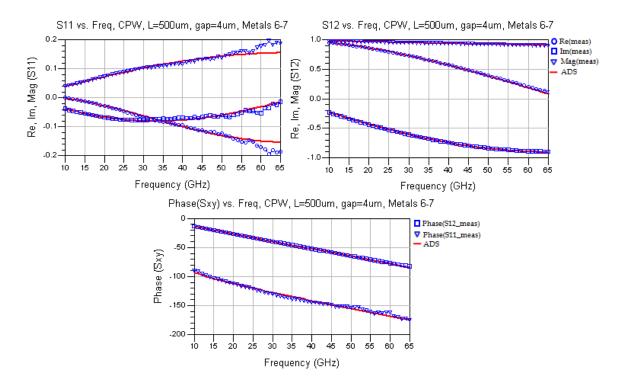

- h. Coplanar, on metal 7, 500 µm length, 10 µm metal width, 4 µm gap

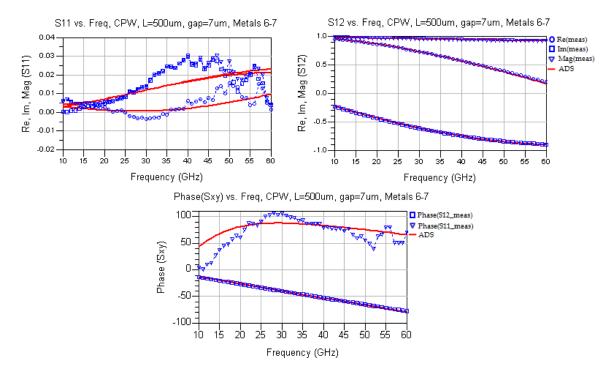

- i. Coplanar, on metal 7, 500 μm length, 10 μm metal width, 7 μm gap

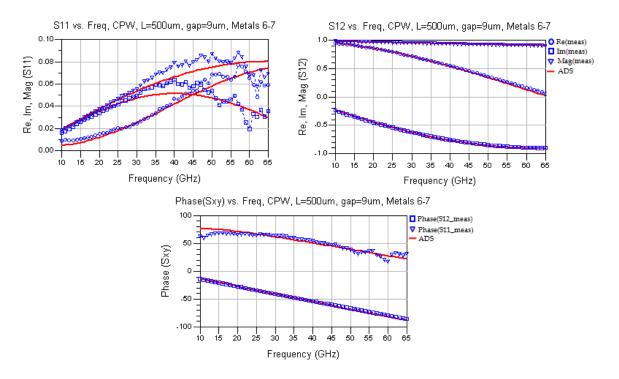

- j. Coplanar, on metal 7, 500 μm length, 10 μm metal width, 9 μm gap

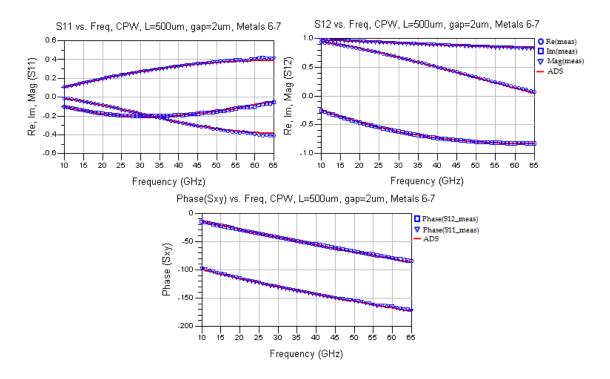

- k. Coplanar, on metals 6 and 7, 500 μm length, 10 μm metal width, 2 μm gap

- 1. Coplanar, on metals 6 and 7, 500 μm length, 10 μm metal width, 3 μm gap

- m. Coplanar, on metals 6 and 7, 500 μm length, 10 μm metal width, 4 μm gap

- n. Coplanar, on metals 6 and 7, 500 μm length, 10 μm metal width, 7 μm gap

- o. Coplanar, on metals 6 and 7, 500 μm length, 10 μm metal width, 9 μm gap

- p. Coplanar, on metal 7, 100 µm length, 10 µm metal width, 2 µm gap

- q. Coplanar, on metal 7, 100 µm length, 10 µm metal width, 3 µm gap

- 3. AC coupling capacitors

- a. Multi- finger, metals 1-5, 10 μm x 12 μm

- b. Multi- finger, metals 1-5, 10 µm x 25 µm

- c. Multi- finger, metals 1-5, 25 μm x 25 μm

- d. Multi- finger, metals 1-5, 25 μm x 50 μm

- e. Multi- finger, metals 1-5, 50 μm x 25 μm

- f. Multi- finger, metals 1-5, 50 μm x 50 μm

- 4. Supply-ground bypass capacitors

- a. Multi-finger, 1-port, 50 μm x 25 μm

- b. Multi-finger, 1-port, 50 μm x 50 μm

- 5.  $50 \Omega$  resistor

- 6. 60 GHz LC tanks

- 7. De-embedding structures

#### 3.4 Conclusion

Modeling of passive structures and active devices plays an increasingly crucial role at mm-wave frequencies as the passive losses due to skin effect, substrate loss, and proximity effects are substantially high and the active devices gains are considerably low such that a very small error margin between measurement and simulation can be tolerated.

The modeling strategy followed in this work consists in breaking up the amplifier into its basic constituent components, building test structures for each component, measuring their S-parameters at frequencies up to 65 GHz, modeling each component on

its own by using custom models and optimizing the model parameters to fit the measured data, and then putting together the complete model.

As CMOS technology scales further, future processes can provide higher gain and thus higher modeling error margin can be tolerated, simplifying the modeling process.

# CHAPTER 4 PASSIVE STRUCTURES DESIGN AND MODELING

#### 4 Passive Structures Design and Modeling

This chapter discusses the design, optimization, and modeling of mm-wave passive structures in detail. The design and modeling of transmission lines, capacitors, and RF pads are covered in sections 4.1, 4.2, and 4.3 respectively.

#### 4.1 Transmission Lines Design and Modeling

Transmission lines play a central role in mm-wave amplifiers. As the frequency of operation increases and the wavelength decreases, electrically long transmission lines such as quarter wave become short enough to be integrated on-chip. Moreover, as the actual physical circuit size approaches a substantial fraction of the signal wavelength when operating at frequencies as high as 60 GHz, the lumped circuit assumption breaks down, and all routing elements should be designed and treated as transmission lines.

Transmission line concepts are covered in section 4.1.1. The advantages of using transmission lines in lieu of lumped passive elements will be discussed in section 4.1.2 and a comparison between coplanar and microstrip transmission lines is given in section 4.1.3. Then, in section 4.1.4, a library of transmission lines of different geometries that are built, measured, and modeled is described. Finally, transmission lines modeling methodology with Agilent's Automated Design System (ADS) [32] and Ansoft's High Frequency Structure Simulator (HFSS) [33] is presented in sections 4.1.5 and 4.1.6 respectively.

#### **4.1.1 Transmission Line Concepts**

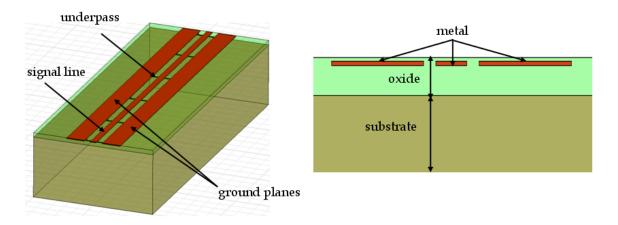

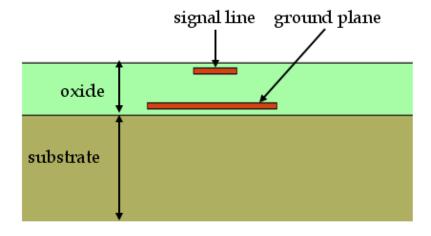

There exist a variety of transmission lines types. However, the coplanar and the microstrip transmission lines shown in Figure 4.1 and Figure 4.2 are the most appropriate to be integrated on silicon and used in amplifier design.

Figure 4.1: Layout of a coplanar transmission line

Figure 4.2: Cross sectional view of the layout of a microstrip transmission line

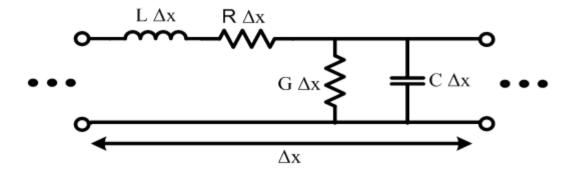

A transmission line is a distributed structure whose voltages and currents can vary in magnitude and phase over length. It can be characterized by its equivalent distributed circuit model shown in Figure 4.3 [29]

Figure 4.3: Transmission line distributed model

The short piece of the transmission line of length  $\Delta x$  is modeled as a frequency dependent lumped element circuit where R, L, G, and C are per unit length quantities defined as follows [34]:

R = series resistance per unit length

L = series inductance per unit length

G =shunt conductance per unit length

C =shunt capacitance per unit length

The R, L, G, and C parameters that characterize a transmission line can be related to its characteristic impedance ( $Z_o$ ) and its complex propagation constant ( $\gamma$ ) by: [35]

$$Z_{o} = \sqrt{\frac{R + j\omega_{o}L}{G + j\omega_{o}C}}$$

$$\gamma = \sqrt{(R + j\omega_{o}L)(G + j\omega_{o}C)} = \alpha + j\beta$$

(4.1)

where  $\alpha$  and  $\beta$  are the attenuation and phase constants. For low loss lines,  $\alpha$  and  $\beta$  can be approximated as follows: [35]

$$lphapprox rac{R}{2Z_o} + rac{GZ_o}{2}$$

(4.2)

$$eta = rac{2\pi}{\lambda_a} = \omega_o \sqrt{LC}$$

When transmission lines are fabricated on high resistivity substrates such as GaAs, the shunt conductance is essentially zero and drops from the attenuation constant equation which becomes a function of the series unit resistance only. However, silicon substrates have relatively low resistivity of about 10  $\Omega$ -cm which leads to non-negligible shunt conductances, and thus both R and G remain combined in the attenuation constant in equation (4.2). In order to de-couple the two loss mechanisms and make it easier to discern the relative importance of R and G, the following four real parameters that characterize the transmission line are proposed in [4]:

$$Z \equiv \sqrt{L/C}$$

$$\lambda \equiv \frac{2\pi}{\omega_o \sqrt{LC}}$$

$$Q_L \equiv \omega_o L/R$$

$$Q_C \equiv \omega_o C/G$$

(4.3)

$\mathcal{Q}_{L}$  and  $\mathcal{Q}_{C}$  are referred to as the inductive and capacitive quality factors respectively.

#### **Quality Factor Metrics**

When a transmission line is used as a resonator, the relevant definition of the quality factor (Q) of the line is [35]

$$Q_{res} = \omega_o \frac{average \ energy \ stored}{average \ power \ loss} = \frac{\omega_o(W_m + W_e)}{P_L}$$

(4.4)

where  $\omega_o$  is the resonance frequency,  $W_m$  and  $W_e$  are the average magnetic and electric energy stored, and  $P_L$  is the average power dissipated in the line.  $Q_{res}$  can be related to  $Q_L$  and  $Q_C$  by [35]

$$\frac{1}{Q_{res}} \approx \frac{1}{Q_L} + \frac{1}{Q_C} \tag{4.5}$$

If on the other hand a transmission line is used as an inductive element whether to resonate with a transistor capacitance or as a matching network element, most of the energy stored in the line is magnetic, and thus a more meaningful definition of its quality factor is [4]

$$Q_{net} \equiv 2\omega_o \frac{net\ energy\ stored}{average\ power\ loss} = \frac{2\omega_o(W_m - W_e)}{P_R + P_G} \tag{4.6}$$

where  $P_R$  and  $P_G$  are the average power dissipated in the resistance and conductance respectively. It is shown in [4, 27] that  $Q_{net}$  can be related to the inductive and capacitive quality factors  $Q_L$  and  $Q_C$  as

$$\frac{1}{Q_{net}} = \frac{1}{\eta_L Q_L} + \frac{1}{\eta_C Q_C}$$

(4.7)

where

$$\eta_L = 1 - \frac{W_e}{W_m}$$

$$\eta_C = \frac{W_m}{W_e} - 1$$

(4.8)

Thus, if the transmission line is used as an inductive element where  $W_m>>W_e$ , we get  $Q_{net}\approx\eta_LQ_L$  and therefore the loss in the line is determined primarily by  $Q_L$ . If on the other hand the transmission line is used as a capacitive element where  $W_e>>W_m$ , we get  $Q_{net}\approx\eta_CQ_C$  and therefore the loss in the line is determined primarily by  $Q_C$  [4, 36].

#### 4.1.2 Advantages of Using Transmission Lines

The on-chip signal quarter wavelength at 60 GHz is around 625 µm which makes possible the realization of integrated electrically long transmission lines on chip. The use of integrated transmission lines opens up a realm of opportunities because it means that complete matching networks, power splitters, and power combiners can be designed

using solely transmission lines and integrated on chip. Transmission lines can be designed to obtain specific characteristic impedances leading to optimized network design. Short sections of transmission lines can be used as capacitors or inductors. Compared to lumped spiral inductors, the transmission lines reactance is more predictable, less influenced by surrounding structures, and provides better isolation.

The use of transmission lines in mm-wave circuits solves the problem of ambiguity as to how the reference planes are defined. Since the ground planes and the signal line in a transmission line are in close proximity and the distance between them is well defined, the return signal path is well known and thus the resulting reactances are well predicted. The well defined return path also reduces magnetic and electric field coupling to adjacent structures.

Moreover, since well modeled transmission lines are used as interconnect between all the basic components, i.e. transistors, capacitors, pads, etc, no parasitic interconnect is left un-modeled. This proves crucial at mm-wave frequencies where short parasitic metal slabs of impedances less than 100 pH can result in large deviation between simulation and measurement results.

Furthermore, transmission lines are scalable in length, i.e. a transmission model that is verified for a 1 mm line would work with any transmission line length. As a result, precise desired impedances can be realized by just changing the length of a given transmission line. This inherent scalability of transmission lines also simplifies simulation and design.

## 4.1.3 Coplanar vs. Microstrip Transmission Lines

Microstrip transmission lines can be realized on silicon by using the top metal layer for the signal line and the lowest metal layer as the ground line. This geometry results in an easy way to connect the transmission lines to the rest of the circuit elements since all signal lines will reside in the top metal layer with a large ground shield underneath. However, since the distance between the metal layers is fixed, microstrip transmission lines provide only one geometry variable, the signal line width, that affects both the line loss as well as the distributed inductance and capacitance along the line. As the distance between the top and the lowest metal layer in standard CMOS processes is usually small, in the order of 4 µm, microstrip transmission lines in such processes enjoy large capacitance per unit length while they suffer from small inductance per unit length. According to equation (4.3), this results in large capacitive and low inductive quality factors. If the signal line width is decreased in order to increase the distributed inductance in an attempt to increase the inductive quality factor, the resistive losses in the line will increase and as a result will lead to low quality factors.

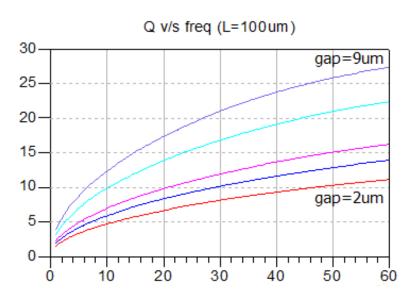

Coplanar transmission lines [37, 38], on the other hand, reside entirely in the top metal layer and their distributed inductance and capacitance are largely determined by the gap spacing between the signal line and the ground planes. This provides an additional degree of freedom in their design as the signal line width can be optimized for minimum resistive losses and the gap spacing can be optimized for the  $Q_L$ - $Q_C$  tradeoff. Since transmission lines in amplifiers are usually used to resonate transistor capacitances and serve as inductive elements in matching networks, coplanar transmission lines are

preferred over microstrip transmission lines in mm-wave design. As shown in Figure 4.4, inductive quality factors of about 27 are achievable at 60 GHz for coplanar transmission lines with gap spacing of 9  $\mu$ m. Moreover, since the gap spacing in coplanar transmission lines is a lateral dimension determined by lithography while in a microstrip it is a vertical dimension, the characteristic impedance of coplanar lines are more predictive and constant over process than that of microstrip lines.

Figure 4.4: Simulated coplanar transmission lines inductive quality factor vs. frequency

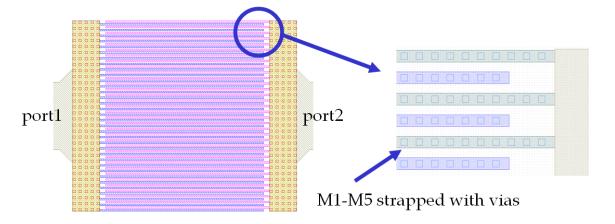

## 4.1.4 Transmission Lines Library

Two sets of coplanar transmission lines have been built. The first set resides exclusively in the top metal layer, M7, i.e. both the signal line and the ground planes are composed of M7 only. In an attempt to achieving lower resistance and thus higher quality factors, the second set of transmission lines utilizes the top metal layer M7 as well as the layer beneath it, M6. Both the signal line and the ground planes are composed of both

metal layers strapped with large density vias. Using M6 effectively increases the metal thickness. Thus, besides resulting in lower metal resistivity, it also results in large capacitance per unit length along the transmission line. This in turn results in lower transmission line characteristic impedance since

$$Z_o = \sqrt{\frac{R + j\omega_o L}{G + j\omega_o C}}$$

(4.9)

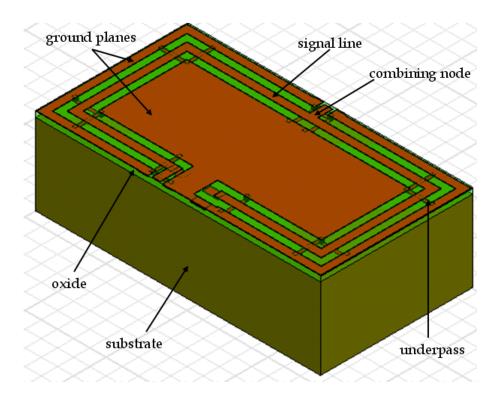

In this case, in order to realize a given impedance, a longer transmission line that utilizes M6 and M7 is needed than that utilizing only M7 which may result in higher overall loss. For each set, transmission lines of five different geometries are built. All transmission lines use  $10~\mu m$  wide signal lines to reduce the resistive losses with wide ground planes, but the gap spacing between the signal line and the ground planes are 2, 3, 4, 7, and  $9~\mu m$ . Underpasses residing in the lowest two metal layers, M1 and M2, connecting the two ground planes are placed at  $100~\mu m$  intervals. They serve to keep the two ground planes at the same potential level and suppress higher order and undesired modes of propagation.

In order to model the transmission line losses accurately, the transmission lines that are built and measured need to have significantly larger loss than the test structure pad losses. Even though the pad losses are de-embedded from the test structure S-parameter measurements, if the transmission line structure itself have very small loss, de-embedding errors will constitute a large fraction of the actual transmission line loss and result in inaccurate results. It has been verified that transmission lines between 500  $\mu$ m and 1 mm of length lead to robust results.

## 4.1.5 Transmission lines modeling with ADS

The ADS suite from Agilent provides a simple, length scalable, electric transmission line model that captures the line high level behavior and proved to be accurate at frequencies as high as 60 GHz. The model possesses a number of advantages over other simulation tools.

First, ADS provides a clear advantage when it comes to speed of simulation. The ADS model simulation is orders of magnitude faster than that resulting from other tools, such as Agilent's High Frequency Structure Simulator (HFSS). This becomes more pronounced as the number of transmission lines increases. The four-way power amplifier presented in section 7.1 uses upward of 30 transmission lines of different sizes and geometries. Simulating the entire amplifier with ADS can be performed in a few seconds, while simulating only the transmission lines in HFSS would take hours or days to complete.

Second, another main advantage the ADS model offers is length scalability. The model is scalable in length, i.e., all its defining parameters (except obviously the length parameter) are independent of the transmission line length. Thus, the model can be optimized to fit the measured S-parameters of specific transmission line geometry of some given length, say 1 mm, and then it can be used to model a transmission line of the same geometry, but of any length, by just changing its length property. This significantly eases the overall amplifier design as transmission lines lengths often need to be changed multiple times in a trial and error fashion in order to realize a given impedance.

The third important advantage that the ADS transmission line model presents is its compatibility with the ADS optimization engine. ADS provides an optimization engine in the same suite where its transmission line model resides. Thus, using ADS, the transmission lines length in a given circuit can be all optimized at once in order to obtain specific performance criteria. For example, a complete amplifier model can be built where matching networks and interconnects employ transmission lines, and the transmission lines lengths can be optimized in order to obtain given overall S-parameters and stability criteria.

On the other hand, the ADS transmission line model presents one main disadvantage. The model is geometry dependent, i.e. once the model is optimized to fit a given transmission line, the model can be employed only to arbitrary length of the same transmission line cross-sectional geometry. As a result, only transmission lines geometries that have been built, measured, and modeled can be used.

The parameters of the ADS two-port transmission line model (TLINP) are tabulated in Table 4.1.

| Model parameter | Description                           |

|-----------------|---------------------------------------|

| Zo              | Characteristic impedance              |

| L               | Length                                |

| Keff            | Oxide effective relative permittivity |

| A               | Skin effect constant                  |

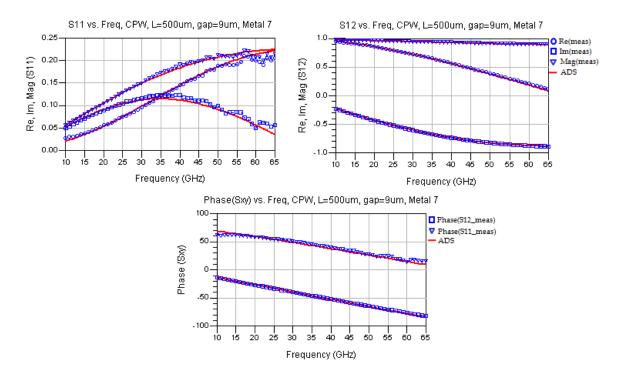

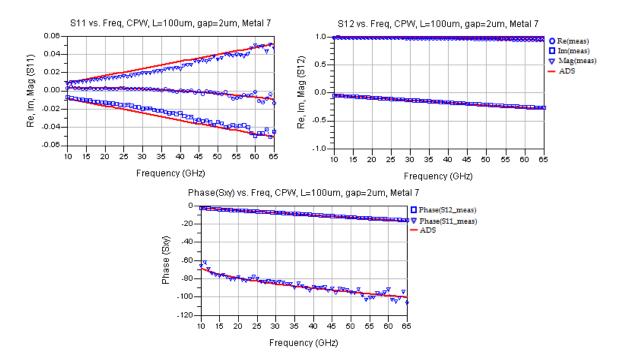

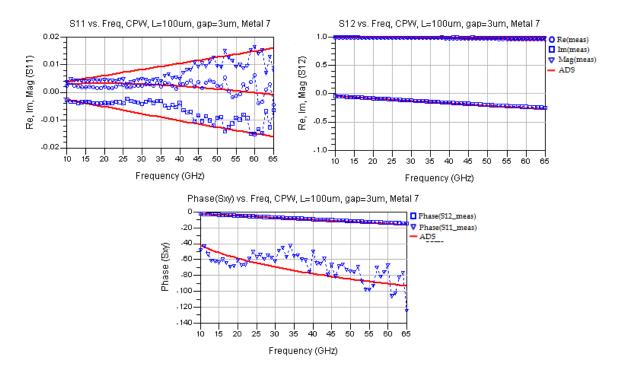

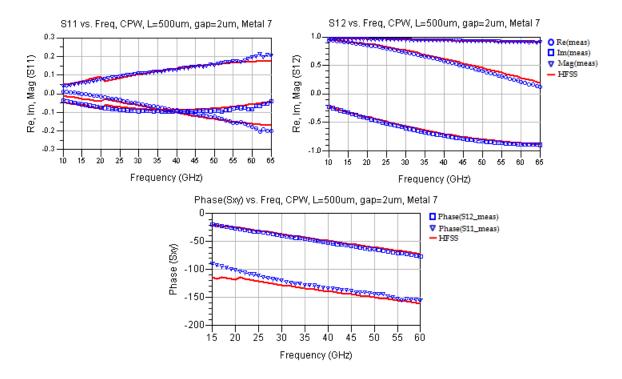

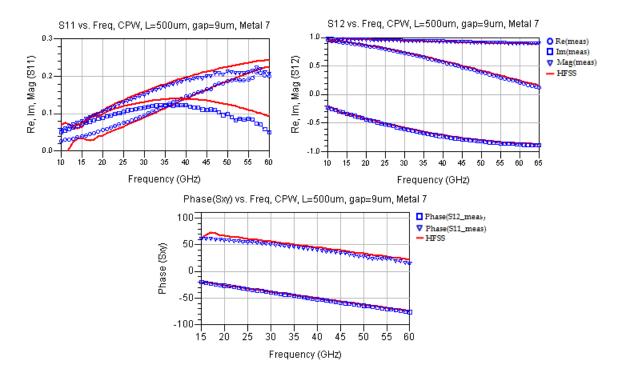

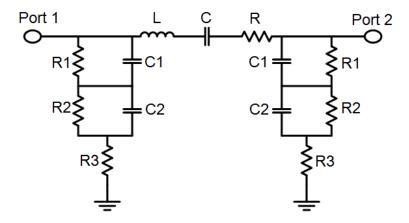

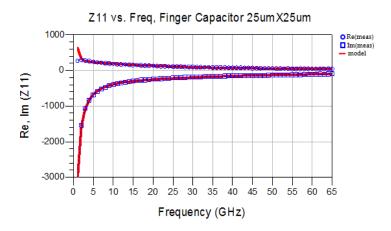

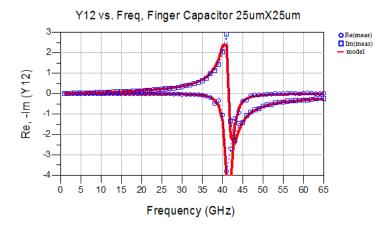

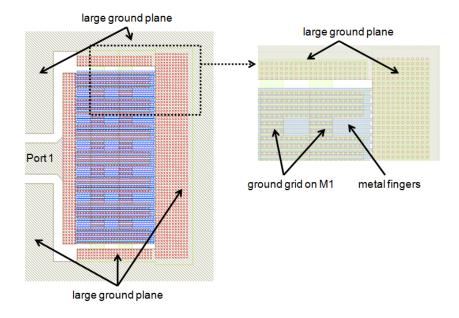

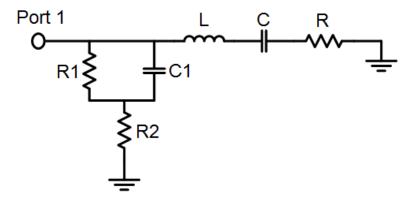

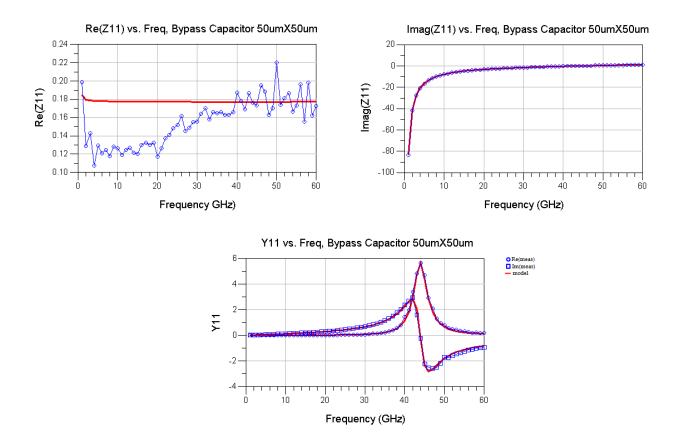

| F               | Relative frequency                    |