# Pattern-Oriented Application Frameworks for Domain Experts to Effectively Utilize Highly Parallel Manycore Microprocessors

Jike Chong

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2010-158 http://www.eecs.berkeley.edu/Pubs/TechRpts/2010/EECS-2010-158.html

December 15, 2010

### Copyright © 2010, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Acknowledgement

This research was supported in part by an Intel Ph.D. Fellowship, a California Nano-Technology Research Fellowship, funding from the Gigascale Systems Research Center, the Microsoft (Award \#024263) and Intel (Award \#024894) funding and by matching funding by U.C. Discovery (Award \#DIG07-10227).

#### Pattern-Oriented Application Frameworks for Domain Experts to Effectively Utilize Highly Parallel Manycore Microprocessors

by

Jike Chong

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Kurt W. Keutzer, Chair Professor David A. Patterson Professor Nelson Morgan Professor Terrence Hendershott

Fall 2010

### Pattern-Oriented Application Frameworks for Domain Experts to Effectively Utilize Highly Parallel Manycore Microprocessors

Copyright 2010 by Jike Chong

#### Abstract

Pattern-Oriented Application Frameworks for Domain Experts to Effectively Utilize Highly Parallel Manycore Microprocessors

by

Jike Chong

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Kurt W. Keutzer, Chair

Manycore microprocessors are powerful computing engines that are architected to embrace the use of parallelism to extract computational throughput from the continued improvements in the semiconductor manufacturing process. Yet the performance of the software applications running on these microprocessors is highly sensitive to factors such as data layout, data placement, and synchronization. These factors are not usually part of an application domain experts daily concerns, as they look to utilize the powerful compute capabilities of manycore microprocessors for their applications, but failure to carefully address these concerns could mean an order of magnitude of loss in application execution latency and/or throughput. With the proliferation of manycore microprocessors from servers to laptops and portable devices, there is increasing demand for the productive development of computationally efficient business and consumer applications in a wide range of usage scenarios. The sensitivity of execution speed to software architecture and programming techniques can impede the adoption of the manycore microprocessors and slow the momentum of the semiconductor industry.

This thesis discusses how we can empower application domain experts with pattern-oriented application frameworks, which can allow them to effectively utilize the capabilities of highly parallel manycore microprocessors and productively develop efficient parallel software applications. Our pattern-oriented application framework includes an application context for outlining application characteristics, a software architecture for describing the application concurrency exploited in the framework, a reference implementation as a sample design, and a set of extension points for flexible customization.

We studied the process of accelerating applications in the fields of machine learning and computational finance, specifically looking at automatic speech recognition (ASR), financial market value-at-risk estimation (VaR), and financial potential future exposure (PFE). We present a pattern-oriented application framework for ASR, as well as efficient reference implementations of VaR and PFE. For the ASR framework, we demonstrate its construction and two separate deployments, one of which flexibly extends the ASR framework to enable lip-reading in high-noise recognition environments. The framework enabled a Matlab/Java

programmer to effectively utilize a manycore microprocessor to achieve a 20x speedup in recognition throughput as compared to a sequential CPU implementation.

Our pattern-oriented application framework provides an approach for crystallizing and transferring the often-tacit knowledge of effective parallel programming techniques while allowing for flexible adaptation to various application usage scenarios. We believe that the pattern-oriented application framework will be an essential tool for the effective utilization of manycore microprocessors for application domain experts.

To Yue, Xuetong, and Peiji, my wonderful wife and supportive parents.

To the application domain experts, who are bravely developing applications on the highly parallel manycore microprocessors.

### Contents

| Li | st of                                  | Figures                                                                                                                       | V                                            |

|----|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1  | Intr<br>1.1<br>1.2                     | Thesis Contributions                                                                                                          | 1<br>3<br>4                                  |

| 2  | Bac<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Computing Technology Trends                                                                                                   | 5<br>8<br>9<br>11<br>12                      |

| 3  | Too<br>3.1<br>3.2                      | Metrics for Evaluating Effectiveness                                                                                          | 13<br>14<br>15<br>16<br>19<br>20             |

|    | 3.4<br>3.5                             | 3.3.2 Skeletons 3.3.3 Frameworks 3.3.4 Pattern-oriented Application Frameworks Parallel Software Implementation Tools Summary | 21<br>22<br>24<br>25<br>28                   |

| 4  | Pat<br>4.1<br>4.2<br>4.3<br>4.4        | tern-Oriented Application Frameworks for Parallel Programming The Four Components of an Application Framework                 | 30<br>31<br>32<br>33<br>34<br>35<br>38<br>42 |

|   |              | 4.4.4 Extension Points                                                 | 45        |

|---|--------------|------------------------------------------------------------------------|-----------|

|   | 4.5          | Discussion                                                             | 48        |

|   | 4.6          | Summary                                                                | 50        |

| 5 | The          | Construction of Pattern-Oriented Application Frameworks                | 51        |

| 0 | 5.1          | Automatic Speech Recognition Application Framework                     | 52        |

|   | 0.1          | 5.1.1 Implementation Efficiency Concerns                               | 55        |

|   |              | 5.1.2 Detailed Efficiency Optimizations                                | 63        |

|   |              | 5.1.3 Application-Specific Algorithm Selection                         | 73        |

|   |              | 5.1.4 Application-Specific Input Transformations                       | 78        |

|   |              | 5.1.5 Optimizations on Various Hardware Platforms                      | 84        |

|   |              | 5.1.6 Productivity Concerns                                            | 90        |

|   | 5.2          | Risk Analytics Application Framework                                   | 90        |

|   | 5.2          | 5.2.1 Market Risk Estimation                                           | 92        |

|   |              | 5.2.2 Counterparty Exposure Estimation                                 | 93        |

|   |              | 5.2.3 The Monte Carlo Method                                           | 93<br>94  |

|   |              |                                                                        | 94<br>95  |

|   |              | v                                                                      | 95<br>109 |

|   |              | v                                                                      |           |

|   |              |                                                                        |           |

|   | <b>E</b> 9   |                                                                        |           |

|   | 5.3          | Summary                                                                | 117       |

| 6 | The          | Deployment of a Pattern-Oriented Application Framework                 | 118       |

|   | 6.1          | Automatic Speech Recognition Application Framework Deployment          | 118       |

|   |              | 6.1.1 Application Framework Reference Implementation                   | 119       |

|   |              | 6.1.2 Deployment for Usage in Meeting Transcription                    | 120       |

|   |              | 6.1.3 Deployment in Audio-Visual Speech Recognition Usage Scenario     | 121       |

|   |              | 6.1.4 Deployments to Industrial Usage Scenarios                        | 124       |

|   | 6.2          | Risk Analytics Application Framework Deployment                        | 124       |

|   |              | 6.2.1 Value-at-Risk Application Framework Deployment                   | 125       |

|   |              | 6.2.2 Potential Future Exposure Application Framework Deployment       | 126       |

|   | 6.3          | Summary                                                                | 127       |

| 7 | A m          | Ecosystem for Pattern-Oriented Application Frameworks                  | 128       |

| • | 7.1          | Lead Users of Pattern-Oriented Application Framework                   |           |

|   | $7.1 \\ 7.2$ | Developers of the Pattern-Oriented Application Framework               |           |

|   | 7.2          | Building Blocks for Developing Pattern-Oriented Application Frameworks |           |

|   |              | Components of a Thriving Ecosystem                                     |           |

|   | 7.4          |                                                                        |           |

|   | 7.5          | Summary                                                                | 197       |

| 8 | Key          | Lessons                                                                | 139       |

|   | 8.1          | Industry Landscape                                                     | 139       |

|   | 8.2          | Implementation Gap                                                     | 140       |

|   | 8.3          | Pattern-Oriented Application Framework                                 | 141       |

|                  | 8.4    | The Construction of Pattern-Oriented Application Frameworks | 142 |

|------------------|--------|-------------------------------------------------------------|-----|

|                  | 8.5    | Deployment of Pattern-Oriented Application Framework        | 143 |

|                  | 8.6    | The Ecosystem for Pattern-Oriented Application Framework    | 143 |

|                  | 8.7    | Summary                                                     |     |

| $\mathbf{B}^{i}$ | ibliog | graphy                                                      | 146 |

| $\mathbf{A}$     | Sam    | aple Pattern: Monte Carlo Methods                           | 159 |

|                  | A.1    | Name                                                        | 159 |

|                  | A.2    | Problem                                                     | 160 |

|                  | A.3    | Context                                                     | 160 |

|                  | A.4    | Forces                                                      | 161 |

|                  |        | A.4.1 Universal forces                                      | 161 |

|                  |        | A.4.2 Implementation forces                                 | 161 |

|                  | A.5    | Solution                                                    | 162 |

|                  |        | A.5.1 Solution Structure                                    | 162 |

|                  |        | A.5.2 Solution Considerations                               | 163 |

|                  | A.6    | Invariant                                                   | 168 |

|                  | A.7    | Examples                                                    | 169 |

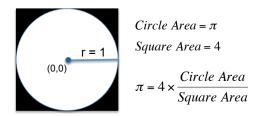

|                  |        | A.7.1 Example 1: $\pi$ Estimation                           | 169 |

|                  |        | A.7.2 Example 2: Financial Market Value-at-Risk Estimation  | 169 |

|                  |        | A.7.3 Example 3: Option Pricing                             | 171 |

|                  |        | A.7.4 Example 4: Molecular Dynamics                         | 173 |

|                  | A.8    | Known Uses                                                  | 174 |

|                  | A.9    | Related Patterns                                            |     |

|                  | A.10   | Notes on: Random Number Generation                          | 176 |

### List of Figures

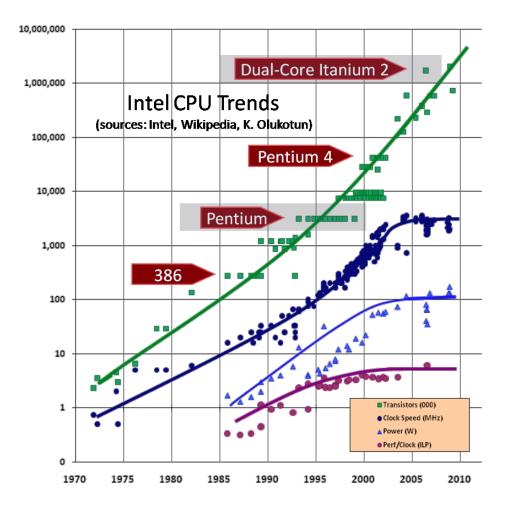

| 2.1                | Microprocessor specification trends over the past four decades (Prepared by Herb Sutter in [144])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6<br>8               |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

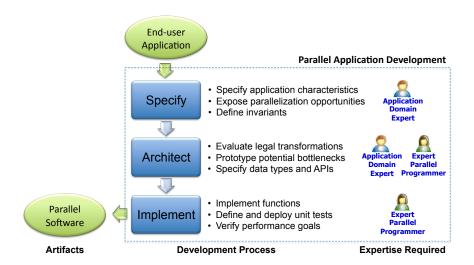

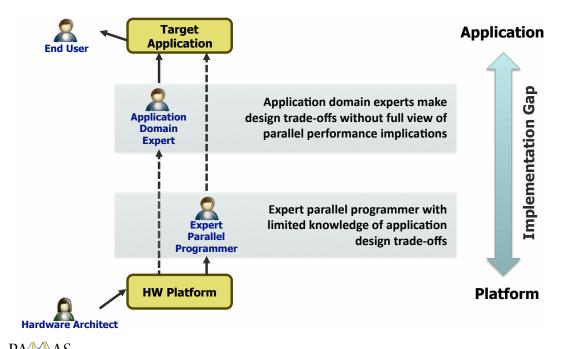

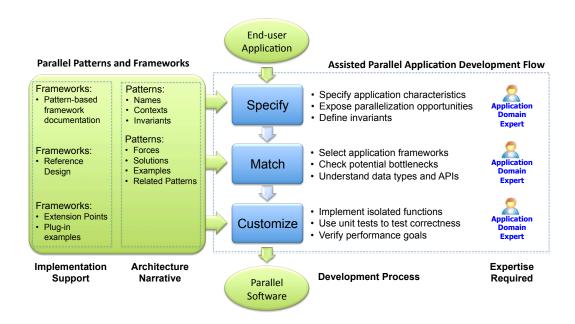

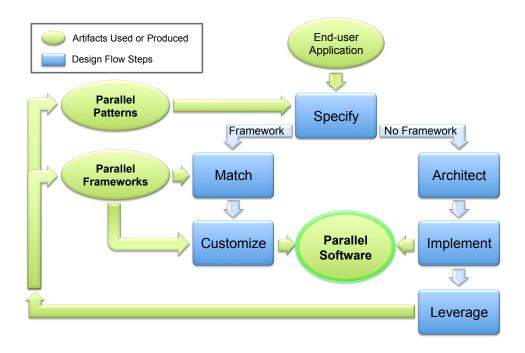

| 2.3<br>2.4         | The three-step process in a parallel applications development flow The parallel application <i>Implementation Gap.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10<br>10             |

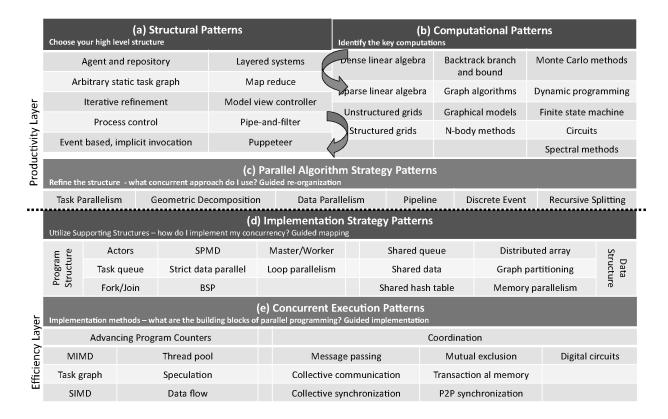

| 3.1                | Our Pattern Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19                   |

| 4.1<br>4.2<br>4.3  | The three-step process in an assisted parallel application development flow . Overall parallel application development flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33<br>35<br>35       |

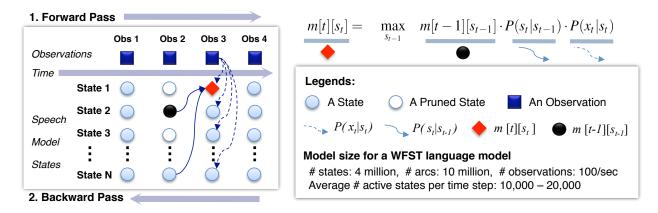

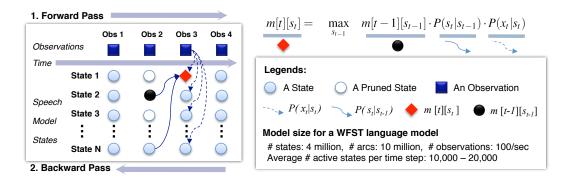

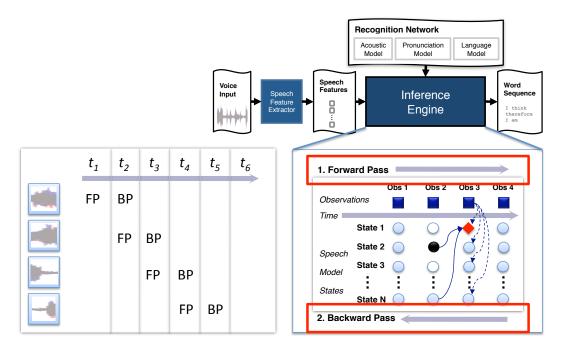

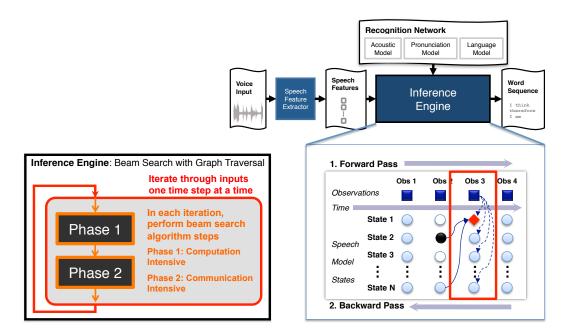

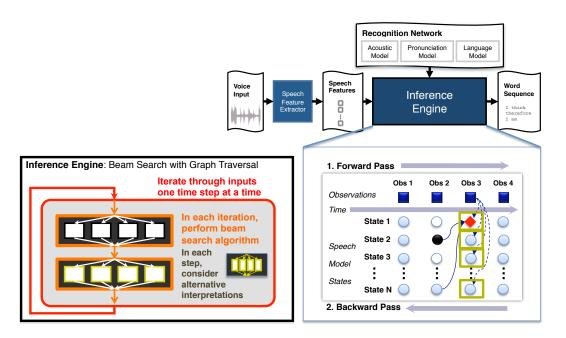

| 4.4                | Application characteristics: the inner-workings of the performance critical Viterbi forward and backward pass steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36                   |

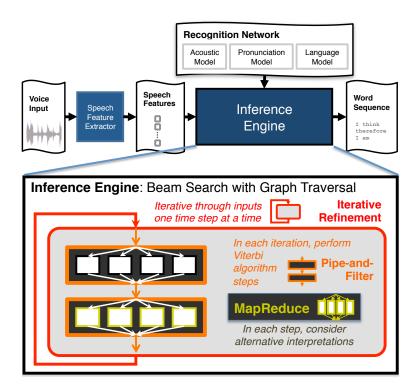

| 4.5                | The software architecture of a large vocabulary continuous speech recognition application. At the top level, the application can be seen as an instance of the <i>Pipe-and-filter pattern</i> , with the speech feature extractor and the inference engine as filters, and the intermediate results between them on pipes. Inside the inference engine, the iterations over each time step in the application is based on the <i>Iterative Refinement pattern</i> , where each iteration handles one input feature vector corresponding to one time-step. Inside each iteration, phases 1 and 2 can be seen as filters in a <i>Pipe-and-filter pattern</i> . Within each phase, the computations can be executed in parallel following the <i>MapReduce pattern</i> | 41                   |

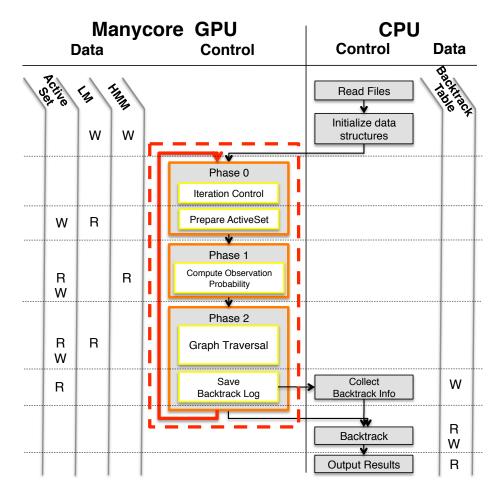

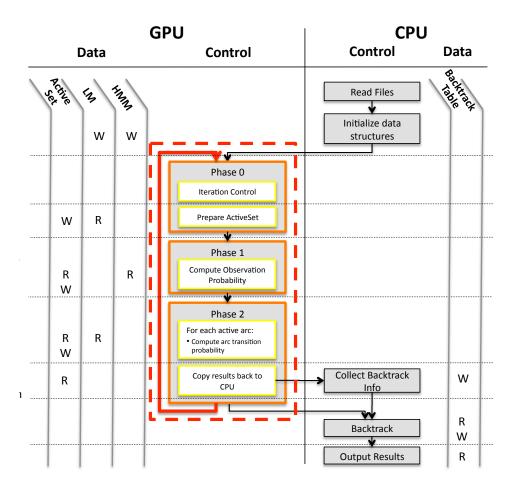

| 4.6                | A summary of the data structure access and control flow of the inference engine on the manycore platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43                   |

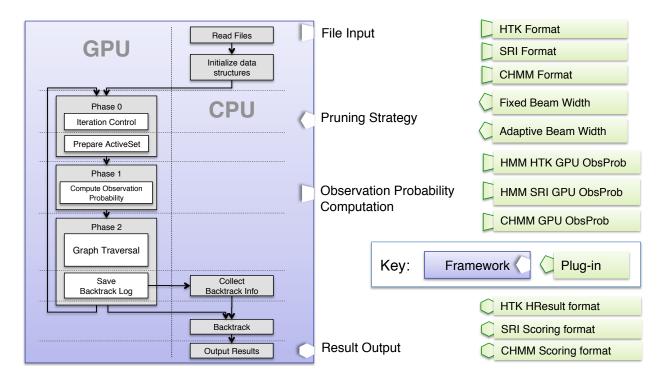

| 4.7                | An application framework for automatic speech recognition with extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.0                  |

| 4.8<br>4.9<br>4.10 | points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46<br>47<br>48<br>48 |

| 5.1                | The construction of pattern-oriented application frameworks using the <i>Leverage</i> step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52                   |

|                    | age step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 02                   |

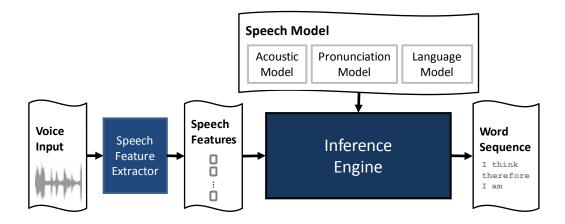

| 5.2  | The system architecture of a large vocabulary continuous speech recognition application.                  |

|------|-----------------------------------------------------------------------------------------------------------|

| 5.3  | Application characteristics: the inner-workings of the performance critical                               |

| _ ,  | Viterbi forward and backward pass steps                                                                   |

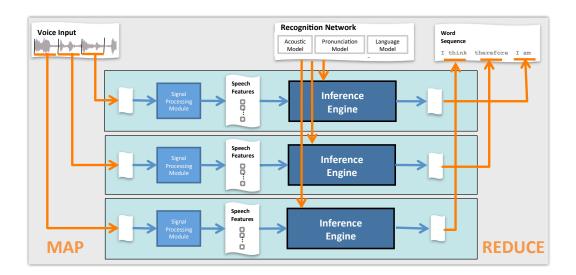

| 5.4  | Parallelization Opportunity 1: Applying MapReduce parallel programming                                    |

|      | pattern over the input speech utterances                                                                  |

| 5.5  | Parallelization Opportunity 2: Applying the Pipe-and-Filter parallel pro-                                 |

| 5.6  | gramming pattern over a sequence of input speech utterances                                               |

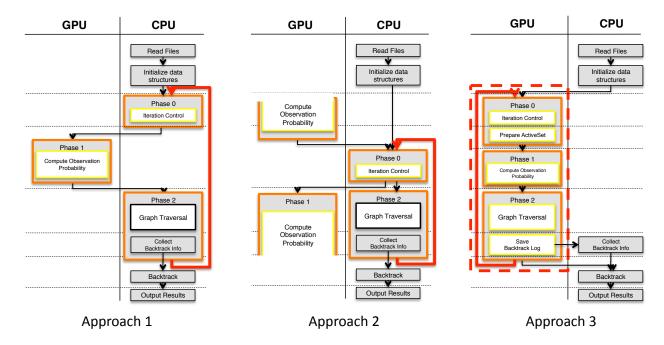

| 5.7  | Alternative approaches for the implementation of Phase 1 and Phase 2 on a CPU-GPU hybrid system           |

| 5.8  | Parallelization Opportunity 4: Applying the MapReduce pattern over the                                    |

|      | functions that implement Phase 1 and Phase 2 in the Viterbi algorithm                                     |

| 5.9  | Summary of the data structure access and control flow of the inference engine                             |

|      | on the manycore platform                                                                                  |

| 5.10 | A demonstration of data-parallel data gathering routines                                                  |

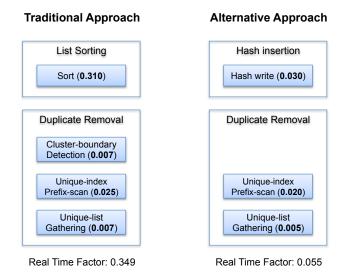

|      | Find unique function approaches                                                                           |

|      | Pseudo code for traversal by <i>propagation</i>                                                           |

|      | The CUDA atomic operation with a logic operation                                                          |

|      | Using the CUDA atomic operation with a logic operation                                                    |

|      | A global queue based implementation of active state list generation with                                  |

|      | pruning                                                                                                   |

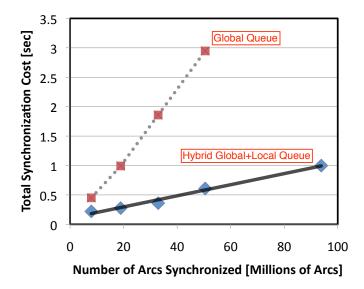

| 5.16 | Comparison of the synchronization cost for global queue and hybrid global and local queue implementations |

| 5.17 | A hybrid global/local queue based implementation of active state list generation with pruning             |

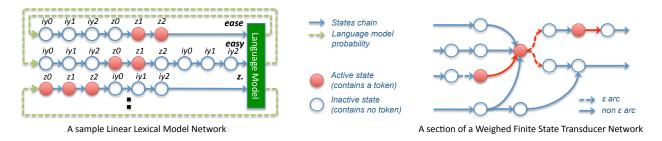

| 5.18 | Structure of the recognition network for the LLM representation and WFST                                  |

|      | representation.                                                                                           |

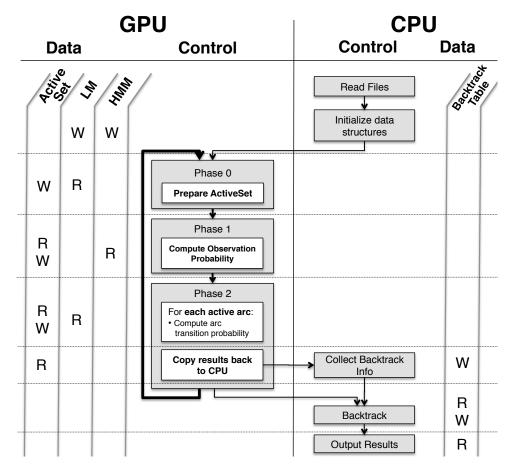

| 5.19 | Control flow for the CPU/GPU software implementation and associated data                                  |

|      | structure access (R: read, W: write)                                                                      |

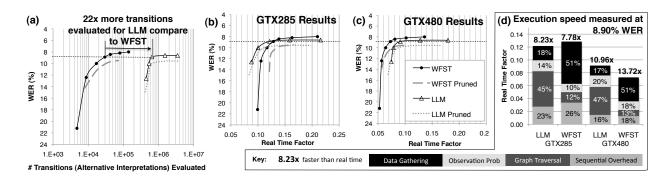

| 5.20 | WER w.r.t. # of transitions evaluated (a), execution time in Real Time                                    |

|      | Factor (b/c), and speed analysis at 8.90% WER (d)                                                         |

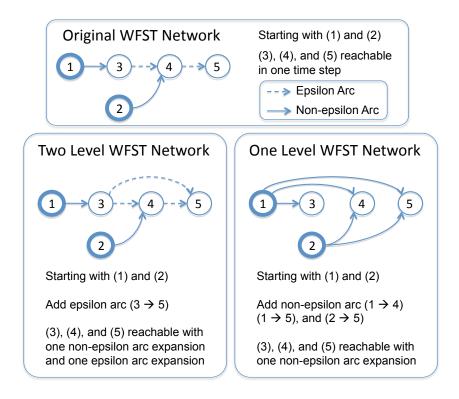

| 5.21 | Network modification techniques for a data parallel inference engine                                      |

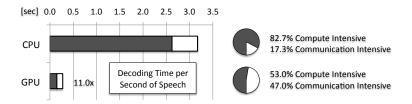

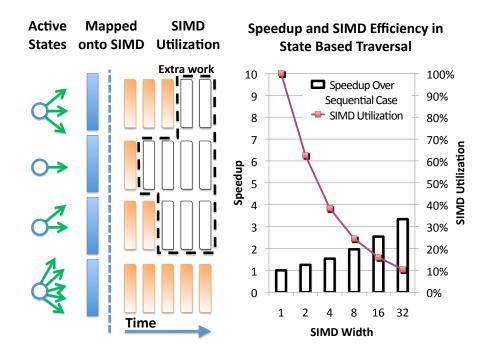

|      | Parallel Speedup of the Inference Engine                                                                  |

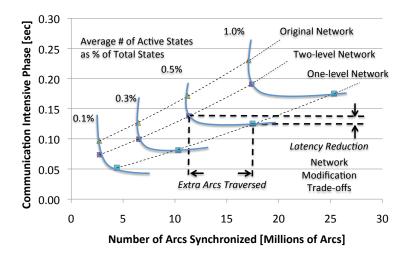

| 5.23 | Communication Intensive Phase Run Time in the Inference Engine (normal-                                   |

|      | ized to one second of speech)                                                                             |

| 5.24 | The algorithmic level design space for graph traversal scalability analysis for                           |

|      | the inference engine                                                                                      |

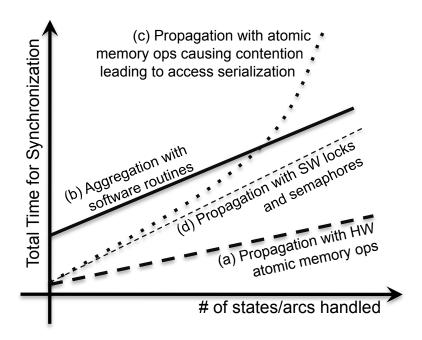

| 5.25 | Scalability of the traversal process in terms of total synchronization time                               |

| 5.26 | SIMD unit utilization in the active-state-based traversal                                                 |

| 5.27 | Ratio of computation intensive phase of the algorithm vs communication                                    |

|      | intensive phase of the algorithm                                                                          |

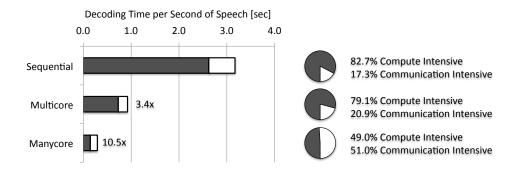

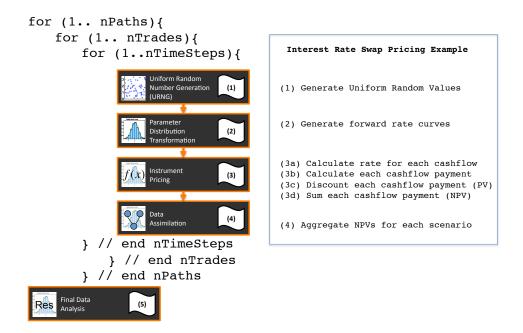

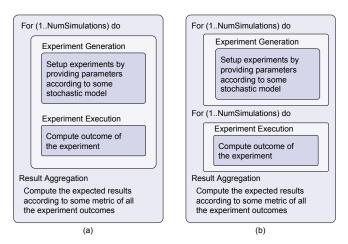

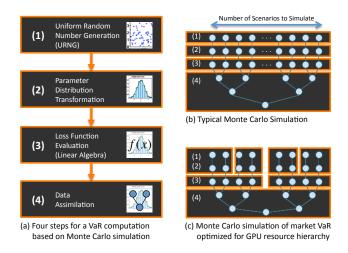

| 5.28       | The solution structure for Monte Carlo based analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 95  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

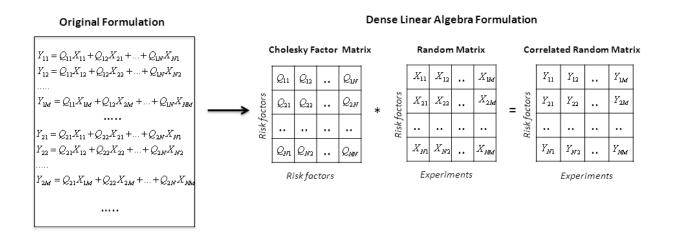

| 5.29       | The correlation of random variables is re-factored as a dense matrix-matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

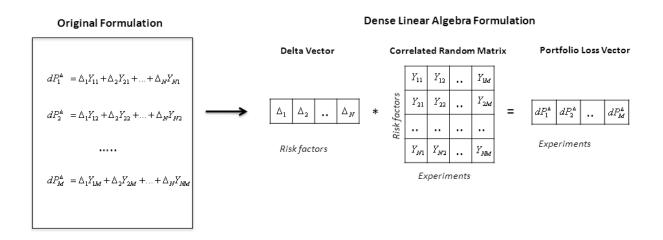

| 5 30       | multiplication in order to use the existing well-parallelized cuBLAS library Loss function evaluation is also re-factored as a dense matrix-vector multipli-                                                                                                                                                                                                                                                                                                                                                                                                    | 98  |

| 0.00       | cation in order to use the existing well-parallelized cuBLAS library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 99  |

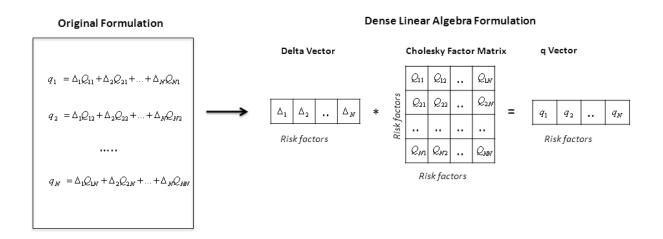

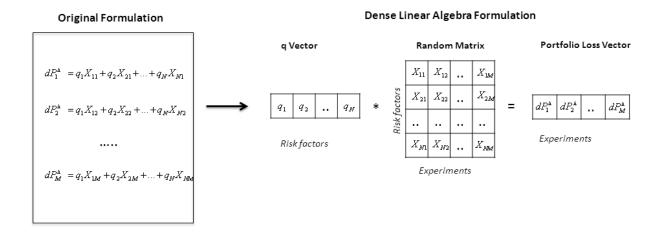

| 5.31       | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 99  |

|            | The reformulated loss function evaluation is also factored as a dense matrix-vector multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100 |

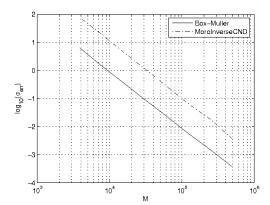

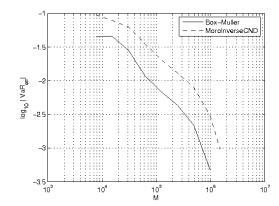

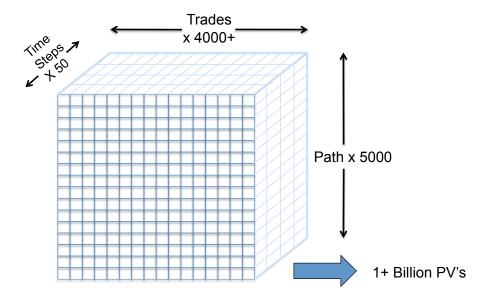

| 5.33       | (Left) A comparison of the standard error (%) in the portfolio loss distribution using Moro's interpolation method and the Box-Muller method applied to Sobol' sequences. (Right) The corresponding error (%) in the simulated 1 day portfolio delta VaR (c=95%) monotonically converges to the analytic delta VaR (9.87%) with the number of scenarios. In single-precision arithmetic, approximately $1.5 \times 10^6$ or $7.5 \times 10^5$ scenarios is sufficient to estimate the delta-VaR to within $0.1\%$ when using Moro's interpolation method or the |     |

| F 94       | ı v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 104 |

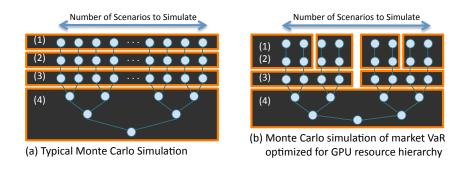

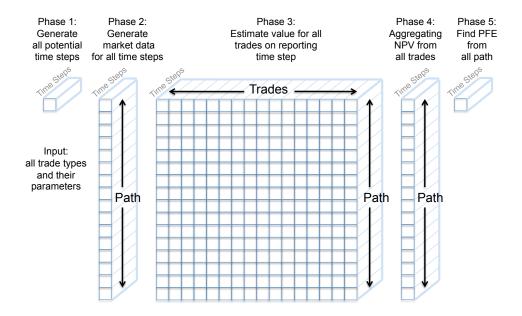

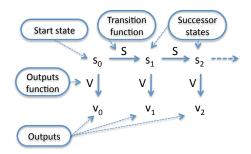

|            | The cube (three dimensional matrix) of Present Values (PVs), or Monte Carlo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 105 |

|            | simulation results, in a Potential Future Exposure (PFE) application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|            | The task-centric perspective of a potential future exposure (PFE) estimation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|            | The data-centric perspective of potential future exposure (PFE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

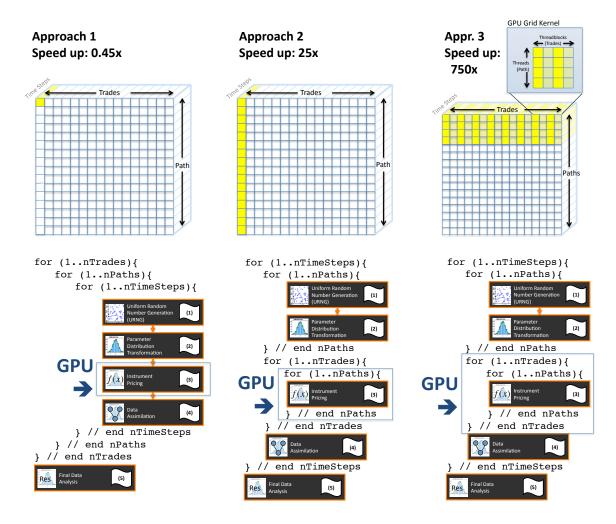

| 5.38       | Three approaches to GPU-based PFE implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 115 |

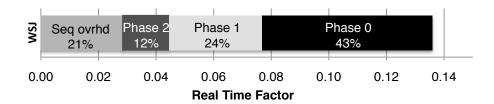

| 6.1<br>6.2 | The recognition speed shown as real time factor (RTF) demonstrated with the Wall Street Journal corpus at 8.0% WER                                                                                                                                                                                                                                                                                                                                                                                                                                              | 119 |

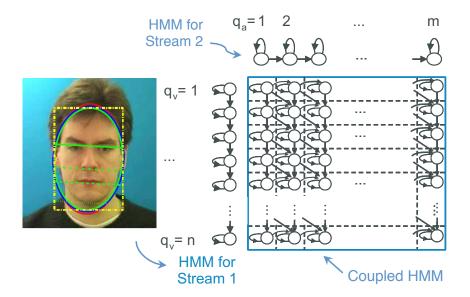

| 0.2        | correspond to the pairing of one audio- and one video-HMM-state, $q_a$ and $q_v$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100 |

| 6.2        | respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 122 |

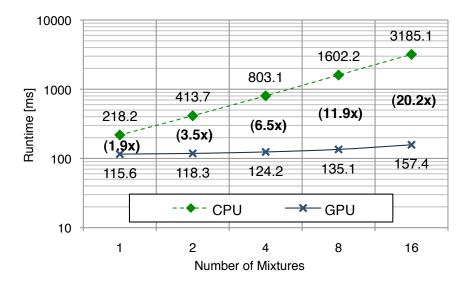

| 6.3        | Runtime in ms per file of 3s length for $M = 1, 2,, 16$ mixture components used in Eq. (6.4). The speedup factor $S$ is given in parentheses                                                                                                                                                                                                                                                                                                                                                                                                                    | 124 |

| 7.1        | A screen shot of the Our Pattern Language (OPL) website                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 135 |

| A.1        | Monte Carlo Methods solution structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 163 |

| A.2        | A sample implementation of the Box-Muller method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 166 |

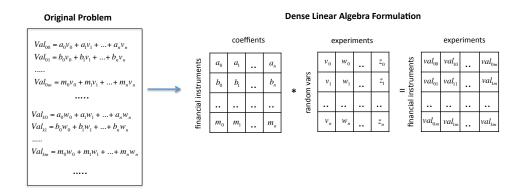

| A.3        | An example of mapping the original problem of generating $val_i$ values for $k$ experiments, using $n$ coefficients $am$ for $m$ financial instruments and $n$                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|            | random variables $v_i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 167 |

| A.4        | $\pi$ estimation problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 169 |

| A.5        | Solution Structure for the value at risk estimation application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 170 |

| A.6        | A Sequential Monte Carlo simulation of the Black-Scholes model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| A.7        | Pseudo code fot the Metropolis Monte Carlo algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| A.8        | A general random number generation algorithm structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

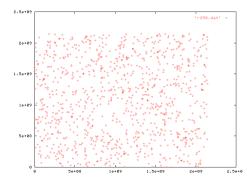

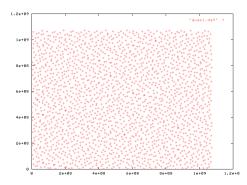

| A.9        | A pseudo-random distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 177 |

|   | ٠ | ٠ | • |  |

|---|---|---|---|--|

| V | 1 | 1 | 1 |  |

|   |   |   |   |  |

| A.10 A quasi-random distribution |  | 77 |

|----------------------------------|--|----|

|----------------------------------|--|----|

#### Acknowledgments

I would like to thank all the people who have guided and supported me on this journey. In particular, I owe my deepest gratitude to my advisor, Kurt Keutzer, whose constant encouragement and unwavering support fill me with confidence even during the most difficult times. By following his guidance and observing him as a role model, I learned not only the process of conducting research, but also the process of sincerely engaging highly talented people to work together in producing world-class contributions. This thesis also would not have been possible without the inspirational leadership of Professor David Patterson, who spearheaded the establishment of the Parallel Computing Lab at University of California, Berkeley, which provided an environment for long term collaboration between application domain experts and parallel programming experts. I am also grateful for Professor Nelson Morgan and Professor Terrence Hendershott, for their generous guidance and support.

It is an honor for me to have met and studied under professors Andrew Isaacs, Henry Chesbrough, Steve Blank, Jihong Sanderson, and the late Dean Richard Newton, as they inspired me to look beyond theories and algorithms, and to use the opportunities from the Mayfield Fellowship and perspectives from the Haas Business School to observe how tools and concepts get deployed in the real world. I would like to give special thanks to Dr Pradeep Dubey, Dr Yen-Kuang Chen, Dr Mikhail Smelyanskiy, Dr Christopher Hughes at Intel Corporation, and Roger W., Dr Alejandro H., Colin W., and Brian C. in other companies for their guidance and support in shaping this research.

I am indebted to many of my colleagues including Dr Matthew Dixon and Dr Dorothea Kolossa, whose support made possible the numerous real world case studies; Arlo Aria, Dr Nadathar Satish, Dr Youngmin Yi, Ekaterina Gonina, Dr Kisun You, Michael Anderson, Dr Andreas Stolcke, Steffen Zeiler, Dr Gerald Friedland, Dr Adam Janin, and Fares Hedayati for their generous support and close collaborations. They each made critical contributions to the research presented here. I would also like to thank Bryan Catanzaro, Matt Moskewicz, Mark Murphy, Narayanan Sundarum, Bor-Ying Su, Chao-Yue Lai, David Sheffield, Dr Wei Zheng, Dr Kelvin Lwin, Dr Abhjit Devare, Dr Qi Zhu and Dr Douglas Densmore for countless stimulating discussions on research as well as on the meaning of life.

I am grateful to my uncle, Dr Xing Zhu, my father in-law, Dr Xiubao Chang, and my mentors, Dr Li Gong and Dr Prakash Hebalkar for their encouragement for me to pursue a PhD; to Dean Pradeep Khosla and Professor Andrjez Strojwas for their generous recommendations that enabled me to come to Berkeley. This research would not have been possible without the sacrifice from my parents, Xuetong Zheng and Peiji Chong, and my grandparents, Weimei Dong and the late Dechen Zheng, Yuhuan Li, and Yidong Chong, who made every effort to provide me with opportunities to receive the best education possible. Finally, I am forever indebted to my wife, Yue Cathy Chang, who has supported me intellectually and emotionally through a journey of six years during the process of this research.

This research was supported in part by an Intel Ph.D. Fellowship, a California Nano-Technology Research Fellowship, funding from the Gigascale Systems Research Center, the Microsoft (Award #024263) and Intel (Award #024894) funding and by matching funding by U.C. Discovery (Award #DIG07-10227).

### Chapter 1

#### Introduction

The evolution of computing technology is at an inflection point where microprocessors are forced by underlying physics to use parallelism to take advantage of the increasing scale of silicon integration [17, 81]. Manycore microprocessors have emerged as powerful computing engines that can efficiently extract computational throughput from the continued improvements in the semiconductor manufacturing process. Manycore processors are architected to embrace the use of parallelism by allowing software applications to utilize tens to hundreds of threads per core, and tens of cores per chip concurrently. This paradigm is in stark contrast to traditional threaded processing, where often only a few threads are used in an application. As a result, the inflection point in the hardware platform is causing a disruption in the software development process, such that the traditional sequential hardware abstraction is no longer sufficient for the development of performance-sensitive end-user applications [18].

To further complicate the situation, the performance of the software applications running on manycore microprocessors can be highly sensitive to factors such as data layout, data placement, and synchronization. Failure to carefully address these factors could result in an order of magnitude of loss in application execution latency and/or throughput [26]. At the same time, the types of applications that can take advantage of the manycore microprocessors are expanding. Significant application domain expertise is required to develop new application capabilities for new application usage scenarios<sup>1</sup>. We consider application domain experts as professionals who are trained in specific domains such as machine learning and computational finance. As application domain experts develop new application capabilities on highly parallel manycore processors, they are usually not familiar with how to take care of concerns in data layout, data placement and synchronization, which makes it challenging to develop efficient implementations for new application usage scenarios.

Without an effective methodology to allow applications to quickly leverage the benefits of the increasing scale of silicon integration, the adoption of manycore microprocessors can be severely limited. Such a slow-down in new technology adoption can stunt the growth of

<sup>&</sup>lt;sup>1</sup>Sections 5.1 and 6.1.3 illustrate that extensive application domain expertise that is required for the development of new application capabilities. The example in Section 6.1.3 involves the implementation of an audio-visual speech recognition application that can perform lip-reading.

the entire semiconductor industry.

This thesis assumes that the productive development of applications for an emerging generation of highly parallel microprocessors is the preeminent programming challenge of our time. We believe that the productive development of applications begins by empowering application domain experts with tools that allow them to utilize the capabilities of the highly parallel manycore microprocessors effectively and to develop efficient parallel software applications productively.

With this perspective in mind, we have developed the pattern-oriented application framework to enable application domain experts to achieve application execution efficiency, development productivity, and the portability of development efforts. Our pattern-oriented application framework contains four components, which includes an application context outlining application characteristics and exposing application concurrency, a software architecture describing the application concurrency exploited in the framework, a reference implementation, which a fully functional, efficient sample design, and a set of extension points for flexible customization.

We demonstrate efficient reference implementations of applications in the fields of machine learning and computational finance, specifically studying automatic speech recognition (ASR), financial market value-at-risk (VaR) estimation, and financial potential future exposure (PFE) estimation.

In the field of machine learning, we analyzed ASR in-depth and optimized it for execution efficiency. ASR allows multimedia content to be transcribed from acoustic signals to word sequences. It is emerging as a critical component in data analytics for a wealth of multimedia data that is being generated on a daily basis. A pattern-oriented application framework was developed in order to assist application domain experts to productively utilize highly parallel computing platforms to deploy ASR based applications. For the ASR pattern-oriented application framework, we demonstrate its construction and two separate deployment case studies. Extensive optimizations were applied in the construction of the ASR reference implementation, including application algorithm selection, input speech model structural transformations, hardware platform feature sensitivity analysis, and implementation efficiency tuning. In one of the deployment case studies, the audio-only ASR framework was extended to an audio-visual speech recognition application that takes in video information and use lip-reading to improve recognition accuracy in noisy recognition environments. The ASR pattern-oriented application framework enabled a programmer with only prior experience in Matlab/Java to effectively utilize a manycore microprocessor to achieve a 20x speedup in recognition throughput as compared to a sequential CPU implementation.

In the field of computational finance, VaR and PFE are the two applications being explored in this thesis. VaR is a measure of market risk for a financial portfolio and refers to the maximum loss expected under normal market conditions over a period time at a given confidence level. It is the preferred risk metric recommended in the Basel II international banking standard [5]. For the VaR implementation, we applied optimizations from multiple perspectives, including task-centric function refactoring to reduce necessary computation, numerical-centric module selection to accelerate algorithm convergence, and data-centric module merging to improve memory bandwidth utilization. The optimized implementation

achieved a speed up of 169x on the GPU when compared to a baseline GPU implementation, making it an efficient reference implementation for the construction of an application framework. The implementation of this application framework is on-going research.

PFE is a measure of the financial default risk that quantifies the counterparty<sup>2</sup> risk posed by future fluctuations in market prices during the lifetime of the transactions in a bank's portfolio. The exploration of an efficient PFE software architecture is based on the production code base of an industry partner that is a global financial information company. For the PFE application, we investigated multiple application programming interfaces to offload batch of computation from a Central Processing Unit (CPU) to a manycore microprocessor based accelerator. When compared to a reference implementation on the CPU, the optimized implementation of the PFE application that is presented here achieved a speed up of 750x on the GPU, making it an efficient reference design for the construction of an application framework. The implementation of this application framework is also part of the ongoing research.

Our pattern-oriented application frameworks are tools that can be widely deployed in the industry, allowing application domain experts to productively develop and deploy software applications for the new generations of highly parallel manycore microprocessors. We analyze an ecosystem for pattern-oriented application frameworks in terms of its lead users, developers, building blocks, and the ecosystem components to help the frameworks find initial adoption and allow them to evolve to meet the needs of the industry.

#### 1.1 Thesis Contributions

The contributions this research offers include:

- 1. Proposing four components that when used together can allow a pattern-oriented application framework to address the efficiency concerns of the application domain experts and help them productively develop software applications for the highly parallel manycore microprocessors<sup>3</sup>

- 2. Demonstrating that both application domain expertise and parallel programming expertise are required to develop high-performance pattern-oriented application framework

- 3. Optimizing implementations of applications in machine learning for automatic speech recognition and in computational finance for market value-at-risk estimation and financial potential future exposure estimation, achieving orders of magnitude speed up in execution time compared to sequential execution

<sup>&</sup>lt;sup>2</sup>Counterparties are brokers, investment banks, and other securities dealers that serve as the contracting party when completing an over-the-counter financial security transaction. The details are explained in Section 5.2.2.

<sup>&</sup>lt;sup>3</sup>The pattern-oriented application framework concept proposed here is inspired by the framework concept discussed in [18].

- 4. Demonstrating a pattern-oriented application framework for automatic speech recognition with deployments in multiple usage scenarios, enabling application domain experts to achieve 20x speedup on the highly parallel manycore microprocessors

- 5. Proposing an ecosystem in which pattern-oriented application frameworks can find adoption in industry and evolve to meet the needs of the application domain experts

#### 1.2 Thesis Outline

The chapters in this thesis are presented as follows:

- Chapter 2 provides the background and motivation that highlights the implementation gap in parallel application development.

- Chapter 3 surveys the existing tools and environments for the productive development of parallel applications and introduces the concept of *pattern-oriented application frameworks* for domain experts.

- Chapter 4 illustrates the proposed *pattern-oriented application frameworks* for domain experts to more effectively program manycore microprocessors.

- Chapter 5 presents the construction process for the pattern-oriented application frameworks.

- Chapter 6 demonstrates how pattern-oriented application frameworks can be deployed in the field.

- Chapter 7 proposes an ecosystem in which pattern-oriented application frameworks can find adoption and evolve to meet the needs of the application domain experts.

- Chapter 8 provides a summary of key lessons learned in the process of developing pattern-oriented application frameworks for application domain experts.

The following chapter explains the industry trends in both hardware and application software that are creating an *implementation gap* for the development of software applications. It then goes on to propose a solution process that will be elaborated upon in the remainder of this thesis.

### Chapter 2

### Background and Motivation

The evolution of computing technology was recently at an inflection point where the industry is transitioned from sequential computing platforms to parallel computing platforms. This inflection point in the hardware platform is causing a disruption in the software development process. The traditional sequential hardware abstraction is no longer sufficient for the development of performance-sensitive end-user applications. This chapter explains the industry trends, with respect to both hardware and application software, that are creating an *implementation gap* for software application development. It then proposes a solution process that will be elaborated upon in details in the remainder of this thesis.

#### 2.1 Computing Technology Trends

For the past four decades, the computer industry has been driven by Moore's Law, which predicted that the density of integrated circuits can double approximately every two years. Moore's Law has become a synchronizing force for all levels of the semiconductor industry. This is most clearly seen in the microprocessor industry, where Moore's Law has synchronized low-level research and development (R&D) efforts, such as the chemistry necessary for chip manufacturing steps, up to the high level R&D of the practically achievable end-user applications performance on the microprocessors. Figure 2.1 illustrates the effect of Moore's Law on microprocessor designs over the past four decades [144]. The data points are based on microprocessor specifications that are plotted according to their release dates. Starting at the top line, which shows the number of transistors that are integrated on-a-chip, it is clear that the industry is on track to increase the scale of integration approximately every two years. Since the early 1970s, the exponential growth during these three decades has enabled more than one billion transistors to be integrated on one microprocessor.

At the application development level, software developers have depended on the assumption that exponential growth in transistor density will result in similar exponential improvement in the execution performance of a single stream of application code executing on one processor. In the last decade, however, the scaling process has reached physical limits in microprocessor clock speed, power consumption, and performance per clock. We see in Figure 2.1 that many of these metrics have plateaued. Asanovic et al. in [17] has described

Figure 2.1: Microprocessor specification trends over the past four decades (Prepared by Herb Sutter in [144])

this effect as the aggregation of three performance scaling challenges:

- 1. "Power Wall": Although power is a scarce resource for computation, transistors are "free" That is, we can put more transistors on a chip than we have the power to turn on.

- 2. "Memory Wall": Load and store instructions are slow, but multiply is fast [155]. Modern microprocessors can take 200 clocks to access Dynamic Random Access Memory (DRAM), but even floating-point multiplies may take only four clock cycles. Many applications are becoming bandwidth-limited.

- 3. "ILP Wall": There are diminishing returns with respect to finding more instruction-level parallelism (ILP) via compilers and architecture innovations including branch prediction, out-of-order execution, speculation, and Very Long Instruction Word systems [81].

The aggregate effect of these three "Walls" is that sequential processing performance is becoming increasingly difficult to improve. While the total number of transistors that one can integrate on a chip continues to increase, we are forced to respect the limitations of physics and to organize microprocessor designs around the physical limitations of power dissipation, memory device proximity, and the limited scope of implicit instruction level parallelism in software implementation.

At the same time, a new breed of "manycore" microprocessor architectures has emerged. Such architecture sacrifices the performance of any single stream of instructions and use many simpler and more power-efficient processor cores in parallel in order to achieve higher overall throughput under any specific power budgets. The more power-efficient core architectures allow manycore processors to mitigate the "Power Wall". The manycore architecture concurrently maintains the context of numerous threads and allows low overhead context switches to occur between threads. This effectively hides long memory latencies by allowing stalled processor pipelines to switch to other ready threads so as to be able to continue, thus mitigating the effects of the "Memory Wall". Lastly, special data-parallel languages are proposed and used to expose and represent more parallelism in applications, thereby mitigate the "ILP Wall".

Having to adapt new applications to a new data-parallel language is not a preferred move in the industry. As summarized in [17], this move has been forced upon us by our desire to continue the scaling of microprocessor performance while respecting the laws of physics:

This shift toward increasing parallelism is not a triumphant stride forward based on breakthroughs in novel software and architectures for parallelism; instead, this plunge into parallelism is actually a retreat from even greater challenges that thwart efficient silicon implementation of traditional uniprocessor architectures.

- Berkeley View, December 2006

Many major microprocessor vendors have general-purpose manycore processors either in production or on the roadmap. For example, as of 2010, NVIDIA has brought to market the G80/GTX200/GTX400 general-purpose manycore processor architectures. AMD/ATI offers the Radeon 4000/5000/6000 series manycore programmable processor architectures. And Intel is developing its many-integrated-core (MIC) processor architecture under the name Aubrey Isle [131], previously known as Larrabee [134].

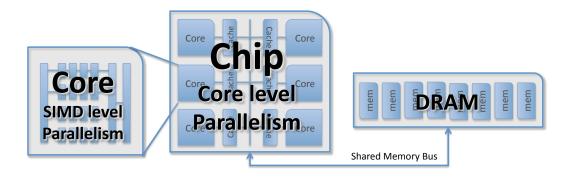

#### Manycore Processor Architecture

Manycore processors are expected to be an increasingly important component in computing technologies. Current and emerging many-core platforms such as the GPUs from NVIDIA and AMD/ATI, as well as the Intel MIC processor are built around an array of processors each running many threads of execution in parallel. As shown in Figure 2.2, each core employs variations of the Single Instruction Multiple Data (SIMD) architecture, where the same instruction can operate on multiple pieces of data at the same time. Amortizing the instruction-processing overhead among many data calculations is an effectively way to reduce power consumption [98]. The cores are then connected together using levels of

Figure 2.2: The generic manycore architecture.

shared memory hierarchy, allowing synchronization to occur between the cores on a chip. The cores also share the same DRAM memory controller, thus enabling a shared memory space abstraction for ease of application development.

In this thesis, the highly parallel manycore microprocessors we use are the NVIDIA graphics processing units (GPU), which are programmed using the Compute Unified Device Architecture (CUDA) [122]. NVIDIA GPUs were chosen because they are representative of an emerging generation of highly parallel microprocessors that have as many as 15-30 of cores and 8-16 SIMD lanes in each core. At the same time, CUDA has a mature software development environment for the shared memory manycore on-a-chip architecture, which allows large user applications to be effectively developed. Although the tools demonstrated in this thesis is based in CUDA, the concepts presented are not limited to CUDA and are applicable to other development environments.

#### 2.2 Software Application Trends

A software application is a solution that solves a problem when it is implemented in software and executed on a computer. The types of applications that could benefit from highly parallel manycore platforms are expanding. In 2005, Pradeep Dubey put forth a vision that by 2015, computing will be increasingly applied to a broad range of applications involving Recognition, Mining, and Synthesis [64]. These applications are expected to demand and gain more utility from the increasing processing capabilities offered by manycore parallel architectures.

At the same time, the application software that is running on top of the highly parallel computation platforms is becoming increasingly complex. Many large projects often involve tens to hundreds of software developers at a time, making the design of succinct software architectures crucial for the success of the projects. With the growing maturity of open source software available, many software projects are designed as a composition of existing optimized software libraries and infrastructures in order to minimize the effort necessary to construct a new application from scratch.

The expanding variety of applications that can take advantage of parallel microproces-

sors and their increasing complexity are the two important points to keep in mind as we develop technologies to assist software developers to be able to better utilize highly parallel microprocessors.

#### 2.3 Current Parallel Software Development Best Practices

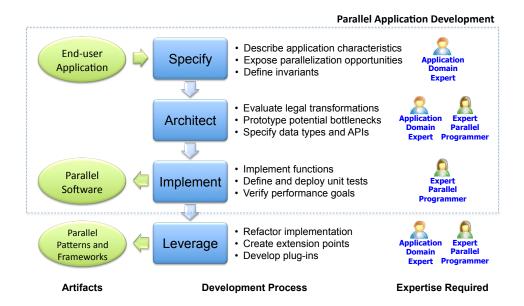

The development of a complex software application involves the coordinated efforts of multiple groups of people with diverse areas of expertise. To successfully construct the end application, they must have a coherent high-level view of a system's structure and organization. Through the process of developing efficient application implementations in diverse fields such as machine learning and computational finance, we found that a three-step process worked well in the construction of efficient parallel application. Figure 2.3 illustrates this three-step process as: specify, architect, and implement.

- 1. In the *specify* step, the application characteristics are described in terms of the type, size, and requirements of the computation required, as well as performance goals that must be met or would be nice to meet. The parallelization opportunities in the application are also exposed, as well as the amount of parallelism that each opportunity entails.

- 2. In the architect step, the design space to be explored is defined. The design space is the set of alternative implementations of the solution that solves the end-user's problem. It is associated with the parallel opportunities that are exposed in the specify step. In this step, the potential performance bottlenecks are also explored and prototyped. The end result is a set of data types and application programming interfaces (APIs).

- 3. In the *implement* step, the functions of the application are implemented by translating the high level descriptions of the application into a software code base, and unit tests are defined and deployed in order to verify functional correctness and to evaluate performance requirements.

The purpose of specifying this three-step process is to partition the design process such that one set of activities should be completed before another set of activities begins. The parallelism opportunities in the *specify* step should be explicitly enumerated before one embarks on the exploration of the design space in the *architect* step. Failure to do so could result in a partially defined design space where better performing implementation alternatives may not be duly explored. All potential bottlenecks in the *architect* step should be analyzed before one starts the detailed implementation in the Implement step. Failure to do so could result in late-stage performance or integration problems that prevent the on-time deployment of a software project from occurring.

Figure 2.3: The three-step process in a parallel applications development flow.

Figure 2.4: The parallel application *Implementation Gap*.

#### 2.4 The Implementation Gap

One can observe two groups of programmers for application development: the parallel programming experts and the application domain experts. The parallel programming experts are often the staff programmers and IT professionals in an organization. They have a deep understanding of the parallel computing platforms. Application domain experts are often the researchers and practitioners in diverse fields like automatic speech recognition, computer vision, and financial risk analytics. They understand application usage characteristics, algorithm variations, and legal transformations of data and control well enough to be able to derive various implementation alternatives to improve application performance.

To achieve an efficient implementation of an application on a highly parallel platform, applications must be designed taking into account the characteristics of the specific application, as well as the capabilities of the underlying computing platform.

Although application domain experts have an in-depth understanding of the application characteristics and requirements, they are often ill equipped to deal with application parallelization challenges because they lack the computing platform insights to anticipate and avoid execution efficiency bottlenecks in various implementation alternatives. For example, Section 5.1.5 demonstrates the nuances in the multicore and manycore computing platforms that a speech recognition domain expert must be aware of to achieve good performance. Specifically, being able to utilize hardware-supported atomic operations can provide a 3x performance gain compared to relying on software-based synchronization mechanisms on the GPU.

Although parallel programming experts have intimate knowledge of the implementation platforms, they often lack the application level perspective to implement application level transformations that can result in significantly more efficient implementations for the application at hand. For example, Section 5.1.4 demonstrates that performing speech model transformations based on application domain expertise can provide up to 2x performance improvements on recognition network traversal speed, which translates to up to 40% improvement in application-level recognition latency.

An application development team that is looking to adopt parallel processing technology must have a collaboration between both application domain experts and parallel programming experts so as to reduce this *implementation gap* (Figure 2.4) in deploying parallel applications.

The implementation gap represents a significant barrier to the successfully construction of efficient implementations. There are very few developers who have expertise in both the application domain and the implementation platform to lead these projects. In order to make parallel programming widely applicable, it is necessary to have a set of application development tools and the infrastructure required to bridge the implementation gap and meet the needs of the end-users of software applications who are demanding an expanding variety of ever more complex applications.

Referring back to Figure 2.3, in the current best practices for parallel software development, parallel programming experts are involved in the Architect and Implement step of every application development project for each usage scenario. In the automatic speech

recognition related application, for example, parallel programming experts must be involved in the development of usage scenarios of an in-car speech recognition system as well as a meeting transcription speech recognition system. While there are many application domains that can benefit from parallel implementations, the different application usage scenarios in each application domain are even more numerous. If parallel programming experts have to be involved in the development of every parallel application, the deployment of highly parallel microprocessors will be severely limited.

#### 2.5 Summary

The "Power Wall", "Memory Wall" and "ILP Wall" are forcing microprocessor architectures to go parallel. The observation here is that the future of computer architecture is heading in the direction of manycore microprocessors, with tens of cores on a chip, and tens of SIMD lanes concurrently executing on each core. This causes a disruption in the software development process, where the traditional sequential hardware abstraction is no longer sufficient for the development of performance-sensitive end-user applications.

Meanwhile, there is an expansion in the variety of recognition, mining, and synthesis based end-user applications that can take advantage of the emerging manycore microprocessor architectures. However, the software is becoming increasingly complex to build.

To effectively implement the great variety of complex software applications with the highly parallel manycore microprocessors, the current best practice is to follow the *specify*, architect, and *implement* three-step process. Yet, going through this process requires both application domain expertise and parallel programming expertise, as having either one or the other alone is not sufficient if one wants to develop efficient parallel software applications. This problematic situation is the parallel application *Implementation Gap*.

Unfortunately, building a team that has both areas of expertise so as to bridge the gap for the development of every end-user application will be cost-prohibitive. At the same time, failure to enable the deployment of efficient end-user applications and demonstrate the value of highly parallel microprocessors will severely stunt the growth of the entire semiconductor industry.

To this end, the establishment of an alternative approach to productively develop efficient and highly parallel software applications is essential. Thus, the next chapter presents a review of the existing work in this area that have attempted to solve this problem, and the following chapters demonstrate a new effective solution toward the closing of the *implementation qap*.

### Chapter 3

## Tools for Closing the Implementation Gap

A tremendous amount of work has been done in software engineering in order to allow larger and more complex problems to be solved using software. This chapter focuses on the techniques that can help resolve today's challenge in closing the implementation gap and enabling "effective" implementation of software on highly parallel microprocessors. Firstly, the metrics for "effectiveness" are defined. Then, three sets of tools are surveyed so as to evaluate their effectiveness in closing the implementation gap. The three sets of tools are: software architecture narratives, software implementation support, and parallel software implementation tools. Finally, a summary of the key lessons learned from prior work is given.

#### 3.1 Metrics for Evaluating Effectiveness

The metrics for the effectiveness of the tools for closing the *Implementation gap* are presented here from the perspective of an application domain expert who is looking to productively implement efficient applications on highly parallel microprocessors.